# Quad, Parallel Input, Voltage Output, 12-/10-Bit Digital-to-Analog Converters

# AD5582/AD5583

#### **FEATURES**

12-Bit Linearity and Monotonic AD5582

10-Bit Linearity and Monotonic AD5583

Wide Operating Range: Single 5 V to 15 V or

Dual ±5 V Supply

Unipolar or Bipolar Operation

Double Buffered Registers Enable Independent or Simultaneous Multichannel Update

4 Independent Rail-to-Rail Reference Inputs

20 mA High Current Output Drive

**Parallel Interface**

**Data Readback Capability**

5 μs Settling Time

**Built-In Matching Resistor Simplifies**

**Negative Reference**

**Unconditionally Stable Under Any Capacitive Loading**

**Compact Footprint: TSSOP-48**

Extended Temperature Range: -40°C to +125°C

### **APPLICATIONS**

Process Control Equipment

Closed-Loop Servo Control

Data Acquisition Systems

Digitally Controlled Calibration

Optical Network Control Loops

4 m to 20 mA Current Transmitter

### GENERAL DESCRIPTION

The AD5582/AD5583 family of quad, 12-/10-bit, voltage output digital-to-analog converters is designed to operate from a single 5 V to 15 V or dual ±5 V supply. It offers the user ease of use in single- or dual-supply systems. Built using an advance BiCMOS process, this high performance DAC is dynamically stable, capable of high current drive, and in small form factor.

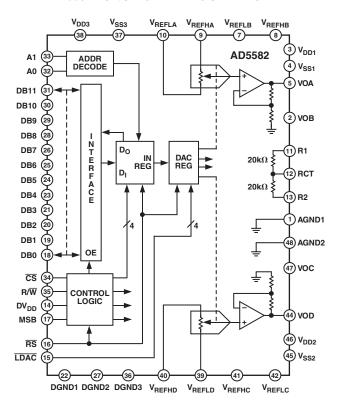

The applied external reference  $V_{REF}$  determines the full-scale output voltage ranges from  $V_{SS}$  to  $V_{DD}$ , resulting in a wide selection of full-scale outputs. For multiplying and wide dynamic applications, ac reference inputs can be as high as  $|V_{DD} - V_{SS}|$ . Two built-in precision trimmed resistors are available and can be configured easily to provide four-quadrant multiplications.

A doubled-buffered parallel interface offers a fast settling time. A common level sensitive load DAC strobe ( $\overline{LDAC}$ ) input allows additional simultaneous update of all DAC outputs. An external asynchronous reset ( $\overline{RS}$ ) forces all registers to the zero code state when the MSB = 0 or to midscale when the MSB = 1.

Both parts are offered in the same pinout and package to allow users to select the appropriate resolution for a given application without PCB layout changes.

### REV. A

Information furnished by Analog Devices is believed to be accurate and reliable. However, no responsibility is assumed by Analog Devices for its use, nor for any infringements of patents or other rights of third parties that may result from its use. No license is granted by implication or otherwise under any patent or patent rights of Analog Devices. Trademarks and registered trademarks are the property of their respective companies.

### AD5582 FUNCTIONAL BLOCK DIAGRAM

DIGITAL CIRCUITRY OMITTED FOR CLARITY

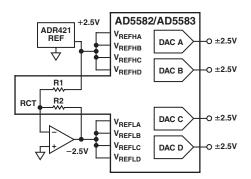

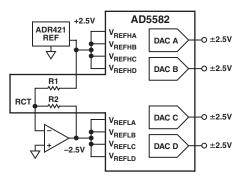

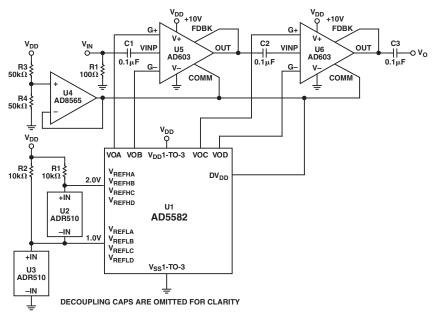

Figure 1. Using Built-In Matching Resistors to Generate a Negative Voltage Reference

The AD5582 is well suited for DAC8412 replacement in medium voltage applications in new designs, as well as any other general purpose multichannel 10- to 12-bit applications.

The AD5582/AD5583 are specified over the extended industrial (-40°C to +125°C) temperature range and offered in a thin and compact 1.1 mm TSSOP-48 package.

One Technology Way, P.O. Box 9106, Norwood, MA 02062-9106, U.S.A. Tel: 781/329-4700 www.analog.com

Fax: 781/326-8703 © 2003 Analog Devices, Inc. All rights reserved.

# AD5582/AD5583—SPECIFICATIONS

# $\begin{array}{l} \textbf{ELECTRICAL CHARACTERISTICS} & (V_{DD}=+5 \text{ V, } V_{SS}=-5 \text{ V, DV}_{DD}=+5 \text{ V} \pm 10\%, V_{REFH}=+2.5 \text{ V, } V_{REFL}=-2.5 \text{ V, } \\ -40 ^{\circ}\text{C} < T_{A} < +125 ^{\circ}\text{C, unless otherwise noted.}) \end{array}$

| Parameter                                                             | Symbol                             | Condition                                                                                                            | Min                                      | Typ <sup>1</sup> | Max               | Unit           |

|-----------------------------------------------------------------------|------------------------------------|----------------------------------------------------------------------------------------------------------------------|------------------------------------------|------------------|-------------------|----------------|

| STATIC PERFORMANCE<br>Resolution <sup>2</sup>                         | N                                  | AD5582<br>AD5583                                                                                                     |                                          | 12<br>10         |                   | Bits<br>Bits   |

| Relative Accuracy <sup>3</sup> Differential Nonlinearity <sup>3</sup> | INL<br>DNL                         | Monotonic                                                                                                            | -1<br>-1                                 | 10               | +1                | LSB<br>LSB     |

| Zero-Scale Error                                                      | V <sub>ZSE</sub>                   | Data = $000_{\rm H}$ for AD5582 and AD5583                                                                           | -2                                       |                  | +2                | LSB            |

| Gain Error                                                            | $V_{GE} \ V_{GE}$                  | Data = $0xFFF_H$ for AD5582<br>Data = $0x3FF_H$ for AD5583                                                           | $\begin{vmatrix} -2 \\ -4 \end{vmatrix}$ |                  | +2<br>+4          | LSB<br>LSB     |

| Gain Error<br>Full-Scale Tempco <sup>4</sup>                          | $V_{GE}$ $TCV_{FS}$                | $V_{\rm DD} = 2.7 \text{ V to } 4.5 \text{ V}$                                                                       | -4                                       | 1.5              | +4                | LSB<br>ppm/°C  |

| REFERENCE INPUT                                                       |                                    |                                                                                                                      |                                          |                  |                   |                |

| V <sub>REFH</sub> Input Range                                         | $V_{REFH}$                         |                                                                                                                      | $V_{REFL} + 0.5$                         |                  | $V_{\mathrm{DD}}$ | V              |

| V <sub>REFL</sub> Input Range <sup>5</sup>                            | $V_{REFL}$                         |                                                                                                                      | V <sub>SS</sub>                          |                  | $V_{REFH} - 0.5$  | V              |

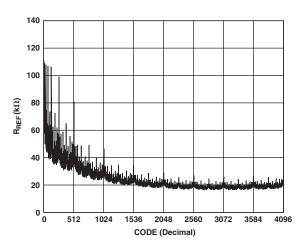

| Input Resistance                                                      | $R_{REF}$                          | Data = $555_H$ (Minimum $R_{REF}$ )<br>for AD5582 and $155_H$ for AD5583                                             | 12                                       | 20               |                   | kΩ¹            |

| Input Capacitance <sup>4</sup>                                        | $C_{REF}$                          | D. SEE C. ADSECT                                                                                                     |                                          | 80               | <b>5</b> 00       | pF             |

| REF Input Current                                                     | I <sub>REF</sub>                   | Data = $555_H$ for AD5582                                                                                            |                                          |                  | 500               | μA<br>MHz      |

| REF Multiplying Bandwidth R1–R2 Matching                              | BW <sub>REF</sub><br>R1/R2         | Code = Full Scale<br>AD5582                                                                                          |                                          |                  | 1.3<br>±0.025     | %              |

| K1-K2 Watching                                                        | K1/K2                              | AD5583                                                                                                               |                                          |                  | ±0.100            | %              |

| ANALOG OUTPUT                                                         |                                    |                                                                                                                      |                                          |                  |                   |                |

| Output Current <sup>6</sup>                                           | $I_{OUT}$                          | Data = $800_H$ for AD5582 and $200_H$ for AD5583, $\Delta V_{OUT} \le 2 \text{ mV}$                                  |                                          |                  | ±2                | mA             |

| Output Current <sup>6</sup>                                           | I <sub>OUT</sub>                   | Data = $800_H$ for AD5582 and                                                                                        |                                          |                  |                   |                |

| •                                                                     | 001                                | $200_{\rm H}$ for AD5583, $\Delta V_{\rm OUT} \le  -8 \text{ mV} $                                                   |                                          |                  | +20               | mA             |

|                                                                       |                                    | $\Delta V_{OUT} \le \pm 15 \text{ mV}$                                                                               |                                          |                  | -20               | mA             |

| Capacitive Load <sup>4, 7</sup>                                       | $C_{L}$                            | No Oscillation                                                                                                       |                                          | Note 7           |                   | pF             |

| LOGIC INPUTS                                                          |                                    |                                                                                                                      |                                          |                  |                   |                |

| Logic Input Low Voltage                                               | $V_{IL}$                           | $DV_{DD} = 5 V \pm 10\%$                                                                                             |                                          |                  | 0.8               | V              |

|                                                                       |                                    | $DV_{DD} = 3 V \pm 10\%$                                                                                             |                                          |                  | 0.4               | V              |

| Logic Input High Voltage                                              | $V_{IH}$                           | $DV_{DD} = 5 V \pm 10\%$                                                                                             | 2.4                                      |                  |                   | V              |

| I . I . I . C                                                         | т.                                 | $DV_{DD} = 3 V \pm 10\%$                                                                                             | 2.1                                      | 0.01             | •                 | V              |

| Input Leakage Current                                                 | $I_{IL}$                           |                                                                                                                      |                                          | 0.01             | 1                 | μA             |

| Input Capacitance <sup>4</sup> Output Voltage High                    | C <sub>IL</sub><br>V <sub>OH</sub> | $I_{OH} = -0.8 \text{ mA}$                                                                                           | 2.4                                      | 5                |                   | pF<br>V        |

| Output Voltage Low                                                    | V <sub>OL</sub>                    | $I_{OL} = 1.2 \text{ mA}, T_A = 85^{\circ}\text{C},$                                                                 | 2.1                                      |                  | 0.4               | V              |

| output voltage now                                                    | , OL                               | $I_{OL} = 0.6 \text{ mA}, DV_{DD} = 3 \text{ V}$                                                                     |                                          |                  | 0.1               | ,              |

|                                                                       |                                    | $I_{OL} = 1.0 \text{ mA}, T_A = 125^{\circ}\text{C},$                                                                |                                          |                  | 0.4               | V              |

|                                                                       |                                    | $I_{OL} = 0.5 \text{ mA}, DV_{DD} = 3 \text{ V}$                                                                     |                                          |                  |                   |                |

| AC CHARACTERISTICS                                                    |                                    |                                                                                                                      |                                          |                  |                   |                |

| Output Slew Rate                                                      | SR                                 | Data = Zero Scale to Full Scale to Zero Scale                                                                        |                                          | 2                |                   | V/µs           |

| Settling Time <sup>8</sup>                                            | $t_S$                              | To ±0.1% of Full Scale                                                                                               |                                          | 5                |                   | μs             |

| DAC Glitch                                                            | Q                                  | Code 7FF <sub>H</sub> to 800 <sub>H</sub> to 7FF <sub>H</sub><br>for AD5582 and 1FF <sub>H</sub> to 200 <sub>H</sub> |                                          | 100              |                   | nV-s           |

|                                                                       |                                    | to 1FF <sub>H</sub> for AD5583                                                                                       |                                          |                  |                   |                |

| Digital Feedthrough                                                   | $V_{OUT}/t_{CS}$                   | Data = Midscale, $\overline{CS}$ Toggles at $f = 16$ MHz                                                             |                                          | 5                |                   | nV-s           |

| Analog Crosstalk                                                      | V <sub>OUT</sub> /V <sub>REF</sub> | $V_{REF} = 1.5 \text{ V dc} + 1 \text{ V p-p},$<br>$Data = 000_{H}, f = 100 \text{ kHz}$                             |                                          | -80              |                   | dB             |

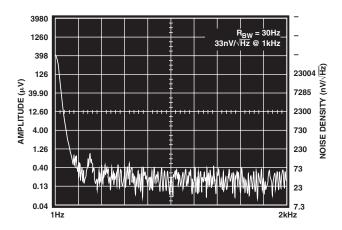

| Output Noise                                                          | e <sub>N</sub>                     | f = 1 kHz                                                                                                            |                                          | 33               |                   | $nV/\sqrt{Hz}$ |

| Parameter                            | Symbol                  | Condition                                         | Min | Typ <sup>1</sup> | Max | Unit  |

|--------------------------------------|-------------------------|---------------------------------------------------|-----|------------------|-----|-------|

| SUPPLY CHARACTERISTICS               |                         |                                                   |     |                  |     |       |

| Single-Supply Voltage Range          | $V_{ m DD}$             | $V_{SS} = 0 \text{ V}$                            | 3   |                  | 18  | V     |

| Dual-Supply Voltage Range            | $V_{\rm DD}/V_{\rm SS}$ | $V_{\rm DD} = +2.7 \text{ V to } +6.5 \text{ V},$ | -9  |                  | +9  | V     |

|                                      |                         | $V_{SS} = -6.5 \text{ V to } -2.7 \text{ V}$      |     |                  |     |       |

| Digital Logic Supply                 | $DV_{DD}$               |                                                   | 2.7 |                  | 8   | V     |

| Positive Supply Current <sup>6</sup> | $I_{ m DD}$             | $V_{IL} = 0 V$ , No Load                          |     | 1.7              | 3   | mA    |

| Negative Supply Current              | $I_{SS}$                | $V_{IL} = 0 V$ , No Load                          |     | 1.5              | 3   | mA    |

| Power Dissipation                    | $P_{DISS}$              | $V_{IL} = 0 V$ , No Load                          |     | 16               | 30  | mW    |

| Power Supply Sensitivity             | P <sub>SS</sub>         | $\Delta V_{\mathrm{DD}} = \pm 5\%$                |     | 30               |     | ppm/V |

### NOTES

Specifications subject to change without notice.

# $\begin{array}{l} \textbf{ELECTRICAL CHARACTERISTICS} & (V_{DD}=15 \ V, \ V_{SS}=0 \ V, \ DV_{DD}=5 \ V \ \pm \ 10\%, \ V_{REFH}=10 \ V, \ V_{REFL}=0 \ V, \\ -40 ^{\circ}C < T_{A} < +125 ^{\circ}C, \ unless \ otherwise \ noted.) \end{array}$

| Parameter                                  | Symbol           | Condition                                                                | Min              | Typ <sup>1</sup> | Max              | Unit        |

|--------------------------------------------|------------------|--------------------------------------------------------------------------|------------------|------------------|------------------|-------------|

| STATIC PERFORMANCE                         |                  |                                                                          |                  |                  |                  |             |

| Resolution <sup>2</sup>                    | N                | AD5582                                                                   |                  | 12               |                  | Bits        |

|                                            |                  | AD5583                                                                   |                  | 10               |                  | Bits        |

| Relative Accuracy <sup>3</sup>             | INL              |                                                                          | -1               |                  | +1               | LSB         |

| Differential Nonlinearity <sup>3</sup>     | DNL              | Monotonic                                                                | -1               |                  |                  | LSB         |

| Zero-Scale Error                           | V <sub>ZSE</sub> | $Data = 000_{H} \text{ for AD5582}$                                      | -2               |                  | +2               | LSB         |

|                                            |                  | and AD5583                                                               | _                |                  |                  |             |

| Gain Error                                 | $V_{GE}$         | Data = $0xFFF_H$ for AD5582                                              | -2               |                  | +2               | LSB         |

| T # 0 1 T 4                                | V <sub>GE</sub>  | Data = $0x3FF_H$ for AD5583                                              | -4               |                  | +4               | LSB         |

| Full-Scale Tempco <sup>4</sup>             | $TCV_{FS}$       |                                                                          |                  | 1.5              |                  | ppm/°C      |

| REFERENCE INPUT                            |                  |                                                                          |                  |                  |                  |             |

| V <sub>REFH</sub> Input Range              | $V_{REFH}$       |                                                                          | $V_{REFL} + 0.5$ |                  | $V_{ m DD}$      | V           |

| V <sub>REFL</sub> Input Range <sup>5</sup> | $V_{REFL}$       |                                                                          | $V_{SS}$         |                  | $V_{REFH} - 0.5$ | V           |

| Input Resistance                           | $R_{REF}$        | Data = $555_H$ (Minimum $R_{REF}$ )<br>for AD5582 and $155_H$ for AD5583 | 12               | 20               |                  | $k\Omega^1$ |

| Input Capacitance <sup>4</sup>             | $C_{REF}$        |                                                                          |                  | 80               |                  | pF          |

| REF Input Current                          | $I_{REF}$        | $Data = 555_{H} \text{ for AD5582}$                                      |                  |                  | 1000             | μΑ          |

| REF Multiplying Bandwidth                  | $BW_{REF}$       | Code = Full Scale                                                        |                  |                  | 1.3              | MHz         |

| R1-R2 Matching                             | R1/R2            | AD5582                                                                   |                  |                  | $\pm 0.025$      | %           |

|                                            |                  | AD5583                                                                   |                  |                  | $\pm 0.100$      | %           |

| ANALOG OUTPUT                              |                  |                                                                          |                  |                  |                  |             |

| Output Current <sup>6</sup>                | I <sub>OUT</sub> | Data = $800_H$ for AD5582 and                                            |                  |                  | 2                | mA          |

| •                                          |                  | $200_{\rm H}$ for AD5583, $\Delta V_{\rm OUT} \le 2$ mV                  |                  |                  |                  |             |

| Output Current <sup>6</sup>                | I <sub>OUT</sub> | Data = $800_H$ for AD5582 and                                            |                  |                  |                  |             |

| -                                          |                  | $200_{\rm H}$ for AD5583, $\Delta V_{\rm OUT} \le  -8 \text{ mV} $       |                  |                  | +20              | mA          |

|                                            |                  | $\Delta V_{OUT} \le 15 \text{ mV}$                                       |                  |                  | -20              | mA          |

| Capacitive Load <sup>4, 7</sup>            | $C_{L}$          | No Oscillation                                                           |                  | Note 7           |                  | pF          |

REV. A -3-

<sup>&</sup>lt;sup>1</sup>Typical specifications represent average readings measured at 25°C.

<sup>&</sup>lt;sup>2</sup>DAC Output Equation:  $V_{OUT} = V_{REFL} + [(V_{REFH} - V_{REFL}) \times D/2^N]$ , where D = data loaded in corresponding DAC Register A, B, C, D, and N equals the number of bits; AD5582 = 12 bits, AD5583 = 10 bits. One LSB step voltage =  $(V_{REFH} - V_{REFL})/4096$  V and  $(V_{REFH} - V_{REFL})/1024$  V for AD5582 and AD5583, respectively.

<sup>&</sup>lt;sup>3</sup>The first two codes (000<sub>H</sub>, 001<sub>H</sub>) of the AD5583 and the first four codes (000<sub>H</sub>, 001<sub>H</sub>, 002<sub>H</sub>, 003<sub>H</sub>) of the AD5582 are excluded from the linearity error measurement in single-supply operation.

<sup>&</sup>lt;sup>4</sup>These parameters are guaranteed by design and not subject to production testing.

$<sup>^5</sup>$ Dual-supply operation,  $V_{REFL} = V_{SS}$ , exclude the lowest eight codes for the AD5582 and two codes for the AD5583 for INL and DNL errors.

<sup>&</sup>lt;sup>6</sup>Short circuit output and supply currents are 24 mA and 25 mA, respectively.

<sup>&</sup>lt;sup>7</sup>Part is stable under any capacitive loading conditions.

<sup>&</sup>lt;sup>8</sup>The settling time specification does not apply for negative-going transitions within the last 3 LSBs of ground in single-supply operation.

# **ELECTRICAL CHARACTERISTICS** (continued)

| Parameter                            | Symbol                      | Condition                                                         | Min  | Typ <sup>1</sup> | Max  | Unit           |

|--------------------------------------|-----------------------------|-------------------------------------------------------------------|------|------------------|------|----------------|

| LOGIC INPUTS/OUTPUTS                 |                             |                                                                   |      |                  |      |                |

| Logic Input Low Voltage              | $V_{ m IL}$                 |                                                                   |      |                  | 0.8  | V              |

|                                      |                             | $DV_{DD} = 3 V \pm 10\%$                                          |      |                  | 0.4  | V              |

| Logic Input High Voltage             | $V_{IH}$                    |                                                                   | 2.4  |                  |      | V              |

|                                      |                             | $DV_{DD} = 3 V \pm 10\%$                                          | 2.1  |                  |      | V              |

| Input Leakage Current                | $I_{IL}$                    |                                                                   |      |                  |      | μA             |

| Input Capacitance <sup>4</sup>       | $C_{IL}$                    |                                                                   |      |                  |      | pF             |

| Output Voltage High                  | $V_{OH}$                    | $I_{OH} = -0.8 \text{ mA}$                                        | 2.4  |                  |      | V              |

| Output Voltage Low                   | $V_{OL}$                    | $I_{OL} = 1.2 \text{ mA}, T_A = 85^{\circ}\text{C},$              |      |                  | 0.4  | V              |

|                                      |                             | $I_{OL} = 0.6 \text{ mA}, DV_{DD} = 3 \text{ V}$                  |      |                  |      |                |

|                                      | $V_{OL}$                    | $I_{OL} = 1.0 \text{ mA}, T_A = 125^{\circ}\text{C},$             |      |                  | 0.4  | V              |

|                                      |                             | $I_{OL}$ = 0.5 mA, $DV_{DD}$ = 3 V                                |      |                  |      |                |

| AC CHARACTERISTICS                   |                             |                                                                   |      |                  |      |                |

| Output Slew Rate                     | SR                          | Data = Zero Scale to Full Scale                                   |      | 2                |      | V/µs           |

|                                      |                             | to Zero Scale                                                     |      |                  |      |                |

| Settling Time <sup>8</sup>           | $t_{S}$                     | To ±0.1% of Full Scale                                            |      | 14               |      | μs             |

| DAC Glitch                           | Q                           | Code 7FF <sub>H</sub> to 800 <sub>H</sub> to 7FF <sub>H</sub> for |      | 100              |      | nV-s           |

|                                      |                             | AD5582 and $1FF_H$ to $200_H$ to                                  |      |                  |      |                |

|                                      |                             | 1FF <sub>H</sub> for AD5583                                       |      |                  |      |                |

| Digital Feedthrough                  | $V_{OUT}/t_{CS}$            | Data = Midscale, $\overline{CS}$ Toggles at                       |      | 5                |      | nV-s           |

|                                      |                             | f = 16 MHz                                                        |      |                  |      |                |

| Analog Crosstalk                     | $V_{OUT}/V_{REF}$           | $V_{REF} = 1.5 \text{ V dc} + 1 \text{ V p-p},$                   |      | -80              |      | dB             |

|                                      |                             | Data = $000_{H}$ , f = $100 \text{ kHz}$                          |      |                  |      | /=-            |

| Output Noise                         | e <sub>N</sub>              | f = 1 kHz                                                         |      | 33               |      | $nV/\sqrt{Hz}$ |

| SUPPLY CHARACTERISTICS               | S                           |                                                                   |      |                  |      |                |

| Single-Supply Voltage Range          | $V_{ m DD}$                 | $V_{SS} = 0 V$                                                    | 3    |                  | 16.5 | V              |

| Dual-Supply Voltage Range            | $V_{\rm DD}/V_{\rm SS}$     | $V_{DD} = +2.7 \text{ V to } +6.5 \text{ V},$                     | -6.5 |                  | +6.5 | V              |

|                                      |                             | $V_{SS} = -6.5 \text{ V to } -2.7 \text{ V}$                      |      |                  |      |                |

| Digital Logic Supply                 | $\mathrm{DV}_{\mathrm{DD}}$ |                                                                   | 2.7  |                  | 6.5  | V              |

| Positive Supply Current <sup>6</sup> | $I_{ m DD}$                 | $V_{\rm IL}$ = 0 V, No Load                                       |      | 2.3              | 3.5  | mA             |

| Power Dissipation                    | $P_{\mathrm{DISS}}$         | $V_{\rm IL}$ = 0 V, No Load                                       |      | 34.5             | 52.5 | mW             |

| Power Supply Sensitivity             | PSS                         | $\Delta V_{DD} = \pm 5\%$                                         |      | 30               |      | ppm/V          |

#### NOTES

Specifications subject to change without notice.

<sup>&</sup>lt;sup>1</sup>Typical specifications represent average readings measured at 25°C.

<sup>&</sup>lt;sup>2</sup>DAC Output Equation:  $V_{OUT} = V_{REFL} + [(V_{REFH} - V_{REFL}) \times D/2^N]$ , where D = data in decimal loaded in corresponding DAC Register A, B, C, D, and N equals the number of bits; AD5582 = 12 bits, AD5583 = 10 bits. One LSB step voltage =  $(V_{REFH} - V_{REFL})/4096$  V and =  $(V_{REFH} - V_{REFL})/1024$  V for AD5582 and AD5583, respectively.

<sup>&</sup>lt;sup>3</sup>The first two codes (000<sub>H</sub>, 001<sub>H</sub>) of the AD5583 and the first four codes (000<sub>H</sub>, 001<sub>H</sub>, 002<sub>H</sub>, 003<sub>H</sub>) of the AD5582 are excluded from the linearity error measurement in single-supply operation.

<sup>&</sup>lt;sup>4</sup>These parameters are guaranteed by design and not subject to production testing.

$<sup>^{5}</sup>$ Dual-supply operation,  $V_{REFL} = V_{SS}$ , exclude the lowest eight codes for the AD5582 and two codes for the AD5583 for INL and DNL errors.

<sup>&</sup>lt;sup>6</sup>Short circuit output and supply currents are 24 mA and 25 mA, respectively.

<sup>&</sup>lt;sup>7</sup>Part is stable under any capacitive loading conditions.

<sup>&</sup>lt;sup>8</sup>The settling time specification does not apply for negative-going transitions within the last 3 LSBs of ground in single-supply operation.

# TIMING CHARACTERISTICS

(V\_DD = 15 V or 5 V, V\_SS = 0 V, DV\_DD = 5 V  $\pm$  10%, V\_REFH = 10 V, V\_REFL = 0 V,  $-40^{\circ}C < T_A < +125^{\circ}C$ , unless otherwise noted.)

| Parameter                          | Symbol             | Condition             | Min | Typ | Max | Unit |

|------------------------------------|--------------------|-----------------------|-----|-----|-----|------|

| INTERFACE TIMING*                  |                    |                       |     |     |     |      |

| Chip Select Write Pulse Width      | t <sub>WCS</sub>   |                       | 20  |     |     | ns   |

| Chip Select Read Pulse Width       | t <sub>RCS</sub>   |                       | 130 |     |     | ns   |

| Write Setup                        | t <sub>WS</sub>    |                       | 35  |     |     | ns   |

| Write Hold                         | t <sub>WH</sub>    |                       | 0   |     |     | ns   |

| Address Setup                      | t <sub>AS</sub>    |                       | 35  |     |     | ns   |

| Address Hold                       | t <sub>AH</sub>    |                       | 0   |     |     | ns   |

| Load Setup                         | $t_{LS}$           |                       | 0   |     |     | ns   |

| Load Hold                          | $t_{LH}$           |                       | 0   |     |     | ns   |

| Write Data Setup                   | $t_{\mathrm{WDS}}$ |                       | 35  |     |     | ns   |

| Write Data Hold                    | $t_{ m WDH}$       |                       | 0   |     |     | ns   |

| Load Data Pulse Width              | $t_{ m LDW}$       |                       | 20  |     |     | ns   |

| Reset Pulse Width                  | t <sub>RESET</sub> |                       | 20  |     |     | ns   |

| Read Data Hold                     | t <sub>RDH</sub>   |                       | 0   |     |     | ns   |

| Read Data Setup                    | $t_{RDS}$          |                       | 0   |     |     | ns   |

| Data to Hi-Z                       | $t_{\mathrm{DZ}}$  | $C_L = 10 \text{ pF}$ |     |     | 100 | ns   |

| Chip Select to Data                | $t_{CSD}$          | $C_L = 10 \text{ pF}$ |     |     | 100 | ns   |

| Chip Select Repetitive Pulse Width | $t_{CSP}$          |                       | 10  |     |     | ns   |

| Load Setup in Double Buffer Mode   | $t_{ m LDS}$       |                       | 20  |     |     | ns   |

| Load Data Hold                     | $t_{ m LDH}$       |                       | 0   |     |     | ns   |

<sup>\*</sup>All input control signals are specified with  $t_R = t_F = 2$  ns (10% to 90% of 3 V) and timed from a voltage level of 1.5 V. Specifications subject to change without notice.

$\begin{tabular}{ll} \textbf{TIMING CHARACTERISTICS} & (V_{DD}=15 \ V \ or \ 5 \ V, \ V_{SS}=0 \ V, \ DV_{DD}=3 \ V \ \pm \ 10\%, \ V_{REFH}=10 \ V, \ V_{REFL}=0 \ V, \ -40 ^{\circ}C \ < T_A \ < \ +125 ^{\circ}C, \ unless otherwise noted.) \\ \end{tabular}$

| Parameter                          | Symbol             | Condition             | Min | Тур | Max | Unit |

|------------------------------------|--------------------|-----------------------|-----|-----|-----|------|

| INTERFACE TIMING*                  |                    |                       |     |     |     |      |

| Chip Select Write Pulse Width      | t <sub>WCS</sub>   |                       | 35  |     |     | ns   |

| Chip Select Read Pulse Width       | t <sub>RCS</sub>   |                       | 130 |     |     | ns   |

| Write Setup                        | t <sub>WS</sub>    |                       | 50  |     |     | ns   |

| Write Hold                         | t <sub>WH</sub>    |                       | 0   |     |     | ns   |

| Address Setup                      | t <sub>AS</sub>    |                       | 50  |     |     | ns   |

| Address Hold                       | t <sub>AH</sub>    |                       | 0   |     |     | ns   |

| Load Setup                         | t <sub>LS</sub>    |                       | 0   |     |     | ns   |

| Load Hold                          | $t_{LH}$           |                       | 0   |     |     | ns   |

| Write Data Setup                   | $t_{ m WDS}$       |                       | 50  |     |     | ns   |

| Write Data Hold                    | $t_{ m WDH}$       |                       | 0   |     |     | ns   |

| Load Data Pulse Width              | $t_{ m LDW}$       |                       | 35  |     |     | ns   |

| Reset Pulse Width                  | t <sub>RESET</sub> |                       | 35  |     |     | ns   |

| Read Data Hold                     | t <sub>RDH</sub>   |                       | 0   |     |     | ns   |

| Read Data Setup                    | $t_{ m RDS}$       |                       | 0   |     |     | ns   |

| Data to Hi-Z                       | $t_{\mathrm{DZ}}$  | $C_L = 10 \text{ pF}$ | 80  |     | 100 | ns   |

| Chip Select to Data                | $t_{CSD}$          | $C_L = 10 \text{ pF}$ | 80  |     | 100 | ns   |

| Chip Select Repetitive Pulse Width | $t_{CSP}$          |                       | 20  |     |     | ns   |

| Load Setup in Double Buffer Mode   | $t_{ m LDS}$       |                       | 35  |     |     | ns   |

| Load Data Hold                     | $t_{ m LDH}$       |                       | 0   |     |     | ns   |

<sup>\*</sup>All input control signals are specified with  $t_R = t_F = 2$  ns (10% to 90% of 3 V) and timed from a voltage level of 1.5 V. Specifications subject to change without notice.

REV. A -5-

### **ABSOLUTE MAXIMUM RATINGS\***

| $V_{DD}$ to $V_{SS}$                                                 |

|----------------------------------------------------------------------|

| $V_{DD}$ to GND0.3 V to +18 V                                        |

| $V_{SS}$ to GND +0.3 V to –9 V                                       |

| $V_{DD}$ to $V_{REF+}$ –0.3 V to +18 V                               |

| $V_{REF-}$ to $V_{SS}$                                               |

| $V_{REFH}$ to $V_{REFL}$                                             |

| $DV_{DD}$ to $GND$                                                   |

| Logic Inputs to GND $V_{SS} - 0.3 \text{ V}, V_{DD} + 0.3 \text{ V}$ |

| $V_{OUT}$ to GND $V_{SS}$ – 0.3 V, $V_{DD}$ + 0.3 V                  |

| I <sub>OUT</sub> Short Circuit to GND                                |

| Thermal Resistance Junction to Ambient, $\theta_{IA}$ 115°C/W        |

| Thermal Resistance Junction to Case, $\theta_{IC}$ 42°C/W |

|-----------------------------------------------------------|

| Maximum Junction Temperature (T <sub>J</sub> Max) 150°C   |

| Package Power Dissipation = $(T_I Max - T_A)/\theta_{IA}$ |

| Operating Temperature Range40°C to +125°C                 |

| Storage Temperature Range65°C to +150°C                   |

| Lead Temperature                                          |

| RV-48 (Soldering, 60 secs) 300°C                          |

\*Stresses above those listed under Absolute Maximum Ratings may cause permanent damage to the device. This is a stress rating only; functional operation of the device at these or any other conditions above those indicated in the operational sections of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

### ORDERING GUIDE<sup>1</sup>

| Model                       | Resolution<br>(Bits) | Temperature<br>Range | Package<br>Description | Package<br>Option | Container<br>Quantity | Top<br>Marking <sup>2</sup> |

|-----------------------------|----------------------|----------------------|------------------------|-------------------|-----------------------|-----------------------------|

| AD5582YRV-REEL <sup>1</sup> | 12                   | −40°C to +125°C      | TSSOP-48               | RV-48             | 2500                  | AD5582Y                     |

| AD5583YRV-REEL              | 10                   | –40°C to +125°C      | TSSOP-48               | RV-48             | 2500                  | AD5583Y                     |

| $AD5582YRV^{1}$             | 12                   | −40°C to +125°C      | TSSOP-48               | RV-48             | 39                    | AD5582Y                     |

| AD5583YRV                   | 10                   | −40°C to +125°C      | TSSOP-48               | RV-48             | 39                    | AD5583Y                     |

### NOTES

### CAUTION \_

ESD (electrostatic discharge) sensitive device. Electrostatic charges as high as 4000 V readily accumulate on the human body and test equipment and can discharge without detection. Although the AD5582/AD5583 features proprietary ESD protection circuitry, permanent damage may occur on devices subjected to high energy electrostatic discharges. Therefore, proper ESD precautions are recommended to avoid performance degradation or loss of functionality.

-6- REV. A

$<sup>^{1}</sup>$ The AD5582 contains 4116 transistors. The die size measures 108 mil imes 144 mil.

<sup>&</sup>lt;sup>2</sup>First row marking is shown in the table above. Second row marking contains date code in YYWW format. Third row marking contains the lot number.

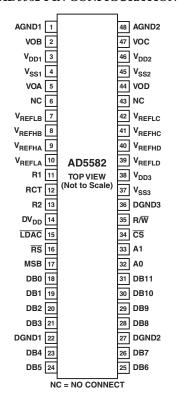

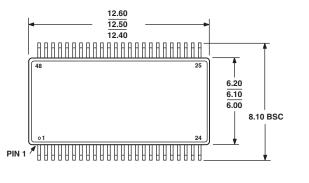

### **AD5582 PIN CONFIGURATION**

### **AD5582 PIN FUNCTION DESCRIPTIONS\***

| Pin<br>No. | Mnemonic                    | Description                                   | Pin<br>No. | Mnemonic           | Description                               |

|------------|-----------------------------|-----------------------------------------------|------------|--------------------|-------------------------------------------|

| 1          | AGND1                       | Analog Ground for DAC A and B                 | 25         | DB6                | Data Bit 6                                |

| 2          | VOB                         | DAC B Output                                  | 26         | DB7                | Data Bit 7                                |

| 3          | $V_{\mathrm{DD1}}$          | Positive Power Supply for DAC A and B         | 27         | DGND2              | Digital Ground 2                          |

| 4          | $V_{SS1}$                   | Negative Power Supply for DAC A and B         | 28         | DB8                | Data Bit 8                                |

| 5          | VOA                         | DAC A Output                                  | 29         | DB9                | Data Bit 9                                |

| 6          | NC                          | No Connect                                    | 30         | DB10               | Data Bit 10                               |

| 7          | V <sub>REFLB</sub>          | DAC B Voltage Reference Low Terminal          | 31         | DB11               | Data Bit 11                               |

| 8          | $V_{REFHB}$                 | DAC B Voltage Reference High Terminal         | 32         | A0                 | Address Input 0                           |

| 9          | $V_{REFHA}$                 | DAC A Voltage Reference High Terminal         | 33         | A1                 | Address Input 1                           |

| 10         | V <sub>REFLA</sub>          | DAC A Voltage Reference Low Terminal          | 34         | CS                 | Chip Select, Active Low                   |

| 11         | R1                          | R1 Terminal (for Negative Reference)          | 35         | $R/\overline{W}$   | Read/Write Mode Select                    |

| 12         | RCT                         | Center Tap Terminal (for Negative Reference)  | 36         | DGND3              | Digital Ground 3                          |

| 13         | R2                          | R2 Terminal (for Negative Reference)          | 37         | $V_{SS3}$          | Negative Power Supply for Analog Switches |

| 14         | $\mathrm{DV}_{\mathrm{DD}}$ | Power Supply for Digital Circuits             | 38         | $V_{\mathrm{DD3}}$ | Positive Power Supply for Analog Switches |

| 15         | LDAC                        | DAC Register Load, Active Low Level Sensitive | 39         | $V_{REFLD}$        | DAC D Voltage Reference Low Terminal      |

| 16         | RS                          | Reset Strobe                                  | 40         | $V_{REFHD}$        | DAC D Voltage Reference High Terminal     |

| 17         | MSB                         | $MSB = 0$ , Reset to $000_H$ .                | 41         | $V_{REFHC}$        | DAC C Voltage Reference High Terminal     |

|            |                             | $MSB = 1$ , Reset to $800_H$ .                | 42         | $V_{REFLC}$        | DAC C Voltage Reference Low Terminal      |

| 18         | DB0                         | Data Bit 0                                    | 43         | NC                 | No Connect                                |

| 19         | DB1                         | Data Bit 1                                    | 44         | VOD                | DAC D Output                              |

| 20         | DB2                         | Data Bit 2                                    | 45         | $V_{SS2}$          | Negative Power Supply for DAC C and D     |

| 21         | DB3                         | Data Bit 3                                    | 46         | $V_{\mathrm{DD2}}$ | Positive Power Supply for DAC C and D     |

| 22         | DGND1                       | Digital Ground 1                              | 47         | VOC                | DAC C Output                              |

| 23         | DB4                         | Data Bit 4                                    | 48         | AGND2              | Analog Ground for DAC C and D             |

| 24         | DB5                         | Data Bit 5                                    |            |                    |                                           |

<sup>\*</sup>AD5582 optimizes internal layout design to reduce die area so that all supply voltage pins are required to be connected externally. See Figure 5.

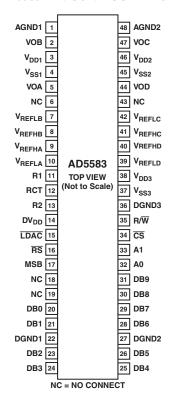

### **AD5583 PIN CONFIGURATION**

### **AD5583 PIN FUNCTION DESCRIPTIONS\***

| Pin<br>No. | Mnemonic                    | Description                                   | Pin<br>No. | Mnemonic           | Description                               |

|------------|-----------------------------|-----------------------------------------------|------------|--------------------|-------------------------------------------|

| 1          | AGND1                       | Analog Ground for DAC A and B                 | 25         | DB4                | Data Bit 4                                |

| 2          | VOB                         | DAC B Output                                  | 26         | DB5                | Data Bit 5                                |

| 3          | $V_{\mathrm{DD1}}$          | Positive Power Supply for DAC A and B         | 27         | DGND2              | Digital Ground 2                          |

| 4          | $V_{SS1}$                   | Negative Power Supply for DAC A and B         | 28         | DB6                | Data Bit 6                                |

| 5          | VOA                         | DAC A Output                                  | 29         | DB7                | Data Bit 7                                |

| 6          | NC                          | No Connect (Do Not Connect Anything           | 30         | DB8                | Data Bit 8                                |

| _          |                             | other than Dummy Pad)                         | 31         | DB9                | Data Bit 9                                |

| 7          | V <sub>REFLB</sub>          | DAC B Voltage Reference Low Terminal          | 32         | A0                 | Address Input 0                           |

| 8          | V <sub>REFHB</sub>          | DAC B Voltage Reference High Terminal         | 33         | A1                 | Address Input 1                           |

| 9          | V <sub>REFHA</sub>          | DAC A Voltage Reference High Terminal         | 34         | CS                 | Chip Select, Active Low                   |

| 10         | V <sub>REFLA</sub>          | DAC A Voltage Reference Low Terminal          | 35         | $R/\overline{W}$   | Read/Write Mode Select                    |

| 11         | R1                          | R1 Terminal (for Negative Reference)          | 36         | DGND3              | Digital Ground 3                          |

| 12         | RCT                         | Center Tap Terminal (for Negative Reference)  | 37         | $V_{SS3}$          | Negative Power Supply for Analog Switches |

| 13         | R2                          | R2 Terminal (for Negative Reference)          | 38         | $V_{\mathrm{DD3}}$ | Positive Power Supply for Analog Switches |

| 14         | $\mathrm{DV}_{\mathrm{DD}}$ | Power Supply for Digital Circuits             | 39         | V <sub>REFLD</sub> | DAC D Voltage Reference Low Terminal      |

| 15         | LDAC                        | DAC Register Load, Active Low Level Sensitive | 40         | $V_{REFHD}$        | DAC D Voltage Reference High Terminal     |

| 16         | RS                          | Reset Strobe                                  | 41         | $V_{REFHC}$        | DAC C Voltage Reference High Terminal     |

| 17         | MSB                         | $MSB = 0$ , Reset to $000_H$ .                | 42         | V <sub>REFLC</sub> | DAC C Voltage Reference Low Terminal      |

|            |                             | $MSB = 1$ , Reset to $200_H$ .                | 43         | NC                 | No Connect (Do Not Connect Anything       |

| 18         | NC                          | No Connect (Do Not Connect Anything           |            |                    | other than Dummy Pad)                     |

|            |                             | other than Dummy Pad)                         | 44         | VOD                | DAC D Output                              |

| 19         | NC                          | No Connect (Do Not Connect Anything           | 45         | $V_{SS2}$          | Negative Power Supply for DAC C and D     |

|            |                             | other than Dummy Pad)                         | 46         | $V_{\mathrm{DD2}}$ | Positive Power Supply for DAC C and D     |

| 20         | DB0                         | Data Bit 0                                    | 47         | VOC                | DAC C Output                              |

| 21         | DB1                         | Data Bit 1                                    | 48         | AGND2              | Analog Ground for DAC C and D             |

| 22         | DGND1                       | Digital Ground 1                              |            |                    |                                           |

| 23         | DB2                         | Data Bit 2                                    |            |                    |                                           |

| 24         | DB3                         | Data Bit 3                                    |            |                    |                                           |

<sup>\*</sup>AD5583 optimizes internal layout design to reduce die area so that all supply voltage pins are required to be connected externally. See Figure 5.

### **TIMING DIAGRAMS**

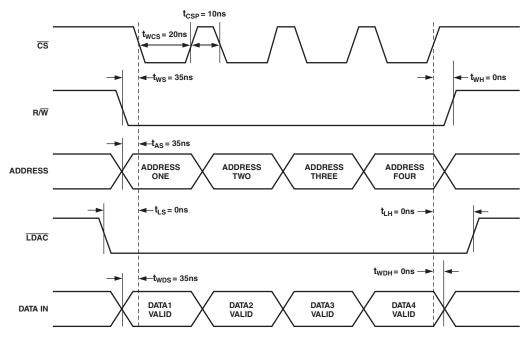

Figure 2a. Single Buffer Mode, Output Updated Individually,  $DV_{DD} = 5 V$

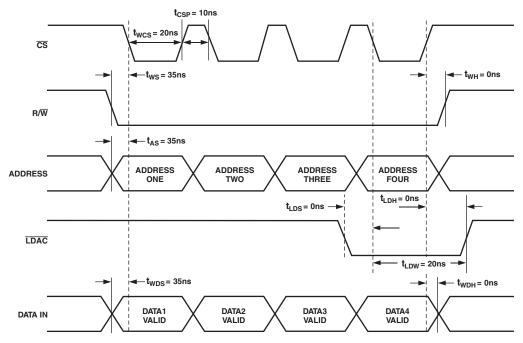

Figure 2b. Double Buffer Mode, Output Updated Simultaneously,  $DV_{DD} = 5 \text{ V}$

REV. A -9-

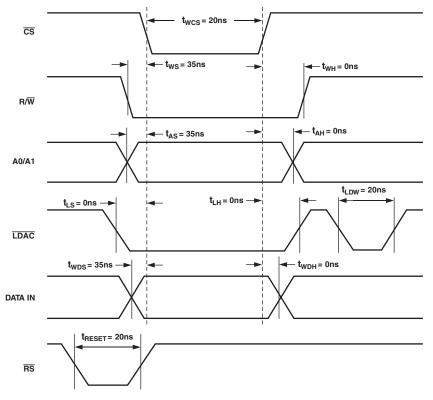

Figure 2c. Data Write (Input and Output Registers) Timing

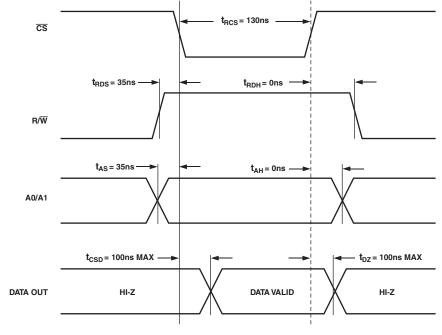

Figure 2d. Data Output (Read Timing)

# **Typical Performance Characteristics—AD5582/AD5583**

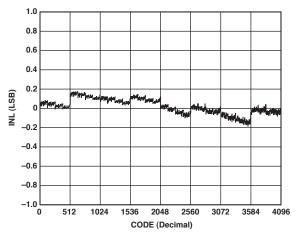

TPC 1. AD5582 Integral Nonlinearity Error

TPC 2. AD5582 Differential Nonlinearity Error

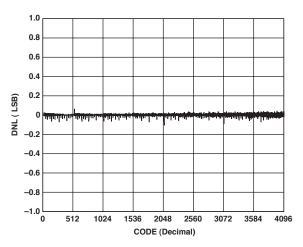

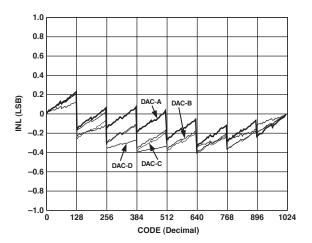

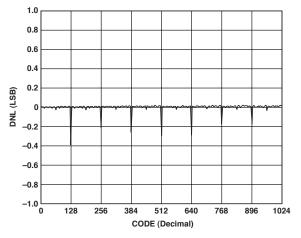

TPC 3. AD5583 Integral Nonlinearity Error

TPC 4. AD5583 Differential Nonlinearity Error

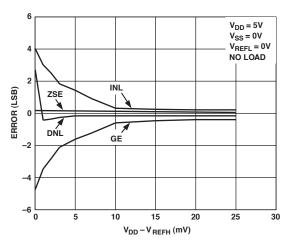

TPC 5. AD5582 INL, DNL, ZSE, and GE at Positive Rail-to-Rail Operation

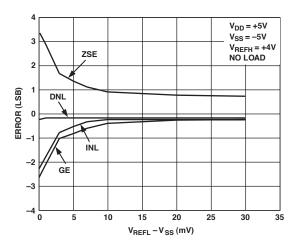

TPC 6. AD5582 INL, DNL, GE, and ZSE at Negative Rail-to-Rail Operation

REV. A -11-

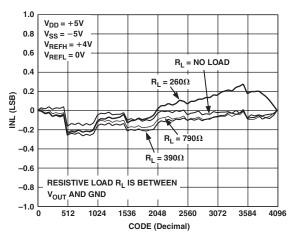

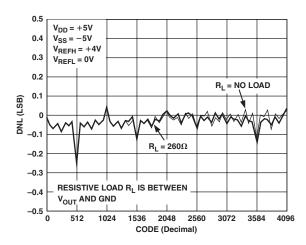

TPC 7. AD5582 INL at Various Resistive Loads

TPC 8. AD5582 DNL at Various Resistive Loads

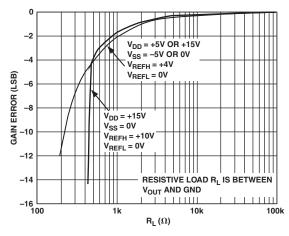

TPC 9. AD5582 Gain Error vs. Resistive Load

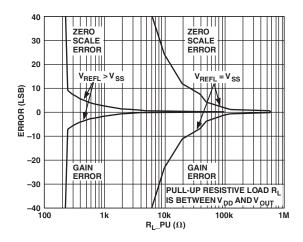

TPC 10. AD5582 Gain and Zero-Scale Error vs. Pull-Up Resistive Loads

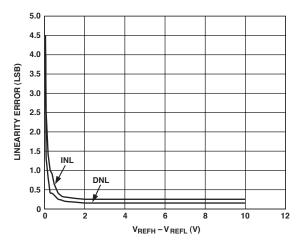

TPC 11. AD5582 Linearity Errors vs. Differential Reference Ranges

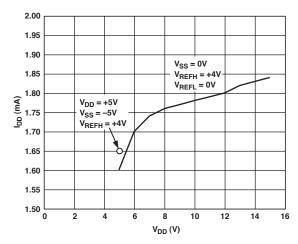

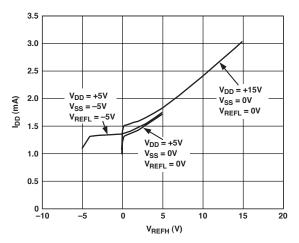

TPC 12. AD5582 Supply Current vs. Supply Voltage

–12– REV. A

TPC 13. AD5582 Supply Current vs. Reference Voltage

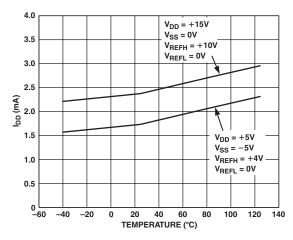

TPC 14. AD5582 Supply Current vs. Temperature

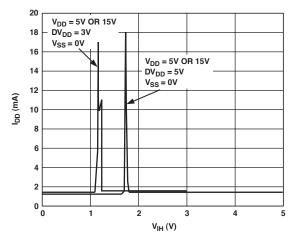

TPC 15. AD5582 Supply Current vs. Logic Input Voltage

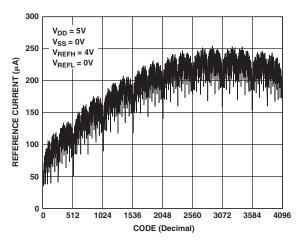

TPC 16. AD5582 Reference Current

TPC 17. AD5582 Referenced Input Resistance

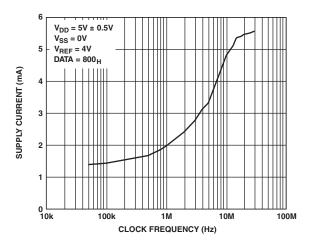

TPC 18. AD5582 Supply Current vs. Clock Frequency

REV. A -13-

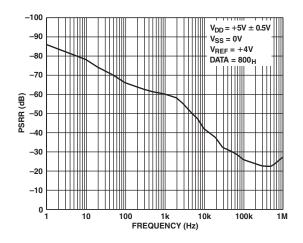

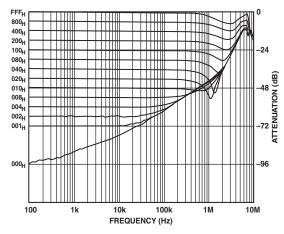

TPC 19. AD5582 PSRR vs. Frequency

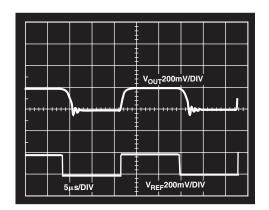

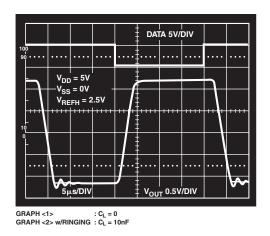

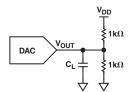

TPC 20. Small Signal Response Operating at Near Rail,  $C_L = 2 \text{ nF}$  (See Test Circuit 1)

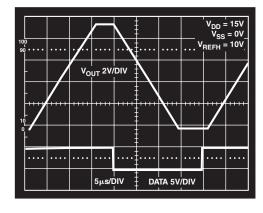

TPC 21. Large Signal Settling

TPC 22. Large Signal Settling When Loaded (See Test Circuit 1)

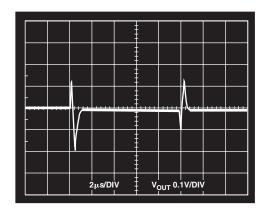

TPC 23. Midscale Transition Glitch

TPC 24. AD5582 Output Noise Density

-14- REV. A

TPC 25. AD5582 Multiplying Bandwidth

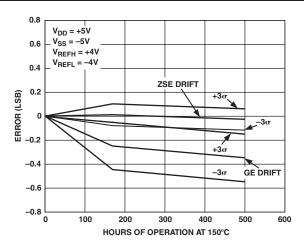

TPC 26. AD5582 Long-Term Drift

### **Test Circuit**

Test Circuit 1

### THEORY OF OPERATION

The AD5582/AD5583 are quad, voltage output, 12-/10-bit parallel input DACs in compact TSSOP-48 packages.

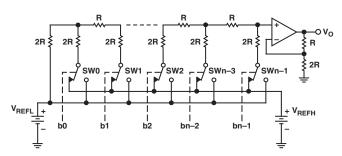

Each DAC is a voltage switching, high impedance (R = 20 k $\Omega$ ), R-2R ladder configuration with segmentation to optimize die area and precision. Figure 3 shows a simplified R-2R structure without the segmentation. The 2R resistances are switched between  $V_{REFH}$  and  $V_{REFL}$ , and the output is obtained from the rightmost ladder node. As the code is sequenced through all possible states, the voltage of this node changes in steps of (2/3  $V_{REFH} - V_{REFL}$ )/(2<sup>N</sup> - 1) starting from the lowest  $V_{REFL}$  and going to the highest  $V_{REFH} - DUTLSB$ . Buffering it with an amplifier with a gain of 1.5 brings the output to:

$$V_{OUT} = \frac{D}{2^N - 1} \left( V_{REFH} - V_{REFL} \right) + \left( V_{REFL} \right) \tag{1}$$

where D is the decimal equivalent of the data bits and N is the numbers of bits.

If  $-V_{REFL}$  is equal to  $V_{REFH}$  as  $V_{REF}$ ,  $V_{OUT}$  is simplified to:

$$V_{OUT} = \left(\frac{2D}{4095} - 1\right)V_{REF}$$

(For AD5582) (2)

$$V_{OUT} = \left(\frac{2D}{1023} - 1\right) V_{REF}$$

(For AD5583) (3)

The advantage of this scheme is that it allows the DAC to interpolate between two voltages for differential references or single-ended reference.

These DACs feature double buffers, which allow both synchronous and asynchronous channels update with additional data readback capability. These parts can be reset to zero scale or midscale controlled by the  $\overline{\text{RS}}$  and MSB pins. When  $\overline{\text{RS}}$  is activated, the MSB of 0 resets the DACs to zero scale and the MSB of 1 resets the DACs to midscale. The ability to operate from wide supply voltages, +5 V to +15 V or  $\pm 5$  V, with multiplying bipolar references is another key feature of these DACs.

Figure 3. Simplified R-2R Architecture (Segmentation Not Shown)

### **Power Supplies**

-15-

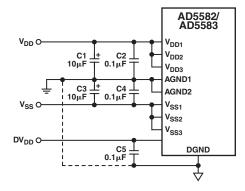

There are three separate power supplies needed for the operation of the DACs. For dual supply,  $V_{SS}$  can be set from -6.5 V to -2.7 V and  $V_{DD}$  can be set from +2.7 V to +6.5 V. For single supply,  $V_{SS}$  should be set at 0 V while  $V_{DD}$  is set from 3 V to 16.5 V. However, setting the single supply of  $V_{DD}$  below 4.5 V can impact the overall accuracy of the device.

REV. A

Since these DACs can be operated at high voltages, the digital signal levels are therefore controlled separately by the provision of  $\mathrm{DV_{DD}}$ .  $\mathrm{DV_{DD}}$  can be set as low as 2.7 V but no greater than 6.5 V. This allows the DAC to be operable from low level digital signals generated from a wide range of microcontrollers, FPGA, and signal processors.

#### **Reference Input**

All four channels of DACs allow independent and differential reference voltages. The flexibility of independent references allows users to apply a unique reference voltage to each channel. Similarly, bipolar references can be applied across the differential references. To maintain optimum accuracy, the difference between  $V_{\rm REFH}$  and  $V_{\rm REFL}$  should be greater than 1 V. See TPC 11.

The voltages applied to these reference inputs set the output voltage limits of all four channels of the DACs, and  $V_{REFH}$  must always be higher than  $V_{REFL}$ .  $V_{REFH}$  can be set at any voltage from  $V_{REFL}+0.5~V$  to  $V_{DD}$ , while  $V_{REFL}$  can be set at any voltage from  $V_{SS}$  to  $V_{REFH}-0.5~V$ . In addition, a symmetrical negative reference can be generated easily by an external op amp in an inverting mode with a pair of built-in precision resistors, R1 and R2. These resistors are matched within  $\pm 0.025\%$  for the AD5582 and 0.1% for the AD5583, which is equivalent to less than 1 LSB mismatch. Figure 4 shows a simple configuration.

Common reference or references can be applied to all four channels, but each reference pin should be decoupled with a  $0.1~\mu F$  ceramic capacitor mounted close to the pin.

Figure 4. Using On-Board Matching Resistors to Generate a Negative Voltage REF

#### Digital I/O

Digital I/O consists of a 12-/10-bit bidirectional data bus, two register select inputs, A0 and A1, an  $R\overline{W}$  input, a Reset ( $\overline{RS}$ ), a Chip Select ( $\overline{CS}$ ), and a Load DAC ( $\overline{LDAC}$ ) input. Control of the DACs and the bus direction is determined by these inputs as shown in Table I. All digital pins are TTL/CMOS compatible and all internal registers are level triggered.

The register selects inputs A0 and A1. Decoding of the registers is enabled by the  $\overline{CS}$  input. When  $\overline{CS}$  is high, no decoding is taking place and neither the writing nor the reading of the input registers is enabled. The loading of the second bank of registers is controlled by the asynchronous  $\overline{LDAC}$  input. By taking  $\overline{LDAC}$  low while  $\overline{CS}$  is enabled, the individual channel is updated as single buffer mode, Figure 2a. If  $\overline{CS}$  is enabled sequentially to load data into all input registers, then a subsequent  $\overline{LDAC}$  pulse will allow all channels to be updated simultaneously as double buffer mode, Figure 2b.

$R/\overline{W}$  controls the writing to and reading from the input register.

### Reset

The  $\overline{\text{RS}}$  function can be used either at power-up or at any time during operation. The  $\overline{\text{RS}}$  function has priority over any other digital inputs. This pin is active low and sets the DAC output registers to either zero scale or midscale, determined by the state of the MSB. The reset to midscale is useful when the DAC is configured for bipolar references and the output will be reset to 0 V.

### **Output Amplifiers**

Unlike many voltage output DACs, the AD5582/AD5583 feature buffered voltage outputs with high output current driving capability. Each output is capable of both sourcing and sinking  $\pm 20$  mA, eliminating the need for external buffers when driving any capacitive loads without oscillation. These amplifiers also have short circuit protection.

#### Glitch

The worst-case glitch of the AD5582 occurs at the transitions between midscale (1000 0000 0000\_B) to midscale minus 1 (0111 1111 1111\_B), or vice versa. The glitch energy is measured as 100 mV  $\times$  1  $\mu s$  or equivalent to 100 nV-s. Such glitch occurs in a shorter duration than the settling time and therefore most applications will be immune to such an effect without a deglitcher.

### Layout and Power Supply Bypassing

It is a good practice to employ compact, minimum lead length PCB layout design. The leads to the input should be as short as possible to minimize IR drop and stray inductance.

It is also essential to bypass the power supplies with quality capacitors for optimum stability. Supply leads to the device should be bypassed with 0.01  $\mu F$  to 0.1  $\mu F$  disc or chip ceramics capacitors. Low ESR 1  $\mu F$  to 10  $\mu F$  tantalum or electrolytic capacitors should also be applied at the supplies to minimize transient disturbance. The AD5582/AD5583 optimize internal layout design to reduce die area so that all analog supply pins are required to be connected externally. See Figure 5.

Figure 5. Power Supply Configurations

### **APPLICATIONS**

### **Programmable Current Source**

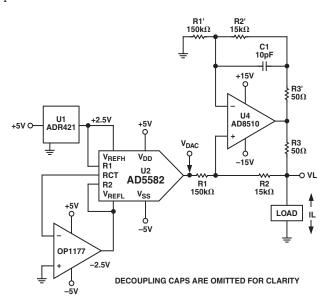

AD5582/AD5583 high current capability allow them to be used directly in programmable current source applications, such as 4 m to 20 mA current transmitter and other general purpose applications. For higher compliance voltage that is higher than 15 V, Figure 6 shows a versatile V-I conversion circuit using an improved Howland Current Pump. In addition to the precision current conversion it provides, this circuit enables a bidirectional current flow and high voltage compliance. The voltage

| Table I. | AD5582/AD55 | 583 Logic Table |

|----------|-------------|-----------------|

|----------|-------------|-----------------|

| A1 | A0 | R/W | CS | LDAC | RS | INPUT<br>REGISTER                                | DAC<br>REGISTER      | OPERATION<br>MODE    | SELECTED<br>DAC |

|----|----|-----|----|------|----|--------------------------------------------------|----------------------|----------------------|-----------------|

| 0  | 0  | 0   | 0  | 0    | 1  | Write                                            | Transparent          | Transparent          | A               |

| 0  | 1  | 0   | 0  | 0    | 1  | Write                                            | Transparent          | Transparent          | В               |

| 1  | 0  | 0   | 0  | 0    | 1  | Write                                            | Transparent          | Transparent          | C               |

| 1  | 1  | 0   | 0  | 0    | 1  | Write                                            | Transparent          | Transparent          | D               |

| 0  | 0  | 0   | 0  | 1    | 1  | Write                                            | Hold                 | Write Input          | A               |

| 0  | 1  | 0   | 0  | 1    | 1  | Write                                            | Hold                 | Write Input          | В               |

| 1  | 0  | 0   | 0  | 1    | 1  | Write                                            | Hold                 | Write Input          | С               |

| 1  | 1  | 0   | 0  | 1    | 1  | Write                                            | Hold                 | Write Input          | D               |

| 0  | 0  | 1   | 0  | 1    | 1  | Read                                             | Hold                 | Readback to D0 to DN | A               |

| 0  | 1  | 1   | 0  | 1    | 1  | Read                                             | Hold                 | Readback to D0 to DN | В               |

| 1  | 0  | 1   | 0  | 1    | 1  | Read                                             | Hold                 | Readback to D0 to DN | С               |

| 1  | 1  | 1   | 0  | 1    | 1  | Read                                             | Hold                 | Readback to D0 to DN | D               |

| X  | X  | X   | 1  | 0    | 1  | Hold                                             | Update All Registers | Update All Registers | All             |

| X  | X  | X   | 1  | 1    | 1  | Hold                                             | Hold                 | Hold                 | All             |

| X  | X  | X   | X  | X    | 0  | All registers reset to midscale or zero scale.   |                      |                      | All             |

| X  | X  | X   | 1  | X    | 1  | All registers latched to midscale or zero scale. |                      |                      | All             |

MSB = 0 resets to zero scale, MSB = 1 resets to midscale. X: Don't Care. Input and output registers are transparent when asserted.

compliance is mainly limited by the op amp supply voltages. This circuit can be used in 4 to 20 mA current transmitters with up to 500  $\Omega$  of load.

Figure 6. Programmable Current Source with Bidirectional Current Control and High Voltage Compliance Capabilities

Figure 6 shows that if the resistor network is matched, the load current is:

$$I_{L} = \frac{(R2 + R3)/R1}{R3} V_{DAC}$$

(4)

R3 in theory can be made small to achieve the current needed within the U4 output current driving capability. In this circuit, the AD8510 can deliver  $\pm 20$  mA in both directions and the voltage compliance approaches  $\pm 15~V.$

This circuit is versatile, but users must pay attention to the compensation. Without C1, it can be shown that the output impedance becomes:

$$Z_O = \frac{R1'R3(R1 + R2)}{R1(R2' + R3') - R1'(R2 + R3)}$$

(5)

If the resistors are perfectly matched,  $Z_O$  is infinite, which is highly desirable. On the other hand, if they are not matched,  $Z_O$  can either be positive or negative. The latter, because of the pole in the right S-plane, can cause oscillation. As a result, C1 in the range of a few pF is needed to prevent the oscillation. For critical applications, C1 should be found empirically without overcompensating.

### **Boosted Programmable Voltage Source**

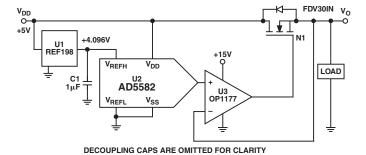

For users who need higher than 20 mA current driving capability, they can add an external op amp and power transistors. The capacitive loading capability will change, but it can still drive 100 nF capacitive load without oscillation in this circuit. Figure 7 shows a programmable power supply with 200 mA capability.

Figure 7. Boosted Programmable Voltage Source

Figure 8. Programmable PGA

In this circuit, the inverting input of the op amp forces the  $V_{\rm O}$  to be equal to the DAC output. The load current is then delivered by the supply via the N-Ch FET N1. U3 needs to be a rail-to-rail input type. With a  $V_{\rm DD}$  of 5 V, this circuit can source a maximum of 200 mA at 4.096 V full scale, 100 mA at midscale, and 50 mA near zero-scale outputs. Higher current can be achieved with N1 in a larger package mounted on a heat sink.

### Programmable PGA

The AD603 is a low noise, voltage controlled amplifier for use in RF and IF AGC (automatic gain control) systems. It provides accurate, pin selectable gains of -11 dB to +31 dB with a bandwidth of 90 MHz, or 9 dB to 51 dB with a bandwidth of 9 MHz. Any intermediate gain range may be arranged using one external resistor between Pin 5 and Pin 7. The input referred noise spectral density is only  $1.3 \text{ nV/}\overline{\text{Hz}}$  and power consumption is 125 mW at the recommended  $\pm 5 \text{ V}$  supplies.

The decibel gain is linear in dB, accurately calibrated, and stable over temperature and supply. The gain is controlled at a high impedance (50 M $\Omega$ ), low bias (200 nA) differential input; the scaling is 25 mV/dB, requiring a gain control voltage of only 1 V to span the central 40 dB of the gain range. An overrange and underrange of 1 dB is provided whatever the selected range. The gain control response time is less than 1 ms for a 40 dB change.

The differential gain control interface allows the use of either differential or single-ended positive or negative control voltages, where the common-mode range is  $-1.2~\rm V$  to  $+2.0~\rm V$ . The AD5582/AD5583 is ideally suited to provide the differential input range of 1 V within the common-mode range of 0 V to 2 V. To accomplish this, place  $\rm V_{REFH}$  at 2.0 V and  $\rm V_{REFL}$  at 1.0 V, then all 4096 V levels of the AD5582 will fall within the gain control range of the AD603. Please refer to the AD603 data sheet for further information regarding gain control, layout, and general operation.

### **OUTLINE DIMENSIONS**

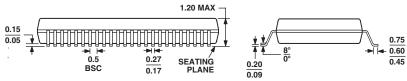

# 48-Lead Thin Shrink Small Outline Package [TSSOP] (RV-48)

Dimensions shown in millimeters

COMPLIANT TO JEDEC STANDARDS MO-153ED

REV. A -19-

# **Revision History**

| Location                                       | Page |

|------------------------------------------------|------|

| 8/03—Data Sheet changed from REV. 0 to REV. A. |      |

| Change to Figure 1                             |      |

| Changes to SPECIFICATIONS                      |      |

| Changes to TIMING CHARACTERISTICS              | 5    |

| Changes to PIN FUNCTION DESCRIPTIONS           | 8    |

| Changes to Figures 2a, 2b                      | 9    |

-20- REV. A