### FEATURES

Direct RF synthesis at 2.5 GSPS update rate DC to 1.25 GHz in baseband mode 1.25 GHz to 3.0 GHz in mix mode Industry leading single/multicarrier IF or RF synthesis fout = 350 MHz, ACLR = 80 dBc fout = 950 MHz, ACLR = 78 dBc fout = 2100 MHz, ACLR = 69 dBc Dual-port LVDS data interface Up to 1.25 GSPS operation Source synchronous DDR clocking Pin-compatible with the AD9739A Multichip synchronization capability Programmable output current: 8.7 mA to 31.7 mA Low power: 1.16 W at 2.5 GSPS

### APPLICATIONS

Broadband communications systems Military jammers Instrumentation, automatic test equipment Radar, avionics

#### **GENERAL DESCRIPTION**

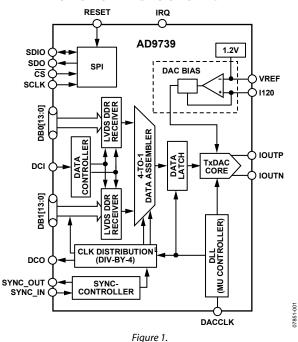

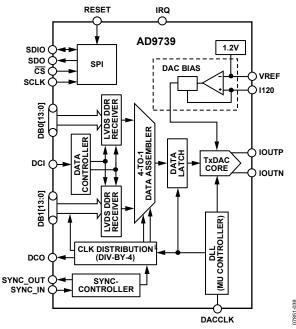

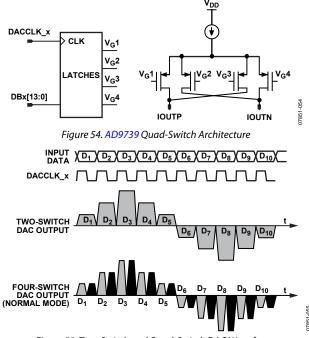

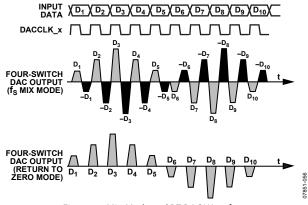

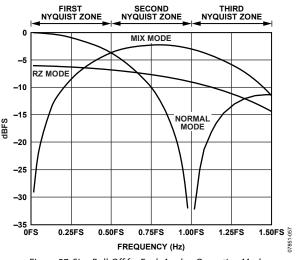

The AD9739 is a 14-bit, 2.5 GSPS high performance RF digitalto-analog converter (DAC) capable of synthesizing wideband signals from dc up to 3.0 GHz. Its DAC core features a quadswitch architecture that provides exceptionally low distortion performance with an industry-leading direct RF synthesis capability. This feature enables multicarrier generation up to the Nyquist frequency in baseband mode as well as second and third Nyquist zones in mix mode. The output current can be programmed over the 8.66 mA to 31.66 mA range.

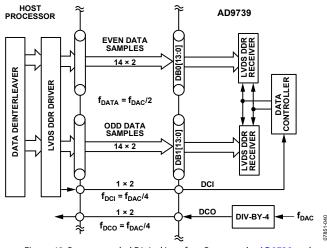

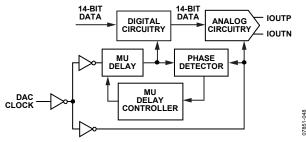

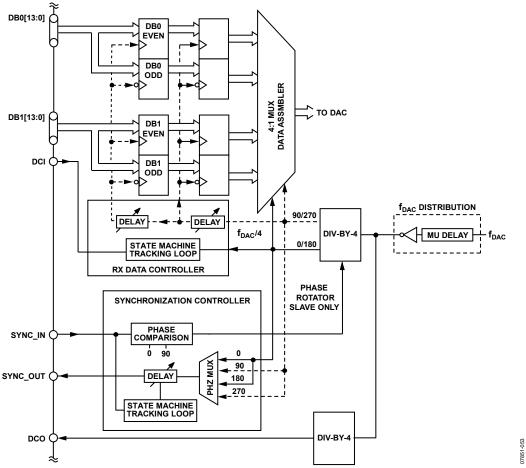

The inclusion of on-chip controllers simplifies system integration. A dual-port, source synchronous, LVDS interface simplifies the digital interface with existing FGPA/ASIC technology. On-chip controllers are used to manage external and internal clock domain variations over temperature to ensure reliable data transfer from the host to the DAC core. Multichip synchronization is possible with an on-chip synchronization controller. A serial peripheral interface (SPI) is used for device configuration as well as readback of status registers.

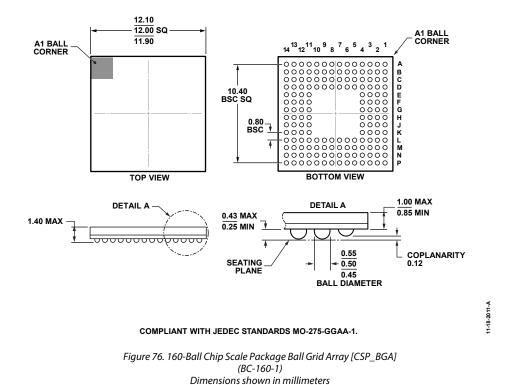

The AD9739 is manufactured on a 0.18 µm CMOS process and operates from 1.8 V and 3.3 V supplies. It is supplied in a 160-ball chip scale ball grid array for reduced package parasitics.

#### Rev. B

Information furnished by Analog Devices is believed to be accurate and reliable. However, no responsibility is assumed by Analog Devices for its use, nor for any infringements of patents or other rights of third parties that may result from its use. Specifications subject to change without notice. No license is granted by implication or otherwise under any patent or patent rights of Analog Devices. Trademarks and registered trademarks are the property of their respective owners.

# 14-Bit, 2.5 GSPS, RF Digital-to-Analog Converter

# AD9739

#### **FUNCTIONAL BLOCK DIAGRAM**

### **PRODUCT HIGHLIGHTS**

- 1. Ability to synthesize high quality wideband signals with bandwidths of up to 1.25 GHz in the first or second Nyquist zone.

- 2. A proprietary quad-switch DAC architecture provides exceptional ac linearity performance while enabling mix mode operation.

- 3. A dual-port, double data rate, LVDS interface supports the maximum conversion rate of 2500 MSPS.

- 4. On-chip controllers manage external and internal clock domain skews.

- 5. A multichip synchronization capability.

- 6. Programmable differential current output with a 8.66 mA to 31.66 mA range.

# AD9739

### **Data Sheet**

# TABLE OF CONTENTS

| Features 1                                                     |

|----------------------------------------------------------------|

| Applications                                                   |

| General Description                                            |

| Functional Block Diagram 1                                     |

| Product Highlights 1                                           |

| Revision History 2                                             |

| Specifications                                                 |

| DC Specifications 4                                            |

| LVDS Digital Specifications5                                   |

| Serial Port Specifications                                     |

| AC Specifications7                                             |

| Absolute Maximum Ratings                                       |

| Thermal Resistance 8                                           |

| ESD Caution 8                                                  |

| Pin Configurations and Function Descriptions                   |

| Typical Performance Characteristics12                          |

| AC (Normal Mode)12                                             |

| AC (Mix Mode)15                                                |

| Terminology17                                                  |

| Serial Port Interface (SPI) Register18                         |

| SPI Register Map Description18                                 |

| SPI Operation18                                                |

| SPI Register Map20                                             |

| SPI Port Configuration and Software Reset                      |

| Power-Down LVDS Interface and TxDAC*                           |

| Controller Clock Disable                                       |

| Interrupt Request (IRQ) Enable/Status                          |

| TxDAC Full-Scale Current Setting (I $_{\rm OUTFS}$ ) and Sleep |

| TxDAC Quad-Switch Mode of Operation                            |

### DCI Phase Alignment Status ...... 23 SYNC\_IN Phase Alignment Status ...... 23 Data and Sync Receiver Controller DCI Delay Data Receiver Controller\_Delay Line Status and Sync Controller SYNC\_OUT Status ...... 24 Sync and Data Receiver Controller Lock/Tracking Status.... 25 CLK Input Common Mode ...... 25 Analog Modes of Operation ...... 38 Analog Outputs ...... 40 Power Dissipation and Supply Domains...... 44 Recommended Start-Up Sequence ...... 45 Ordering Guide ...... 48

### **REVISION HISTORY**

1/12-Rev. A to Rev. B

| Changes to Features Section, Applications Section, General |    |

|------------------------------------------------------------|----|

| Description Section, Figure 1, Product Highlights Section  | 1  |

| Changes to DC Specifications Section                       | 4  |

| Changed Digital Specifications Section to LVDS Digital     |    |

| Specifications Section                                     | 5  |

| Changes to LVDS Digital Specifications Section             | 5  |

| Added Serial Port Specifications Section and Table 3;      |    |

| Renumbered Sequentially                                    | 6  |

| Changes to AC Specifications Section                       | 7  |

| Changes to Table 5                                         | 8  |

| Changes to Table 7                                         | 10 |

|                                                            |    |

Deleted Static Linearity Section and Figure 7 to Figure 17;Renumbered Sequentially11Changed Dynamic Performance Normal Mode, 20 mA FullScale (Unless Otherwise Noted) Section to AC (Normal Mode)Section12Changes to AC (Normal Mode) Section12Changed Dynamic Performance Mix Mode, 20 mA Full ScaleSection to AC (Mix Mode) Section15Changes to AC (Mix Mode) Section15Changes to AC (Mix Mode) Section15Changes to AC (Mix Mode) Section15Operation Section, Reset Section, Table 8, and SPI18Operation Section and Figure 3418

Rev. B | Page 2 of 48

| Deleted DOCSIS Performance Section and                                 | Changes to Analog Modes of Operation Section                     |

|------------------------------------------------------------------------|------------------------------------------------------------------|

| Figure 46 to Figure 72                                                 | Deleted Clocking the AD9739 Section, Figure 85, and Figure 8639  |

| Added Figure 35 through Figure 38; Renumbered Sequentially 19          | Added Clock Input Considerations Section, Figure 58 to           |

| Changes to SPI Register Map Section and Table 9                        | Figure 60                                                        |

| Added SPI Port Configuration and Software Reset Section,               | Deleted Clock Phase Noise Affects on AC Performance Section,     |

| Power-Down LVDS Interface and TxDAC <sup>®</sup> Section, Controller   | Table 32 to Table 34, Applying Data to the AD9739 Section, and   |

| Clock Disable Section, Interrupt Request (IRQ) Enable/Status           | Figure 87                                                        |

| Section, and Table 10 to Table 13                                      | Moved Figure 61                                                  |

| Added TxDAC Full-Scale Current Setting (I <sub>OUTES</sub> ) and Sleep | Changes to Voltage References Section and Analog Outputs         |

| Section, TxDAC Quad-Switch Mode of Operation Section, DCI              | Section                                                          |

| Phase Alignment Status Section, SYNC_IN Phase Alignment                | Added Equivalent DAC Output and Transfer Function and            |

| Status Section, Data Receiver Controller Configuration Section,        | Figure 63                                                        |

| and Table 14 to Table 18                                               | Deleted Mu Control Operation Section, Search Mode Section,       |

|                                                                        |                                                                  |

| Added Data Receiver Controller_Data Sample Delay Value                 | and Figure 89                                                    |

| Section, Data and Sync Receiver Controller_DCI Delay                   | Moved Figure 64                                                  |

| Value/Window and Phase Rotation Section, Data Receiver                 | Added Peak DAC Output Power Capability Section and Figure 65. 41 |

| Controller_Delay Line Status and Sync Controller SYNC_OUT              | Deleted Figure 90, Figure 91, Track Mode Section, Mu Delay       |

| Status Section, and Table 19 to Table 21                               | and Phase Readback Section, Operating the Mu Controller          |

| Deleted Serial Peripheral Interface Section, General Operation         | Manually Section, and Calculating Mu Delay Line Step Size        |

| of the Serial Interface Section, Instruction Mode (8-Bit Instruction)  | Section                                                          |

| Section, and Serial Interface Port Pin Description Section25           | Added Output Stage Configuration Section and Figure 66 to        |

| Added Sync and Data Receiver Controller Lock/Tracking Status           | Figure 70                                                        |

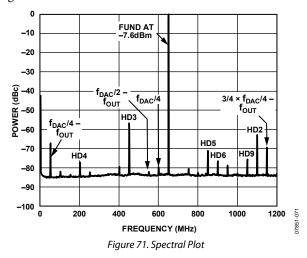

| Section, CLK Input Common Mode Section, Mu Controller                  | Added Nonideal Spectral Artifacts Section, Figure 71, and        |

| Configuration and Status Section, and Table 22 to Table 2425           | Table 3043                                                       |

| Deleted MSB/LSB Transfers Section, Serial Port Configuration           | Deleted Operation in Master Mode, Figure 93, and                 |

| Section, and Figure 74 to Figure 7926                                  | Figure 94                                                        |

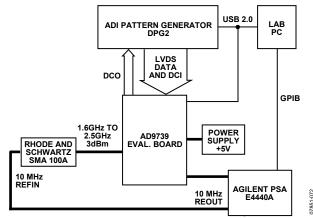

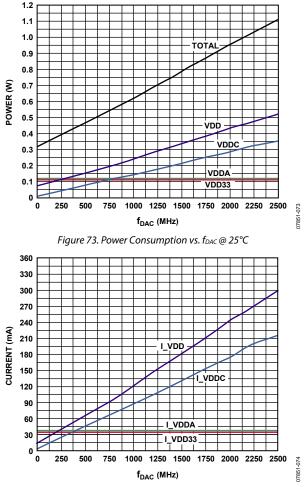

| Added Part ID Section and Table 2526                                   | Added Lab Evaluation of the AD9739 Section, Power Dissipation    |

| Changes to Theory of Operation Section27                               | and Supply Domains Section, and Figure 72 to Figure 7444         |

| Added Figure 3927                                                      | Deleted Figure 95, Operation in Slave Mode Section, and Data     |

| Deleted SPI Registers Section and Table 8 to Table 3128                | Receiver Operation in Auto Mode Section45                        |

| Moved and Changes to LVDS Data Port Interface Section28                | Changes to Recommended Start-Up Sequence Section45               |

| Added Figure 40 and Figure 4128                                        | Added Figure 7545                                                |

| Changes to Figure 4229                                                 | Deleted Figure 97, Data Receiver Operation in Manual Mode        |

| Moved and Changes to Figure 4329                                       | Section, Calculating the DCI Delay Line Step Size Section, and   |

| Added Data Receiver Controller Initialization Description              | Maximum Allowable Data Timing Skew/Jitter Section46              |

| Section, Table 26, and Data Receiver Operation at Lower Clock          | Added Table 3146                                                 |

| Rates Section                                                          | Deleted Optimizing the Clock Common-Mode Voltage Section,        |

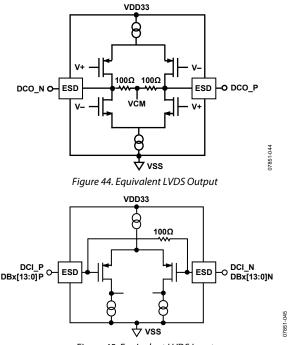

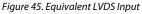

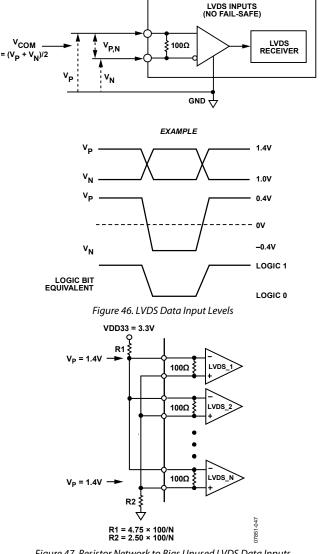

| Added LVDS Driver and Receiver Input Section, Figure 44 to             | Figure 99, Analog Control Registers Section, Mirror Roll-Off     |

| Figure 47, and Table 27                                                | Frequency Control Section, and Figure 10147                      |

| Changed and Moved Mu Delay Controller Section to Mu                    | Added Table 3247                                                 |

| Controller Section                                                     | Deleted Figure 103, Figure 104, and Figure 10648                 |

| Changes to Mu Controller Section, Figure 48, and Figure 4932           | Updated Outline Dimensions                                       |

| Added Figure 50 and Table 28                                           | Deleted Figure 107 to Figure 10949                               |

| Added Mu Controller Initialization Description Section33               | Deleted Table 35 to Table 4450                                   |

| Changes to Interrupt Requests Section                                  |                                                                  |

| Added Table 29                                                         | 7/11—Rev 0 to Rev A                                              |

| Changed Synchronization Controller Section to Multiple                 | Changes to Table 2, DAC CLOCK INPUT (DACCLK_P,                   |

| Device Synchronization Section                                         | DACCLK_N), Added DAC Clock Rate                                  |

| Added Figure 52                                                        | Changes to Table 3, Added Dynamic Performance Parameters5        |

| Changes to Figure 53                                                   | Change to Ordering Guide                                         |

| Added Sync Controller Initialization Description Section               |                                                                  |

| Added Synchronization Limitations Section                              | 2/09—Revision 0: Initial Release                                 |

| Changed Applications Information to Analog Interface                   |                                                                  |

| Considerations Section                                                 |                                                                  |

# **SPECIFICATIONS**

### DC SPECIFICATIONS

VDDA = VDD33 = 3.3 V, VDDC = VDD = 1.8 V,  $I_{OUTFS} = 20 mA$ .

| Parameter                                                            | Min  | Тур   | Max   | Unit   |

|----------------------------------------------------------------------|------|-------|-------|--------|

| RESOLUTION                                                           |      | 14    |       | Bits   |

| ACCURACY                                                             |      |       |       |        |

| Integral Nonlinearity (INL)                                          |      | ±1.3  |       | LSB    |

| Differential Nonlinearity (DNL)                                      |      | ±0.8  |       | LSB    |

| ANALOG OUTPUTS                                                       |      |       |       |        |

| Gain Error (with Internal Reference)                                 |      | 5.5   |       | %      |

| Full-Scale Output Current                                            | 8.66 | 20.2  | 31.66 | mA     |

| Output Compliance Range                                              | -1.0 |       | +1.0  | V      |

| Common-Mode Output Resistance                                        |      | 10    |       | MΩ     |

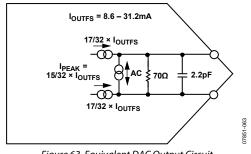

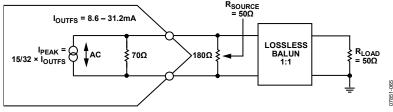

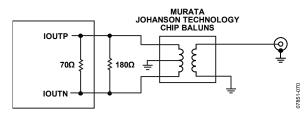

| Differential Output Resistance                                       |      | 70    |       | Ω      |

| Output Capacitance                                                   |      | 1     |       | pF     |

| DAC CLOCK INPUT (DACCLK_P, DACCLK_N)                                 |      |       |       |        |

| Differential Peak-to-Peak Voltage                                    | 1.2  | 1.6   | 2.0   | V      |

| Common-Mode Voltage                                                  |      | 900   |       | mV     |

| DAC Clock Rate                                                       | 0.8  |       | 2.5   | GHz    |

| TEMPERATURE DRIFT                                                    |      |       |       |        |

| Gain                                                                 |      | 60    |       | ppm/°0 |

| Reference Voltage                                                    |      | 20    |       | ppm/°0 |

| REFERENCE                                                            |      |       |       |        |

| Internal Reference Voltage                                           | 1.15 | 1.2   | 1.25  | V      |

| Output Resistance                                                    |      | 5     |       | kΩ     |

| ANALOG SUPPLY VOLTAGES                                               |      |       |       |        |

| VDDA                                                                 | 3.1  | 3.3   | 3.5   | v      |

| VDDC                                                                 | 1.70 | 1.8   | 1.90  | V      |

| DIGITAL SUPPLY VOLTAGES                                              |      |       |       |        |

| VDD33                                                                | 3.10 | 3.3   | 3.5   | V      |

| VDD                                                                  | 1.70 | 1.8   | 1.90  | V      |

| SUPPLY CURRENTS AND POWER DISSIPATION, 2.0 GSPS                      |      |       |       |        |

| Ivdda                                                                |      | 37    | 38    | mA     |

| lvddc                                                                |      | 159   | 166   | mA     |

| IVDD33                                                               |      | 34    | 37    | mA     |

| lvdd                                                                 |      | 233   | 238   | mA     |

| Power Dissipation                                                    |      | 0.940 | 0.975 | W      |

| Sleep Mode, Ivdda                                                    |      | 2.5   | 2.75  | mA     |

| Power-Down Mode (Register $0x01 = 0x33$ and Register $0x02 = 0x80$ ) |      |       |       |        |

| Ivdda                                                                |      | 0.02  |       | mA     |

| I <sub>VDDC</sub>                                                    |      | 3.8   |       | mA     |

| Ivdd33                                                               |      | 0.5   |       | mA     |

| lvdd                                                                 |      | 0.1   |       | mA     |

| SUPPLY CURRENTS AND POWER DISSIPATION, 2.5 GSPS                      |      |       |       |        |

| Ivdda                                                                |      | 37    |       | mA     |

| lvddc                                                                |      | 223   |       | mA     |

| IVDD33                                                               |      | 34    |       | mA     |

| lvod                                                                 |      | 290   |       | mA     |

| Power Dissipation                                                    |      | 1.16  |       | W      |

### LVDS DIGITAL SPECIFICATIONS

VDDA = VDD33 = 3.3 V, VDDC = VDD = 1.8 V, IOUTES = 20 mA. LVDS drivers and receivers are compliant to the IEEE Standard 1596.3-1996 reduced range link, unless otherwise noted.

### Table 2.

| Parameter                                                   | Min  | Тур  | Max  | Unit |

|-------------------------------------------------------------|------|------|------|------|

| LVDS DATA INPUTS (DB0[13:0], DB1[13:0]) <sup>1</sup>        |      |      |      |      |

| Input Common-Mode Voltage Range, V <sub>сом</sub>           | 825  |      | 1575 | mV   |

| Logic High Differential Input Threshold, VIH_DTH            | 175  | 400  |      | mV   |

| Logic Low Differential Input Threshold, V <sub>IL_DTH</sub> | -175 | -400 |      | mV   |

| Receiver Differential Input Impedance, R <sub>IN</sub>      | 80   |      | 120  | Ω    |

| Input Capacitance                                           |      | 1.2  |      | pF   |

| LVDS Input Rate                                             | 1250 |      |      | MSPS |

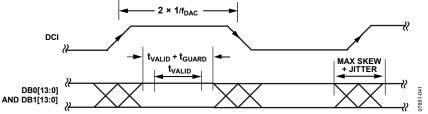

| LVDS Minimum Data Valid Period, tvalid (See Figure 41)      |      |      | 344  | ps   |

| LVDS CLOCK INPUT (DCI and SYNC_IN) <sup>2</sup>             |      |      |      |      |

| Input Common-Mode Voltage Range, V <sub>сом</sub>           | 825  |      | 1575 | mV   |

| Logic High Differential Input Threshold, VIH_DTH            | 175  | 400  |      | mV   |

| Logic Low Differential Input Threshold, VIL_DTH             | -175 | -400 |      | mV   |

| Receiver Differential Input Impedance, R <sub>IN</sub>      | 80   |      | 120  | Ω    |

| Input Capacitance                                           |      | 1.2  |      | pF   |

| Maximum Clock Rate                                          | 625  |      |      | MHz  |

| LVDS CLOCK OUTPUT (DCO and SYNC_OUT) <sup>3</sup>           |      |      |      |      |

| Output Voltage High (x_P or x_N)                            |      |      | 1375 | mV   |

| Output Voltage Low (x_P or x_N)                             | 1025 |      |      | mV   |

| Output Differential Voltage, Vod                            | 150  | 200  | 250  | mV   |

| Output Offset Voltage, Vos                                  | 1150 |      | 1250 | mV   |

| Output Impedance, Single-Ended, R <sub>o</sub>              | 80   | 100  | 120  | Ω    |

| Ro Single-Ended Mismatch                                    |      |      | 10   | %    |

| Maximum Clock Rate                                          | 625  |      |      | MHz  |

<sup>1</sup> DB0[x]P, DB0[x]N, DB1[x]P, and DB1[x]N pins.

<sup>2</sup> DCI\_P and DCI\_N pins, as well as SYNC\_IN\_P and SYNC\_IN\_N pins. <sup>3</sup> DCO\_P and DCO\_N pins, as well as SYNC\_OUT\_P/SYNC\_OUT\_N pins with 100 Ω differential termination.

### SERIAL PORT SPECIFICATIONS

VDDA = VDD33 = 3.3 V, VDDC = VDD = 1.8 V.

### Table 3.

| Parameter                                                                       | Min | Тур | Мах | Unit |

|---------------------------------------------------------------------------------|-----|-----|-----|------|

| WRITE OPERATION (See Figure 36)                                                 |     |     |     |      |

| SCLK Clock Rate, f <sub>SCLK</sub> (or /t <sub>SCLK</sub> )                     |     |     | 20  | MHz  |

| SCLK Clock High, t <sub>HI</sub>                                                | 18  |     |     | ns   |

| SCLK Clock Low, t <sub>LOW</sub>                                                | 18  |     |     | ns   |

| SDIO to SCLK Setup Time, t <sub>DS</sub>                                        | 2   |     |     | ns   |

| SCLK to SDIO Hold Time, t <sub>DH</sub>                                         | 1   |     |     | ns   |

| CS to SCLK Setup Time, ts                                                       | 3   |     |     | ns   |

| SCLK to $\overline{CS}$ Hold Time, t <sub>H</sub>                               | 2   |     |     | ns   |

| READ OPERATION (See Figure 37 and Figure 38)                                    |     |     |     |      |

| SCLK Clock Rate, fsclk (or /tsclk)                                              |     |     | 20  | MHz  |

| SCLK Clock High, t <sub>HI</sub>                                                | 18  |     |     | ns   |

| SCLK Clock Low, t <sub>LOW</sub>                                                | 18  |     |     | ns   |

| SDIO to SCLK Setup Time, t <sub>DS</sub>                                        | 2   |     |     | ns   |

| SCLK to SDIO Hold Time, t <sub>DH</sub>                                         | 1   |     |     | ns   |

| $\overline{\text{CS}}$ to SCLK Setup Time, t <sub>s</sub>                       | 3   |     |     | ns   |

| SCLK to SDIO (or SDO) Data Valid Time, t <sub>DV</sub>                          |     |     | 15  | ns   |

| $\overline{\text{CS}}$ to SDIO (or SDO) Output Valid to High-Z, t <sub>EZ</sub> |     | 2   |     | ns   |

| INPUTS (SDIO, SCLK, CS)                                                         |     |     |     |      |

| Voltage in High, V <sub>H</sub>                                                 | 2.0 | 3.3 |     | V    |

| Voltage in Low, $V_{IL}$                                                        |     | 0   | 0.8 | V    |

| Current in High, I <sub>II</sub>                                                | -10 |     | +10 | μA   |

| Current in Low, I⊩                                                              | -10 |     | +10 | μA   |

| OUTPUT (SDIO)                                                                   |     |     |     |      |

| Voltage Out High, Vон                                                           | 2.4 |     | 3.5 | V    |

| Voltage Out Low, Vol                                                            | 0   |     | 0.4 | V    |

| Current Out High, Іон                                                           |     | 4   |     | mA   |

| Current Out Low, IoL                                                            |     | 4   |     | mA   |

### AC SPECIFICATIONS

VDDA = VDD33 = 3.3 V, VDDC = VDD = 1.8 V,  $I_{OUTFS} = 20 mA$ ,  $f_{DAC} = 2400 MSPS$ .

### Table 4.

| Parameter                                                                           | Min | Тур   | Max  | Unit   |

|-------------------------------------------------------------------------------------|-----|-------|------|--------|

| DYNAMIC PERFORMANCE                                                                 |     |       |      |        |

| DAC Clock Rate                                                                      | 800 |       | 2500 | MSPS   |

| Adjusted DAC Update Rate <sup>1</sup>                                               | 800 |       | 2500 | MSPS   |

| Output Settling Time (t <sub>st</sub> ) to 0.1%                                     |     | 13    |      | ns     |

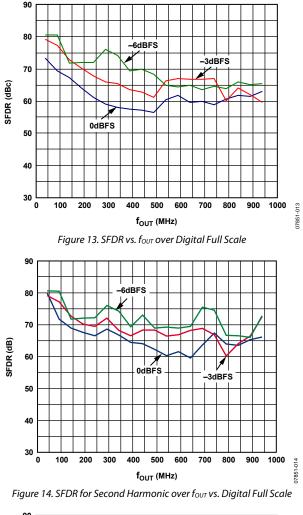

| SPURIOUS-FREE DYNAMIC RANGE (SFDR)                                                  |     |       |      |        |

| fout = 100 MHz                                                                      |     | 69.5  |      | dBc    |

| fout = 350 MHz                                                                      |     | 58.5  |      | dBc    |

| fout = 550 MHz                                                                      |     | 54    |      | dBc    |

| foυτ = 950 MHz                                                                      |     | 60    |      | dBc    |

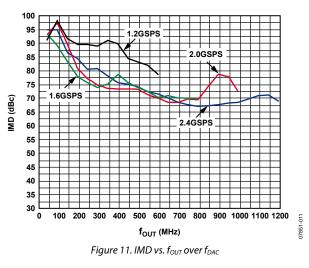

| TWO-TONE INTERMODULATION DISTORTION (IMD), $f_{OUT2} = f_{OUT1} + 1.25 \text{ MHz}$ |     |       |      |        |

| $f_{OUT} = 100 \text{ MHz}$                                                         |     | 94    |      | dBc    |

| fout = 350 MHz                                                                      |     | 78    |      | dBc    |

| $f_{OUT} = 550 \text{ MHz}$                                                         |     | 72    |      | dBc    |

| four = 950 MHz                                                                      |     | 68    |      | dBc    |

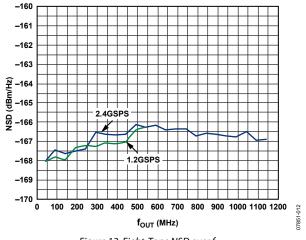

| NOISE SPECTRAL DENSITY (NSD), 0 dBFS SINGLE TONE                                    |     |       |      |        |

| fout = 100 MHz                                                                      |     | -166  |      | dBm/Hz |

| fout = 350 MHz                                                                      |     | -161  |      | dBm/Hz |

| fout = 550 MHz                                                                      |     | -160  |      | dBm/Hz |

| $f_{OUT} = 850 \text{ MHz}$                                                         |     | -160  |      | dBm/Hz |

| WCDMA ACLR (SINGLE CARRIER), ADJACENT/ALTERNATE ADJACENT CHANNEL                    |     |       |      |        |

| $f_{DAC} = 2457.6 \text{ MSPS } f_{OUT} = 350 \text{ MHz}$                          |     | 80/80 |      | dBc    |

| f <sub>DAC</sub> = 2457.6 MSPS, f <sub>OUT</sub> = 950 MHz                          |     | 78/79 |      | dBc    |

| f <sub>DAC</sub> = 2457.6 MSPS, f <sub>OUT</sub> = 1700 MHz (Mix Mode)              |     | 74/74 |      | dBc    |

| f <sub>DAC</sub> = 2457.6 MSPS, f <sub>OUT</sub> = 2100 MHz (Mix Mode)              |     | 69/72 |      | dBc    |

<sup>1</sup> Adjusted DAC updated rate is calculated as  $f_{DAC}$  divided by the minimum required interpolation factor. For the AD9739, the minimum interpolation factor is 1. Thus, with  $f_{DAC} = 2500$  MSPS,  $f_{DAC}$  adjusted = 2500 MSPS.

# **ABSOLUTE MAXIMUM RATINGS**

Table 5.

|                                    | With              |                         |

|------------------------------------|-------------------|-------------------------|

| Parameter                          | <b>Respect To</b> | Rating                  |

| VDDA                               | VSSA              | –0.3 V to +3.6 V        |

| VDD33                              | VSS               | –0.3 V to +3.6 V        |

| VDD                                | VSS               | –0.3 V to +1.98 V       |

| VDDC                               | VSSC              | –0.3 V to +1.98 V       |

| VSSA                               | VSS               | –0.3 V to +0.3 V        |

| VSSA                               | VSSC              | –0.3 V to +0.3 V        |

| VSS                                | VSSC              | –0.3 V to +0.3 V        |

| DACCLK_P, DACCLK_N                 | VSSC              | -0.3 V to VDDC + 0.18 V |

| DCI, DCO, SYNC_IN,<br>SYNC_OUT     | VSS               | –0.3 V to VDD33 + 0.3 V |

| LVDS Data Inputs                   | VSS               | –0.3 V to VDD33 + 0.3 V |

| IOUTP, IOUTN                       | VSSA              | -1.0 V to VDDA + 0.3 V  |

| 1120, VREF                         | VSSA              | -0.3 V to VDDA + 0.3 V  |

| IRQ, CS, SCLK, SDO,<br>SDIO, RESET | VSS               | –0.3 V to VDD33 + 0.3 V |

|                                    |                   | 150°C                   |

| Junction Temperature               |                   |                         |

| Storage Temperature                |                   | −65°C to +150°C         |

Stresses above those listed under Absolute Maximum Ratings may cause permanent damage to the device. This is a stress rating only; functional operation of the device at these or any other conditions above those indicated in the operational section of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

### THERMAL RESISTANCE

$\theta_{JA}$  is specified for the worst-case conditions, that is, a device soldered in a circuit board for surface-mount packages.

### Table 6. Thermal Resistance

| Package Type     | θιΑ  | θις | Unit              |

|------------------|------|-----|-------------------|

| 160-Ball CSP_BGA | 31.2 | 7.0 | °C/W <sup>1</sup> |

<sup>1</sup> With no airflow movement.

### **ESD CAUTION**

**ESD** (electrostatic discharge) sensitive device. Charged devices and circuit boards can discharge without detection. Although this product features patented or proprietary protection circuitry, damage may occur on devices subjected to high energy ESD. Therefore, proper ESD precautions should be taken to avoid performance degradation or loss of functionality.

804

7851

0000

0000

0000

0000

0000

0000

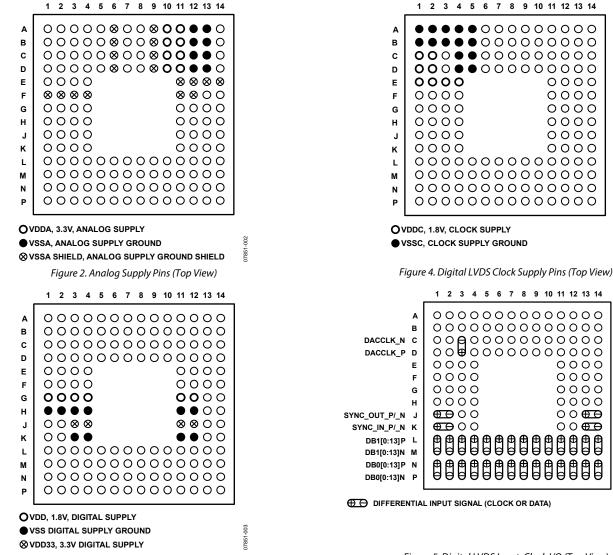

# PIN CONFIGURATIONS AND FUNCTION DESCRIPTIONS

Figure 3. Digital Supply Pins (Top View)

Figure 5. Digital LVDS Input, Clock I/O (Top View)

DCO P/ N

DCI\_P/\_N

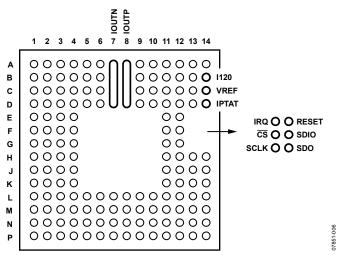

Figure 6. Analog I/O and SPI Control Pins (Top View)

| Table 7. AD9739 Pin Function Descripti<br>Pin No. | Mnemonic              | Description                                                                                                             |

|---------------------------------------------------|-----------------------|-------------------------------------------------------------------------------------------------------------------------|

| C1, C2, D1, D2, E1, E2, E3, E4                    | VDDC                  | 1.8 V Clock Supply Input.                                                                                               |

| A1, A2, A3, A4, A5, B1, B2, B3, B4, B5, C4,       | VBBC                  | Clock Supply Return.                                                                                                    |

| C5, D4, D5                                        | V35C                  |                                                                                                                         |

| A10, A11, B10, B11, C10, C11, D10, D11            | VDDA                  | 3.3 V Analog Supply Input.                                                                                              |

| A12, A13, B12, B13, C12, C13, D12, D13,           | VSSA                  | Analog Supply Return.                                                                                                   |

| A6, A9, B6, B9, C6, C9, D6, D9, F1, F2, F3,       | VSSA Shield           | Analog Supply Return Shield. Tie to VSSA at the DAC.                                                                    |

| F4, E11, E12, E13, E14, F11, F12                  |                       |                                                                                                                         |

| A14                                               | NC                    | No Connect. Do not connect to this pin.                                                                                 |

| A7, B7, C7, D7                                    | IOUTN                 | DAC Negative Current Output Source.                                                                                     |

| A8, B8, C8, D8                                    | IOUTP                 | DAC Positive Current Output Source.                                                                                     |

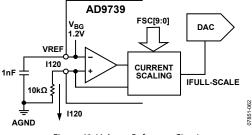

| B14                                               | 1120                  | Nominal 1.2 V Reference. Tie to analog ground via a 10 k $\Omega$ resistor to generate a 120 $\mu$ A reference current. |

| C14                                               | VREF                  | Voltage Reference Input/Output. Decouple to VSSA with a                                                                 |

|                                                   |                       | 1 nF capacitor.                                                                                                         |

| D14                                               | NC                    | Factory Test Pin. Do not connect to this pin.                                                                           |

| C3, D3                                            | DACCLK_N/DACCLK_P     | Negative/Positive DAC Clock Input (DACCLK).                                                                             |

| F13                                               | IRQ                   | Interrupt Request Open Drain Output. Active high. Pull up to VDD33 with a 10 k $\Omega$ resistor.                       |

| F14                                               | RESET                 | Reset Input. Active high. Tie to VSS if unused.                                                                         |

| G13                                               | <u>cs</u>             | Serial Port Enable Input.                                                                                               |

| G14                                               | SDIO                  | Serial Port Data Input/Output.                                                                                          |

| H13                                               | SCLK                  | Serial Port Clock Input.                                                                                                |

| H14                                               | SDO                   | Serial Port Data Output.                                                                                                |

| J3, J4, J11, J12                                  | VDD33                 | 3.3 V Digital Supply Input.                                                                                             |

| G1, G2, G3, G4, G11, G12                          | VDD                   | 1.8 V Digital Supply. Input.                                                                                            |

| H1, H2, H3, H4, H11, H12, K3, K4, K11, K12        | VSS                   | Digital Supply Return.                                                                                                  |

| J1, J2                                            | SYNC_OUT_P/SYNC_OUT_N | Positive/Negative SYNC Output (SYNC_OUT)                                                                                |

| K1, K2                                            | SYNC_IN_P/SYNC_IN_N   | Positive/Negative SYNC Input (SYNC_IN)                                                                                  |

| J13, J14                                          | DCO_P/DCO_N           | Positive/Negative Data Clock Output (DCO).                                                                              |

| K13, K14                                          | DCI_P/DCI_N           | Positive/Negative Data Clock Input (DCI).                                                                               |

| L1, M1                                            | DB1[0]P/DB1[0]N       | Port 1 Positive/Negative Data Input Bit 0.                                                                              |

| L2, M2                                            | DB1[1]P/DB1[1]N       | Port 1 Positive/Negative Data Input Bit 1.                                                                              |

| L3, M3                                            | DB1[2]P/DB1[2]N       | Port 1 Positive/Negative Data Input Bit 2.                                                                              |

| L4, M4                                            | DB1[3]P/DB1[3]N       | Port 1 Positive/Negative Data Input Bit 3.                                                                              |

| L5, M5                                            | DB1[4]P/DB1[4]N       | Port 1 Positive/Negative Data Input Bit 4.                                                                              |

| L6, M6                                            | DB1[5]P/DB1[5]N       | Port 1 Positive/Negative Data Input Bit 5.                                                                              |

Rev. B | Page 10 of 48

| Pin No.  | Mnemonic          | Description                                 |

|----------|-------------------|---------------------------------------------|

| L7, M7   | DB1[6]P/DB1[6]N   | Port 1 Positive/Negative Data Input Bit 6.  |

| L8, M8   | DB1[7]P/DB1[7]N   | Port 1 Positive/Negative Data Input Bit 7.  |

| L9, M9   | DB1[8]P/DB1[8]N   | Port 1 Positive/Negative Data Input Bit 8.  |

| L10, M10 | DB1[9]P/DB1[9]N   | Port 1 Positive/Negative Data Input Bit 9.  |

| L11, M11 | DB1[10]P/DB1[10]N | Port 1 Positive/Negative Data Input Bit 10. |

| L12, M12 | DB1[11]P/DB1[11]N | Port 1 Positive/Negative Data Input Bit 11. |

| L13, M13 | DB1[12]P/DB1[12]N | Port 1 Positive/Negative Data Input Bit 12. |

| L14, M14 | DB1[13]P/DB1[13]N | Port 1 Positive/Negative Data Input Bit 13. |

| N1, P1   | DB0[0]P/DB0[0]N   | Port 0 Positive/Negative Data Input Bit 0.  |

| N2, P2   | DB0[1]P/DB0[1]N   | Port 0 Positive/Negative Data Input Bit 1.  |

| N3, P3   | DB0[2]P/DB0[2]N   | Port 0 Positive/Negative Data Input Bit 2.  |

| N4, P4   | DB0[3]P/DB0[3]N   | Port 0 Positive/Negative Data Input Bit 3.  |

| N5, P5   | DB0[4]P/DB0[4]N   | Port 0 Positive/Negative Data Input Bit 4.  |

| N6, P6   | DB0[5]P/DB0[5]N   | Port 0 Positive/Negative Data Input Bit 5.  |

| N7, P7   | DB0[6]P/DB0[6]N   | Port 0 Positive/Negative Data Input Bit 6.  |

| N8, P8   | DB0[7]P/DB0[7]N   | Port 0 Positive/Negative Data Input Bit 7.  |

| N9, P9   | DB0[8]P/DB0[8]N   | Port 0 Positive/Negative Data Input Bit 8.  |

| N10, P10 | DB0[9]P/DB0[9]N   | Port 0 Positive/Negative Data Input Bit 9.  |

| N11, P11 | DB0[10]P/DB0[10]N | Port 0 Positive/Negative Data Input Bit 10. |

| N12, P12 | DB0[11]P/DB0[11]N | Port 0 Positive/Negative Data Input Bit 11. |

| N13, P13 | DB0[12]P/DB0[12]N | Port 0 Positive/Negative Data Input Bit 12. |

| N14, P14 | DB0[13]P/DB0[13]N | Port 0 Positive/Negative Data Input Bit 13. |

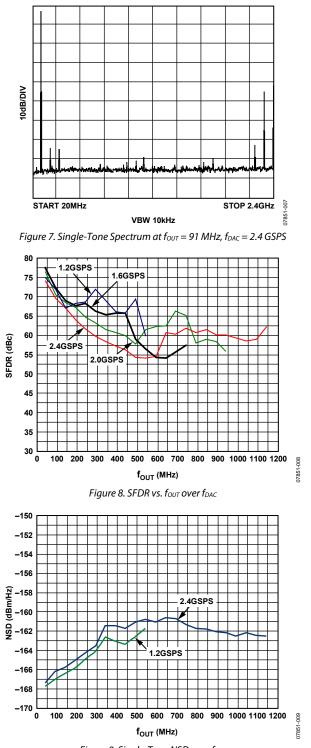

# **TYPICAL PERFORMANCE CHARACTERISTICS**

### AC (NORMAL MODE)

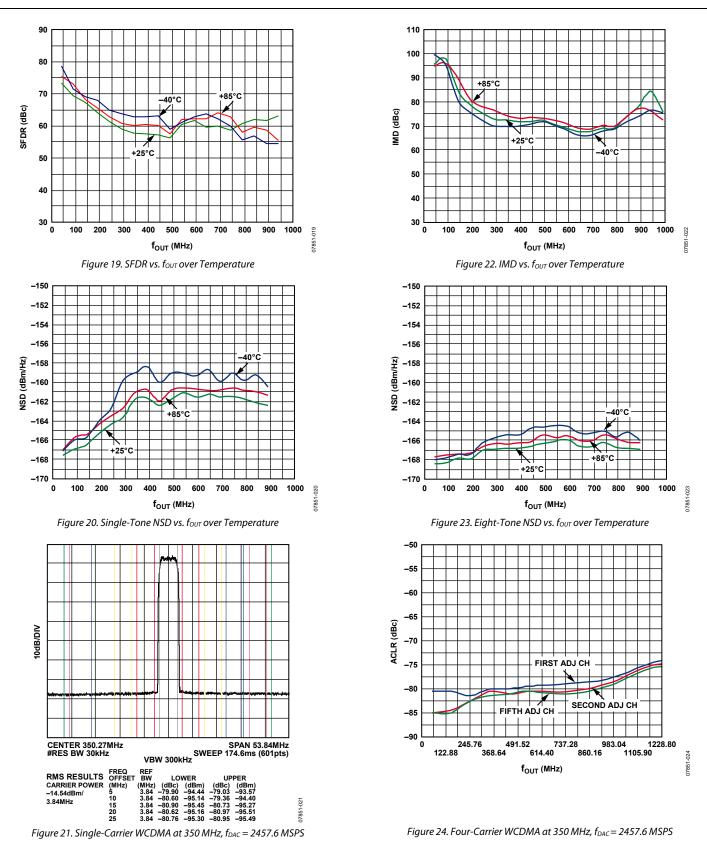

I<sub>OUTFS</sub> = 20 mA, nominal supplies, 25°C, unless otherwise noted.

Figure 9. Single-Tone NSD over four

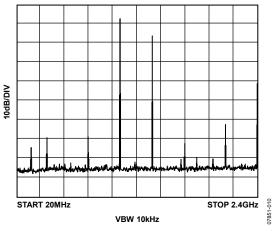

Figure 10. Single-Tone Spectrum at  $f_{OUT} = 1091 \text{ MHz}$ ,  $f_{DAC} = 2.4 \text{ GSPS}$

Figure 12. Eight-Tone NSD over four

f<sub>DAC</sub> = 2 GSPS, I<sub>OUTFS</sub> = 20 mA, nominal supplies, 25°C, unless otherwise noted.

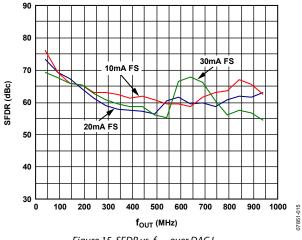

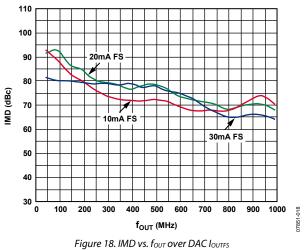

Figure 15. SFDR vs. fout over DAC loutes

# AD9739

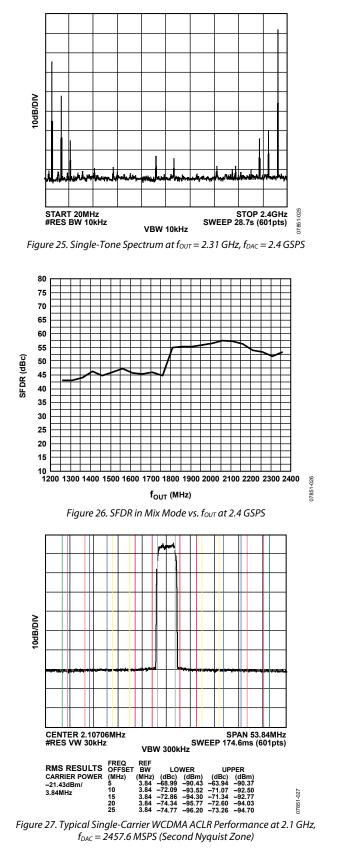

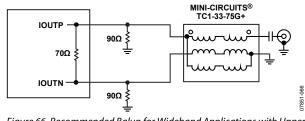

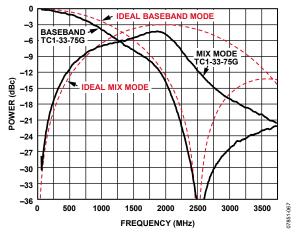

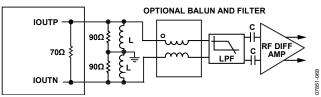

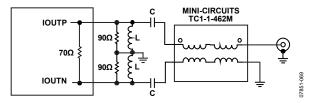

### AC (MIX MODE)

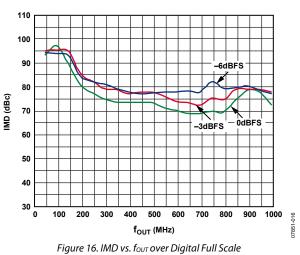

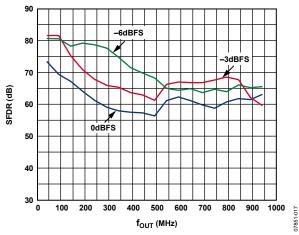

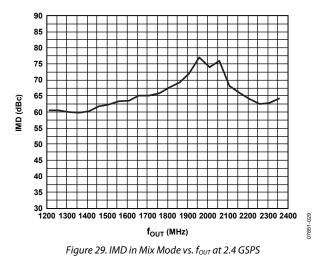

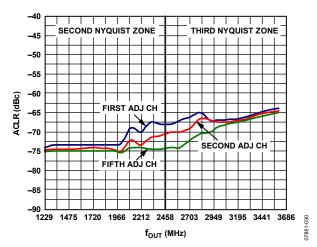

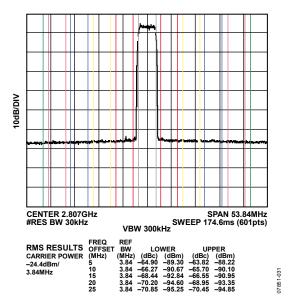

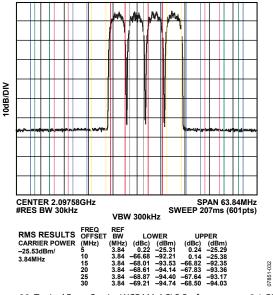

$f_{DAC}$  = 2.4 GSPS,  $I_{OUTFS}$  = 20 mA, nominal supplies, 25°C, unless otherwise noted.

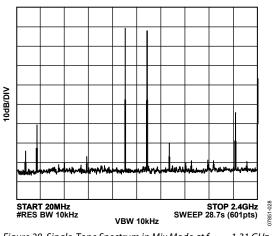

Figure 28. Single-Tone Spectrum in Mix Mode at  $f_{OUT}$  = 1.31 GHz,  $f_{DAC}$  = 2.4 GSPS

Figure 30. Single-Carrier WCDMA ACLR vs. four at 2457.6 MSPS

# AD9739

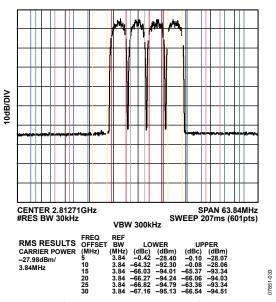

Figure 31. Typical Single-Carrier WCDMA ACLR Performance at 2.8 GHz,  $f_{DAC} = 2457.6$  MSPS (Third Nyquist Zone)

Figure 32. Typical Four-Carrier WCDMA ACLR Performance at 2.1 GHz,  $f_{DAC} = 2457.6$  MSPS (Second Nyquist Zone)

Figure 33. Typical Four-Carrier WCDMA ACLR Performance at 2.8 GHz,  $f_{DAC} = 2457.6$  MSPS (Third Nyquist Zone)

### TERMINOLOGY

### Linearity Error (Integral Nonlinearity or INL)

The maximum deviation of the actual analog output from the ideal output, determined by a straight line drawn from 0 to full scale.

### Differential Nonlinearity (DNL)

The measure of the variation in analog value, normalized to full scale, associated with a 1 LSB change in digital input code.

### Monotonicity

A DAC is monotonic if the output either increases or remains constant as the digital input increases.

### **Offset Error**

The deviation of the output current from the ideal of 0 is called the offset error. For IOUTP, 0 mA output is expected when the inputs are all 0s. For IOUTN, 0 mA output is expected when all inputs are set to 1.

### **Gain Error**

The difference between the actual and ideal output span. The actual span is determined by the output when all inputs are set to 1 minus the output when all inputs are set to 0.

### **Output Compliance Range**

The range of allowable voltage at the output of a current output DAC. Operation beyond the maximum compliance limits may cause either output stage saturation or breakdown, resulting in nonlinear performance.

### **Temperature Drift**

Specified as the maximum change from the ambient (25°C) value to the value at either  $T_{MIN}$  or  $T_{MAX}$ . For offset and gain drift, the drift is reported in ppm of full-scale range (FSR) per °C. For reference drift, the drift is reported in ppm per °C.

### Power Supply Rejection (PSR)

The maximum change in the full-scale output as the supplies are varied from nominal to minimum and maximum specified voltages.

#### Spurious-Free Dynamic Range (SFDR)

The difference, in decibels (dB), between the rms amplitude of the output signal and the peak spurious signal over the specified bandwidth.

### **Total Harmonic Distortion (THD)**

The ratio of the rms sum of the first six harmonic components to the rms value of the measured input signal. It is expressed as a percentage or in decibels (dB).

### Noise Spectral Density (NSD)

NSD is the converter noise power per unit of bandwidth. This is usually specified in dBm/Hz in the presence of a 0 dBm full-scale signal.

### Adjacent Channel Leakage Ratio (ACLR)

The adjacent channel leakage (power) ratio is a ratio, in dBc, of the measured power within a channel relative to its adjacent channels.

### **Modulation Error Ratio (MER)**

Modulated signals create a discrete set of output values referred to as a constellation. Each symbol creates an output signal corresponding to one point on the constellation. MER is a measure of the discrepancy between the average output symbol magnitude and the rms error magnitude of the individual symbol.

### Intermodulation Distortion (IMD)

IMD is the result of two or more signals at different frequencies mixing together. Many products are created according to the formula,  $aF1 \pm bF2$ , where a and b are integer values.

# SERIAL PORT INTERFACE (SPI) REGISTER

### The AD9739 contains a set of programmable re

The AD9739 contains a set of programmable registers described in Table 10 that are used to configure and monitor various internal parameters. Note the following points when programming the AD9739 SPI registers:

- Registers pertaining to similar functions are grouped together and assigned adjacent addresses.

- Bits that are undefined within a register should be assigned a 0 when writing to that register.

- Registers that are undefined should not be written to.

- A hardware or software reset is recommended upon power-up to place SPI registers in a known state.

- A SPI initialization routine is required as part of the boot process. See Table 31 and Table 32 for example procedures.

### Reset

Issuing a hardware or software reset places the AD9739 SPI registers in a known state. All SPI registers (excluding 0x00) are set to their default states as described in Table 10 upon issuing a reset. After issuing a reset, the SPI initialization process need only write to registers that are required for the boot process as well as any other register settings that must be modified, depending on the target application.

Although the AD9739 does feature an internal power-on-reset (POR), it is still recommended that a software or hardware reset be implemented shortly after power-up. The internal reset signal is derived from a logical OR operation from the internal POR signal, the RESET pin, and the software reset state. A software reset can be issued via the reset bit (Register 0x00, Bit 5) by toggling the bit high then low. Note that, because the MSB/LSB format may still be unknown upon initial power-up (that is, internal POR is unsuccessful), it is also recommended that the bit settings for Bits[7:5] be mirrored onto Bits[2:0] for the instruction cycle that issues a software reset. A hardware reset can be issued from a host or external supervisory IC by applying a high pulse with a minimum width of 40 ns to the RESET pin (that is, Pin F14). RESET should be tied to VSS if unused.

| Table 8. SPI Registers | Pertaining to SPI Options |

|------------------------|---------------------------|

|------------------------|---------------------------|

| Address (Hex) | Bit | Description          |

|---------------|-----|----------------------|

| 0x00          | 7   | Enable 3-wire SPI    |

|               | 6   | Enable SPI LSB first |

|               | 5   | Software reset       |

### **SPI OPERATION**

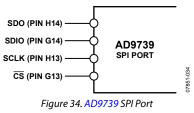

The serial port of the AD9739 shown in Figure 34 has a 3- or 4-wire SPI capability, allowing read/write access to all registers that configure the device's internal parameters. It provides a flexible, synchronous serial communications port, allowing easy interface to many industry-standard microcontrollers and microprocessors. The 3.3 V serial I/O is compatible with most synchronous transfer formats, including the Motorola<sup>®</sup> SPI and the Intel<sup>®</sup> SSR protocols.

The default 4-wire SPI interface consists of a clock (SCLK), serial port enable  $\overline{(CS)}$ , serial data input (SDIO), and serial data output (SDO). The inputs to SCLK,  $\overline{CS}$ , and SDIO contain a Schmitt trigger with a nominal hysteresis of 0.4 V centered about VDD33/2. The maximum frequency for SCLK is 20 MHz. The SDO pin is active only during the transmission of data and remains three-stated at any other time.

A 3-wire SPI interface can be enabled by setting the SDIO\_DIR bit (Register 0x00, Bit 7). This causes the SDIO pin to become bidirectional such that output data only appears on the SDIO pin during a read operation. The SDO pin remains three-stated in a 3-wire SPI interface.

### Instruction Header Information

| MSB |    |    |    |    |    |    | LSB |

|-----|----|----|----|----|----|----|-----|

| 17  | 16 | 15 | 14 | 13 | 12 | 11 | 10  |

| R/W | A6 | A5 | A4 | A3 | A2 | A1 | A0  |

An 8-bit instruction header must accompany each read and write operation. The MSB is a  $R/\overline{W}$  indicator bit with logic high indicating a read operation. The remaining seven bits specify the address bits to be accessed during the data transfer portion. The eight data bits immediately follow the instruction header for both read and write operations. For write operations, registers change immediately upon writing to the last bit of each transfer byte.  $\overline{CS}$  can be raised after each sequence of eight bits (except the last byte) to stall the bus. The serial transfer resumes when  $\overline{CS}$  is lowered. Stalling on nonbyte boundaries resets the SPI.

# AD9739

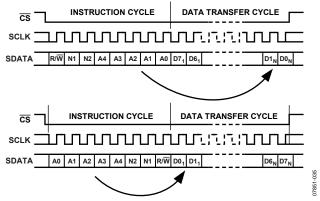

The AD9739 serial port can support both most significant bit (MSB) first and least significant bit (LSB) first data formats. Figure 35 illustrates how the serial port words are formed for the MSB first and LSB first modes. The bit order is controlled by the SDIO\_DIR bit (Register 0x00, Bit 7). The default value is 0, MSB first. When the LSB first bit is set high, the serial port interprets both instruction and data bytes LSB first.

Figure 35. SPI Timing, MSB First (Upper) and LSB First (Lower)

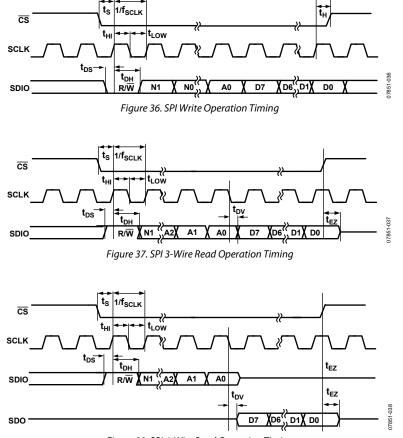

Figure 36 illustrates the timing requirements for a write operation to the SPI port. After the serial port enable ( $\overline{CS}$ ) signal goes low, data (SDIO) pertaining to the instruction header is read on the rising edges of the clock (SCLK). To initiate a write operation, the read/not-write bit is set low. After the instruction header is read, the eight data bits pertaining to the specified register are shifted into the SDIO pin on the rising edge of the next eight clock cycles.

Figure 37 illustrates the timing for a 3-wire read operation to the SPI port. After  $\overline{CS}$  goes low, data (SDIO) pertaining to the instruction header is read on the rising edges of SCLK. A read operation occurs if the read/not-write indicator is set high. After the address bits of the instruction header are read, the eight data bits pertaining to the specified register are shifted out of the SDIO pin on the falling edges of the next eight clock cycles.

Figure 38 illustrates the timing for a 4-wire read operation to the SPI port. The timing is similar to the 3-wire read operation with the exception that data appears at the SDO pin only, while the SDIO pin remains at high impedance throughout the operation. The SDO pin is an active output only during the data transfer phase and remains three-stated at all other times.

Figure 38. SPI 4-Wire Read Operation Timing

Rev. B | Page 19 of 48

# **SPI REGISTER MAP**

Table 9. Full Register Map (N/A = Not Applicable)

| Name                   | Hex<br>Addr | Bit 7              | Bit 6              | Bit 5                   | Bit 4                   | Bit 3                   | Bit 2                   | Bit 1                   | Bit 0                   | Default |

|------------------------|-------------|--------------------|--------------------|-------------------------|-------------------------|-------------------------|-------------------------|-------------------------|-------------------------|---------|

| Mode                   | 00          | SDIO_DIR           | LSB/MSB            | Reset                   | N/A                     | N/A                     | N/A                     | N/A                     | N/A                     | 0x00    |

| Power-<br>Down         | 01          | N/A                | N/A                | LVDS_<br>DRVR_PD        | LVDS_<br>RCVR_PD        | N/A                     | N/A                     | CLK_<br>RCVR_PD         | DAC_<br>BIAS_PD         | 0x00    |

| CNT_<br>CLK_DIS        | 02          | N/A                | N/A                | N/A                     | N/A                     | CLKGEN_PD               | N/A                     | REC_CNT_<br>CLK         | MU_CNT_<br>CLK          | 0x03    |

| IRQ_EN                 | 03          | N/A                | N/A                | SYNC_<br>LST_EN         | SYNC_<br>LCK_EN         | MU_LST_EN               | MU_LCK_EN               | RCV_<br>LST_EN          | RCV_<br>LCK_EN          | 0x00    |

| IRQ_REQ                | 04          | N/A                | N/A                | SYNC_<br>LST_IRQ        | SYNC_<br>LCK_IRQ        | MU_LST_<br>IRQ          | MU_LCK_<br>IRQ          | RCVLST_<br>IRQ          | RCVLCK_<br>IRQ          | 0x00    |

| RSVD                   | 05          | N/A                | N/A                | N/A                     | N/A                     | N/A                     | N/A                     | N/A                     | N/A                     | N/A     |

| FSC_1                  | 06          | FSC[7]             | FSC[6]             | FSC[5]                  | FSC[4]                  | FSC[3]                  | FSC[2]                  | FSC[1]                  | FSC[0]                  | 0x00    |

| FSC_2                  | 07          | Sleep              | N/A                | N/A                     | N/A                     | N/A                     | N/A                     | FSC[9]                  | FSC[8]                  | 0x02    |

| DEC_<br>CNT            | 08          | N/A                | N/A                | N/A                     | N/A                     | N/A                     | N/A                     | DAC_DEC[1]              | DAC_DEC[0]              | 0x00    |

| RSVD                   | 09          | N/A                | N/A                | N/A                     | N/A                     | N/A                     | N/A                     | N/A                     | N/A                     | N/A     |

| LVDS_<br>CNT           | 0A          | N/A                | N/A                | N/A                     | N/A                     | HNDOFF_<br>CHK_RST      | N/A                     | LVDS_<br>Bias[1]        | LVDS_<br>Bias[0]        | 0x00    |

| DIG_<br>STAT           | OB          | HNDOFF_<br>Fall[3] | HNDOFF_<br>Fall[2] | HNDOFF_<br>Fall[1]      | HNDOFF_<br>Fall[0]      | HNDOFF_<br>Rise[3]      | HNDOFF_<br>Rise[2]      | HNDOFF_<br>Rise[1]      | HNDOFF_<br>Rise[0]      | RNDM    |

| LVDS_<br>STAT1         | 0C          | SUP/HLD_<br>Edge1  | N/A                | DCI_<br>PHS3            | DCI_<br>PHS1            | DCI_PRE_<br>PH2         | DCI_PRE_<br>PH0         | DCI_PST_<br>PH2         | DCI_PST_<br>PH0         | RNDM    |

| LVDS_<br>STAT2         | 0D          | SUP/HLD_<br>SYNC   | SUP/HLD_<br>Edge0  | SYNC_<br>SAMP1          | SYNC_<br>SAMP0          | LVDS1_HI                | LVDS1_LO                | LVDS0_HI                | LVDS0_LO                | RNDM/0  |

| RSVD                   | 0E          | N/A                | N/A                | N/A                     | N/A                     | N/A                     | N/A                     | N/A                     | N/A                     | N/A     |

| RSVD                   | 0F          | N/A                | N/A                | N/A                     | N/A                     | N/A                     | N/A                     | N/A                     | N/A                     | N/A     |

| LVDS_<br>REC_<br>CNT1  | 10          | SYNC_<br>FLG_RST   | SYNC_<br>LOOP_ON   | SYNC_<br>MST/SLV        | SYNC_<br>CNT_ENA        | N/A                     | RCVR_<br>FLG_RST        | RCVR_<br>LOOP_ON        | RCVR_<br>CNT_ENA        | 0x42    |

| LVDS_<br>REC_<br>CNT2  | 11          | SMP_DEL[1]         | SMP_<br>DEL[0]     | FINE_<br>DEL_<br>MID[3] | FINE_<br>DEL_<br>MID[2] | FINE_DEL_<br>MID[1]     | FINE_DEL_<br>MID[0]     | RCVR_<br>GAIN[1]        | RCVR_<br>GAIN[0]        | 0xDD    |

| LVDS_<br>REC_<br>CNT3  | 12          | SMP_DEL[9]         | SMP_<br>DEL[8]     | SMP_<br>DEL[7]          | SMP_<br>DEL[6]          | SMP_<br>DEL[5]          | SMP_<br>DEL[4]          | SMP_<br>DEL[3]          | SMP_<br>DEL[2]          | 0x29    |

| LVDS_<br>REC_<br>CNT4  | 13          | DCI_DEL[3]         | DCI_<br>DEL[2]     | DCI_<br>DEL[1]          | DCI_<br>DEL[0]          | FINE_DEL_<br>SKW[3]     | FINE_DEL_<br>SKW[2]     | FINE_DEL_<br>SKW[1]     | FINE_DEL_<br>SKW[0]     | 0x71    |

| LVDS_<br>REC_<br>CNT5  | 14          | CLKDIVPH[1]        | CLKDIVPH[0]        | DCI_<br>DEL[9]          | DCI_<br>DEL[8]          | DCI_<br>DEL[7]          | DCI_<br>DEL[6]          | DCI_<br>DEL[5]          | DCI_<br>DEL[4]          | 0x0A    |

| LVDS_<br>REC_<br>CNT6  | 15          | SYNC_<br>GAIN[1]   | SYNC_<br>GAIN[0]   | SYNCOUT_<br>PH[1]       | SYNCOUT_<br>PH[0]       | LCKTHR[3]               | LCKTHR[2]               | LCKTHR[1]               | LCKTHR[0]               | 0x42    |

| LVDS_<br>REC_<br>CNT7  | 16          | N/A                | SYNCO_<br>DEL[6]   | SYNCO_<br>DEL[5]        | SYNCO_<br>DEL[4]        | SYNCO_<br>DEL[3]        | SYNCO_<br>DEL[2]        | SYNCO_<br>DEL[1]        | SYNCO_<br>DEL[0]        | 0x00    |

| LVDS_<br>REC_<br>CNT8  | 17          | SYNCSH_<br>DEL[0]  | N/A                | N/A                     | N/A                     | N/A                     | N/A                     | N/A                     | N/A                     | 0x00    |

| LVDS_<br>REC_<br>CNT9  | 18          | SYNCSH_<br>DEL[8]  | SYNCSH_<br>DEL[7]  | SYNCSH_<br>DEL[6]       | SYNCSH_<br>DEL[5]       | SYNCSH_<br>DEL[4]       | SYNCSH_<br>DEL[3]       | SYNCSH_<br>DEL[2]       | SYNCSH_<br>DEL[1]       | 0x00    |

| LVDS_<br>REC_<br>STAT1 | 19          | SMP_DEL[1]         | SMP_DEL[0]         | N/A                     | N/A                     | SMP_<br>FINE_<br>DEL[3] | SMP_<br>FINE_<br>DEL[2] | SMP_<br>FINE_<br>DEL[1] | SMP_<br>FINE_<br>DEL[0] | 0xC7    |

| LVDS_<br>REC_<br>STAT2 | 1A          | SMP_DEL[9]         | SMP_<br>DEL[8]     | SMP_<br>DEL[7]          | SMP_<br>DEL[6]          | SMP_<br>DEL[5]          | SMP_<br>DEL[4]          | SMP_<br>DEL[3]          | SMP_<br>DEL[2]          | 0x29    |

# AD9739

| Name                   | Hex<br>Addr | Bit 7               | Bit 6               | Bit 5               | Bit 4               | Bit 3               | Bit 2               | Bit 1               | Bit 0               | Default |

|------------------------|-------------|---------------------|---------------------|---------------------|---------------------|---------------------|---------------------|---------------------|---------------------|---------|

| LVDS_<br>REC_<br>STAT3 | 1B          | DCI_DEL[1]          | DCI_DEL[0]          | N/A                 | N/A                 | SYNCOUT<br>PH[1]    | SYNCOUT<br>PH[0]    | CLKDIV<br>PH[1]     | CLKDIV<br>PH[0]     | 0xC0    |

| LVDS_<br>REC_<br>STAT4 | 1C          | DCI_DEL[9]          | DCI_<br>DEL[8]      | DCI_<br>DEL[7]      | DCI_<br>DEL[6]      | DCI_<br>DEL[5]      | DCI_<br>DEL[4]      | DCI_<br>DEL[3]      | DCI_<br>DEL[2]      | 0x29    |

| LVDS_<br>REC_<br>STAT5 | 1D          | FINE_DEL_<br>PST[3] | FINE_DEL_<br>PST[2] | FINE_DEL_<br>PST[1] | FINE_DEL_<br>PST[0] | FINE_DEL_<br>PRE[3] | FINE_DEL_<br>PRE[2] | FINE_DEL_<br>PRE[1] | FINE_DEL_<br>PRE[0] | 0x86    |

| LVDS_<br>REC_<br>STAT6 | 1E          | N/A                 | SYNCO_<br>DEL[6]    | SYNCO_<br>DEL[5]    | SYNCO_<br>DEL[4]    | SYNCO_<br>DEL[3]    | SYNCO_<br>DEL[2]    | SYNCO_<br>DEL[1]    | SYNCO_<br>DEL[0]    | 0x00    |

| LVDS_<br>REC_<br>STAT7 | 1F          | SYNCSH_<br>DEL[0]   | N/A                 | 0x00    |

| LVDS_<br>REC_<br>STAT8 | 20          | SYNCSH_<br>DEL[8]   | SYNCSH_<br>DEL[7]   | SYNCSH_<br>DEL[6]   | SYNCSH_<br>DEL[5]   | SYNCSH_<br>DEL[4]   | SYNCSH_<br>DEL[3]   | SYNCSH_<br>DEL[2]   | SYNCSH_<br>DEL[1]   | 0x00    |

| LVDS_<br>REC_<br>STAT9 | 21          | SYNC_<br>TRK_ON     | SYNC_<br>INIT_ON    | SYNC_<br>LST_LCK    | SYNC_LCK            | RCVR_<br>TRK_ON     | RCVR_<br>FE_ON      | RCVR_LST            | RCVR_LCK            | 0x00    |

| CROSS_<br>CNT1         | 22          | N/A                 | N/A                 | N/A                 | DIR_P               | CLKP_<br>OFFSET[3]  | CLKP_<br>OFFSET[2]  | CLKP_<br>OFFSET[1]  | CLKP_<br>OFFSET[0]  | 0x00    |

| CROSS_<br>CNT2         | 23          | N/A                 | N/A                 | N/A                 | DIR_N               | CLKN_<br>OFFSET[3]  | CLKN_<br>OFFSET[2]  | CLKN_<br>OFFSET[1]  | CLKN_<br>OFFSET[0]  | 0x00    |

| PHS_<br>DET            | 24          | N/A                 | N/A                 | CMP_BST             | PHS_DET<br>AUTO_EN  | Bias[3]             | Bias[2]             | Bias[1]             | Bias[0]             | 0x00    |

| MU_<br>DUTY            | 25          | MU_<br>DUTYAUTO_EN  | POS/NEG             | ADJ[5]              | ADJ[4]              | ADJ[3]              | ADJ[2]              | ADJ[1]              | ADJ[0]              | 0x00    |

| MU_<br>CNT1            | 26          | N/A                 | Slope               | Mode[1]             | Mode[0]             | Read                | Gain[1]             | Gain[0]             | Enable              | 0x42    |

| MU_<br>CNT2            | 27          | MUDEL[0]            | SRCH_MODE<br>[1]    | SRCH_MODE<br>[0]    | SET_PHS[4]          | SET_PHS[3]          | SET_PHS[2]          | SET_PHS[1]          | SETPHS[0]           | 0x40    |

| MU_<br>CNT3            | 28          | MUDEL[8]            | MUDEL[7]            | MUDEL[6]            | MUDEL[5]            | MUDEL[4]            | MUDEL[3]            | MUDEL[2]            | MUDEL[1]            | 0x00    |

| MU_<br>CNT4            | 29          | SEARCH_TOL          | Retry               | CONTRST             | Guard[4]            | Guard[3]            | Guard[2]            | Guard[1]            | Guard[0]            | 0x0B    |

| MU_<br>STAT1           | 2A          | N/A                 | N/A                 | N/A                 | N/A                 | N/A                 | N/A                 | MU_LOST             | MU_LKD              | 0x00    |

| RSVD                   | 2B          | N/A                 | N/A     |

| RSVD                   | 2C          | N/A                 | N/A     |

| ANA_<br>CNT1           | 32          | HDRM[7]             | HDRM[6]             | HDRM[5]             | HDRM[4]             | HDRM[3]             | HDRM[2]             | HDRM[1]             | HDRM[0]             | 0xCA    |

| ANA_<br>CNT2           | 33          | N/A                 | N/A                 | N/A                 | N/A                 | N/A                 | N/A                 | MSEL[1]             | MSEL[0]             | 0x03    |

| RSVD                   | 34          | N/A                 | N/A     |

| PARTID                 | 35          | ID[7]               | ID[6]               | ID[5]               | ID[4]               | ID[3]               | ID[2]               | ID[1]               | ID[0]               | 0x20    |

### SPI PORT CONFIGURATION AND SOFTWARE RESET

| Address<br>(Hex) | Name     | Bit | R/W | Default<br>Setting | Comments                                                                                                                                                                                                                                                                                                             |

|------------------|----------|-----|-----|--------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0x00             | SDIO_DIR | 7   | R/W | 0                  | 0 = 4-wire SPI, $1 = 3$ -wire SPI.                                                                                                                                                                                                                                                                                   |

|                  | LSB/MSB  | 6   | R/W | 0                  | 0 = MSB first, 1 = LSB first.                                                                                                                                                                                                                                                                                        |

|                  | Reset    | 5   | R/W | 0                  | Software reset is recommended before modification of other SPI registers from the default setting. Setting the bit to 1 causes all registers (except 0x00) to be set to the default setting. Setting the bit to 0 corresponds to the inactive state, allowing the user to modify registers from the default setting. |

### Table 10. SPI Port Configuration and Software Reset Register

### **POWER-DOWN LVDS INTERFACE AND TXDAC®**

| Table 11 | . Power-Down | LVDS Interfa | ace and TxDAO | C Register |

|----------|--------------|--------------|---------------|------------|

|----------|--------------|--------------|---------------|------------|

| Address |              |     | DAM | Default |                                                     |

|---------|--------------|-----|-----|---------|-----------------------------------------------------|

| (Hex)   | Name         | Bit | R/W | Setting | Comments                                            |

| 0x01    | LVDS_DRVR_PD | 5   | R/W | 0       | Power-down of the LVDS drivers/receivers and TxDAC. |

|         | LVDS_RCVR_PD | 4   | R/W | 0       | 0 = enable, 1 = disable.                            |

|         | CLK_RCVR_PD  | 1   | R/W | 0       |                                                     |

|         | DAC_BIAS_PD  | 0   | R/W | 0       |                                                     |

### CONTROLLER CLOCK DISABLE

### Table 12. Controller Clock Disable Register

| Address<br>(Hex) | Name        | Bit | R/W | Default<br>Setting | Comments                                                      |

|------------------|-------------|-----|-----|--------------------|---------------------------------------------------------------|

| 0x02             | CLKGEN_PD   | 3   | R/W | 0                  | Internal CLK distribution enable:<br>0 = enable, 1 = disable. |

|                  | REC_CNT_CLK | 1   | R/W | 1                  | LVDS receiver and Mu controller clock disable.                |

|                  | MU_CNT_CLK  | 0   | R/W | 1                  | 0 = disable, 1 = enable.                                      |

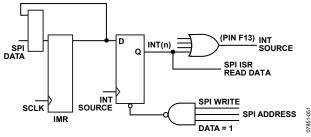

### **INTERRUPT REQUEST (IRQ) ENABLE/STATUS**

### Table 13. Interrupt Request (IRQ) Enable/Status Register

| Address<br>(Hex) | Name         | Bit | R/W | Default<br>Setting | Comments                                                                                                                               |

|------------------|--------------|-----|-----|--------------------|----------------------------------------------------------------------------------------------------------------------------------------|

| 0x03             | SYNC_LST_EN  | 5   | W   | 0                  | This register enables the sync, mu, and LVDS Rx controllers to update their                                                            |

|                  | SYNC_LCK_EN  | 4   | W   | 0                  | corresponding IRQ status bits in Register 0x04, which defines whether the controller is                                                |

|                  | MU_LST_EN    | 3   | W   | 0                  | locked (LCK) or unlocked (LST).<br>0 = disable (resets the status bit).                                                                |

|                  | MU_LCK_EN    | 2   | W   | 0                  | 1 = enable.                                                                                                                            |

|                  | RCV_LST_EN   | 1   | W   | 0                  |                                                                                                                                        |

|                  | RCV_LCK_EN   | 0   | W   | 0                  |                                                                                                                                        |

| 0x04             | SYNC_LST_IRQ | 5   | R   | 0                  | This register indicates the status of the controllers. For LCK_IQR bits: 0 = lost locked, 1                                            |

|                  | SYNC_LCK_IRQ | 4   | R   | 0                  | = locked. For LST_IQR bits: 0 = not lost locked, 1 = unlocked. Note that, if the                                                       |

|                  | MU_LST_IRQ   | 3   | R   | 0                  | controller IRQ is serviced, the relevant bits in Register 0x03 should be reset by writing 0, followed by another write of 1 to enable. |

|                  | MU_LCK_IRQ   | 2   | R   | 0                  |                                                                                                                                        |

|                  | RCV_LST_IRQ  | 1   | R   | 0                  |                                                                                                                                        |

|                  | RCV_LCK_IRQ  | 0   | R   | 0                  |                                                                                                                                        |

### **TxDAC FULL-SCALE CURRENT SETTING (IOUTFS) AND SLEEP**

| Address<br>(Hex) | Name  | Bit   | R/W | Default<br>Setting | Comments                                                                     |

|------------------|-------|-------|-----|--------------------|------------------------------------------------------------------------------|

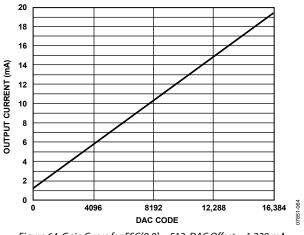

| 0x06             | FSC_1 | [7:0] | R/W | 0x00               | Sets the TxDAC $I_{OUTFS}$ current between 8 mA and 31 mA (default = 20 mA). |

| 0x07             | FSC_2 | [1:0] | R/W | 0x02               | $I_{OUTFS} = 0.0226 \times FSC[9:0] + 8.58$ , where FSC = 0 to 1023.         |

|                  | Sleep | 7     | R/W |                    | 0 = enable DAC output, 1 = disable DAC output (sleep).                       |

#### Table 14. TxDAC Full-Scale Current Setting (IOUTFS) and Sleep Register

### **TxDAC QUAD-SWITCH MODE OF OPERATION**

#### Table 15. TxDAC Quad-Switch Mode of Operation Register

| Address<br>(Hex) | Name    | Bit   | R/W | Default<br>Setting | Comments                                                                        |

|------------------|---------|-------|-----|--------------------|---------------------------------------------------------------------------------|

| 0x08             | DAC-DEC | [1:0] | R/W | 0x00               | 0x00 = normal baseband mode.<br>0x01 = return-to-zero mode.<br>0x02 = mix mode. |

### DCI PHASE ALIGNMENT STATUS

#### Table 16. DCI Phase Alignment Status Register

| Address<br>(Hex) | Name        | Bit | R/W | Default<br>Setting | Comments                                                                                                                                                                    |

|------------------|-------------|-----|-----|--------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0x0C             | DCI_PRE_PH0 | 2   | R   | 0                  | 0 = DCI rising edge is after the PRE delayed version of the Phase 0 sampling edge.<br>1 = DCI rising edge is before the PRE delayed version of the Phase 0 sampling edge.   |

|                  | DCI_PST_PH0 | 0   | R   | 0                  | 0 = DCI rising edge is after the POST delayed version of the Phase 0 sampling edge.<br>1 = DCI rising edge is before the POST delayed version of the Phase 0 sampling edge. |

### SYNC\_IN PHASE ALIGNMENT STATUS

#### Table 17. SYNC\_IN Phase Alignment Status Register

| Address<br>(Hex) | Name         | Bit | R/W | Default<br>Setting | Comments                                                                                                            |

|------------------|--------------|-----|-----|--------------------|---------------------------------------------------------------------------------------------------------------------|

| 0x0D             | SYNC_IN_PH90 | 5   | R   | 0                  | 0 = SYNCIN rising edge is after Phase 90 sampling edge.<br>1 = SYNCIN rising edge is before Phase 90 sampling edge. |

|                  | SYNC_IN_PH0  | 4   | R   | 0                  | 0 = SYNCIN rising edge is after Phase 0 sampling edge.<br>1 = SYNCIN rising edge is before Phase 0 sampling edge.   |

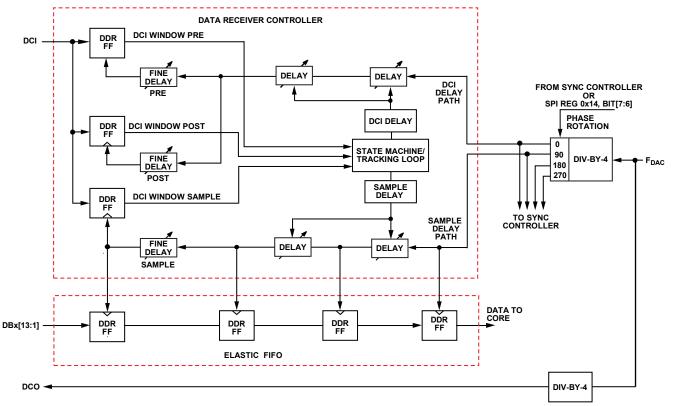

### DATA RECEIVER CONTROLLER CONFIGURATION

### Table 18. Data Receiver Controller Configuration Register

| Address<br>(Hex) | Name         | Bit | R/W | Default<br>Setting | Comments                                                                                                                                                                     |

|------------------|--------------|-----|-----|--------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0x10             | SYNC_FLG_RST | 7   | W   | 0                  | Sync controller flag reset. Write 1 followed by 0 to reset flags.                                                                                                            |

|                  | SYNC_LOOP_ON | 6   | R/W | 1                  | 0 = disable, 1 = enable. Enable for master only. When enabled, sync controller generates an IRQ when master falls out of lock and automatically begins search/track routine. |

|                  | SYNC_MST/SLV | 5   | R/W | 0                  | Sync controller configuration. $0 =$ slave, $1 =$ master.                                                                                                                    |

|                  | SYNC_CNT_ENA | 4   | R/W | 0                  | Sync controller enable. 0 = disable, 1 = enable                                                                                                                              |

|                  | RCVR_FLG_RST | 2   | W   | 0                  | Data receiver controller flag reset. Write 1 followed by 0 to reset flags.                                                                                                   |

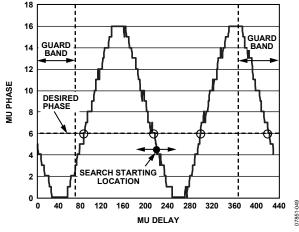

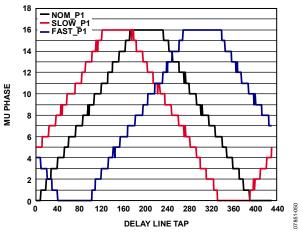

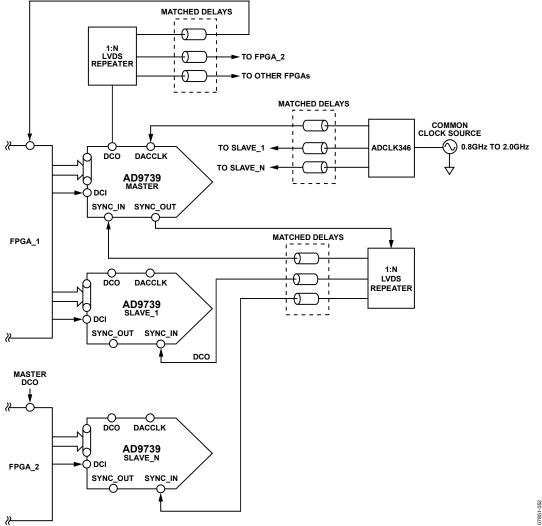

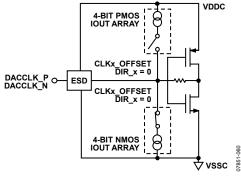

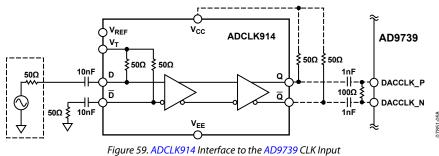

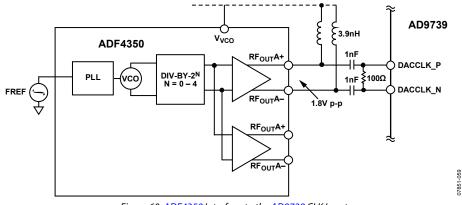

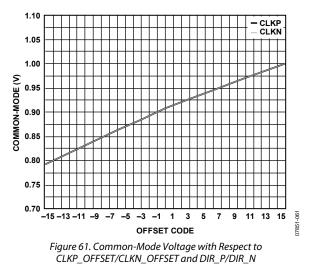

|                  | RCVR_LOOP_ON | 1   | R/W | 1                  | 0 = disable, 1 = enable. When enabled, the data receiver controller generates an IRQ; it falls out of lock and automatically begins a search/track routine.                  |