# 16-Bit 900 kSPS $\Sigma$ - $\Delta$ ADC with a Programmable Postprocessor

### AD7725

#### FEATURES

Programmable Filtering:

Any Characteristic up to 108 Tap FIR and/or IIR Polynomial Signal Conditioning up to 8<sup>th</sup> Order Programmable Decimation and Output Word Rate Flexible Programming Modes:

Boot from DSP or External EPROM Parallel/Serial Interface Internal Default Filter for Evaluation 14.4 MHz Max Master Clock Frequency 0 V to +4 V (Single-Ended) or ±2 V (Differential) Input Range Power Supplies: AV<sub>DD</sub>, DV<sub>DD</sub>: 5 V ± 5% On-Chip 2.5 V Voltage Reference 44-Lead MQFP Package TYPICAL APPLICATIONS

Radar Sonar Auxiliary Car Functions Medical Communications

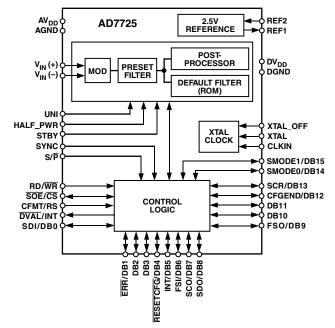

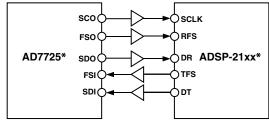

#### FUNCTIONAL BLOCK DIAGRAM

#### **GENERAL DESCRIPTION**

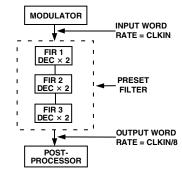

The AD7725 is a complete 16-bit,  $\Sigma$ - $\Delta$  analog-to-digital converter with on-chip, user-programmable signal conditioning. The output of the modulator is processed by three cascaded finite impulse response (FIR) filters, followed by a fully user-programmable postprocessor. The postprocessor provides processing power of up to 130 million accumulates (MAC) per second. The user has complete control over the filter response, the filter coefficients, and the decimation ratio.

The postprocessor permits the signal conditioning characteristics to be programmed through a parallel or serial interface. It is programmed by loading a user-defined filter in the form of a configuration file. This filter can be loaded from a DSP or an external serial EPROM. It is generated using a digital filter design package called Filter Wizard, which is available from the AD7725 section on the Analog Devices website. Filter Wizard allows the user to design different filter types and generates the appropriate configuration file to be downloaded to the postprocessor. The AD7725 also has an internal default filter for evaluation purposes.

It provides 16-bit performance for input bandwidths up to 350 kHz with an output word rate of 900 kHz maximum. The input sample rate is set either by the crystal oscillator or an external clock.

This part has an accurate on-chip 2.5 V reference for the modulator. A reference input/output function allows either the internal reference or an external system reference to be used as the reference source for the modulator.

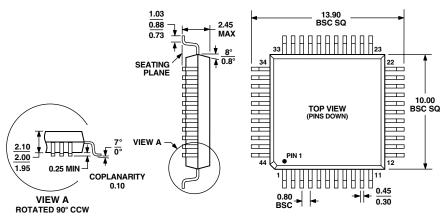

The device is available in a 44-lead MQFP package and is specified over a  $-40^{\circ}$ C to  $+85^{\circ}$ C temperature range.

#### REV. A

Information furnished by Analog Devices is believed to be accurate and reliable. However, no responsibility is assumed by Analog Devices for its use, nor for any infringements of patents or other rights of third parties that may result from its use. No license is granted by implication or otherwise under any patent or patent rights of Analog Devices. Trademarks and registered trademarks are the property of their respective owners.

One Technology Way, P.O. Box 9106, Norwood, MA 02062-9106, U.S.A. Tel: 781/329-4700 www.analog.com Fax: 781/326-8703 © 2004 Analog Devices, Inc. All rights reserved.

## $\label{eq:additional} AD7725 \mbox{--}SPECIFICATIONS^{1} (AV_{DD} = 5 \mbox{ V} \pm 5\%, \mbox{ AGND} = \mbox{ AGND1} = \mbox{ AGND2} = \mbox{ DGND} = 0 \mbox{ V}, \\ f_{CLKIN}^{2} = 9.6 \mbox{ MHz}, \mbox{ REF2} = 2.5 \mbox{ V}, \mbox{ T}_{A} = \mbox{ T}_{MIN} \mbox{ to } \mbox{ T}_{MAX}, \mbox{ unless otherwise noted.})$

|                                                                                                                                                                                                                                   |                                                                                                                                                                                                       |           | B Ver                                                      | sion                                                                      |                                        |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------|------------------------------------------------------------|---------------------------------------------------------------------------|----------------------------------------|

| Parameter                                                                                                                                                                                                                         | Test Conditions/Comments                                                                                                                                                                              | Min       | Тур                                                        | Max                                                                       | Unit                                   |

| DYNAMIC SPECIFICATIONS<br>Bipolar Mode<br>Signal-to-Noise <sup>3</sup><br>Total Harmonic Distortion <sup>3, 5</sup><br>Spurious Free Dynamic Range <sup>3, 5</sup><br>Unipolar Mode<br>Signal-to-Noise <sup>3</sup>               | When tested with the FIR filter in<br>Figure 1, HALF_PWR = Logic High<br>Measurement Bandwidth = $0.5 \times f_0^4$<br>2.5 V Reference<br>3 V Reference<br>Measurement Bandwidth = $0.5 \times f_0^4$ | 77<br>79  | 83<br>85<br>-94<br>-98<br>83                               | -86<br>-89                                                                | dB<br>dB<br>dB<br>dB<br>dB             |

| Total Harmonic Distortion <sup>3, 5</sup>                                                                                                                                                                                         |                                                                                                                                                                                                       |           | -94                                                        |                                                                           | dB                                     |

| ANALOG INPUTS<br>Full-Scale Input Span<br>Bipolar Mode<br>Unipolar Mode<br>Absolute Input Voltage<br>Input Sampling Capacitance<br>Input Sampling Rate, f <sub>CLKIN</sub>                                                        | $ \begin{array}{l} V_{IN}(+)-V_{IN}(-)\\ Differential \ or \ Single-Ended \ Input\\ Single-Ended \ Input\\ V_{IN}(+) \ and/or \ V_{IN}(-) \end{array} $                                               | 0<br>AGND | 2                                                          | $\pm 4/5 	imes V_{REF2}$<br>$8/5 	imes V_{REF2}$<br>$AV_{DD}$<br>$14.4^6$ | V<br>V<br>V<br>pF<br>MHz               |

| CLOCK<br>CLKIN Duty Ratio                                                                                                                                                                                                         |                                                                                                                                                                                                       | 45        |                                                            | 55                                                                        | %                                      |

| REFERENCE<br>REF1 Output Resistance<br>Reference Buffer<br>Offset Voltage<br>Using Internal Reference<br>REF2 Output Voltage<br>REF2 Output Voltage Drift<br>Using External Reference<br>REF2 Input Impedance                     | Offset between REF1 and REF2<br>REF1 = AGND                                                                                                                                                           | 2.39      | 3.5<br>±3<br>2.54<br>60<br>8                               | 2.69                                                                      | kΩ<br>mV<br>V<br>ppm/°C<br>kΩ<br>V     |

| REF2 External Voltage Input <sup>7</sup><br>STATIC PERFORMANCE<br>Resolution<br>Differential Nonlinearity (DNL) <sup>3</sup><br>Integral Nonlinearity (INL) <sup>3</sup><br>DC CMRR<br>Offset Error<br>Gain Error <sup>3, 9</sup> | Guaranteed Monotonic                                                                                                                                                                                  | 16        | 2.5<br>$\pm 0.5$<br>$\pm 2$<br>80<br>$\pm 20$<br>$\pm 0.5$ | ±1 <sup>8</sup>                                                           | Bits<br>LSB<br>LSB<br>dB<br>mV<br>%FSR |

| LOGIC INPUTS (Excluding CLKIN)<br>V <sub>INH</sub> , Input High Voltage<br>V <sub>INL</sub> , Input Low Voltage                                                                                                                   |                                                                                                                                                                                                       | 2.0       |                                                            | 0.8                                                                       | V<br>V                                 |

| CLOCK INPUT (CLKIN)<br>V <sub>INH</sub> , Input High Voltage<br>V <sub>INL</sub> , Input Low Voltage                                                                                                                              |                                                                                                                                                                                                       | 0.7 × D   | V <sub>DD</sub>                                            | $0.3 	imes DV_{DD}$                                                       | V<br>V                                 |

NOTES

<sup>1</sup>Operating temperature range is as follows: B Version: -40 °C to +85°C.

<sup>2</sup>f<sub>CLKIN</sub> is the CLKIN frequency.

<sup>3</sup>See Terminology section.

${}^{4}F_{O}$  = output data rate.

<sup>5</sup>When using the internal reference, THD and SFDR specifications apply only to input signals above 10 kHz with a 10 µF decoupling capacitor between REF2 and AGND2. At frequencies below 10 kHz, THD degrades to -80 dB and SFDR degrades to -83 dB.

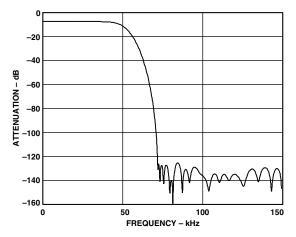

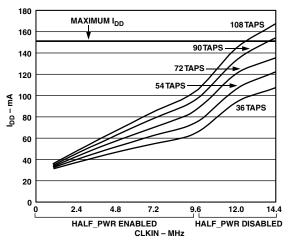

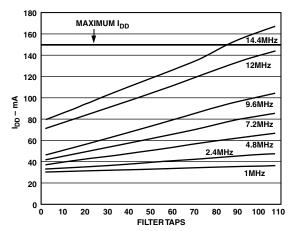

<sup>6</sup>See Figures 23 and 24 for information regarding the number of filter taps allowed and the current consumption as the CLKIN frequency is varied.

$^7$ The AD7725 can operate with an external reference input in the range of 1.2 V to 3.15 V.

<sup>8</sup>Guaranteed by the design.

<sup>9</sup>Gain Error excludes reference error.

$^{10}\mbox{All}\ I_{DD}$  tests are done with the digital inputs equal to 0 V or  $DV_{DD}.$

<sup>11</sup>Analog current does not vary as the CLKIN frequency and the number of filter taps used in the postprocessor is varied.

<sup>12</sup>If HALF\_PWR is logic low, AI<sub>DD</sub> will typically double.

<sup>13</sup>Digital current varies as the CLKIN frequency and the number of filter taps used in the postprocessor is varied. See Figures 23 and 24.

<sup>14</sup>Digital inputs static and equal to 0 V or  $DV_{DD}$ .

Specifications subject to change without notice.

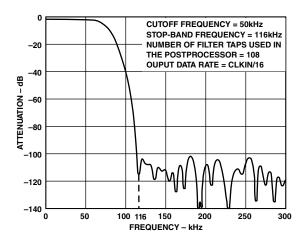

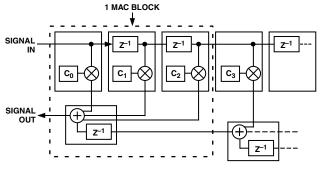

Figure 1. Digital Filter Characteristics Used for Specifications

### Preset Filter, Default Filter, and Postprocessor Characteristics<sup>1, 2</sup>

| Parameter                                                                                                                                                                 | Test Conditions/Comments          | Min                       | Тур                                                                                                             | Max                   | Unit                     |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------|---------------------------|-----------------------------------------------------------------------------------------------------------------|-----------------------|--------------------------|

| DIGITAL FILTER RESPONSE<br>PRESET FIR<br>Data Output Rate<br>Stop-Band Attenuation<br>Low-Pass Corner Frequency<br>Group Delay <sup>3</sup><br>Settling Time <sup>3</sup> |                                   | 70                        | $f_{cLKIN}/16$<br>133/(2 × $f_{cLKIN}$ )<br>133/ $f_{cLKIN}$                                                    | $f_{\rm CLKIN}/8$     | Hz<br>dB<br>Hz<br>s<br>s |

| DEFAULT FILTER<br>Number of Taps<br>Frequency Response                                                                                                                    | Internal FIR Filter Stored in ROM |                           |                                                                                                                 | 106                   |                          |

| 0 kHz to f <sub>CLKIN</sub> /546.08<br>f <sub>CLKIN</sub> /195.04<br>f <sub>CLKIN</sub> /184.08                                                                           |                                   | -3<br>-6                  |                                                                                                                 | ±0.001                | dB<br>dB<br>dB           |

| $f_{CLKIN}/133.2$ to $f_{CLKIN}/2$<br>Group Delay <sup>3</sup><br>Settling Time <sup>3</sup><br>Output Data Rate, $f_0$                                                   |                                   |                           | $\begin{array}{c} 2141/(2 \times f_{\text{CLKIN}}) \\ 2141/f_{\text{CLKIN}} \\ f_{\text{CLKIN}}/32 \end{array}$ | -120                  | dB<br>s<br>s<br>Hz       |

| POSTPROCESSOR CHARACTE<br>Input Data Rate<br>Coefficient Precision <sup>4</sup><br>Arithmetic Precision                                                                   | ERISTICS                          |                           | 24 30                                                                                                           | $f_{\rm CLKIN}/8$     | Hz<br>Bits<br>Bits       |

| Number of Taps Permitted<br>Decimation Factor<br>Number of Decimation Stages                                                                                              |                                   | 2                         |                                                                                                                 | 108<br>256<br>5       |                          |

| Output Data Rate                                                                                                                                                          |                                   | $f_{\text{CLKIN}}\!/4096$ |                                                                                                                 | $f_{\text{CLKIN}}/16$ | Hz                       |

NOTES

<sup>1</sup>These characteristics are fixed by the design. <sup>2</sup>f<sub>CLKIN</sub> is the CLKIN frequency. <sup>3</sup>See Terminology section.

<sup>4</sup>See the Configuration File Format section for more information.

| Parameter                                                                | Symbol                             | Min               | Тур | Max              | Unit             |

|--------------------------------------------------------------------------|------------------------------------|-------------------|-----|------------------|------------------|

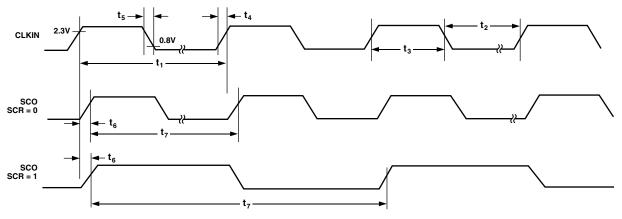

| CLKIN Frequency                                                          | f <sub>CLKIN</sub>                 | 1                 |     | 14.4             | MHz              |

| CLKIN Period ( $t_{CLK} = 1/f_{CLKIN}$ )                                 | t <sub>1</sub>                     | 0.07              |     | 1                | μs               |

| CLKIN Low Pulse Width                                                    | t <sub>2</sub>                     | $0.45 \times t_1$ |     | $0.55 	imes t_1$ |                  |

| CLKIN High Pulse Width                                                   | t <sub>3</sub>                     | $0.45 \times t_1$ |     | $0.55 	imes t_1$ |                  |

| CLKIN Rise Time                                                          | t <sub>4</sub>                     | 5                 |     | -                | ns               |

| CLKIN Fall Time                                                          | t <sub>5</sub>                     | 5                 |     |                  | ns               |

| CLKIN to SCO Delay                                                       | t <sub>6</sub>                     |                   | 35  | 50               | ns               |

| SCO Period: $SCR = 0$                                                    | t <sub>7</sub>                     |                   | 1   |                  | t <sub>CLK</sub> |

| SCR = 1                                                                  | t <sub>7</sub>                     |                   | 2   |                  | t <sub>CLK</sub> |

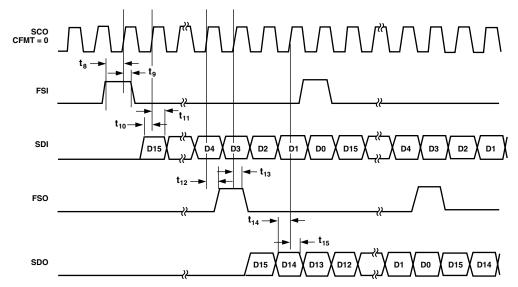

| SERIAL INTERFACE (DSP MODE ONLY)                                         |                                    |                   |     |                  |                  |

| FSI Setup Time before SCO Transition                                     | t <sub>8</sub>                     | 30                |     |                  | ns               |

| FSI Hold Time after SCO Transition                                       | t <sub>9</sub>                     | 0                 |     |                  | ns               |

| SDI Setup Time                                                           | t <sub>10</sub>                    | 30                |     |                  | ns               |

| SDI Hold Time                                                            | t <sub>11</sub>                    | 0                 |     |                  | ns               |

| SERIAL INTERFACE (DSP AND BFR MODES)                                     |                                    |                   |     |                  |                  |

| SCO Transition to FSO High Delay                                         | t <sub>12</sub>                    |                   |     | 20               | ns               |

| SCO Transition to FSO Low Delay                                          | t <sub>13</sub>                    |                   |     | 20               | ns               |

| SDO Setup before SCO Transition                                          | t <sub>14</sub>                    |                   |     | 10               | ns               |

| SDO Hold after SCO Transition                                            | t <sub>15</sub>                    | 0                 |     |                  | ns               |

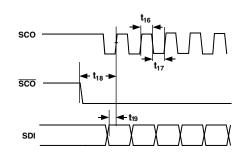

| SERIAL INTERFACE (EPROM MODE)                                            |                                    |                   |     |                  |                  |

| SCO High Time                                                            | t <sub>16</sub>                    |                   |     | 8                | t <sub>CLK</sub> |

| SCO Low Time                                                             | t <sub>17</sub>                    |                   |     | 8                | t <sub>CLK</sub> |

| SOE Low to First SCO Rising Edge                                         | t <sub>18</sub>                    |                   |     | 20               | t <sub>CLK</sub> |

| Data Setup before SCO Rising Edge                                        | t <sub>19</sub>                    |                   | 22  |                  | ns               |

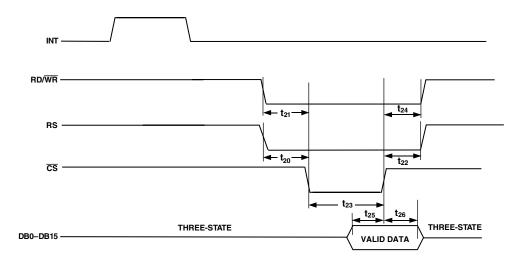

| PARALLEL INTERFACE                                                       |                                    |                   |     |                  |                  |

| DATA WRITE                                                               |                                    |                   |     |                  |                  |

| RS Low to $\overline{CS}$ Low                                            | t <sub>20</sub>                    | 15                |     |                  | ns               |

| $\overline{WR}$ Setup before $\overline{CS}$ Low                         | t <sub>21</sub>                    | 15                |     |                  | ns               |

| RS Hold after $\overline{CS}$ Rising Edge                                | t <sub>22</sub>                    | 0                 |     |                  | ns               |

| $\overline{\text{CS}}$ Pulse Width                                       | t <sub>23</sub>                    | 50                |     |                  | ns               |

| $\overline{\mathrm{WR}}$ Hold after $\overline{\mathrm{CS}}$ Rising Edge | t <sub>24</sub>                    | 0                 |     |                  | ns               |

| Data Setup Time                                                          | t <sub>25</sub>                    | 10                |     |                  | ns               |

| Data Hold Time                                                           | t <sub>26</sub>                    | 5                 |     |                  | ns               |

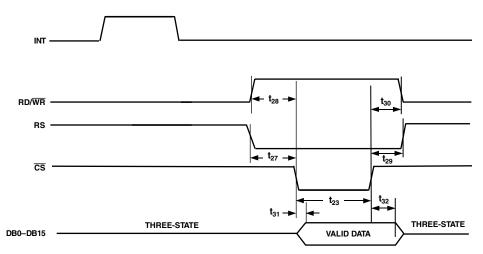

| DATA READ                                                                | 20                                 |                   |     |                  |                  |

| RS Low to $\overline{CS}$ Low                                            | t <sub>27</sub>                    | 15                |     |                  | ns               |

| RD Setup before $\overline{CS}$ Low                                      | t <sub>28</sub>                    | 15                |     |                  | ns               |

| RS Hold after $\overline{CS}$ Rising Edge                                | t <sub>29</sub>                    | 0                 |     |                  | ns               |

| RD Hold after $\overline{CS}$ Rising Edge                                | t <sub>30</sub>                    | 0                 |     |                  | ns               |

| Data Valid after $\overline{CS}$ Falling Edge <sup>3</sup>               | t <sub>30</sub>                    |                   |     | 30               | ns               |

| Data Hold after $\overline{CS}$ Rising Edge                              | t <sub>31</sub><br>t <sub>32</sub> | 10                |     | 2.0              | ns               |

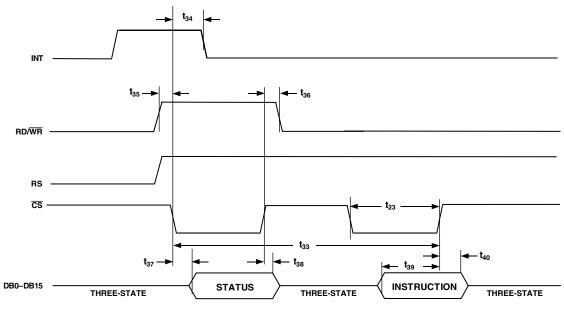

| STATUS READ/INSTRUCTION WRITE                                            | -32                                | 1                 |     |                  |                  |

| $\overline{\text{CS}}$ Duty Cycle                                        | t <sub>33</sub>                    | 1                 |     |                  | t <sub>CLK</sub> |

| Interrupt Clear after $\overline{CS}$ Low                                | t <sub>33</sub>                    | 1                 |     | 15               | ns               |

| RD Setup to $\overline{CS}$ Low                                          | t <sub>34</sub><br>t <sub>35</sub> | 15                |     | 15               | ns               |

| RD Hold after $\overline{CS}$ Rising Edge                                | t <sub>35</sub>                    |                   |     | 0                | ns               |

| Read Data Access Time <sup>3</sup>                                       |                                    |                   |     | 30               | ns               |

| Read Data Hold after $\overline{CS}$ Rising Edge                         | t <sub>37</sub>                    | 10                |     | 50               |                  |

| Write Data Setup before CS Rising Edge                                   | t <sub>38</sub>                    | 10                |     |                  | ns               |

| Write Data Hold after $\overline{CS}$ Rising Edge                        | t <sub>39</sub>                    | 5                 |     |                  | ns               |

| while Data Hold after US Kishig Edge                                     | t <sub>40</sub>                    | 9                 |     |                  | ns               |

NOTES

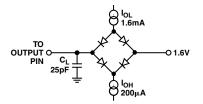

<sup>1</sup>Guaranteed by design. <sup>2</sup>Guaranteed by characterization. All input signals are specified with tr = tf = 5 ns (10% to 90% of  $DV_{DD}$ ) and timed from a voltage level of 1.6 V. <sup>3</sup>Measured with the load circuit in Figure 2 and defined as the time required for the output to cross 0.8 V and 2.4 V.

Figure 2. Load Circuit for Digital Output Timing Specifications

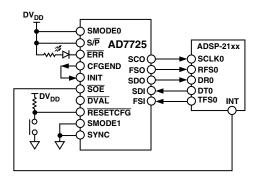

Figure 3. CLKIN to SCO Relationship

Figure 4. Serial Mode (DSP Mode and Boot from ROM (BFR) Mode). In BFR Mode, FSI and SDI are not used.

Figure 5. Serial Mode (EPROM Mode)

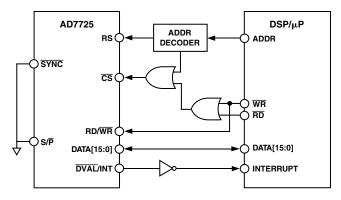

Figure 6. Parallel Mode (Writing Data to the AD7725)

Figure 7. Parallel Mode (Reading Data from the AD7725)

Figure 8. Parallel Mode (Reading the Status Register and Writing Instructions)

#### ABSOLUTE MAXIMUM RATINGS<sup>1</sup>

<sup>1</sup> Stresses above those listed under Absolute Maximum Ratings may cause permanent damage to the device. This is a stress rating only; functional operation of the device at these or any other conditions above those indicated in the operational section of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

<sup>2</sup> Transient currents of up to 100 mA will not cause SCR latch-up.

#### CAUTION .

ESD (electrostatic discharge) sensitive device. Electrostatic charges as high as 4000 V readily accumulate on the human body and test equipment and can discharge without detection. Although the AD7725 features proprietary ESD protection circuitry, permanent damage may occur on devices subjected to high energy electrostatic discharges. Therefore, proper ESD precautions are recommended to avoid performance degradation or loss of functionality.

#### **ORDERING GUIDE**

| Model                                 | Temperature<br>Range | Package<br>Description  | Package<br>Option <sup>1</sup> |  |  |

|---------------------------------------|----------------------|-------------------------|--------------------------------|--|--|

| AD7725BS                              | -40°C to +85°C       | Metric Quad<br>Flatpack | S-44-2                         |  |  |

| AD7725BS-REEL                         | -40°C to +85°C       | Metric Quad<br>Flatpack | S-44-2                         |  |  |

| EVAL-<br>AD7725CB <sup>2</sup>        |                      | Evaluation<br>Board     |                                |  |  |

| EVAL-<br>CONTROL<br>BRD2 <sup>3</sup> |                      | Controller<br>Board     |                                |  |  |

#### NOTES

<sup>1</sup>S = Metric Quad Flat Package (MQFP).

<sup>2</sup>This board can be used as a standalone evaluation board or in conjunction with the Evaluation Board Controller for evaluation/demonstration purposes. It is accompanied by software and technical documentation.

<sup>3</sup>Evaluation Board Controller. This board is a complete unit allowing a PC to control and communicate with all Analog Devices boards ending in the CB designator. To obtain the complete evaluation kit, the following needs to be ordered: EVAL-AD7725CB, EVAL-CONTROL BRD2, and a 12 V ac transformer. The Filter Wizard software can be downloaded from the Analog Devices website.

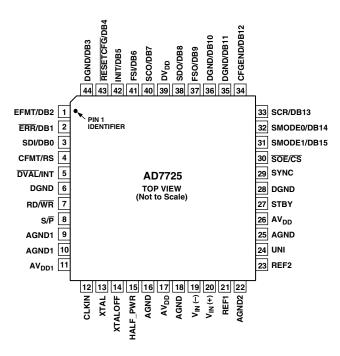

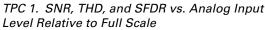

#### PIN CONFIGURATION

#### PIN FUNCTION DESCRIPTIONS

| Pin No. | Mnemonic S/P | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|---------|--------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1       | EFMT/DB2     | Serial Mode. EFMT–Serial Clock Format, Logic Input. This clock format pin selects<br>the clock edge to be used during configuration. When EFMT is low, Serial Data In is<br>valid on the rising edge of SCO; when EFMT is high, Serial Data In is valid<br>on the falling edge of SCO. During normal operation, this pin is ignored.<br>Parallel Mode. DB2–Data Input/Output Bit.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| 2       | ERR/DB1      | Serial Mode. ERR–Configuration Error Flag, Logic Output. If an error occurs during configuration, this output goes low and is reset high by a pulse on the RESETCFG pin. Parallel Mode. DB1–Data Input/Output Bit.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| 3       | SDI/DB0      | Serial Mode. SDI–Serial Data Input. Serial data is shifted in to the AD7725 MSB first, in twos complement format, synchronous with SCO.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| 4       | CFMT/RS      | <ul> <li>Parallel Mode. DB0–Data Input/Output Bit (LSB).</li> <li>Serial Mode. CFMT–Serial Clock Format, Logic Input. This clock format pin selects the clock edge to be used during normal operation. When CFMT is low, Serial Data Out is valid on the rising edge of SCO; when CFMT is high, Serial Data Out is valid on the falling edge of SCO. During configuration, this pin is ignored.</li> <li>Parallel Mode. RS–Register Select. RS selects between the data register, used to read conversion data or write configuration data, and the instruction register. When RS is high, the status register can be read or an instruction can be written to the AD7725. When RS is low, data such as the configuration file can be written to the ADC while data such as the device ID or a conversion result can be read from the AD7725 (see Table I).</li> </ul> |

REV. A

| Pin No. | Mnemonic S/P        | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|---------|---------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 5       | DVAL/INT            | <ul> <li>Serial Mode. DVAL-Data Valid Logic Output. This output is low when there are no overflows in the postprocessor and goes high when an overflow occurs in the postprocessor.</li> <li>Parallel Mode. INT-Interrupt Logic Output. INT idles low. A logic high on this output pin indicates that user intervention is required. There are several cases when this may occur:</li> <li>An instruction is completed. Writing an instruction or reading the status register clears the interrupt.</li> <li>Write data is requested. Writing data clears the interrupt.</li> </ul> |

|         |                     | <ul> <li>Read data is ready. Reading data clears the interrupt.</li> <li>An error occurs - ID or CRC error in the configuration file format, or an overflow in the postprocessor. Reading the status register clears the interrupt.</li> </ul>                                                                                                                                                                                                                                                                                                                                      |

|         |                     | • The device completes power-on reset. Reading the status register clears the interrupt.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| 6<br>7  | DGND<br>RD/WR       | Ground Reference for Digital Circuitry.<br><b>Serial Mode</b> . This input is not used in serial mode and should be tied to DGND.<br><b>Parallel Mode</b> . Read/Write Logic Input. This input is used in conjunction with the $\overline{CS}$                                                                                                                                                                                                                                                                                                                                      |

| 8       | S/P                 | input to read data from or write data to the device. A read cycle is initiated when $RD/\overline{WR}$ is high. A write cycle is initiated when $RD/\overline{WR}$ is low. To read or write data, $\overline{CS}$ should be low. Serial/Parallel Interface Select. When $S/\overline{P}$ is tied low, parallel mode is selected. Serial mode is selected when $S/\overline{P}$ is tied high. To change the mode, a full power cycle needs                                                                                                                                           |

|         |                     | to be performed.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| 9,10    | AGND1               | Digital Logic Power Supply Ground for the Analog Modulator.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| 11      | AV <sub>DD1</sub>   | Digital Logic Power Supply for the Analog Modulator.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

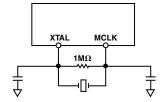

| 12      | CLKIN               | Clock Input. An external clock source can be applied directly to this pin with XTALOFF tied high. Alternatively, a parallel resonant fundamental frequency crystal, in parallel with a 1 M $\Omega$ resistor, can be connected between the XTAL pin and the CLKIN pin with XTALOFF tied low. External capacitors are then required from the CLKIN and XTAL pins to ground. Consult the crystal manufacturer's recommendation for the load capacitors.                                                                                                                               |

|         |                     | In both cases, once power is applied to the AD7725, the clock input has to be continual.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| 13      | XTAL                | Input to Crystal Oscillator Amplifier. If an external clock is used, XTAL should be tied to AGND1.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| 14      | XTALOFF             | Oscillator Enable Input. A logic high disables the crystal oscillator amplifier to allow the use of an external clock source. Set low to enable the crystal oscillator amplifier when using an external crystal between the CLKIN and XTAL pins.                                                                                                                                                                                                                                                                                                                                    |

| 15      | HALF_PWR            | Logic Input. When this input is low, the typical analog current is 50 mA and a maximum CLKIN frequency of 14.4 MHz applies. When this input is high, the analog current typically halves and a maximum CLKIN frequency of 9.6 MHz applies.                                                                                                                                                                                                                                                                                                                                          |

| 16, 18  | AGND                | Power Supply Ground for the Analog Modulator.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| 17      | AV <sub>DD</sub>    | Power Supply Voltage for the Analog Modulator.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| 19      | V <sub>IN</sub> (-) | Negative Terminal of the Differential Analog Input.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| 20      | $V_{IN}(+)$         | Positive Terminal of the Differential Analog Input.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

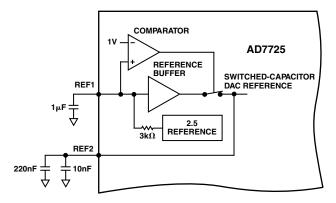

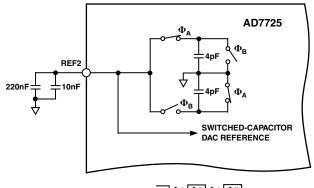

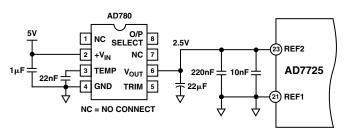

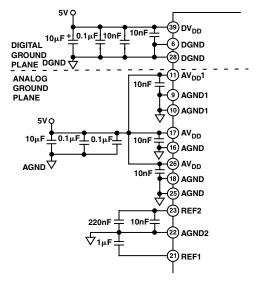

| 21      | REF1                | Reference Output. REF1 is connected to the output of the internal 2.5 V reference through a 3 k $\Omega$ resistor and to a reference buffer amplifier that drives the $\Sigma$ - $\Delta$ modulator. When the internal reference is used, a 1 $\mu$ F capacitor is required between REF1 and AGND to decouple the band gap noise and REF2 should be decoupled to AGND with a 220 nF and a 10 nF capacitor in parallel.                                                                                                                                                              |

| 22      | AGND2               | Power Supply Ground for the Reference Circuitry, REF2, of the Analog Modulator.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| 23      | REF2                | Reference Input. REF2 connects to the output of an external buffer amplifier used to drive the $\Sigma$ - $\Delta$ modulator. When REF2 is used as an input, REF1 must be connected to AGND to disable the internal buffer amplifier.                                                                                                                                                                                                                                                                                                                                               |

| 24      | UNI                 | Analog Input Range Select Input. The UNI pin selects the analog input range for either bipolar (differential or single-ended input) or unipolar (single-ended input) operation. A logic high input selects unipolar operation and a logic low input selects bipolar operation.                                                                                                                                                                                                                                                                                                      |

| 25      | AGND                | Power Supply Ground for the Analog Modulator.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| 26      | AV <sub>DD</sub>    | Power Supply Voltage for the Analog Modulator.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| Pin No. | Mnemonic S/P                   | Description                                                                                                                                                                                                                                                                                                                                                                               |

|---------|--------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 27      | STBY                           | Standby, Logic Input. When STBY is taken high, the device will enter a low power mode.<br>If the device was fully configured before entering this mode, it will not lose its configuration data.<br>When STBY is brought low, the device exits the low power mode. If the device<br>was partially configured before entering the low power mode, it will restart the configuration        |

|         |                                | process in the case of boot from ROM (BFR) mode, DSP mode, and EPROM mode or, in<br>parallel mode, a new configure instruction must be issued to configure the device. If the device<br>was fully configured before entering the low power mode, it will continue to output conversion<br>results in all serial modes; in parallel mode, the device will wait for an instruction to begin |

|         |                                | converting. In STBY mode, the clock input must be continual.                                                                                                                                                                                                                                                                                                                              |

| 28      | DGND                           | Ground Reference for Digital Circuitry.                                                                                                                                                                                                                                                                                                                                                   |

| 29      | SYNC                           | Synchronization Logic Input. When using more than one AD7725 operated from a common master clock, SYNC allows each ADC to simultaneously sample its analog input and update its output register. When SYNC is high, the digital filter sequencer counter is reset to zero and the postprocessor core is reset. Because the digital filter and sequencer                                   |

|         |                                | are completely reset during this action, SYNC pulses cannot be applied continuously.<br>When SYNC is taken low, normal conversions continue, with valid data resulting after the                                                                                                                                                                                                          |

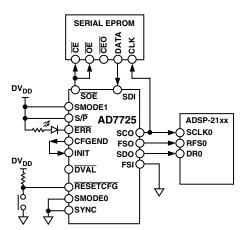

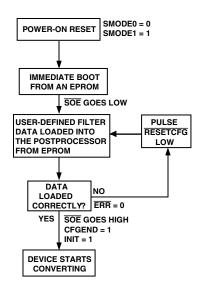

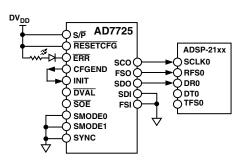

| 30      | <del>SOE</del> / <del>CS</del> | filter setting time.<br>Serial Mode. SOE-Serial Output Enable. In EPROM mode, SOE going low enables the                                                                                                                                                                                                                                                                                   |

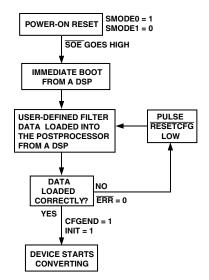

|         |                                | external EPROM and is used to reset the EPROM's address counter. In DSP mode, SOE is an active high interrupt. It goes high after a power-on reset and after a pulse on the RESETCERG                                                                                                                                                                                                     |

|         |                                | pin, indicating the device is ready to be configured. It also goes high following a successful                                                                                                                                                                                                                                                                                            |

|         |                                | configuration, indicating that the device was configured correctly. SOE is reset low when FSI is detected high by CLKIN. In BFR mode, SOE pulses high for eight CLKIN cycles at the end                                                                                                                                                                                                   |

|         |                                | of a successful configuration.<br><b>Parallel Mode</b> . CS-Chip Select Logic Input. This is an active low logic input used in                                                                                                                                                                                                                                                            |

|         |                                | conjunction with the $RD/\overline{WR}$ input to read data from or write data to the device. For a                                                                                                                                                                                                                                                                                        |

|         |                                | read operation, the falling edge of $\overline{CS}$ takes the bus out of three-state and either the                                                                                                                                                                                                                                                                                       |

|         |                                | conversion data or the status register data (depending on the state of the RS input), is                                                                                                                                                                                                                                                                                                  |

|         |                                | placed onto the data bus, after the time $t_{31}$ . For a write operation, the rising edge of $\overline{CS}$ is used to latch either the configuration data or the instruction (depending on the state of                                                                                                                                                                                |

|         |                                | the RS input) into the AD7725. In this case, the data should be set up for a time $t_{25}$ before the $\overline{CS}$ rising edge.                                                                                                                                                                                                                                                        |

| 31      | SMODE1/DB15                    | Serial Mode. SMODE1-Serial Mode Select, Logic Input. This pin selects the serial mode to                                                                                                                                                                                                                                                                                                  |

|         |                                | be used (see Table IV) and thus informs the device where to download configuration data from                                                                                                                                                                                                                                                                                              |

|         |                                | automatically on power up. To change the value on this pin, a full power cycle needs to be performed.                                                                                                                                                                                                                                                                                     |

|         |                                | Parallel Mode. DB15–Data Input/Output Bit (MSB).                                                                                                                                                                                                                                                                                                                                          |

| 32      | SMODE0/DB14                    | Serial Mode. SMODE0–Serial Mode Select, Logic Input. This pin selects the serial mode to                                                                                                                                                                                                                                                                                                  |

|         |                                | be used (see Table IV) and thus informs the device where to download configuration data                                                                                                                                                                                                                                                                                                   |

|         |                                | from automatically on power-up. To change the value on this pin, a full power cycle needs to be performed.                                                                                                                                                                                                                                                                                |

| 33      | SCR/DB13                       | Parallel Mode. DB14–Data Input/Output Bit.           Serial Mode. SCR–Serial Clock Rate Select, Logic Input. With SCR set to logic low,                                                                                                                                                                                                                                                   |

| 55      | SCIUDIIS                       | the serial clock output frequency, SCO, is equal to the CLKIN frequency. A logic high                                                                                                                                                                                                                                                                                                     |

|         |                                | sets the frequency of SCO to one half the CLKIN frequency.                                                                                                                                                                                                                                                                                                                                |

|         |                                | Parallel Mode. DB13–Data Input/Output Bit.                                                                                                                                                                                                                                                                                                                                                |

| 34      | CFGEND/DB12                    | Serial Mode. CFGEND-Configuration End, Logic Output. A logic high on CFGEND                                                                                                                                                                                                                                                                                                               |

|         |                                | indicates that device programming is complete and no programming errors occurred.                                                                                                                                                                                                                                                                                                         |

| 35      | DGND/DB11                      | Parallel Mode. DB12–Data Input/Output Bit.<br>Serial Mode. DGND–Digital Ground.                                                                                                                                                                                                                                                                                                           |

|         |                                | Parallel Mode. DB11–Data Input/Output Bit.                                                                                                                                                                                                                                                                                                                                                |

| 36      | DGND/DB10                      | Serial Mode. DGND-Digital Ground.                                                                                                                                                                                                                                                                                                                                                         |

|         |                                | Parallel Mode. DB10-Data Input/Output Bit.                                                                                                                                                                                                                                                                                                                                                |

| 37      | FSO/DB9                        | <b>Serial Mode</b> . FSO–Frame Synchronization Output. FSO indicates the beginning of a                                                                                                                                                                                                                                                                                                   |

|         |                                | word transmission on the SDO pin. The FSO signal is a positive pulse approximately one SCO period wide.                                                                                                                                                                                                                                                                                   |

|         |                                | Parallel Mode. DB9–Data Input/Output Bit.                                                                                                                                                                                                                                                                                                                                                 |

| Pin No. | Mnemonic S/P         | Description                                                                                      |

|---------|----------------------|--------------------------------------------------------------------------------------------------|

| 38      | SDO/DB8              | Serial Mode. SDO-Serial Data Output. The serial data is shifted out of the AD7725 MSB            |

|         |                      | first, in twos complement format, synchronous with SCO.                                          |

|         |                      | Parallel Mode. DB8–Data Input/Output Bit.                                                        |

| 39      | DV <sub>DD</sub>     | Digital Power Supply Voltage.                                                                    |

| 40      | SCO/DB7              | Serial Mode. SCO-Serial Clock Output. The frequency of SCO is a function of the CLKIN            |

|         |                      | frequency and is set by the SCR pin. When configuration data is being loaded into the            |

|         |                      | AD7725, SCO = $f_{CLKIN}/16$ .                                                                   |

|         |                      | Parallel Mode. DB7–Data Input/Output Bit.                                                        |

| 41      | FSI/DB6              | Serial Mode. FSI-Frame Synchronization Input. FSI indicates the beginning of a word              |

|         |                      | transmission on the SDI pin.                                                                     |

|         |                      | Parallel Mode. DB6–Data Input/Output Bit.                                                        |

| 42      | INIT/DB5             | Serial Mode. INIT-Logic Input. When the device is correctly configured, a logic low on this      |

|         |                      | pin will prevent the device from converting. When this pin is taken high, the device will start  |

|         |                      | converting. When daisy-chaining multiple devices, this pin ensures that all devices sample their |

|         |                      | analog inputs simultaneously without needing to activate the SYNC pin.                           |

|         |                      | Parallel Mode. DB5–Data Input/Output Bit.                                                        |

| 43      | <b>RESETCFG</b> /DB4 | Serial Mode. RESETCFG-Logic Input. RESETCFG is used to reset the part when a                     |

|         |                      | configuration error occurs. A low pulse on this pin will reset the part, and the configuration   |

|         |                      | file will be downloaded again. The SOE pin will go high following a pulse on the RESETCFG        |

|         |                      | pin and then again following a successful configuration.                                         |

|         |                      | Parallel Mode. DB4–Data Input/Output Bit.                                                        |

| 44      | DGND/DB3             | Serial Mode. DGND-Digital Ground.                                                                |

|         |                      | Parallel Mode. DB3–Data Input/Output Bit.                                                        |

#### TERMINOLOGY

#### Integral Nonlinearity (INL)

This is the maximum deviation of any code from a straight line passing through the endpoints of the transfer function. The endpoints of the transfer function are zero scale (not to be confused with bipolar zero), a point 0.5 LSB below the first code transition  $(100 \dots 00 \text{ to } 100 \dots 01 \text{ in bipolar mode}, 000 \dots 00 \text{ to } 000 \dots 01 \text{ in unipolar mode})$  and full scale, a point 0.5 LSB above the last code transition  $(011 \dots 10 \text{ to } 011 \dots 11 \text{ in bipolar mode}, 111 \dots 10 \text{ to } 111 \dots 11 \text{ in unipolar mode})$ . The error is expressed in LSBs.

#### Differential Nonlinearity (DNL)

This is the difference between the measured and the ideal 1 LSB change between two adjacent codes in the ADC.

#### **Unipolar Offset Error**

Unipolar offset error is the deviation of the first code transition from the ideal  $V_{IN}(+)$  voltage, which is  $(V_{IN}(-) + 0.5 \text{ LSB})$  when operating in the unipolar mode.

#### **Bipolar Offset Error**

This is the deviation of the midscale transition code  $(111\ldots 11 \text{ to } 000\ldots 00)$  from the ideal  $V_{\rm IN}(+)$  voltage, which is  $(V_{\rm IN}(-)-0.5$  LSB) when operating in the bipolar mode.

#### **Gain Error**

The first code transition should occur at an analog value 0.5 LSB above negative full scale. The last code transition should occur for an analog value 1.5 LSB below the nominal full scale. Gain error is the deviation of the actual difference between first and last code transitions and the ideal difference between first and last code transitions.

#### Signal-to-Noise Ratio (SNR)

SNR is the measured signal-to-noise ratio at the output of the ADC. The signal is the rms magnitude of the fundamental. Noise is the rms sum of all of the nonfundamental signals up to half the output data rate ( $f_0/2$ ), excluding dc. The ADC is evaluated by applying a low noise, low distortion sine wave signal to the input pins. By generating a Fast Fourier Transform (FFT) plot, the SNR data can then be obtained from the output spectrum.

#### **Total Harmonic Distortion (THD)**

THD is the ratio of the rms sum of the harmonics to the rms value of the fundamental. THD is defined as

THD =

$$20 \log \left( \frac{\sqrt{V_2^2 + V_3^2 + V_4^2 + V_5^2 + V_6^2}}{V_1} \right)$$

where  $V_1$  is the rms amplitude of the fundamental and  $V_2$ ,  $V_3$ ,  $V_4$ ,  $V_5$ , and  $V_6$  are the rms amplitudes of the second through sixth harmonics.

#### Spurious Free Dynamic Range (SFDR)

Defined as the difference, in dB, between the peak spurious or harmonic component in the ADC output spectrum (up to  $f_0/2$  and excluding dc) and the rms value of the fundamental. Normally, the value of this specification will be determined by the largest harmonic in the output spectrum of the FFT. For input signals whose second harmonics occur in the stop band region of the digital filter, the spur in the noise floor limits the SFDR.

#### Settling Time and Group Delay

The settling time of a digital filter is dependent on the amount of decimation employed and the number of filter taps used in the filter design and is calculated as follows:

settling time =

$$\left(\frac{1}{data \ input \ rate}\right) \times number \ of \ taps$$

The settling time for each filter stage should be calculated separately and then added to get the total filter settling time. Group delay is half the settling time.

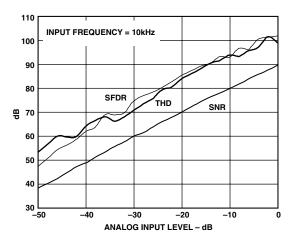

### **AD7725–Typical Performance Characteristics**

#### PERFORMANCE PLOTS

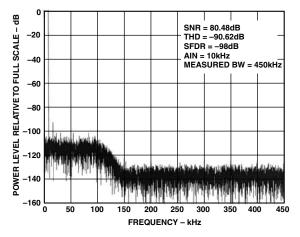

The following typical plots are generated using the digital filter shown in Figure 1.  $(AV_{DD} = DV_{DD}, T_A = 25^{\circ}C, CLKIN = 9.6 \text{ MHz}, \text{ External Reference} = 2.5 \text{ V}, unless otherwise noted.})$

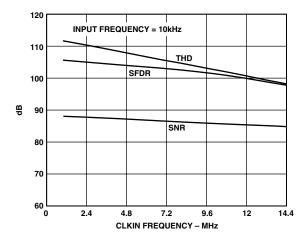

TPC 2. SNR, THD, and SFDR vs. Sampling Frequency

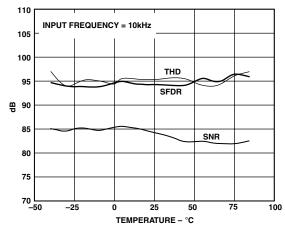

TPC 3. SNR, THD, and SFDR vs. Temperature

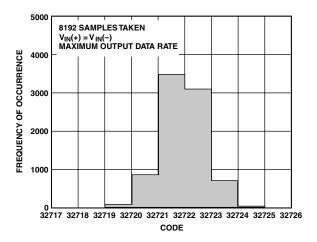

TPC 4. Histogram of Output Codes for a DC Input

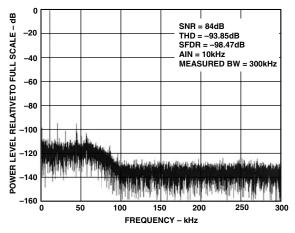

TPC 5. 16k Point FFT

TPC 6. 16k Point FFT for a 108 Tap Low-Pass FIR Filter Operating with a CLKIN Frequency of 14.4 MHz

#### CIRCUIT DESCRIPTION

The AD7725 employs a  $\Sigma$ - $\Delta$  conversion technique to convert the analog input into an equivalent digital word. The modulator samples the input waveform and outputs an equivalent digital word at the input clock frequency, f<sub>CLKIN</sub>.

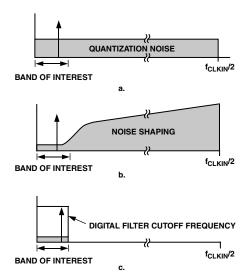

Due to the high oversampling rate, which spreads the quantization noise from 0 to  $f_{CLKIN}/2$ , the noise energy contained in the band of interest is reduced (Figure 9a). To further reduce the quantization noise, a high order modulator is employed to shape the noise spectrum so that most of the noise energy is shifted out of the band of interest (Figure 9b).

The digital filtering that follows the modulator removes the large out-of-band quantization noise (Figure 9c) while also reducing the data rate from  $f_{\rm CLKIN}$  at the input of the filter to  $f_{\rm CLKIN}/16$  or less at the output of the filter, depending on the filter type used.

Digital filtering has certain advantages over analog filtering. Because digital filtering occurs after the A/D conversion, it can remove noise injected during the conversion process. Analog filtering cannot do this. The digital filter also has a linear phase response.

#### Figure 9. $\Sigma$ - $\Delta$ ADC

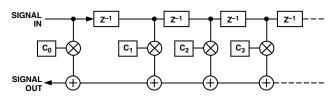

The AD7725 employs three fixed finite impulse response (FIR) filters in series. Each individual filter's output data rate is half that of its input data rate. The fourth stage is programmable; the user can select a range of different filter responses at this stage. Both the filter response and the decimation are user programmable. See the Filtering section for more details.

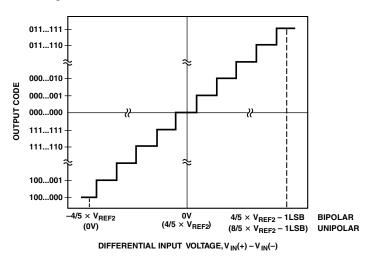

#### APPLYING THE AD7725 Analog Input Range

The AD7725 has differential inputs to provide common-mode noise rejection. In unipolar mode, the analog input is singleended and its range is 0 V to  $(8/5 \times V_{REF2})$ . In bipolar mode, the analog input is single-ended or differential, and its input range is  $\pm (4/5 \times V_{REF2})$ . The output code is twos complement in both modes with 1 LSB = 61  $\mu$ V.

The ideal input/output transfer characteristics for the two modes are shown in Figure 10. In both modes, the absolute voltage on each input must remain within the supply range AGND to  $AV_{DD}$ . Bipolar mode allows either single-ended or differential input signals while unipolar mode allows single-ended signals.

Figure 10. Bipolar/(Unipolar) Mode Transfer Function

The AD7725 will accept full-scale inband signals; however, large scale out-of-band signals can overload the modulator inputs. A minimal single-pole RC antialias filter set to  $f_{\rm CLKIN}/24$  will allow full-scale input signals over the entire frequency spectrum.

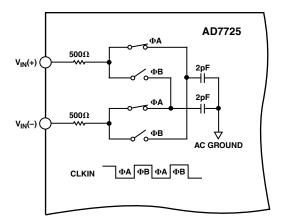

#### Analog Input

The analog input of the AD7725 uses a switched capacitor technique to sample the input signal. For the purpose of driving the AD7725, an equivalent circuit of the analog inputs is shown in Figure 11. For each half-clock cycle, two highly linear sampling capacitors are switched to both inputs, converting the input signal into an equivalent sampled charge. A signal source driving the analog inputs must be able to source this charge, while also settling to the required accuracy by the end of each half-clock phase.

Figure 11. Analog Input Equivalent Circuit

#### **Driving the Analog Inputs**

To interface the signal source to the AD7725, at least one op amp will generally be required. The choice of op amp will be critical to achieving the full performance of the AD7725. The op amp not only has to recover from the transient loads that the ADC imposes on it, but it must also have good distortion characteristics and very low input noise. Resistors in the signal path will also add to the overall thermal noise floor, necessitating the choice of low value resistors.

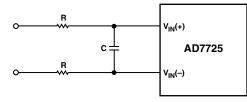

Placing an RC filter between the drive source and the ADC inputs, as shown in Figure 12, has a number of beneficial effects: transients on the op amp outputs are significantly reduced since the external capacitor now supplies the instantaneous charge required when the sampling capacitors are switched to the ADC input pins, and input circuit noise at the sample images is now significantly attenuated, resulting in improved overall SNR. The external resistor serves to isolate the external capacitor from the ADC output, thus improving op amp stability while also isolating the op amp output from any remaining transients on the capacitor. By experimenting with different filter values, the optimum performance can be achieved for each application. As a guideline, the RC time constant  $(R \times C)$  should be less than a quarter of the clock period to avoid nonlinear currents from the ADC inputs being stored on the external capacitor and degrading distortion. This restriction means that this filter cannot form the main antialias filter for the ADC.

Figure 12. Input RC Network

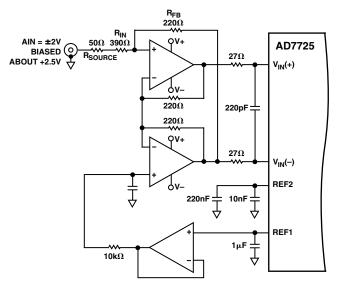

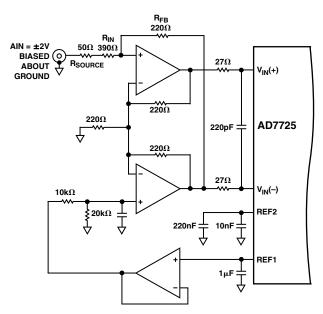

With the unipolar input mode selected, just one op amp is required to buffer the single-ended input signal to the  $V_{IN}(+)$  input, and a dc input is applied to the  $V_{IN}(-)$  pin to provide an offset. However, driving the AD7725 with differential signals (i.e., the bipolar input range is selected) has some distinct advantages: even-order harmonics in both the drive circuits and the AD7725 front end are attenuated, and the peak-to-peak input signal range on both inputs is halved. Halving the input signal range allows some op amps to be powered from the same supplies as the AD7725. An example of providing differential drive to the AD7725 is to use a dual op amp.

#### **Dual Op Amp**

Although this differential drive circuit will require two op amps per ADC, it may avoid the need to generate additional supplies just for these op amps.

Figures 13 and 14 show two circuits for driving the AD7725. Figure 13 is intended for use when the input signal is biased about 2.5 V, while Figure 14 is used when the input signal is biased about ground. While both circuits convert the input signal into a differential signal, the circuit in Figure 14 also level shifts the signal so that both outputs are biased about 2.5 V.

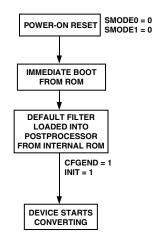

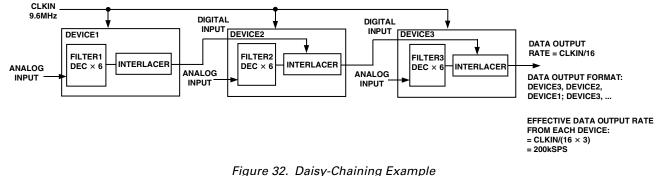

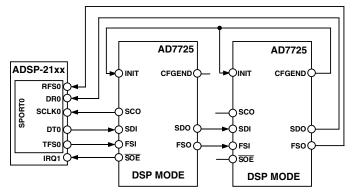

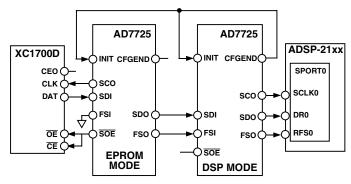

Suitable op amps include the AD8047, the AD8041 and its dual equivalent the AD8042, or the AD8022. The AD8047 has lower input noise than the AD8041/AD8042 but has to be supplied from a +7.5 V/-2.5 V supply. The AD8041/AD8042 will typically degrade the SNR from 83 dB to 81 dB but can be powered from the same single 5 V supply as the AD7725.