# **Broadband Modem Mixed-Signal Front End**

AD9868

#### **FEATURES**

Low cost 3.3 V CMOS MxFE for broadband modems 10-bit DAC converter 2×/4× interpolation filter 200 MSPS DAC update rate Integrated 17 dBm line driver with 19.5 dB gain control 10-bit, 80 MSPS, ADC converter -12 dB to +48 dB low noise RxPGA (<3 nV/√Hz) Third-order, programmable low-pass filter Flexible digital data path interface Half- and full-duplex operation Pin compatible with the AD9865 Various power-down/reduction modes Internal clock multiplier (PLL) 2 auxiliary programmable clock outputs Available in a 64-lead LFCSP\_VQ

#### **APPLICATIONS**

**Broadband wireline networking**

#### **GENERAL DESCRIPTION**

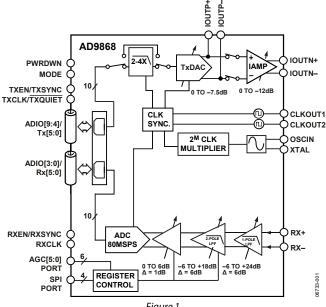

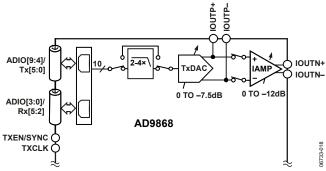

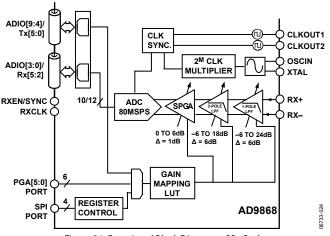

The AD9868 is a mixed-signal front-end (MxFE\*) IC for transceiver applications requiring Tx path and Rx path functionality with data rates up to 80 MSPS. A lower cost, pincompatible version of the AD9865, the AD9868 removes the current amplifier (IAMP) IOUTP functionality and limits the PLL VCO operating range of 80 MHz to 200 MHz.

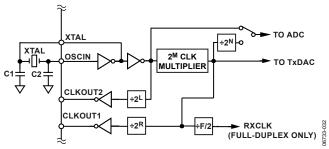

The part is well-suited for half- and full-duplex applications. The digital interface is extremely flexible, allowing simple interfacing to digital back ends that support half- or full-duplex data transfers, often allowing the AD9868 to replace discrete ADC and DAC solutions. Power-saving modes include the ability to reduce power consumption of individual functional blocks or power down unused blocks in half-duplex applications. A serial port interface (SPI) allows software programming of the various functional blocks. An on-chip PLL clock multiplier and synthesizer provide all the required internal clocks, as well as two external clocks, from a single crystal or clock source.

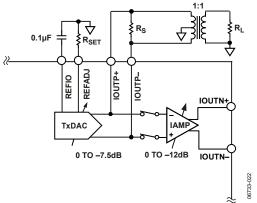

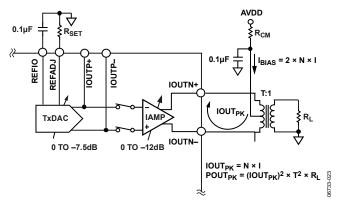

The Tx signal path consists of a  $2\times/4\times$  low-pass interpolation filter, a 10-bit TxDAC, and a line driver. The transmit path signal bandwidth can be as high as 34 MHz at an input data rate

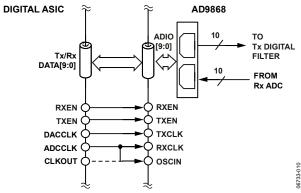

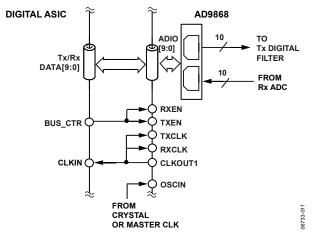

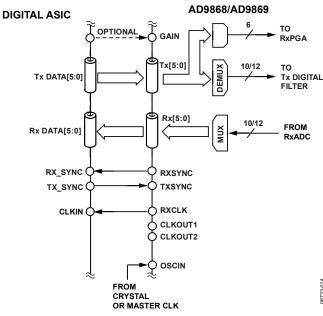

#### FUNCTIONAL BLOCK DIAGRAM

Figure 1.

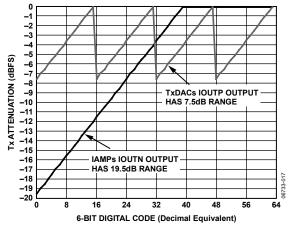

of 80 MSPS. The TxDAC provides differential current outputs that can be steered directly to an external load or to an internal low distortion current amplifier (IAMP) capable of delivering 17 dBm peak signal power. Tx power can be digitally controlled over a 19.5 dB range in 0.5 dB steps.

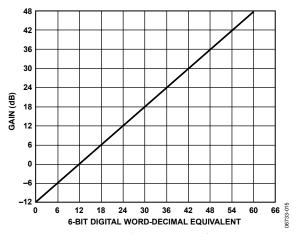

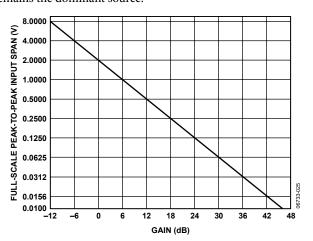

The receive path consists of a programmable amplifier (RxPGA), a tunable low-pass filter (LPF), and a 10-bit ADC. The low noise RxPGA has a programmable gain range of −12 dB to +48 dB in 1 dB steps. Its input referred noise is less than 3 nV/ $\sqrt{\text{Hz}}$  for gain settings beyond 36 dB. The receive path LPF cutoff frequency can be set over a 15 MHz to 35 MHz range or it can be simply bypassed. The 10-bit ADC achieves excellent dynamic performance up to an 80 MSPS span. Both the RxPGA and the ADC offer scalable power consumption allowing power/performance optimization.

The AD9868 provides a highly integrated solution for many broadband modems. It is available in a space-saving package, a 16-lead LFCSP, and is specified over the commercial temperature range  $(-40^{\circ}\text{C to } +85^{\circ}\text{C})$ .

Information furnished by Analog Devices is believed to be accurate and reliable. However, no  $responsibility is assumed by Analog \, Devices for its \, use, nor for any infringements \, of \, patents \, or \, other \, or$ rights of third parties that may result from its use. Specifications subject to change without notice. No license is granted by implication or otherwise under any patent or patent rights of Analog Devices. Trademarks and registered trademarks are the property of their respective owners.

# **TABLE OF CONTENTS**

| Features                                                         | 1        |

|------------------------------------------------------------------|----------|

| Applications                                                     | 1        |

| Functional Block Diagram                                         | 1        |

| General Description                                              | 1        |

| Revision History                                                 | 2        |

| Specifications                                                   | 3        |

| Tx Path Specifications                                           | 3        |

| Rx Path Specifications                                           | 4        |

| Power Supply Specifications                                      | 6        |

| Digital Specifications                                           | 7        |

| Serial Port Timing Specifications                                | 7        |

| Half-Duplex Data Interface (ADIO Port) Timing Specifications     | 8        |

| Full-Duplex Data Interface (Tx and Rx Port) Timin Specifications | _        |

| Absolute Maximum Ratings                                         | 9        |

| Thermal Characteristics                                          |          |

| Explanation of Test Levels                                       | 9        |

| ESD Caution                                                      | 9        |

| Pin Configuration and Function Descriptions                      | 10       |

|                                                                  |          |

| Serial Port                                                      | 12       |

| Serial Port<br>Register Map Description                          |          |

|                                                                  | 14       |

| Register Map Description                                         | 14<br>14 |

| Full-Duplex Mode                       | 17 |

|----------------------------------------|----|

| RxPGA Control                          | 19 |

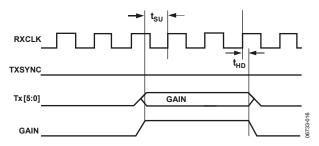

| TxPGA Control                          | 20 |

| Transmit Path                          | 21 |

| Digital Interpolation Filters          | 21 |

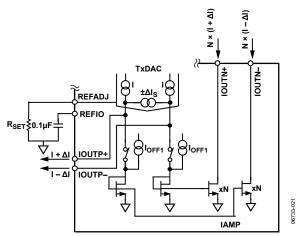

| TxDAC and IAMP Architecture            | 22 |

| Tx Programmable Gain Control           | 23 |

| TxDAC Output Operation                 | 23 |

| IAMP Current-Mode Operation            | 23 |

| Receive Path                           | 24 |

| Rx Programmable Gain Amplifier         | 24 |

| Low-Pass Filter                        | 25 |

| Analog-to-Digital Converter (ADC)      | 26 |

| AGC Timing Considerations              | 27 |

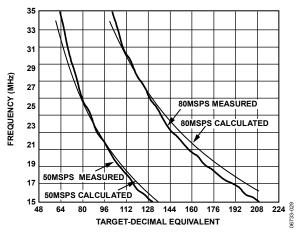

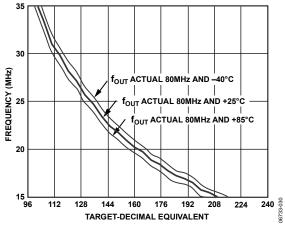

| Clock Synthesizer                      | 28 |

| Power Control and Dissipation          | 30 |

| Power-Down                             | 30 |

| Half-Duplex Power Savings              | 30 |

| Power Reduction Options                | 31 |

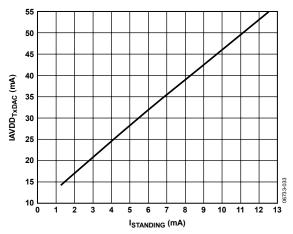

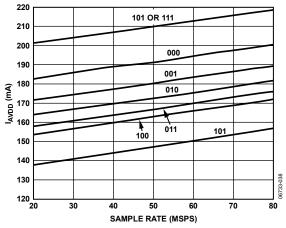

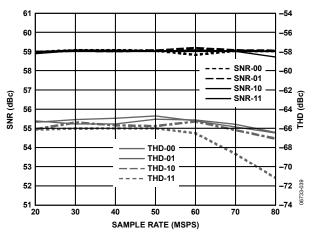

| Power Dissipation                      | 33 |

| Mode Select upon Power-Up and Reset    | 33 |

| Analog and Digital Loopback Test Modes | 34 |

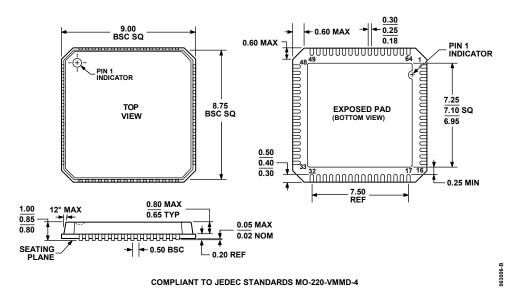

| Outline Dimensions                     | 35 |

| Ordaring Cuida                         | 25 |

#### **REVISION HISTORY**

5/07—Revision 0: Initial Version

# **SPECIFICATIONS**

### **Tx PATH SPECIFICATIONS**

$AVDD = 3.3~V \pm 5\%, DVDD = CLKVDD = DRVDD = 3.3~V \pm 10\%, f_{OSCIN} = 50~MHz, f_{DAC} = 200~MHz, R_{SET} = 2.0~k\Omega, unless otherwise noted.$

Table 1.

| Parameter                                                                   | Temp | Test Level <sup>1</sup> | Min  | Тур     | Max   | Unit                               |

|-----------------------------------------------------------------------------|------|-------------------------|------|---------|-------|------------------------------------|

| TxDAC DC CHARACTERISTICS                                                    |      |                         |      |         |       |                                    |

| Resolution                                                                  | Full |                         |      | 10      |       | Bits                               |

| Update Rate                                                                 | Full | П                       |      |         | 200   | MSPS                               |

| ·<br>Full-Scale Output Current (IOUTP_FS)                                   | Full | IV                      | 2    |         | 25    | mA                                 |

| Gain Error <sup>2</sup>                                                     | 25°C | 11                      |      | ±2      |       | % FS                               |

| Offset Error                                                                | 25°C | V                       |      | 2       |       | μΑ                                 |

| Voltage Compliance Range                                                    | Full |                         | -1   | _       | +1.5  | V                                  |

| TXDAC GAIN CONTROL CHARACTERISTICS                                          |      |                         | •    |         |       | -                                  |

| Minimum Gain                                                                | 25°C | V                       |      | -7.5    |       | dB                                 |

| Maximum Gain                                                                | 25°C | V                       |      | 0       |       | dB                                 |

| Gain Step Size                                                              | 25°C | V                       |      | 0.5     |       | dB                                 |

| Gain Step Size                                                              | 25℃  | IV                      |      | Monotor | nic   | dB                                 |

| Gain Range Error                                                            | 25°C | V                       |      | ±2      | IIC   | dB                                 |

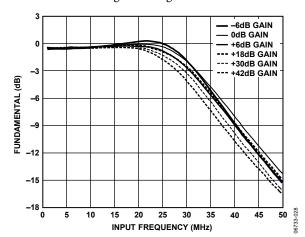

| TxDAC AC CHARACTERISTICS <sup>3</sup>                                       | 25 C | + <b>v</b>              |      |         |       | UD                                 |

| Fundamental                                                                 |      |                         |      | 0.5     |       | dBm                                |

| Signal-to-Noise and Distortion (SINAD)                                      | Full | IV                      | 62.0 | 63.1    |       | dBc                                |

|                                                                             | Full | IV                      | 1    |         |       | dBc                                |

| Signal-to-Noise Ratio (SNR)                                                 | -    |                         | 62.5 | 63.2    | 67.0  |                                    |

| Total Harmonic Distortion (THD)                                             | Full | IV                      | 67.1 | -77.7   | -67.0 | dBc                                |

| Spurious-Free Dynamic Range (SFDR)                                          | Full | IV                      | 67.1 | 79.3    |       | dBc                                |

| IAMP DC CHARACTERISTICS                                                     |      |                         |      |         |       |                                    |

| IOUTN Full-Scale Current = IOUTN+ + IOUTN-                                  | Full | IV                      | 2    |         | 105   | mA                                 |

| AC Voltage Compliance Range                                                 | Full | IV                      | 1    |         | 3.9   | V                                  |

| IAMPN AC CHARACTERISTICS <sup>4</sup>                                       |      |                         |      |         |       |                                    |

| Fundamental                                                                 | 25°C |                         |      | 13      |       | dBm                                |

| IOUTN SFDR (Third Harmonic)                                                 | Full | IV                      | 43.3 | 45.2    |       | dBc                                |

| REFERENCE                                                                   |      |                         |      |         |       |                                    |

| Internal Reference Voltage <sup>5</sup>                                     | 25°C | 1                       |      | 1.23    |       | V                                  |

| Reference Error                                                             | Full | V                       |      | 0.7     | 3.4   | %                                  |

| Reference Drift                                                             | Full | V                       |      | 30      |       | ppm/°C                             |

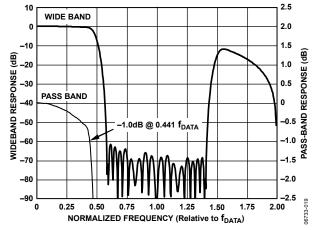

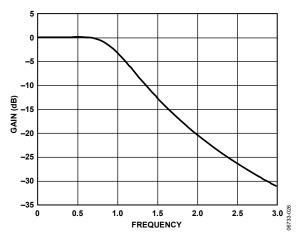

| Tx DIGITAL FILTER CHARACTERISTICS (2× Interpolation)                        |      |                         |      |         |       |                                    |

| Latency (Relative to 1/f <sub>DAC</sub> )                                   | Full | V                       |      | 43      |       | Cycles                             |

| –0.2 dB Bandwidth                                                           | Full | V                       |      | 0.2187  |       | f <sub>OUT</sub> /f <sub>DAC</sub> |

| −3 dB Bandwidth                                                             | Full | V                       |      | 0.2405  |       | f <sub>OUT</sub> /f <sub>DAC</sub> |

| Stop-Band Rejection (0.289 f <sub>DAC</sub> to 0.711 f <sub>DAC</sub> )     | Full | V                       |      | 50      |       | dB                                 |

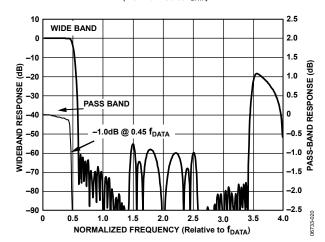

| Tx DIGITAL FILTER CHARACTERISTICS (4× Interpolation)                        |      |                         |      |         |       |                                    |

| Latency (Relative to 1/f <sub>DAC</sub> )                                   | Full | V                       |      | 96      |       | Cycles                             |

| –0.2 dB Bandwidth                                                           | Full | V                       |      | 0.1095  |       | fout/fdac                          |

| −3 dB Bandwidth                                                             | Full | V                       |      | 0.1202  |       | f <sub>OUT</sub> /f <sub>DAC</sub> |

| Stop Band Rejection (0.289 f <sub>oscin</sub> to 0.711 f <sub>oscin</sub> ) | Full | V                       |      | 50      |       | dB                                 |

| PLL CLK MULTIPLIER                                                          |      | <del>  -</del>          |      |         |       |                                    |

| OSCIN Frequency Range                                                       |      |                         |      |         |       |                                    |

| PLL M Factor Set to 2                                                       | Full | IV                      | 40   |         | 80    | MHz                                |

| PLL M Factor Set to 2                                                       | Full | IV                      | 20   |         | 50    | MHz                                |

| PLL M Factor Set to 8                                                       | Full | IV                      | 10   |         | 25    | MHz                                |

|                                                                             | Full |                         | 80   |         | 200   | MHz                                |

| Internal VCO Frequency Range                                                |      | IV                      |      |         |       |                                    |

| Duty Cycle                                                                  | Full | II                      | 40   |         | 60    | %                                  |

Rev. 0 | Page 3 of 36

| Parameter                                   | Temp | Test Level <sup>1</sup> | Min | Тур    | Max | Unit   |

|---------------------------------------------|------|-------------------------|-----|--------|-----|--------|

| OSCIN Impedance                             | 25°C | V                       |     | 10  03 |     | MΩ  pF |

| CLKOUT1 Jitter <sup>6</sup>                 | 25°C | III                     |     | 12     |     | ps rms |

| CLKOUT2 Jitter <sup>7</sup>                 | 25°C | III                     |     | 6      |     | ps rms |

| CLKOUT1 and CLKOUT2 Duty Cycle <sup>8</sup> | Full | III                     | 45  |        | 55  | %      |

$<sup>^{\</sup>mbox{\tiny 1}}$  See the Explanation of Test Levels section.

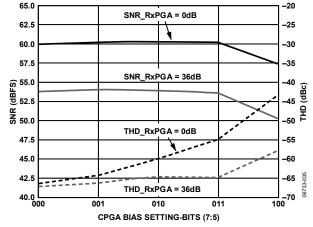

#### **Rx PATH SPECIFICATIONS**

$AVDD = 3.3 \text{ V} \pm 5\%$ ,  $DVDD = CLKVDD = DRVDD = 3.3 \text{ V} \pm 10\%$ , half- or full-duplex operation with CONFIG = 0 default power bias settings, unless otherwise noted.

Table 2.

| Parameter                                                            | Temp | Test Level <sup>1</sup> | Min Typ     | Max Max | Unit   |

|----------------------------------------------------------------------|------|-------------------------|-------------|---------|--------|

| Rx INPUT CHARACTERISTICS                                             |      |                         |             |         |        |

| Input Voltage Span                                                   |      |                         |             |         |        |

| RxPGA Gain = $-10 \text{ dB}$                                        | Full | III                     | 6.33        | 3       | V p-p  |

| RxPGA Gain = $+48 \text{ dB}$                                        | Full | III                     | 8           |         | mV p-p |

| Input Common-Mode Voltage                                            | 25°C | III                     | 1.3         |         | V      |

| Differential Input Impedance                                         | 25°C | III                     | 400         | 4.0     | Ω  pF  |

| Input Bandwidth with RxLPF Disabled, RxPGA = $0 \text{ dB}$          | 25°C | III                     | 53          |         | MHz    |

| Input Voltage Noise Density                                          |      |                         |             |         |        |

| RxPGA Gain = $36 \text{ dB}$ , $f_{-3 \text{ dBF}} = 26 \text{ MHz}$ | 25°C | III                     | 3.0         |         | nV/√Hz |

| RxPGA Gain = 48 dB, $f_{-3 dBF}$ = 26 MHz                            | 25°C | III                     | 2.4         |         | nV/√Hz |

| RxPGA CHARACTERISTICS                                                |      |                         |             |         |        |

| Minimum Gain                                                         | 25°C | III                     | -12         | 2       | dB     |

| Maximum Gain                                                         | 25°C | III                     | 48          |         | dB     |

| Gain Step Size                                                       | 25°C | III                     | 1           |         | dB     |

| Gain Step Accuracy                                                   | 25°C | III                     | Monotonic   |         | dB     |

| Gain Range Error                                                     | 25°C | III                     | 0.5         |         | dB     |

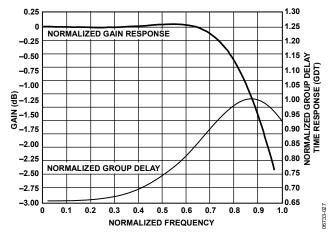

| RxLPF CHARACTERISTICS                                                |      |                         |             |         |        |

| Cutoff Frequency (f <sub>−3 dBF</sub> ) Range                        | Full | III                     | 15          | 35      | MHz    |

| Attenuation at 55.2 MHz with $f_{-3 dBF} = 21 MHz$                   | 25°C | III                     | 20          |         | dB     |

| Pass-Band Ripple                                                     | 25°C | III                     | ±1          |         | dB     |

| Settling Time                                                        |      |                         |             |         |        |

| 5 dB RxPGA Gain Step @ f <sub>ADC</sub> = 50 MSPS                    | 25°C | III                     | 20          |         | ns     |

| 60 dB RxPGA Gain Step @ f <sub>ADC</sub> = 50 MSPS                   | 25°C | III                     | 100         | )       | ns     |

| ADC DC CHARACTERISTICS                                               |      |                         |             |         |        |

| Resolution                                                           | N/A  | N/A                     | 10          |         | Bits   |

| Conversion Rate                                                      | Full | II                      | 20          | 80      | MSPS   |

| Rx PATH LATENCY <sup>2</sup>                                         |      |                         |             |         |        |

| Full-Duplex Interface                                                | Full | V                       | 10.         |         | Cycles |

| Half-Duplex Interface                                                | Full | V                       | 10.0        | )       | Cycles |

| Rx PATH COMPOSITE AC PERFORMANCE @ $f_{ADC} = 50 \text{ MSPS}^3$     |      |                         |             |         |        |

| RxPGA Gain = $48 \text{ dB}$ (Full-Scale = $8.0 \text{ mV p-p}$ )    |      |                         |             |         |        |

| Signal-to-Noise and Distortion (SINAD)                               | 25°C | III                     | 43.7        |         | dBc    |

| Total Harmonic Distortion (THD)                                      | 25°C | III                     | <b>-7</b> 1 |         | dBc    |

<sup>&</sup>lt;sup>2</sup> Gain error and gain temperature coefficients are based on the ADC only (with a fixed 1.23 V external reference and a 1 V p-p differential analog input).

<sup>&</sup>lt;sup>3</sup> TxDAC IOUTP\_FS = 20 mA, differential output with 1:1 transformer with source and load termination of 50 Ω, f<sub>out</sub> = 5 MHz, 4x interpolation.

$<sup>^4</sup>$  IOUTN full-scale current = 80 mA,  $f_{OSCIN}$  = 80 MHz,  $f_{DAC}$  =160 MHz, 2x interpolation.

<sup>&</sup>lt;sup>5</sup> Use external amplifier to drive additional load.

<sup>&</sup>lt;sup>6</sup> Internal VCO operates at 200 MHz; set to divide-by-1.

<sup>7</sup> Because CLKOUT2 is a divided-down version of OSCIN, its jitter is typically equal to OSCIN.

<sup>&</sup>lt;sup>8</sup> CLKOUT2 is an inverted replica of OSCIN, if set to divide-by-1.

| Parameter                                                                  | Temp | Test Level <sup>1</sup> | Min  | Тур   | Max   | Unit |

|----------------------------------------------------------------------------|------|-------------------------|------|-------|-------|------|

| RxPGA Gain = 24 dB (Full-Scale = 126 mV p-p)                               |      |                         |      |       |       |      |

| Signal-to-Noise Ratio (SNR)                                                | 25°C | III                     |      | 59    |       | dBc  |

| Total Harmonic Distortion (THD)                                            | 25°C | III                     |      | -67.2 |       | dBc  |

| RxPGA Gain = 0 dB (Full-Scale = 2.0 V p-p)                                 |      |                         |      |       |       |      |

| Signal-to-Noise and Distortion (SINAD)                                     | Full | IV                      | 58   | 59    |       | dBc  |

| Total Harmonic Distortion (THD)                                            | Full | IV                      |      | -66   | -62.9 | dBc  |

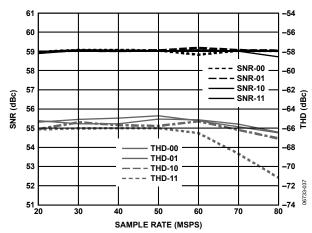

| Rx PATH COMPOSITE AC PERFORMANCE @ f <sub>ADC</sub> = 80 MSPS <sup>4</sup> |      |                         |      |       |       |      |

| RxPGA Gain = $48 \text{ dB}$ (Full-Scale = $8.0 \text{ mV p-p}$ )          |      |                         |      |       |       |      |

| Signal-to-Noise Ratio (SNR)                                                | 25°C | III                     |      | 41.8  |       | dBc  |

| Total Harmonic Distortion (THD)                                            | 25°C | III                     |      | -67   |       | dBc  |

| RxPGA Gain = 24 dB (Full-Scale = 126 mV p-p)                               |      |                         |      |       |       |      |

| Signal-to-Noise Ratio (SNR)                                                | 25°C | III                     |      | 58.6  |       | dBc  |

| Total Harmonic Distortion (THD)                                            | 25°C | III                     |      | -62.9 |       | dBc  |

| RxPGA Gain = 0 dB (Full-Scale = 2.0 V p-p)                                 |      |                         |      |       |       |      |

| Signal-to-Noise Ratio (SNR)                                                | 25°C | II                      | 58.9 | 59.6  |       | dBc  |

| Total Harmonic Distortion (THD)                                            | 25°C | II                      |      | -69.7 | -59.8 | dBc  |

| Rx-to-Tx PATH FULL-DUPLEX ISOLATION (1 V p-p, 10 MHz Sine Wave Tx Output)  |      |                         |      |       |       |      |

| RxPGA Gain = $40 \text{ dB}$                                               |      |                         |      |       |       |      |

| IOUTP± Pins to RX± Pins                                                    | 25°C | III                     |      | 83    |       | dBc  |

| RxPGA Gain = $0 \text{ dB}$                                                |      |                         |      |       |       |      |

| IOUTP± Pins to RX± Pins                                                    | 25°C | III                     |      | 123   |       | dBc  |

$<sup>^1</sup>$  See the Explanation of Test Levels section.  $^2$  Includes RxPGA, ADC pipeline, and ADIO bus delay relative to  $f_{ADC}$ .  $^3$   $f_{\rm IN}=5$  MHz, AIN =-1.0 dBFS, LPF cutoff frequency set to 15.5 MHz with Register 0x08 =0x80.  $^4$   $f_{\rm IN}=5$  MHz, AIN =-1.0 dBFS, LPF cutoff frequency set to 26 MHz with Register 0x08 =0x80.

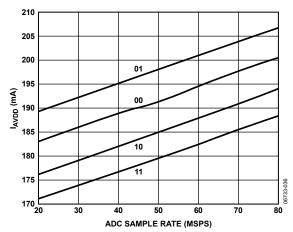

#### **POWER SUPPLY SPECIFICATIONS**

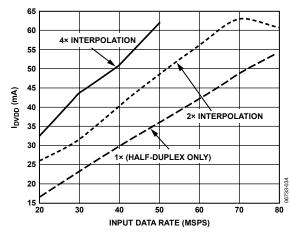

$AVDD = 3.3 \text{ V}, DVDD = CLKVDD = DRVDD = 3.3 \text{ V}, R_{SET} = 2 \text{ k}\Omega, \text{ full-duplex operation with } f_{DATA} = 80 \text{ MSPS}^1, \text{ unless otherwise noted.}$

Table 3.

| Parameter                                                                                      | Temp | Test Level <sup>2</sup> | Min   | Тур  | Max   | Unit |

|------------------------------------------------------------------------------------------------|------|-------------------------|-------|------|-------|------|

| SUPPLY VOLTAGES                                                                                |      |                         |       |      |       |      |

| AVDD                                                                                           | Full | V                       | 3.135 | 3.3  | 3.465 | V    |

| CLKVDD                                                                                         | Full | V                       | 3.0   | 3.3  | 3.6   | V    |

| DVDD                                                                                           | Full | V                       | 3.0   | 3.3  | 3.6   | V    |

| DRVDD                                                                                          | Full | V                       | 3.0   | 3.3  | 3.6   | V    |

| IS_TOTAL (Total Supply Current)                                                                | Full | II                      |       | 406  | 475   | mA   |

| POWER CONSUMPTION                                                                              |      |                         |       |      |       |      |

| I <sub>AVDD</sub> + I <sub>CLKVDD</sub> (Analog Supply Current)                                | Full | IV                      |       | 311  | 342   | mA   |

| I <sub>DVDD</sub> + I <sub>DRVDD</sub> (Digital Supply Current)                                | Full | IV                      |       | 95   | 133   | mA   |

| POWER CONSUMPTION (Half-Duplex Operation with $f_{DATA} = 50 \text{ MSPS}$ ) <sup>3</sup>      |      |                         |       |      |       |      |

| Tx Mode                                                                                        |      |                         |       |      |       |      |

| lavdd + Iclkvdd                                                                                | 25°C | IV                      |       | 112  | 130   | mA   |

| lovod + lorvod                                                                                 | 25°C | IV                      |       | 46   | 49.5  | mA   |

| Rx Mode                                                                                        |      |                         |       |      |       |      |

| lavdd + Iclkvdd                                                                                | 25°C | IV                      |       | 225  | 253   | mA   |

| $I_{DVDD} + I_{DRVDD}$                                                                         | 25°C | IV                      |       | 36.5 | 39    | mA   |

| POWER CONSUMPTION OF FUNCTIONAL BLOCKS <sup>1</sup> (I <sub>AVDD</sub> + I <sub>CLKVDD</sub> ) |      |                         |       |      |       |      |

| RxPGA and LPF                                                                                  | 25°C | III                     |       | 87   |       | mA   |

| ADC                                                                                            | 25°C | III                     |       | 108  |       | mA   |

| TxDAC                                                                                          | 25°C | III                     |       | 38   |       | mA   |

| IAMP (Programmable)                                                                            | 25°C | III                     | 10    |      | 100   | mA   |

| Reference                                                                                      | 25°C | III                     |       | 170  |       | mA   |

| CLK PLL and Synthesizer                                                                        | 25°C | III                     |       | 107  |       | mA   |

| MAXIMUM ALLOWABLE POWER DISSIPATION                                                            | Full | IV                      |       |      | 1.66  | W    |

| STANDBY POWER CONSUMPTION                                                                      |      |                         |       |      |       |      |

| IS_TOTAL (Total Supply Current)                                                                | Full |                         |       | 13   |       | mA   |

| POWER-DOWN DELAY (Using PWRDWN Pin)                                                            |      |                         |       |      |       |      |

| RxPGA and LPF                                                                                  | 25°C | III                     |       | 440  |       | ns   |

| ADC                                                                                            | 25°C | III                     |       | 12   |       | ns   |

| TxDAC                                                                                          | 25°C | III                     |       | 20   |       | ns   |

| IAMP                                                                                           | 25°C | III                     |       | 20   |       | ns   |

| CLK PLL and Synthesizer                                                                        | 25°C | III                     |       | 27   |       | ns   |

| POWER-UP DELAY (Using PWRDWN Pin)                                                              |      |                         |       |      |       |      |

| RxPGA and LPF                                                                                  | 25°C | III                     |       | 7.8  |       | μs   |

| ADC                                                                                            | 25°C | III                     |       | 88   |       | ns   |

| TxDAC                                                                                          | 25°C | III                     |       | 13   |       | μs   |

| IAMP                                                                                           | 25°C | III                     |       | 20   |       | ns   |

| CLK PLL and Synthesizer                                                                        | 25°C | III                     |       | 20   |       | μs   |

<sup>&</sup>lt;sup>1</sup> Default power-up settings for MODE = high and CONFIG = low, IOUTP\_FS = 20 mA, does not include IAMP current consumption, which is application dependent.

<sup>&</sup>lt;sup>2</sup> See the Explanation of Test Levels section.

<sup>&</sup>lt;sup>3</sup> Default power-up settings for MODE = low and CONFIG = low.

#### **DIGITAL SPECIFICATIONS**

AVDD = 3.3 V  $\pm$  5%, DVDD = CLKVDD = DRVDD = 3.3 V  $\pm$  10%, R<sub>SET</sub> = 2 k $\Omega$ , unless otherwise noted.

Table 4.

| Parameter                                          | Temp | Test Level <sup>1</sup> | Min         | Тур     | Max | Unit         |

|----------------------------------------------------|------|-------------------------|-------------|---------|-----|--------------|

| CMOS LOGIC INPUTS                                  |      |                         |             |         |     |              |

| High Level Input Voltage                           | Full | VI                      | DRVDD - 0.7 |         |     | V            |

| Low Level Input Voltage                            | Full | VI                      |             |         | 0.4 | V            |

| Input Leakage Current                              |      |                         |             |         | 12  | μΑ           |

| Input Capacitance                                  | Full | VI                      |             | 3       |     | pF           |

| CMOS LOGIC OUTPUTS (C <sub>LOAD</sub> = 5 pF)      |      |                         |             |         |     |              |

| High Level Output Voltage (I <sub>OH</sub> = 1 mA) | Full | VI                      | DRVDD - 0.7 |         |     | V            |

| Low Level Output Voltage (I <sub>OH</sub> = 1 mA)  | Full | VI                      |             |         | 0.4 | V            |

| Output Rise/Fall Time                              |      |                         |             |         |     |              |

| High Strength Mode and CLOAD = 15 pF               | Full | VI                      |             | 1.5/2.3 |     | ns           |

| Low Strength Mode and CLOAD = 15 pF                | Full | VI                      |             | 1.9/2.7 |     | ns           |

| High Strength Mode and CLOAD = 5 pF                | Full | VI                      |             | 0.7/0.7 |     | ns           |

| Low Strength Mode and C <sub>LOAD</sub> = 5 pF     | Full | VI                      |             | 1.0/1.0 |     | ns           |

| RESET                                              |      |                         |             |         |     |              |

| Minimum Low Pulse Width (Relative to fade)         |      |                         | 1           |         |     | Clock cycles |

$<sup>^{\</sup>mbox{\tiny 1}}$  See the Explanation of Test Levels section.

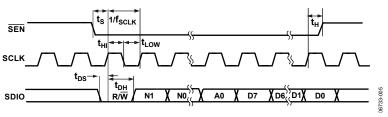

#### **SERIAL PORT TIMING SPECIFICATIONS**

AVDD = 3.3 V  $\pm$  5%, DVDD = CLKVDD = DRVDD = 3.3 V  $\pm$  10%, unless otherwise noted.

Table 5.

| Parameter                                                   | Temp | Test Level <sup>1</sup> | Min | Тур | Max | Unit |

|-------------------------------------------------------------|------|-------------------------|-----|-----|-----|------|

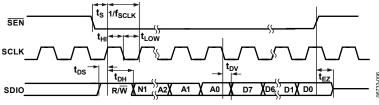

| WRITE OPERATION (See Figure 5)                              |      |                         |     |     |     |      |

| SCLK Clock Rate (f <sub>SCLK</sub> )                        | Full | IV                      |     |     | 32  | MHz  |

| SCLK Clock High (t <sub>HI</sub> )                          | Full | IV                      | 14  |     |     | ns   |

| SCLK Clock Low (t <sub>LOW</sub> )                          | Full | IV                      | 14  |     |     | ns   |

| SDIO to SCLK Setup Time (t <sub>DS</sub> )                  | Full | IV                      | 14  |     |     | ns   |

| SCLK to SDIO Hold Time (t <sub>DH</sub> )                   | Full | IV                      | 0   |     |     | ns   |

| SEN to SCLK Setup Time (ts)                                 | Full | IV                      | 14  |     |     | ns   |

| SCLK to $\overline{\text{SEN}}$ Hold Time (t <sub>H</sub> ) | Full | IV                      | 0   |     |     | ns   |

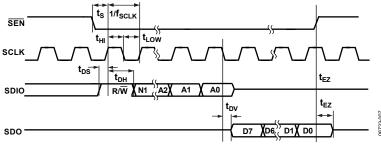

| READ OPERATION (See Figure 6 and Figure 7)                  |      |                         |     |     |     |      |

| SCLK Clock Rate (fsclk)                                     | Full | IV                      |     |     | 32  | MHz  |

| SCLK Clock High (t <sub>HI</sub> )                          | Full | IV                      | 14  |     |     | ns   |

| SCLK Clock Low (t <sub>LOW</sub> )                          | Full | IV                      | 14  |     |     | ns   |

| SDIO to SCLK Setup Time (t <sub>DS</sub> )                  | Full | IV                      | 14  |     |     | ns   |

| SCLK to SDIO Hold Time (t <sub>DH</sub> )                   | Full | IV                      | 0   |     |     | ns   |

| SCLK to SDIO (or SDO) Data Valid Time (t <sub>DV</sub> )    | Full | IV                      |     |     | 14  | ns   |

| SEN to SDIO Output Valid to High-Z (t <sub>EZ</sub> )       | Full | IV                      |     | 2   |     | ns   |

<sup>&</sup>lt;sup>1</sup> See the Explanation of Test Levels section.

### HALF-DUPLEX DATA INTERFACE (ADIO PORT) TIMING SPECIFICATIONS

AVDD = 3.3 V  $\pm$  5%, DVDD = CLKVDD = DRVDD = 3.3 V  $\pm$  10%, unless otherwise noted.

Table 6.

| Parameter                                           | Temp | Test Level <sup>1</sup> | Min | Тур | Max | Unit |

|-----------------------------------------------------|------|-------------------------|-----|-----|-----|------|

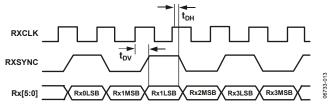

| READ OPERATION <sup>2</sup> (See Figure 9)          |      |                         |     |     |     |      |

| Output Data Rate                                    | Full | II                      | 20  |     | 80  | MSPS |

| Three-State Output Enable Time (tpzl)               | Full | II                      |     |     | 3   | ns   |

| Three-State Output Disable Time (t <sub>PLZ</sub> ) | Full | II                      |     |     | 3   | ns   |

| Rx Data Valid Time (t <sub>VT</sub> )               | Full | II                      | 1.5 |     |     | ns   |

| Rx Data Output Delay (tod)                          | Full | II                      |     |     | 4   | ns   |

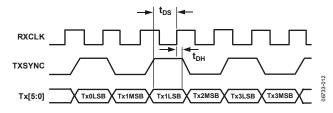

| WRITE OPERATION (See Figure 8)                      |      |                         |     |     |     |      |

| Input Data Rate (2× Interpolation)                  | Full | II                      | 40  |     | 80  | MSPS |

| Input Data Rate (4× Interpolation)                  | Full | II                      | 20  |     | 50  | MSPS |

| Tx Data Setup Time (t <sub>DS</sub> )               | Full | II                      | 1   |     |     | ns   |

| Tx Data Hold Time (t <sub>DH</sub> )                | Full | II                      | 2.5 |     |     | ns   |

| Latch Enable Time (ten)                             | Full | II                      |     |     | 3   | ns   |

| Latch Disable Time (t <sub>DIS</sub> )              | Full | II                      |     |     | 3   | ns   |

<sup>&</sup>lt;sup>1</sup> See the Explanation of Test Levels section.

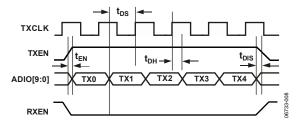

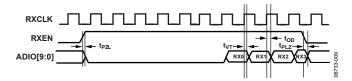

#### **FULL-DUPLEX DATA INTERFACE (Tx AND Rx PORT) TIMING SPECIFICATIONS**

AVDD = 3.3 V  $\pm$  5%, DVDD = CLKVDD = DRVDD = 3.3 V  $\pm$  10%, unless otherwise noted.

Table 7.

| Parameter                                      | Temp | Test Level <sup>1</sup> | Min | Тур | Max | Unit |

|------------------------------------------------|------|-------------------------|-----|-----|-----|------|

| Tx PATH INTERFACE (See Figure 12)              |      |                         |     |     |     |      |

| Input Nibble Rate (2× Interpolation)           | Full | II                      | 80  |     | 160 | MSPS |

| Input Nibble Rate (4× Interpolation)           | Full | II                      | 40  |     | 100 | MSPS |

| Tx Data Setup Time (t <sub>DS</sub> )          | Full | II                      | 2.5 |     |     | ns   |

| Tx Data Hold Time (t <sub>DH</sub> )           | Full | II                      | 1.5 |     |     | ns   |

| Rx PATH INTERFACE <sup>2</sup> (See Figure 13) |      |                         |     |     |     |      |

| Output Nibble Rate                             | Full | II                      | 40  |     | 160 | MSPS |

| Rx Data Valid Time (t <sub>DV</sub> )          | Full | II                      | 3   |     |     | ns   |

| Rx Data Hold Time (t <sub>DH</sub> )           | Full | II                      | 0   |     |     | ns   |

$<sup>^{\</sup>mbox{\tiny 1}}$  See the Explanation of Test Levels section.

$<sup>^{2}</sup>$  C<sub>LOAD</sub> = 5 pF for digital data outputs.

$<sup>^{2}</sup>$  C<sub>LOAD</sub> = 5 pF for digital data outputs.

## **ABSOLUTE MAXIMUM RATINGS**

Table 8.

| Parameter                             | Rating                  |

|---------------------------------------|-------------------------|

| ELECTRICAL                            |                         |

| AVDD, CLKVDD Voltage                  | 3.9 V maximum           |

| DVDD, DRVDD Voltage                   | 3.9 V maximum           |

| RX+, RX-, REFT, REFB                  | -0.3 V to AVDD + 0.3 V  |

| IOUTP+, IOUTP-                        | -1.5 V to AVDD + 0.3 V  |

| IOUTN+, IOUTN-                        | -0.3 V to +3.9 V        |

| OSCIN, XTAL                           | -0.3 V to CLVDD + 0.3 V |

| REFIO, REFADJ                         | -0.3 V to AVDD + 0.3 V  |

| Digital Input and Output Voltage      | -0.3 V to DRVDD + 0.3 V |

| Digital Output Current                | 5 mA maximum            |

| ENVIRONMENTAL                         |                         |

| Operating Temperature Range (Ambient) | −40°C to +85°C          |

| Maximum Junction Temperature          | 125°C                   |

| Lead Temperature (Soldering, 10 sec)  | 150°C                   |

| Storage Temperature Range (Ambient)   | −65°C to +150°C         |

Stresses above those listed under Absolute Maximum Ratings may cause permanent damage to the device. This is a stress rating only; functional operation of the device at these or any other conditions above those indicated in the operational section of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

#### THERMAL CHARACTERISTICS

Thermal Resistance: 64-lead LFCSP (4-layer board).

$\theta_{JA} = 24$ °C/W (paddle soldered to ground plane, 0 LPM air).

$\theta_{JA} = 30.8$ °C/W (paddle not soldered to ground plane, 0 LPM air).

#### **EXPLANATION OF TEST LEVELS**

- I. 100% production tested.

- II. 100% production tested at 25°C and guaranteed by design and characterization at specified temperatures.

- III. Sample tested only.

- IV. Parameter is guaranteed by design and characterization testing.

- V. Parameter is a typical value only.

- VI. 100% production tested at 25°C and guaranteed by design and characterization for industrial temperature range.

#### **ESD CAUTION**

**ESD** (electrostatic discharge) sensitive device. Charged devices and circuit boards can discharge without detection. Although this product features patented or proprietary protection circuitry, damage may occur on devices subjected to high energy ESD. Therefore, proper ESD precautions should be taken to avoid performance degradation or loss of functionality.

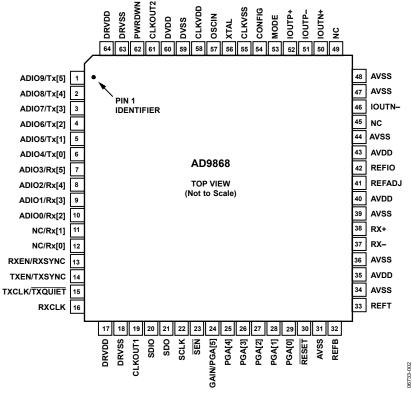

## PIN CONFIGURATION AND FUNCTION DESCRIPTIONS

Figure 2. Pin Configuration

**Table 9. Pin Function Descriptions**

| Pin No. | Mnemonic       | Mode <sup>1</sup> | Description                                      |

|---------|----------------|-------------------|--------------------------------------------------|

| 1       | ADIO9          | HD                | MSB of ADIO Buffer.                              |

|         | Tx[5]          | FD                | MSB of Tx Nibble Input.                          |

| 2 to 5  | ADIO8 to ADIO5 | HD                | Bit 8 to Bit 5 of ADIO Buffer.                   |

|         | Tx[4:1]        | FD                | Bit 4 to Bit 1 of Tx Nibble Input.               |

| 6       | ADIO4          | HD                | Bit 4 of ADIO Buffer.                            |

|         | Tx[0]          | FD                | LSB of Tx Nibble Input.                          |

| 7       | ADIO3          | HD                | Bit 3 of ADIO Buffer.                            |

|         | Rx[5]          | FD                | MSB of Rx Nibble Output.                         |

| 8, 9    | ADIO2, ADIO1   | HD                | Bit 2 to Bit 1 of ADIO Buffer.                   |

|         | Rx[4:3]        | FD                | Bit 4 to Bit 3 of Rx Nibble Output.              |

| 10      | ADIO0          | HD                | LSB of ADIO Buffer.                              |

|         | Rx[2]          | FD                | Bit 2 of Rx Nibble Output.                       |

| 11      | NC             | HD                | No Connect.                                      |

|         | Rx[1]          | FD                | Bit 1 of Rx Nibble Output.                       |

| 12      | NC             | HD                | No Connect.                                      |

|         | Rx[0]          | FD                | LSB of Rx Nibble Output.                         |

| 13      | RXEN           | HD                | ADIO Buffer Control Input.                       |

|         | RXSYNC         | FD                | Rx Data Synchronization Output.                  |

| 14      | TXEN           | HD                | Tx Path Enable Input.                            |

|         | TXSYNC         | FD                | Tx Data Synchronization Input.                   |

| 15      | TXCLK          | HD                | ADIO Sample Clock Input.                         |

|         | TXQUIET        | FD                | Fast TxDAC/IAMP Power-Down.                      |

| 16      | RXCLK          | HD                | ADIO Request Clock Input.                        |

|         |                | FD                | Rx and Tx Clock Output at 2 x f <sub>ADC</sub> . |

Rev. 0 | Page 10 of 36

| Pin No.                    | Mnemonic   | Mode <sup>1</sup> | Description                                               |

|----------------------------|------------|-------------------|-----------------------------------------------------------|

| 17, 64                     | DRVDD      |                   | Digital Output Driver Supply Input.                       |

| 18, 63                     | DRVSS      |                   | Digital Output Driver Supply Return.                      |

| 19                         | CLKOUT1    |                   | $f_{ADC}/N$ Clock Output (R = 1, 2, or 3).                |

| 20                         | SDIO       |                   | Serial Port Data Input/Output.                            |

| 21                         | SDO        |                   | Serial Port Data Output.                                  |

| 22                         | SCLK       |                   | Serial Port Clock Input.                                  |

| 23                         | SEN        |                   | Serial Port Enable Input.                                 |

| 24                         | GAIN       | FD                | Tx Data Port (Tx[5:0]) Mode Select.                       |

|                            | PGA[5]     | HD or FD          | MSB of PGA Input Data Port.                               |

| 25 to 29                   | PGA[4:0]   | HD or FD          | Bit 4 to Bit 0 of PGA Input Data Port.                    |

| 30                         | RESET      |                   | Reset Input (Active Low).                                 |

| 31, 34, 36, 39, 44, 47, 48 | AVSS       |                   | Analog Supply Return.                                     |

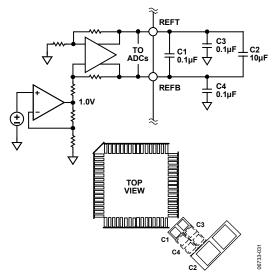

| 32, 33                     | REFB, REFT |                   | ADC Reference Decoupling Nodes.                           |

| 35, 40, 43                 | AVDD       |                   | Analog Power Supply Input.                                |

| 37, 38                     | RX-, RX+   |                   | Receive Path – and + Analog Inputs.                       |

| 41                         | REFADJ     |                   | TxDAC Full-Scale Current Adjust.                          |

| 42                         | REFIO      |                   | TxDAC Reference Input/Output.                             |

| 45, 49                     | NC         |                   | Do Not Connect; Leave Open.                               |

| 46                         | IOUTN-     |                   | –Tx Mirror Current Output Sink.                           |

| 50                         | IOUTN+     |                   | +Tx Mirror Current Output Sink.                           |

| 51                         | IOUTP-     |                   | -TxDAC Current Output Source.                             |

| 52                         | IOUTP+     |                   | +TxDAC Current Output Source.                             |

| 53                         | MODE       |                   | Digital Interface Mode Select Input, Low = HD, High = FD. |

| 54                         | CONFIG     |                   | Power-Up SPI Register Default Setting Input.              |

| 55                         | CLKVSS     |                   | Clock Oscillator/Synthesizer Supply Return.               |

| 56                         | XTAL       |                   | Crystal Oscillator Inverter Output.                       |

| 57                         | OSCIN      |                   | Crystal Oscillator Inverter Input.                        |

| 58                         | CLKVDD     |                   | Clock Oscillator/Synthesizer Supply.                      |

| 59                         | DVSS       |                   | Digital Supply Return.                                    |

| 60                         | DVDD       |                   | Digital Supply Input.                                     |

| 61                         | CLKOUT2    |                   | $f_{OSCIN}/L$ Clock Output (L = 1, 2, or 4).              |

| 62                         | PWRDWN     |                   | Power-Down Input.                                         |

$<sup>^{1}</sup>$  HD = half-duplex mode; FD = full-duplex mode.

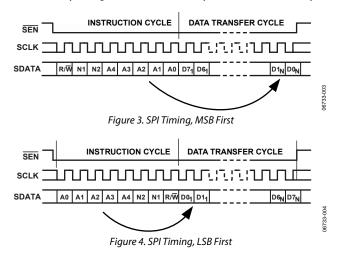

# **SERIAL PORT**

**Table 10. SPI Register Mapping**

|                          |          | ļ                                    |          | Pow        | er-Up Default    | : Value                   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|--------------------------|----------|--------------------------------------|----------|------------|------------------|---------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Address                  |          |                                      |          |            | E = 0<br>Ouplex) | MODE = 1<br>(Full-Duplex) |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| (Hex) Bit <sup>1</sup> D |          | Description                          | Width    | CONFIG = 0 | CONFIG = 1       | CONFIG = 0                | Comments                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| SPI PORT                 | CONFIGL  | JRATION AND SOFTWA                   | RE RESET |            |                  |                           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| 0x00                     | 7        | 4-Wire SPI                           | 1        | 0          | 0                | 0                         | Default SPI configuration is 3-wire,                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|                          | 6        | SPI LSB First                        | 1        | 0          | 0                | 0                         | MSB first.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|                          | 5        | Software Reset                       | 1        | 0          | 0                | 0                         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| POWER CO                 | ONTROL   | REGISTERS (Via PWRD)                 | WN Pin)  |            |                  |                           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| 0x01                     | 7        | CLK Synthesizer                      | 1        | 0          | 0                | 0                         | PWRDWN = 0.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|                          | 6        | TxDAC/IAMP                           | 1        | 0          | 0                | 0                         | Default setting is for all blocks powered or                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |