#### **Features**

- Core

- ARM® Cortex®-M3 revision 2.0 running at up to 48 MHz

- Thumb<sup>®</sup>-2 instruction

- 24-bit SysTick Counter

- Nested Vector Interrupt Controller

- Pin-to-pin compatible with SAM7S legacy products (48- and 64-pin versions) and SAM3S (48-, 64- and 100-pin versions)

- Memories

- From 64 to 256 Kbytes embedded Flash, 128-bit wide access, memory accelerator, single plane

- From 8 to 24 Kbytes embedded SRAM

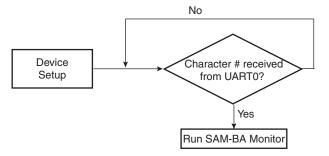

- 16 Kbytes ROM with embedded bootloader routines (UART) and IAP routines

- System

- Embedded voltage regulator for single supply operation

- Power-on-Reset (POR), Brown-out Detector (BOD) and Watchdog for safe operation

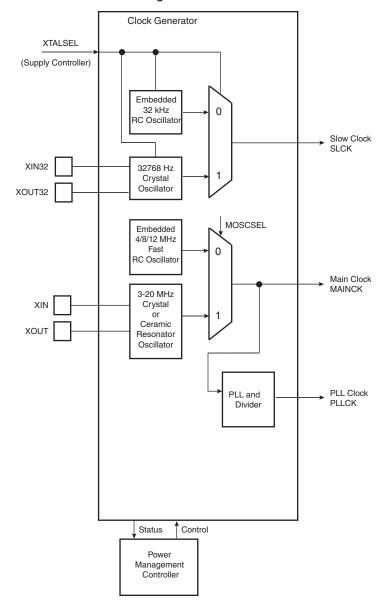

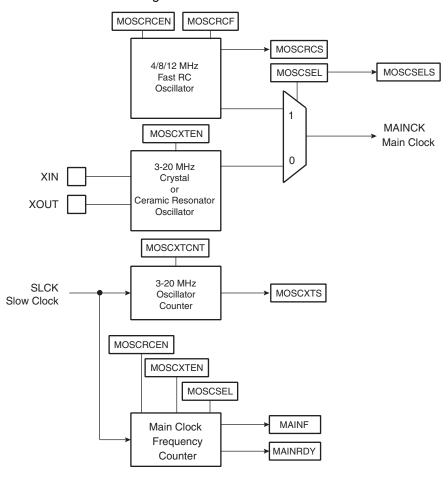

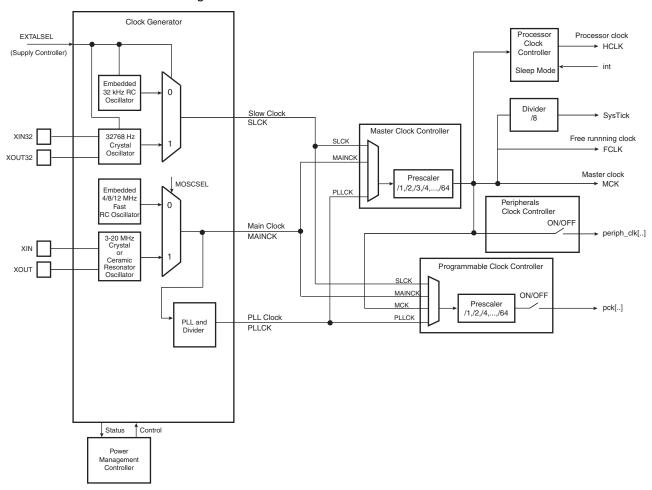

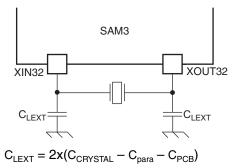

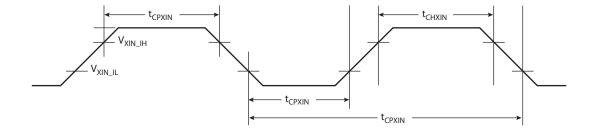

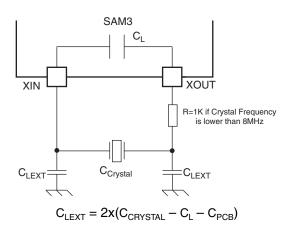

- Quartz or ceramic resonator oscillators: 3 to 20 MHz main power with Failure

Detection and optional low power 32.768 kHz for RTC or device clock

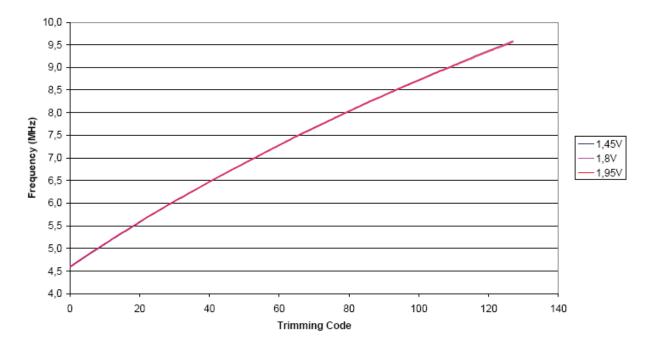

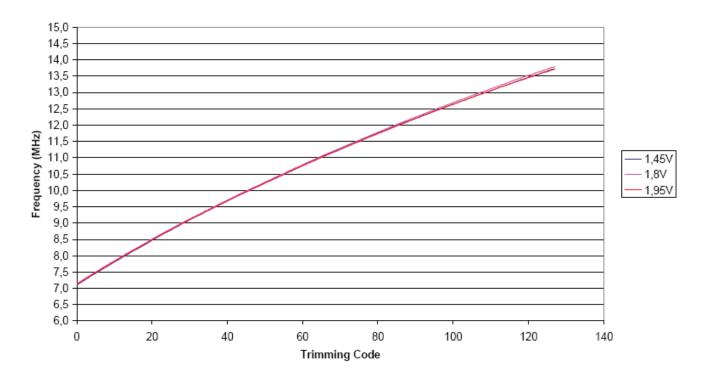

- High precision 8/12 MHz factory trimmed internal RC oscillator with 4 MHz default frequency for device startup. In-application trimming access for frequency adjustment

- Slow Clock Internal RC oscillator as permanent low-power mode device clock

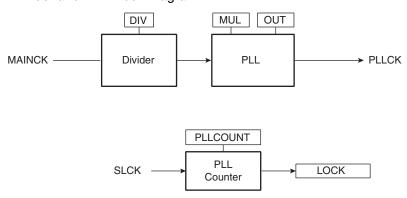

- One PLL up to 130 MHz for device clock

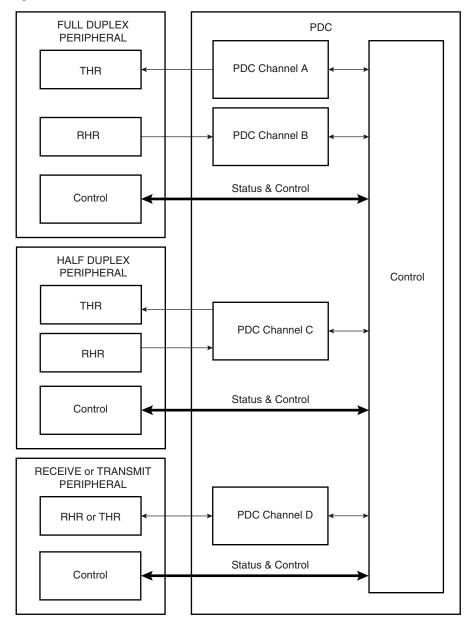

- Up to 10 peripheral DMA (PDC) channels

- Low Power Modes

- Sleep and Backup modes, down to 3 µA in Backup mode

- Ultra low power RTC

- Peripherals

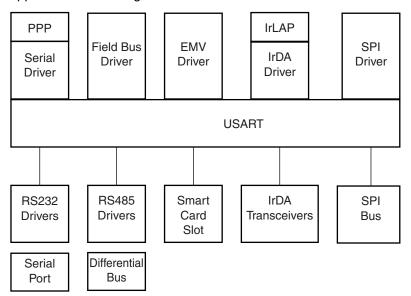

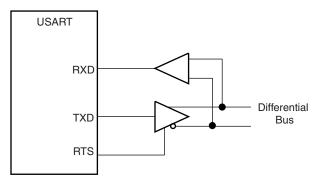

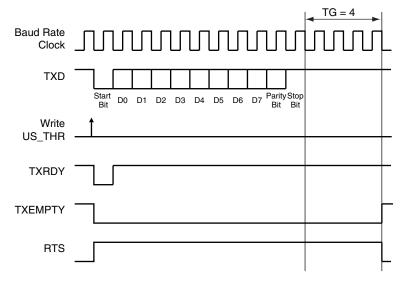

- Up to 2 USARTs with ISO7816, IrDA®, RS-485 and SPI mode

- Two 2-wire UARTs

- 2 Two Wire Interface (I2C compatible), 1 SPI

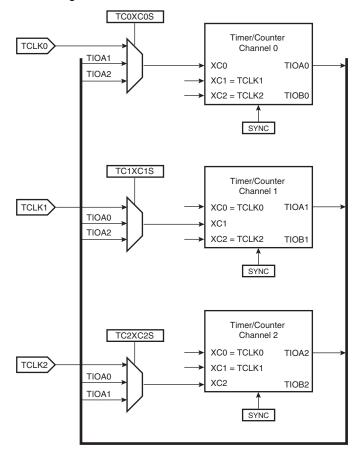

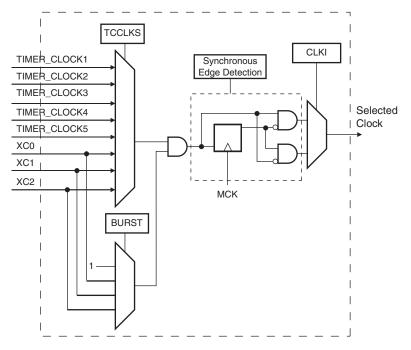

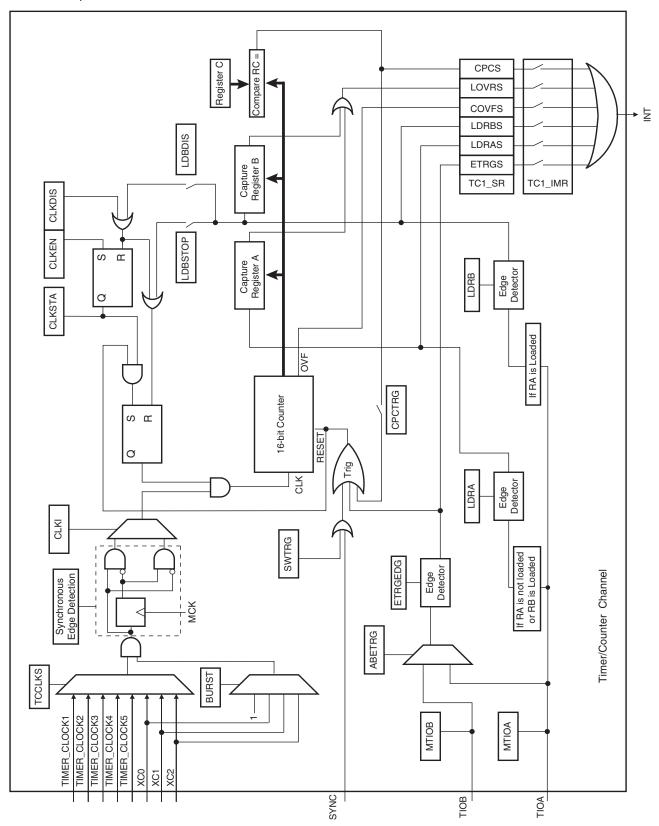

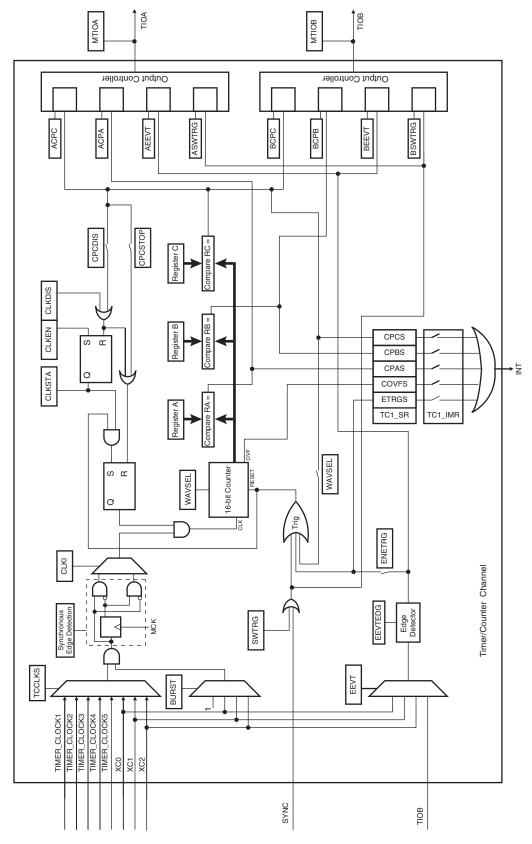

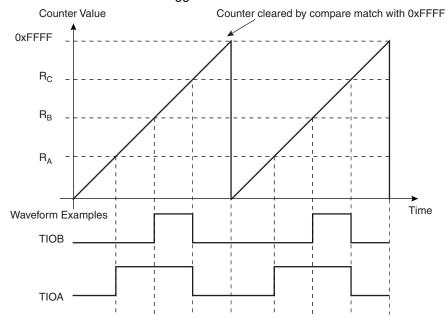

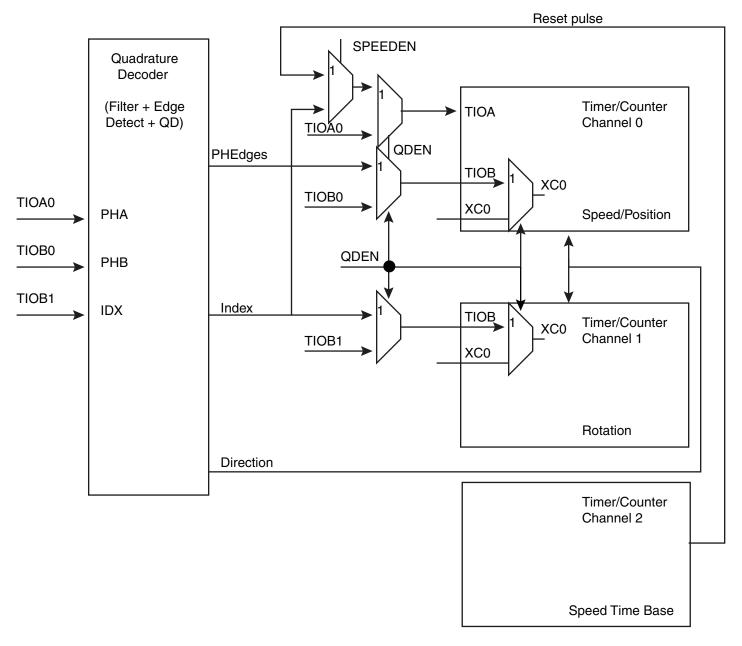

- Up to 6 Three-Channel 16-bit Timer/Counter with capture, waveform, compare and PWM mode. Quadrature Decoder Logic and 2-bit Gray Up/Down Counter for Stepper Motor

- 4-channel 16-bit PWM

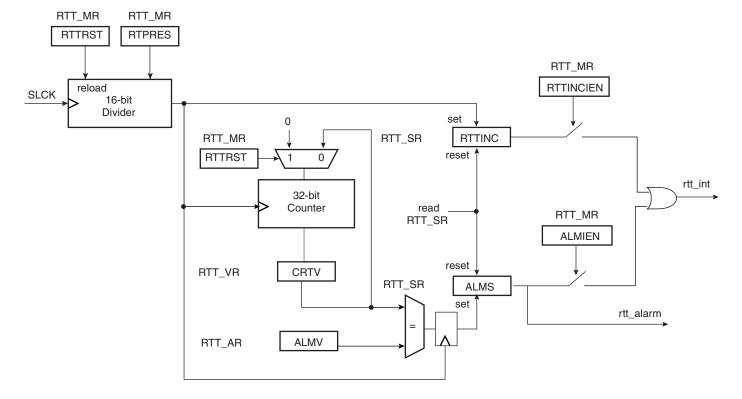

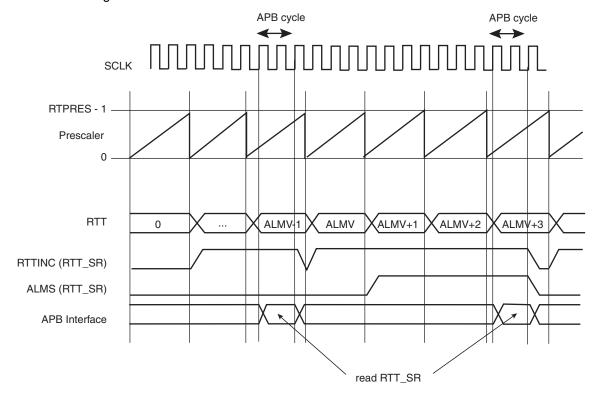

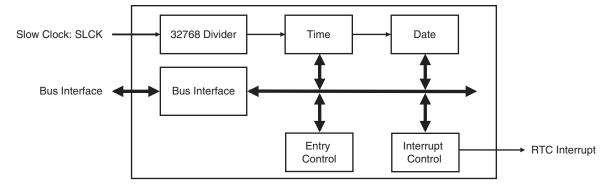

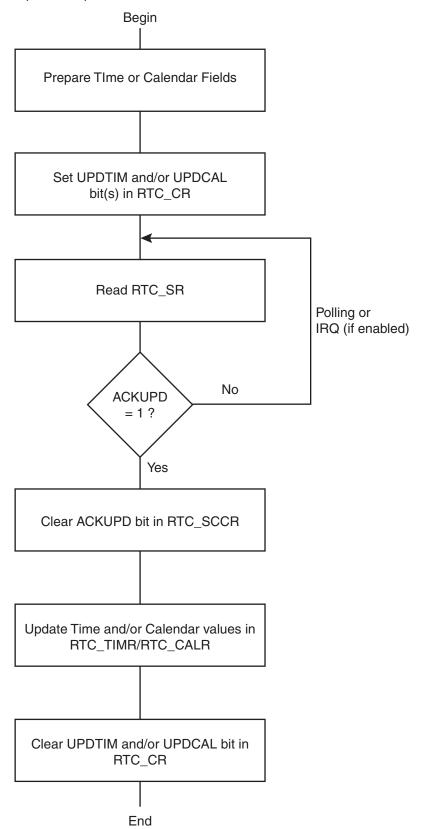

- 32-bit Real-time Timer and RTC with calendar and alarm features

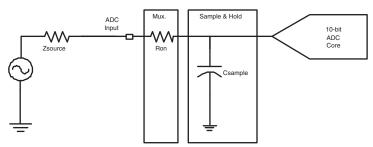

- Up to 16 channels, 384 KSPS 10-bit ADC

- One 500 KSPS 10-bit DAC

- I/O

- Up to 79 I/O lines with external interrupt capability (edge or level sensitivity), debouncing, glitch filtering and on-die Series Resistor Termination

- Three 32-bit Parallel Input/Output Controllers

- Packages

- 100-lead LQFP, 14 x 14 mm, pitch 0.5 mm / 100-ball LFBGA, 9 x 9 mm, pitch 0.8 mm

- 64-lead LQFP, 12 x 12 mm, pitch 0.5 mm / 64-pad QFN 9x9 mm, pitch 0.45 mm

- 48-lead LQFP, 9 x 9 mm, pitch 0.5 mm / 48-pad QFN 7x7 mm, pitch 0.45 mm

# AT91SAM ARM-based Flash MCU

### **ATSAM3N Series**

### 1. SAM3N Description

Atmel's SAM3N series is a member of a family of Flash microcontrollers based on the high performance 32-bit ARM Cortex-M3 RISC processor. It operates at a maximum speed of 48 MHz and features up to 256 Kbytes of Flash and up to 24 Kbytes of SRAM. The peripheral set includes 2x USARTs, 2x UARTs, 2x TWIs, 3x SPI, as well as 1 PWM timer, 6x general purpose 16-bit timers, an RTC, a 10-bit ADC and a 10-bit DAC.

The SAM3N series is ready for capacitive touch thanks to the QTouch library, offering an easy way to implement buttons, wheels and sliders.

The SAM3N device is an entry-level general purpose microcontroller. That makes the SAM3N the ideal starting point to move from 8-/16-bit to 32-bit microcontrollers.

It operates from 1.62V to 3.6V and is available in 48-pin, 64-pin and 100-pin QFP, 48-pin and 64-pin QFN, and 100-pin BGA packages.

The SAM3N series is the ideal migration path from the SAM3S for applications that require a reduced BOM cost. The SAM3N series is pin-to-pin compatible with the SAM3S series. Its aggressive price point and high level of integration pushes its scope of use far into cost-sensitive, high-volume applications.

#### 1.1 Configuration Summary

The SAM3N4/2/1 differ in memory size, package and features list. Table 1-1 summarizes the configurations of the 9 devices.

**Table 1-1.** Configuration Summary

| Device  | Flash      | SRAM      | Package           | Number of PIOs | ADC         | Timer             | PDC<br>Channels | USART | DAC |

|---------|------------|-----------|-------------------|----------------|-------------|-------------------|-----------------|-------|-----|

| SAM3N4A | 256 Kbytes | 24 Kbytes | LQFP48<br>QFN48   | 34             | 8 channels  | 6 <sup>(1)</sup>  | 8               | 1     | _   |

| SAM3N4B | 256 Kbytes | 24 Kbytes | LQFP64<br>QFN64   | 47             | 10 channels | 6 <sup>(2)</sup>  | 10              | 2     | 1   |

| SAM3N4C | 256 Kbytes | 24 Kbytes | LQFP100<br>BGA100 | 79             | 16 channels | 6                 | 10              | 2     | 1   |

| SAM3N2A | 128 Kbytes | 16 Kbytes | LQFP48<br>QFN48   | 34             | 8 channels  | 6 <sup>(1)</sup>  | 8               | 1     | _   |

| SAM3N2B | 128 Kbytes | 16 Kbytes | LQFP64<br>QFN64   | 47             | 10 channels | 6( <sup>(2)</sup> | 10              | 2     | 1   |

| SAM3N2C | 128 Kbytes | 16 Kbytes | LQFP100<br>BGA100 | 79             | 16 channels | 6                 | 10              | 2     | 1   |

| SAM3N1A | 64 Kbytes  | 8 Kbytes  | LQFP48<br>QFN48   | 34             | 8 channels  | 6 <sup>(1)</sup>  | 8               | 1     | _   |

| SAM3N1B | 64 Kbytes  | 8 Kbytes  | LQFP64<br>QFN64   | 47             | 10 channels | 6 <sup>(2)</sup>  | 10              | 2     | 1   |

| SAM3N1C | 64 Kbytes  | 8 Kbytes  | LQFP100<br>BGA100 | 79             | 16 channels | 6                 | 10              | 2     | 1   |

Notes: 1. Only two TC channels are accessible through the PIO.

2. Only three TC channels are accessible through the PIO.

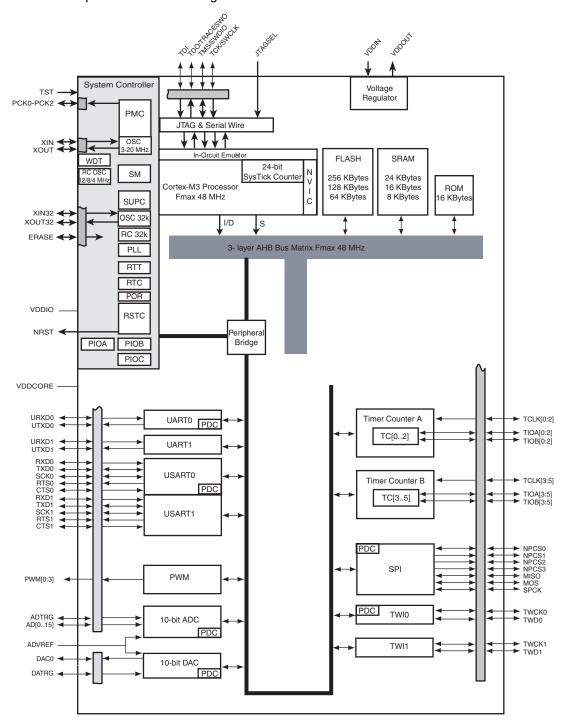

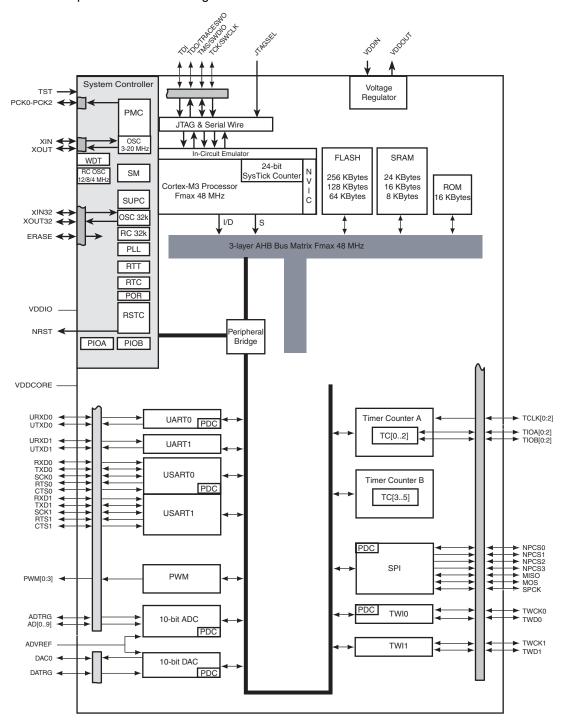

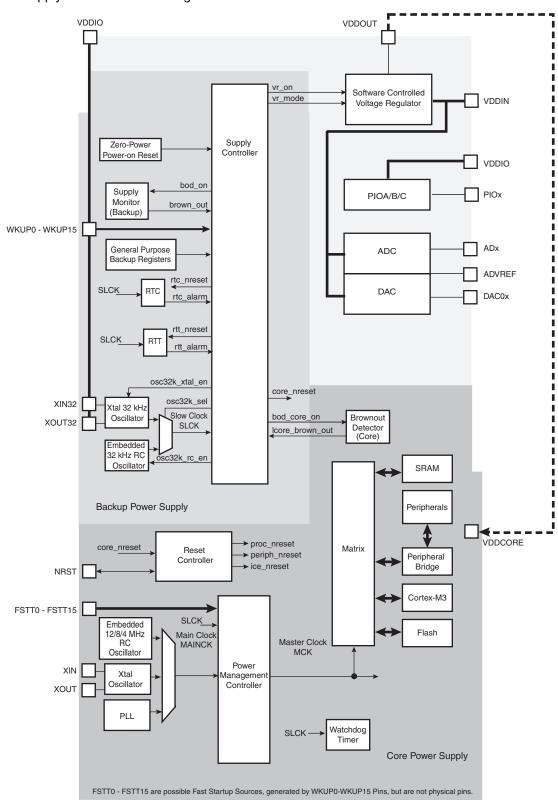

### 2. SAM3N Block Diagram

Figure 2-1. SAM3N 100-pin version Block Diagram

Figure 2-2. SAM3N 64-pin version Block Diagram

System Controller Voltage TST Regulator PCK0-PCK2 PMC JTAG & Serial Wire OSC 3-20 MHz XIN In-Circuit Emulato FLASH SRAM WDT 24-bit SM SysTick Cour 256 KBytes 24 KBytes Cortex-M3 Processor Fmax 48 MHz 128 KBytes 16 KBytes ROM 64 KBytes 8 KBytes 16 KByte SUPC XIN32 ← OSC 32k XOUT32 I/D s RC 32k 3-layer AHB Bus Matrix Fmax 48 MHz PLL RTT RTC VDDIO RSTC NRST < eripheral PIOA PIOB Bridge VDDCORE URXD0 UART0 PDC Timer Counter A ► TCLK[0:2] UTXD0 ► TIOA[0:2] ► TIOB[0:2] TC[0..2] URXD1 UTXD1 UART1 Timer Counter B USART0 TC[3..5] PDC SPI PWM PWM[0:3] PDC ADTRG AD[0..7] TWCK0 TWI0 10-bit ADC PDC TWCK1 TWI1

Figure 2-3. SAM3N 48-pin version Block Diagram

# 3. Signal Description

Table 3-1 gives details on the signal name classified by peripheral.

Table 3-1.

Signal Description List

| Signal Name  | Function                                                  | Туре          | Active<br>Level | Voltage<br>Reference | Comments                                                                                     |

|--------------|-----------------------------------------------------------|---------------|-----------------|----------------------|----------------------------------------------------------------------------------------------|

|              | Power S                                                   | upplies       |                 |                      |                                                                                              |

| VDDIO        | Peripherals I/O Lines Power Supply                        | Power         |                 |                      | 1.62V to 3.6V                                                                                |

| VDDIN        | Voltage Regulator, ADC and DAC Power Supply               | Power         |                 |                      | 1.8V to 3.6V <sup>(3)</sup>                                                                  |

| VDDOUT       | Voltage Regulator Output                                  | Power         |                 |                      | 1.8V Output                                                                                  |

| VDDPLL       | Oscillator and PLL Power Supply                           | Power         |                 |                      | 1.65 V to 1.95V                                                                              |

| VDDCORE      | Power the core, the embedded memories and the peripherals | Power         |                 |                      | 1.65V to 1.95V<br>Connected externally<br>to VDDOUT                                          |

| GND          | Ground                                                    | Ground        |                 |                      |                                                                                              |

|              | Clocks, Oscilla                                           | tors and PLLs |                 |                      |                                                                                              |

| XIN          | Main Oscillator Input Input                               |               |                 |                      | Reset State:                                                                                 |

| XOUT         | Main Oscillator Output                                    | Output        |                 |                      | - PIO Input<br>- Internal Pull-up<br>disabled<br>- Schmitt Trigger<br>enabled <sup>(1)</sup> |

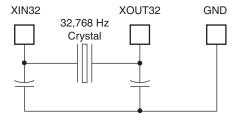

| XIN32        | Slow Clock Oscillator Input                               | Input         |                 | _                    |                                                                                              |

| XOUT32       | Slow Clock Oscillator Output                              | Output        |                 |                      |                                                                                              |

| PCK0 - PCK2  | Programmable Clock Output                                 | Output        |                 | VDDIO                | Reset State: - PIO Input - Internal Pull-up enabled - Schmitt Trigger enabled <sup>(1)</sup> |

|              | ICE and                                                   | JTAG          |                 |                      |                                                                                              |

| TCK/SWCLK    | Test Clock/Serial Wire Clock                              | Input         |                 |                      | Reset State:                                                                                 |

| TDI          | Test Data In                                              | Input         |                 |                      | - SWJ-DP Mode                                                                                |

| TDO/TRACESWO | Test Data Out/Trace Asynchronous Data Out                 | Output        |                 | VDDIO                | - Internal pull-up<br>disabled                                                               |

| TMS/SWDIO    | Test Mode Select /Serial Wire Input/Output                |               |                 |                      | - Schmitt Trigger<br>enabled <sup>(1)</sup>                                                  |

| JTAGSEL      | JTAG Selection                                            | Input         | High            |                      | Permanent Internal pull-down                                                                 |

Table 3-1.

Signal Description List (Continued)

| Signal Name | Function                                          | Туре          | Active<br>Level | Voltage<br>Reference | Comments                                                                                         |

|-------------|---------------------------------------------------|---------------|-----------------|----------------------|--------------------------------------------------------------------------------------------------|

| -           | Flash M                                           | emory         |                 |                      | 1                                                                                                |

| ERASE       | Flash and NVM Configuration Bits Erase<br>Command | Input         | High            | VDDIO                | Reset State: - Erase Input - Internal pull-down enabled - Schmitt Trigger enabled <sup>(1)</sup> |

|             | Reset                                             | /Test         |                 |                      |                                                                                                  |

| NRST        | Microcontroller Reset                             | I/O           | Low             | VDDIO                | Permanent Internal pull-up                                                                       |

| TST         | Test Mode Select                                  | Input         |                 | VDDIO                | Permanent Internal pull-down                                                                     |

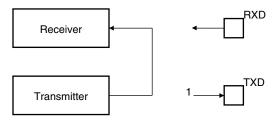

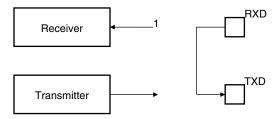

|             | Universal Asynchronous Re                         | ceiver Transc | eiver - UART    | x                    |                                                                                                  |

| URXDx       | UART Receive Data                                 | Input         |                 |                      |                                                                                                  |

| UTXDx       | UART Transmit Data                                | Output        |                 |                      |                                                                                                  |

|             | PIO Controller - PI                               | OA - PIOB - P | OC              |                      |                                                                                                  |

| PA0 - PA31  | Parallel IO Controller A                          | I/O           |                 |                      | Reset State:                                                                                     |

| PB0 - PB14  | Parallel IO Controller B                          | I/O           |                 |                      | - PIO or System<br>IOs <sup>(2)</sup>                                                            |

| PC0 - PC31  | Parallel IO Controller C                          | I/O           |                 | VDDIO                | - Internal pull-up enabled - Schmitt Trigger enabled <sup>(1)</sup>                              |

|             | Universal Synchronous Asynchron                   | ous Receiver  | Transmitter     | USARTx               | 1                                                                                                |

| SCKx        | USARTx Serial Clock                               | I/O           |                 |                      |                                                                                                  |

| TXDx        | USARTx Transmit Data                              | I/O           |                 |                      |                                                                                                  |

| RXDx        | USARTx Receive Data                               | Input         |                 |                      |                                                                                                  |

| RTSx        | USARTx Request To Send                            | Output        |                 |                      |                                                                                                  |

| CTSx        | USARTx Clear To Send                              | Input         |                 |                      |                                                                                                  |

|             | Timer/Cou                                         | nter - TC     | •               | •                    | •                                                                                                |

| TCLKx       | TC Channel x External Clock Input                 | Input         |                 |                      |                                                                                                  |

| TIOAx       | TC Channel x I/O Line A                           | I/O           |                 |                      |                                                                                                  |

| TIOBx       | TC Channel x I/O Line B                           | I/O           |                 |                      |                                                                                                  |

|             | Pulse Width Modulation                            | on Controller | PWMC            |                      |                                                                                                  |

| PWMx        | PWM Waveform Output for channel x                 | Output        |                 |                      |                                                                                                  |

Table 3-1.

Signal Description List (Continued)

| Signal Name              | Function                          | Туре                 | Active<br>Level | Voltage<br>Reference | Comments |  |

|--------------------------|-----------------------------------|----------------------|-----------------|----------------------|----------|--|

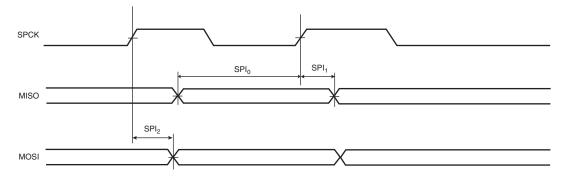

|                          | Serial Peripheral Interface - SPI |                      |                 |                      |          |  |

| MISO                     | Master In Slave Out               | I/O                  |                 |                      |          |  |

| MOSI                     | Master Out Slave In               | I/O                  |                 |                      |          |  |

| SPCK                     | SPI Serial Clock                  | I/O                  |                 |                      |          |  |

| SPI_NPCS0                | SPI Peripheral Chip Select 0      | I/O                  | Low             |                      |          |  |

| SPI_NPCS1 -<br>SPI_NPCS3 | SPI Peripheral Chip Select        | Output               | Low             |                      |          |  |

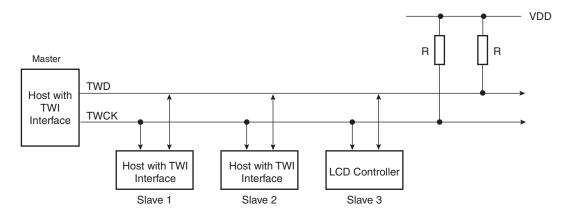

|                          | Two-Wire                          | Interface- TWIx      |                 |                      |          |  |

| TWDx                     | TWIx Two-wire Serial Data         | I/O                  |                 |                      |          |  |

| TWCKx                    | TWIx Two-wire Serial Clock        | I/O                  |                 |                      |          |  |

|                          |                                   | Analog               |                 |                      |          |  |

| ADVREF                   | ADC and DAC Reference             | Analog               |                 |                      |          |  |

|                          | 10-bit Analog-to-                 | -Digital Converter - | ADC             |                      |          |  |

| AD0 - AD15               | Analog Inputs                     | Analog               |                 |                      |          |  |

| ADTRG                    | ADC Trigger                       | Input                |                 | VDDIO                |          |  |

|                          | Digital-to-Analog C               | onverter Controlle   | r- DACC         |                      |          |  |

| DAC0                     | DACC channel analog output        | Analog               |                 |                      |          |  |

| DATRG                    | DACC Trigger                      | Input                |                 | VDDIO                |          |  |

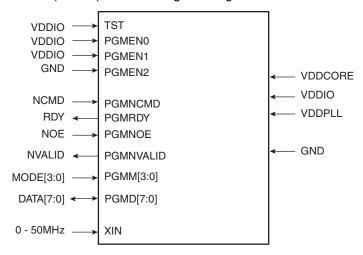

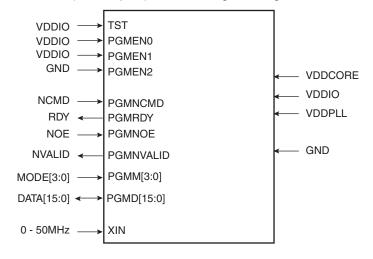

|                          | Fast Flash Pr                     | ogramming Interfa    | се              |                      |          |  |

| PGMEN0-PGMEN2            | Programming Enabling              | Input                |                 |                      |          |  |

| PGMM0-PGMM3              | Programming Mode                  | Input                |                 |                      |          |  |

| PGMD0-PGMD15             | Programming Data                  | I/O                  |                 |                      |          |  |

| PGMRDY                   | Programming Ready                 | Output               | High            | VDDIO                |          |  |

| PGMNVALID                | Data Direction                    | Output               | Low             | VIDIO                |          |  |

| PGMNOE                   | Programming Read                  | Input                | Low             |                      |          |  |

| PGMCK                    | Programming Clock                 | Input                |                 |                      |          |  |

| PGMNCMD                  | Programming Command               | Input                | Low             |                      |          |  |

Notes: 1. Schmitt Triggers can be disabled through PIO registers.

- 2. Some PIO lines are shared with System IOs.

- 3. See Section 5.3 "Typical Powering Schematics" for restriction on voltage range of Analog Cells.

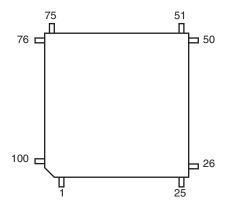

### 4. Package and Pinout

SAM3N4/2/1 series is pin-to-pin compatible with SAM3S products. Furthermore SAM3N4/2/1 devices have new functionalities referenced in italic inTable 4-1, Table 4-3 and Table 4-4.

#### 4.1 SAM3N4/2/1C Package and Pinout

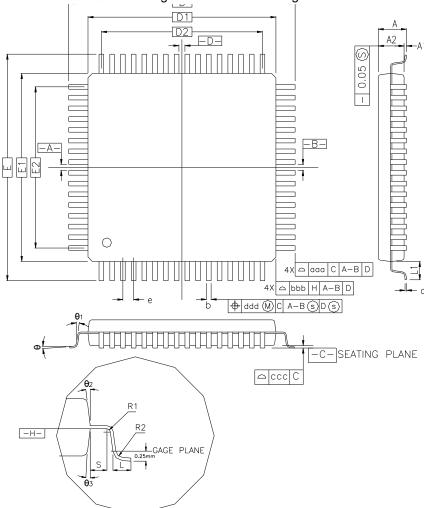

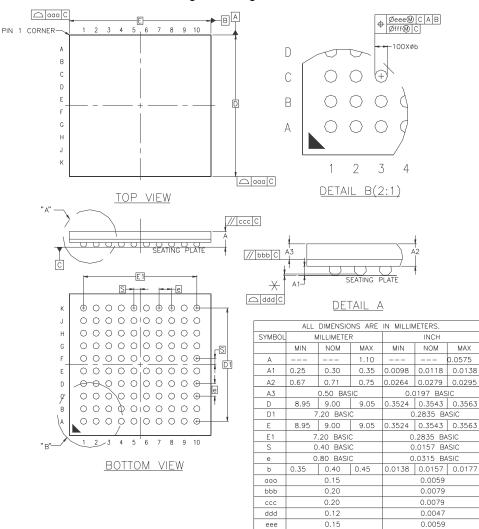

#### 4.1.1 100-lead LQFP Package Outline

Figure 4-1. Orientation of the 100-lead LQFP Package

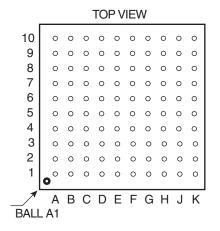

#### 4.1.2 100-ball LFBGA Package Outline

The 100-Ball LFBGA package has a 0.8 mm ball pitch and respects Green Standards. Its dimensions are 9 x 9 x 1.1 mm.

Figure 4-2. Orientation of the 100-ball LFBGA Package

#### 4.1.3 100-Lead LQFP Pinout

Table 4-1. 100-lead LQFP SAM3N4/2/1C Pinout

| 1  | ADVREF         |

|----|----------------|

| 2  | GND            |

| 3  | PB0/AD4        |

| 4  | PC29/AD13      |

| 5  | PB1/AD5        |

| 6  | PC30/AD14      |

| 7  | PB2/AD6        |

| 8  | PC31/AD15      |

| 9  | PB3/AD7        |

| 10 | VDDIN          |

| 11 | VDDOUT         |

| 12 | PA17/PGMD5/AD0 |

| 13 | PC26           |

| 14 | PA18/PGMD6/AD1 |

| 15 | PA21/AD8       |

| 16 | VDDCORE        |

| 17 | PC27           |

| 18 | PA19/PGMD7/AD2 |

| 19 | PC15/AD11      |

| 20 | PA22/AD9       |

| 21 | PC13/AD10      |

| 22 | PA23           |

| 23 | PC12/AD12      |

| 24 | PA20/AD3       |

| 25 | PC0            |

|    |                |

| 26 | GND                     |

|----|-------------------------|

| 27 | VDDIO                   |

| 28 | PA16/PGMD4              |

| 29 | PC7                     |

| 30 | PA15/PGMD3              |

| 31 | PA14/PGMD2              |

| 32 | PC6                     |

| 33 | PA13/PGMD1              |

| 34 | PA24                    |

| 35 | PC5                     |

| 36 | VDDCORE                 |

| 37 | PC4                     |

| 38 | PA25                    |

| 39 | PA26                    |

| 40 | PC3                     |

| 41 | PA12/PGMD0              |

| 42 | PA11/PGMM3              |

| 43 | PC2                     |

| 44 | PA10/PGMM2              |

| 45 | GND                     |

| 46 | PA9/PGMM1               |

| 47 | PC1                     |

| 48 | PA8/XOUT32/<br>PGMM0    |

| 49 | PA7/XIN32/<br>PGMNVALID |

| 50 | VDDIO                   |

|    |                         |

| 51 | TDI/PB4     |

|----|-------------|

| 52 | PA6/PGMNOE  |

| 53 | PA5/PGMRDY  |

| 54 | PC28        |

| 55 | PA4/PGMNCMD |

| 56 | VDDCORE     |

| 57 | PA27        |

| 58 | PC8         |

| 59 | PA28        |

| 60 | NRST        |

| 61 | TST         |

| 62 | PC9         |

| 63 | PA29        |

| 64 | PA30        |

| 65 | PC10        |

| 66 | PA3         |

| 67 | PA2/PGMEN2  |

| 68 | PC11        |

| 69 | VDDIO       |

| 70 | GND         |

| 71 | PC14        |

| 72 | PA1/PGMEN1  |

| 73 | PC16        |

| 74 | PA0/PGMEN0  |

| 75 | PC17        |

| 76  | TDO/TRACESWO/PB5 |

|-----|------------------|

| 77  | JTAGSEL          |

| 78  | PC18             |

| 79  | TMS/SWDIO/PB6    |

| 80  | PC19             |

| 81  | PA31             |

| 82  | PC20             |

| 83  | TCK/SWCLK/PB7    |

| 84  | PC21             |

| 85  | VDDCORE          |

| 86  | PC22             |

| 87  | ERASE/PB12       |

| 88  | PB10             |

| 89  | PB11             |

| 90  | PC23             |

| 91  | VDDIO            |

| 92  | PC24             |

| 93  | PB13/DAC0        |

| 94  | PC25             |

| 95  | GND              |

| 96  | PB8/XOUT         |

| 97  | PB9/PGMCK/XIN    |

| 98  | VDDIO            |

| 99  | PB14             |

| 100 | VDDPLL           |

#### 4.1.4 100-ball LFBGA Pinout

Table 4-2.100-ball LFBGA SAM3N4/2/1C Pinout

| A1         | PB1/AD5              |

|------------|----------------------|

| A2         | PC29                 |

| A3         | VDDIO                |

| A4         | PB9/PGMCK/XIN        |

| <b>A</b> 5 | PB8/XOUT             |

| A6         | PB13/DAC0            |

| A7         | DDP/PB11             |

| A8         | DDM/PB10             |

| A9         | TMS/SWDIO/PB6        |

| A10        | JTAGSEL              |

| B1         | PC30                 |

| B2         | ADVREF               |

| В3         | GNDANA               |

| B4         | PB14/DAC1            |

| B5         | PC21                 |

| В6         | PC20                 |

| B7         | PA31                 |

| B8         | PC19                 |

| B9         | PC18                 |

| B10        | TDO/TRACESWO/<br>PB5 |

| C1         | PB2/AD6              |

| C2         | VDDPLL               |

| C3         | PC25                 |

| C4         | PC23                 |

| C5         | ERASE/PB12           |

| C6  | TCK/SWCLK/PB7      |  |

|-----|--------------------|--|

| C7  | PC16               |  |

| C8  | PA1/PGMEN1         |  |

| C9  | PC17               |  |

| C10 | PA0/PGMEN0         |  |

| D1  | PB3/AD7            |  |

| D2  | PB0/AD4            |  |

| D3  | PC24               |  |

| D4  | PC22               |  |

| D5  | GND                |  |

| D6  | GND                |  |

| D7  | VDDCORE            |  |

| D8  | PA2/PGMEN2         |  |

| D9  | PC11               |  |

| D10 | PC14               |  |

| E1  | PA17/PGMD5/<br>AD0 |  |

| E2  | PC31               |  |

| E3  | VDDIN              |  |

| E4  | GND                |  |

| E5  | GND                |  |

| E6  | NRST               |  |

| E7  | PA29/AD13          |  |

| E8  | PA30/AD14          |  |

| E9  | PC10               |  |

| E10 | PA3                |  |

| F1  | PA18/PGMD6/<br>AD1 |

|-----|--------------------|

|     |                    |

| F2  | PC26               |

| F3  | VDDOUT             |

| F4  | GND                |

| F5  | VDDIO              |

| F6  | PA27               |

| F7  | PC8                |

| F8  | PA28               |

| F9  | TST                |

| F10 | PC9                |

| G1  | PA21/AD8           |

| G2  | PC27               |

| G3  | PA15/PGMD3         |

| G4  | VDDCORE            |

| G5  | VDDCORE            |

| G6  | PA26               |

| G7  | PA12/PGMD0         |

| G8  | PC28               |

| G9  | PA4/PGMNCMD        |

| G10 | PA5/PGMRDY         |

| H1  | PA19/PGMD7/<br>AD2 |

| H2  | PA23               |

| НЗ  | PC7                |

| H4  | PA14/PGMD2         |

| H5  | PA13/PGMD1         |

| H6  | PC4         |

|-----|-------------|

| H7  | PA11/PGMM3  |

| Н8  | PC1         |

| H9  | PA6/PGMNOE  |

| H10 | TDI/PB4     |

| J1  | PC15/AD11   |

| J2  | PC0         |

| J3  | PA16/PGMD4  |

| J4  | PC6         |

| J5  | PA24        |

| J6  | PA25        |

| J7  | PA10/PGMM2  |

| J8  | GND         |

| J9  | VDDCORE     |

| J10 | VDDIO       |

| K1  | PA22/AD9    |

| K2  | PC13/AD10   |

| КЗ  | PC12/AD12   |

| K4  | PA20/AD3    |

| K5  | PC5         |

| K6  | PC3         |

| K7  | PC2         |

| K8  | PA9/PGMM1   |

| K9  | PA8/XOUT32/ |

| 113 | PGMM0       |

| K10 | PA7/XIN32/  |

|     | PGMNVALID   |

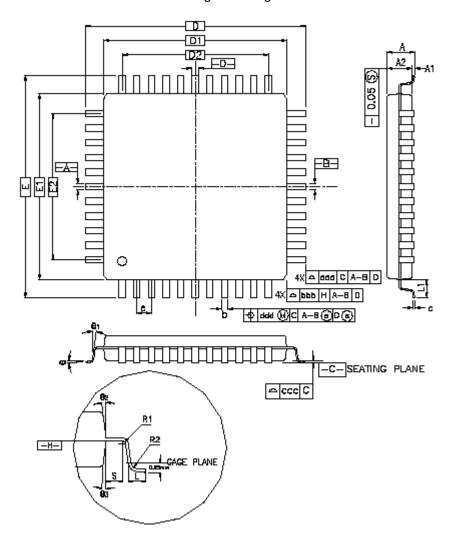

### 4.2 SAM3N4/2/1B Package and Pinout

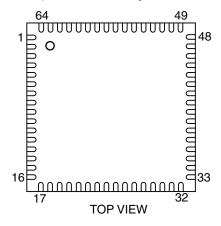

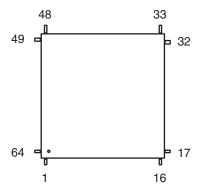

Figure 4-3. Orientation of the 64-pad QFN Package

Figure 4-4. Orientation of the 64-lead LQFP Package

#### 4.2.1 64-Lead LQFP and QFN Pinout

64-pin version SAM3N devices are pin-to-pin compatible with SAM3S products. Furthermore, SAM3N products have new functionalities shown in italic in Table 4-3.

Table 4-3.64-pin SAM3N4/2/1B Pinout

| 1  | ADVREF          | 17 | GND                            | 33 | TDI/PB4     | 49 | TDO/TRACESWO/PB5 |

|----|-----------------|----|--------------------------------|----|-------------|----|------------------|

| 2  | GND             | 18 | VDDIO                          | 34 | PA6/PGMNOE  | 50 | JTAGSEL          |

| 3  | PB0/AD4         | 19 | PA16/PGMD4                     | 35 | PA5/PGMRDY  | 51 | TMS/SWDIO/PB6    |

| 4  | PB1AD5          | 20 | PA15/PGMD3                     | 36 | PA4/PGMNCMD | 52 | PA31             |

| 5  | PB2/AD6         | 21 | PA14/PGMD2                     | 37 | PA27/PGMD15 | 53 | TCK/SWCLK/PB7    |

| 6  | PB3/AD7         | 22 | PA13/PGMD1                     | 38 | PA28        | 54 | VDDCORE          |

| 7  | VDDIN           | 23 | PA24/PGMD12                    | 39 | NRST        | 55 | ERASE/PB12       |

| 8  | VDDOUT          | 24 | VDDCORE                        | 40 | TST         | 56 | PB10             |

| 9  | PA17/PGMD5/AD0  | 25 | PA25/PGMD13                    | 41 | PA29        | 57 | PB11             |

| 10 | PA18/PGMD6/AD1  | 26 | PA26/PGMD14                    | 42 | PA30        | 58 | VDDIO            |

| 11 | PA21/PGMD9/AD8  | 27 | PA12/PGMD0                     | 43 | PA3         | 59 | PB13/DAC0        |

| 12 | VDDCORE         | 28 | PA11/PGMM3                     | 44 | PA2/PGMEN2  | 60 | GND              |

| 13 | PA19/PGMD7/AD2  | 29 | PA10/PGMM2                     | 45 | VDDIO       | 61 | XOUT/PB8         |

| 14 | PA22/PGMD10/AD9 | 30 | PA9/PGMM1                      | 46 | GND         | 62 | XIN/PGMCK/PB9    |

| 15 | PA23/PGMD11     | 31 | PA8/XOUT32/PGMM<br>0           | 47 | PA1/PGMEN1  | 63 | PB14             |

| 16 | PA20/PGMD8/AD3  | 32 | PA7/XIN32/XOUT32/<br>PGMNVALID | 48 | PA0/PGMEN0  | 64 | VDDPLL           |

Note: The bottom pad of the QFN package must be connected to ground.

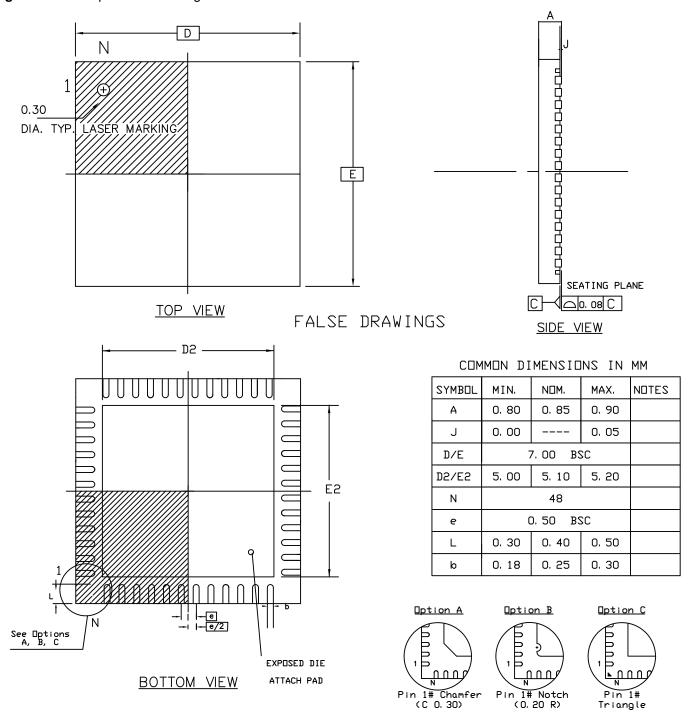

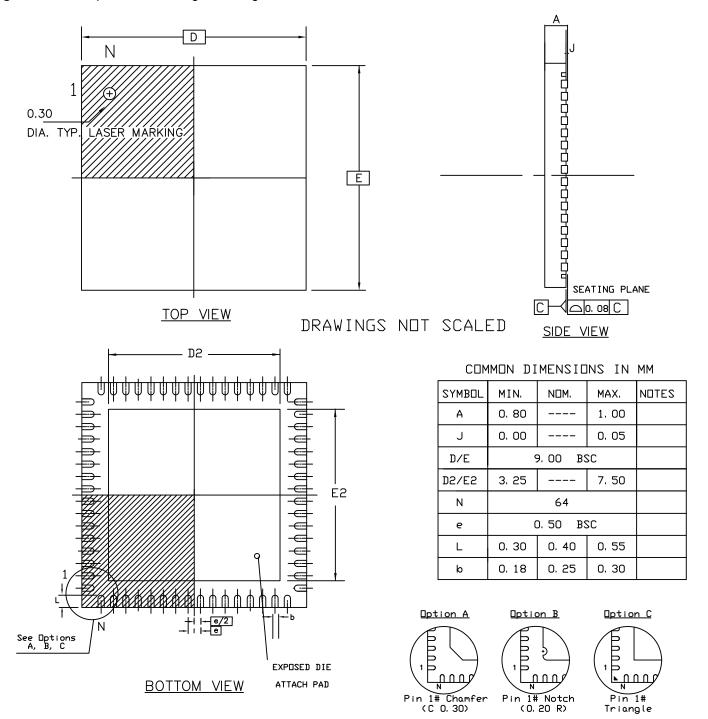

### 4.3 SAM3N4/2/1A Package and Pinout

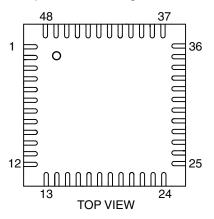

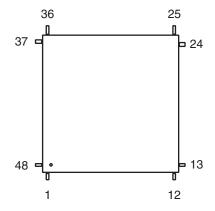

Figure 4-5. Orientation of the 48-pad QFN Package

Figure 4-6. Orientation of the 48-lead LQFP Package

#### 4.3.1 48-Lead LQFP and QFN Pinout

Table 4-4.48-pin SAM3N4/2/1A Pinout

| 1  | ADVREF         |

|----|----------------|

| 2  | GND            |

| 3  | PB0/AD4        |

| 4  | PB1/AD5        |

| 5  | PB2/AD6        |

| 6  | PB3/AD7        |

| 7  | VDDIN          |

| 8  | VDDOUT         |

| 9  | PA17/PGMD5/AD0 |

| 10 | PA18/PGMD6/AD1 |

| 11 | PA19/PGMD7/AD2 |

| 12 | PA20/AD3       |

| 13 | VDDIO                   |

|----|-------------------------|

| 14 | PA16/PGMD4              |

| 15 | PA15/PGMD3              |

| 16 | PA14/PGMD2              |

| 17 | PA13/PGMD1              |

| 18 | VDDCORE                 |

| 19 | PA12/PGMD0              |

| 20 | PA11/PGMM3              |

| 21 | PA10/PGMM2              |

| 22 | PA9/PGMM1               |

| 23 | PA8/XOUT32/PG<br>MM0    |

| 24 | PA7/XIN32/PGMN<br>VALID |

| 25 | TDI/PB4     |

|----|-------------|

| 26 | PA6/PGMNOE  |

| 27 | PA5/PGMRDY  |

| 28 | PA4/PGMNCMD |

| 29 | NRST        |

| 30 | TST         |

| 31 | PA3         |

| 32 | PA2/PGMEN2  |

| 33 | VDDIO       |

| 34 | GND         |

| 35 | PA1/PGMEN1  |

| 36 | PA0/PGMEN0  |

|    | ·           |

| TDO/TRACESWO/<br>PB5 |  |  |

|----------------------|--|--|

| JTAGSEL              |  |  |

| TMS/SWDIO/PB6        |  |  |

| TCK/SWCLK/PB7        |  |  |

| VDDCORE              |  |  |

| ERASE/PB12           |  |  |

| PB10                 |  |  |

| PB11                 |  |  |

| XOUT/PB8             |  |  |

| XIN/P/PB9/GMCK       |  |  |

| VDDIO                |  |  |

| VDDPLL               |  |  |

|                      |  |  |

Note: The bottom pad of the QFN package must be connected to ground.

#### 5. Power Considerations

#### 5.1 Power Supplies

The SAM3N product has several types of power supply pins:

- VDDCORE pins: Power the core, including the processor, the embedded memories and the peripherals. Voltage ranges from 1.62V to 1.95V.

- VDDIO pins: Power the Peripherals I/O lines, Backup part, 32 kHz crystal oscillator and oscillator pads. Voltage ranges from 1.62V to 3.6V

- VDDIN pin: Voltage Regulator, ADC and DAC Power Supply. Voltage ranges from 1.8V to 3.6V for the Voltage Regulator

- VDDPLL pin: Powers the PLL, the Fast RC and the 3 to 20 MHz oscillators. Voltage ranges from 1.62V to 1.95V.

#### 5.2 Voltage Regulator

The SAM3N embeds a voltage regulator that is managed by the Supply Controller.

This internal regulator is intended to supply the internal core of SAM3N. It features two different operating modes:

- In Normal mode, the voltage regulator consumes less than 700 μA static current and draws 60 mA of output current. Internal adaptive biasing adjusts the regulator quiescent current depending on the required load current. In Wait Mode quiescent current is only 7 μA.

- In Backup mode, the voltage regulator consumes less than 1 μA while its output (VDDOUT) is driven internally to GND. The default output voltage is 1.80V and the start-up time to reach Normal mode is less than 100 μs.

For adequate input and output power supply decoupling/bypassing, refer to "Voltage Regulator" in the "Electrical Characteristics" section of the datasheet.

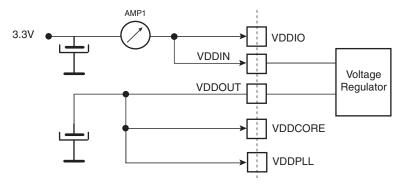

### 5.3 Typical Powering Schematics

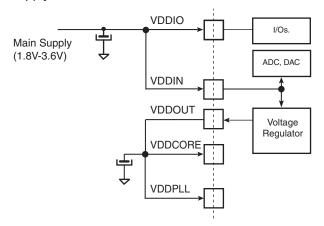

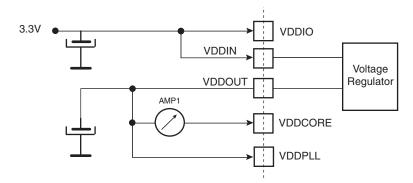

The SAM3N supports a 1.62V-3.6V single supply mode. The internal regulator input connected to the source and its output feeds VDDCORE. Figure 5-1 shows the power schematics.

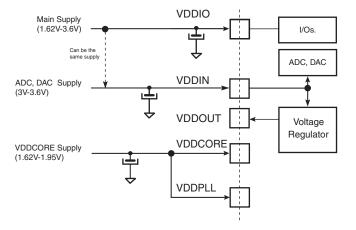

As VDDIN powers the voltage regulator and the ADC/DAC, when the user does not want to use the embedded voltage regulator, it can be disabled by software via the SUPC (note that it is different from Backup mode).

Figure 5-1. Single Supply

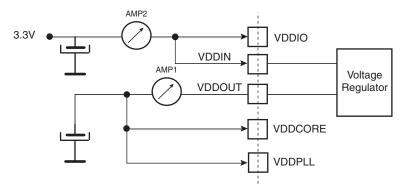

Figure 5-2. Core Externally Supplied

Note: Restrictions

With Main Supply < 3V, ADC and DAC are not usable. With Main Supply >= 3V, all peripherals are usable.

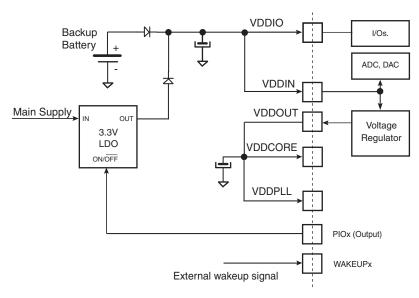

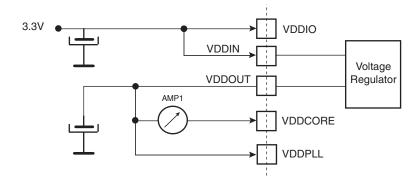

Figure 5-3 below provides an example of the powering scheme when using a backup battery. Since the PIO state is preserved when in backup mode, any free PIO line can be used to switch off the external regulator by driving the PIO line at low level (PIO is input, pull-up enabled after backup reset). External wake-up of the system can be from a push button or any signal. See Section 5.6 "Wake-up Sources" for further details.

Figure 5-3. Core Externally Supplied (backup battery)

ADC, DAC Supply (3V-3.6V)

Note: The two diodes provide a "switchover circuit" (for illustration purpose; between the backup battery and the main supply when the system is put in backup mode.

#### 5.4 Active Mode

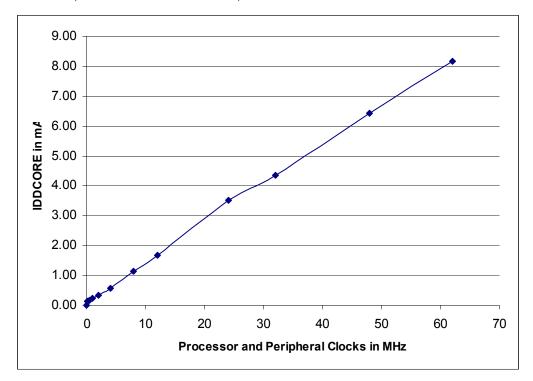

Active mode is the normal running mode with the core clock running from the fast RC oscillator, the main crystal oscillator or the PLL. The power management controller can be used to adapt the frequency and to disable the peripheral clocks.

#### 5.5 Low Power Modes

The various low-power modes of the SAM3N are described below:

#### 5.5.1 Backup Mode

The purpose of backup mode is to achieve the lowest power consumption possible in a system that is performing periodic wakeups to carry out tasks but not requiring fast startup time (<0.1ms). Total current consumption is 3 µA typical.

The Supply Controller, zero-power power-on reset, RTT, RTC, Backup registers and 32 kHz oscillator (RC or crystal oscillator selected by software in the Supply Controller) are running. The regulator and the core supply are off.

Backup mode is based on the Cortex-M3 deep sleep mode with the voltage regulator disabled.

The SAM3N can be awakened from this mode through WUP0-15 pins, the supply monitor (SM), the RTT or RTC wake-up event.

Backup mode is entered by using WFE instructions with the SLEEPDEEP bit in the System Control Register of the Cortex-M3 set to 1. (See the "Power Management" description in The ARM Cortex M3 Processor section of the product datasheet).

Exit from Backup mode happens if one of the following enable wake-up events occurs:

WKUPEN0-15 pins (level transition, configurable debouncing)

- · Supply Monitor alarm

- RTC alarm

- RTT alarm

#### 5.5.2 Wait Mode

The purpose of the wait mode is to achieve very low power consumption while maintaining the whole device in a powered state for a startup time of less than 10  $\mu$ s. Current Consumption in Wait mode is typically 15  $\mu$ A (total current consumption) if the internal voltage regulator is used or 8  $\mu$ A if an external regulator is used.

In this mode, the clocks of the core, peripherals and memories are stopped. However, the core, peripherals and memories power supplies are still powered. From this mode, a fast start up is available.

This mode is entered via Wait for Event (WFE) instructions with LPM = 1 (Low Power Mode bit in PMC\_FSMR). The Cortex-M3 is able to handle external or internal events in order to wake up the core (WFE). By configuring the WUP0-15 external lines as fast startup wake-up pins (refer to Section 5.7 "Fast Start-Up"). RTC or RTT Alarm wake-up events can be used to wake up the CPU (exit from WFE).

#### Entering Wait Mode:

- Select the 4/8/12 MHz fast RC oscillator as Main Clock

- Set the LPM bit in the PMC Fast Startup Mode Register (PMC FSMR)

- Execute the Wait-For-Event (WFE) instruction of the processor

Note: Internal Main clock resynchronization cycles are necessary between the writing of MOSCRCEN bit and the effective entry in Wait mode. Depending on the user application, Waiting for MOSCRCEN bit to be cleared is recommended to ensure that the core will not execute undesired instructions.

#### 5.5.3 Sleep Mode

The purpose of sleep mode is to optimize power consumption of the device versus response time. In this mode, only the core clock is stopped. The peripheral clocks can be enabled. The current consumption in this mode is application dependent.

This mode is entered via Wait for Interrupt (WFI) or Wait for Event (WFE) instructions with LPM = 0 in PMC FSMR.

The processor can be woke up from an interrupt if WFI instruction of the Cortex M3 is used, or from an event if the WFE instruction is used to enter this mode.

#### 5.5.4 Low Power Mode Summary Table

The modes detailed above are the main low power modes. Each part can be set to on or off separately and wake up sources can be individually configured. Table 5-1 below shows a summary of the configurations of the low power modes.

Table 5-1.

Low Power Mode Configuration Summary

| Mode           | SUPC,<br>32 kHz<br>Oscillator<br>RTC RTT<br>Backup<br>Registers,<br>POR<br>(Backup<br>Region) | Regulator | Core<br>Memory<br>Peripherals           | Mode Entry                                          | Potential Wake Up<br>Sources                                                                                                                                                     | Core at<br>Wake Up | PIO State<br>while in Low<br>Power Mode | PIO State<br>at Wake Up                             | Consumption               | Wake Up<br>Time <sup>(1)</sup> |

|----------------|-----------------------------------------------------------------------------------------------|-----------|-----------------------------------------|-----------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------|-----------------------------------------|-----------------------------------------------------|---------------------------|--------------------------------|

| Backup<br>Mode | ON                                                                                            | OFF       | OFF<br>(Not powered)                    | WFE<br>+SLEEPDEEP<br>bit = 1                        | WUP0-15 pins<br>BOD alarm<br>RTC alarm<br>RTT alarm                                                                                                                              | Reset              | Previous<br>state saved                 | PIOA &<br>PIOB &<br>PIOC<br>Inputs with<br>pull ups | 3 µА typ <sup>(4)</sup>   | < 0.1 ms                       |

| Wait<br>Mode   | ON                                                                                            | ON        | Powered<br>(Not clocked)                | WFE<br>+SLEEPDEEP<br>bit = 0<br>+LPM bit = 1        | Any Event from: Fast<br>startup through<br>WUP0-15 pins<br>RTC alarm<br>RTT alarm<br>USB wake-up                                                                                 | Clocked<br>back    | Previous<br>state saved                 | Unchanged                                           | 5 μΑ/15 μΑ <sup>(5)</sup> | < 10 μs                        |

| Sleep<br>Mode  | ON                                                                                            | ON        | Powered <sup>(7)</sup><br>(Not clocked) | WFE or WFI<br>+SLEEPDEEP<br>bit = 0<br>+LPM bit = 0 | Entry mode = WFI<br>Interrupt Only; Entry<br>mode = WFE Any<br>Enabled Interrupt<br>and/or Any Event<br>from: Fast start-up<br>through WUP0-15<br>pins<br>RTC alarm<br>RTT alarm | Clocked<br>back    | Previous<br>state saved                 | Unchanged                                           | (6)                       | (6)                            |

Notes:

- 1. When considering wake-up time, the time required to start the PLL is not taken into account. Once started, the device works with the 4/8/12 MHz Fast RC oscillator. The user has to add the PLL start-up time if it is needed in the system. The wake-up time is defined as the time taken for wake up until the first instruction is fetched.

- 2. The external loads on PIOs are not taken into account in the calculation.

- 3. Supply Monitor current consumption is not included.

- 4. Total Current consumption.

- 5.  $5 \mu A$  on VDDCORE,  $15 \mu A$  for total current consumption (using internal voltage regulator),  $8 \mu A$  for total current consumption (without using internal voltage regulator).

- 6. Depends on MCK frequency.

- 7. In this mode the core is supplied and not clocked but some peripherals can be clocked.

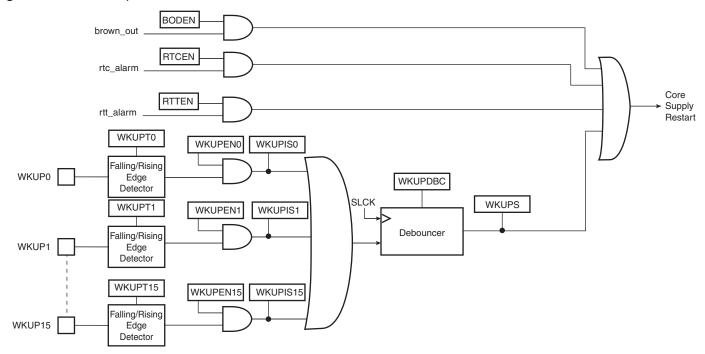

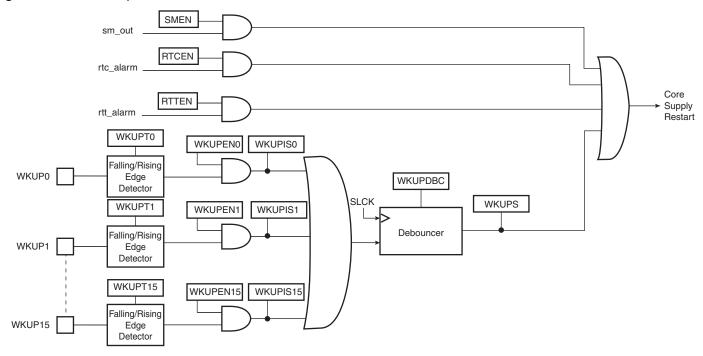

### 5.6 Wake-up Sources

The wake-up events allow the device to exit backup mode. When a wake-up event is detected, the Supply Controller performs a sequence which automatically reenables the core power supply and the SRAM power supply, if they are not already enabled.

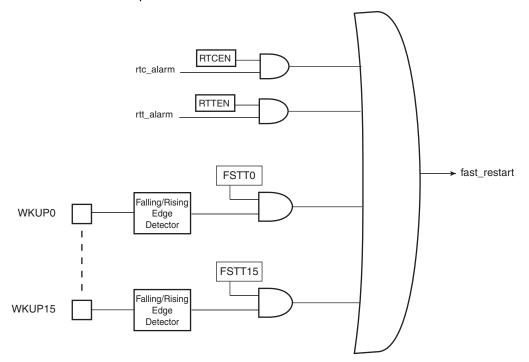

Figure 5-4. Wake-up Source

#### 5.7 Fast Start-Up

The SAM3N allows the processor to restart in a few microseconds while the processor is in wait mode. A fast start up can occur upon detection of a low level on one of the 19 wake-up inputs (WKUP0 to 15 + SM + RTC + RTT).

The fast restart circuitry, as shown in Figure 5-5, is fully asynchronous and provides a fast start-up signal to the Power Management Controller. As soon as the fast start-up signal is asserted, the PMC automatically restarts the embedded 4 MHz fast RC oscillator, switches the master clock on this 4 MHz clock and reenables the processor clock.

Figure 5-5. Fast Start-Up Sources

### 6. Input/Output Lines

The SAM3N has several kinds of input/output (I/O) lines such as general purpose I/Os (GPIO) and system I/Os. GPIOs can have alternate functionality due to multiplexing capabilities of the PIO controllers. The same PIO line can be used whether in IO mode or by the multiplexed peripheral. System I/Os include pins such as test pins, oscillators, erase or analog inputs.

#### 6.1 General Purpose I/O Lines

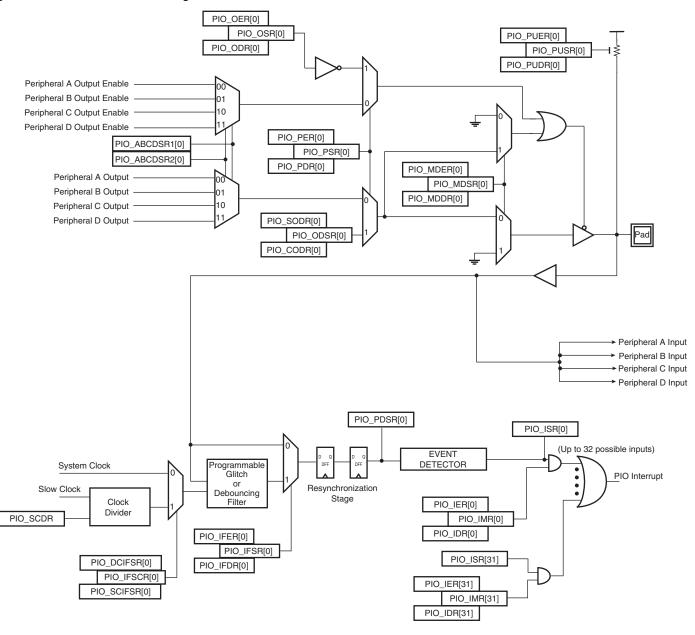

GPIO Lines are managed by PIO Controllers. All I/Os have several input or output modes such as pull-up or pull-down, input Schmitt triggers, multi-drive (open-drain), glitch filters, debouncing or input change interrupt. Programming of these modes is performed independently for each I/O line through the PIO controller user interface. For more details, refer to the product PIO controller section.

The input output buffers of the PIO lines are supplied through VDDIO power supply rail.

The SAM3N embeds high speed pads able to handle up to 45 MHz for SPI clock lines and 35 MHz on other lines. See "AC Characteristics" in the "Electrical Characteristics" section of the datasheet for more details. Typical pull-up and pull-down value is 100 k $\Omega$  for all I/Os.

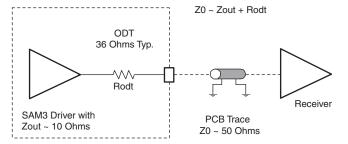

Each I/O line also embeds an ODT (On-Die Termination), (see Figure 6-1). It consists of an internal series resistor termination scheme for impedance matching between the driver output (SAM3N) and the PCB trace impedance preventing signal reflection. The series resistor helps to reduce I/O switching current (di/dt) thereby reducing in turn, EMI. It also decreases overshoot and undershoot (ringing) due to inductance of interconnect between devices or between boards. In conclusion ODT helps diminish signal integrity issues.

Figure 6-1. On-Die Termination

#### 6.2 System I/O Lines

System I/O lines are pins used by oscillators, test mode, reset and JTAG to name but a few. Described below are the SAM3N system I/O lines shared with PIO lines:

These pins are software configurable as general purpose I/O or system pins. At startup the default function of these pins is always used.

**Table 6-1.** System I/O Configuration Pin List.

| SYSTEM_IO<br>bit number | Default function after reset | Other function | Constraints for normal start        | Configuration                                                    |  |

|-------------------------|------------------------------|----------------|-------------------------------------|------------------------------------------------------------------|--|

| 12                      | ERASE                        | PB12           | Low Level at startup <sup>(1)</sup> | In Matrix User Interface Registers                               |  |

| 7                       | TCK/SWCLK                    | PB7            | -                                   | (Refer to the System I/O                                         |  |

| 6                       | TMS/SWDIO                    | PB6            | -                                   | Configuration Register in the Bus  Matrix section of the product |  |

| 5                       | TDO/TRACESWO                 | PB5            | -                                   | datasheet.)                                                      |  |

| 4                       | TDI                          | PB4            | -                                   |                                                                  |  |

| -                       | PA7                          | XIN32          | -                                   | 0 ( ) (2) 1                                                      |  |

| -                       | PA8                          | XOUT32         | -                                   | See footnote (2) below                                           |  |

| -                       | PB9                          | XIN            | -                                   | See footnote (3) below                                           |  |

| -                       | PB8                          | XOUT           | -                                   |                                                                  |  |

Notes: 1. If PB12 is used as PIO input in user applications, a low level must be ensured at startup to prevent Flash erase before the user application sets PB12 into PIO mode.

- 2. In the product Datasheet Refer to: Slow Clock Generator of the Supply Controller section.

- 3. In the product Datasheet Refer to: 3 to 20 MHZ Crystal Oscillator information in the PMC section.

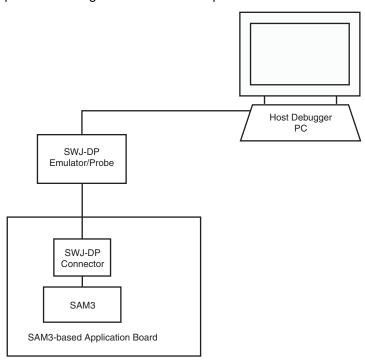

#### 6.2.1 Serial Wire JTAG Debug Port (SWJ-DP) Pins

The SWJ-DP pins are TCK/SWCLK, TMS/SWDIO, TDO/SWO, TDI and commonly provided on a standard 20-pin JTAG connector defined by ARM. For more details about voltage reference and reset state, refer to Table 3-1 on page 6.

At startup, SWJ-DP pins are configured in SWJ-DP mode to allow connection with debugging probe. Please refer to the "Debug and Test" section of the product datasheet.

SWJ-DP pins can be used as standard I/Os to provide users more general input/output pins when the debug port is not needed in the end application. Mode selection between SWJ-DP mode (System IO mode) and general IO mode is performed through the AHB Matrix Special Function Registers (MATRIX\_SFR). Configuration of the pad for pull-up, triggers, debouncing and glitch filters is possible regardless of the mode.

The JTAGSEL pin is used to select the JTAG boundary scan when asserted at a high level. It integrates a permanent pull-down resistor of about 15 k $\Omega$  to GND, so that it can be left unconnected for normal operations.

By default, the JTAG Debug Port is active. If the debugger host wants to switch to the Serial Wire Debug Port, it must provide a dedicated JTAG sequence on TMS/SWDIO and TCK/SWCLK which disables the JTAG-DP and enables the SW-DP. When the Serial Wire Debug Port is active, TDO/TRACESWO can be used for trace.

The asynchronous TRACE output (TRACESWO) is multiplexed with TDO. So the asynchronous trace can only be used with SW-DP, not JTAG-DP. For more information about SW-DP and JTAG-DP switching, please refer to the" Debug and Test" section.

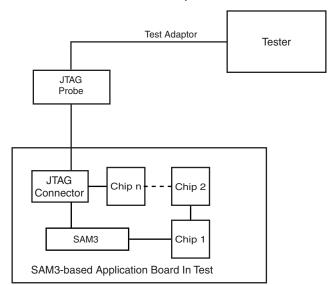

#### 6.3 Test Pin

The TST pin is used for JTAG Boundary Scan Manufacturing Test or Fast Flash programming mode of the SAM3N series. The TST pin integrates a permanent pull-down resistor of about 15 k $\Omega$  to GND, so that it can be left unconnected for normal operations. To enter fast programming mode, see the "Fast Flash Programming Interface" section of the product datasheet. For more on the manufacturing and test mode, refer to the "Debug and Test" section of the product datasheet.

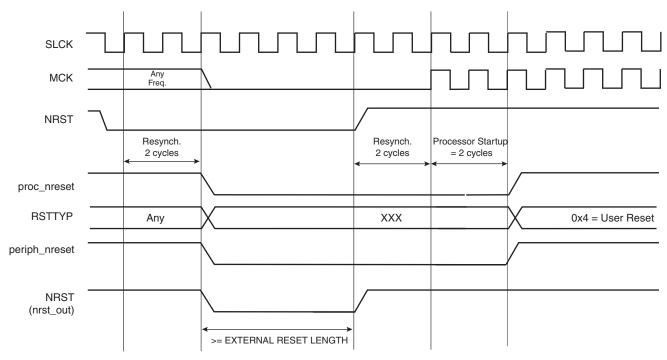

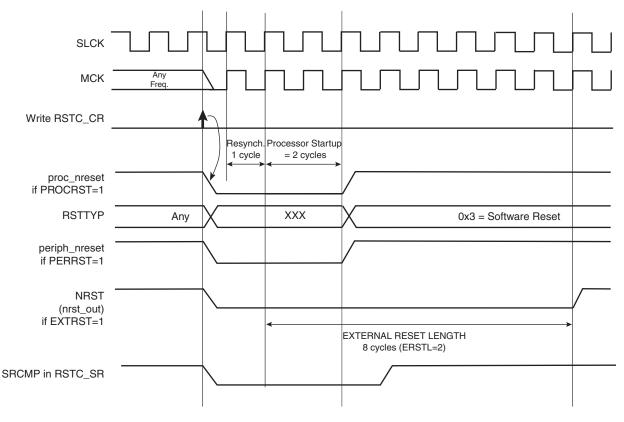

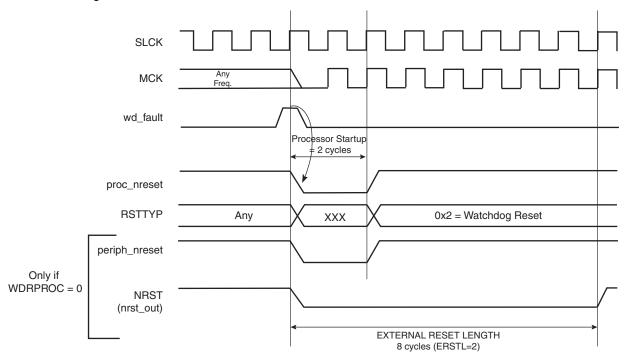

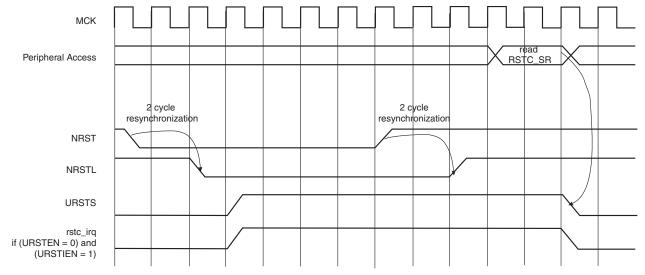

#### 6.4 NRST Pin

The NRST pin is bidirectional. It is handled by the on-chip reset controller and can be driven low to provide a reset signal to the external components or asserted low externally to reset the microcontroller. It will reset the Core and the peripherals except the Backup region (RTC, RTT and Supply Controller). There is no constraint on the length of the reset pulse and the reset controller can guarantee a minimum pulse length. The NRST pin integrates a permanent pull-up resistor to VDDIO of about 100 k $\Omega$ . By default, the NRST pin is configured as an input.

#### 6.5 ERASE Pin

The ERASE pin is used to reinitialize the Flash content (and some of its NVM bits) to an erased state (all bits read as logic level 1). It integrates a pull-down resistor of about 100 k $\Omega$  to GND, so that it can be left unconnected for normal operations.

This pin is debounced by SCLK to improve the glitch tolerance. When the ERASE pin is tied high during less than 100 ms, it is not taken into account. The pin must be tied high during more than 220 ms to perform a Flash erase operation.

The ERASE pin is a system I/O pin and can be used as a standard I/O. At startup, the ERASE pin is not configured as a PIO pin. If the ERASE pin is used as a standard I/O, startup level of this pin must be low to prevent unwanted erasing. Please refer to Section 9.3 "Peripheral Signal Multiplexing on I/O Lines" on page 34. Also, if the ERASE pin is used as a standard I/O output, asserting the pin to low does not erase the Flash.

#### 7. Memories

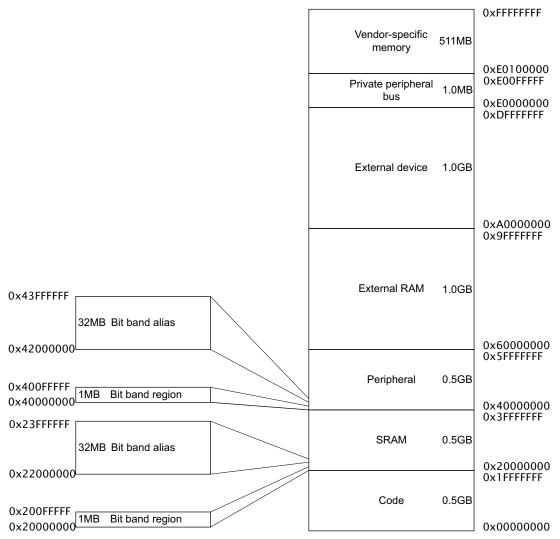

### 7.1 Product Mapping

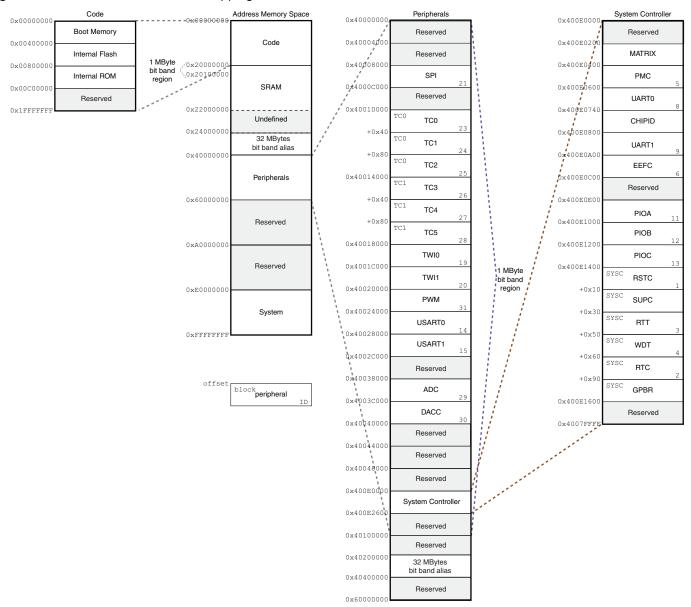

Figure 7-1. SAM3N4/2/1 Product Mapping

#### 7.2 Embedded Memories

#### 7.2.1 Internal SRAM

The SAM3N4 product embeds a total of 24-Kbytes high-speed SRAM.

The SAM3N2 product embeds a total of 16-Kbytes high-speed SRAM.

The SAM3N1 product embeds a total of 8-Kbytes high-speed SRAM.

The SRAM is accessible over System Cortex-M3 bus at address 0x2000 0000.

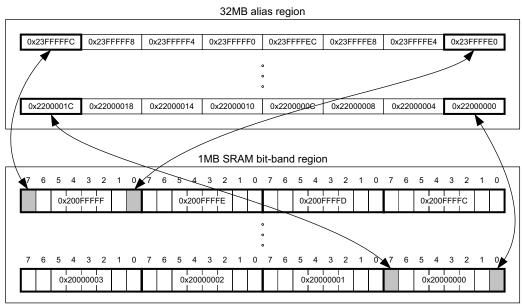

The SRAM is in the bit band region. The bit band alias region is from 0x2200 0000 and 0x23FF FFFF.

RAM size must be configurable by calibration fuses.

#### 7.2.2 Internal ROM

The SAM3N product embeds an Internal ROM, which contains the SAM Boot Assistant (SAM-BA), In Application Programming routines (IAP) and Fast Flash Programming Interface (FFPI).

At any time, the ROM is mapped at address 0x0080 0000.

#### 7.2.3 Embedded Flash

#### 7.2.3.1 Flash Overview

The Flash of the SAM3N4 (256 Kbytes) is organized in one bank of 1024 pages of 256 bytes (Single plane).

The Flash of the SAM3N2 (128 Kbytes) is organized in one bank of 512 pages of 256 bytes (Single Plane).

The Flash of the SAM3N1 (64 Kbytes) is organized in one bank of 256 pages of 256 bytes (Single plane).

The Flash contains a 128-byte write buffer, accessible through a 32-bit interface.

#### 7.2.3.2 Flash Power Supply

The Flash is supplied by VDDCORE.

#### 7.2.3.3 Enhanced Embedded Flash Controller

The Enhanced Embedded Flash Controller (EEFC) manages accesses performed by the masters of the system. It enables reading the Flash and writing the write buffer. It also contains a User Interface, mapped on the APB.

The Enhanced Embedded Flash Controller ensures the interface of the Flash block with the 32-bit internal bus. Its 128-bit wide memory interface increases performance.

The user can choose between high performance or lower current consumption by selecting either 128-bit or 64-bit access. It also manages the programming, erasing, locking and unlocking sequences of the Flash using a full set of commands.

One of the commands returns the embedded Flash descriptor definition that informs the system about the Flash organization, thus making the software generic.

#### 7.2.3.4 Flash Speed

The user needs to set the number of wait states depending on the frequency used.

For more details, refer to the AC Characteristics sub section in the "Electrical Characteristics" section.

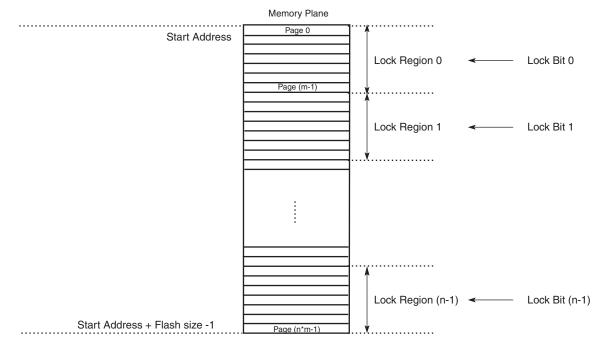

#### 7.2.3.5 Lock Regions

Several lock bits used to protect write and erase operations on lock regions. A lock region is composed of several consecutive pages, and each lock region has its associated lock bit.

Table 7-1. Lock bit number

| Product | Number of lock bits | Lock region size     |

|---------|---------------------|----------------------|

| SAM3N4  | 16                  | 16 kbytes (64 pages) |

| SAM3N2  | 8                   | 16 kbytes (64 pages) |

| SAM3N1  | 4                   | 16 kbytes (64 pages) |

If a locked-region's erase or program command occurs, the command is aborted and the EEFC triggers an interrupt.

The lock bits are software programmable through the EEFC User Interface. The command "Set Lock Bit" enables the protection. The command "Clear Lock Bit" unlocks the lock region.

Asserting the ERASE pin clears the lock bits, thus unlocking the entire Flash.

#### 7.2.3.6 Security Bit Feature

The SAM3N features a security bit, based on a specific General Purpose NVM bit (GPNVM bit 0). When the security is enabled, any access to the Flash, either through the ICE interface or through the Fast Flash Programming Interface, is forbidden. This ensures the confidentiality of the code programmed in the Flash.

This security bit can only be enabled, through the command "Set General Purpose NVM Bit 0" of the EEFC User Interface. Disabling the security bit can only be achieved by asserting the ERASE pin at 1, after a full Flash erase is performed. When the security bit is deactivated, all accesses to the Flash are permitted.

It is important to note that the assertion of the ERASE pin should always be longer than 200 ms.

As the ERASE pin integrates a permanent pull-down, it can be left unconnected during normal operation. However, it is safer to connect it directly to GND for the final application.

#### 7.2.3.7 Calibration Bits

NVM bits are used to calibrate the brownout detector and the voltage regulator. These bits are factory configured and cannot be changed by the user. The ERASE pin has no effect on the calibration bits.

#### 7.2.3.8 Unique Identifier

Each device integrates its own 128-bit unique identifier. These bits are factory configured and cannot be changed by the user. The ERASE pin has no effect on the unique identifier.

#### 7.2.3.9 Fast Flash Programming Interface

The Fast Flash Programming Interface allows programming the device through either a serial JTAG interface or through a multiplexed fully-handshaked parallel port. It allows gang programming with market-standard industrial programmers.

The FFPI supports read, page program, page erase, full erase, lock, unlock and protect commands.

The Fast Flash Programming Interface is enabled and the Fast Programming Mode is entered when TST and PA0 and PA1are tied low.

#### 7.2.3.10 SAM-BA Boot

The SAM-BA Boot is a default Boot Program which provides an easy way to program in-situ the on-chip Flash memory.

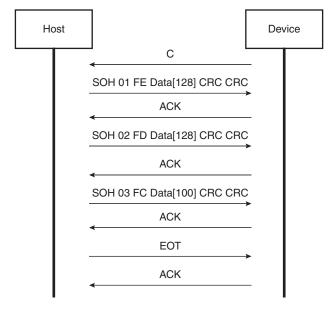

The SAM-BA Boot Assistant supports serial communication via the UARTO.

The SAM-BA Boot provides an interface with SAM-BA Graphic User Interface (GUI).

The SAM-BA Boot is in ROM and is mapped in Flash at address 0x0 when GPNVM bit 1 is set to 0.

#### 7.2.3.11 GPNVM Bits

The SAM3N features three GPNVM bits that can be cleared or set respectively through the commands "Clear GPNVM Bit" and "Set GPNVM Bit" of the EEFC User Interface.

**Table 7-2.** General-purpose Non volatile Memory Bits

| GPNVMBit[#] | Function            |

|-------------|---------------------|

| 0           | Security bit        |

| 1           | Boot mode selection |

#### 7.2.4 Boot Strategies

The system always boots at address 0x0. To ensure a maximum boot possibilities the memory layout can be changed via GPNVM.

A general purpose NVM (GPNVM) bit is used to boot either on the ROM (default) or from the Flash.

The GPNVM bit can be cleared or set respectively through the commands "Clear General-purpose NVM Bit" and "Set General-purpose NVM Bit" of the EEFC User Interface.

Setting the GPNVM Bit 1 selects the boot from the Flash, clearing it selects the boot from the ROM. Asserting ERASE clears the GPNVM Bit 1 and thus selects the boot from the ROM by default.

## 8. System Controller

The System Controller is a set of peripherals, which allow handling of key elements of the system, such as power, resets, clocks, time, interrupts, watchdog, etc...

See the System Controller block diagram in Figure 8-1 on page 31.

VDDOUT vr\_on Software Controlled vr\_mode VDDIN Voltage Regulator Supply Zero-Power Controller Power-on Reset VDDIO  $bod\_on$ Supply PIOx PIOA/B/C Monitor brown\_out\_ (Backup) WKUP0 - WKUP15 ADx General Purpose ADC Backup Registers ADVREF rtc\_nreset SLCK DAC rtc\_alarm\_ DAC0 SLCK rtt\_alarm, osc32k\_xtal\_en core\_nreset osc32k\_sel XIN32 Xtal 32 kHz Slow Clock bod\_core\_on Oscillator Brownout XOUT32 SLCK Detector lcore\_brown\_out (Core) Embedded osc32k\_rc\_en 32 kHz RC Oscillator SRAM **Backup Power Supply** Peripherals **VDDCORE** ➤ proc\_nreset core\_nreset Matrix Reset > periph nreset Peripheral Controller → ice\_nreset Bridge NRST Cortex-M3 FSTT0 - FSTT15 SLCK\_ Embedded Flash 12/8/4 MHz Main Clock Master Clock MCK RC Oscillator MAINCK Power XIN Xtal Management Controller Oscillator XOUT PLL Watchdog SLCK-Timer

Figure 8-1. System Controller Block Diagram

Core Power Supply

#### 8.1 System Controller and Peripheral Mapping

Please refer to Figure 7-1, "SAM3N4/2/1 Product Mapping" on page 26.

All the peripherals are in the bit band region and are mapped in the bit band alias region.

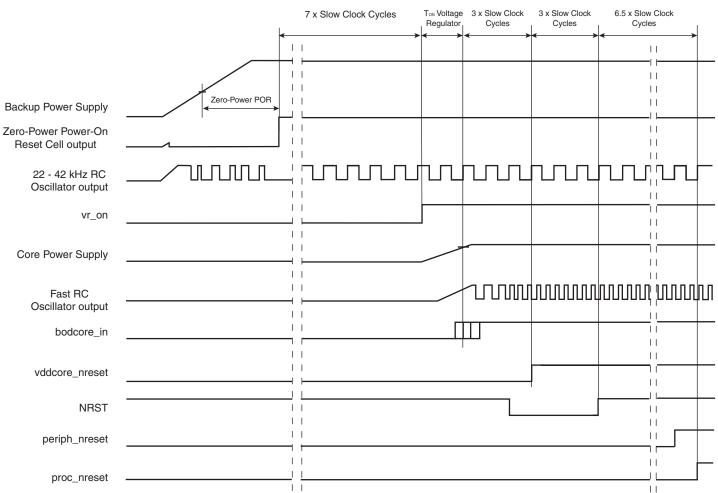

#### 8.2 Power-on-Reset, Brownout and Supply Monitor

The SAM3N embeds three features to monitor, warn and/or reset the chip:

- Power-on-Reset on VDDIO

- Brownout Detector on VDDCORE

- Supply Monitor on VDDIO

#### 8.2.1 Power-on-Reset

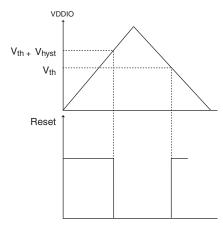

The Power-on-Reset monitors VDDIO. It is always activated and monitors voltage at start up but also during power down. If VDDIO goes below the threshold voltage, the entire chip is reset. For more information, refer to the "Electrical Characteristics" section of the datasheet.

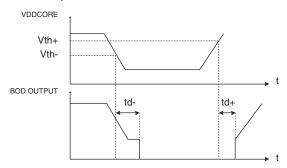

#### 8.2.2 Brownout Detector on VDDCORE

The Brownout Detector monitors VDDCORE. It is active by default. It can be deactivated by software through the Supply Controller (SUPC\_MR). It is especially recommended to disable it during low-power modes such as wait or sleep modes.

If VDDCORE goes below the threshold voltage, the reset of the core is asserted. For more information, refer to the Supply Controller (SUPC) and Electrical Characteristics sections of the datasheet.

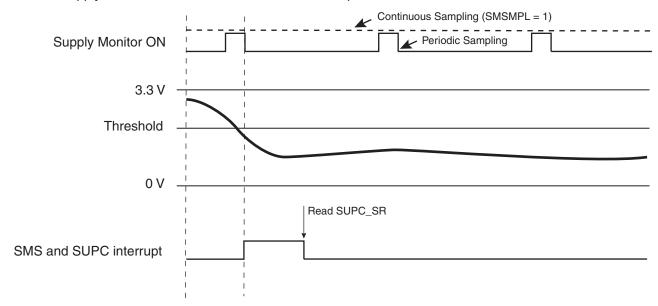

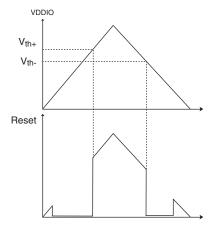

#### 8.2.3 Supply Monitor on VDDIO

The Supply Monitor monitors VDDIO. It is inactive by default. It can be activated by software and is fully programmable with 16 steps for the threshold (between 1.9V to 3.4V). It is controlled by the Supply Controller (SUPC). A sample mode is possible. It allows to divide the supply monitor power consumption by a factor of up to 2048. For more information, refer to the Supply Controller and Electrical Characteristics sections of the datasheet.

## 9. Peripherals

### 9.1 Peripheral Identifiers

Table 9-1 defines the Peripheral Identifiers of the SAM3N4/2/1. A peripheral identifier is required for the control of the peripheral interrupt with the Nested Vectored Interrupt Controller and for the control of the peripheral clock with the Power Management Controller.

Table 9-1.

Peripheral Identifiers

| Instance ID | Instance Name | NVIC Interrupt | PMC Clock Control | Instance Description        |  |

|-------------|---------------|----------------|-------------------|-----------------------------|--|

| 0           | SUPC          | Х              |                   | Supply Controller           |  |

| 1           | RSTC          | X              |                   | Reset Controller            |  |

| 2           | RTC           | X              |                   | Real Time Clock             |  |

| 3           | RTT           | X              |                   | Real Time Timer             |  |

| 4           | WDT           | X              |                   | Watchdog Timer              |  |

| 5           | PMC           | X              |                   | Power Management Controller |  |

| 6           | EEFC          | X              |                   | Enhanced Flash Controller   |  |

| 7           | -             | -              |                   | Reserved                    |  |

| 8           | UART0         | X              | X                 | UART 0                      |  |

| 9           | UART1         | X              | X                 | UART 1                      |  |

| 10          | -             | -              | -                 | Reserved                    |  |

| 11          | PIOA          | X              | X                 | Parallel I/O Controller A   |  |

| 12          | PIOB          | X              | X                 | Parallel I/O Controller B   |  |

| 13          | PIOC          | X              | X                 | Parallel I/O Controller C   |  |

| 14          | USART0        | X              | X                 | USART 0                     |  |

| 15          | USART1        | X              | X                 | USART 1                     |  |

| 16          | -             | -              | -                 | Reserved                    |  |

| 17          | -             | -              | -                 | Reserved                    |  |

| 18          | -             | -              | -                 | Reserved                    |  |

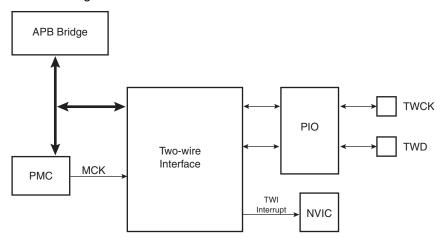

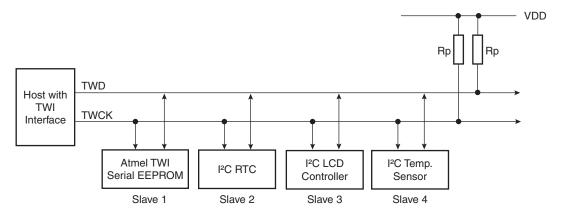

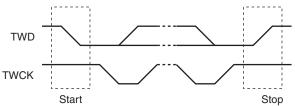

| 19          | TWI0          | X              | X                 | Two Wire Interface 0        |  |

| 20          | TWI1          | X              | X                 | Two Wire Interface 1        |  |

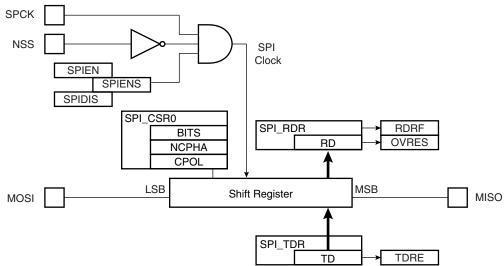

| 21          | SPI           | X              | X                 | Serial Peripheral Interface |  |

| 22          | -             | -              | -                 | Reserved                    |  |

| 23          | TC0           | Х              | X                 | Timer/Counter 0             |  |

| 24          | TC1           | X              | X                 | Timer/Counter 1             |  |

| 25          | TC2           | X              | X                 | Timer/Counter 2             |  |

| 26          | TC3           | X              | Х                 | Timer/Counter 3             |  |

| 27          | TC4           | Х              | х                 | Timer/Counter 4             |  |

| 28          | TC5           | Х              | х                 | Timer/Counter 5             |  |

| 29          | ADC           | X              | X                 | Analog-to-Digital Converter |  |

| 30          | DACC          | X              | X                 | Digital-to-Analog Converter |  |

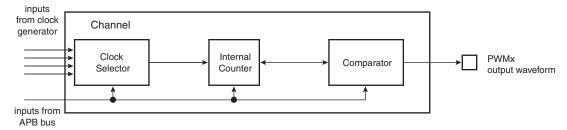

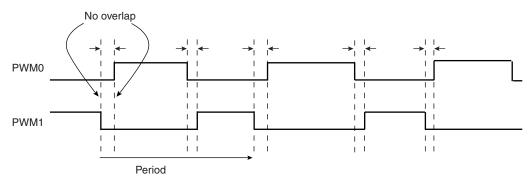

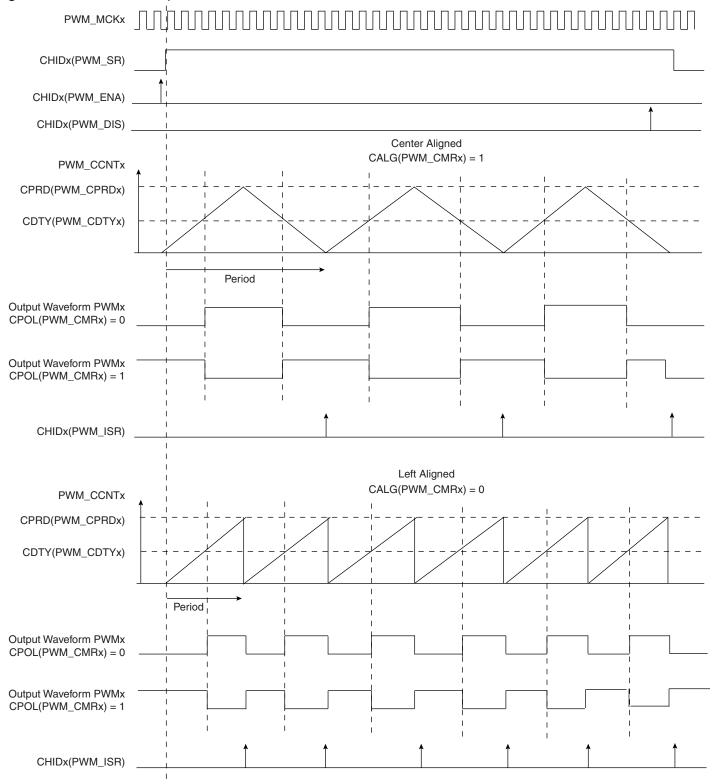

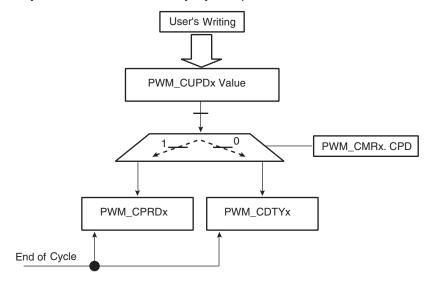

| 31          | PWM           | Х              | Х                 | Pulse Width Modulation      |  |

#### 9.2 APB/AHB Bridge

The SAM3N4/2/1 product embeds one peripheral bridge:

The peripherals of the bridge are clocked by MCK.

#### 9.3 Peripheral Signal Multiplexing on I/O Lines

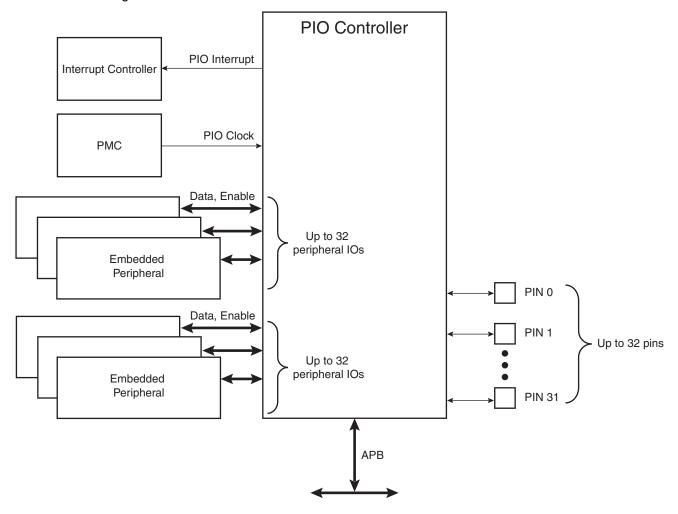

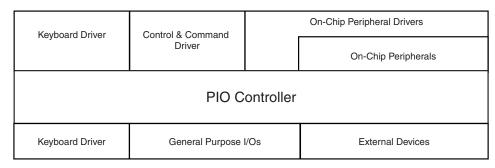

The SAM3N product features 2 PIO controllers (48-pin and 64-pin version) or 3 PIO controllers (100-pin version), PIOA, PIOB and PIOC, that multiplex the I/O lines of the peripheral set.

The SAM3N 64-pin and 100-pin PIO Controller controls up to 32 lines (see Table 9-2, "Multiplexing on PIO Controller A (PIOA)," on page 35). Each line can be assigned to one of three peripheral functions: A, B or C. The multiplexing tables in the following paragraphs define how the I/O lines of the peripherals A, B and C are multiplexed on the PIO Controllers. The column "Comments" has been inserted in this table for the user's own comments; it may be used to track how pins are defined in an application.

Note that some peripheral functions which are output only, might be duplicated within the tables.

### 9.3.1 PIO Controller A Multiplexing

Table 9-2.

Multiplexing on PIO Controller A (PIOA)

| I/O Line | Peripheral A | Peripheral B | Peripheral C | Extra Function | System Function | Comments            |

|----------|--------------|--------------|--------------|----------------|-----------------|---------------------|

| PA0      | PWM0         | TIOA0        |              | WKUP0          |                 | High drive          |

| PA1      | PWM1         | TIOB0        |              | WKUP1          |                 | High drive          |

| PA2      | PWM2         | SCK0         | DATRG        | WKUP2          |                 | High drive          |

| PA3      | TWD0         | NPCS3        |              |                |                 | High drive          |

| PA4      | TWCK0        | TCLK0        |              | WKUP3          |                 |                     |

| PA5      | RXD0         | NPCS3        |              | WKUP4          |                 |                     |

| PA6      | TXD0         | PCK0         |              |                |                 |                     |

| PA7      | RTS0         | PWM3         |              |                | XIN32           |                     |

| PA8      | CTS0         | ADTRG        |              | WKUP5          | XOUT32          |                     |

| PA9      | URXD0        | NPCS1        |              | WKUP6          |                 |                     |

| PA10     | UTXD0        | NPCS2        |              |                |                 |                     |

| PA11     | NPCS0        | PWM0         |              | WKUP7          |                 |                     |

| PA12     | MISO         | PWM1         |              |                |                 |                     |

| PA13     | MOSI         | PWM2         |              |                |                 |                     |

| PA14     | SPCK         | PWM3         |              | WKUP8          |                 |                     |

| PA15     |              | TIOA1        |              | WKUP14         |                 |                     |

| PA16     |              | TIOB1        |              | WKUP15         |                 |                     |

| PA17     |              | PCK1         |              | AD0            |                 |                     |

| PA18     |              | PCK2         |              | AD1            |                 |                     |

| PA19     |              |              |              | AD2/WKUP9      |                 |                     |

| PA20     |              |              |              | AD3/WKUP10     |                 |                     |

| PA21     | RXD1         | PCK1         |              | AD8            |                 | 64/100-pin versions |

| PA22     | TXD1         | NPCS3        |              | AD9            |                 | 64/100-pin versions |

| PA23     | SCK1         | PWM0         |              |                |                 | 64/100-pin versions |

| PA24     | RTS1         | PWM1         |              |                |                 | 64/100-pin versions |

| PA25     | CTS1         | PWM2         |              |                |                 | 64/100-pin versions |

| PA26     |              | TIOA2        |              |                |                 | 64/100-pin versions |

| PA27     |              | TIOB2        |              |                |                 | 64/100-pin versions |

| PA28     |              | TCLK1        |              |                |                 | 64/100-pin versions |

| PA29     |              | TCLK2        |              |                |                 | 64/100-pin versions |

| PA30     |              | NPCS2        |              | WKUP11         |                 | 64/100-pin versions |

| PA31     | NPCS1        | PCK2         |              |                |                 | 64/100-pin versions |

### 9.3.2 PIO Controller B Multiplexing

Table 9-3.

Multiplexing on PIO Controller B (PIOB)

| I/O Line | Peripheral A | Peripheral B | Peripheral C | Extra Function | System Function  | Comments            |

|----------|--------------|--------------|--------------|----------------|------------------|---------------------|

| PB0      | PWM0         |              |              | AD4            |                  |                     |

| PB1      | PWM1         |              |              | AD5            |                  |                     |

| PB2      | URXD1        | NPCS2        |              | AD6/WKUP12     |                  |                     |

| PB3      | UTXD1        | PCK2         |              | AD7            |                  |                     |

| PB4      | TWD1         | PWM2         |              |                | TDI              |                     |

| PB5      | TWCK1        |              |              | WKUP13         | TDO/<br>TRACESWO |                     |

| PB6      |              |              |              |                | TMS/SWDIO        |                     |

| PB7      |              |              |              |                | TCK/SWCLK        |                     |

| PB8      |              |              |              |                | XOUT             |                     |

| PB9      |              |              |              |                | XIN              |                     |

| PB10     |              |              |              |                |                  |                     |

| PB11     |              |              |              |                |                  |                     |

| PB12     |              |              |              |                | ERASE            |                     |

| PB13     |              | PCK0         |              | DAC0           |                  | 64/100-pin versions |

| PB14     | NPCS1        | PWM3         |              |                |                  | 64/100-pin versions |

# 9.3.3 PIO Controller C Multiplexing

| I/O Line | Peripheral A | Peripheral B | Peripheral C | Extra Function | System Function | Comments        |

|----------|--------------|--------------|--------------|----------------|-----------------|-----------------|

| PC0      |              |              |              |                |                 | 100-pin version |

| PC1      |              |              |              |                |                 | 100-pin version |

| PC2      |              |              |              |                |                 | 100-pin version |

| PC3      |              |              |              |                |                 | 100-pin version |

| PC4      |              | NPCS1        |              |                |                 | 100-pin version |

| PC5      |              |              |              |                |                 | 100-pin version |

| PC6      |              |              |              |                |                 | 100-pin version |

| PC7      |              | NPCS2        |              |                |                 | 100-pin version |

| PC8      |              | PWM0         |              |                |                 | 100-pin version |

| PC9      |              | PWM1         |              |                |                 | 100-pin version |

| PC10     |              | PWM2         |              |                |                 | 100-pin version |

| PC11     |              | PWM3         |              |                |                 | 100-pin version |

| PC12     |              |              |              | AD12           |                 | 100-pin version |

| PC13     |              |              |              | AD10           |                 | 100-pin version |

| PC14     |              | PCK2         |              |                |                 | 100-pin version |

| PC15     |              |              |              | AD11           |                 | 100-pin version |

| PC16     |              | PCK0         |              |                |                 | 100-pin version |

| PC17     |              | PCK1         |              |                |                 | 100-pin version |

| PC18     |              | PWM0         |              |                |                 | 100-pin version |

| PC19     |              | PWM1         |              |                |                 | 100-pin version |

| PC20     |              | PWM2         |              |                |                 | 100-pin version |

| PC21     |              | PWM3         |              |                |                 | 100-pin version |

| PC22     |              | PWM0         |              |                |                 | 100-pin version |

| PC23     |              | TIOA3        |              |                |                 | 100-pin version |

| PC24     |              | TIOB3        |              |                |                 | 100-pin version |

| PC25     |              | TCLK3        |              |                |                 | 100-pin version |

| PC26     |              | TIOA4        |              |                |                 | 100-pin version |

| PC27     |              | TIOB4        |              |                |                 | 100-pin version |

| PC28     |              | TCLK4        |              |                |                 | 100-pin version |

| PC29     |              | TIOA5        |              | AD13           |                 | 100-pin version |

| PC30     |              | TIOB5        |              | AD14           |                 | 100-pin version |

| PC31     |              | TCLK5        |              | AD15           |                 | 100-pin version |

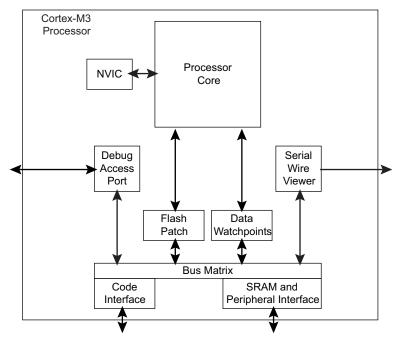

# 10. ARM Cortex® M3 Processor