11-S5-24A Series-072001

# DATA SHEET

S524A Series (I<sup>2</sup>C-Bus) Serial EEPROM Revision 1

# S524A Series (I<sup>2</sup>C-Bus)

# Serial EEPROM DATA SHEET

**Revision 1**

### **Important Notice**

The information in this publication has been carefully checked and is believed to be entirely accurate at the time of publication. Samsung assumes no responsibility, however, for possible errors or omissions, or for any consequences resulting from the use of the information contained herein.

Samsung reserves the right to make changes in its products or product specifications with the intent to improve function or design at any time and without notice and is not required to update this documentation to reflect such changes.

This publication does not convey to a purchaser of semiconductor devices described herein any license under the patent rights of Samsung or others.

Samsung makes no warranty, representation, or guarantee regarding the suitability of its products for any particular purpose, nor does Samsung assume any liability arising out of the application or use of any product or circuit and specifically disclaims any and all liability, including without limitation any consequential or incidental damages. "Typical" parameters can and do vary in different applications. All operating parameters, including "Typicals" must be validated for each customer application by the customer's technical experts.

Samsung products are not designed, intended, or authorized for use as components in systems intended for surgical implant into the body, for other applications intended to support or sustain life, or for any other application in which the failure of the Samsung product could create a situation where personal injury or death may occur.

Should the Buyer purchase or use a Samsung product for any such unintended or unauthorized application, the Buyer shall indemnify and hold Samsung and its officers, employees, subsidiaries, affiliates, and distributors harmless against all claims, costs, damages, expenses, and reasonable attorney fees arising out of, either directly or indirectly, any claim of personal injury or death that may be associated with such unintended or unauthorized use, even if such claim alleges that Samsung was negligent regarding the design or manufacture of said product.

#### S524A Series (I<sup>2</sup>C Bus) Serial EEPROM Data Sheet, Revision 1 Publication Number: 11-S5-24A Series-072001

© 2001 Samsung Electronics

All rights reserved. No part of this publication may be reproduced, stored in a retrieval system, or transmitted in any form or by any means, electric or mechanical, by photocopying, recording, or otherwise, without the prior written consent of Samsung Electronics.

Samsung Electronics' microcontroller business has been awarded full ISO-14001 certification (BSI Certificate No. FM24653). All semiconductor products are designed and manufactured in accordance with the highest quality standards and objectives.

Samsung Electronics Co., Ltd. San #24 Nongseo-Lee, Kiheung-Eup Yongin-City, Kyunggi-Do, Korea C.P.O. Box #37, Suwon 449-900

TEL: (82)-(31)-209-6530 FAX: (82)-(31)-209-6547 Home-Page URL: Http://www.samsungsemi.com

Printed in the Republic of Korea

Serial EEPROM Selection Guide \$524A40X10/40X20/40X40 \$524A40X11/40X21/40X41/60X81/60X51 \$524AB0X91/B0XB1

S524AD0XD1/D0XF1

S524AE0XH1

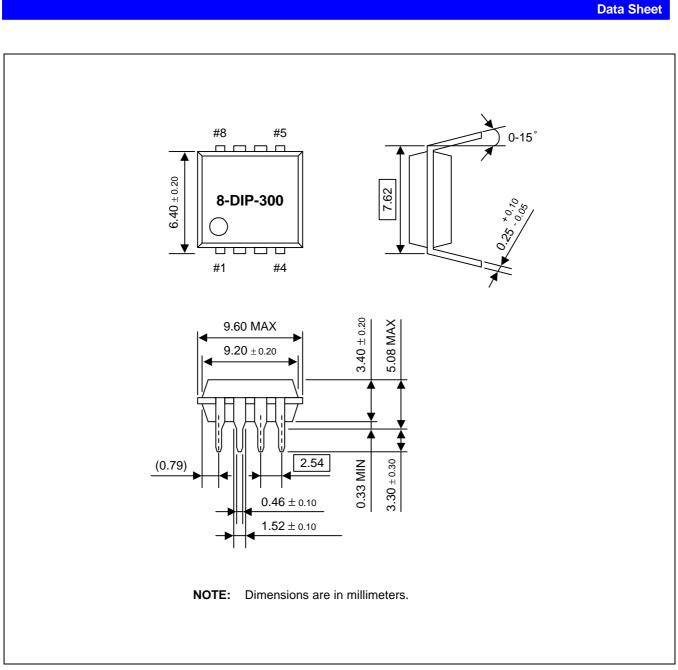

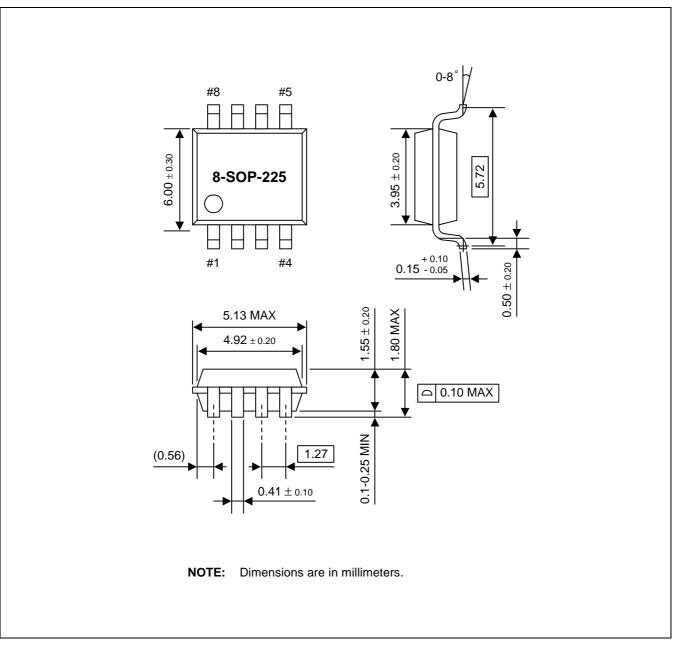

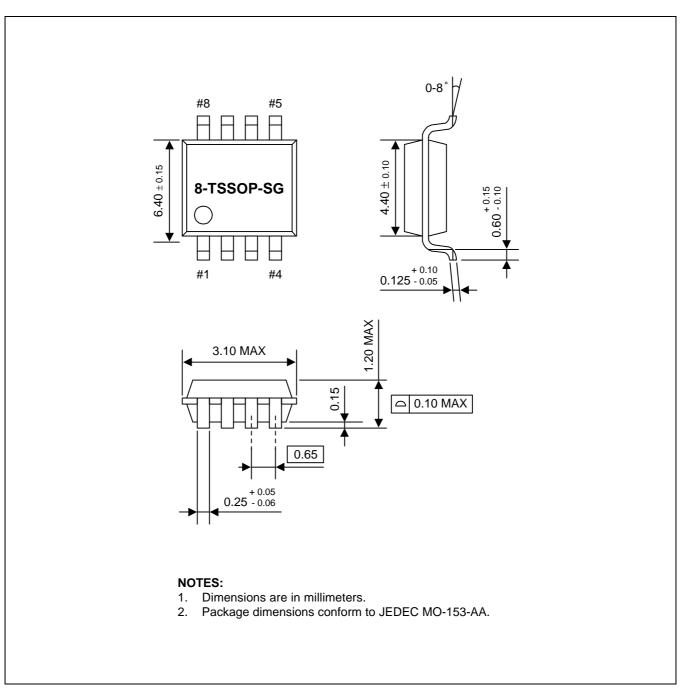

**Packaging Information**

**Application Note**

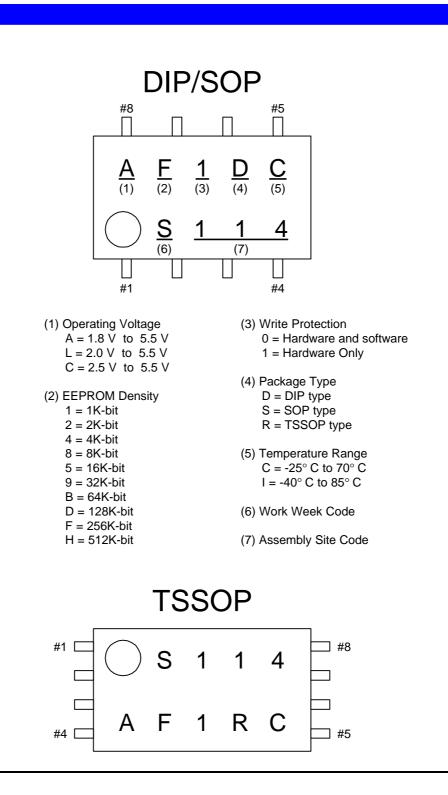

**Marking Information**

**Ordering Information**

# Serial EEPROM Selection Guide

Data Sheet

| Product    | Density<br>(Organization) | Page<br>Buffer | Write<br>Time<br>(Max) | Write<br>Protect | Endurance | Operating<br>Voltage | Package        |

|------------|---------------------------|----------------|------------------------|------------------|-----------|----------------------|----------------|

| S524A40X11 | 1K-bit (128 × 8)          | 16 bytes       | 5 ms                   | H/W              | 1M        | 1.8V–5.5V            | 8DIP/SOP/TSSOP |

| S524A40X10 | 1K-bit (128 × 8)          | 16 bytes       | 5 ms                   | H/W, S/W         | 1M        | 1.8V–5.5V            | 8DIP/SOP/TSSOP |

| S524A40X21 | 2K-bit (256 × 8)          | 16 bytes       | 5 ms                   | H/W              | 1M        | 1.8V–5.5V            | 8DIP/SOP/TSSOP |

| S524A40X20 | 2K-bit (256 × 8)          | 16 bytes       | 5 ms                   | H/W, S/W         | 1M        | 1.8V–5.5V            | 8DIP/SOP/TSSOP |

| S524A40X41 | 4K-bit (512 × 8)          | 16 bytes       | 5 ms                   | H/W              | 1M        | 1.8V–5.5V            | 8DIP/SOP/TSSOP |

| S524A40X40 | 4K-bit (512 × 8)          | 16 bytes       | 5 ms                   | H/W, S/W         | 1M        | 1.8V–5.5V            | 8DIP/SOP/TSSOP |

| S524A60X81 | 8K-bit (1024 × 8)         | 16 bytes       | 5 ms                   | H/W              | 1M        | 1.8V–5.5V            | 8DIP/SOP/TSSOP |

| S524A60X51 | 16K-bit (2048 × 8)        | 16 bytes       | 5 ms                   | H/W              | 1M        | 1.8V–5.5V            | 8DIP/SOP/TSSOP |

| S524AB0X91 | 32K-bit (4096 × 8)        | 32 bytes       | 5 ms                   | H/W              | 1M        | 1.8V–5.5V            | 8DIP/SOP/TSSOP |

| S524AB0XB1 | 64K-bit (8192 × 8)        | 32 bytes       | 5 ms                   | H/W              | 1M        | 1.8V–5.5V            | 8DIP/SOP/TSSOP |

| S524AD0XD1 | 128K-bit<br>(16384 × 8)   | 64 bytes       | 5 ms                   | H/W              | 500K      | 1.8V–5.5V            | 8DIP/TSSOP     |

| S524AD0XF1 | 256K-bit<br>(32768 × 8)   | 64 bytes       | 5 ms                   | H/W              | 500K      | 1.8V–5.5V            | 8DIP/TSSOP     |

#### SERIAL EEPROM SELECTION GUIDE

NOTES

## S524A40X10/40X20/40X40

#### 1K/2K/4K-bit Serial EEPROM for Low Power

Data Sheet

#### OVERVIEW

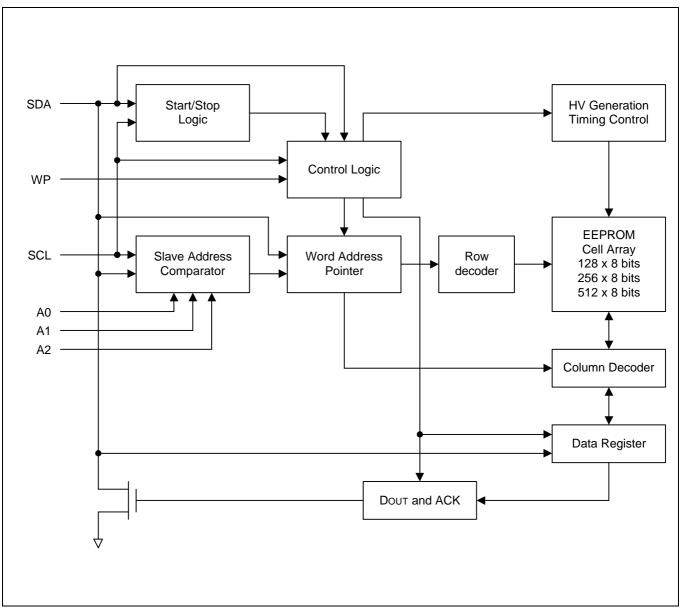

The S524A40X10/40X20/40X40 serial EEPROM has a 1,024/2,048/4,096-bit (128/256/512-byte) capacity, supporting the standard I<sup>2</sup>C<sup>TM</sup>-bus serial interface. It is fabricated using Samsung's most advanced CMOS technology. It has been developed for low power and low voltage applications (1.8 V to 5.5 V). Important features are a hardware-based write protection circuit for the entire memory area and software-based write protection logic for the lower 128 bytes. Hardware-based write protection is controlled by the state of the write-protect (WP) pin. The software-based method is one-time programmable and permanent. Using one-page write mode, you can load up to 16 bytes of data into the EEPROM in a single write operation. Another significant feature of the S524A40X10/40X20/40X40 is its support for fast mode and standard mode.

#### **FEATURES**

#### I<sup>2</sup>C-Bus Interface

- Two-wire serial interface

- Automatic word address increment

#### EEPROM

- 1K/2K/4K-bit (128/256/512-byte) storage area

- 16-byte page buffer

- Hardware-based write protection for the entire EEPROM (using the WP pin)

- Software-based write protection for the lower 128-byte EEPROM

- EEPROM programming voltage generated on chip

- 1,000,000 erase/write cycles

- 100 years data retention

#### **Operating Characteristics**

- Operating voltage

- 1.8 V to 5.5 V

- Operating current

- Maximum write current: < 3 mA at 5.5 V</li>

- Maximum read current: < 200 μA at 5.5 V

- Maximum stand-by current: < 5 μA at 5.5 V

- Operating temperature range

- - 25°C to + 70°C (commercial)

- - 40°C to + 85°C (industrial)

- Operating clock frequencies

- 100 kHz at standard mode

- 400 kHz at fast mode

- Electrostatic discharge (ESD)

- 5,000 V (HBM)

- 500 V (MM)

#### Packages

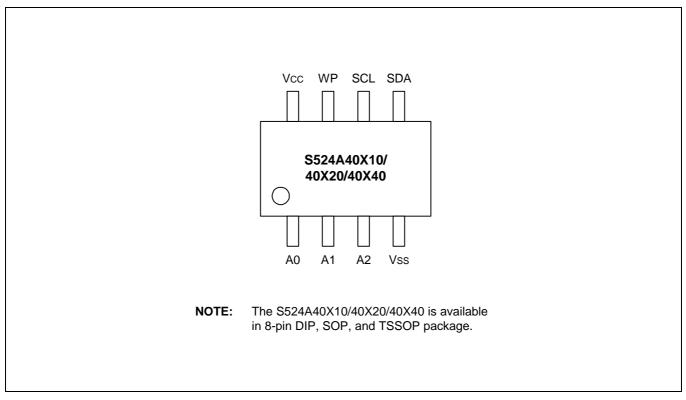

8-pin DIP, SOP, and TSSOP

Figure 2-1. S524A40X10/40X20/40X40 Block Diagram

#### Figure 2-2. Pin Assignment Diagram

| Name            | Туре  | Description                                                                                                                                                                                                                                                                              | Circuit<br>Type |

|-----------------|-------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------|

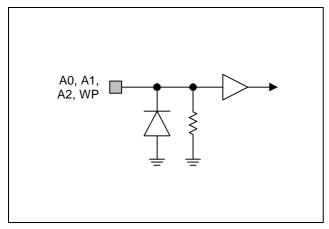

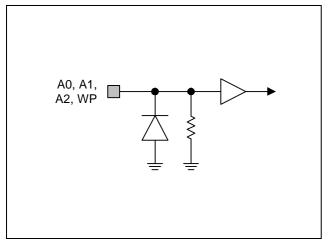

| A0, A1, A2      | Input | Input pins for device address selection. To configure a device address, these pins should be connected to the V <sub>CC</sub> or V <sub>SS</sub> of the device. These pins are internally pulled down to V <sub>SS</sub> .                                                               | 1               |

| V <sub>SS</sub> | -     | Ground pin.                                                                                                                                                                                                                                                                              | _               |

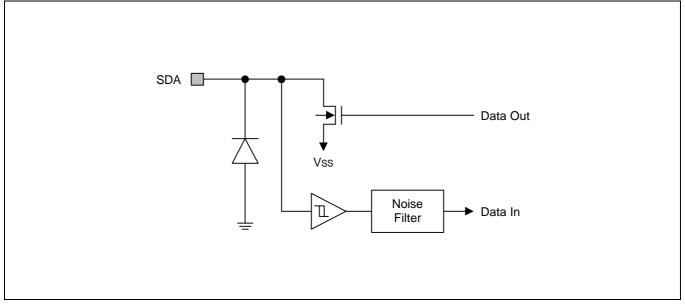

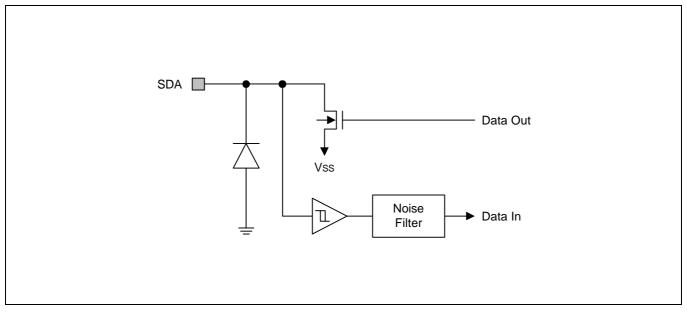

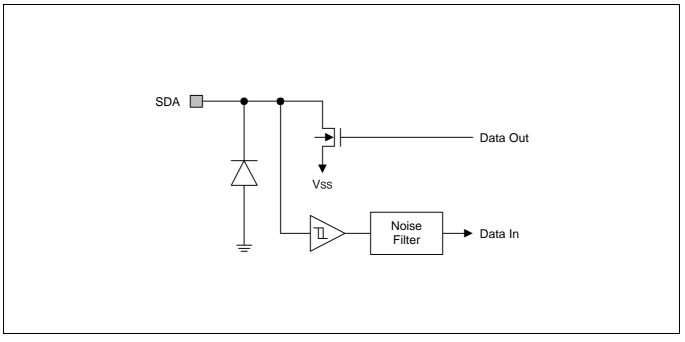

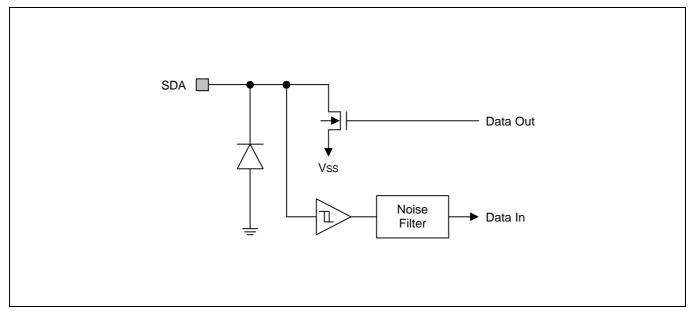

| SDA             | I/O   | Bi-directional data pin for the I <sup>2</sup> C-bus serial data interface. Schmitt trigger input and open-drain output. An external pull-up resistor must be connected to $V_{CC.}$ Typical values for this pull-up resistor are 4.7 k $\Omega$ (100 kHz) and 1 k $\Omega$ (400 kHz).   | 3               |

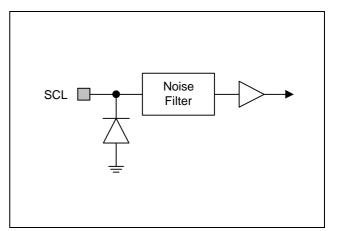

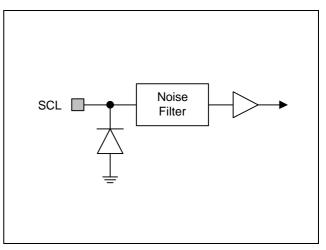

| SCL             | Input | Schmitt trigger input pin for serial clock input.                                                                                                                                                                                                                                        | 2               |

| WP              | Input | Input pin for hardware write protection control. If you tie this pin to $V_{CC,}$ the write function is disabled to protect previously written data in the entire memory; if you tie it to $V_{SS}$ , the write function is enabled.<br>This pin is internally pulled down to $V_{SS}$ . | 1               |

| V <sub>CC</sub> | _     | Single power supply.                                                                                                                                                                                                                                                                     | _               |

**NOTE**: See the following page for diagrams of pin circuit types 1, 2, and 3.

Figure 2-4. Pin Circuit Type 2

Figure 2-5. Pin Circuit Type 3

#### **FUNCTION DESCRIPTION**

#### I<sup>2</sup>C-BUS INTERFACE

The S524A40X10/40X20/40X40 supports the l<sup>2</sup>C-bus serial interface data transmission protocol. The two-wire bus consists of a serial data line (SDA) and a serial clock line (SCL). The SDA and the SCL lines must be connected to  $V_{CC}$  by a pull-up resistor that is located somewhere on the bus.

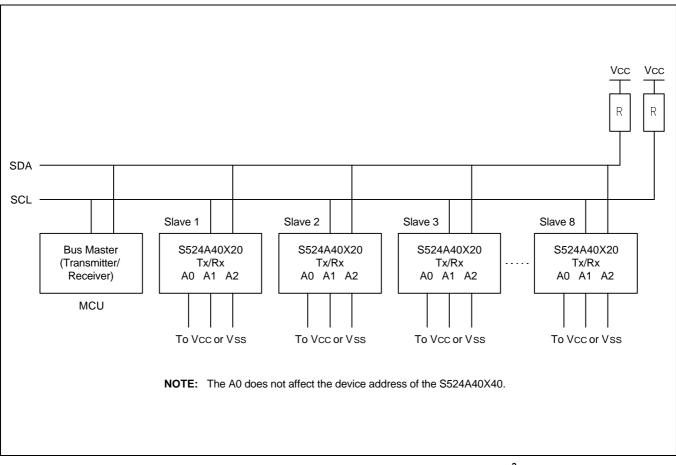

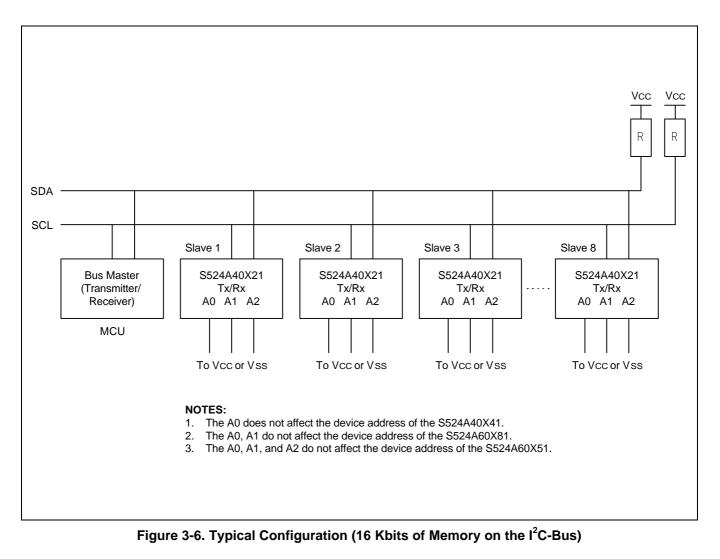

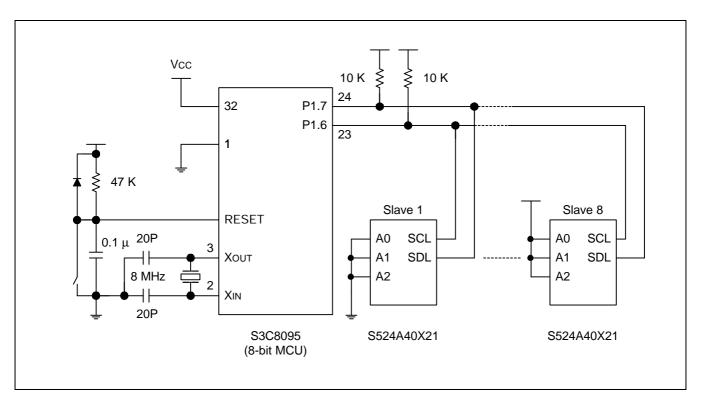

Any device that puts data onto the bus is defined as the "transmitter" and any device that gets data from the bus is the "receiver." The bus is controlled by a master device which generates the serial clock and start/stop conditions, controlling bus access. Using the A0,A1 and A2 input pins, up to eight S524A40X10/40X20 (four for S524A40X40) devices can be connected to the same I<sup>2</sup>C-bus as slaves (see Figure 2-6). Both the master and slaves can operate as transmitter or receiver, but the master device determines which bus operating mode would be active.

Figure 2-6. Typical Configuration (16 Kbits of Memory on the I<sup>2</sup>C-Bus)

#### **I<sup>2</sup>C-BUS PROTOCOLS**

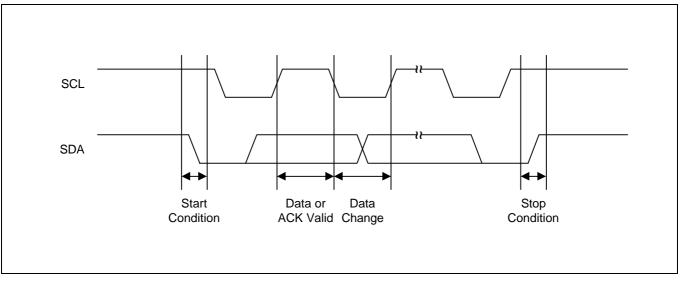

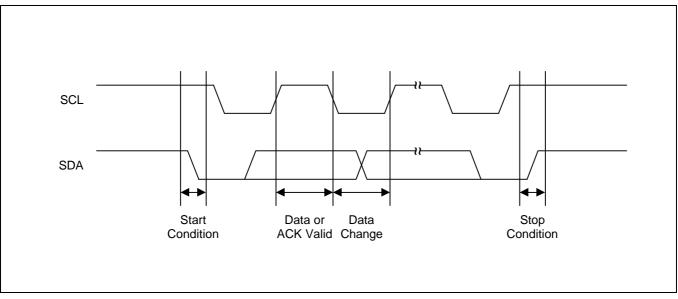

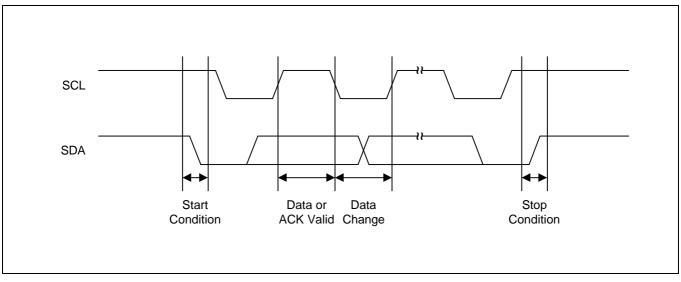

Here are several rules for I<sup>2</sup>C-bus transfers:

- A new data transfer can be initiated only when the bus is currently not busy.

- MSB is always transferred first in transmitting data.

- During a data transfer, the data line (SDA) must remain stable whenever the clock line (SCL) is High.

The I<sup>2</sup>C-bus interface supports the following communication protocols:

- Bus not busy: The SDA and the SCL lines remain High level when the bus is not active.

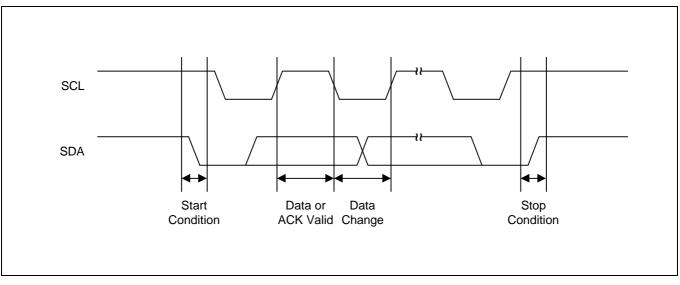

- <u>Start condition</u>: Start condition is initiated by a High-to-Low transition of the SDA line while SCL remains High level. All bus commands must be preceded by a start condition.

- <u>Stop condition</u>: A stop condition is initiated by a Low-to-High transition of the SDA line while SCL remains High level. All bus operations must be completed by a stop condition (see Figure 2-7).

Figure 2-7. Data Transmission Sequence

- <u>Data valid</u>: Following a start condition, the data becomes valid if the data line remains stable for the duration of the High period of SCL. New data must be put onto the bus while SCL is Low. Bus timing is one clock pulse per data bit. The number of data bytes to be transferred is determined by the master device. The total number of bytes that can be transferred in one operation is theoretically unlimited.

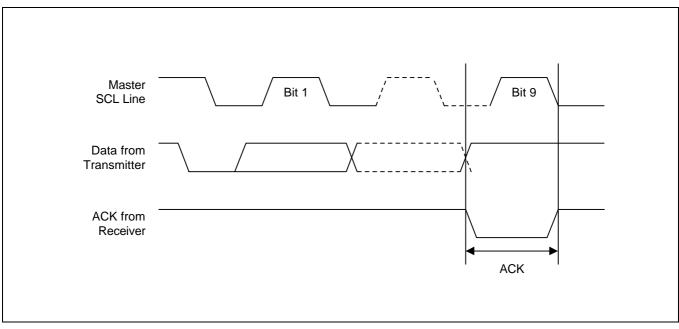

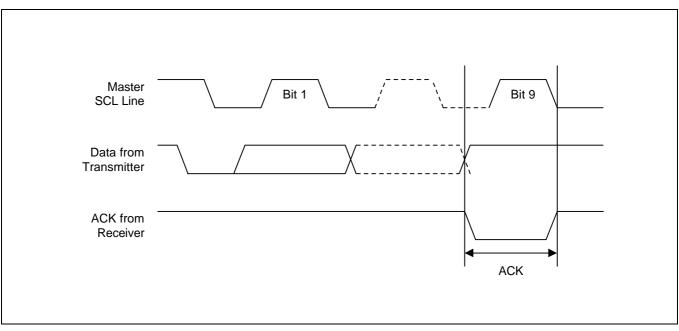

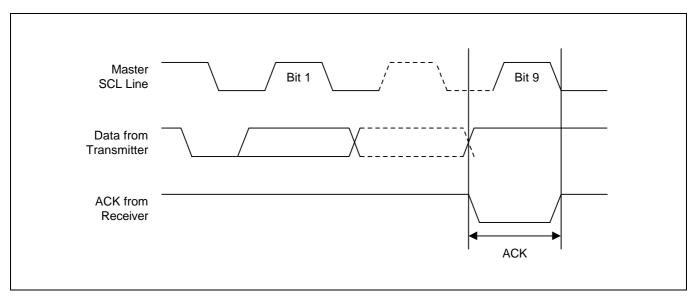

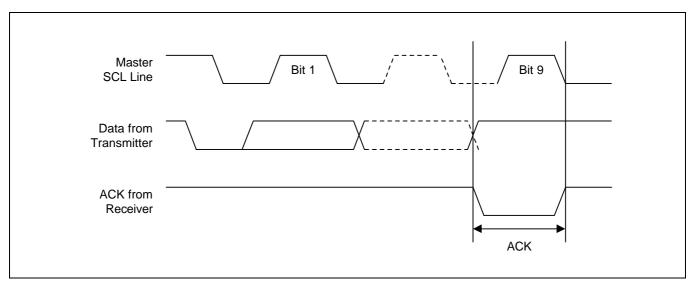

- <u>ACK (Acknowledge)</u>: An ACK signal indicates that a data transfer is completed successfully. The transmitter (the master or the slave) releases the bus after transmitting eight bits. During the 9th clock, which the master generates, the receiver pulls the SDA line low to acknowledge that it successfully received the eight bits of data (see Figure 2-8). But the slave does not send an ACK if an internal write cycle is still in progress.

In data read operations, the slave releases the SDA line after transmitting 8 bits of data and then monitors the line for an ACK signal during the 9th clock period. If an ACK is detected, the slave will continue to transmit data. If an ACK is not detected, the slave terminates data transmission and waits for a stop condition to be issued by the master before returning to its stand-by mode.

Figure 2-8. Acknowledge Response From Receiver

- <u>Slave Address</u>: After the master initiates a Start condition, it must output the address of the device to be accessed. The most significant four bits of the slave address are called the "device identifier". The identifier for the S524A40X10/40X20/40X40 is "1010B". The next three bits comprise the address of a specific device. The device address is defined by the state of the A0, A1 and A2 pins. Using this addressing scheme, you can cascade up to eight S524A40X10/40X20 or four S524A40X40 on the bus (see Table 2-2 below). The b1 for S524A40X40 is used by the master to select which of the blocks of internal memory (1 block = 256 words) are to be accessed. The bit is in effect the most significant bit of the word address.

- <u>Read/Write</u>: The final (eighth) bit of the slave address defines the type of operation to be performed. If the R/W bit is "1", a read operation is executed. If it is "0", a write operation is executed.

| Function      | De | vice I | dentif | ier | Γ  | R/W Bit |                      |    |

|---------------|----|--------|--------|-----|----|---------|----------------------|----|

|               | b7 | b6     | b5     | b4  | b3 | b2      | b1 <sup>(note)</sup> | b0 |

| Read          | 1  | 0      | 1      | 0   | A2 | A1      | A0                   | 1  |

| Write         | 1  | 0      | 1      | 0   | A2 | A1      | A0                   | 0  |

| Write-protect | 0  | 1      | 1      | 0   | A2 | A1      | A0                   | 0  |

| Table 2-2. | Slave Device | Addressing |

|------------|--------------|------------|

|------------|--------------|------------|

**NOTE:** The b1 for S524A40X40 corresponds to the MSB of the memory array address word.

#### BYTE WRITE OPERATION

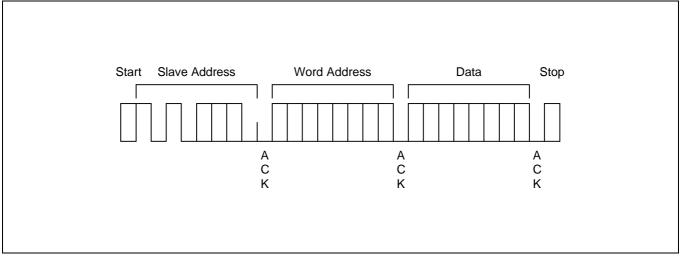

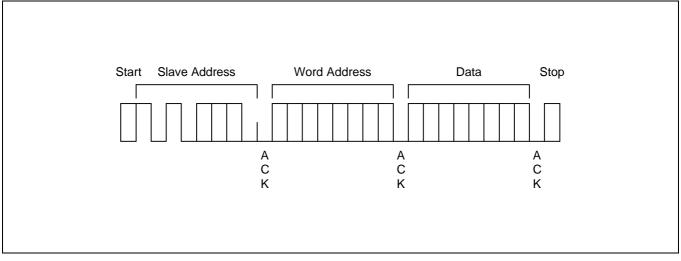

In a complete byte write operation, the master transmits the slave address, word address, and one data byte to the S524A40X10/40X20/40X40 slave device (see Figure 2-9).

Figure 2-9. Byte Write Operation

Following the Start condition, the master sends the device identifier (4 bits), the device address (3 bits), and an R/W bit set to "0" onto the bus. Then the addressed S524A40X10/40X20/40X40 generates an ACK and waits for the next byte. The next byte to be transmitted by the master is the word address. This 8-bit address is written into the word address pointer of the S524A40X10/40X20/40X40.

When the S524A40X10/40X20/40X40 receives the word address, it responds by issuing an ACK and then waits for the next 8-bit data. When it receives the data byte, the S524A40X10/40X20/40X40 again responds with an ACK. The master terminates the transfer by generating a Stop condition, at which time the S524A40X10/40X20/40X40 begins the internal write cycle.

While the internal write cycle is in progress, all S524A40X10/40X20/40X40 inputs are disabled and the S524A40X10/40X20/40X40 does not respond to additional requests from the master.

#### PAGE WRITE OPERATION

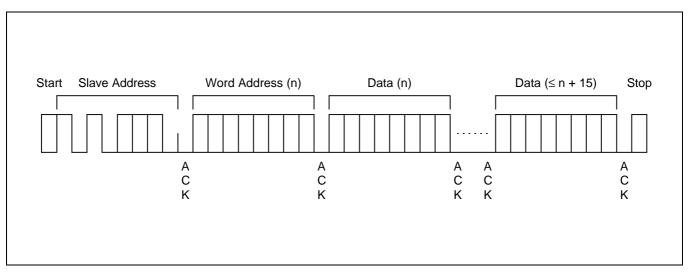

The S524A40X10/40X20/40X40 can also perform 16-byte page write operation. A page write operation is initiated in the same way as a byte write operation. However, instead of finishing the write operation after the first data byte is transferred, the master can transmit up to 15 additional bytes. The S524A40X10/40X20/40X40 responds with an ACK each time it receives a complete byte of data (see Figure 2-10).

Figure 2-10. Page Write Operation

The S524A40X10/40X20/40X40 automatically increments the word address pointer each time it receives a complete data byte. When one byte has been received, the internal word address pointer increments to the next address and the next data byte can be received.

If the master transmits more than 16 bytes before it generates a stop condition to end the page write operation, the S524A40X10/40X20/40X40 word address pointer value "rolls over" and the previously received data is overwritten. If the master transmits less than 16 bytes and generates a stop condition, the S524A40X10/40X20/40X40 writes the received data to the corresponding EEPROM address.

During a page write operation, all inputs are disabled and there is no response to additional requests from the master until the internal write cycle is completed.

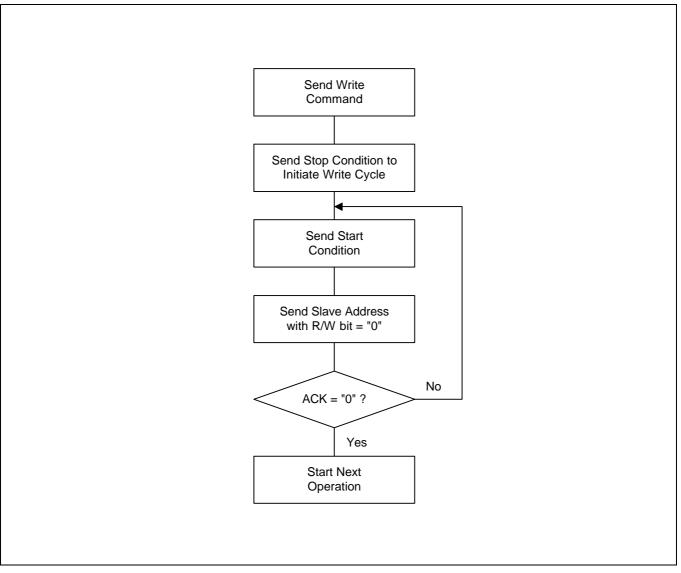

#### POLLING FOR AN ACK SIGNAL

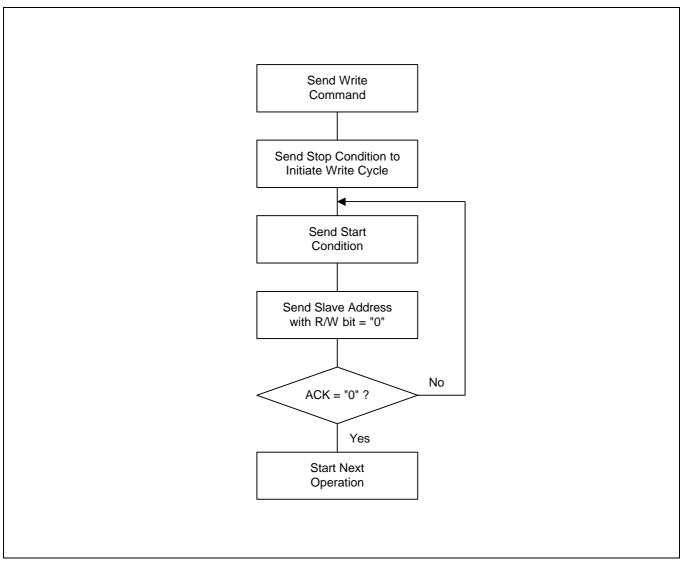

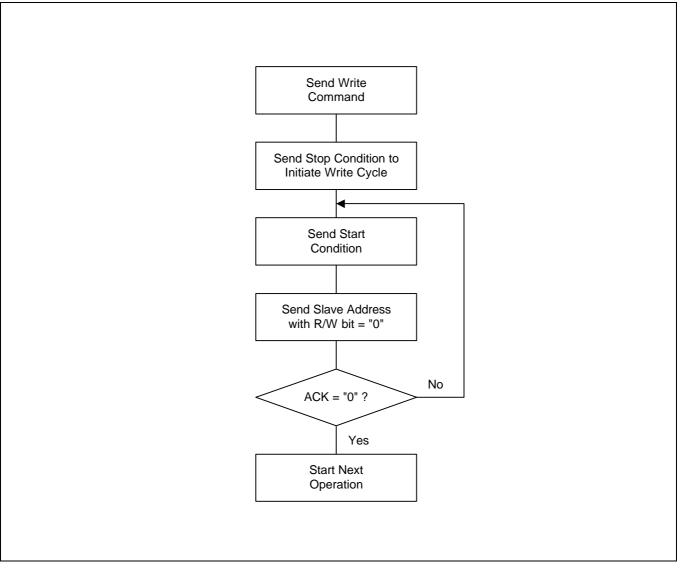

When the master issues a stop condition to initiate a write cycle, the S524A40X10/40X20/40X40 starts an internal write cycle. The master can then immediately begin polling for an ACK from the slave device.

To poll for an ACK signal in a write operation, the master issues a start condition followed by the slave address. As long as the S524A40X10/40X20/40X40 remains busy with the write operation, no ACK is returned. When the S524A40X10/40X20/40X40 completes the write operation, it returns an ACK and the master can then proceed with the next read or write operation (see Figure 2-11).

Figure 2-11. Master Polling for an ACK Signal from a Slave Device

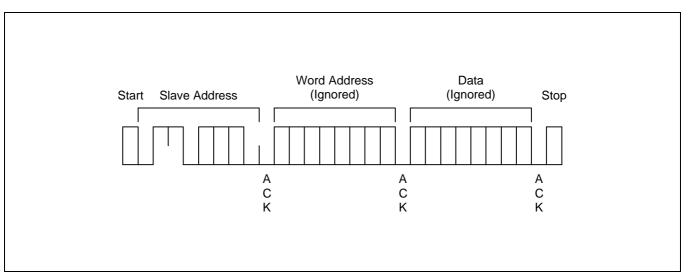

#### SOFTWARE-BASED WRITE PROTECTION

You can write-protect the lower 128 bytes of the EEPROM, locations 00H–7FH, in one operation. To do this, you simply write a value to a one-time, write-only register. Once you have applied this write protection, any write attempt to access the lower 128-byte area is ignored. In other words, the write protection is permanent. The effect of such a failed attempt is processed in the same way as an invalid I<sup>2</sup>C-bus protocol.

To enable write protection, you must execute a write operation to the write protection register. To access the write protection register, you use the device address "0110". The word address and data in this write operation can be any value and the timing and wave form characteristics are identical to a normal byte write operation (see Figure 2-12).

Figure 2-12. Write Protection Operation

#### HARDWARE-BASED WRITE PROTECTION

You can also write-protect the entire memory area of the S524A40X10/40X20/40X40. This method of write protection is controlled by the state of the Write Protect (WP) pin.

When the WP pin is connected to  $V_{CC}$ , any attempt to write a value to the memory is ignored.

The S524A40X10/40X20/40X40 will acknowledge slave and word address, but it will not generate an acknowledge after receiving the first byte of the data. Thus the write cycle will not be started when the stop condition is generated. By connecting the WP pin to  $V_{SS}$ , the write function is allowed for the entire memory.

These write protection features effectively change the EEPROM to a ROM in order to prevent data from being overwritten. Whenever the write function is disabled, a slave address and a word address are acknowledged on the bus, but data bytes are not acknowledged.

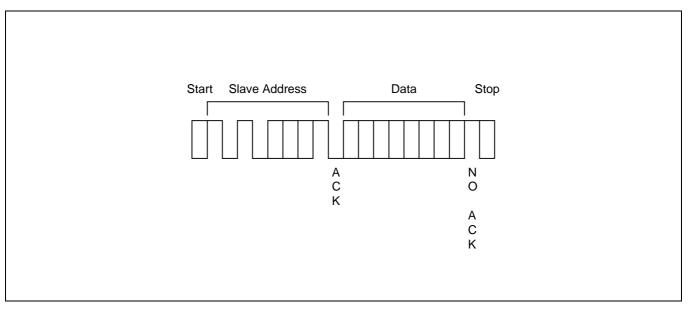

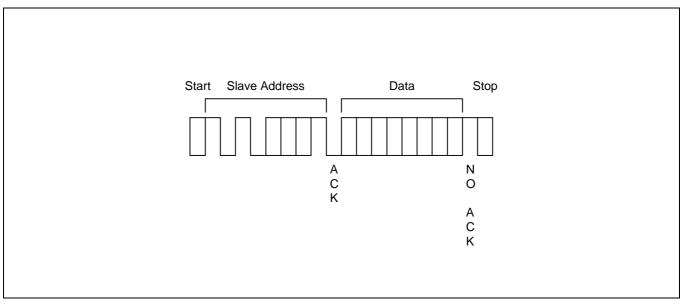

#### **CURRENT ADDRESS BYTE READ OPERATION**

The internal word address pointer maintains the address of the last word accessed, incremented by one. Therefore, if the last access (either read or write) was to the address "n", the next read operation would access data at address "n+1".

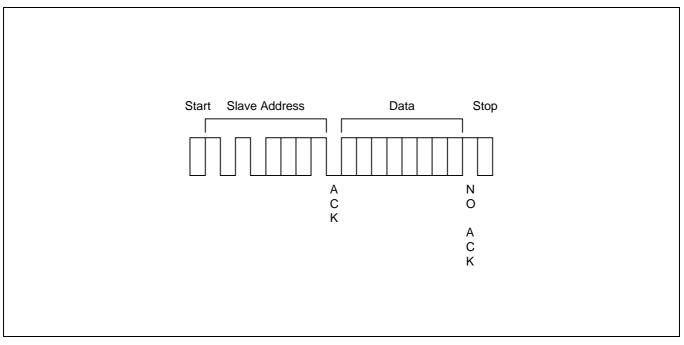

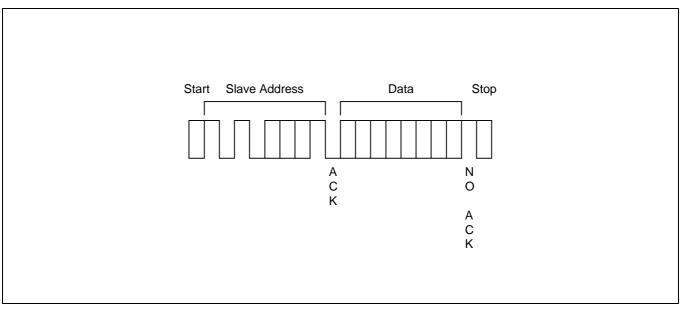

When the S524A40X10/40X20/40X40 receives a slave address with the R/W bit set to "1", it issues an ACK and sends the eight bits of data. The master does not acknowledge the transfer but it does generate a Stop condition. In this way, the S524A40X10/40X20/40X40 effectively stops the transmission (see Figure 2-13).

Figure 2-13. Current Address Byte Read Operation

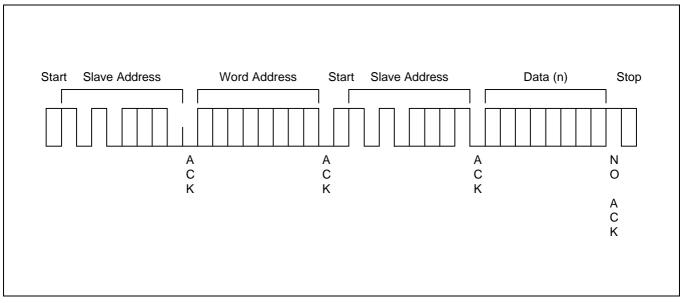

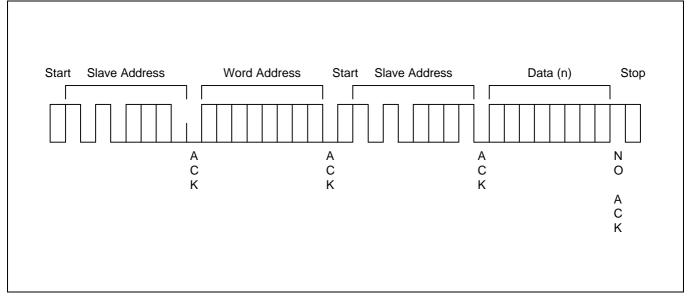

#### RANDOM ADDRESS BYTE READ OPERATION

Using random read operations, the master can access any memory location at any time. Before it issues the slave address with the R/W bit set to "1", the master must first perform a "dummy" write operation. This operation is performed in the following steps:

- 1. The master first issues a Start condition, the slave address, and the word address to be read. (This step sets the internal word address pointer of the S524A40X10/40X20/40X40 to the desired address.)

- 2. When the master receives an ACK for the word address, it immediately re-issues a start condition followed by another slave address, with the R/W bit set to "1".

- 3. The S524A40X10/40X20/40X40 then sends an ACK and the 8-bit data stored at the desired address.

- 4. At this point, the master does not acknowledge the transmission, but generates a stop condition instead.

- In response, the S524A40X10/40X20/40X40 stops transmitting data and reverts to its stand-by mode (see Figure 2-14).

Figure 2-14. Random Address Byte Read Operation

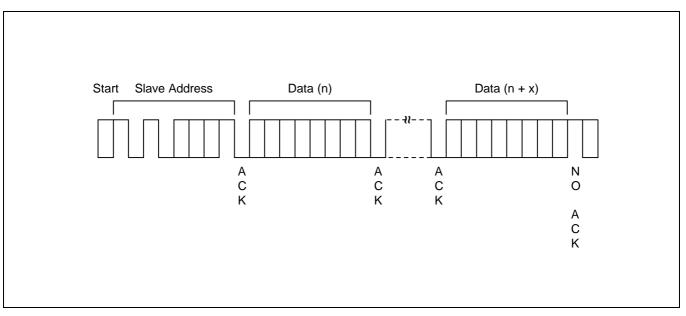

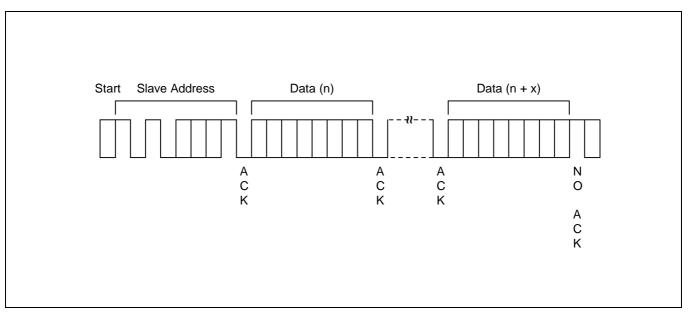

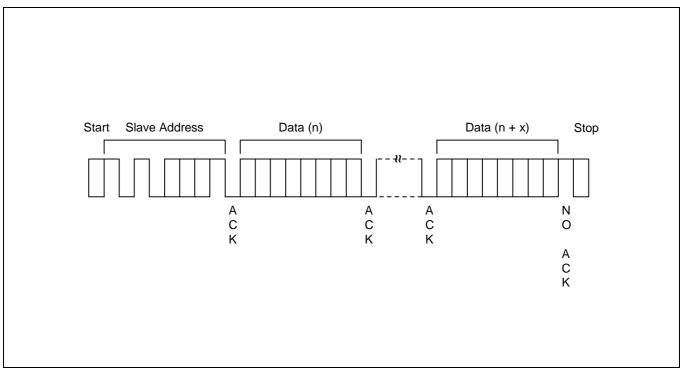

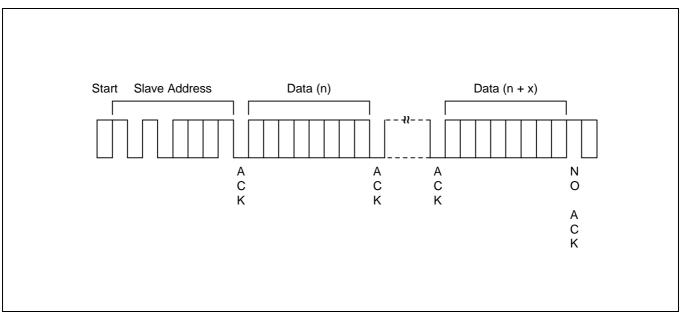

#### SEQUENTIAL READ OPERATION

Sequential read operations can be performed in two ways: as a series of current address reads or as random address reads. The first data is sent in the same way as the previous read mode used on the bus. The next time, however, the master responds with an ACK, indicating that it requires additional data.

The S524A40X10/40X20/40X40 continues to output data for each ACK it receives. To stop the sequential read operation, the master does not respond with an ACK, but instead issues a Stop condition.

Using this method, data is output sequentially with the data from address "n" followed by the data from "n+1". The word address pointer for read operations increments all word addresses, allowing the entire EEPROM to be read sequentially in a single operation. After the entire EEPROM is read, the word address pointer "rolls over" and the S524A40X10/40X20/40X40 continues to transmit data for each ACK it receives from the master (see Figure 2-15).

Figure 2-15. Sequential Read Operation

#### ELECTRICAL DATA

#### Table 2-3. Absolute Maximum Ratings

#### $(T_A = 25^{\circ}C)$

| Parameter               | Symbol           | Conditions | Rating         | Unit |

|-------------------------|------------------|------------|----------------|------|

| Supply voltage          | V <sub>CC</sub>  | _          | - 0.3 to + 7.0 | V    |

| Input voltage           | V <sub>IN</sub>  | -          | - 0.3 to + 7.0 | V    |

| Output voltage          | Vo               | _          | - 0.3 to + 7.0 | V    |

| Operating temperature   | T <sub>A</sub>   | _          | - 40 to + 85   | °C   |

| Storage temperature     | T <sub>STG</sub> | _          | - 65 to + 150  | °C   |

| Electrostatic discharge | V <sub>ESD</sub> | HBM        | 5000           | V    |

|                         |                  | MM         | 500            |      |

#### Table 2-4. D.C. Electrical Characteristics

| Parame             | eter    | Symbol           | Conditions                                         | Min                 | Тур | Max                 | Unit |

|--------------------|---------|------------------|----------------------------------------------------|---------------------|-----|---------------------|------|

| Input low voltage  |         | V <sub>IL</sub>  | SCL, SDA, A0, A1, A2                               | _                   | _   | 0.3 V <sub>CC</sub> | V    |

| Input high voltage | ge      | V <sub>IH</sub>  |                                                    | 0.7 V <sub>CC</sub> | -   | -                   | V    |

| Input leakage cu   | urrent  | ILI              | $V_{IN} = 0$ to $V_{CC}$                           | -                   | _   | 10                  | μA   |

| Output leakage     | current | I <sub>LO</sub>  | $V_0 = 0$ to $V_{CC}$                              | -                   | _   | 10                  | μA   |

| Output low voltage |         | V <sub>OL</sub>  | $I_{OL} = 0.15 \text{ mA}, V_{CC} = 1.8 \text{ V}$ | -                   | _   | 0.2                 | V    |

|                    |         |                  | $I_{OL} = 2.1 \text{ mA}, V_{CC} = 2.5 \text{ V}$  | -                   | _   | 0.4                 |      |

| Supply current     | Write   | I <sub>CC1</sub> | V <sub>CC</sub> = 5.5 V, 400 kHz                   | -                   | _   | 3                   | mA   |

|                    |         | I <sub>CC2</sub> | V <sub>CC</sub> = 1.8 V, 100 kHz                   | -                   | -   | 1                   |      |

|                    | Read    | I <sub>CC3</sub> | V <sub>CC</sub> = 5.5 V, 400 kHz                   | -                   | -   | 0.2                 |      |

|                    |         | I <sub>CC4</sub> | V <sub>CC</sub> = 1.8 V, 100 kHz                   | -                   | -   | 60                  | μA   |

| Stand-by curren    | t       | I <sub>CC5</sub> | $V_{CC} = SDA = SCL = 5.5 V,$                      | -                   | _   | 5                   | μA   |

|                    |         |                  | all other inputs = $0 V$                           |                     |     |                     |      |

|                    |         | I <sub>CC6</sub> | V <sub>CC</sub> = SDA = SCL = 1.8 V,               | -                   | _   | 1                   |      |

|                    |         |                  | all other inputs = $0 V$                           |                     |     |                     |      |

$(T_A = -25^{\circ}C \text{ to } + 70^{\circ}C \text{ (C)}, -40^{\circ}C \text{ to } + 85^{\circ}C \text{ (I)}, V_{CC} = 1.8 \text{ V to } 5.5 \text{ V})$

#### Table 2-4. D.C. Electrical Characteristics (Continued)

| Parameter                | Symbol           | Conditions                                                                                           | Min | Тур | Max | Unit |

|--------------------------|------------------|------------------------------------------------------------------------------------------------------|-----|-----|-----|------|

| Input capacitance        | C <sub>IN</sub>  | $25^{\circ}$ C, 1MHz,<br>V <sub>CC</sub> = 5 V, V <sub>IN</sub> = 0 V,<br>A0, A1, A2, SCL and WP pin | _   | _   | 10  | pF   |

| Input/output capacitance | C <sub>I/O</sub> | 25°C, 1MHz,<br>$V_{CC} = 5 V, V_{I/O} = 0 V,$<br>SDA pin                                             | _   | _   | 10  |      |

#### (T<sub>A</sub> = $-25^{\circ}$ C to + $70^{\circ}$ C (C), $-40^{\circ}$ C to + $85^{\circ}$ C (I), V<sub>CC</sub> = 1.8 V to 5.5 V)

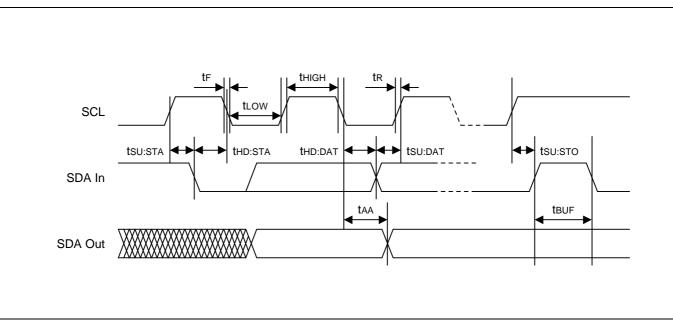

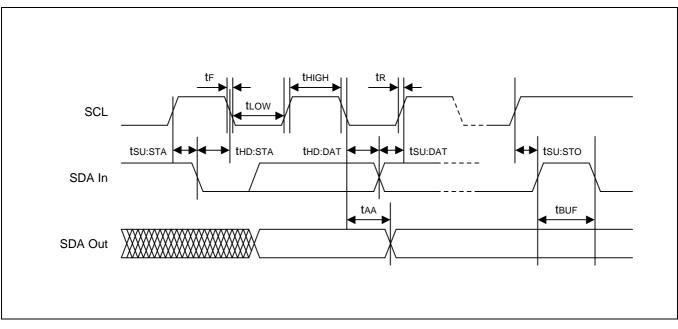

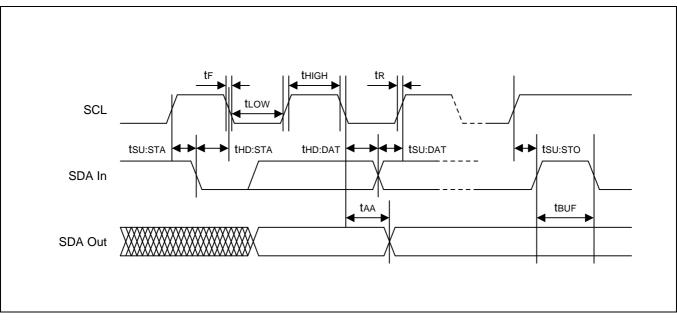

#### Table 2-5. A.C. Electrical Characteristics

$(T_A = -25^{\circ}C \text{ to } + 70^{\circ}C \text{ (C)}, -40^{\circ}C \text{ to } + 85^{\circ}C \text{ (I)}, V_{CC} = 1.8 \text{ V to } 5.5 \text{ V})$

| Parameter                                          | Symbol              | Conditions              | ••   | 3 to 5.5 V<br>d Mode) | V <sub>CC</sub> = 2.5<br>(Fast | Unit |     |

|----------------------------------------------------|---------------------|-------------------------|------|-----------------------|--------------------------------|------|-----|

|                                                    |                     |                         | Min  | Max                   | Min                            | Max  |     |

| External clock frequency                           | F <sub>CLK</sub>    | -                       | 0    | 100                   | 0                              | 400  | kHz |

| Clock high time                                    | t <sub>HIGH</sub>   | -                       | 4    | -                     | 0.6                            | -    | μs  |

| Clock low time                                     | t <sub>LOW</sub>    | -                       | 4.7  | -                     | 1.3                            | -    |     |

| Rising time                                        | t <sub>R</sub>      | SDA, SCL                | _    | 1                     | -                              | 0.3  |     |

| Falling time                                       | t <sub>F</sub>      | SDA, SCL                | _    | 0.3                   | _                              | 0.3  |     |

| Start condition hold time                          | t <sub>HD:STA</sub> | -                       | 4    | _                     | 0.6                            | _    |     |

| Start condition setup time                         | t <sub>SU:STA</sub> | -                       | 4.7  | -                     | 0.6                            | -    |     |

| Data input hold time                               | t <sub>HD:DAT</sub> | -                       | 0    | -                     | 0                              | -    |     |

| Data input setup time                              | t <sub>SU:DAT</sub> | -                       | 0.25 | -                     | 0.1                            | -    |     |

| Stop condition setup time                          | t <sub>SU:STO</sub> | -                       | 4    | -                     | 0.6                            | -    |     |

| Bus free time t <sub>BUF</sub>                     |                     | Before new transmission | 4.7  | _                     | 1.3                            | -    |     |

| Data output valid from clock low <sup>(note)</sup> | t <sub>AA</sub>     | -                       | 0.3  | 3.5                   | _                              | 0.9  |     |

| Noise spike width                                  | t <sub>SP</sub>     | -                       | _    | 100                   | -                              | 50   | ns  |

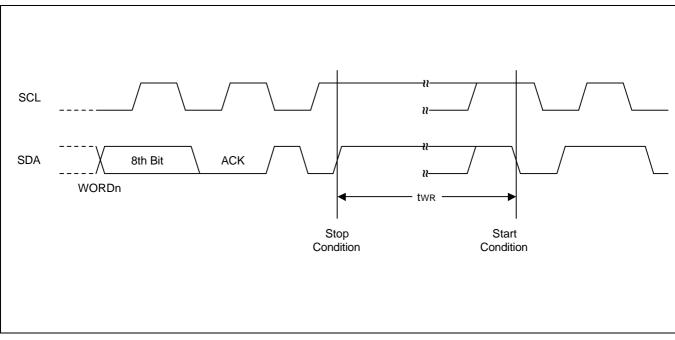

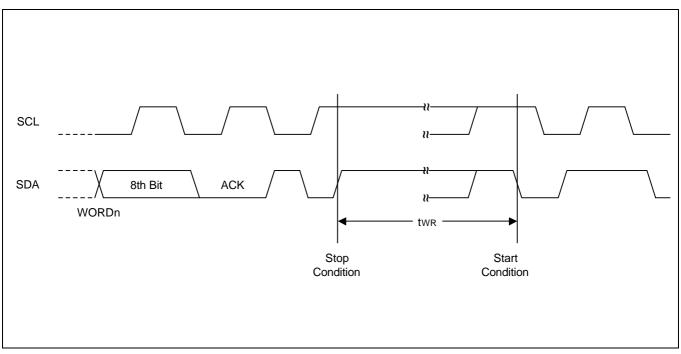

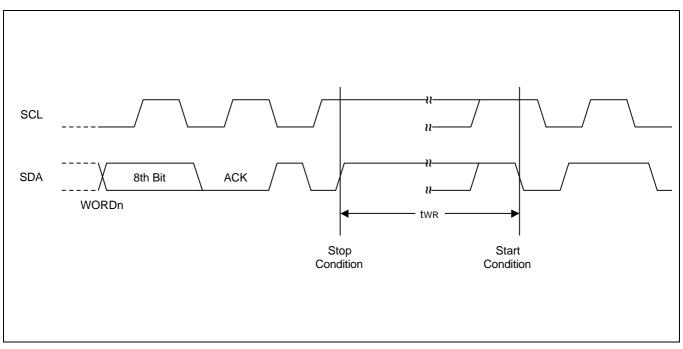

| Write cycle time                                   | t <sub>WR</sub>     | -                       | _    | 5                     | -                              | 5    | ms  |

#### NOTES:

1. Upon customers request, up to 400 kHz (Max.) in standard mode and 1 MHz in fast mode are available.

2. When acting as a transmitter, the S524A40X10/40X20/40X40 must provide an internal minimum delay time to bridge the undefined period (minimum 300 ns) of the falling edge of SCL. This is required to avoid unintended generation of a start or stop condition.

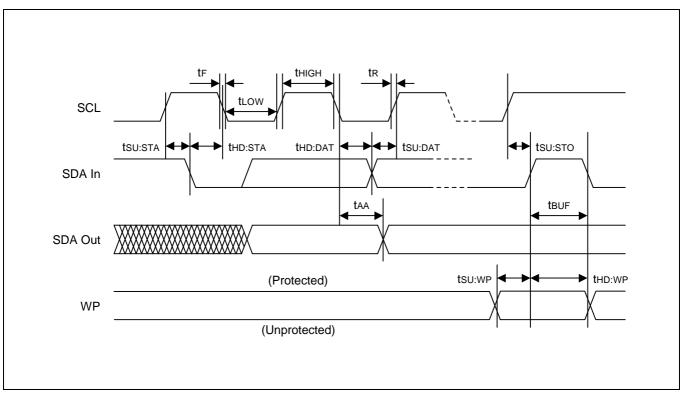

Figure 2-16. Timing Diagram for Bus Operations

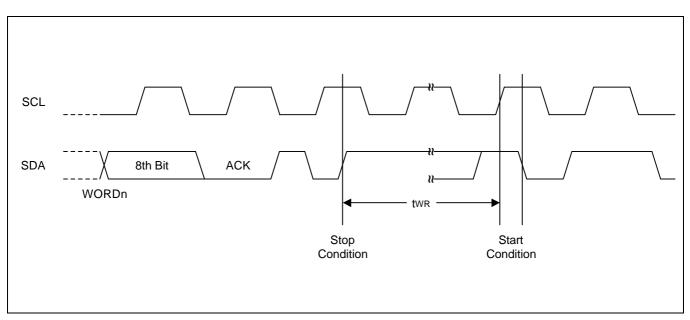

Figure 2-17. Write Cycle Timing Diagram

NOTES

## S524A40X11/40X21/ 40X41/60X81/60X51

1K/2K/4K/8K/16K-bit Serial EEPROM for Low Power

Data Sheet

#### OVERVIEW

The S524A40X11/40X21/40X41/60X81/60X51 serial EEPROM has a 1,024/2,048/4,096/8,192/16,384-bit capacity, supporting the standard  $I^2C^{TM}$ -bus serial interface. It is fabricated using Samsung's most advanced CMOS technology. It has been developed for low power and low voltage applications (1.8 V to 5.5 V). One of its major feature is a hardware-based write protection circuit for the entire memory area. Hardware-based write protection is controlled by the state of the write-protect (WP) pin. Using one-page write mode, you can load up to 16 bytes of data into the EEPROM in a single write operation. Another significant feature of the S524A40X11/40X21/40X41/60X81/60X51 is its support for fast mode and standard mode.

#### FEATURES

#### I<sup>2</sup>C-Bus Interface

- Two-wire serial interface

- Automatic word address increment

#### EEPROM

- 1K/2K/4K/8K/16K-bit (128/256/512/1,024/2,048-byte) storage area

- 16-byte page buffer

- Hardware-based write protection for the entire EEPROM (using the WP pin)

- EEPROM programming voltage generated on chip

- 1,000,000 erase/write cycles

- 100 years data retention

#### **Operating Characteristics**

- Operating voltage

- 1.8 V to 5.5 V

- Operating current

- Maximum write current: < 3 mA at 5.5 V</li>

- Maximum read current: < 200 μA at 5.5 V

- Maximum stand-by current: < 5 μA at 5.5 V

- Operating temperature range

- - 25°C to + 70°C (commercial)

- - 40°C to + 85°C (industrial)

- Operating clock frequencies

- 100 kHz at standard mode

- 400 kHz at fast mode

- Electrostatic discharge (ESD)

- 5,000 V (HBM)

- 500 V (MM)

#### Packages

• 8-pin DIP, SOP, and TSSOP

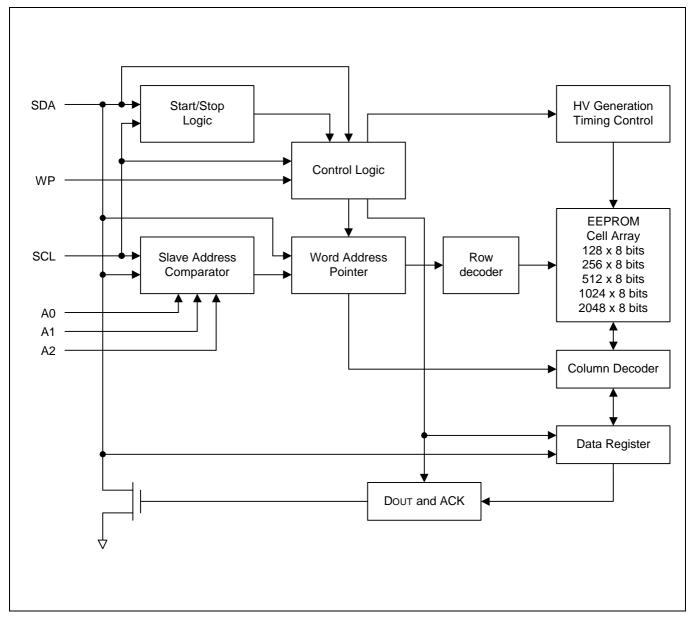

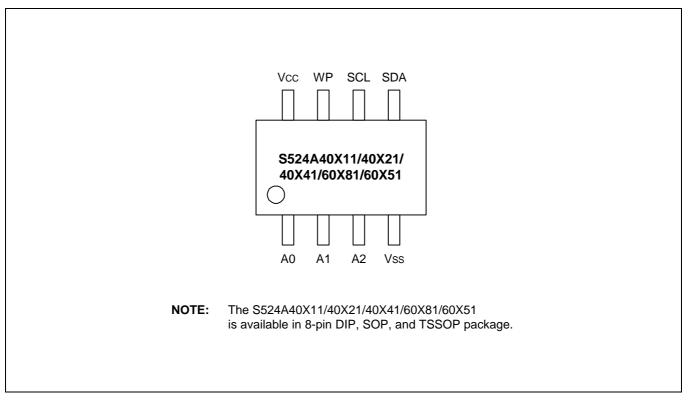

Figure 3-1. S524A40X11/40X21/40X41/60X81/60X51 Block Diagram

#### Figure 3-2. Pin Assignment Diagram

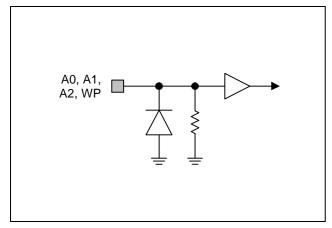

| Name            | Туре  | Description                                                                                                                                                                                                                                                                                                 | Circuit<br>Type |

|-----------------|-------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------|

| A0, A1, A2      | Input | Input pins for device address selection. To configure a device address, these pins should be connected to the V <sub>CC</sub> or V <sub>SS</sub> of the device. These pins are internally pulled down to V <sub>SS</sub> .                                                                                  | 1               |

| V <sub>SS</sub> | -     | Ground pin.                                                                                                                                                                                                                                                                                                 | _               |

| SDA             | I/O   | Bi-directional data pin for the I <sup>2</sup> C-bus serial data interface. Schmitt trigger input and open-drain output. An external pull-up resistor must be connected to $V_{CC.}$ Typical values for this pull-up resistor are 4.7 k $\Omega$ (100 kHz) and 1 k $\Omega$ (400 kHz).                      | 3               |

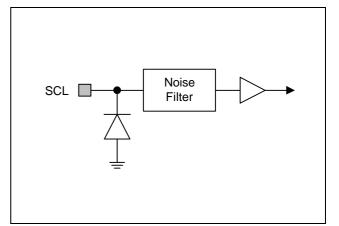

| SCL             | Input | Schmitt trigger input pin for serial clock input.                                                                                                                                                                                                                                                           | 2               |

| WP              | Input | Input pin for hardware write protection control. If you tie this pin to V <sub>CC</sub> , the write function is disabled to protect previously written data in the entire memory; if you tie it to V <sub>SS</sub> , the write function is enabled. This pin is internally pulled down to V <sub>SS</sub> . | 1               |

| V <sub>CC</sub> | _     | Single power supply.                                                                                                                                                                                                                                                                                        | _               |

**NOTE**: See the following page for diagrams of pin circuit types 1, 2, and 3.

Figure 3-4. Pin Circuit Type 2

Figure 3-5. Pin Circuit Type 3

#### FUNCTION DESCRIPTION

#### I<sup>2</sup>C-BUS INTERFACE

The S524A40X11/40X21/40X41/60X81/60X51 supports the I<sup>2</sup>C-bus serial interface data transmission protocol. The two-wire bus consists of a serial data line (SDA) and a serial clock line (SCL). The SDA and the SCL lines must be connected to  $V_{CC}$  by a pull-up resistor that is located somewhere on the bus.

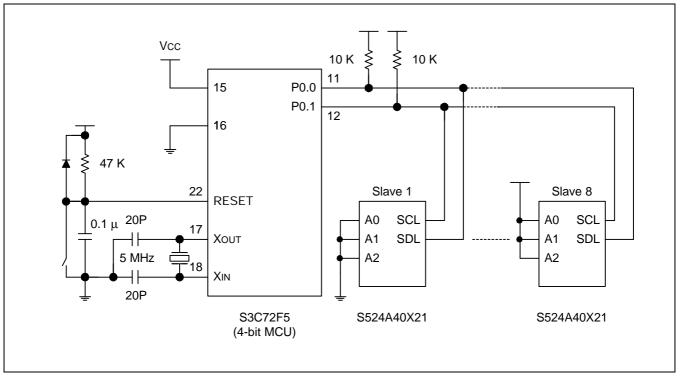

Any device that puts data onto the bus is defined as the "transmitter" and any device that gets data from the bus is the "receiver." The bus is controlled by a master device which generates the serial clock and start/stop conditions, controlling bus access. Using the A0, A1, and A2 input pins, up to eight S524A40X11/40X21 (four S524A40X41, two for S524A60X81, one for S524A60X51) devices can be connected to the same I<sup>2</sup>C-bus as slaves (see Figure 3-6). Both the master and slaves can operate as transmitter or receiver, but the master device determines which bus operating mode would be active.

SAMSUNG ELECTRONICS

#### I<sup>2</sup>C-BUS PROTOCOLS

Here are several rules for I<sup>2</sup>C-bus transfers:

- A new data transfer can be initiated only when the bus is currently not busy.

- MSB is always transferred first in transmitting data.

- During a data transfer, the data line (SDA) must remain stable whenever the clock line (SCL) is High.

The I<sup>2</sup>C-bus interface supports the following communication protocols:

- Bus not busy: The SDA and the SCL lines remain High level when the bus is not active.

- <u>Start condition</u>: Start condition is initiated by a High-to-Low transition of the SDA line while SCL remains High level. All bus commands must be preceded by a start condition.

- <u>Stop condition</u>: A stop condition is initiated by a Low-to-High transition of the SDA line while SCL remains High level. All bus operations must be completed by a stop condition (see Figure 3-7).

Figure 3-7. Data Transmission Sequence

- <u>Data valid</u>: Following a start condition, the data becomes valid if the data line remains stable for the duration of the High period of SCL. New data must be put onto the bus while SCL is Low. Bus timing is one clock pulse per data bit. The number of data bytes to be transferred is determined by the master device. The total number of bytes that can be transferred in one operation is theoretically unlimited.

- <u>ACK (Acknowledge)</u>: An ACK signal indicates that a data transfer is completed successfully. The transmitter (the master or the slave) releases the bus after transmitting eight bits. During the 9th clock, which the master generates, the receiver pulls the SDA line low to acknowledge that it successfully received the eight bits of data (see Figure 3-8). But the slave does not send an ACK if an internal write cycle is still in progress.

In data read operations, the slave releases the SDA line after transmitting 8 bits of data and then monitors the line for an ACK signal during the 9th clock period. If an ACK is detected, the slave will continue to transmit data. If an ACK is not detected, the slave terminates data transmission and waits for a stop condition to be issued by the master before returning to its stand-by mode.

Figure 3-8. Acknowledge Response From Receiver

- <u>Slave Address</u>: After the master initiates a Start condition, it must output the address of the device to be accessed. The most significant four bits of the slave address are called the "device identifier". The identifier for the S524A40X11/40X21/40X41/60X81/60X51 is "1010B". The next three bits comprise the address of a specific device. The device address is defined by the state of the A0, A1 and A2 pins. Using this addressing scheme, you can cascade up to eight S524A40X11/40X21 or four S524A40X41 or two S524A60X81 or one S524A60X51 on the bus (see Table 3-2 below). The b1 for S524A40X41 or the b1, b2 for S524A60X81 or the b1, b2, b3 for S524A60X51 are used by the master to select which of the blocks of internal memory (1 block = 256 words) are to be accessed. The bits are in effect the most significant bits of the word address.

- <u>Read/Write</u>: The final (eighth) bit of the slave address defines the type of operation to be performed. If the R/W bit is "1", a read operation is executed. If it is "0", a write operation is executed.

| Device           | Device Identifier |    |    | ier | [  | R/W Bit |    |     |

|------------------|-------------------|----|----|-----|----|---------|----|-----|

|                  | b7                | b6 | b5 | b4  | b3 | b2      | b1 | b0  |

| S524A40X11/40X21 | 1                 | 0  | 1  | 0   | A2 | A1      | A0 | R/W |

| S524A40X41       | 1                 | 0  | 1  | 0   | A2 | A1      | B0 | R/W |

| S524A60X81       | 1                 | 0  | 1  | 0   | A2 | B1      | B0 | R/W |

| S524A60X51       | 1                 | 0  | 1  | 0   | B2 | B1      | B0 | R/W |

Table 3-2. Slave Device Addressing

NOTE: The B2, B1, B0 correspond to the MSB of the memory array address word.

#### BYTE WRITE OPERATION

In a complete byte write operation, the master transmits the slave address, word address, and one data byte to the S524A40X11/40X21/40X41/60X81/60X51 slave device (see Figure 3-9).

Figure 3-9. Byte Write Operation

Following the Start condition, the master sends the device identifier (4 bits), the device address (3 bits), and an R/W bit set to "0" onto the bus. Then the addressed S524A40X11/40X21/40X41/60X81/60X51 generates an ACK and waits for the next byte. The next byte to be transmitted by the master is the word address. This 8-bit address is written into the word address pointer of the S524A40X11/40X21/40X41/60X81/60X51.

When the S524A40X11/40X21/40X41/60X81/60X51 receives the word address, it responds by issuing an ACK and then waits for the next 8-bit data. When it receives the data byte, the S524A40X11/40X21/40X41/60X81/60X51 again responds with an ACK. The master terminates the transfer by generating a Stop condition, at which time the S524A40X11/40X21/40X41/60X81/60X51 begins the internal write cycle.

While the internal write cycle is in progress, all S524A40X11/40X21/40X41/60X81/60X51 inputs are disabled and the S524A40X11/40X21/40X41/60X81/60X51 does not respond to additional requests from the master.

#### PAGE WRITE OPERATION

The S524A40X11/40X21/40X41/60X81/60X51 can also perform 16-byte page write operation. A page write operation is initiated in the same way as a byte write operation. However, instead of finishing the write operation after the first data byte is transferred, the master can transmit up to 15 additional bytes. The S524A40X11/40X21/40X41/60X81/60X51 responds with an ACK each time it receives a complete byte of data (see Figure 3-10).

Figure 3-10. Page Write Operation

The S524A40X11/40X21/40X41/60X81/60X51 automatically increments the word address pointer each time it receives a complete data byte. When one byte has been received, the internal word address pointer increments to the next address and the next data byte can be received.

If the master transmits more than 16 bytes before it generates a stop condition to end the page write operation, the S524A40X11/40X21/40X41/60X81/60X51 word address pointer value "rolls over" and the previously received data is overwritten. If the master transmits less than 16 bytes and generates a stop condition, the S524A40X11/40X21/40X41/60X81/60X51 writes the received data to the corresponding EEPROM address.

During a page write operation, all inputs are disabled and there is no response to additional requests from the master until the internal write cycle is completed.

#### POLLING FOR AN ACK SIGNAL

When the master issues a stop condition to initiate a write cycle, the S524A40X11/40X21/40X41/60X81/60X51 starts an internal write cycle. The master can then immediately begin polling for an ACK from the slave device.

To poll for an ACK signal in a write operation, the master issues a start condition followed by the slave address. As long as the S524A40X11/40X21/40X41/60X81/60X51 remains busy with the write operation, no ACK is returned. When the S524A40X11/40X21/40X41/60X81/60X51 completes the write operation, it returns an ACK and the master can then proceed with the next read or write operation (see Figure 3-11).

Figure 3-11. Master Polling for an ACK Signal from a Slave Device

#### HARDWARE-BASED WRITE PROTECTION

You can also write-protect the entire memory area of the S524A40X11/40X21/40X41/60X81/60X51. This method of write protection is controlled by the state of the Write Protect (WP) pin.

When the WP pin is connected to  $V_{CC}$ , any attempt to write a value to the memory is ignored.

The S524A40X11/40X21/40X41/60X81/60X51 will acknowledge slave and word address, but it will not generate an acknowledge after receiving the first byte of the data. Thus the write cycle will not be started when the stop condition is generated. By connecting the WP pin to  $V_{SS}$ , the write function is allowed for the entire memory.

These write protection features effectively change the EEPROM to a ROM in order to prevent data from being overwritten. Whenever the write function is disabled, a slave address and a word address are acknowledged on the bus, but data bytes are not acknowledged.

#### **CURRENT ADDRESS BYTE READ OPERATION**

The internal word address pointer maintains the address of the last word accessed, incremented by one. Therefore, if the last access (either read or write) was to the address "n", the next read operation would access data at address "n+1".

When the S524A40X11/40X21/40X41/60X81/60X51 receives a slave address with the R/W bit set to "1", it issues an ACK and sends the eight bits of data. The master does not acknowledge the transfer but it does generate a Stop condition. In this way, the S524A40X11/40X21/40X41/60X81/60X51 effectively stops the transmission (see Figure 3-12).

Figure 3-12. Current Address Byte Read Operation

#### RANDOM ADDRESS BYTE READ OPERATION

Using random read operations, the master can access any memory location at any time. Before it issues the slave address with the R/W bit set to "1", the master must first perform a "dummy" write operation. This operation is performed in the following steps:

- 1. The master first issues a Start condition, the slave address, and the word address to be read. (This step sets the internal word address pointer of the S524A40X11/40X21/40X41/60X81/60X51 to the desired address.)

- 2. When the master receives an ACK for the word address, it immediately re-issues a start condition followed by another slave address, with the R/W bit set to "1".

- 3. The S524A40X11/40X21/40X41/60X81/60X51 then sends an ACK and the 8-bit data stored at the desired address.

- 4. At this point, the master does not acknowledge the transmission, but generates a stop condition instead.

- 5. In response, the S524A40X11/40X21/40X41/60X81/60X51 stops transmitting data and reverts to its stand-by mode (see Figure 3-13).

Figure 3-13. Random Address Byte Read Operation

#### SEQUENTIAL READ OPERATION

Sequential read operations can be performed in two ways: as a series of current address reads or as random address reads. The first data is sent in the same way as the previous read mode used on the bus. The next time, however, the master responds with an ACK, indicating that it requires additional data. The S524A40X11/40X21/40X41/60X81/60X51 continues to output data for each ACK it receives. To stop the sequential read operation, the master does not respond with an ACK, but instead issues a Stop condition.

Using this method, data is output sequentially with the data from address "n" followed by the data from "n+1". The word address pointer for read operations increments all word addresses, allowing the entire EEPROM to be read sequentially in a single operation. After the entire EEPROM is read, the word address pointer "rolls over" and the S524A40X11/40X21/40X41/60X81/60X51 continues to transmit data for each ACK it receives from the master (see Figure 3-14).

Figure 3-14. Sequential Read Operation

# **ELECTRICAL DATA**

#### Table 3-3. Absolute Maximum Ratings

$(T_A = 25^{\circ}C)$

| Parameter               | Symbol           | Conditions | Rating         | Unit |

|-------------------------|------------------|------------|----------------|------|

| Supply voltage          | V <sub>CC</sub>  | -          | - 0.3 to + 7.0 | V    |

| Input voltage           | V <sub>IN</sub>  | -          | - 0.3 to + 7.0 | V    |

| Output voltage          | V <sub>O</sub>   | -          | - 0.3 to + 7.0 | V    |

| Operating temperature   | T <sub>A</sub>   | -          | - 40 to + 85   | °C   |

| Storage temperature     | T <sub>STG</sub> | -          | - 65 to + 150  | °C   |

| Electrostatic discharge | V <sub>ESD</sub> | HBM        | 5000           | V    |

|                         |                  | MM         | 500            |      |

#### Table 3-4. D.C. Electrical Characteristics

| Paramet            | ter     | Symbol           | Conditions                                              | Min                 | Тур | Max                 | Unit |

|--------------------|---------|------------------|---------------------------------------------------------|---------------------|-----|---------------------|------|

| Input low voltage  | )       | V <sub>IL</sub>  | SCL, SDA, A0, A1, A2                                    | -                   | _   | 0.3 V <sub>CC</sub> | V    |

| Input high voltag  | е       | V <sub>IH</sub>  |                                                         | 0.7 V <sub>CC</sub> | _   | -                   | V    |

| Input leakage cu   | rrent   | Ι <sub>LI</sub>  | $V_{IN} = 0$ to $V_{CC}$                                | -                   | _   | 10                  | μA   |

| Output leakage of  | current | I <sub>LO</sub>  | $V_0 = 0$ to $V_{CC}$                                   | _                   | -   | 10                  | μA   |

| Output low voltage |         | V <sub>OL</sub>  | $I_{OL} = 0.15 \text{ mA}, V_{CC} = 1.8 \text{ V}$      | _                   | -   | 0.2                 | V    |

|                    |         |                  | $I_{OL} = 2.1 \text{ mA}, V_{CC} = 2.5 \text{ V}$       | _                   | -   | 0.4                 |      |

| Supply current     | Write   | I <sub>CC1</sub> | V <sub>CC</sub> = 5.5 V, 400 kHz                        | -                   | -   | 3                   | mA   |

|                    |         | I <sub>CC2</sub> | V <sub>CC</sub> = 1.8 V, 100 kHz                        | -                   | -   | 1                   |      |

|                    | Read    | I <sub>CC3</sub> | V <sub>CC</sub> = 5.5 V, 400 kHz                        | _                   | -   | 0.2                 |      |

|                    |         | I <sub>CC4</sub> | V <sub>CC</sub> = 1.8 V, 100 kHz                        | -                   | -   | 60                  | μA   |

| Stand-by current   |         | I <sub>CC5</sub> | $V_{CC} = SDA = SCL = 5.5 V,$<br>all other inputs = 0 V | _                   | -   | 5                   | μA   |

|                    |         | I <sub>CC6</sub> | $V_{CC} = SDA = SCL = 1.8 V,$<br>all other inputs = 0 V | -                   | -   | 1                   |      |

#### $(T_A = -25^{\circ}C \text{ to } + 70^{\circ}C \text{ (C)}, -40^{\circ}C \text{ to } + 85^{\circ}C \text{ (I)}, V_{CC} = 1.8 \text{ V to } 5.5 \text{ V})$

#### Table 3-4. D.C. Electrical Characteristics (Continued)

| Parameter                | Symbol           | Conditions                                                                      | Min | Тур | Max | Unit |

|--------------------------|------------------|---------------------------------------------------------------------------------|-----|-----|-----|------|

| Input capacitance        | C <sub>IN</sub>  | 25 °C, 1MHz,<br>$V_{CC} = 5 V$ , $V_{IN} = 0 V$ ,<br>A0, A1, A2, SCL and WP pin | _   | _   | 10  | pF   |

| Input/output capacitance | C <sub>I/O</sub> | 25 °C, 1MHz,<br>$V_{CC} = 5 V, V_{I/O} = 0 V,$<br>SDA pin                       | _   | _   | 10  |      |

$(T_A = -25^{\circ}C \text{ to } + 70^{\circ}C \text{ (C)}, -40^{\circ}C \text{ to } + 85^{\circ}C \text{ (I)}, V_{CC} = 1.8 \text{ V to } 5.5 \text{ V})$

#### Table 3-5. A.C. Electrical Characteristics

$(T_A = -25^{\circ}C \text{ to } + 70^{\circ}C \text{ (C)}, -40^{\circ}C \text{ to } + 85^{\circ}C \text{ (I)}, V_{CC} = 1.8 \text{ V to } 5.5 \text{ V})$

| Parameter                                          | Symbol              | Conditions              | ••   | 3 to 5.5 V<br>d Mode) |     | 5 to 5.5 V<br>Mode) | Unit |

|----------------------------------------------------|---------------------|-------------------------|------|-----------------------|-----|---------------------|------|

|                                                    |                     |                         | Min  | Max                   | Min | Max                 |      |

| External clock frequency                           | F <sub>CLK</sub>    | -                       | 0    | 100                   | 0   | 400                 | kHz  |

| Clock high time                                    | t <sub>HIGH</sub>   | -                       | 4    | -                     | 0.6 | _                   | μs   |

| Clock low time                                     | t <sub>LOW</sub>    | -                       | 4.7  | -                     | 1.3 | -                   |      |

| Rising time                                        | t <sub>R</sub>      | SDA, SCL                | _    | 1                     | -   | 0.3                 |      |

| Falling time                                       | t <sub>F</sub>      | SDA, SCL                | _    | 0.3                   | -   | 0.3                 |      |

| Start condition hold time                          | t <sub>HD:STA</sub> | -                       | 4    | -                     | 0.6 | _                   |      |

| Start condition setup time                         | t <sub>SU:STA</sub> | -                       | 4.7  | -                     | 0.6 | _                   |      |

| Data input hold time                               | t <sub>HD:DAT</sub> | -                       | 0    | -                     | 0   | _                   |      |

| Data input setup time                              | t <sub>SU:DAT</sub> | -                       | 0.25 | -                     | 0.1 | _                   |      |

| Stop condition setup time                          | t <sub>SU:STO</sub> | -                       | 4    | -                     | 0.6 | _                   |      |

| Bus free time                                      | t <sub>BUF</sub>    | Before new transmission | 4.7  | _                     | 1.3 | _                   | -    |

| Data output valid from clock low <sup>(note)</sup> | t <sub>AA</sub>     | -                       | 0.3  | 3.5                   | -   | 0.9                 |      |

| Noise spike width                                  | t <sub>SP</sub>     | -                       | _    | 100                   | -   | 50                  | ns   |

| Write cycle time                                   | t <sub>WR</sub>     | -                       | _    | 5                     | -   | 5                   | ms   |

#### NOTES:

1. Upon customers request, up to 400 kHz (Max.) in standard mode and 1 MHz in fast mode are available.

2. When acting as a transmitter, the S524A40X11/40X21/40X41/60X81/60X51 must provide an internal minimum delay time to bridge the undefined period (minimum 300 ns) of the falling edge of SCL. This is required to avoid unintended generation of a start or stop condition.

Figure 3-15. Timing Diagram for Bus Operations

Figure 3-16. Write Cycle Timing Diagram

# S524AB0X91/B0XB1

# 32K/64K-bit Serial EEPROM for Low Power

Data Sheet

# **OVERVIEW**

The S524AB0X91/B0XB1 serial EEPROM has a 32K/64K-bit (4,096/8,192 bytes) capacity, supporting the standard I<sup>2</sup>C<sup>™</sup>-bus serial interface. It is fabricated using Samsung's most advanced CMOS technology. It has been developed for low power and low voltage applications (1.8 V to 5.5 V). One of its major feature is a hardware-based write protection circuit for the entire memory area. Hardware-based write protection is controlled by the state of the write-protect (WP) pin. Using one-page write mode, you can load up to 32 bytes of data into the EEPROM in a single write operation. Another significant feature of the S524AB0X91/B0XB1 is its support for fast mode and standard mode.

# FEATURES

#### I<sup>2</sup>C-Bus Interface

- Two-wire serial interface

- Automatic word address increment

#### EEPROM

- 32K/64K-bit (4,096/8,192 bytes) storage area

- 32-byte page buffer

- Hardware-based write protection for the entire EEPROM (using the WP pin)

- EEPROM programming voltage generated on chip

- 1,000,000 erase/write cycles

- 100 years data retention

#### **Operating Characteristics**

- Operating voltage

- 1.8 V to 5.5 V

- Operating current

- Maximum write current: < 3 mA at 5.5 V</li>

- Maximum read current: < 400 μA at 5.5 V

- Maximum stand-by current: < 5 μA at 5.5 V

- Operating temperature range

- - 25°C to + 70°C (commercial)

- - 40°C to + 85°C (industrial)

- Operating clock frequencies

- 100 kHz at standard mode

- 400 kHz at fast mode

- Electrostatic discharge (ESD)

- 5,000 V (HBM)

- 500 V (MM)

#### Packages

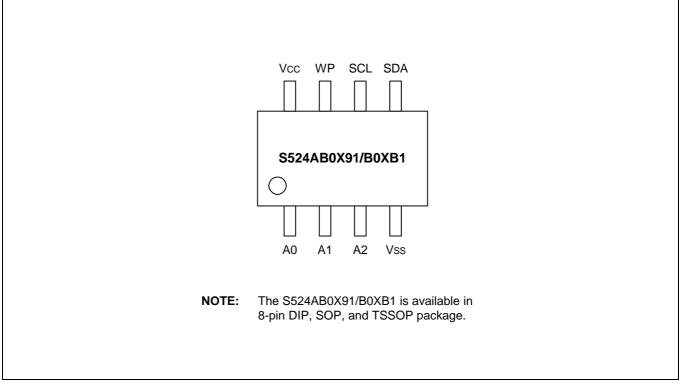

• 8-pin DIP, SOP, and TSSOP

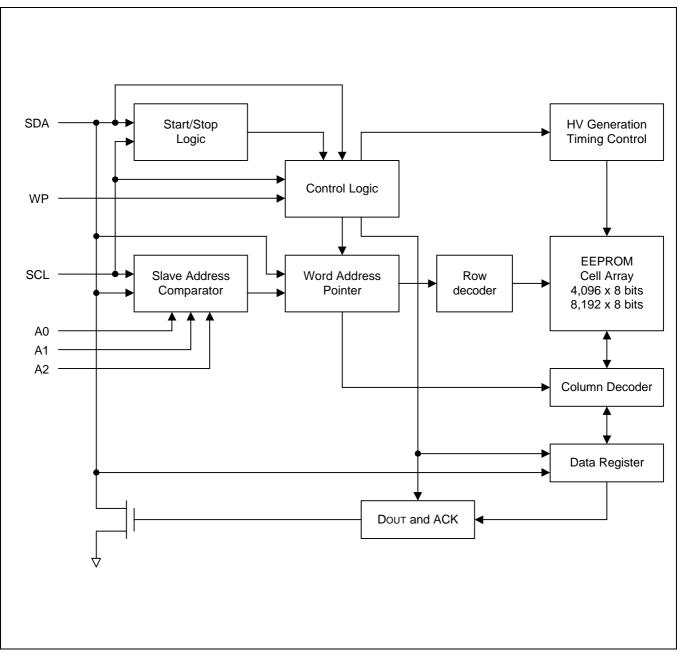

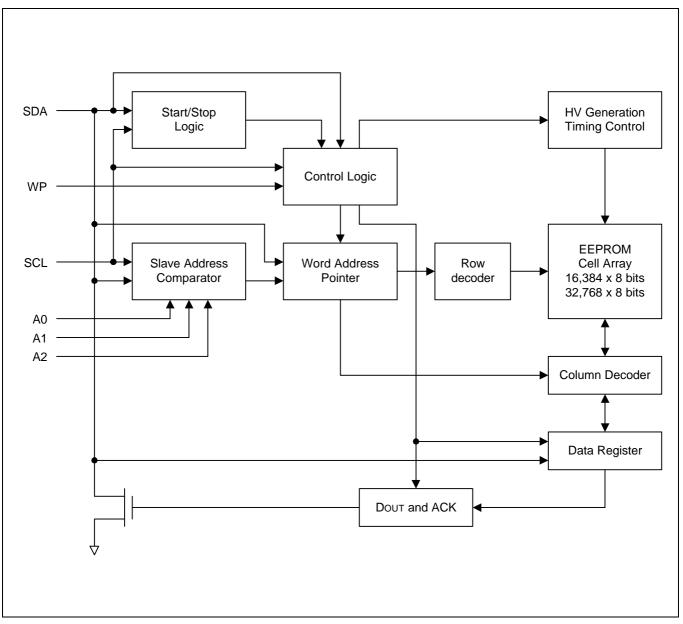

Figure 4-1. S524AB0X91/B0XB1 Block Diagram

#### Figure 4-2. Pin Assignment Diagram

| Name            | Туре  | Description                                                                                                                                                                                                                                                                                                 | Circuit<br>Type |

|-----------------|-------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------|

| A0, A1, A2      | Input | Input pins for device address selection. To configure a device address, these pins should be connected to the V <sub>CC</sub> or V <sub>SS</sub> of the device. These pins are internally pulled down to V <sub>SS</sub> .                                                                                  | 1               |

| V <sub>SS</sub> | _     | Ground pin.                                                                                                                                                                                                                                                                                                 | _               |

| SDA             | I/O   | Bi-directional data pin for the $I^2$ C-bus serial data interface.<br>Schmitt trigger input and open-drain output.<br>An external pull-up resistor must be connected to V <sub>DD</sub> .<br>Typical values for this pull-up resistor are 4.7 K $\Omega$ (100 KHz)                                          | 3               |

|                 |       | and 1 K $\Omega$ (400 KHz).                                                                                                                                                                                                                                                                                 |                 |

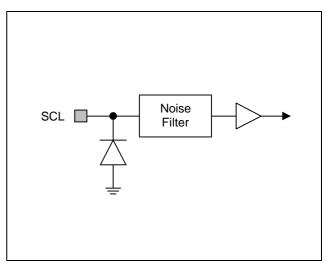

| SCL             | Input | Schmitt trigger input pin for serial clock input.                                                                                                                                                                                                                                                           | 2               |

| WP              | Input | Input pin for hardware write protection control. If you tie this pin to V <sub>CC</sub> , the write function is disabled to protect previously written data in the entire memory; if you tie it to V <sub>SS</sub> , the write function is enabled. This pin is internally pulled down to V <sub>SS</sub> . | 1               |

| V <sub>CC</sub> | _     | Single power supply.                                                                                                                                                                                                                                                                                        | _               |

#### Table 4-1. S524AB0X91/B0XB1 Pin Descriptions

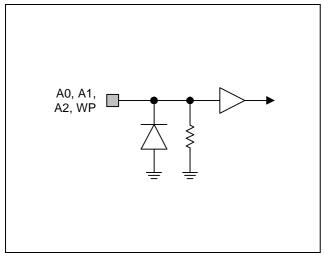

**NOTE**: See the following page for diagrams of pin circuit types 1, 2, and 3.

Figure 4-4. Pin Circuit Type 2

Figure 4-5. Pin Circuit Type 3

# **FUNCTION DESCRIPTION**

#### I<sup>2</sup>C-BUS INTERFACE

The S524AB0X91/B0XB1 supports the  $I^2$ C-bus serial interface data transmission protocol. The two-wire bus consists of a serial data line (SDA) and a serial clock line (SCL). The SDA and the SCL lines must be connected to V<sub>CC</sub> by a pull-up resistor that is located somewhere on the bus.

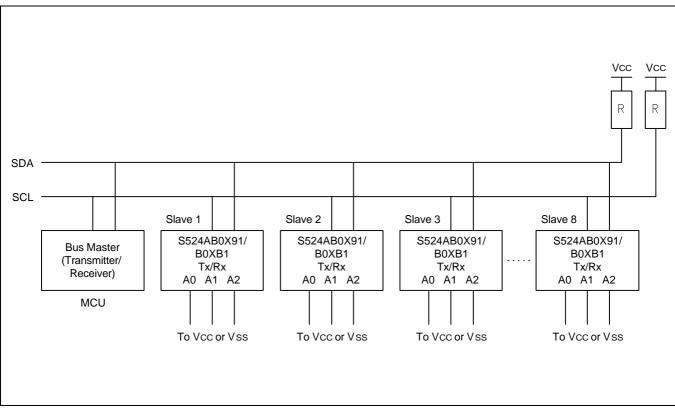

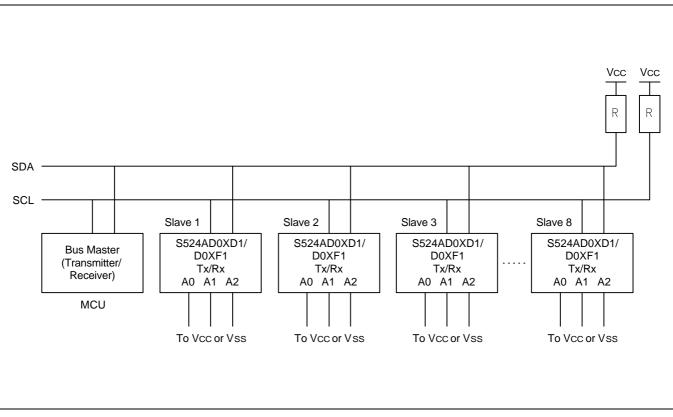

Any device that puts data onto the bus is defined as a "transmitter" and any device that gets data from the bus is a "receiver." The bus is controlled by a master device which generates the serial clock and start/stop conditions, controlling bus access. Using the A0, A1, and A2 input pins, up to eight S524AB0X91/B0XB1 devices can be connected to the same I<sup>2</sup>C-bus as slaves (see Figure 4-6). Both the master and slaves can operate as a transmitter or a receiver, but the master device determines which bus operating mode would be active.

Figure 4-6. Typical Configuration

#### **I<sup>2</sup>C-BUS PROTOCOLS**

Here are several rules for l<sup>2</sup>C-bus transfers:

- A new data transfer can be initiated only when the bus is currently not busy.

- MSB is always transferred first in transmitting data.

- During a data transfer, the data line (SDA) must remain stable whenever the clock line (SCL) is High.

The I<sup>2</sup>C-bus interface supports the following communication protocols:

- Bus not busy: The SDA and the SCL lines remain in High level when the bus is not active.

- <u>Start condition</u>: A start condition is initiated by a High-to-Low transition of the SDA line while SCL remains in High level. All bus commands must be preceded by a start condition.

- <u>Stop condition</u>: A stop condition is initiated by a Low-to-High transition of the SDA line while SCL remains in High level. All bus operations must be completed by a stop condition (see Figure 4-7).

Figure 4-7. Data Transmission Sequence

- <u>Data valid</u>: Following a start condition, the data becomes valid if the data line remains stable for the duration of the High period of SCL. New data must be put onto the bus while SCL is Low. Bus timing is one clock pulse per data bit. The number of data bytes to be transferred is determined by the master device. The total number of bytes that can be transferred in one operation is theoretically unlimited.

- <u>ACK (Acknowledge)</u>: An ACK signal indicates that a data transfer is completed successfully. The transmitter (the master or the slave) releases the bus after transmitting eight bits. During the 9th clock, which the master generates, the receiver pulls the SDA line low to acknowledge that it has successfully received the eight bits of data (see Figure 4-8). But the slave does not send an ACK if an internal write cycle is still in progress.

In data read operations, the slave releases the SDA line after transmitting 8 bits of data and then monitors the line for an ACK signal during the 9th clock period. If an ACK is detected but no stop condition, the slave will continue to transmit data. If an ACK is not detected, the slave terminates data transmission and waits for a stop condition to be issued by the master before returning to its stand-by mode.

Figure 4-8. Acknowledge Response From Receiver

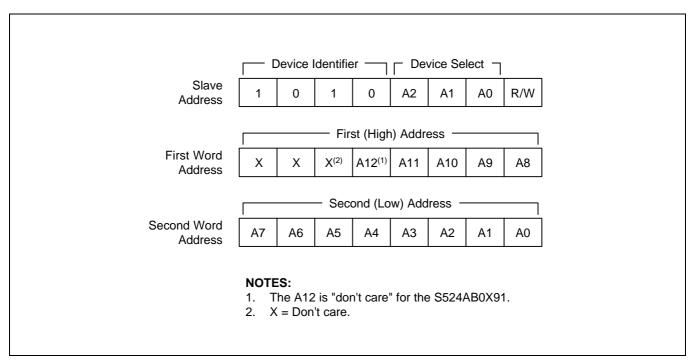

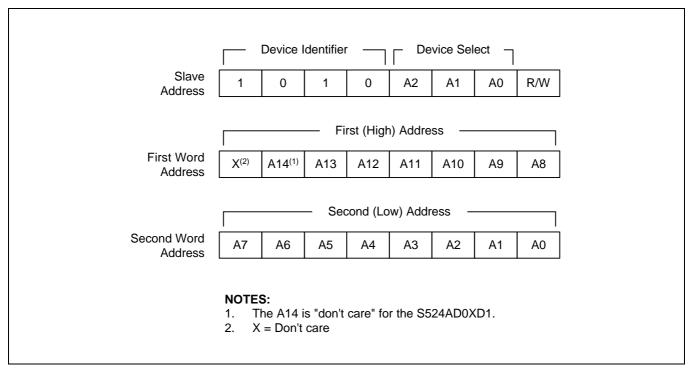

- <u>Slave Address</u>: After the master initiates a start condition, it must output the address of the device to be accessed. The most significant four bits of the slave address are called the "device identifier." The identifier for the S524AB0X91/B0XB1 is "1010B". The next three bits comprise the address of a specific device. The device address is defined by the state of the A0, A1, and A2 pins. Using this addressing scheme, you can cascade up to eight S524AB0X91/B0XB1s on the bus (see Figure 4-9 below).

- <u>Read/Write</u>: The final (eighth) bit of the slave address defines the type of operation to be performed. If the R/W bit is "1", a read operation is executed. If it is "0", a write operation is executed.

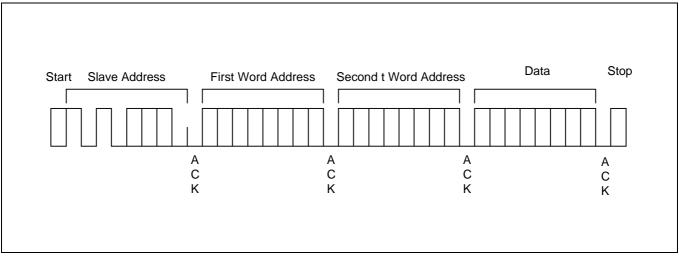

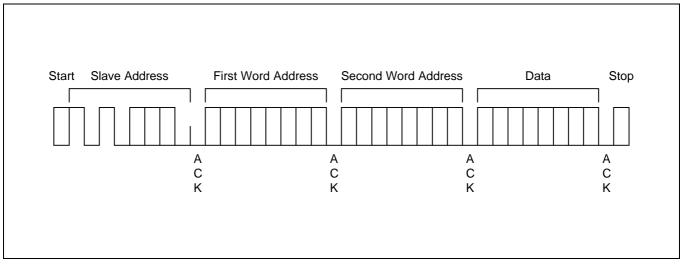

#### BYTE WRITE OPERATION

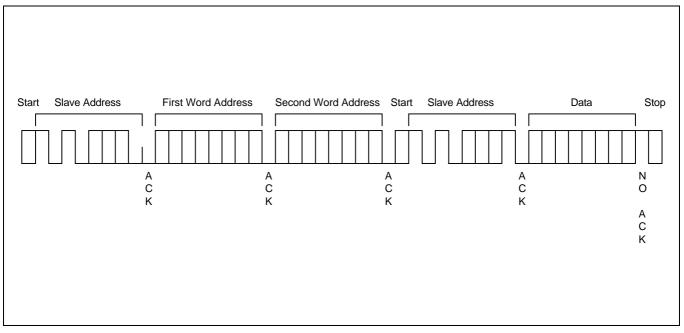

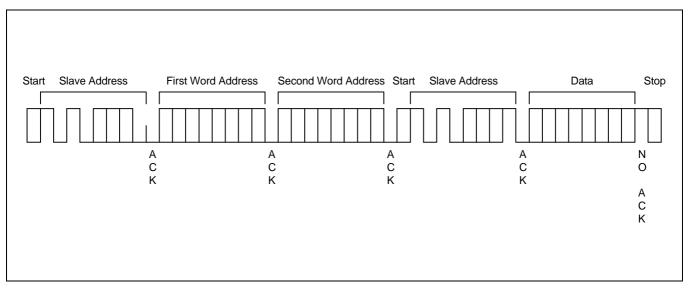

A write operation requires 2-byte word addresses, the first (high) word address and the second (low) word address. In a byte write operation, the master transmits the slave address, the first word address, the second word address, and one data byte to the S524AB0X91/B0XB1 slave device (see Figure 4-10).

#### Figure 4-10. Byte Write Operation

Following a start condition, the master puts the device identifier (4 bits), the device address (3 bits), and an R/W bit set to "0" onto the bus. Upon the receipt of the slave address, the S524AB0X91/B0XB1 responds with an ACK. And the master transmits the first word address, the second word address, and one byte data to be written into the addressed memory location.

The master terminates the transfer by generating a stop condition, at which time the S524AB0X91/B0XB1 begins the internal write cycle. While the internal write cycle is in progress, all S524AB0X91/B0XB1 inputs are disabled and the S524AB0X91/B0XB1 does not respond to any additional request from the master.

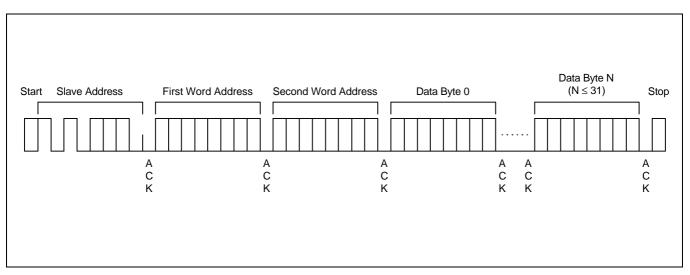

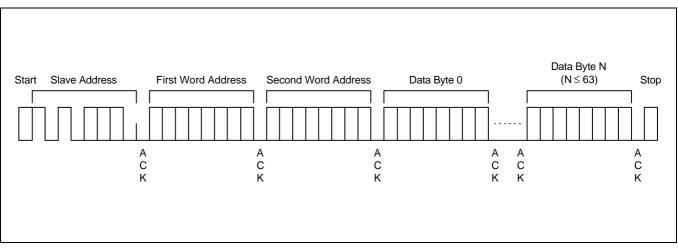

#### PAGE WRITE OPERATION

The S524AB0X91/B0XB1 can also perform 32-byte page write operation. A page write operation is initiated in the same way as a byte write operation. However, instead of finishing the write operation after the first data byte is transferred, the master can transmit up to 31 additional bytes. The S524AB0X91/B0XB1 responds with an ACK each time it receives a complete byte of data (see Figure 4-11).

#### Figure 4-11. Page Write Operation

The S524AB0X91/B0XB1 automatically increments the word address pointer each time it receives a complete data byte. When one byte is received, the internal word address pointer increments to the next address so that the next data byte can be received.

If the master transmits more than 32 bytes before it generates a stop condition to end the page write operation, the S524AB0X91/B0XB1 word address pointer value "rolls over" and the previously received data is overwritten. If the master transmits less than 32 bytes and generates a stop condition, the S524AB0X91/B0XB1 writes the received data to the corresponding EEPROM address.

During a page write operation, all inputs are disabled and there would be no response to additional requests from the master until the internal write cycle is completed.

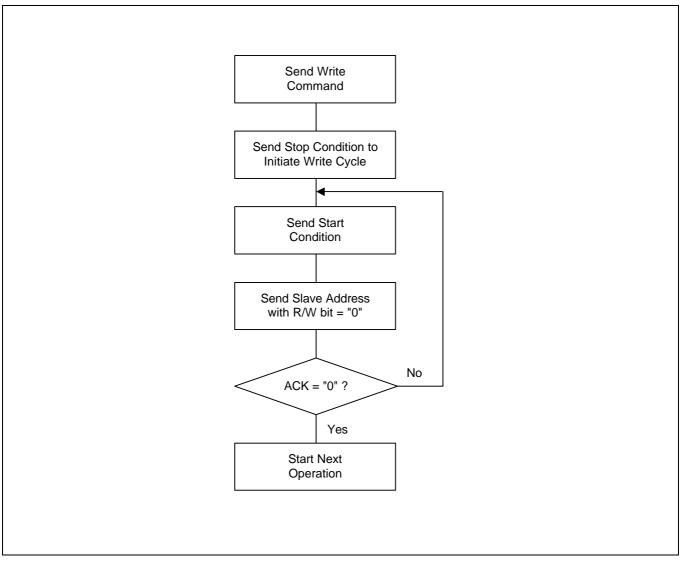

#### POLLING FOR AN ACK SIGNAL

When the master issues a stop condition to initiate a write cycle, the S524AB0X91/B0XB1 starts an internal write cycle. The master can then immediately begin polling for an ACK from the slave device to determine whether the write cycle is completed.

To poll for an ACK signal in a write operation, the master issues a start condition followed by the slave address. As long as the S524AB0X91/B0XB1 remains busy with the write operation, no ACK is returned. When the S524AB0X91/B0XB1 completes the write operation, it returns an ACK and the master can then proceed with the next read or write operation (see Figure 4-12).

Figure 4-12. Master Polling for an ACK Signal from a Slave Device

#### HARDWARE-BASED WRITE PROTECTION

You can also write-protect the entire memory area of the S524AB0X91/B0XB1. This write protection is controlled by the state of the Write Protect (WP) pin.

When the WP pin is connected to  $V_{CC}$ , any attempt to write a value to it is ignored. The S524AB0X91/B0XB1 will acknowledge slave and word addresses, but it will not generate an acknowledge after receiving the first byte of data. In this situation, the write cycle will not be started when a stop condition is generated. By connecting the WP pin to  $V_{SS}$ , the write function is allowed for the entire memory.

These write protection features effectively change the EEPROM to a ROM in order to protect data from being overwritten. Whenever the write function is disabled, a slave address and word addresses are acknowledged on the bus, but data bytes are not acknowledged.

#### **CURRENT ADDRESS BYTE READ OPERATION**

The internal word address pointer maintains the address of the last word accessed, incremented by one. Therefore, if the last access (either read or write) was to the address "n", the next read operation would be to access data at address "n+1".

When the S524AB0X91/B0XB1 receives a slave address with the R/W bit set to "1", it issues an ACK and sends the eight bits of data. In a current address byte read operation, the master does not acknowledge the data, and it generates a stop condition, forcing the S524AB0X91/B0XB1 to stop the transmission (see Figure 4-13).

Figure 4-13. Current Address Byte Read Operation

#### RANDOM ADDRESS BYTE READ OPERATION

Using random read operations, the master can access any memory location at any time. Before it issues the slave address with the R/W bit set to "1", the master must first perform a "dummy" write operation. This operation is performed in the following steps:

- 1. The master first issues a start condition, the slave address, and the word address (the first and the second addresses) to be read. (This step sets the internal word address pointer of the S524AB0X91/B0XB1 to the desired address.)

- 2. When the master receives an ACK for the word address, it immediately re-issues a start condition followed by another slave address, with the R/W bit set to "1".

- 3. The S524AB0X91/B0XB1 then sends an ACK and the 8-bit data stored at the pointed address.

- 4. At this point, the master does not acknowledge the transmission, generating a stop condition.

- 5. The S524AB0X91/B0XB1 stops transmitting data and reverts to stand-by mode (see Figure 4-14).

Figure 4-14. Random Address Byte Read Operation

#### SEQUENTIAL READ OPERATION

Sequential read operations can be performed in two ways: current address sequential read operation, and random address sequential read operation. The first data is sent in either of the two ways, current address byte read operation described earlier. If the master responds with an ACK, the S524AB0X91/B0XB1 continues transmitting data. If the master does not issue an ACK, generating a stop condition, the slave stops transmission, ending the sequential read operation.

Using this method, data is output sequentially from address "n" followed by address "n+1". The word address pointer for read operations increments to all word addresses, allowing the entire EEPROM to be read sequentially in a single operation. After the entire EEPROM is read, the word address pointer "rolls over" and the S524AB0X91/B0XB1 continues to transmit data for each ACK it receives from the master (see Figure 4-15).

Figure 4-15. Sequential Read Operation

# **ELECTRICAL DATA**

#### Table 4-2. Absolute Maximum Ratings

$(T_A = 25^{\circ}C)$

| Parameter               | Symbol           | Conditions | Rating         | Unit |

|-------------------------|------------------|------------|----------------|------|

| Supply voltage          | V <sub>CC</sub>  | -          | - 0.3 to + 7.0 | V    |

| Input voltage           | V <sub>IN</sub>  | -          | - 0.3 to + 7.0 | V    |

| Output voltage          | V <sub>O</sub>   | -          | - 0.3 to + 7.0 | V    |

| Operating temperature   | T <sub>A</sub>   | -          | - 40 to + 85   | °C   |

| Storage temperature     | T <sub>STG</sub> | -          | - 65 to + 150  | °C   |

| Electrostatic discharge | V <sub>ESD</sub> | HBM        | 5000           | V    |

|                         |                  | MM         | 500            |      |

#### Table 4-3. D.C. Electrical Characteristics

| Parame            | ter                                                              | Symbol           | Conditions                                              | Min                 | Тур | Max                 | Unit |

|-------------------|------------------------------------------------------------------|------------------|---------------------------------------------------------|---------------------|-----|---------------------|------|

| Input low voltage | 9                                                                | V <sub>IL</sub>  | SCL, SDA, A0, A1, A2                                    | _                   | _   | 0.3 V <sub>CC</sub> | V    |

| Input high voltag | le                                                               | V <sub>IH</sub>  |                                                         | 0.7 V <sub>CC</sub> | _   | -                   | V    |

| Input leakage cu  | rrent                                                            | ILI              | $V_{IN} = 0$ to $V_{CC}$                                | _                   | _   | 10                  | μA   |

| Output leakage    | current                                                          | I <sub>LO</sub>  | $V_0 = 0$ to $V_{CC}$                                   | -                   | -   | 10                  | μA   |

| Output low volta  | ge $V_{OL}$ $I_{OL} = 0.15 \text{ mA}, V_{CC} = 1.8 \text{ V}$ ( |                  | 0.2                                                     | V                   |     |                     |      |

|                   |                                                                  |                  | I <sub>OL</sub> = 2.1 mA, V <sub>CC</sub> = 2.5 V       | -                   | -   | 0.4                 |      |

| Supply current    | Write                                                            | I <sub>CC1</sub> | V <sub>CC</sub> = 5.5 V, 400 kHz                        | -                   | _   | 3                   | mA   |

|                   |                                                                  | I <sub>CC2</sub> | V <sub>CC</sub> = 1.8 V, 100 kHz                        | -                   | _   | 1                   |      |

|                   | Read                                                             | I <sub>CC3</sub> | V <sub>CC</sub> = 5.5 V, 400 kHz                        | -                   | _   | 0.4                 |      |

|                   |                                                                  | I <sub>CC4</sub> | V <sub>CC</sub> = 1.8 V, 100 kHz                        | -                   | _   | 60                  | μA   |

| Stand-by current  |                                                                  | I <sub>CC5</sub> | $V_{CC} = SDA = SCL = 5.5 V,$<br>all other inputs = 0 V | _                   | -   | 5                   | μA   |

|                   |                                                                  | I <sub>CC6</sub> | $V_{CC} = SDA = SCL = 1.8 V,$<br>all other inputs = 0 V | _                   | -   | 1                   |      |

$(T_A = -25^{\circ}C \text{ to } + 70^{\circ}C \text{ (Commercial)}, -40^{\circ}C \text{ to } + 85^{\circ}C \text{ (Industrial)}, V_{CC} = 1.8 \text{ V to } 5.5 \text{ V})$

#### Table 4-3. D.C. Electrical Characteristics (Continued)

| Parameter                | Symbol           | Conditions                                                                     | Min | Тур | Max | Unit |

|--------------------------|------------------|--------------------------------------------------------------------------------|-----|-----|-----|------|

| Input capacitance        | C <sub>IN</sub>  | 25°C, 1MHz,<br>$V_{CC} = 5 V$ , $V_{IN} = 0 V$ ,<br>A0, A1, A2, SCL and WP pin | _   | _   | 10  | pF   |

| Input/Output capacitance | C <sub>I/O</sub> | 25°C, 1MHz,<br>$V_{CC} = 5 V, V_{I/O} = 0 V,$<br>SDA pin                       | _   | -   | 10  |      |

$(T_A = -25^{\circ}C \text{ to } + 70^{\circ}C \text{ (Commercial)}, -40^{\circ}C \text{ to } + 85^{\circ}C \text{ (Industrial)}, V_{CC} = 1.8 \text{ V to } 5.5 \text{ V})$

#### Table 4-4. A.C. Electrical Characteristics

$(T_A = -25^{\circ}C \text{ to } + 70^{\circ}C \text{ (Commercial)}, -40^{\circ}C \text{ to } + 85^{\circ}C \text{ (Industrial)}, V_{CC} = 1.8 \text{ V to } 5.5 \text{ V})$

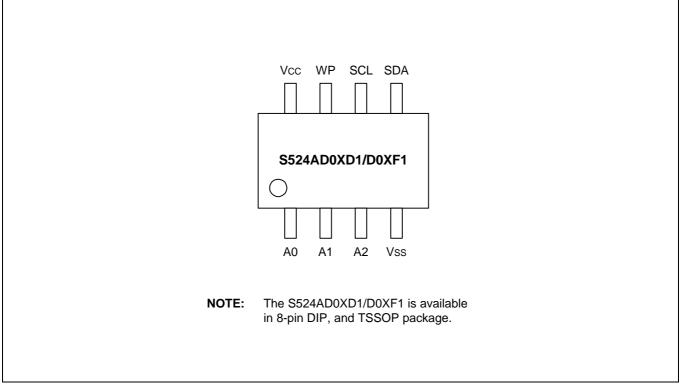

|                                                 |                     |                         | , , , |                        |     |                     |      |