# ICs for Communications

DUAL CHANNEL SLICOFI-2, SLIC DuSLIC

PEB 3265 Version 1.1 PEB 4265 Version 1.1 PEB 4266 Version 1.1

Preliminary Product Overview 10.99

| Revision History:                |                                 | Current Version: 10.99                       |

|----------------------------------|---------------------------------|----------------------------------------------|

| Previous Version:                |                                 |                                              |

| Page<br>(in previous<br>Version) | Page<br>(in current<br>Version) | Subjects (major changes since last revision) |

|                                  |                                 |                                              |

|                                  |                                 |                                              |

For questions on technology, delivery and prices please contact the Infineon Technologies Offices in Germany or the Infineon Technologies Companies and Representatives worldwide: see our webpage at http://www.infineon.com

November 19, 1999

ABM®, AOP®, ARCOFI®, ARCOFI®-BA, ARCOFI®-SP, DigiTape®, EPIC®-1, EPIC®-S, ELIC®, FALC®54, FALC®56, FALC®-E1, FALC®-LH, IDEC®, IOM®, IOM®-1, IOM®-2, IPAT®-2, ISAC®-P, ISAC®-S, ISAC®-S TE, ISAC®-P TE, ITAC®, IWE®, MUSAC®-A, OCTAT®-P, QUAT®-S, SICAT®, SICOFI®, SICOFI®-2, SICOFI®-4, SICOFI®-4µC, SLICOFI® are registered trademarks of Infineon Technologies AG.

ACE<sup>™</sup>, ASM<sup>™</sup>, ASP<sup>™</sup>, POTSWIRE<sup>™</sup>, QuadFALC<sup>™</sup>, SCOUT<sup>™</sup> are trademarks of Infineon Technologies AG.

#### Edition 10.99 Published by Infineon Technologies AG, TR, Balanstraße 73, 81541 München © Infineon Technologies 1999.

All Rights Reserved.

#### Attention please!

As far as patents or other rights of third parties are concerned, liability is only assumed for components, not for applications, processes and circuits implemented within components or assemblies.

The information describes the type of component and shall not be considered as assured characteristics.

Terms of delivery and rights to change design reserved.

Due to technical requirements components may contain dangerous substances. For information on the types in question please contact your nearest Infineon Technologies Office.

Infineon Technologies AG is an approved CECC manufacturer.

#### Packing

Please use the recycling operators known to you. We can also help you – get in touch with your nearest sales office. By agreement we will take packing material back, if it is sorted. You must bear the costs of transport. For packing material that is returned to us unsorted or which we are not obliged to accept, we shall have to invoice you for any costs incurred.

Components used in life-support devices or systems must be expressly authorized for such purpose!

Critical components<sup>1</sup> of the Infineon Technologies AG, may only be used in life-support devices or systems<sup>2</sup> with the express written approval of the Infineon Technologies AG.

- 1 A critical component is a component used in a life-support device or system whose failure can reasonably be expected to cause the failure of that life-support device or system, or to affect its safety or effectiveness of that device or system.

- 2 Life support devices or systems are intended (a) to be implanted in the human body, or (b) to support and/or maintain and sustain human life. If they fail, it is reasonable to assume that the health of the user may be endangered.

#### **Table of Contents**

| Page |

|------|

|------|

| 1<br>1.1<br>1.2<br>1.3                                     | Overview1-2Features1-4Typical Applications1-5Logic Symbols1-6                                                                                                                                                   |

|------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 2<br>2.1<br>2.2<br>2.3<br>2.3.1<br>2.3.2<br>2.3.3<br>2.3.4 | Functional Description2-1Functional Overview2-1BORSCHT Functions2-2DC Feeding2-5Constant Current Zone2-7Resistive Zone2-8Constant Voltage Zone2-9Programmable Voltage and Current Range of DC Characteristic2-9 |

| 2.3.5<br>2.3.6                                             | Programmable Voltage Reserve                                                                                                                                                                                    |

| 2.3.7                                                      | SLIC Power Dissipation                                                                                                                                                                                          |

| 2.4                                                        | AC Transmission Characteristics                                                                                                                                                                                 |

| 2.4.1                                                      | Transmit Path                                                                                                                                                                                                   |

| 2.4.2                                                      | Receive Path                                                                                                                                                                                                    |

| 2.4.3                                                      | Impedance Matching                                                                                                                                                                                              |

| 2.4.4                                                      | Transhybrid Balance                                                                                                                                                                                             |

| 2.5                                                        | Ringing                                                                                                                                                                                                         |

| 2.5.1                                                      | Ringer Load                                                                                                                                                                                                     |

| 2.5.2                                                      | Ring Trip                                                                                                                                                                                                       |

| 2.5.3                                                      | Ringing Methods                                                                                                                                                                                                 |

| 2.5.4                                                      | DuSLIC Ringing Options2-19                                                                                                                                                                                      |

| 2.5.5                                                      | Internal Balanced Ringing via SLICs 2-20                                                                                                                                                                        |

| 2.5.6                                                      | Internal Unbalanced Ringing with SLIC-P 2-21                                                                                                                                                                    |

| 2.5.7                                                      | External Unbalanced Ringing2-22                                                                                                                                                                                 |

| 2.6                                                        | Metering                                                                                                                                                                                                        |

| 2.6.1                                                      | Metering by 12/16 kHz Sinusoidal Bursts 2-22                                                                                                                                                                    |

| 2.6.2                                                      | Metering by Polarity Reversal2-24                                                                                                                                                                               |

| 2.6.2.1                                                    | Soft reversal 2-24                                                                                                                                                                                              |

| 2.7                                                        | Signaling (Supervision)                                                                                                                                                                                         |

| 2.8                                                        | DuSLIC Enhanced Signal processing Capabilities 2-26                                                                                                                                                             |

| 2.8.1                                                      | DTMF Generation and Detection 2-26                                                                                                                                                                              |

| 2.8.2                                                      | Caller ID Generation                                                                                                                                                                                            |

| 2.8.3                                                      | Line Echo Cancelling (LEC) 2-30                                                                                                                                                                                 |

| 2.8.4                                                      | Universal Tone Detection (UTD)2-31                                                                                                                                                                              |

| 2.9                                                        | Message Waiting Indication 2-33                                                                                                                                                                                 |

| 2.10                                                       | Three-party Conferencing                                                                                                                                                                                        |

| 2.11                                                       | 16 kHz Modes on PCM Highway 2-35                                                                                                                                                                                |

## DuSLIC

#### **Table of Contents**

| 3<br>3.1<br>3.2<br>3.3<br>3.4<br>3.4.1<br>3.4.2<br>3.4.3<br>3.4.3.1<br>3.4.3.2<br>3.4.3.3<br>3.4.3.4<br>3.4.3.5<br>3.5<br>3.5.1<br>3.5.2<br>3.5.3<br>3.5.4 | Operational Description3-1Operating Modes for the DuSLIC Chipset3-1Operating Modes for SLICOFI-2 and SLIC-E3-3Operating Modes for SLICOFI-2 and SLIC-P3-5Operating Modes and Power Management3-7Introduction3-7Power Dissipation of the SLICOFI-23-8Power Dissipation of the SLICOFI-23-9Power Down Modes3-9Active Mode3-9SLIC Power Consumption Calculation in Active Mode3-10Ringing Modes3-15SLIC Power Consumption Calculation in Ringing Mode3-17Test Modes3-21Introduction3-21Conventional Line Testing3-22Test Loops3-25 |

|------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 4<br>4.1<br>4.1.1<br>4.1.2<br>4.2<br>4.3<br>4.4<br>4.5                                                                                                     | Interfaces4-1PCM Interface with a Serial Microcontroller Interface4-1PCM Interface4-1Serial Microcontroller Interface4-4The IOM-2 Interface4-5TIP/RING Interface4-8SLICOFI-2 and SLIC-E Interface4-9SLICOFI-2 and SLIC-P Interface4-10                                                                                                                                                                                                                                                                                          |

| 5<br>5.1<br>5.1.1<br>5.1.2<br>5.2<br>5.2.1<br>5.2.2<br>5.3<br>5.4                                                                                          | Electrical Characteristics5-1Electrical Characteristics PEB 4265 (SLIC-E)5-1Absolute Maximum Ratings PEB 42655-1Operating Range PEB 42655-2Electrical Characteristics PEB 4266 (SLIC-P)5-3Absolute Maximum Ratings PEB 42665-3Operating Range PEB 42665-3Operating Range PEB 42665-3Operating Range PEB 42665-4AC Transmission DuSLIC5-5DC Characteristics5-9                                                                                                                                                                   |

| 6<br>6.1<br>6.1.1<br>6.2<br>6.2.1<br>6.3                                                                                                                   | Application Circuits6-1Balanced Ringing6-1Protection Circuit for SLIC-E and SLIC-S6-2Unbalanced Ringing6-4Protection Circuit for SLIC-P6-5External Unbalanced Ringing with DuSLIC-S/E/P6-7                                                                                                                                                                                                                                                                                                                                      |

## List of Figures

| Page |

|------|

|------|

| Figure 1-1  | DuSLIC-E and DuSLIC-P Chip Set 1-3                                     |

|-------------|------------------------------------------------------------------------|

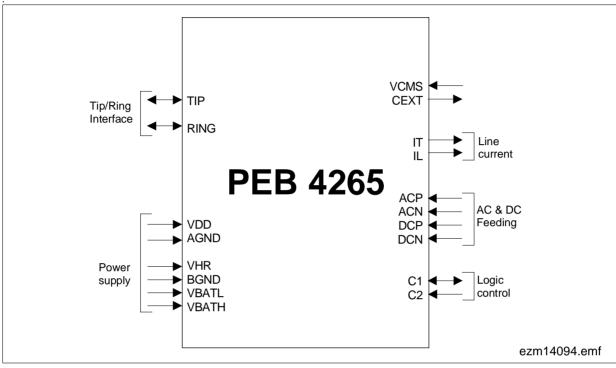

| Figure 1-2  | Logic Symbol SLIC-E 1-6                                                |

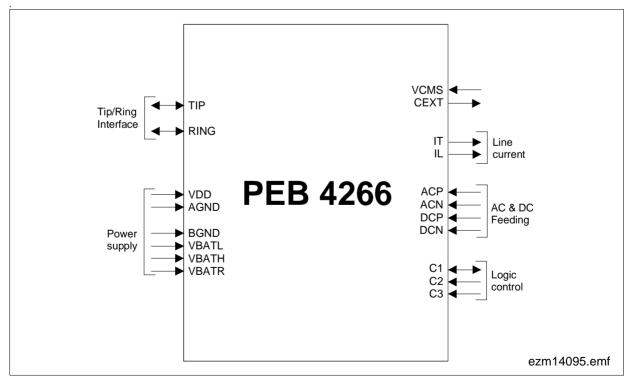

| Figure 1-3  | Logic Symbol SLIC-P1-6                                                 |

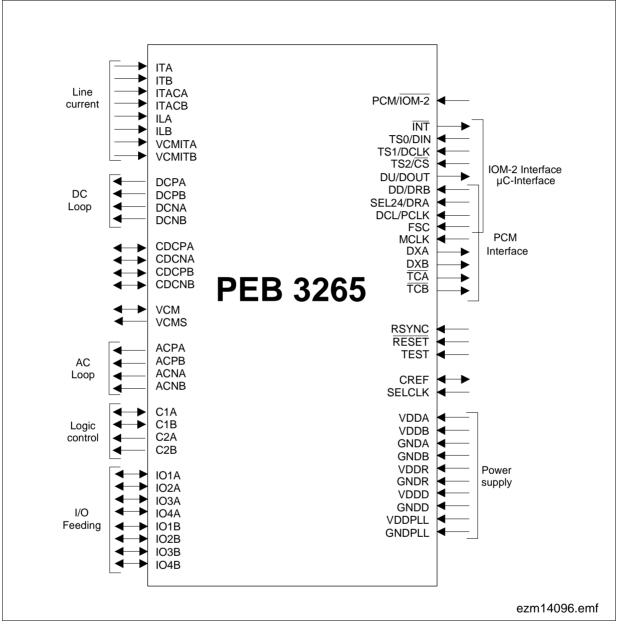

| Figure 1-4  | Logic Symbol SLICOFI-2 1-7                                             |

| Figure 2-1  | Typical Line Circuit Functions                                         |

| Figure 2-2  | Signal Paths - DC Feeding                                              |

| Figure 2-3  | DC Feeding Characteristic                                              |

| Figure 2-4  | Constant Current Zone                                                  |

| Figure 2-5  | Resistive Zone                                                         |

| Figure 2-6  | Constant Voltage Zone 2-9                                              |

| Figure 2-7  | DC Characteristic (Detailed Description)                               |

| Figure 2-8  | TTX Voltage Reserve Schematic                                          |

| Figure 2-9  | DC Feeding Characteristics (ACTH, ACTR)                                |

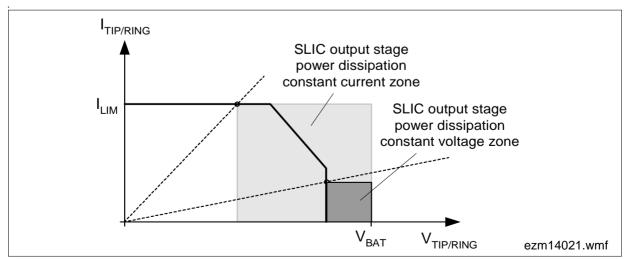

| Figure 2-10 | Power Dissipation                                                      |

| Figure 2-11 | Signal Paths - AC Transmission                                         |

| Figure 2-12 | Signal Flow in Voice Channel (A)                                       |

| Figure 2-13 | 2/4-wire Conversion in the Hybrid Circuit                              |

| Figure 2-14 | Typical Ringer Loads of 1 and 5 REN used in US                         |

| Figure 2-15 | Balanced Ringing via SLIC-E and SLIC-P                                 |

| Figure 2-16 | Unbalanced Ringing Signal                                              |

| Figure 2-17 | Teletax Injection and Metering                                         |

| Figure 2-18 | Soft Reversal (Example for Open Loop)                                  |

| Figure 2-18 | DuSLIC AC Signal Path                                                  |

| Figure 2-19 | Bellcore On-hook Caller ID Physical Layer Transmission 2-30            |

| 0           |                                                                        |

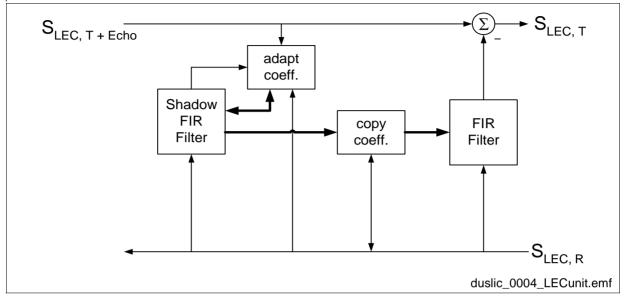

| Figure 2-21 | Line Echo Cancellation Unit - Block Diagram                            |

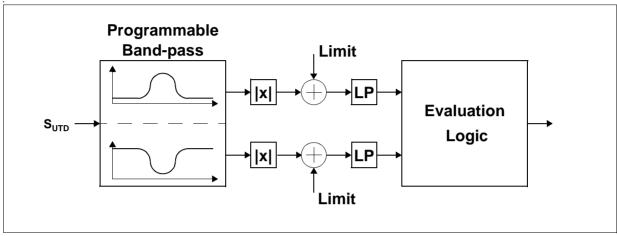

| Figure 2-22 | UTD Functional Block Diagram                                           |

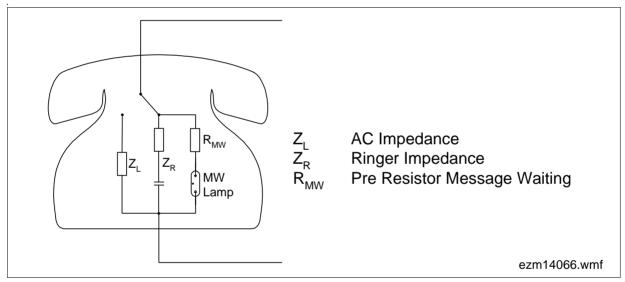

| Figure 2-23 | MWI Circuitry with Glow Lamp                                           |

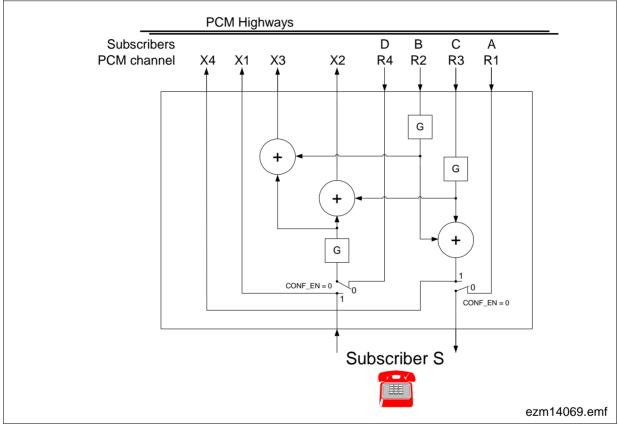

| Figure 2-24 | Conference Block for one DuSLIC Channel                                |

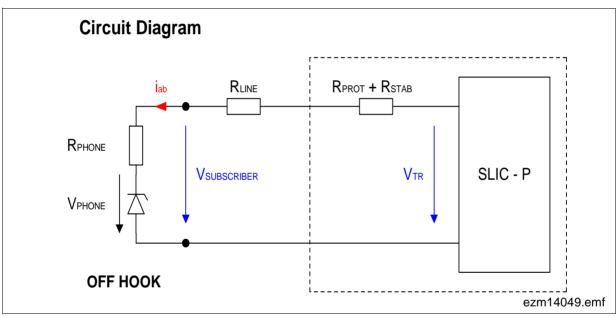

| Figure 3-1  | Circuit Diagram for Power Consumption                                  |

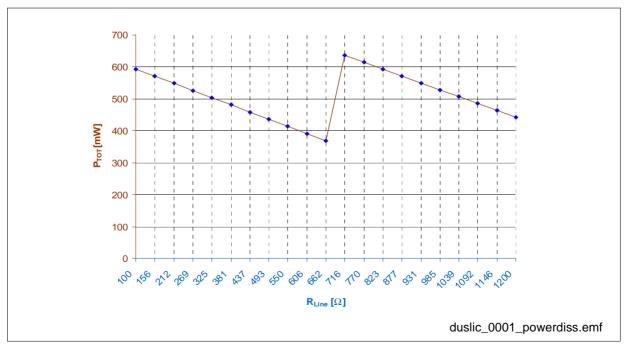

| Figure 3-2  | SLIC-E Power Dissipation with switched Battery Voltage                 |

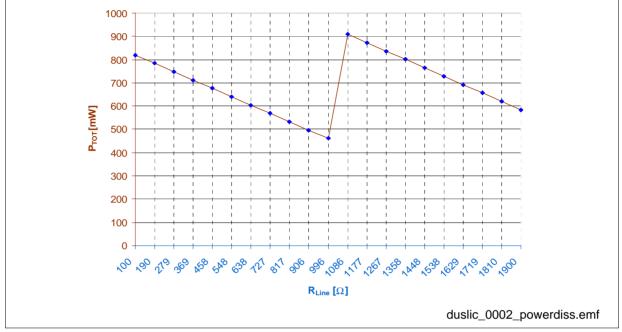

| Figure 3-3  | SLIC-P Power Dissipation (Switched Battery Voltage, Long loops) 3-13   |

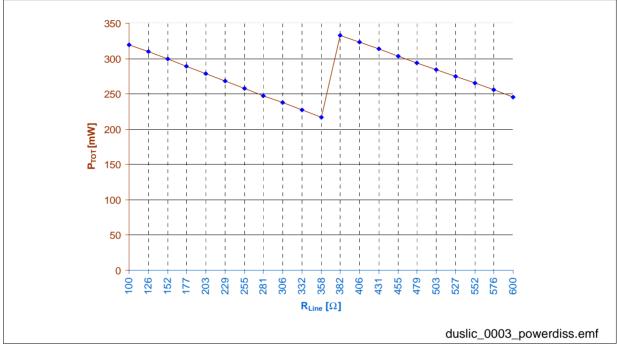

| Figure 3-4  | SLIC-P Power Dissipation (Switched Battery Voltage, Short Loops). 3-15 |

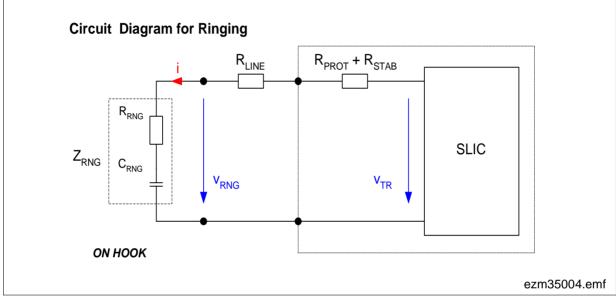

| Figure 3-5  | Circuit Diagram for Ringing                                            |

| Figure 3-6  | Capacitance Measurement                                                |

| Figure 3-7  | Resistance Measurement                                                 |

| Figure 3-8  | SLICOFI-2 Testloops                                                    |

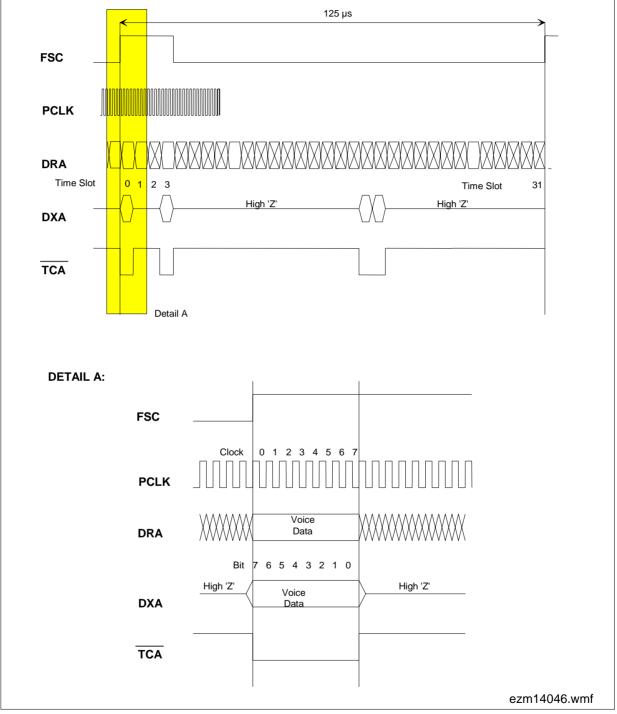

| Figure 4-1  | General PCM Interface Timing                                           |

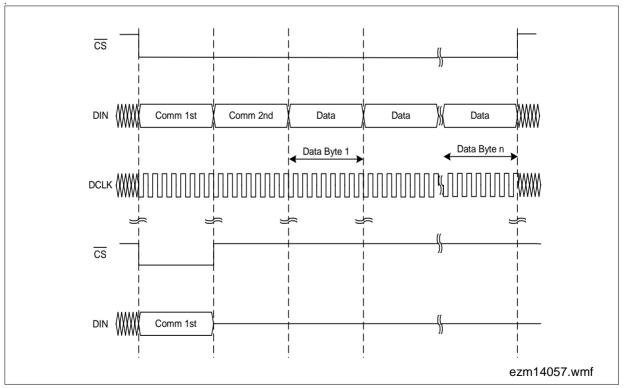

| Figure 4-2  | Serial $\mu$ C Int Write Acc. (n Data Bytes and Single Byte Com.) 4-4  |

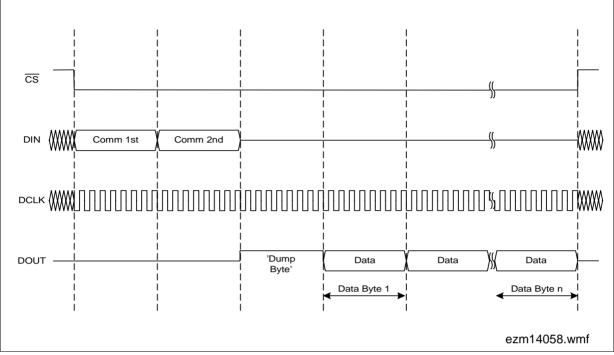

| Figure 4-3  | Serial µC Interface - Read Acc. (n Data Bytes Transfered) 4-5          |

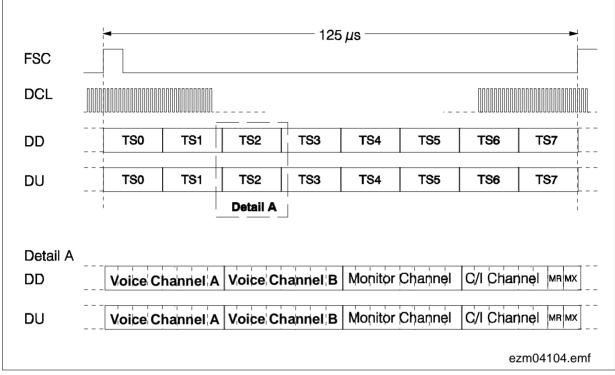

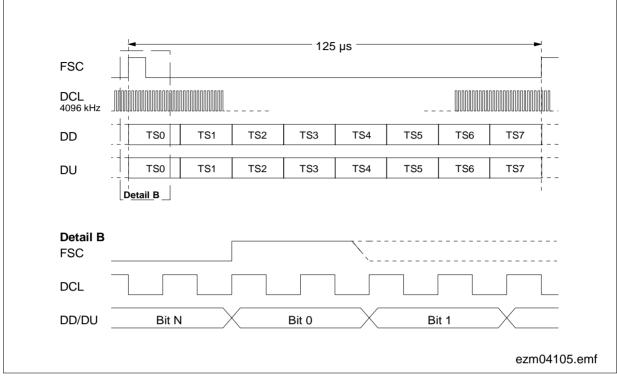

| Figure 4-4  | IOM-2 Int. Timing for up to 16 Voice Channels (Per 8 kHz Frame) 4-6    |

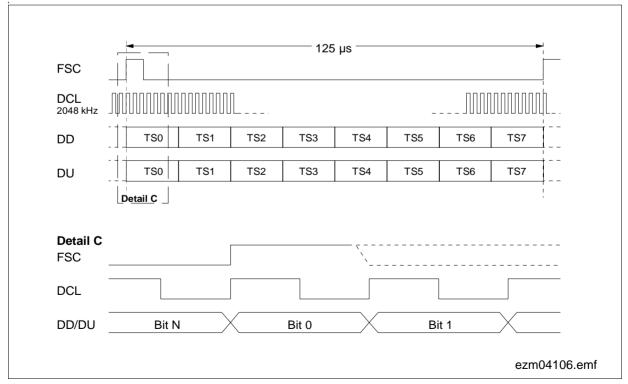

| Figure 4-5  | IOM-2 Interface Timing (DCL=4096 kHz, Per 8 kHz Frame) 4-7             |

| Figure 4-6  | IOM-2 Interface Timing (DCL = 2048 kHz, Per 8 kHz Frame) 4-7           |

## List of Figures

## Page

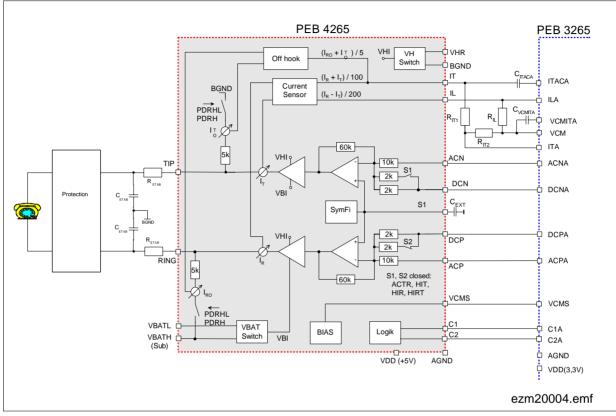

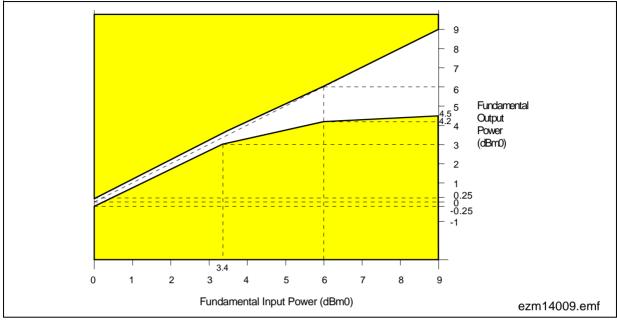

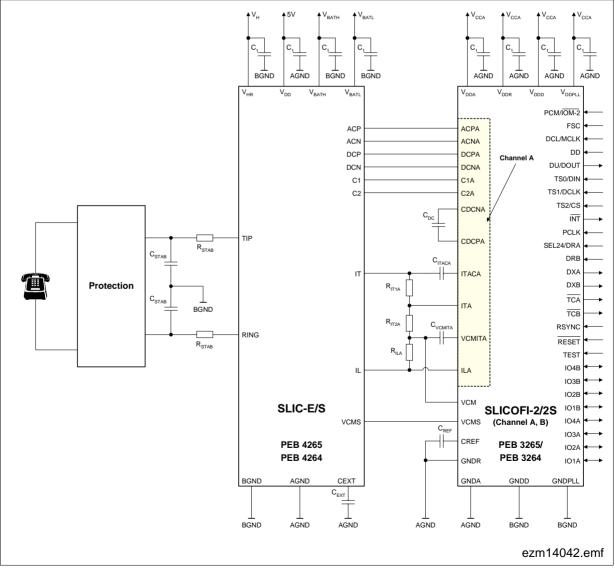

| Figure 4-7<br>Figure 4-8<br>Figure 5-1 | Minimal Application Circuit SLICOFI-2 and SLIC-E                                                                                                                  |

|----------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Figure 6-1<br>Figure 6-2<br>Figure 6-3 | Application Circuit, Internal Balanced Ringing                                                                                                                    |

| Figure 6-4<br>Figure 6-5<br>Figure 6-6 | Typical Overvoltage Protection for SLIC-P6-5Application Circuit, External Unbalanced Ringing6-7Application Circuit, External Unbalanced Ringing for Long Loops6-8 |

## Preface

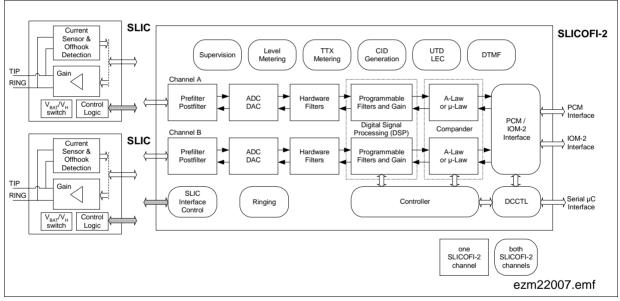

The DuSLIC chip set consists of a programmable dual channel SLICOFI<sup>®</sup>-2 CODEC and two single channel high-voltage SLIC chips.

### **Organization of this Document**

This Preliminary Product Overview is divided into six chapters. It is organized as follows:

- Chapter 1, Overview

A general description of the product, list of its key features and some typical applications.

- Chapter 2, Functional Description The main functions are presented following a functional block diagram.

- Chapter 3, Operational Description A brief description of the three operating modes: power down, active and ringing (plus signal monitoring techniques).

- Chapter 4, Interfaces Connection information including standard IOM<sup>®</sup>-2 and PCM interface timing frames and pins.

- Chapter 5, Electrical Characteristics Parameters, symbols and limit values.

- Chapter 6, Application Circuits Illustrations of balanced ringing, unbalanced ringing and protection circuits.

## 1 Overview

DuSLIC is a chip set, comprising one dual channel SLICOFI-2 CODEC and two singlechannel SLIC chips. It is a highly flexible CODEC/SLIC solution for an analog line circuit and is widely programmable. Users can now access different markets with a single hardware design that meets all different standards worldwide.

The interconnections between the single channel high-voltage SLIC (170 V process) and the dual channel SLICOFI-2 CODEC (advanced CMOS process) are a seamless fit. This guarantees maximum transmission performance with a minimum of necessary components.

Currently there are three DuSLIC chip sets available:

DuSLIC-S (Standard), DuSLIC-E (Extended) and DuSLIC-P (Power Management). Optimized for different applications the main differences are in ringing features, power management and additional functions like DTMF recognition, Caller ID generation or Universal Tone Detection (UTD).

For DuSLIC-E and DuSLIC-S additionally the different performance versions DuSLIC-E2 and DuSLIC-S2 are available.

This document describes the DuSLIC-E and DuSLIC-P chip sets. For the other chip sets see our "DuSLIC Chip Set Selection Guide".

All line circuit functions are implemented on the chip set:

- BORSCHT functions

- Max. 85 V<sub>RMS</sub> sinusoidal ringing generation

- Metering by Polarity Reversal and by 12/16 kHz Sinusoidal Bursts

- Dual-Tone Multifrequency (DTMF) detection and generation

- Caller ID generation.

- Universal Tone Detection (UTD) unit for fax-/modemtone detection

- Line Echo Cancellation unit

Integrated battery switches guarantee minimum power consumption during the off-hook, on-hook and ringing modes. Test and diagnosis functions have been integrated to simplify testing. No external test equipment except one relay is needed for either subscriber line testing in the field or board testing during production or in the field.

The employment of SLIC-E or SLIC-P depends on the application. SLIC-E (PEB 4265) is optimized for access network requirements, while the power management SLIC-P (PEB 4266) is an enhanced version for extremely power-sensitive applications or when internal unbalanced ringing is required.

#### **DuSLIC Architecture**

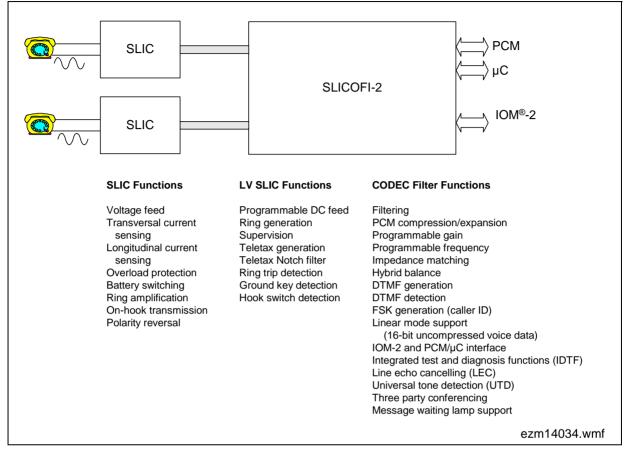

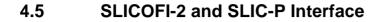

Unlike traditional designs, DuSLIC splits the SLIC function into high-voltage SLIC functions and low-voltage SLIC functions.

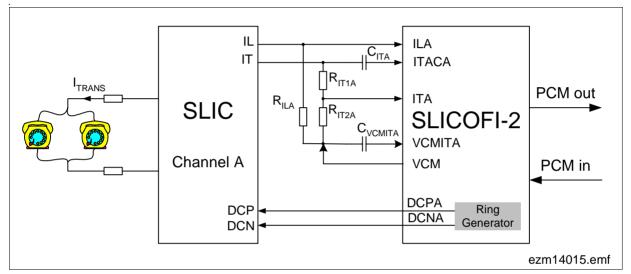

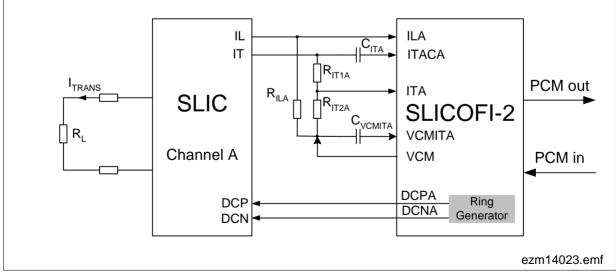

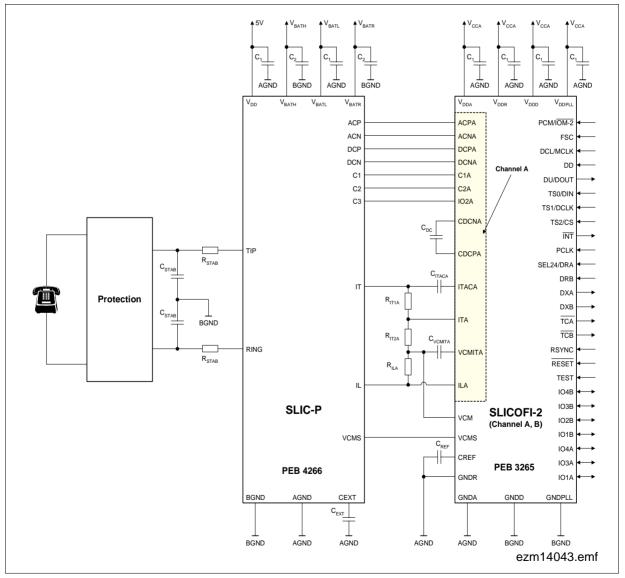

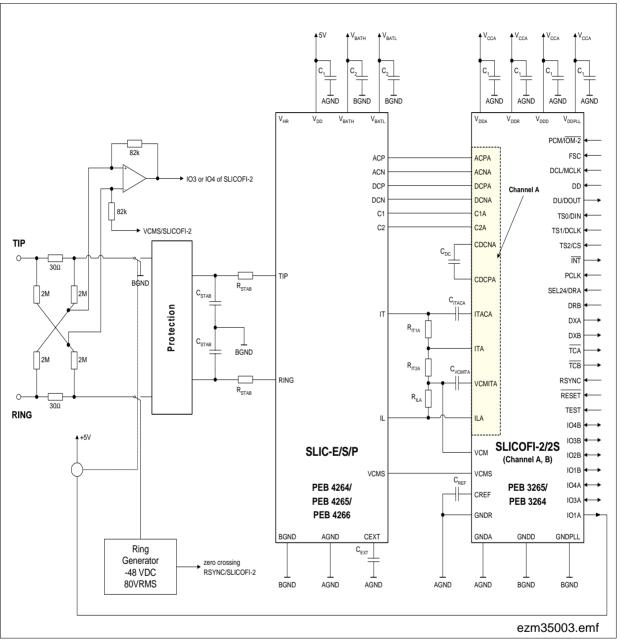

The low voltage functions are handled in the SLICOFI-2 device. The partitioning of the functions is shown in **Figure 1-1**. For further information see **Chapter 2.2**.

## DuSLIC

#### Overview

Figure 1-1 DuSLIC-E and DuSLIC-P Chip Set

PEB 4265 (SLIC-E)

PEB 3265 (SLICOFI-2)

Туре

## **DUAL CHANNEL SLICOFI-2, SLIC** DuSLIC

## Version 1.0

Infineon

#### 1.1 Features

- Internal unbalanced/balanced ringing capability up to 50  $V_{RMS}$ /85  $V_{RMS}$

- Programmable Teletax (TTX) generation

- Programmable battery feed with cabability for driving longer loops

- Fully programmable dual-channel CODEC

- Ground/loop start signaling

- Polarity reversal

- Integrated test and diagnosis functions

- On-hook transmission

- Integrated DTMF generator

- Integrated DTMF decoder

- Integrated caller ID (FSK) generator

- Optimized filter structure for modem transmission

- Integrated Line Echo Cancellation unit

- Integrated fax/modem detection

- Three party conferencing (in PCM/µC mode)

- Message waiting lamp support (PBX)

- Power optimized architecture

- Power Management capability (integrated battery switches)

- 8 and 16 kHz PCM Transmission

- Specification in accordance with ITU-T Recommendation Q.552 for Z-interface and applicable LSSGR

P-DSO-20-5

1-4

Package

P-MQFP-64-1

P-DSO-20-5

P-DSO-20-5

**PEB 3265 PEB 4265 PEB 4266**

## 1.2 Typical Applications

The Infineon Technologies DuSLIC family is particularily designed for all access network applications but adresses all major telephone applications including:

- Digital Loop Carrier

- Wireless Local Loop

- Fiber in the Loop

- Private Branch Exchange

- Intelligent NT (Network Terminations) for ISDN

- ISDN Terminal Adapters

- Central Office

- Voice over IP

## 1.3 Logic Symbols

Figure 1-2 Logic Symbol SLIC-E

Figure 1-3 Logic Symbol SLIC-P

Figure 1-4 Logic Symbol SLICOFI-2

## 2 Functional Description

## 2.1 Functional Overview

The DuSLIC chip set is a cost-effective, high-performance solution that provides the BORSCHT functions of an analog line circuit. DuSLIC has the advantage of offering all the functions integrated in a single channel high-voltage SLIC and in a dual channel DSP-based CODEC.

An important feature of the DuSLIC design is the fact that all the SLIC and CODEC functions are programmable via the dual-channel CODEC device. Conventional designs need a number of external components to adapt the circuit for use in different countries and applications. In contrast, the configuration software DuSLICOS can be used to program the following functions of the DuSLIC chip set:

- DC (battery) feed characteristics

- AC impedance matching

- Transmit gain

- Receive gain

- Hybrid balance

- Frequency response in transmit and receive direction

- Ring frequency and amplitude

- Hook thresholds

- DTMF and FSK

- Universal Tone Detection

- Line Echo Cancellation

- Testfunctions

- TTX modes

One of the main challenges of linecard development is to adapt the above-mentioned functions to country-specific requirements. These adaptations used to be handled by hardware, an approach that required a different linecard board for every modification to a specification.

Because signal processing within the SLICOFI-2 is completely digital, it is possible to adapt to the requirements listed above by simply updating the coefficients that control DSP processing of all data. This means, for example, that changing impedance matching or hybrid balance no longer requires hardware modifications. The same hardware is now capable of meeting the requirements of different markets. The digital nature of the filters and gain stages also assures high reliability, no drifts (over temperature or time) and minimal variations between different lines.

The characteristics for the two voice channels within SLICOFI-2 can be programmed independently of each other. The DuSLICOS software is provided to automate calculation of coefficients to match different requirements. DuSLICOS also verifies the calculated coefficients.

## 2.2 BORSCHT Functions

- B Battery feed

- O Overvoltage protection

- **R** Ringing

- S Signaling (supervision)

- C Coding

- H Hybrid for 2/4-wire conversion

- T Testing

**Figure 2-1** shows the BORSCHT functions with the other function blocks normally required for an analog line circuit.

Figure 2-1 Typical Line Circuit Functions

The following paragraphs explain the advantages of using DuSLIC to implement the BORSCHT functions.

## **Battery Feed**

An analog line circuit provides the voltage and current for subscriber equipment. In conventional line circuits, extra hardware is needed to adapt the battery feed characteristics to the requirements for different applications and countries. With the DuSLIC chip set, the battery feed (DC) characteristics can be programmed in the SLICOFI-2 (low-voltage SLIC function, see **Figure 1-1**) and applied to the line via the SLIC.

#### **Overvoltage Protection**

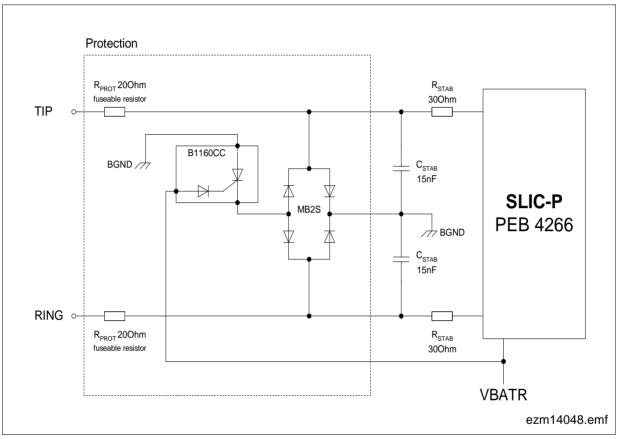

Overvoltage protection is indispensable to prevent damage to the line circuit if the system is exposed to high voltages that can result from power lines crossing or lightning strikes. The robust 170 V SLIC technology together with the external low cost protection network, consisting of varistors, resistors and thyristor diodes, form a reliable overvoltage protection solution. If an overvoltage occurs, the protection network separates the DuSLIC from the Tip and Ring lines.

## Ringing

The ringing signal is a low-frequency, high-voltage signal to the subscriber equipment. In conventional line circuits, the ringing voltage (40  $V_{RMS}$  to 85  $V_{RMS}$ ) is generated in an external ringing generator and applied to the Tip and Ring lines by a relay. With the DuSLIC chip set, the ringing generator is integrated and this relay is not needed. This saves space and costs in the line circuit design. The ringing signal is generated in the low-voltage SLICOFI-2 and amplified in the high-voltage SLIC. DuSLIC supports balanced and unbalanced ringing. With balanced ringing, the ringing voltage is applied differentially to the Tip and Ring lines. With unbalanced ringing, the ringing voltage is applied single-ended to either the Tip or Ring line against a potential which is near ground (for details see "Ringing Modes" on page 3-15). Balanced ringing is generated by SLIC-E, while SLIC-P can generate both balanced and unbalanced ringing.

## Signaling (Supervision)

DuSLIC must detect when a subscriber changes from on-hook mode to off-hook mode in both non-ringing (hook switch detection) and ringing modes (ring trip detection). With this chip set, the thresholds for ring trip detection can be programmed in SLICOFI-2 to suit applications without using external components.

## Coding

SLICOFI-2 encodes an analog input signal to a digital PCM signal and decodes a PCM signal to an analog signal. Both A-law and  $\mu$ -law coding is supported and can be selected via software.

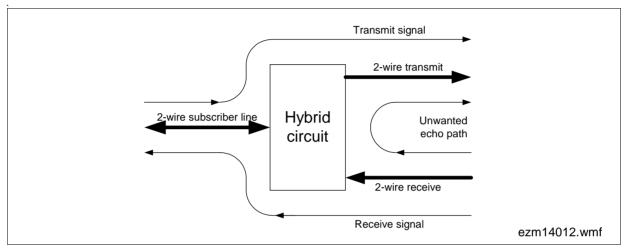

#### Hybrid for 2/4-wire Conversion

The subscriber equipment is connected to a 2-wire interface (Tip and Ring) where information is transmitted bidirectionally. For digital transmission through the switching network, the information must be split into separate transmit and receive paths (4 wires). To avoid generating echoes, the hybrid function requires a balanced network matched to the line impedance. Hybrid balancing can be programmed in the DuSLIC device without using any external components.

## Testing

Access to the analog loop is necessary to perform the regular measurements involved in monitoring the local loop. Line circuit functions must also be tested. In conventional line circuit solutions, test units have to be switched to perform loop and line circuit tests. A remote testing unit and relays are normally necessary to perform a full range of tests. DuSLIC already offers a number of internal test features to check both the local loop and the line circuit.

## Additional Line Circuit Functions:

## **Teletax Metering**

In many countries, Teletax metering signals (TTX signals) are sent to the subscriber for billing purposes. A 12/16 kHz sinusoidal metering burst has to be transmitted. As soon as metering pulses are applied to the subscriber line, they also divert to the transmit signal path which means that a notch filter has to block the 12/16 kHz signal to prevent overloading the transmit A/D converter. In contrast to conventional line circuits, the DuSLIC chip set generates the metering signal internally. The fact that the notch filter is integrated is one of the big advantages of DuSLIC.

## DTMF

A DTMF signal is used for touchtone signaling from a subscriber to the Central Office. Each digit is represented by a pair of tones. DuSLIC has an integrated DTMF decoder. The decoder monitors the transmit path for valid tone pairs and outputs the corresponding digital code for each pair. DuSLIC also has an integrated DTMF generator comprising two tone generators.

## Caller ID Frequency Shift Keying (FSK) Modulator

Caller ID is used to provide caller information to the subscriber during on-hook transmission. DuSLIC has an integrated FSK modulator capable of sending caller ID information. The caller ID modulator complies with all requirements of ITU-T recommendation V.23 and Bell 202.

## **Universal Tone Detection Unit (UTD)**

An Universal Tone Detection unit can be used to detect special tones, e.g. fax- or modem-tones. This is e.g. useful for activating the optimized filter coefficient set for modem transmission.

## Line Echo Cancellation Unit (LEC)

An adaptive Line Echo Cancellation unit can be used for the cancellation of near end echos.

## 2.3 DC Feeding

Analog telephones need a DC current in the off-hook state. AC speech signals in the receive and transmit directions are superimposed on this DC current.

Once the off-hook state has been detected, the SLIC must supply a DC current to the subscriber line. The current is typically in the range of 14 to 40 mA, depending on local country specifications. Conventional linecard solutions require additional hardware to adjust the DC feed current to meet different country specifications.

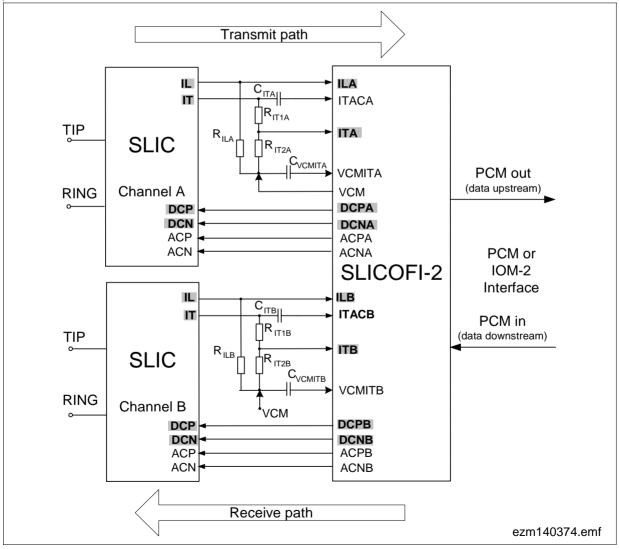

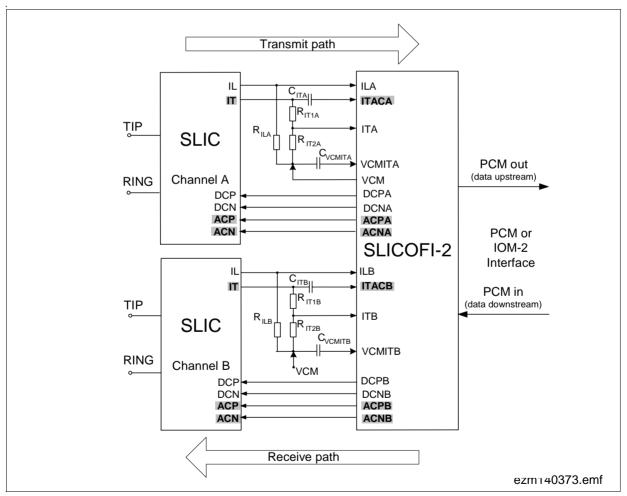

By contrast, DC feeding with the SLICOFI-2 is fully programmable. Special digital filter technology offers an extremely cost-effective solution that is far more flexible than analog DC feeding circuits. The DC feeding characteristic in SLICOFI-2 is programmed using software coefficients. **Figure 2-2** shows the signal paths for DC feeding between the SLIC's and SLICOFI-2:

Figure 2-2 Signal Paths - DC Feeding

## **DC Characteristic Feeding Zones**

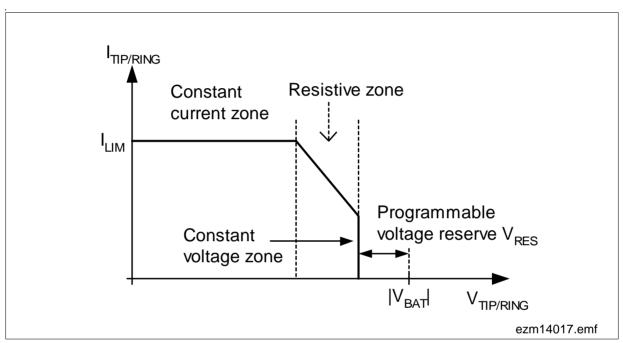

The DuSLIC DC feeding characteristic has three different zones: the constant current zone, the resistive zone and the constant voltage zone. A programmable voltage reserve can be selected to avoid clipping the high AC signals (e.g. TTX) and to take into account the voltage drop of the SLIC (see **Chapter 2.3.5**). The DC feeding characteristic is shown in **Figure 2-3**.

#### Figure 2-3 DC Feeding Characteristic

The simplified diagram shows the constant current zone as an ideal current source with an infinite internal resistance, while the constant voltage zone is shown as an ideal voltage source with an internal resistance of 0  $\Omega$ . For the specification of the internal resistances see **Chapter 2.3.4**

## DuSLIC

#### **Functional Description**

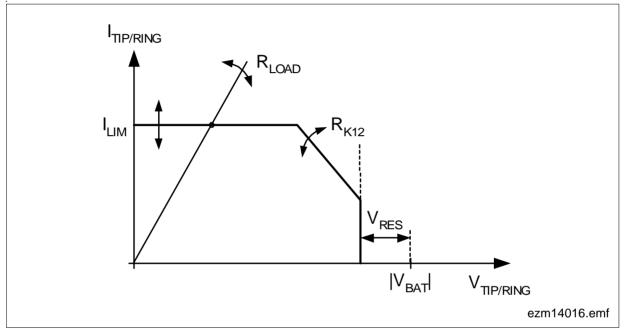

## 2.3.1 Constant Current Zone

In the off-hook state, the feed current must usually be kept at a constant value independent of load (see **Figure 2-4**). The SLIC senses the DC current and supplies this information to SLICOFI-2 via the IT pin (input pin for DC control). SLICOFI-2 compares the actual current with the programmed value and adjusts the SLIC drivers as necessary.  $I_{\text{TIP/RING}}$  in the constant current zone is programmable from 0 to 32 mA.

#### Figure 2-4 Constant Current Zone

Depending on the load, the operating point is determined by  $V_{\text{TIP}/\text{RING}}$  between the Tip and Ring pins.

The operating point is calculated from:

$V_{\text{TIP/RING}} = R_{\text{LOAD}} \times I_{\text{TIP/RING}}$

#### where

$R_{LOAD} = R_{PRE} + R_{LINE} + R_{PHONE,OFFHOOK}$

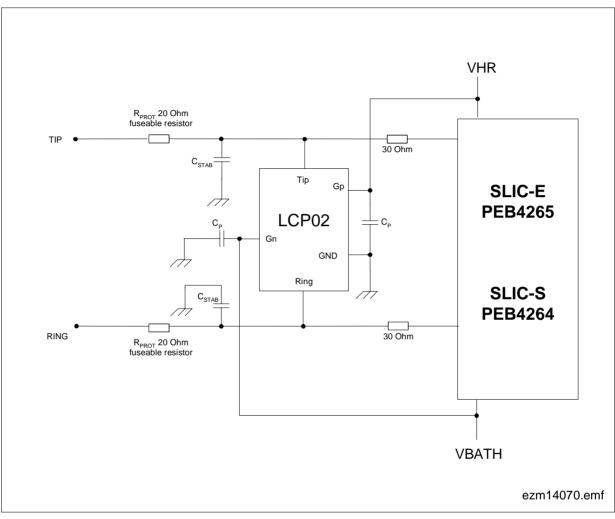

$R_{PRE} = R_{PROT} + R_{STAB}$  (see **Figure 6-1**, page 6-1 and **Figure 6-2**, page 6-2).

The lower the load resistance, the lower the voltage between the Tip and Ring pins.

## \_\_\_\_\_

**DuSLIC**

#### **Functional Description**

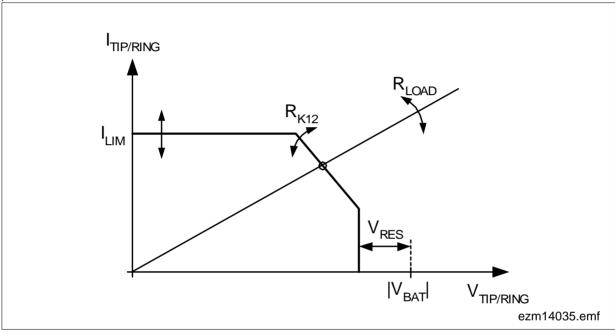

## 2.3.2 Resistive Zone

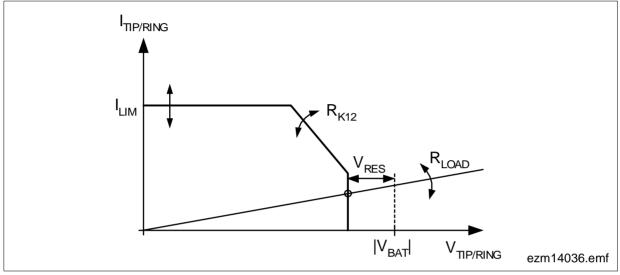

The programmable resistive zone of SLICOFI-2 provides extra flexibility over a wide range of applications. The resistive zone is used for very long lines where the battery is incapable of feeding a constant current into the line.

The operating point in this case crosses from the constant current zone for low and medium impedance loops to the resistive zone for high impedance loops (see **Figure 2-5**). The resistance of the zone  $R_{K12}$  is programmable from  $R_{PRE}$  to 1000  $\Omega$ .

Figure 2-5 Resistive Zone

**DuSLIC**

#### **Functional Description**

## 2.3.3 Constant Voltage Zone

The constant voltage zone is used in some applications to supply current through the line. In this case  $V_{\text{TIP/RING}}$  is constant (see **Figure 2-6**) and the current depends on the load between the Tip and Ring pins.

Figure 2-6 Constant Voltage Zone

## 2.3.4 Programmable Voltage and Current Range of DC Characteristic

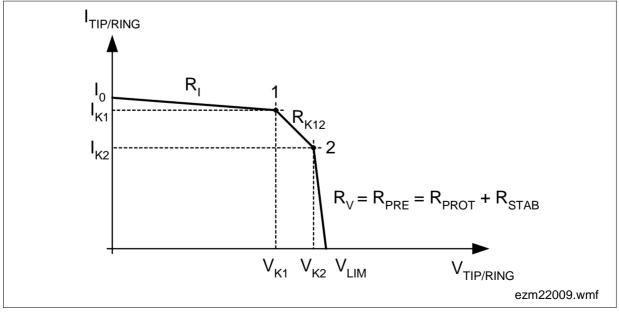

In the above chapters the idealized DC characteristics were shown. A detailed description is given in **Figure 2-7**.

Figure 2-7 DC Characteristic (Detailed Description)

In the constant current zone a finite resistor value of typically  $R_1 = 10 \text{ k}\Omega$  is usually applied for stability reasons.

In the constant voltage zone an internal resistor value of 0  $\Omega$  is applied.

The external resistors  $R_{PRE} = R_{Stab} + R_{Prot}$  necessary for stability and protection define the resistance  $R_V$  seen at the RING and TIP wires of the application.

The programmable range of the parameters  $R_I$ ,  $I_0$ ,  $I_{K1}$ ,  $V_{K1}$ ,  $R_{K12}$  and  $V_{LIM}$  is given in **Table 2-1**.

| Symbol           | Programmable Range                                                              | Condition                                 |  |

|------------------|---------------------------------------------------------------------------------|-------------------------------------------|--|

| R <sub>I</sub>   | 1.8 kΩ 40 kΩ                                                                    |                                           |  |

| I <sub>0</sub>   | 0 32 mA                                                                         |                                           |  |

| I <sub>K1</sub>  | 0 32 mA                                                                         |                                           |  |

| V <sub>K1</sub>  | 0 50 V                                                                          |                                           |  |

|                  | $V_{K1} < V_{LIM} - I_{K1} \cdot R_{K12}$                                       | only (V <sub>K1</sub> , I <sub>K1</sub> ) |  |

|                  | $V_{K1} < V_{LIM} - I_{K1} \cdot R_V$ $V_{K1} > V_{LIM} - I_{K1} \cdot R_{K12}$ | $(V_{K1}, I_{K1})$ and $(V_{K2}, I_{K2})$ |  |

| R <sub>K12</sub> | $R_{V}$ 1000 $\Omega$                                                           |                                           |  |

| V <sub>LIM</sub> | 0 50 V                                                                          |                                           |  |

|                  | $V_{\text{LIM}} > V_{\text{K1}} + I_{\text{K1}} \cdot R_{\text{K12}}$           | only (V <sub>K1</sub> , I <sub>K1</sub> ) |  |

Table 2-1 DC Characteristic

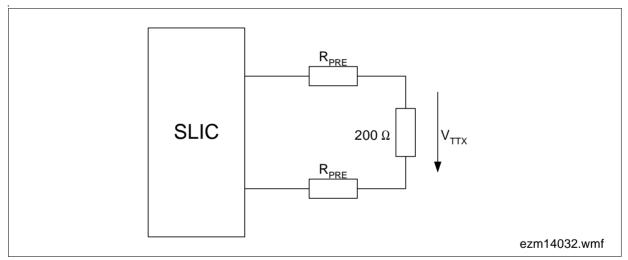

## 2.3.5 Programmable Voltage Reserve

To avoid clipping AC speech signals as well as AC metering pulses, a programmable voltage reserve  $V_{RES}$  (see **Figure 2-3**) has to be provided.

V<sub>RES</sub> consists of:

- Voltage reserve of the SLIC output buffers: this voltage drop depends on the output current through the Tip and Ring pins. For a standard output current of 25 mA, this voltage reserve is a few volts (see **Table 3-5**).

- Voltage reserve for AC speech signals: 2 V

- Voltage reserve for AC metering pulses: The TTX signal amplitude V<sub>TTX</sub> depends on local specifications and varies from 0.1 V<sub>RMS</sub> to several V<sub>RMS</sub> at a load of 200 Ω. To obtain V<sub>TTX</sub> = 2 V<sub>RMS</sub> at a load of 200 Ω and R<sub>PRE</sub> = 50 Ω (R<sub>PRE</sub> = R<sub>PROT</sub> + R<sub>STAB</sub> (see Figure 6-2, page 6-2)), 3 V<sub>RMS</sub> = 4.24 V<sub>PEAK</sub> are needed at the SLIC output.

$V_{RES}$  must therefore be programmed to 10.24 V (= 4 V (SLIC drop for peak current of DC and speech and TTX) + 2 V (AC speech signals) + 4.24 V (TTX-signal)).

Figure 2-8 TTX Voltage Reserve Schematic

## DuSLIC

#### **Functional Description**

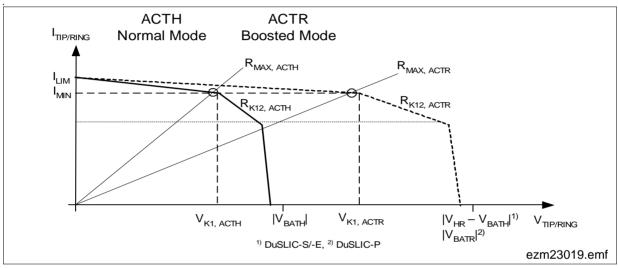

## 2.3.6 Extended Battery Feeding

If the battery voltage is not sufficient to supply the minimum required current through the line even in the resistive zone, an auxiliary positive battery voltage is used to expand the possible voltage amplitude between Tip and Ring. With this voltage ( $V_{HR} - V_{BATH}$ ), it is possible to supply the constant current through very long lines. **Figure 2-9** shows the DC feeding impedances  $R_{MAX,ACTH}$  in ACTH mode and  $R_{MAX,ACTR}$  in ACTR mode (for ACTH and ACTR modes see **Chapter 3.1**).

Figure 2-9 DC Feeding Characteristics (ACTH, ACTR)

## 2.3.7 SLIC Power Dissipation

The power dissipation in the SLIC can be estimated by the power dissipation in the output stages (see **Chapter 3.4.3**). The power dissipation can be calculated from:

$$\mathsf{P}_{\mathsf{SLIC}} \thicksim (\mathsf{V}_{\mathsf{BAT}} \textbf{-} \mathsf{V}_{\mathsf{TIP/RING}}) \And \mathsf{I}_{\mathsf{TIP/RING}}$$

Figure 2-10 Power Dissipation

Preliminary Product Overview

## 2.4 AC Transmission Characteristics

SLICOFI-2 connects to the digital world either via an IOM-2 or PCM interface. The SLIC performs the high voltage functions. In receive direction, SLICOFI-2 converts PCM data from the network and outputs a differential analog signal (ACP and ACN) to SLIC, that amplifies the signal and applies it to the subscriber line. In transmit direction, the transversal (IT) and longitudinal (IL) currents on the line are sensed by the SLIC and fed to SLICOFI-2. A capacitor separates the transversal line current into DC (IT) and AC (ITAC) components. As ITAC is the sensed transversal (also called metallic) current on the line, it includes both the receive and transmit components. SLICOFI-2 separates the receive and transmit components digitally, via a transhybrid circuit (see **Figure 2-13**). **Figure 2-11** shows the signal paths for AC transmission between the SLIC and SLICOFI-2:

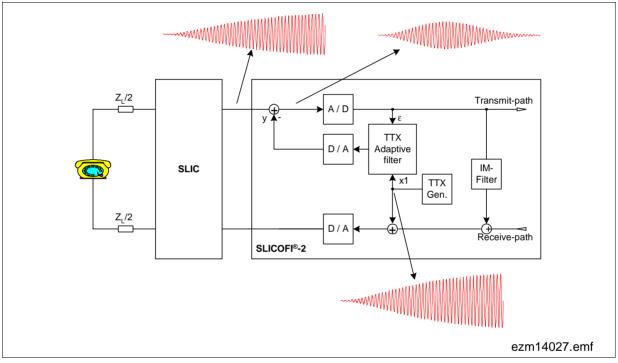

Figure 2-11 Signal Paths - AC Transmission

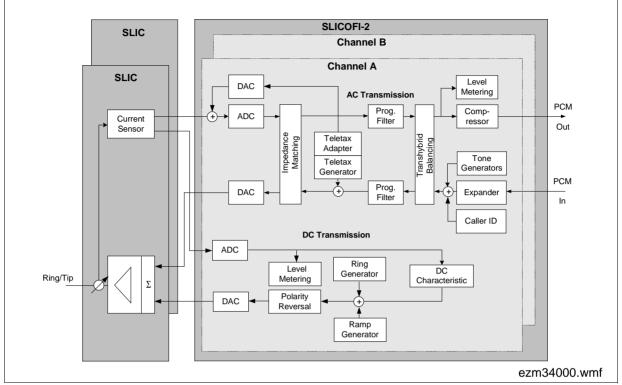

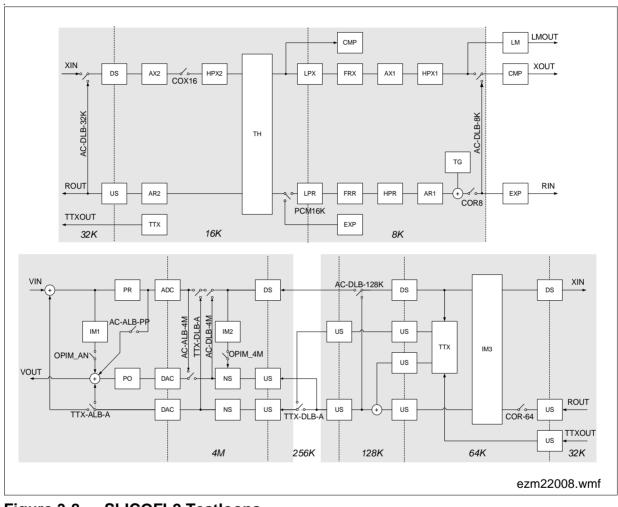

The signal flow within the SLICOFI-2 for one voice channel is shown in **Figure 2-12** by the following schematic circuitry. With the exception of a few analog filter functions, signal processing is performed digitally in the SLICOFI-2.

Figure 2-12 Signal Flow in Voice Channel (A)

## 2.4.1 Transmit Path

The current sense signal (ITAC) is converted to a voltage by an external resistor. This voltage is first filtered by a simple anti-aliasing filter (Prefilter, see **Figure 2-1**) that stops producing noise in the voiceband from signals near the A/D sampling frequency. A/D conversion is done by a 1-bit sigma-delta converter. The digital signal is down-sampled further and routed through programmable gain and filter stages. The coefficients for the filter and gain stages can be programmed to meet specific requirements. The processed digital signal goes through a compander (CMP) that converts the voice data into A-law or  $\mu$ -law codes. A time slot assignment unit outputs the voice data to the programmed time slot. SLICOFI-2 can also operate in 16-bit linear mode for processing uncompressed voice data. In this case, two time slots are used for one voice channel.

## 2.4.2 Receive Path

The digital input signal is received via the IOM-2 or PCM interface. Expansion (EXP), PCM low-pass filtering, frequency response correction and gain correction are performed by the DSP. The digital data stream is up-sampled and converted to a corresponding analog signal. After smoothing by post-filters in the SLICOFI-2 (Postfilter, see **Figure 2-1**), the AC signal is fed to the SLIC, where it is superimposed on the DC

signal. The DC signal has been processed in a separate DC path. A TTX signal, generated digitally within SLICOFI-2, can also be added.

## 2.4.3 Impedance Matching

The SLIC outputs the voice signal to the line (receive direction) and also senses the voice signal coming from the subscriber. The AC impedance of the SLIC and the load impedance need to be matched in order to maximize power transfer and minimize 2-wire return loss. The 2-wire return loss is a measure of the impedance matching between a transmission line and the AC termination of the DuSLIC.

The actual line impedance however can vary considerably, depending on loop length, loaded/unloaded lines, cable type, etc. Reference networks have therefore been defined to represent the average characteristics of a country's local loop. These reference networks differ from country to country and need to be reflected by the linecard being used in that country.

Impedance matching is done digitally within SLICOFI-2 by providing three impedance matching feedback loops. The loops feed the transmit signal back to the receive signal simulating the programmed impedance through the SLIC. When calculating the feedback filter coefficients, the external resistors between protection network and SLIC ( $R_{PRE} = R_{PROT} + R_{STAB}$ , see **Figure 6-2**, page 6-2) have to be taken into account. Impedance can be programmed to any appropriate value (real and complex impedance values). This means the device can be adapted to requirements anywhere in the world without the hardware changes that are necessary with conventional line card designs.

## 2.4.4 Transhybrid Balance

Digital switching systems can handle voice data only if receive and transmit data are separated on distinctive channels. The analog voice signal on the local loop is 2-wire full duplex, so it needs to be converted from 2-wire to 4-wire (2 wires each for receive and transmit). The circuitry, that performs this task, is commonly referred to as a hybrid circuit (see **Figure 2-13**)

Figure 2-13 2/4-wire Conversion in the Hybrid Circuit

To prevent the receive voice signal being looped back (echoed) directly into the transmit voice path, the hybrid circuit has to separate the receive path signal from the transmit path signal.

In contrast with conventional line card designs, echo cancellation is implemented digitally within SLICOFI-2. **Figure 2-13** shows the transhybrid loop that subtracts the receive signal from the transmit signal. The hybrid function is also dependent on loop condition. It has to be adapted to country-specific requirements. In conventional line card designs, this is done by external hardware adaptation. With SLICOFI-2, adaptation is simply a matter of updating coefficients. No hardware changes are necessary.

## 2.5 Ringing

With the 170 V technology used by the SLIC, a ringing voltage of up to 85  $V_{RMS}$  can be generated on-chip without the need for an external ringing generator. SLICOFI-2 generates a sinusoidal ringing signal that causes less noise and cross-talk in neighboring lines than a trapezoidal ringing signal. The ringing frequency is programmable from 15 to 100 Hz.

The advantage over traditional applications with a central ringing generator and decoupling resistors (approx.  $R = 400 \Omega$ ) is the very low source impedance of DuSLIC (approx. 60  $\Omega$  without  $R_{PROT}$ ). Thus it is possible to supply the subscriber line with a lower ringing voltage from the SLIC. SLIC-E and SLIC-P support different ringing methods (see **Chapter 2.5.3**).

## 2.5.1 Ringer Load

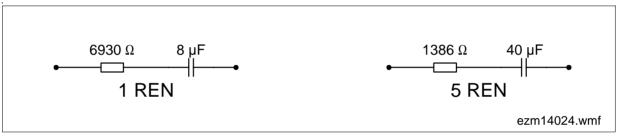

A typical ringer load can be thought of as a resistor in series with a capacitor. Ringer loads are usually described as a REN (Ringer Equivalence Number) value. REN is used to describe the on-hook impedance of the terminal equipment, and is actually a dimensionless ratio that reflects a certain load. REN definitions vary from country to country. A commonly used REN is described in FCC part 68 that defines a single REN as either 5 k $\Omega$ , 7 k $\Omega$  or 8 k $\Omega$  of AC impedance at 20 Hz. The impedance of an n-multiple REN is equivalent to parallel connection of n single RENs. In this manual, all references to REN assume the 7 k $\Omega$  model.

For example, a 1 REN and 5 REN load would be:

Figure 2-14 Typical Ringer Loads of 1 and 5 REN used in US

## 2.5.2 Ring Trip

Once the subscriber has gone off-hook, the ringing signal must be removed within a specified time, and power must start feeding to the subscriber's phone. There are two ring trip methods:

## DC ring trip detection:

By applying a DC voltage together with the ringing signal, a transversal DC loop current starts to flow when the subscriber goes off-hook. This DC current is sensed and in this way used as an off hook criterion. The threshold for the ring trip DC current is set internally in SLICOFI-2, programmed via the digital interface.

The DC voltage for ring trip detection can be generated by the DuSLIC chip set and the internal ring trip function can be used, even if an external ringing generator is used.

## AC ring trip detection:

For short lines (< 1 k $\Omega$  loop length) and low power applications, the DC offset can be avoided to reduce the battery voltage for a given ring amplitude. Ring trip detection is then performed by interpreting the AC impedance without using a DC offset voltage.

Most applications with DuSLIC are using DC ring trip detection, which is more reliable than AC ring trip detection.

## 2.5.3 Ringing Methods

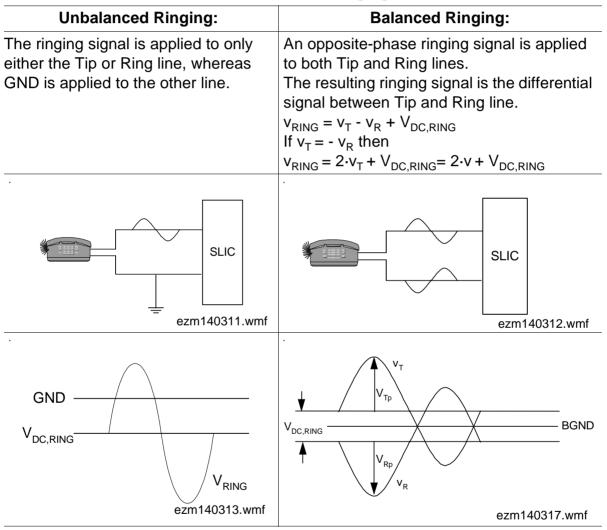

There are two methods of ringing:

- Balanced ringing (bridged ringing)

- Unbalanced ringing (divided ringing)

## Table 2-2 Unbalanced versus Balanced Ringing

The resulting ringing amplitude in balanced mode is twice the amplitude of  $v_T$  or  $v_R$ . This is an advantage over the unbalanced mode because the ringing generator circuit in balanced mode has to handle voltages of only half the amplitude to generate the same amplitude of ringing signal. The SLIC process technology used is capable of generating balanced ringing signals with amplitudes of up to 85  $V_{RMS}$ .

Internal balanced ringing generally offers more benefits compared to unbalanced ringing:

- Balanced ringing produces much less longitudinal voltage, which results in a lower amount of noise coupled into adjacent cable pairs

- By using a differential ringing signal, lower supply voltages become possible

The phone itself cannot distinguish between balanced and unbalanced ringing. Where unbalanced ringing is still used, it is often simply a historical leftover. For a comparison between balanced and unbalanced ringing see also ANSI document T1.401-1993.

Additionally, integrated ringing with the DuSLIC offers the following advantages:

- Internal ringing (no need for external ringing generator and relays)

- Reduction of board space because of much higher integration and fewer external components

- Programmable ringing amplitude, frequency and ringing DC offset without hardware changes

- Programmable ring trip thresholds

- Switching of the ringing signal at zero-crossing

## 2.5.4 DuSLIC Ringing Options

Application requirements differ with regard to ringing amplitudes, power requirements, loop length and loads. The DuSLIC options include two different SLICs to select the most appropriate ringing methods (see **Table 2-3**):

| SLIC Version /<br>Ringing facility,<br>battery voltages                                                             | SLIC-E<br>PEB 4265              | SLIC-P<br>PEB 4266                                     |

|---------------------------------------------------------------------------------------------------------------------|---------------------------------|--------------------------------------------------------|

| Internal balanced ringing<br>Max voltage in V <sub>RMS</sub> (sinusoidal) at<br>20 Vdc used for ring trip detection | 85 V <sub>RMS</sub>             | 85 V <sub>RMS</sub>                                    |

| DC-voltage for balanced ringing <sup>1)</sup>                                                                       | programmable<br>typically 050 V | programmable typically<br>050 V                        |

| Internal unbalanced ringing<br>Max. voltage in V <sub>RMS</sub> (sinusoidal)                                        | NO                              | 50 V <sub>RMS</sub>                                    |

| DC-voltage for unbalanced ringing                                                                                   | NO                              | V <sub>BATR</sub> / 2                                  |

| Required SLIC supply voltages for maximum ringing amplitude (typ.)                                                  | +5 V, -70 V, +80 V              | +5 V, -150 V                                           |

| Number of battery voltages for power saving                                                                         | 2                               | 2 (internal ringing used)<br>3 (external ringing used) |

## Table 2-3 Ringing Options with SLIC-E and SLIC-P

<sup>&</sup>lt;sup>1)</sup> In most applications 20 V DC are sufficient for reliable ring tip detection. A higher DC voltage will reduce the achievable maximum ringing voltage. In special applications the full range of the DC voltage (V<sub>HR</sub> - V<sub>BATH</sub> -10V) can be used and is programmable.

SLIC-E can be used for long-haul exchange requirements and has an integrated facility for balanced ringing up to 85  $V_{RMS}$ . The low-power SLIC-P is optimized for power-critical applications (e.g. intelligent ISDN network termination). Internal ringing can be used up to 85  $V_{RMS}$  balanced or 50  $V_{RMS}$  unbalanced. For lowest power applications where external ringing is preferred, three different battery voltages can be used for optimizing the power consumption of the application.

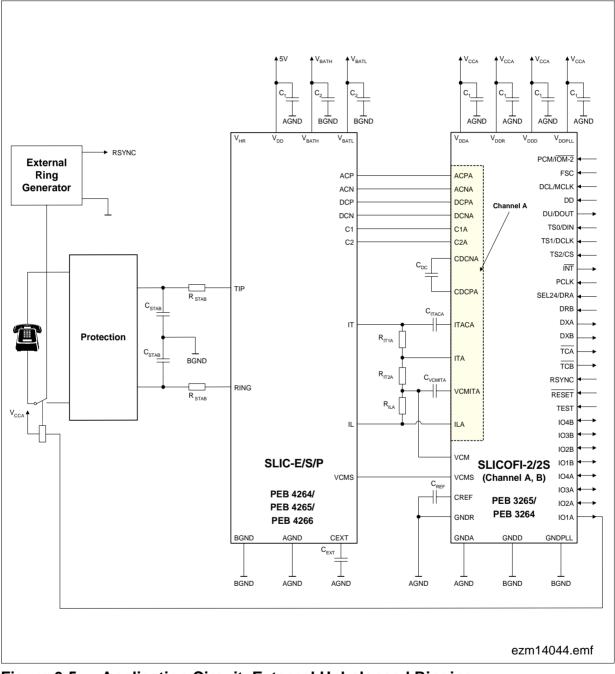

SLIC-E and SLIC-P differ in supply voltage configuration and the ring voltages ( $v_T$ ,  $v_R$ ) in the SLICOFI-2. External ringing is supported by the programmable I/Os and the RSYNC pin in the SLICOFI-2 for both SLIC's.

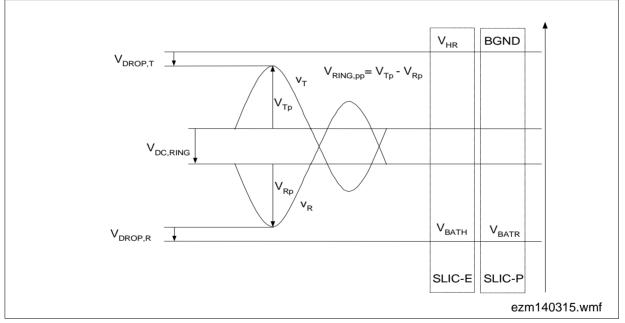

## 2.5.5 Internal Balanced Ringing via SLICs

SLIC-E and SLIC-P support internal balanced ringing up to 85  $V_{RMS}$ . The ringing signal is generated digitally within SLICOFI-2.

Figure 2-15 Balanced Ringing via SLIC-E and SLIC-P

In ringing mode, the DC feeding is not active. A programmable DC offset voltage is applied to the line instead. During ring bursts, the ringing DC offset and the ringing signal are summed digitally within SLICOFI-2 in accordance with the programmed values. This signal is then converted to an analog signal and applied to the SLIC. The SLIC amplifies the signal and supplies the line with ringing voltages up to 85 V<sub>RMS</sub>. In balanced ringing mode, the SLICs use an additional supply voltage (V<sub>HR</sub> for SLIC-E, V<sub>BATR</sub> for SLIC-P). The total supply span is now V<sub>HR</sub> - V<sub>BATH</sub> for SLIC-E and -V<sub>BATR</sub> for SLIC-P. The maximum ringing voltage that can be achieved is:

for SLIC-E:  $V_{RING,RMS} = (V_{HR} - V_{BATH} - V_{DROP,RT} - V_{DC,RING}) / 1.41$ for SLIC-P:  $V_{RING,RMS} = (-V_{BATR} - V_{DROP,RT} - V_{DC,RING}) / 1.41$ where:  $V_{DROP,RT} = V_{DROP,T} + V_{DROP,R}$

With the DUSLIC ringing voltages up to 85  $V_{RMS}$  sinusoidal can be applied, but also other ringing waveforms with other CREST-factors can be programmed.

The SLIC senses the transversal current on the line and supplies this information to the SLICOFI-2 at the IT pin. The IT current is monitored by SLICOFI-2. If the DC current exceeds the programmed ring trip threshold, SLICOFI-2 generates an interrupt. Ring trip is reliably detected and reported within two ring signal periods. The ringing signal is switched off during zero crossing by the SLICOFI-2. For a detailed application diagram of internal balanced ringing refer to the chapter on "Application Circuits" (see **Figure 6-1**, page 6-1).

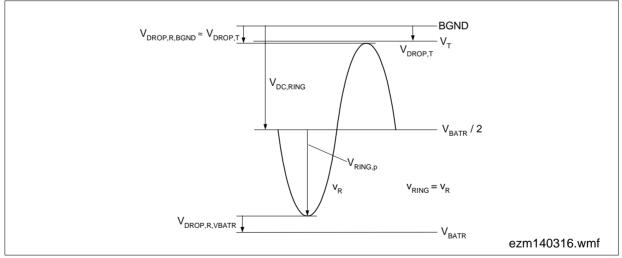

## 2.5.6 Internal Unbalanced Ringing with SLIC-P

The internal unbalanced ringing together with SLIC-P can be used for ringing voltages up to 50 V<sub>RMS</sub>. The SLICOFI-2 integrated ringing generator is used and the ringing signal is applied to either the Tip or Ring line. Ringing signal generation is the same as described above for balanced ringing. Since only one line is used for ringing, technology limits the ringing amplitude to about half the value of balanced ringing, to maximum 50 V<sub>RMS</sub>.

Figure 2-16 Unbalanced Ringing Signal

The above diagram shows an example with the ring line used for ringing and the tip line fixed at -  $V_{DROP,T}$  which is the drop in the output buffer of the tip line of SLIC-P (typ. < 1 V). The ring line has a fixed DC voltage of  $V_{BATR}$  / 2 used for ring trip detection. The maximum ringing voltage is:

$V_{RING,RMS} = (-V_{BATR} - V_{DROP,R,VBATR} - V_{DROP,T}) / 2.82$

When the called subscriber goes off-hook, a DC path is established from the Ring to the Tip line. The DC current is recognized by the SLICOFI-2 because it monitors the IT pin. An interrupt indicates ring trip if the line current exceeds the programmed threshold.

The same hardware can be used for integrated balanced or unbalanced ringing. The balanced or unbalanced modes are configured by software. The maximum achievable amplitudes depend on the values selected for  $V_{BATR}$ .

In both balanced and unbalanced ringing modes, SLICOFI-2 automatically applies and removes the ringing signal during zero-crossing. This reduces noise and cross-talk to adjacent lines.

## 2.5.7 External Unbalanced Ringing

SLICOFI-2 supports external ringing for higher unbalanced ringing voltage requirements above 50  $V_{RMS}$  with both SLICs. For a detailed application diagram of unbalanced ringing see **Figure 6-5** and **Figure 6-6** on page 6-7 and page 6-8.

Since high voltages are involved, an external relay should be used to switch the RING line off and to switch the external ringing signal together with a DC voltage for ring trip to the line. This results in a DC offset between the Ring and Tip lines.

The SLICOFI-2 has to be set in the external ringing mode. A synchronisation signal of the external ringer is applied to the SLICOFI-2 via the RSYNC pin. The external relay is switched on or off synchronously to this signal via the IO1 pin of the SLICOFI-2 according to the actual mode of the DuSLIC. An interrupt is generated if the DC current exceeds the programmed ring trip threshold.

## 2.6 Metering

There are two different metering methods:

- Metering by sinusoidal bursts with either 12 or 16 kHz or

- Polarity reversal of Tip and Ring.

## 2.6.1 Metering by 12/16 kHz Sinusoidal Bursts

The required amplitude of the sinusoidal 12 or 16 kHz metering signals varies from a few hundred millivolts to 5  $V_{RMS}$  and even more, depending on the country specifications and the application (long loop or short loop application). These signals are superimposed onto the speech signal. As soon as metering pulses are applied to the subscriber line, they also divert to the transmit signal path which means that a notch filter has to block the 12/16 kHz signal, to prevent overloading the transmit A/D converter. In contrast to conventional line circuits, the DuSLIC chip set generates the metering signal internally. The fact that the adaptive notch filter is integrated is one of the big advantages of DuSLIC.

## DuSLIC

#### **Functional Description**

#### **Teletax Metering and Filtering**

To satisfy worldwide application requirements, SLICOFI-2 offers integrated metering injection of either 12 or 16 kHz signals with programmable amplitudes. SLICOFI-2 also has an integrated adaptive TTX notch filter and can switch the TTX signal to the line in a smooth way. When switching the signal to the line, the switching noise is less than 1 mV. **Figure 2-17** shows the TTX bursts at certain points of the signal flow within SLICOFI-2.

Figure 2-17 Teletax Injection and Metering

The integrated, adaptive TTX notch filter guarantees an attenuation of > 40 dB. No external components for filtering TTX bursts are required.

# 2.6.2 Metering by Polarity Reversal

SLICOFI-2 also supports metering by changing the actual polarity of the voltages on the TIP/RING lines. Metering with polarity reversal is usually used for pay phones (coin lines). Every time the polarity changes, a magnet in the pay phone releases a coin.

# 2.6.2.1 Soft reversal

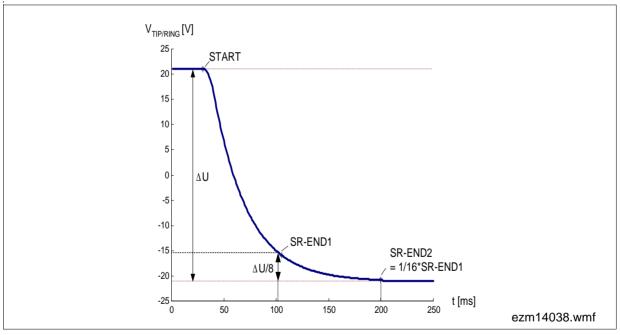

Some applications require a smooth polarity reversal (soft reversal), as shown in **Figure 2-18**. Soft reversal helps to prevent negative effects like non-required ringing. Soft reversal is deactivated by the SOFT-DIS bit in register BCR2.

- SOFT-DIS = 1 Immediate reversal is performed (hard reversal)

- SOFT-DIS = 0 Soft reversal is performed. Transition time (time from START to SR-END1, see **Figure 2-18**) is programmable by CRAM-coefficients, default value 80 ms.

Figure 2-18 Soft Reversal (Example for Open Loop)

START: The soft ramp starts by setting the REVPOL bit in register BCR1 to 1. The DC characteristic is switched off.

SR-END1: At the soft reversal end one point, the DC characteristic is switched on again. Programmable by the DuSLICOS software, e.g.  $\Delta U/8$ .

SR-END2: At the soft reversal end two point, the soft ramp is switched off. Programmable by the DuSLICOS software, e.g. 1/16\*SR-END1.

# 2.7 Signaling (Supervision)

Signaling in the subscriber loop is monitored internally by the DuSLIC chip set.

Supervision is performed by sensing the longitudinal and transversal line currents on the Ring and Tip wires. The scaled values of these currents are generated in the SLIC and fed to the SLICOFI-2 via the IT and IL pins.

Transversal line current:  $(I_R + I_T) / 2$ Longitudinal line current:  $(I_R - I_T) / 2$ where  $I_R$ ,  $I_T$  are the loop currents on the Ring and Tip wires.

## **Off-hook Detection**

Loop start signaling is the most common type of signaling. The subscriber loop is closed by the hook switch inside the subscriber equipment. In active mode, the resulting transversal loop current is sensed by the internal current sensor in the SLIC. The IT pin of the SLIC indicates the subscriber loop current to the SLICOFI-2. An external resistor ( $R_{IT1}$ ,  $R_{IT2}$ , see **Figure 6-1**) converts the current information to a voltage on the ITA (or ITB) pin. The analog information is first converted to a digital value. It is then filtered and processed further which effectively suppresses line disturbances. If the result exceeds a programmable threshold, an interrupt is generated to indicate off-hook detection.

A similar mechanism is used in Power Down mode. In this mode, the internal current sensor is switched off to minimize power consumption. The loop current is therefore fed and sensed through 5 k $\Omega$  resistors. The information is made available on the IT pin and interpreted by the SLICOFI-2.

In applications using ground start loop signaling, DuSLIC can be set in the ground start mode. In this mode, the Tip wire is switched to high impedance mode. Ring ground detection is performed by the internal current sensor in the SLIC and transferred to to the SLICOFI-2 via the IT pin.

### Ground Key Detection

The scaled longitudinal current information is transferred from the SLIC via the IL pin and the external resistor  $R_{IL}$  to the SLICOFI-2. This voltage is compared with a fixed threshold value. For the specified  $R_{IL}$  (1.6 k $\Omega$ , see application circuit **Figure 6-1**) this threshold corresponds to 17 mA (positive and negative). After further post-processing, this information generates an interrupt and ground key detection is indicated.

The post-processing is performed to guarantee ground key detection, even if longitudinal AC currents with frequencies of 16 2/3, 50 or 60 Hz are superimposed. The time delay between triggering the ground key function and registering the ground key interrupt will in most cases (f = 50 Hz, 60 Hz) be less than 40 ms.

In Power Down mode, the SLIC's internal current sensors are switched off and ground key detection is disabled.

# 2.8 DuSLIC Enhanced Signalprocessing Capabilities

The signal processing capabilities described in this chapter are realized by an Extended Digital Signal Processor (EDSP) except DTMF generation. Each function can be individually enabled or disabled for each DuSLIC channel. Therefore power consumption can be reduced according the needs of the application.

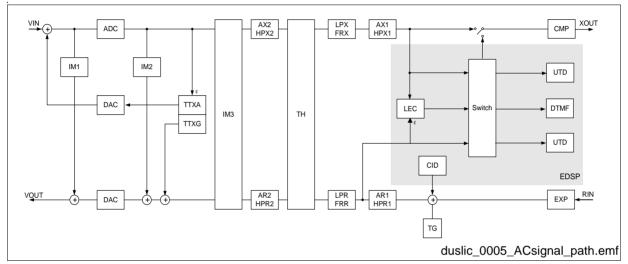

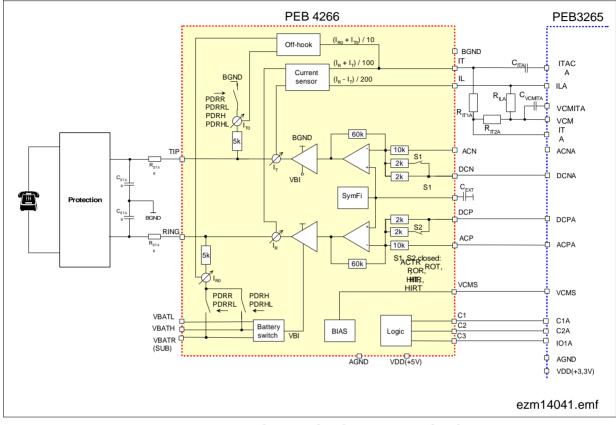

**Figure 2-19** shows the AC signal path for DuSLIC with the ADCs and DACs, impedance matching loop, thranshybrid filter, gain stages and the connection to the EDSP.

Figure 2-19 DuSLIC AC Signal Path

# 2.8.1 DTMF Generation and Detection

Dual Tone Multi-Frequency (DTMF) is a signaling scheme using voice frequency tones to signal dialing information. A DTMF signal is the sum of two tones, one from a low group (697-941 Hz) and one from a high group (1209-1633 Hz), with each group containing four individual tones. This scheme allows 16 unique combinations. Ten of these codes represent the numbers from zero through nine on the telephone keypad, the remaining six codes (\*,#,A,B,C,D) are reserved for special signaling. The buttons are arranged in a matrix, with the rows determining the low group tones, and the columns determining the high group tone for each button.

In SLICOFI-2, all 16 standard DTMF tone pairs can be generated independent in each channel via two integrated tone generators. Alternatively the frequency and the amplitude of the tone generators can be programmed individually via the digital interface. Each tone generator can be switched on and off. The generated DTMF tone signals meet the frequency variation tolerances specified in the ITU-T Q.23 recommendation.

Both channels A and B of SLICOFI-2 have a powerful built-in DTMF decoder that will meet most national requirements. The receiver algorithm performance meets the quality criteria for central office / exchange applications. It complies with the requirements of ITU-T Q.24, "Deutsche Telekom" network (BAPT 223 ZV 5, Approval Specification of the

Federal Office for Post and Telecommunications, Germany) and Bellcore GR-30-CORE (TR-NWT-000506).

The performance of the algorithm can be adapted according the needs of the application via the digital interface (detection level, twist, bandwith and center frequency of the notch filter). **Table 2-4** shows the performance characteristics of the DTMF decoder algorithm:

|    | Characteristics                                                   | Value                                                                           | Notes                                        |

|----|-------------------------------------------------------------------|---------------------------------------------------------------------------------|----------------------------------------------|

| 1  | Valid input signal detection level                                | - 48 to 0 dBm0                                                                  | Programmable                                 |

| 2  | Input signal rejection level                                      | - 5 dB of valid signal detection level                                          |                                              |

| 3  | Positive twist accept                                             | < 8 dB                                                                          | Programmable                                 |

| 4  | Negative twist accept                                             | < 8 dB                                                                          | Programmable                                 |

| 5  | Frequency deviation accept                                        | < ± (1.5 % + 4 Hz) and<br><±1.8 %                                               | Related to center frequency                  |

| 6  | Frequency deviation reject                                        | > ± 3%                                                                          | Related to center frequency                  |

| 7  | DTMF noise tolerance<br>(could be the same as 14)                 | -12 dB                                                                          | dB referenced to<br>lowest amplitude<br>tone |

| 8  | Minimum tone accept duration                                      | 40 ms                                                                           |                                              |

| 9  | Maximum tone reject duration                                      | 25 ms                                                                           |                                              |

| 10 | Signaling velocity                                                | ≥ 93 ms/digit                                                                   |                                              |

| 11 | Minimum inter-digit pause duration                                | 40 ms                                                                           |                                              |

| 12 | Maximum tone drop-out duration                                    | 20 ms                                                                           |                                              |

| 13 | Interference rejection 30 Hz to 480 Hz for valid DTMF recognition | Level in frequency<br>range 30 Hz480 Hz ≤<br>Level of DTMF<br>frequency - 22 dB | dB referenced to<br>lowest amplitude<br>tone |

| 14 | Gaussian noise influence<br>Signal level -22 dBm0, SNR = 23 dB    | Error rate better than 1<br>in 10000                                            |                                              |

| 15 | Pulse noise influence<br>Impulse noise tape 201                   | Error rate better than 14<br>in 10000                                           |                                              |

Table 2-4

Performance Characteristic of SLICOFI-2 DTMF Decoder Algorithm

In the event of pauses < 20 ms:

- If the pause is followed by a tone pair with the same frequencies as before, this is interpreted as drop-out.

- If the pause is followed by a tone pair with different frequencies and if all other conditions are valid, this is interpreted as two different numbers.

DTMF decoders can be switched on or off individually to reduce power consumption. In normal operation, the decoder monitors the Tip and Ring wires via the ITAC pins (transmit path). Alternatively the decoder can be switched also in the receive path. On detecting a valid DTMF tone pair, SLICOFI-2 generates an interrupt via the appropriate INT pin and indicates a change of status. The DTMF code information is provided by a register read via the digital interface.

The DTMF decoder also has excellent speech-rejection capabilities and complies with Bellcore TR-TSY-000763. The algorithm has been fully tested with the speech sample sequences in the Series-1 Digit Simulation Test Tapes for DTMF decoders from Bellcore.

## 2.8.2 Caller ID Generation

A generator to send calling line identification (Caller ID, CID) is integrated in the DuSLIC chip set. Caller ID is a generic name for the service provided by telephone utilities that supply information like the telephone number or the name of the calling party to the called subscriber at the start of a call. In call waiting, the Caller ID service supplies information about a second incoming caller to a subscriber already busy with a phone call.

In typical Caller ID (CID) systems, the coded calling number information is sent from the central exchange to the called phone. This information can be shown on a display on the subscriber telephone set. In this case, the Caller ID information is usually displayed before the subscriber decides to answer the incoming call. If the line is connected to a computer, caller information can be used to search in databases and additional services can be offered.

There are two methods used for sending CID information depending on the application and country specific requirements:

- Caller ID generation using DTMF signaling (see **Chapter 2.8.1**)

- Caller ID generation using FSK

DuSLIC contains DTMF generation units and FSK generation units which can be used for both channels simultaneously.

# DuSLIC

#### **Functional Description**

### **DuSLIC FSK Generation**

Different countries use different standards to send Caller ID information. The SLICOFI-2 chip set is compatible with the widely used standards, Bellcore GR-30-CORE, British Telecom (BT) SIN227, SIN242 or the UK Cable Communications Association (CCA) specification TW/P&E/312. A continuous phase binary frequency shift keying (FSK) modulation is used for coding which is compatible with BELL 202 (see **Table 2-5**) and ITU-T V.23, the most common standards. SLICOFI-2 can be easily adapted to these requirements by programming via the microcontroller interface. Coefficient sets are provided for the most common standards.

| Characteristic     | ITU-T V.23    | Bell 202                   |  |  |  |

|--------------------|---------------|----------------------------|--|--|--|

| Mark (Logic 1):    | 1300 ± 3 Hz   | 1200 ± 3 Hz                |  |  |  |

| Space (Logic 0):   | 2100 ± 3 Hz   | 2200 ± 3 Hz                |  |  |  |

| Modulation:        | F             | FSK                        |  |  |  |

| Transmission rate: | 1200 ±        | 1200 ± 6 baud              |  |  |  |

| Data format:       | Serial binary | Serial binary asynchronous |  |  |  |

#### Table 2-5 FSK Modulation Characteristics

The Caller ID data of the calling party can be transferred via the microcontroller interface into a SLICOFI-2 buffer register. An FSK enable signal, together with the first write operation into the buffer register, will start sending the FSK data when the amount of data in the buffer register exceeds the buffer request size plus two. The data transfer into the buffer register is handled by a SLICOFI-2 interrupt signal. Caller data is transferred from the buffer via the interface pins to the SLIC and fed to the Tip and Ring wires.

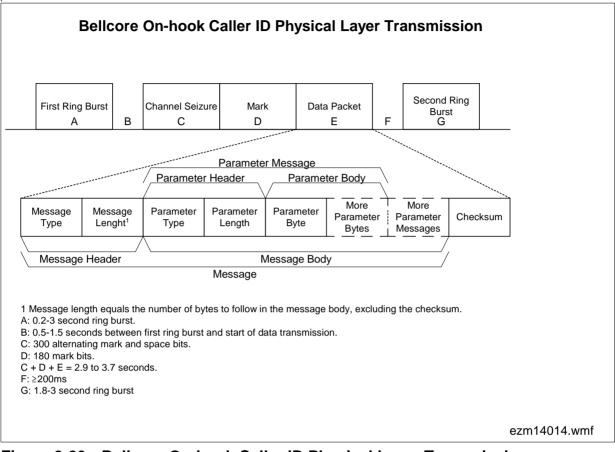

DuSLIC offers two different levels of framing:

• A basic low level framing mode

All the data necessary to implement the FSK data stream - including channel seizure, mark sequence and framing for the data packet or checksum - has to be configured by firmware. SLICOFI-2 transmits the data stream in the same order in which the data is written to the buffer register.

• A high level framing mode

The number of cannel seizure and mark bits can be programmed and are automatically sent by the DuSLIC. Only the data packet information has to be written into the CID buffer.

The example below shows signaling of CID on-hook data transmission in accordance with Bellcore specifications. The Caller ID information applied on Tip and Ring is sent during the period between the first and second ring burst.

Figure 2-20 Bellcore On-hook Caller ID Physical Layer Transmission

# 2.8.3 Line Echo Cancelling (LEC)

The DuSLIC contains an adaptive line echo cancellation unit for the cancellation of near end echoes. With the adaptive balancing of the LEC unit the transhybrid loss can be improved up to a value of about 50 dB. The maximum echo length considered is 8 ms. The 8 ms cancellation is available for each channel only when no further signal processing functions of the EDSP are used. The line echo cancellation unit is especially useful in front of the DTMF detection unit. In critical situations the performance of the DTMF detection can be improved.

If for both DuSLIC channels DTMF detection and LEC are used the maximum line echo lenght for the LEC is reduced to 4 ms.

The DuSLIC line echo canceller is compatible with applicable standards ITU-T G.165 and G.168 with the restriction that a longer echo cancelling path than 8 ms cannot be realized.

The LEC unit consists basically of a FIR filter and a shadow FIR filter and a coefficient adaption mechanism between these two filters as shown in **Figure 2-21**.

Figure 2-21 Line Echo Cancellation Unit - Block Diagram

The adaption process is controlled by the three parameters  $Pow_{LECR}$  (Power Detection Level Receive),  $DeltaP_{LEC}$  (Delta Power) and DeltaQ (Delta Quality). Adaption takes place only if both of the following conditions hold:

1.  $S_{LEC, R}$  >  $Pow_{LECR}$ 2.  $S_{LEC, R}$  -  $S_{LEC, T}$  >  $DeltaP_{LEC}$

With the first condition, adaption to small signals can be avoided. The second condition avoids adaption during double talk. The parameter  $\text{DeltaP}_{\text{LEC}}$  represents the echo loss provided by external circuitry.

If the adaption of the shadow filter is performed better than the adaption of the actual filter by a value of more than DeltaQ then the shadow filter coefficients will be copied to the actual filter.

At the start of an adaption process the coefficients of the LEC unit can be set to default initial values or set to the old coefficient values. A freezing of the coefficients can also be performed.