PM5395

## CRSU™ 4x2488

## Quad Clock Recovery and Synthesis Unit for 2488 Mbit/s

## **Data Sheet**

### Released Issue 5: December, 2002

Proprietary and Confidential to PMC-Sierra, Inc., and for its Customers' Internal Use Document ID: PMC-2001972, Issue 5

### **Legal Information**

#### Copyright

© 2002 PMC-Sierra, Inc.

The information is proprietary and confidential to PMC-Sierra, Inc., and for its customers' internal use. In any event, you cannot reproduce any part of this document, in any form, without the express written consent of PMC-Sierra, Inc.

#### Disclaimer

None of the information contained in this document constitutes an express or implied warranty by PMC-Sierra, Inc. as to the sufficiency, fitness or suitability for a particular purpose of any such information or the fitness, or suitability for a particular purpose, merchantability, performance, compatibility with other parts or systems, of any of the products of PMC-Sierra, Inc., or any portion thereof, referred to in this document. PMC-Sierra, Inc. expressly disclaims all representations and warranties of any kind regarding the contents or use of the information, including, but not limited to, express and implied warranties of accuracy, completeness, merchantability, fitness for a particular use, or non-infringement.

In no event will PMC-Sierra, Inc. be liable for any direct, indirect, special, incidental or consequential damages, including, but not limited to, lost profits, lost business or lost data resulting from any use of or reliance upon the information, whether or not PMC-Sierra, Inc. has been advised of the possibility of such damage.

#### Trademarks

PMC-Sierra, PMC, PMCS, and CRSU are trademarks of PMC-Sierra, Inc. Other product and company names mentioned herein may be the trademarks of their respective owners.

#### Patents

The technology discussed in this document may be protected by one or more patent grants.

#### **Contacting PMC-Sierra**

PMC-Sierra 8555 Baxter Place Burnaby, BC Canada V5A 4V7

Tel: (604) 415-6000 Fax: (604) 415-6200

Document Information: document@pmc-sierra.com Corporate Information: info@pmc-sierra.com Technical Support: apps@pmc-sierra.com Web Site: <u>http://www.pmc-sierra.com</u>

### **Revision History**

|                  | Details of Change                                                                                                                                                                                                                                                                                                                                                                   |

|------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| December<br>2002 | Updated power numbers.<br>Added reference to Bellcore spec GR253 -CORE 1995 and 2000 release.<br>Note added to QSFI-4 Common Electrical Interface Overview, detailing the<br>QSFI-4 is not IEEE LVDS compliant when CSU channel 0 is reset.<br>Added Jitter Tolerance plot.<br>Typical Intrinsic Jitter number added.<br>LCRUTO pins are now documented.<br>CRU reset period added. |

| November<br>2002 | Master register 000DH ICO Swing Bits no longer reserved and updated for looptime settings.                                                                                                                                                                                                                                                                                          |

| May 2002         | Document ported to new template. System side OIF SFI-4 interface is now referenced as QSFI-4.                                                                                                                                                                                                                                                                                       |

| Nov 2001         | Added more FEC details. Removed note that indicated automatic AIS insertion (mechanism provided for AIS insertion but not automatic).                                                                                                                                                                                                                                               |

|                  | Added Patent information                                                                                                                                                                                                                                                                                                                                                            |

| March 2000       | Document created                                                                                                                                                                                                                                                                                                                                                                    |

|                  | 13                                                                                                                                                                                                                                                                                                                                                                                  |

|                  |                                                                                                                                                                                                                                                                                                                                                                                     |

|                  | 2002<br>November<br>2002<br>May 2002<br>Nov 2001                                                                                                                                                                                                                                                                                                                                    |

### **Table of Contents**

| Leo       | al Info      | ormation                                                         | 2  |

|-----------|--------------|------------------------------------------------------------------|----|

|           |              | Copyright                                                        |    |

|           |              | Disclaimer.                                                      | 2  |

|           |              | Trademarks                                                       | 2  |

|           |              | Patents                                                          | 2  |

| <u>Co</u> | ntactin      | g PMC-Sierra                                                     | 3  |

|           |              | History                                                          |    |

|           |              | Contents                                                         |    |

| List      | t of Re      | gisters                                                          | 10 |

| List      | of Fig       | <u>jures</u>                                                     | 14 |

| List      |              | bles                                                             |    |

| <u>1</u>  |              | itions                                                           |    |

| <u>2</u>  | <u>Feat</u>  | <u>ires</u>                                                      | 18 |

|           | <u>2.1</u>   | General                                                          | 18 |

|           | <u>2.2</u>   | SONET Section and Line / SDH Regenerator and Multiplexer Section | 18 |

|           | <u>2.3</u>   | SONET / SDH In-band Forward Error Correction                     |    |

| <u>3</u>  |              | cations                                                          |    |

| <u>4</u>  |              | rences                                                           |    |

| <u>5</u>  |              | cation Examples                                                  |    |

| <u>6</u>  |              | Diagram.                                                         |    |

| <u>7</u>  | <u>Desc</u>  | ription                                                          | 27 |

| <u>8</u>  | <u>Pin D</u> | liagram                                                          | 30 |

| <u>9</u>  | <u>Pin D</u> | vescription                                                      | 34 |

|           | <u>9.1</u>   | Serial Line Side Interface Signals (33)                          | 34 |

|           | <u>9.2</u>   | Clocks and Alarms (12)                                           | 35 |

|           | <u>9.3</u>   | System Side Interface Signals (100)                              |    |

|           | <u>9.4</u>   | Microprocessor Interface Signals (36)                            | 42 |

|           | <u>9.5</u>   | JTAG Test Access Port (TAP) Signals (5)                          | 43 |

|           | <u>9.6</u>   | Analog Miscellaneous Signals (32)                                | 43 |

|           | <u>9.7</u>   | Analog Power (120)                                               | 44 |

|           | <u>9.8</u>   | Digital Power (56)                                               | 48 |

|           | <u>9.9</u>   | Ground (186)                                                     | 50 |

|           | <u>9.10</u>  | Pad Summary                                                      | 54 |

| <u>10</u> | Funct        | ctional Description                                                    |     |  |  |

|-----------|--------------|------------------------------------------------------------------------|-----|--|--|

|           | <u>10.1</u>  | Receive Line Interface (RXLI)                                          |     |  |  |

|           | <u>10.2</u>  | 2 SONET/SDH Receive Line Interface (SRLI)                              |     |  |  |

|           | <u>10.3</u>  | Receive Regenerator and Multiplexor Processor (RRMP)                   | .58 |  |  |

|           | <u>10.4</u>  | Receive In-band Forward Error Correction Decoder (RIFD)                | .60 |  |  |

|           |              | 10.4.1 FEC Decoder                                                     | .60 |  |  |

|           |              | 10.4.2 Performance Monitors                                            | .60 |  |  |

|           | <u>10.5</u>  | SONET/SDH Bit Error Rate Monitor (SBER)                                | .61 |  |  |

|           | <u>10.6</u>  | Receive QSFI-4 Interface (Rx QSFI-4 I/F)                               | .61 |  |  |

|           |              | 10.6.1 Receive QSFI-4 Clock Output                                     | .61 |  |  |

|           | <u>10.7</u>  | Transmit QSFI-4 Interface (Tx QSFI-4 I/F)                              | .62 |  |  |

|           |              | 10.7.1 Transmit QSFI-4 Clock Synthesis Unit (Tx QSFI-4 CSU)            | .62 |  |  |

|           | <u>10.8</u>  | Receive Section Overhead Processor (RSOP)                              | .62 |  |  |

|           | <u>10.9</u>  | Transmit In-band Forward Error Correction Encoder (TIFE)               | .62 |  |  |

|           |              | 10.9.1 B2 Compensation                                                 | .62 |  |  |

|           |              | 10.9.2 FEC Encoder                                                     | .63 |  |  |

|           | <u>10.10</u> | Transmit Regenerator and Section Processor (TRSP)                      | .63 |  |  |

|           | <u>10.11</u> | SONET/SDH Transmit Line Interface (STLI)                               | .66 |  |  |

|           | <u>10.12</u> | Transmit Line Interface (TXLI)                                         | .66 |  |  |

|           |              | 10.12.1 Transmit Line Interface Clock Synthesis Unit (Tx Line I/F CSU) | .66 |  |  |

|           | <u>10.13</u> | JTAG Test Access Port Interface                                        | .66 |  |  |

|           | <u>10.14</u> | Microprocessor Interface                                               | .66 |  |  |

| <u>11</u> | <u>Norm</u>  | al Mode Register Description                                           | .83 |  |  |

|           | <u>11.1</u>  | Channel Register Map                                                   | 127 |  |  |

|           |              | Register 1056H: TRSP Reserved                                          | 154 |  |  |

|           |              | Register 1057H: TRSP Reserved                                          | 155 |  |  |

|           |              | Register 1058H: TRSP Reserved                                          | 156 |  |  |

|           |              | Register 1059H: TRSP Reserved                                          | 157 |  |  |

|           |              | Register 105B-105FH: unused                                            | 158 |  |  |

| <u>12</u> | Test I       | Features Description                                                   | 228 |  |  |

|           | <u>12.1</u>  | Master Test and Test Configuration Registers                           | 228 |  |  |

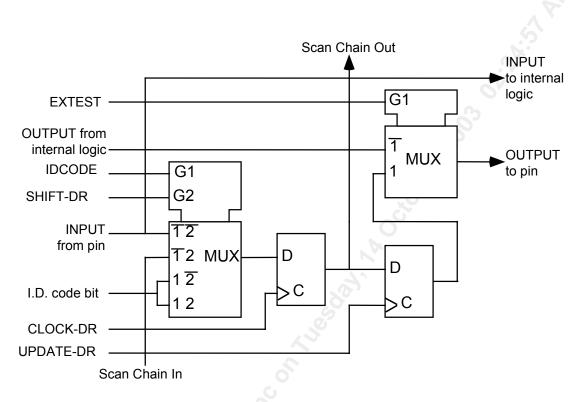

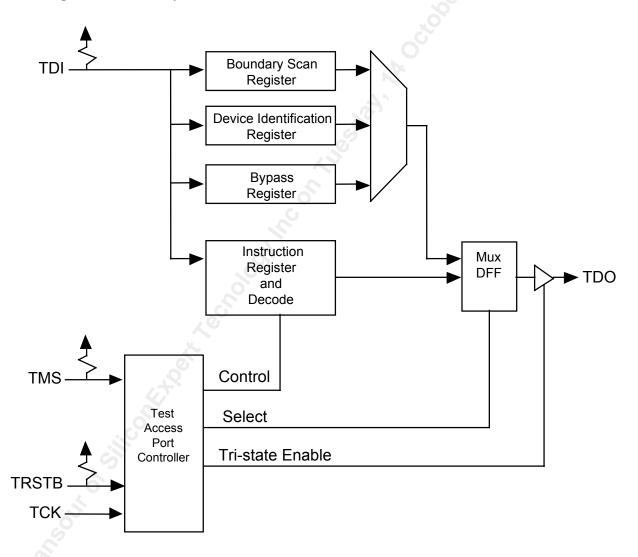

|           | <u>12.2</u>  | JTAG Test Port                                                         | 234 |  |  |

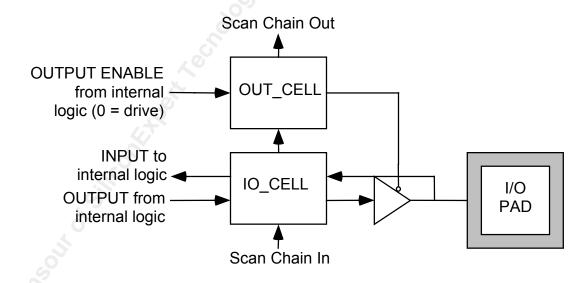

|           | <u>12.3</u>  | Boundary Scan Cells                                                    | 238 |  |  |

|           | <u>12.4</u>  | JTAG Control                                                           | 241 |  |  |

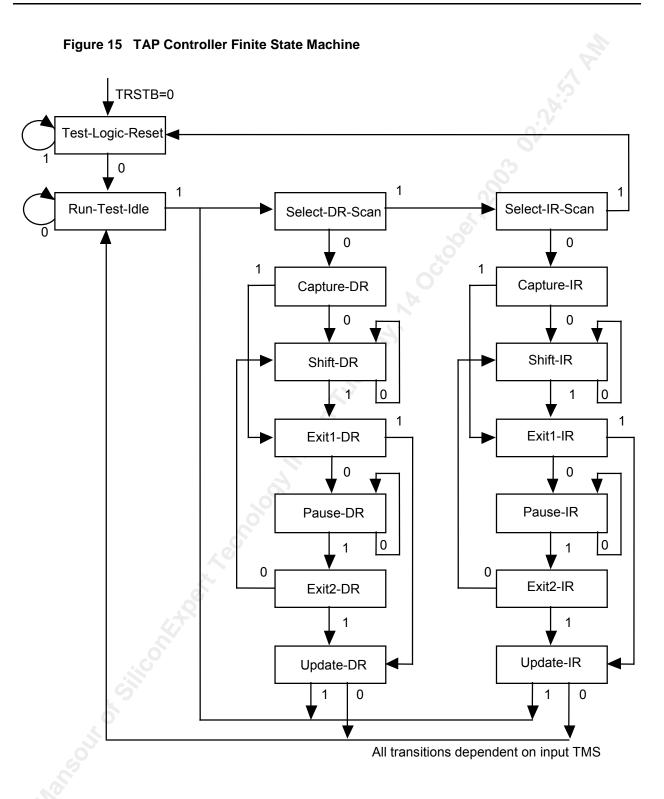

|           |              | 12.4.1 TAP Controller                                                  | 242 |  |  |

|           |              | <u>12.4.2</u>  | States                                                   | 244 |

|-----------|--------------|----------------|----------------------------------------------------------|-----|

|           |              | <u>12.4.3</u>  | Instructions                                             | 245 |

| <u>13</u> | <u>Opera</u> | ation          |                                                          | 246 |

|           | <u>13.1</u>  | Initializ      | ation Settings                                           | 246 |

|           |              | <u>13.1.1</u>  | TRSP Register settings:                                  | 246 |

|           | <u>13.2</u>  | System         | n side interface issues                                  | 246 |

|           |              | <u>13.2.1</u>  | B1 Byte Recalculated                                     | 246 |

|           |              | <u>13.2.2</u>  | Line side data frequency out of specification issues     | 246 |

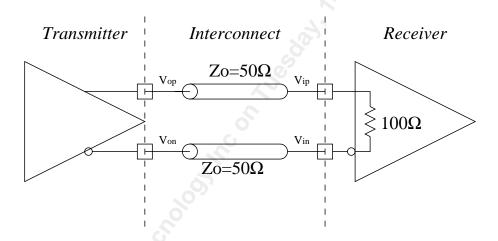

|           | <u>13.3</u>  | <u>QSFI-4</u>  | Common Electrical Interface Overview                     | 246 |

|           |              |                | LVDS Receiver (RXLVDS)                                   |     |

|           |              |                | Serial-In Parallel-Out (SIPO)                            |     |

|           |              | <u>13.3.3</u>  | LVDS Transmitter (TXLVDS)                                | 248 |

|           |              | <u>13.3.4</u>  | Parallel-In Serial-Out (PISO)                            | 248 |

|           |              | <u>13.3.5</u>  | LVDS Transmit Reference (TXLVREF)                        | 248 |

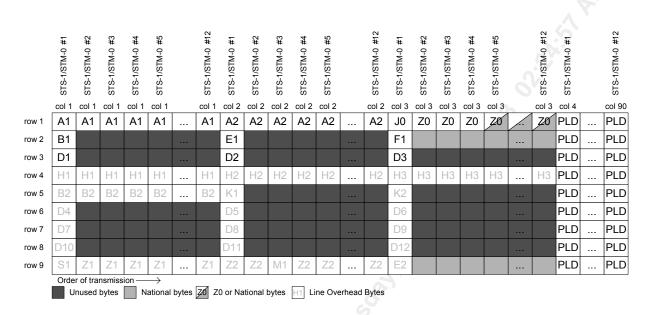

|           | <u>13.4</u>  | Transp         | ort Overhead Bytes                                       | 248 |

|           | <u>13.5</u>  | SBER           | Bit Error Rate Monitor                                   | 250 |

|           | <u>13.6</u>  | <u>Clockin</u> | ng Operations                                            | 254 |

|           | <u>13.7</u>  | Looptin        | ne Operation                                             | 254 |

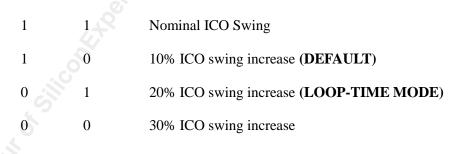

|           |              | Registe        | er 000DH: Diagnostic Loopback and ICO control            | 254 |

|           |              | Registe        | er 10A1H: TXLI CSU Control                               | 254 |

|           | <u>13.8</u>  | System         | n side serial Loopback Operation                         | 254 |

|           |              | Registe        | er RXLI 1102H: CRU Control                               | 255 |

|           | <u>13.9</u>  | System         | side Parallel Loopback operation                         | 255 |

|           |              | Registe        | er RXLI 1102H: CRU Control                               | 255 |

|           |              | Registe        | er 000CH: Diagnostic Bypass Modes                        | 255 |

|           |              | Registe        | er 000DH: Diagnostic Bypass Modes                        | 256 |

|           | <u>13.10</u> | Line Si        | de Parallel Loopback Operation                           | 256 |

|           |              | Registe        | er 000DH: Diagnostic Loopback and ICO control            | 256 |

|           |              | Registe        | er 10A1H: TXLI CSU Control                               | 256 |

|           |              | Registe        | er TXLI 10A0H: TXLI Control                              | 256 |

|           |              | Registe        | er RXLI 1103H: RXLI CRU clock training and Configuration | 256 |

|           | <u>13.11</u> | Line Si        | de, same Channel Loopback Operation                      | 257 |

|           |              | Registe        | er 000DH: Diagnostic Loopback and ICO control            | 257 |

|           |              | Registe        | er 10A1H: TXLI CSU Control                               | 257 |

|           |              | Registe        | er 000FH: Bypass and Loop-across                         | 257 |

|           | 13.12 Line side, Channel to Channel Loopback Operation             | .257 |

|-----------|--------------------------------------------------------------------|------|

|           | Register 000DH: Diagnostic Loopback and ICO control                | .258 |

|           | Register 10A1H: TXLI CSU Control                                   | .258 |

|           | Register 12A1H: TXLI CSU Control                                   | .258 |

|           | Register 000FH: Bypass and Loop-across                             | .258 |

|           | 13.13 Interrupt Service Routine                                    | .259 |

|           | 13.14 Using the Performance Monitoring Features                    | .259 |

|           | 13.14.1 Required Reset Sequence                                    | .259 |

|           | 13.15 Transmit FEC Encoder Error Insertion.                        | .260 |

| <u>14</u> | Board Design Recommendations                                       | .262 |

|           | 14.1 Interfacing the CRSU 4x2488 to the S/UNI-9953 or SPECTRA-9953 | .262 |

|           | 14.2 Power Supplies                                                | .263 |

|           | 14.2.1 QSFI-4 Interface Power Supply Decoupling Recommendations    | .263 |

|           | 14.2.2 2.488 GHz Line Side Power Supply Decoupling Recommendations | 263  |

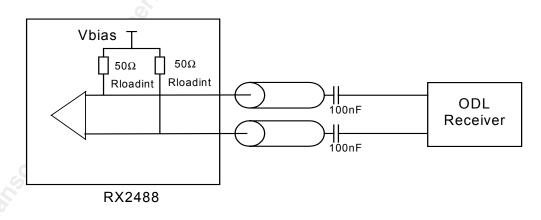

|           | 14.3 Interfacing to ODL Devices                                    |      |

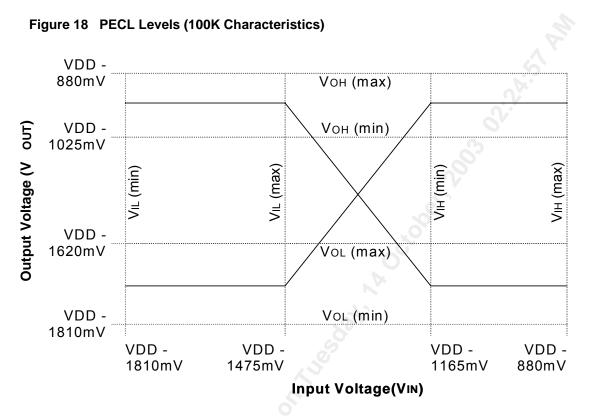

|           | 14.3.1 Output Levels                                               | .263 |

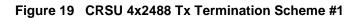

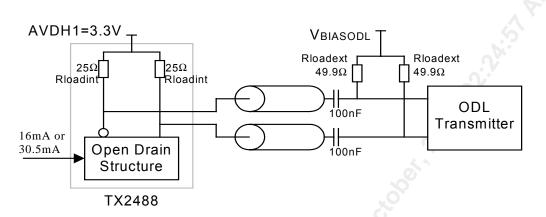

|           | 14.3.2 Termination Scheme                                          | .265 |

| <u>15</u> | Functional Timing                                                  | .267 |

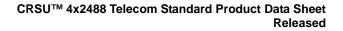

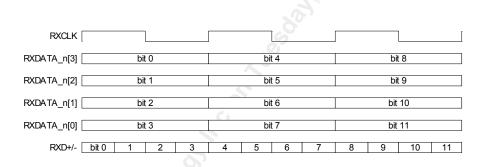

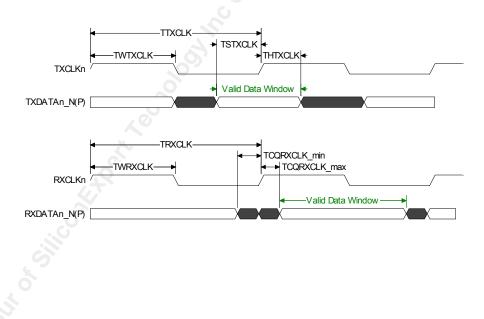

|           | 15.1 QSFI-4 Interface Timing                                       | .267 |

| <u>16</u> | Absolute Maximum Ratings                                           | .269 |

| <u>17</u> | Power Information                                                  | .270 |

|           | 17.1 Power Requirements                                            | .270 |

|           | 17.2 Power Sequencing                                              | .271 |

| <u>18</u> | D.C. Characteristics                                               | .273 |

| <u>19</u> | A.C. Timing Characteristics                                        | .276 |

|           | 19.1 Microprocessor Interface Timing Characteristics               | .276 |

|           | 19.2 Reset Timing                                                  | .279 |

|           | 19.3 JTAG Timing                                                   | .279 |

|           | <u>19.4</u> <u>QSFI-4 Timing</u>                                   | .281 |

|           | 19.5 OC-48 Interface Timing Characteristics                        | .282 |

| <u>20</u> | Ordering Information                                               | .283 |

| <u>21</u> | Thermal Information                                                | .284 |

| <u>22</u> | Mechanical Information                                             | .285 |

| Not       | <u>es</u>                                                          | .286 |

Proprietary and Confidential to PMC-Sierra, Inc., and for its Customers' Internal Use Document ID: PMC-2001972, Issue 5

### **List of Registers**

| Register 0000H: Identity and Global Performance Monitor Update Trigger | 84  |

|------------------------------------------------------------------------|-----|

| Register 0001H: Master Reset                                           | 86  |

| Register 0002H: Master Interrupt Status RX CH0                         | 88  |

| Register 0003H: Master Interrupt Status RX CH1                         |     |

| Register 0004H: Master Interrupt Status RX CH2                         | 92  |

| Register 0005H: Master Interrupt Status RX CH3                         |     |

| Register 0006H: Master Interrupt Status TX CH0                         | 96  |

| Register 0007H: Master Interrupt Status TX CH1                         |     |

| Register 0008H: Master Interrupt Status TX CH2                         |     |

| Register 0009H: Master Interrupt Status TX CH3                         | 102 |

| Register 000AH: Channel Interrupt Status                               | 104 |

| Register 000BH: Configuration                                          |     |

| Register 000CH: Bypass and fiber order                                 | 107 |

| Register 000DH: Diagnostic Loopback and ICO control                    | 109 |

| Register 000EH: Clock Control                                          | 111 |

| Register 000FH: Bypass and Loop-across                                 | 113 |

| Register 0010H: Diagnostics#1                                          | 115 |

| Register 0011H: Channel 3 and 2 SALM Enables                           | 116 |

| Register 0012H: Channel 1 and 0 SALM ENABLES                           | 120 |

| Register 0013H: TXENB Control                                          | 124 |

| Register 0014H: Device Number                                          | 126 |

| Channel 0 Register Map:                                                | 128 |

| Register 1000H: QSFIM_2488 Status                                      | 128 |

| Register 1001H: QSFIM_2488 Control                                     | 129 |

| Register 1002H: QSFIM_2488 Reserved                                    | 131 |

| Register 1030H: RSOP Control                                           | 132 |

| Register 1031H: RSOP Interrupt Status                                  | 133 |

| Register 1040H: TIFE Configuration                                     | 134 |

| Register 1041H: TIFE Control                                           | 135 |

| Register 1042H: TIFE Error Insertion Byte 0                            | 137 |

| Register 1043H: TIFE Error Insertion Byte 1                            | 139 |

| Register 1044H: TIFE Error Insertion Byte 2                            | 141 |

| Register 1045H: TIFE Error Insertion Byte 3                            | 143 |

| Register 1050H: TRSP Configuration                               | 145 |

|------------------------------------------------------------------|-----|

| Register 1051H: TRSP Register Insertion                          |     |

| Register 1052H: TRSP Error Insertion                             | 149 |

| Register 1053H: TRSP Transmit J0 and Z0                          | 151 |

| Register 1054H: TRSP Transmit E1 and F1                          | 152 |

| Register 1055H: TRSP Transmit D1D3                               |     |

| Register 105AH: TRSP Transmit B1Mask                             |     |

| Register 1060H: TRSP Aux1 Configuration                          |     |

| Register 1070H: TRSP Aux2 Configuration                          |     |

| Register 1080H: TRSP Aux3 Configuration                          | 159 |

| Register 1061H: TRSP Aux1 Register Insertion                     |     |

| Register 1071H: TRSP Aux2 Register Insertion                     |     |

| Register 1081H: TRSP Aux3 Register Insertion                     |     |

| Register 1062H: TRSP Aux1 Error Insertion                        |     |

| Register 1072H: TRSP Aux2 Error Insertion                        | 161 |

| Register 1082H: TRSP Aux3 Error Insertion                        | 161 |

| Register 1063H: TRSP Aux1 Transmit Z0                            |     |

| Register 1073H: TRSP Aux2 Transmit Z0                            |     |

| Register 1083H: TRSP Aux3 Transmit Z0                            |     |

| Register 1064-106AH: TRSP Aux1 Reserved                          |     |

| Register 106BH- 106FH unused                                     |     |

| Register 1074-107AH: TRSP Aux2 Reserved                          |     |

| Register 107BH- 107FH unused                                     | 164 |

| Register 1084-108AH: TRSP Aux3 Reserved                          | 164 |

| Register 108BH- 108FH unused                                     | 164 |

| Register 1090H: STLI Clock Configuration                         | 165 |

| Register 10A0H: TXLI Control/Status                              |     |

| Register 10A1H: TXLI CSU Control                                 |     |

| Register 10A2H: TXLI Pattern Register                            | 172 |

| Register 1100H: RXLI Interrupt Status                            | 173 |

| Register 1101H: RXLI Interrupt Control                           | 176 |

| Register RXLI 1102H: CRU Control                                 | 178 |

| Register 1103H: RXLI CRU Clock Training Configuration and Status |     |

| Register 1104H: RXLI PRBS Control                                |     |

| Register 1105H: RXLI Pattern                                     |     |

| Register 1106H – 110FH: RXLI Reserved                   |     |

|---------------------------------------------------------|-----|

| Register 1110H: SRLI Clock Configuration                |     |

| Register 1120H: RRMP Configuration                      |     |

| Register 1121H: RRMP Status                             |     |

| Register 1122H: RRMP Interrupt Enable                   |     |

| Register 1123H: RRMP Interrupt Status                   |     |

| Register 1124H: RRMP Receive APS                        |     |

| Register 1125H: RRMP Receive SSM                        |     |

| Register 1126H: RRMP AIS Enable                         |     |

| Register 1127H: RRMP Section BIP Error Counter          |     |

| Register 1128H: RRMP Line BIP Error Counter (LSB)       | 201 |

| Register 1129H: RRMP Line BIP Error Counter (MSB)       | 201 |

| Register 112AH: RRMP Line REI Error Counter (LSB)       |     |

| Register 112BH: RRMP Line REI Error Counter (MSB)       | 202 |

| Register 1136H: RRMP AIS Enable 2 (Slave)               |     |

| Register 1146H: RRMP AIS Enable 3 (Slave)               |     |

| Register 1156H: RRMP AIS Enable 4 (Slave)               |     |

| Register 1160H: RIFD Configuration                      | 204 |

| Register 1161H: RIFD Status                             | 206 |

| Register 1162H: RIFD Interrupt Enable                   | 207 |

| Register 1163H: RIFD Interrupt Status                   | 209 |

| Register1164H: RIFD correctable error count LSB         | 211 |

| Register 1165H: RIFD correctable error count MSB        | 212 |

| Register 1166H: RIFD line BIP error count LSB           | 213 |

| Register 1167H: RIFD line BIP error count MSB           | 214 |

| Register 1180H: SBER Configuration                      | 215 |

| Register 1181H: SBER Status                             | 217 |

| Register 1182H: SBER Interrupt Enable                   | 218 |

| Register 1183H: SBER Interrupt Status                   | 219 |

| Register 1184H: SBER SF BERM Accumulation Period (LSB)  | 220 |

| Register 1185H: SBER SF BERM Accumulation Period (MSB)  | 220 |

| Register 1186H: SBER SF BERM Saturation Threshold (LSB) | 221 |

| Register 1187H: SBER SF BERM Saturation Threshold (MSB) | 221 |

| Register 1188H: SBER SF BERM Declaring Threshold (LSB)  | 222 |

| Register 1189H: SBER SF BERM Declaring Threshold (MSB)  |     |

| Register 118AH: SBER SF BERM Clearing Threshold (LSB)      | 223 |

|------------------------------------------------------------|-----|

| Register 118BH: SBER SF BERM Clearing Threshold (MSB)      | 223 |

| Register 118CH: SBER SD BERM Accumulation Period (LSB)     | 224 |

| Register 118DH: SBER SD BERM Accumulation Period (MSB)     | 224 |

| Register 118EH: SBER SD BERM Saturation Threshold (LSB)    |     |

| Register 118FH: SBER SD BERM Saturation Threshold (MSB)    | 225 |

| Register 1190H: SBER SD BERM Declaration Threshold (LSB)   | 226 |

| Register 1191H: SBER SD BERM Declaration Threshold (MSB)   | 226 |

| Register 1192H: SBER SD BERM Clearing Threshold (LSB)      | 227 |

| Register 1193H: SBER SD BERM Clearing Threshold (MSB)      | 227 |

| Register 1194-11FFH: Unused                                | 227 |

| Register 2000H: CRSU 4x2488 Master Test                    | 229 |

| Register 2001H: CRSU-4X2488 Test Mode Address Force Enable | 231 |

| Register 2002H: CRSU-4X2488Test Mode Address Force Value   | 232 |

| Register 2003H: CRSU-4X2488 Reserved Test Register         | 233 |

### **List of Figures**

| Figure 1  | 2.488 Gbit/s Stream Pure SERDES Application                          | 22  |

|-----------|----------------------------------------------------------------------|-----|

| Figure 2  | STS-48 (STM-16) SERDES Application                                   |     |

| Figure 3  | STS-48 (STM-16) FEC Line Regeneration Equipment (LRE)<br>Application | 24  |

| Figure 4  | Normal Operation                                                     |     |

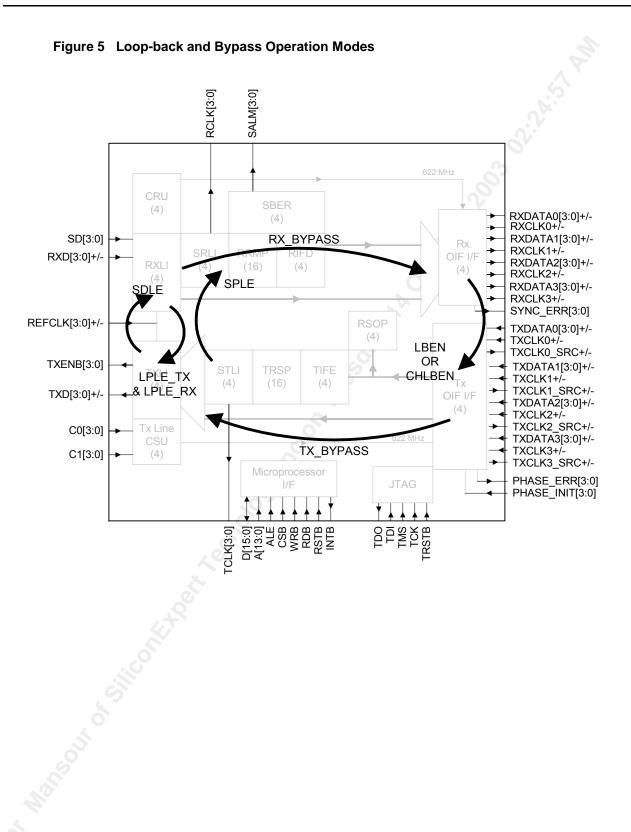

| Figure 5  | Loop-back and Bypass Operation Modes                                 |     |

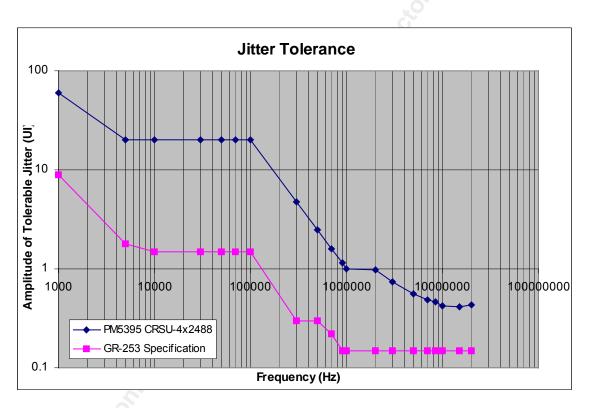

| Figure 6  | Typical STS-48c (STM-16c) Jitter Tolerance                           | 57  |

| Figure 7  | STS-48 (STM-16) in SOH, Master TRSP                                  | 64  |

| Figure 8  | SOH Insertion Priority                                               | 64  |

| Figure 9  | Z0/National Growth Bytes Definition for Row #1                       | 65  |

| Figure 10 | Input Observation Cell (IN_CELL)                                     | 239 |

| Figure 11 | Output Cell (OUT_CELL)                                               | 239 |

| Figure 12 | Bidirectional Cell (IO_CELL)                                         | 240 |

| Figure 13 | Layout of Output Enable and Bidirectional Cells                      | 240 |

| Figure 14 | Boundary Scan Architecture                                           | 241 |

| Figure 15 | TAP Controller Finite State Machine                                  | 243 |

| Figure 16 | Generic LVDS Link Block Diagram                                      | 247 |

| Figure 17 | CRSU 4x2488 to S/UNI-9953 Interface                                  |     |

| Figure 18 | PECL Levels (100K Characteristics)                                   | 264 |

| Figure 19 | CRSU 4x2488 Tx Termination Scheme #1                                 |     |

| Figure 20 | CRSU 4x2488 Tx Termination Scheme #2                                 |     |

| Figure 21 | CRSU 4x2488 Rx Termination Scheme                                    |     |

| Figure 22 | Receive Side Timing Diagram                                          |     |

| Figure 23 | Transmit Side Timing Diagram                                         |     |

| Figure 24 | QSFI-4 Error Indication Timing Diagram                               |     |

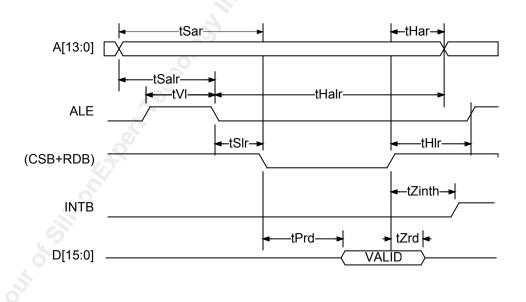

| Figure 25 | Intel Microprocessor Interface Read Timing                           | 276 |

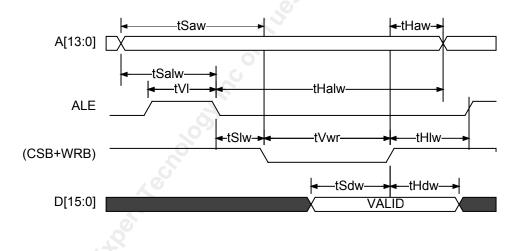

| Figure 26 | Intel Microprocessor Interface Write Timing                          | 278 |

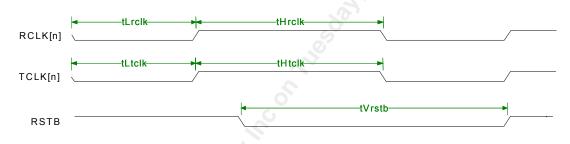

| Figure 27 | System Miscellaneous Timing Diagram Timing                           | 279 |

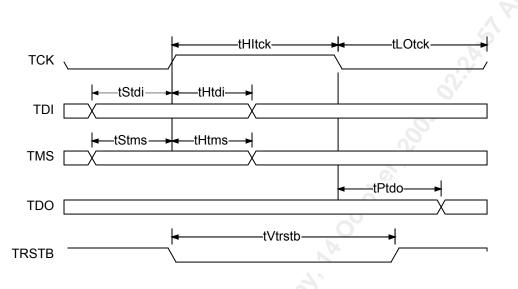

| Figure 28 | JTAG Port Interface Timing                                           |     |

| Figure 29 | QSFI-4 Master Interface Timing                                       |     |

|           |                                                                      |     |

|           |                                                                      |     |

|           |                                                                      |     |

| <br>      |                                                                      |     |

#### **List of Tables**

| Table 1 Abb  | previations Used in this Document                                                                | 16  |

|--------------|--------------------------------------------------------------------------------------------------|-----|

| Table 2 CR   | SU 4x2488 Modes of Operation                                                                     | 28  |

| Table 3 CRS  | SU 4x2488 Top Left Corner Pin-Out                                                                |     |

| Table 4 CRS  | SU 4x2488 Bottom Left Corner Pin-Out                                                             | 31  |

|              | SU 4x2488 Top Right Corner Pin-Out                                                               |     |

| Table 6 CRS  | SU 4x2488 Bottom Right Corner Pin-Out                                                            | 33  |

|              | nctional Block use per Mode                                                                      |     |

|              | ister Memory Map                                                                                 |     |

|              | SU 4x2488 Channel Register Map                                                                   |     |

| Table 10 TX  | X2488 Mode Control                                                                               | 167 |

| Table 11 Te  | est Mode Register Memory Map                                                                     | 228 |

| Table 12 In: | struction Register (Length - 3 bits)                                                             | 234 |

| Table 13 Id  | entification Register                                                                            | 234 |

| Table 14 Bo  | oundary Scan Register                                                                            | 234 |

|              | ecommended BERM settings for different data and BER rates, neeting Bellcore Objectives           | 251 |

|              | ecommended BERM settings for different data and BER rates, neeting Bellcore and ITU requirements | 252 |

| Table 17 Cl  | RSU 4x2488 and ODL Amplitudes                                                                    | 264 |

| Table 18 At  | osolute Maximum Ratings                                                                          | 269 |

| Table 19 Po  | ower Requirements                                                                                | 270 |

| Table 20 D.  | C. Characteristics (CMOS/TTL) <sup>1</sup>                                                       | 273 |

| Table 21 Mi  | icroprocessor Interface Read Access                                                              | 276 |

| Table 22 Mi  | icroprocessor Interface Write Access                                                             | 278 |

| Table 23 Sy  | ystem Miscellaneous Timing                                                                       | 279 |

| Table 24 JT  | AG Port Interface (Figure 28)                                                                    | 279 |

| Table 25 Q   | SFI-4 Interface Timing                                                                           | 281 |

| Table 26 O   | C-48 Interface Timing                                                                            | 282 |

| Table 27 Or  | rdering Information                                                                              | 283 |

| Table 28 Or  | utside Plant Thermal Information                                                                 | 284 |

| Table 29 De  | evice Compact Model <sup>3</sup>                                                                 | 284 |

| Table 30 He  | eat Sink Requirements                                                                            | 284 |

|              |                                                                                                  |     |

#### 1 **Definitions**

The following table defines the abbreviations for the CRSU<sup>TM</sup> 4x2488.

| Table 1 | Abbreviations | Used in this  | Document |

|---------|---------------|---------------|----------|

|         | Approviduolio | 0000 111 1110 | Dooument |

| AIS   | Alarm Indication Signal                   |

|-------|-------------------------------------------|

| AIS-L | Alarm Indication Signal for Line overhead |

| APS   | Automatic Protection Switching            |

| ASSP  | Application Specific Standard Product     |

| ATM   | Asynchronous Transfer Mode                |

| BER   | Bit Error Rate                            |

| BIP   | Bit Interleaved Parity                    |

| CMOS  | Complementary Metal Oxide Semiconductor   |

| CRC   | Cyclic Redundancy Check                   |

| CRU   | Clock Recovery Unit                       |

| CSU   | Clock Synthesis Unit                      |

| DCC   | Data Communication Channel                |

| DRU   | Data Recovery Unit                        |

| ECL   | Emitter Controlled Logic                  |

| ERDI  | Enhanced Remote Defect Indication         |

| ESD   | Electrostatic Discharge                   |

| FCS   | Frame Check Sequence                      |

| FEBE  | Far-End Block Error                       |

| FIFO  | First-In First-Out                        |

| GFC   | Generic Flow Control                      |

| HCS   | Header Check Sequence                     |

| HDLC  | High-level Data Link Layer                |

| ICO   | Current Controlled Oscillator             |

| JAT   | Jitter Attenuator                         |

| LCD   | Loss of Cell Delineation                  |

| LOF   | Loss of Frame                             |

| LOP   | Loss of Pointer                           |

| LOS   | Loss of Signal                            |

| LVDS  | Low Voltage Differential Signaling        |

| NC    | No Connect, indicates an Unused pin       |

| NDF   | New Data Flag                             |

| NNI   | Network-Network Interface                 |

| ODL   | Optical Data Link                         |

| OOF   | Out of Frame                              |

| PECL  | Pseudo-ECL                                |

| PISO   | Parallel to Serial Converter                  |

|--------|-----------------------------------------------|

| PLL    | Phase-Locked Loop                             |

| POS    | Packet Over SONET                             |

| PPP    | Point-to-Point Protocol                       |

| PRBS   | Pseudo-Random Bit Sequence                    |

| QSFI-4 | Quad Serdes/Framer Electrical Interface       |

| RDI-L  | Line Remote Defect Indication                 |

| RRMP   | Receive Regenerator and Multiplexor Processor |

| RDI    | Remote Defect Indication                      |

| RIFD   | Receive In-band FEC Decoder                   |

| RSOP   | Receive Section Overhead Processor            |

| RXLI   | Receive Line Interface                        |

| SBER   | SONET/SDH Bit Error Rate Monitor              |

| SD     | Signal Degrade                                |

| SDH    | Synchronous Digital Hierarchy                 |

| SF     | Signal Fail                                   |

| SONET  | Synchronous Optical Network                   |

| SPE    | Synchronous Payload Envelopes                 |

| SRLI   | SONET/SDH Receive Line Interface              |

| STLI   | SONET/SDH Transmit Line Interface             |

| STSI   | Space and Timeslot Interchange                |

| TIFE   | Transmit In-band FEC Encoder                  |

| ТОН    | Transport Overhead                            |

| TRSP   | Transmit Regenerator and Section Processor    |

| TXLI   | Transmit Line Interface                       |

| UI     | Unit Interval                                 |

| UNI    | User-Network Interface                        |

| VCI    | Virtual Connection Indicator                  |

| VCXO   | Voltage Controlled Crystal Oscillator         |

| VPI    | Virtual Path Indicator                        |

| WAN    | Wide Area Network                             |

| XOR    | Exclusive OR logic operator                   |

#### 2 Features

#### 2.1 General

- Single chip Clock Recovery and Synthesis Unit supporting four SONET/SDH links operating at 2488.32 Mbit/s.

- Processes four independent bit-serial 2488.32 Mbit/s STS-48 (STM-16) data streams with onchip clock and data recovery and clock synthesis.

- Complies with Bellcore GR-253-CORE jitter tolerance, jitter transfer and intrinsic jitter criteria.

- Implements In-band Forward Error Correction (FEC) source and sink function according to ANSI Committee T1, Letter Ballot LB812.

- Implements In-band Forward Error Correction (FEC) line regeneration equipment (LRE) function according to ANSI Committee T1, Letter Ballot LB812.

- Provides performance monitoring of SONET Section, and Line layer entities or SDH Regenerator Section, and Multiplexer Section entities.

- Interfaces with downstream SONET/SDH framer devices over a set of four 4-bit, 622 MHz ports that conforms to the timing and AC characteristics defined in the Optical Internetworking Forum, contribution OIF-SFI4-01.0.

- Supports line loop-back from the line side receive stream to the transmit stream and system side loop-back from the QSFI-4 transmit interface to the QSFI-4 receive stream interface.

- Supports loop-timing of the transmit stream from the associated receive stream.

- Supports Internal Channel-to-Channel loop Function. Channel 0 can be internally connected to Channel 1, and Channel 2 can be connected to Channel 3.

- Provides a standard 5 signal IEEE 1149.1 JTAG test port for boundary scan board test purposes.

- Provides a generic 16-bit microprocessor bus interface for configuration, control, and status monitoring.

- Low power 1.8V CMOS core logic with 3.3V CMOS/TTL compatible digital inputs and digital outputs. PECL inputs and CML outputs are 3.3V compatible.

- Industrial temperature range (-40°C to +85°C Ambient, 125°C Maximum Junction Temperature).

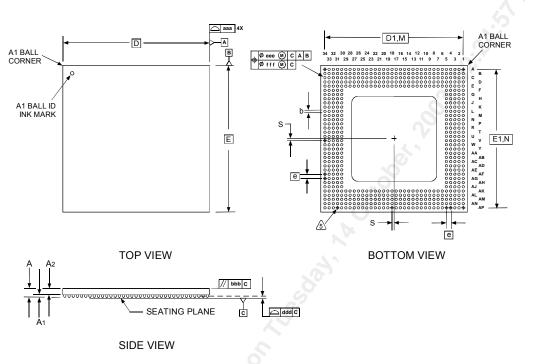

- 580 pin 35mmx35mm UBGA package.

# 2.2 SONET Section and Line / SDH Regenerator and Multiplexer Section

• Frames to the SONET/SDH receive stream and inserts the framing bytes (A1, A2) into the transmit stream; unscrambles the received stream and scrambles the transmit stream.

- Calculates and compares the bit interleaved parity (BIP) error detection codes (B1, B2) for the receive stream. Calculates and inserts B1 in the transmit stream. Accumulates near end errors (B1, B2) and far end errors (M1).

- Extracts and filters the automatic protection switch (APS) channel (K1, K2) bytes into internal registers.

- Extracts and filters the synchronization status message (S1) byte into an internal register for the receive stream.

- Detects loss of signal (LOS), out of frame (OOF), loss of frame (LOF), line remote defect indication (RDI-L), line alarm indication signal (AIS-L), and protection switching byte failure alarms on the receive stream.

- Provides a mechanism to insert automatic line AIS insertion following detection of various received alarms LOS and LOF on to the QSFI-4 system side receive interface.

- Configurable to force Line AIS in the transmit stream.

#### 2.3 SONET / SDH In-band Forward Error Correction

- Implements In-band Forward Error Correction sink function with a maximum delay of 15µs. Frames to the FEC status indication signal (FSI), and optionally outputs corrected data onto the receive system side interface.

- Counts corrected FEC errors in a set of software readable registers.

- Implements In-band Forward Error Correction source function with a maximum delay of 15µs. Optionally inserts FEC checksum bytes and FSI into the transmit stream. Line BIP (B2) bytes are compensated for the inserted FEC byte values.

- Support FEC Line Regeneration Equipment function with a maximum delay of 15.36µs by looping the receive stream to the transmit stream after FEC error correction.

### **3** Applications

- DWDM Terminal Multiplexers.

- ATM and Multi-service Switches, routers, and switch/routers

- SONET/SDH Add/Drop Multiplexers with data processing capabilities

- SONET/SDH ATM/POS Test Equipment

#### 4 References

- 1. Applicable Recommendations and Standards. The designer is required to read these references during the Design Planning task. See the Device Design Procedure, PMC-1940424.

- 2. Telcordia GR-253-CORE "SONET Transport Systems: Common Generic Criteria", Issue 3, September 2000.

- 3. Telcordia GR-253-CORE "SONET Transport Systems: Common Generic Criteria", Issue 2, December 1995.

- 4. Telcordia GR-436-CORE "Digital Network Synchronization Plan", Issue 1 Revision 1, June 1996.

- 5. ANSI T1.105-1995, "Synchronous Optical Network (SONET) Basic Description including Multiplex Structure, Rates, and Formats", 1995.

- 6. ANSI T1 Letter Ballot LB812, "In-band FEC for SONET", October 1999.

- 7. ETS 300 417-1-1, "Generic Functional Requirements for Synchronous Digital Hierarchy (SDH) Equipment", January 1996.

- 8. ITU-T Recommendation G.703 "Physical/Electrical Characteristics of Hierarchical Digital Interfaces", 1991.

- ITU-T Recommendation G.704 "General Aspects of Digital Transmission Systems; Terminal Equipment - Synchronous Frame Structures Used At 1544, 6312, 2048, 8488 and 44 736 kbit/s Hierarchical Levels", July 1995.

- 10. ITU, Recommendation G.707 "Network Node Interface For The Synchronous Digital Hierarchy", 1996.

- 11. ITU Recommendation G781, "Structure of Recommendations on Equipment for the Synchronous Design Hierarchy (SDH)", January 1994.

- 12. ITU, Recommendation G.783 "Characteristics of Synchronous Digital Hierarchy (SDH) Equipment Functional Blocks", 1996.

- 13. OIF-SFI4-01.0, "SFI-4: Common electrical interface between framers and serializer/deserializer parts for STS-192/STM-64 interfaces". September 26, 2000.

- 14. IEEE std 1596.3-1996, "IEEE Standard for Low-Voltage Differential Signals (LVDS) for scaleable Coherent Interface (SCI)", March 21, 1996

### **5** Application Examples

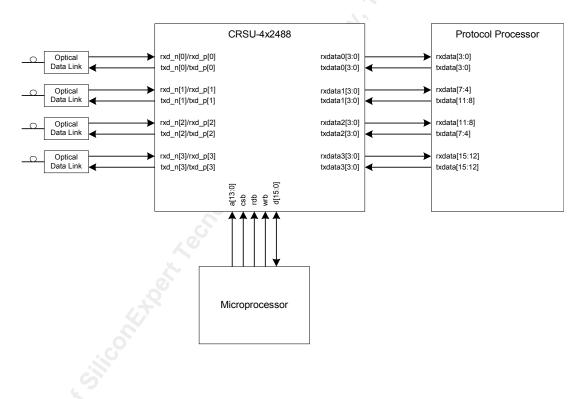

The PM5395 CRSU 4x2488 is applicable to many types of equipment that implement a 2.488 Gbit/s serial interfaces. When the device is configured for pass through mode the CRSU 4x2488 bridges between an optical module and a Protocol Processor. No higher level processing of the data is done after the data is extracted from the serial stream. In this mode, the CRSU 4x2488 may serve as the SERDES for data streams of arbitrary formats provided for optical line-side data rates of 2.488Gbit/s. The CRSU 4x2488 provides clock and data recovery functions in the receive direction and clock synthesis functions in the transmit direction. The four interfaces to the optical module are serial 2.488 Gbit/s serial streams and the interface to the Protocol Processor is a quad 4-bit version of the Optical Internetworking Forum SFI-4 Specification. Figure 1 shows a simplified connection diagram to illustrate the example of the CRSU 4x2488 connected to a Protocol Processor.

#### Figure 1 2.488 Gbit/s Stream Pure SERDES Application

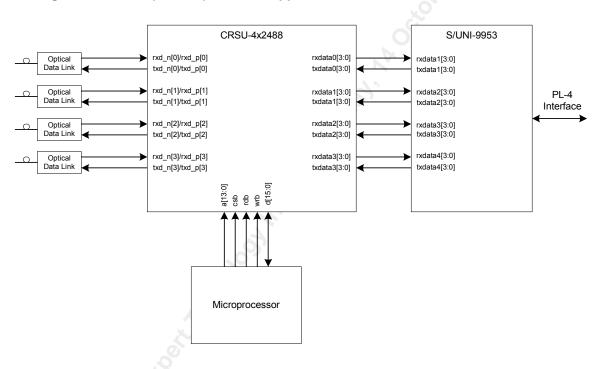

The PM5395 CRSU 4x2488 is applicable to equipment implementing SONET OC-48 or SDH STM-16 interfaces. Figure 2 shows the CRSU 4x2488 connected to the S/UNI-9953 OC-192 Physical Layer Device. The CRSU 4x2488 also directly connects to the SPECTRA-9953 SONET/SDH Payload Extractor Aligner for channelized OC-192 applications. In addition to bridging between the optical module and the SONET/SDH framer devices, the CRSU 4x2488 optionally performs SONET section and line layer or SDH regenerator and multiplex section performance monitoring. It provides clock and data recovery functions in the receive direction and clock synthesis functions in the transmit direction. The interfaces to the optical module are serial 2.488 Gbit/s streams and the interface to SONET/SDH framers is a quad 4-bit version of the Optical Internetworking Forum SFI-4 Specification.

#### Figure 2 STS-48 (STM-16) SERDES Application

In a typical In-band Forward Error Correction (FEC) termination application, the CRSU 4x2488 performs clock and data recovery in the receive direction and clock synthesis in the transmit direction of the line interface. In addition, in the receive direction, errors in the received data stream are corrected using the FEC checksum bytes embedded in the SONET transport overhead or SDH section overhead bytes. In the transmit direction, FEC checksum bytes are inserted into the overhead bytes.

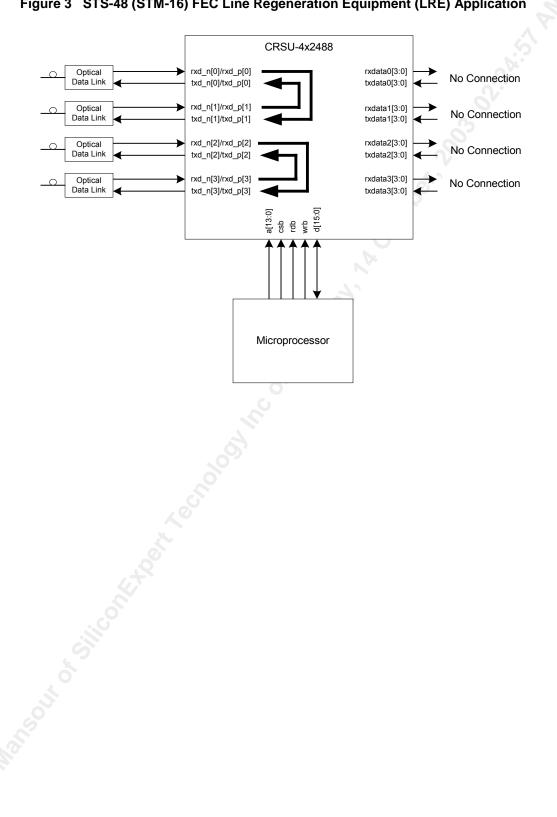

In a typical In-band Forward Error Correction (FEC) Line Regeneration Equipment (LRE) application as shown in Figure 3, the CRSU 4x2488 performs clock and data recovery in the receive direction and is loop timed in the transmit direction of the line interface. Errors in the received data stream are corrected using the FEC checksum bytes embedded in the SONET transport overhead or SDH section overhead bytes and it transmitted out the transmit line interface

#### 6 Block Diagram

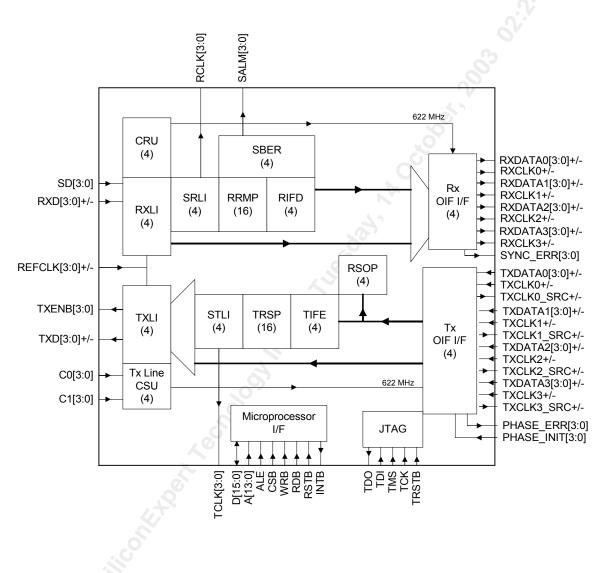

#### Figure 4 Normal Operation

#### 7 Description

The PM5395 CRSU 4x2488 Quad Clock Recovery and Synthesis Unit Interface is a monolithic integrated circuit that bridges between the optical module and the SONET/SDH framer devices. It provides clock and data recovery functions in the receive direction and clock synthesis functions in the transmit direction. The interfaces to the optical module are serial 2.488 Gbit/s streams and the interface to SONET/SDH framers is a quad 4-bit version of the Optical Internetworking Forum SFI-4 Specification.

The CRSU 4x2488 receives SONET/SDH streams using a bit serial interface, recovers the clock and data and processes section and line overhead. The CRSU 4x2488 performs framing (A1, A2), de-scrambling, detects alarm conditions, and monitors section and line bit interleaved parity (B1, B2), accumulating error counts at each level for performance monitoring purposes. Line remote error indications (M1) are also accumulated. Optionally, the CRSU 4x2488 frames to the in-band forward error correction status indication byte and processes the checksum bytes. Detected errors are accumulated and corrected. Processing delay is limited to less than 15µs.

The CRSU-4x2488 transmits SONET/SDH streams using a bit serial interface. The CRSU 4x2488 synthesizes the transmit clock from a 155.52MHz frequency reference and performs framing pattern insertion (A1, A2), scrambling, alarm signal insertion, and creates section bit interleaved parity codes (B1) as required to allow performance monitoring at the far end. Optionally, the CRSU 4x2488 supports In-band FEC functions. FEC status indication bytes, and checksum bytes are inserted into the transport overhead bytes and the line BIP bytes are compensated to reflect the inserted checksum bytes. Processing delay is limited to less than 15µs. The CRSU 4x2488 also supports the insertion of a large variety of errors into the transmit stream, such as framing pattern errors, and bit interleaved parity errors which are useful for system diagnostics and tester applications.

For all modes no line rate clocks are required directly by the CRSU–4x2488 as it synthesizes the transmit clock and recovers the receive clock using a 155.52 MHz reference clock. The CRSU 4x2488 outputs a set of four differential PECL line data (TXD[3:0]+/-).

The CRSU–4x2488 is configured, controlled and monitored via a generic 16-bit microprocessor bus interface. The CRSU–4x2488 also provides a standard 5 signal IEEE 1149.1 JTAG test port for boundary scan board test purposes.

The CRSU–4x2488 is implemented in low power, +1.8 Volt, CMOS technology. It has TTL compatible digital inputs and TTL/CMOS compatible digital outputs. High speed inputs and outputs support 3.3V compatible pseudo-ECL (PECL) and CML, respectively. The CRSU–4x2488 is packaged in a 580 pin UBGA package.

The CRSU 4x2488 provides three main modes of operation, SERDES mode, PMON mode and Regenerator modes as shown in Table 2. In-band FEC is an optional feature that can be used in both the PMON and Regenerator modes.

| Table 2 | CRSU 4x2488 | Modes of O | peration |

|---------|-------------|------------|----------|

|---------|-------------|------------|----------|

| Operational Mode | Mode Description                                                                                                                             |

|------------------|----------------------------------------------------------------------------------------------------------------------------------------------|

| SERDES Mode      | Quad 2.488 Gbit/s serializer/deserializer                                                                                                    |

| PMON Mode        | Quad OC-48 (2.488 Gbit/s) serializer/deserializer<br>with SONET/SDH overhead performance<br>monitoring and optional Forward Error Correction |

| Regenerator Mode | Quad 2.488 Gbit/s serializer/deserializer with internal regenerator connection between                                                       |

|                  | channel 0 to channel 1 and                                                                                                                   |

|                  | channel 2 to channel 3                                                                                                                       |

|                  | Performance monitoring (PMON Mode) and Forward Error Correction are optional for this mode.                                                  |

#### SERDES Mode

In SERDES Mode, the CRSU 4x2488 provides clock recovery and synthesis for four independent bit-serial streams. In this mode, the CRSU 4x2488 can be used as a bridge between a SONET/SDH framer and other devices such as emerging G.709 framers. The CRSU 4x2488 connects to the framer or higher layer device via a quad 4-bit version of the OIF SFI-4 specification.

#### **PMON Mode**

The CRSU 4x2488 provides a PMON Mode to support DWDM and other applications that require optimized devices to perform SONET/SDH compliant data recovery as well as overhead performance monitoring. The CRSU–4x2488 receives SONET/SDH streams using a bit serial interface, recovers the clock and data and processes section and line overhead. The CRSU 4x2488 performs framing (A1, A2), de-scrambling, detects alarm conditions, and monitors section and line bit interleaved parity (B1, B2), accumulating error counts at each level for performance monitoring purposes. Line remote error indications (M1) are also accumulated. Optionally, the CRSU–4x2488 frames to the in-band forward error correction status indication byte and processes the checksum bytes. Detected errors are accumulated and corrected. Processing delay is limited to less than 15 µs.

The CRSU–4x2488 transmits SONET/SDH streams using a bit serial interface. The CRSU–4x2488 synthesizes the transmit clock from a 155.52 MHz frequency reference and performs framing pattern insertion (A1, A2), scrambling, alarm signal insertion, and creates section bit interleaved parity codes (B1) as required to allow performance monitoring at the far end. Optionally, the CRSU–4x2488 supports In-band FEC functions. FEC status indication bytes, and checksum bytes are inserted into the transport overhead bytes and the line BIP bytes are compensated to reflect the inserted checksum bytes. Processing delay is limited to less than 15 $\mu$ s. The CRSU–4x2488 also supports the insertion of a large variety of errors into the transmit stream, such as framing pattern errors, and bit interleaved parity errors which are useful for system diagnostics and tester applications.

#### **Regenerator Mode**

The CRSU 4x2488 provides a Regenerator Mode to support dense regenerator applications. In this mode, the CRSU 4x2488 provides an internal connection between channel 0 to channel 1 and from channel 2 to channel 3. The CRSU 4x2488 performs clock and data recovery in the receive direction and is loop timed in the transmit direction of the line interface. While in regenerator mode, the performance monitoring capability (PMON Mode) and Forward Error Correction functions may be utilized. These functions can be flexibly configured to allow conversion from OC-48 SONET/SDH streams on one side while supporting in-band forward error correction on the other side, processing delay is limited to less than  $15.36\mu$ s.

Both PMON and Regenerator modes of the CRSU 4x2488 support in-band FEC according to ANSI-T1 letter ballot LB812. In-band FEC checksum bytes are inserted into the SONET Transport or SDH section overhead bytes in the transmit direction. In the receive direction, errors in the received data stream are corrected using the FEC checksum bytes embedded in the SONET transport overhead or the SDH section overhead bytes.

### 8 Pin Diagram

#### Table 3 CRSU 4x2488 Top Left Corner Pin-Out

|   | 34    | 33    | 32    | 31            | 30             | 29             | 28              | 27              | 26              | 25              | 24              | 23              | 22              | 21              | 20              | 19            |

|---|-------|-------|-------|---------------|----------------|----------------|-----------------|-----------------|-----------------|-----------------|-----------------|-----------------|-----------------|-----------------|-----------------|---------------|

| A | vss   | vss   | vss   | vss           | vss            | avdl_qs<br>fim | vss             | rxdata0<br>[1]+ | rxdata0<br>[2]+ | txclk_s<br>rc0+ | rxdatal<br>[1]+ | rxdatal<br>[2]+ | txclk_s<br>rcl+ | rxdata2<br>[1]+ | rxdata2<br>[2]+ | txclk<br>rc2+ |

| в | vss   | vss   | vss   | vss           | res            | avdl_qs<br>fim | vss             | rxdata0<br>[1]- | rxdata0<br>[2]- | txclk_s<br>cr0- | rxdatal<br>[1]- | rxdatal<br>[2]- | txclk_s<br>rcl- | rxdata2<br>[1]- | rxdata2<br>[2]- | txclk<br>rc2- |

| С | vss   | vss   | vss   | vss           | resk           | VSS            | rxdata0<br>[0]- | rxclk0-         | rxdata0<br>[3]- | rxdatal<br>[0]- | rxclk1-         | rxdatal<br>[3]- | rxdata2<br>[0]- | rxclk2-         | rxdata2<br>[3]- | rxdat<br>[0]- |

| D | vss   | vss   | vss   | vss           | avdh_qs<br>fim | VSS            | rxdata0<br>[0]+ | rxclk0+         | rxdata0<br>[3]+ | rxdatal<br>[0]+ | rxclk1+         | rxdatal<br>[3]+ | rxdata2<br>[0]+ | rxclk2+         | rxdata2<br>[3]+ | rxdat<br>[0]+ |

| E | vss   | vss   | vss   | vss           | avdh_qs<br>fim | avdl_qs<br>fim | avdl_qs<br>fim  | avdh_qs<br>fim  | avdl_qs<br>fim  | avdh_qs<br>fim  | avdl_qs<br>fim  | avdh_qs<br>fim  | avdl_qs<br>fim  | avdh_qs<br>fim  | avdl_qs<br>fim  | avdh_<br>fim  |

| F | vddo  | vddo  | vddo  | vddo          | vddo           |                | <u>I</u>        | Į               | Į               | <u> </u>        | Į               | <u> </u>        | <u>I</u>        | <u>I</u>        | <u>I</u>        | <u> </u>      |

| G | d[15] | d[14] | d[13] | vddo          | vddi           |                |                 |                 |                 |                 |                 |                 |                 |                 |                 |               |

| н | d[12] | d[11] | d[9]  | vddo          | d[10]          | -              |                 |                 |                 |                 |                 |                 |                 |                 |                 |               |

| J | d[8]  | d[7]  | d[5]  | d[6]          | vddi           | -              |                 |                 |                 |                 |                 |                 |                 |                 |                 |               |

| к | d[4]  | d[3]  | d[1]  | d[2]          | vddo           | -              |                 |                 |                 |                 |                 |                 |                 |                 |                 |               |

| L | d[0]  | csb   | wrb   | rdb           | vddi           |                |                 |                 |                 |                 |                 |                 |                 |                 |                 |               |

| М | ale   | a[0]  | vddo  | a[2]          | a[1]           |                |                 |                 |                 |                 |                 |                 |                 |                 |                 |               |

| N | a[3]  | a[4]  | a[6]  | a[5]          | vddi           |                |                 |                 |                 |                 |                 |                 |                 |                 |                 |               |

| P | a[7]  | a[8]  | a[11] | a[10]         | a[9]           | 1              |                 |                 |                 |                 |                 |                 |                 |                 |                 |               |

| R | vddo  | a[12] | rstb  | a[13]         | vddi           |                |                 |                 |                 |                 |                 |                 |                 |                 |                 |               |

|   | intb  | NC    | vddi  | lcruto[<br>0] | VSS            |                |                 |                 |                 |                 |                 |                 |                 |                 |                 |               |

| т |       |       |       | vddo          | vddo           |                |                 |                 |                 |                 |                 |                 |                 |                 |                 |               |

I

c0[0]

c1[0]

V

|          | 34      | 33     |                       |                       |                          |                |        |                |         |               |         |         |                |                |        |              |

|----------|---------|--------|-----------------------|-----------------------|--------------------------|----------------|--------|----------------|---------|---------------|---------|---------|----------------|----------------|--------|--------------|

|          |         |        | 32                    | 31                    | 30                       | 29             | 28     | 27             | 26      | 25            | 24      | 23      | 22             | 21             | 20     | 19           |

| ٩P       | VSS     | vss    | vss                   | vss                   | vss                      | c0[1]          | vss    | rxd[1]+        | rxd[1]- | vss           | txd[1]- | txd[1]+ | vss            | vss            | avdl_1 | NC           |

| ۹N       | vss     | vss    | vss                   | vss                   | vss                      | c1[1]          | VSS    | vss            | vss     | vss           | vss     | vss     | vss            | vss            | avdl_1 | VSS          |

| ١M       | vss     | vss    | vss                   | vss                   | vss                      | avdh_cr<br>u_1 | VSS    | avdh_cr<br>u_1 | vss     | avdh_tx<br>_1 | vss     | vss     | refclk[<br>1]+ | refclk[<br>1]- | avdl_1 | lcruto<br>2] |

| ۸L       | vss     | vss    | vss                   | vss                   | vss                      | avdh_cr<br>u_1 | qavd   | avdh_cr<br>u_1 | vss     | avdh_tx<br>_1 | vss     | vss     | avdh_cs<br>u_1 | avdh_cs<br>u_1 | avdl_1 | lcruto<br>1] |

| K        | vss     | vss    | vss                   | vss                   | vss                      | avdh_cr<br>u_1 | avdl_1 | avdh_cr<br>u_1 | avdl_1  | avdh_tx<br>_1 | avdl_1  | avdl_1  | avdh_cs<br>u_1 | avdh_cs<br>u_1 | vddo   | vddi         |

| J        | vss     | vss    | vss                   | vss                   | vss                      |                |        |                |         |               |         |         |                |                |        |              |

| Η        | vss     | VSS    | VSS                   | vddi                  | vddi                     |                |        |                |         |               |         |         |                |                |        |              |

| G        | avdl_0  | avdl_0 | avdl_0                | avdl_0                | avd1_0                   |                |        |                |         |               |         |         |                |                |        |              |

| F        | vss     | vss    | refclk[<br>0]-        | u_0<br>avdh_cs<br>u_0 | u_0<br>avdh_cs<br>u_0    |                |        |                |         |               |         |         |                |                |        |              |

| E        | vss     | vss    | refclk[<br>0]+        | avdh_cs<br>u_0        | avdh_cs<br>u_0           |                |        |                |         |               |         |         |                |                |        |              |

| D        | txd[0]+ | vss    | vss                   | vss                   | avdl_0                   |                |        |                |         |               |         |         |                |                |        |              |

| ND<br>NC | txd[0]- | vss    | _0<br>vss             | _0<br>vss             | _0<br>avdl_0             |                |        |                |         |               |         |         |                |                |        |              |

| B        | vss     | vss    | avdh_tx               | avdh_tx               | avdh_tx                  |                |        |                |         |               |         |         |                |                |        |              |

| ,        | rxd[0]+ | vss    | avdh_cr<br>u_0<br>vss | avdh_cr<br>u_0<br>vss | avdh_cr<br>u_0<br>avdl_0 |                |        |                |         |               |         |         |                |                |        |              |

| /        | vss     | VSS    | VSS                   | qavd                  | avdl_0                   |                |        |                |         |               |         |         |                |                |        |              |

#### Table 4 CRSU 4x2488 Bottom Left Corner Pin-Out

avdh\_cr avdh\_cr avdh\_cr u\_0 u\_0 u\_0

I

1

|               | Ta              | ble 5           | CRSI            | J 4x24          | 488 To          | op Rig          | ght Co          | orner           | Pin-O           | ut              |                 |                 |                   |                   |                   |                  |                   |   |

|---------------|-----------------|-----------------|-----------------|-----------------|-----------------|-----------------|-----------------|-----------------|-----------------|-----------------|-----------------|-----------------|-------------------|-------------------|-------------------|------------------|-------------------|---|

| 8             | 17              | 16              | 15              | 14              | 13              | 12              | 11              | 10              | 9               | 8               | 7               | 6               | 5                 | 4                 | 3                 | 2                | 1                 |   |

| xdata3<br>1]+ | rxdata3<br>[2]+ | vss             | vddi            | txdata0<br>[1]+ | txdata0<br>[2]+ | txdatal<br>[0]+ | txclk1+         | txdatal<br>[3]+ | txdata2<br>[1]+ | txdata2<br>[2]+ | txdata3<br>[0]+ | txclk3+         | vss               | vss               | vss               | vss              | vss               | A |

| xdata3<br>1]- | rxdata3<br>[2]- | vddi            | vddi            | txdata0<br>[1]- | txdata0<br>[2]- | txdatal<br>[0]- | txclk1-         | txdatal<br>[3]- | txdata2<br>[1]- | txdata2<br>[2]- | txdata3<br>[0]- | txclk3-         | vss               | vss               | vss               | vss              | vss               | в |

| clk3-         | rxdata3<br>[3]- | txclk_s<br>rc3+ | txdata0<br>[0]- | txclk0-         | txdata0<br>[3]- | txdatal<br>[1]- | txdatal<br>[2]- | txdata2<br>[0]- | txclk2-         | txdata2<br>[3]- | txdata3<br>[1]- | txdata3<br>[2]- | txdata3<br>[3]+   | vss               | vss               | vss              | vss               | С |

| clk3+         | rxdata3<br>[3]+ | txclk_s<br>rc3- | txdata0<br>[0]+ | txclk0+         | txdata0<br>[3]+ | txdatal<br>[1]+ | txdatal<br>[2]+ | txdata2<br>[0]+ | txclk2+         | txdata2<br>[3]+ | txdata3<br>[1]+ | txdata3<br>[2]+ | txdata3<br>[3]-   | vss               | vss               | vss              | vss               | D |

| dl_qs<br>m    | avdh_qs<br>fim  | avdl_qs<br>fim  | avdl_qs<br>fim  | avdh_qs<br>fim  | avdl_qs<br>fim    | vss               | vss               | vss              | vss               | Е |

|               | I               | <u> </u>        | L               | I               | vddo              | vddo              | vddo              | vddo             | vddo              | F |

|               |                 |                 |                 |                 |                 |                 |                 |                 |                 |                 |                 |                 | vddo              | NC                | sync_er<br>r[3]   | sync_er<br>r[2]  | sync_er<br>r[1]   | G |

|               |                 |                 |                 |                 |                 |                 |                 |                 |                 |                 |                 |                 | vddo              | sync_er<br>r[0]   | phase_i<br>nit[3] | vddo             | phase_i<br>nit[2] | н |

|               |                 |                 |                 |                 |                 |                 |                 |                 |                 |                 |                 |                 | phase_i<br>nit[1] | phase_i<br>nit[0] | vddo              | phase_e<br>rr[3] | phase_e<br>rr[2]  | J |

|               |                 |                 |                 |                 |                 |                 |                 |                 |                 |                 |                 |                 | vddi              | phase_e<br>rr[1]  | phase_e<br>rr[0]  | rclk[3]          | vss               | к |

|               |                 |                 |                 |                 |                 |                 |                 |                 |                 |                 |                 |                 | rclk[2]           | vddi              | rclk[1]           | rclk[0]          | vss               | L |

|               |                 |                 |                 |                 |                 |                 |                 |                 |                 |                 |                 |                 | tclk[3]           | tclk[2]           | tclk[1]           | vddi             | tclk[0]           | М |

|               |                 |                 |                 |                 |                 |                 |                 |                 |                 |                 |                 |                 | salm[3]           | salm[2]           | vddi              | salm[1]          | VSS               | N |

|               |                 |                 |                 |                 |                 |                 |                 |                 |                 |                 |                 |                 | vddo              | salm[0]           | tck               | tms              | vss               | Ρ |

|               |                 |                 |                 |                 |                 |                 |                 |                 |                 |                 |                 |                 | tdi               | tdo               | vddi              | trstb            | vss               | R |

|               |                 |                 |                 |                 |                 |                 |                 |                 |                 |                 |                 |                 | NC                | VSS               | vddi              | lcruto[<br>3]    | vss               | т |

|               |                 |                 |                 |                 |                 |                 |                 |                 |                 |                 |                 |                 | vddo              | vddo              | vddo              | vddo             | vddo              | U |

|               |                 |                 |                 |                 |                 |                 |                 |                 |                 |                 |                 |                 |                   |                   |                   |                  |                   | J |

|     | Та    | ble 6        | CRSL           | J 4x24 | 488 Bo         | ottom   | Righ          | t Corr  | ner Pi  | n-Out          |                |        |                           |                           |                           |        |         |    |

|-----|-------|--------------|----------------|--------|----------------|---------|---------------|---------|---------|----------------|----------------|--------|---------------------------|---------------------------|---------------------------|--------|---------|----|

|     |       |              |                |        |                |         |               |         |         |                |                |        | avdl_3                    | avdl_3                    | avdl_3                    | avdl_3 | avdl_3  | v  |

|     |       |              |                |        |                |         |               |         |         |                |                |        | avdh_cs<br>u_3            | avdh_cs<br>u_3            | refclk[<br>3]-            | vss    | vss     | w  |

|     |       |              |                |        |                |         |               |         |         |                |                |        | avdh_cs<br>u_3            | avdh_cs<br>u_3            | refclk[<br>3]+            | vss    | vss     | Y  |

|     |       |              |                |        |                |         |               |         |         |                |                |        | avdl_3                    | vss                       | vss                       | vss    | txd[3]+ | АА |

|     |       |              |                |        |                |         |               |         |         |                |                |        | avdl_3                    | vss                       | vss                       | vss    | txd[3]- | АВ |