# **DATA SHEET LXT359** Integrated T1 LH/SH Transceiver for DS1/DSX-1/CSU or NTU/ISDN PRI Applications

## **General Description**

The LXT359 is a T1 Primary rate, combination transceiver for T1 long and short-haul applications. It operates over (22 AWG) twisted-pair cable for 0 to 6 kft and offers Line Build-Outs and pulse equalization settings for all T1 applications including D4 Channel bank.

The LXT359 provides both a serial port for microprocessor control and a hardware control mode for stand alone operation. It incorporates crystal-less digital jitter attenuation in either the transmit or receive data path starting at 3 Hz. B8ZS encoding/decoding and unipolar or bipolar data I/O are available. It provides loss of signal monitoring and a variety of diagnostic loopback modes.

The LXT359 uses an advanced double-poly, double-metal fabrication process and requires only a single 5-volt power supply.

## Applications

- HDSL access systems

- ISDN Primary Rate Interface (ISDN PRI)

- CSU interface to T1 service

- T1 LAN/WAN bridge/routers

- D4 Channel bank and newer generation DLC

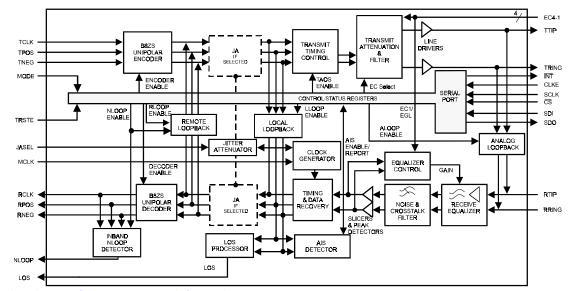

## LXT359 Block Diagram

## Features

• Fully integrated transceiver for Long or Short-Haul T1 interfaces

**JUNE 1999**

Revision 2.1

- Crystal-less digital jitter attenuation

- Select either transmit or receive path

- No crystal or high speed external clock required

- Meet or exceed specifications in ANSI T1.403 and T1.408; ITU I.431, T1.102 and AT&T Pub 62411

- Selectable receiver sensitivity fully restores the received signal after transmission through a cable with attenuation of either 0 to 26 dB, or 0 to 36 dB @ 772 kHz

- Five Pulse Equalization Settings for T1 short-haul applications (DSX-1)

- 6V output signal for D4 Channel bank

- Four Line Build-Outs for T1 long-haul applications from 0 dB to -22.5 dB

- LOS processor per ANSI T1.231

- Selectable unipolar or bipolar data I/O and B8ZS encoding/decoding

- Local, remote, analog and inband network loopback generation and detection

- Serial-interface for microprocessor control

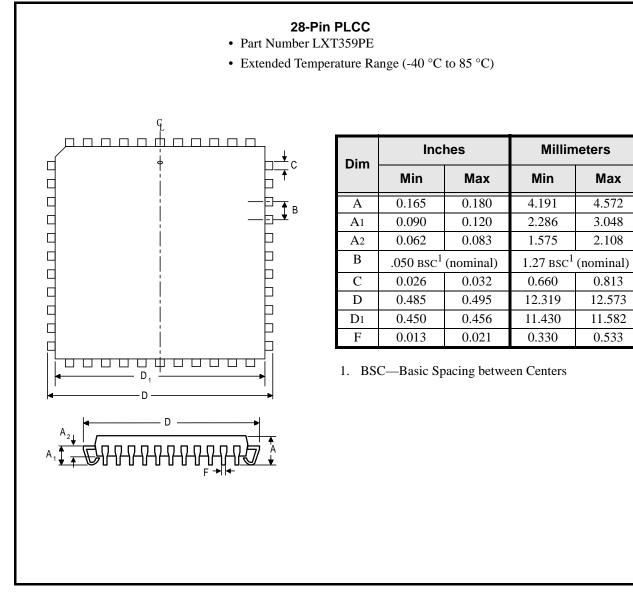

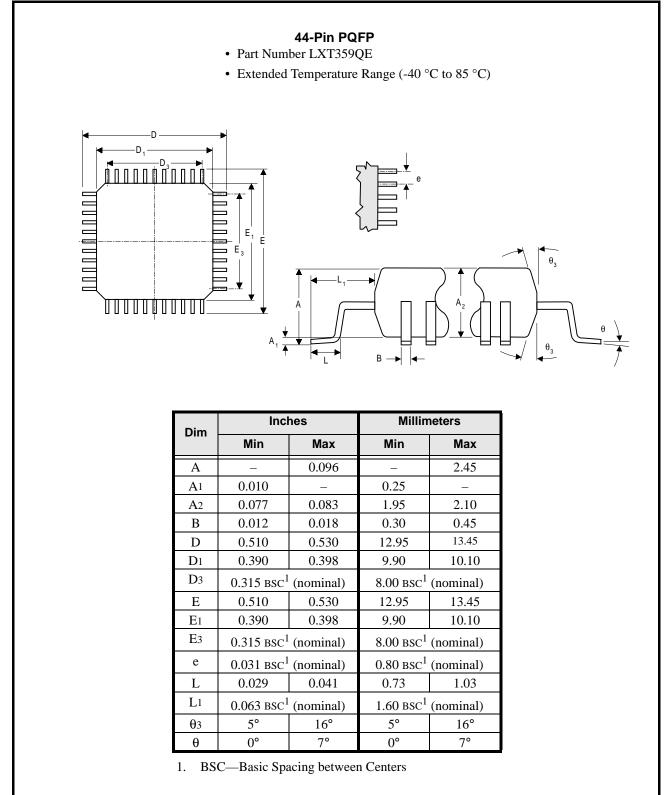

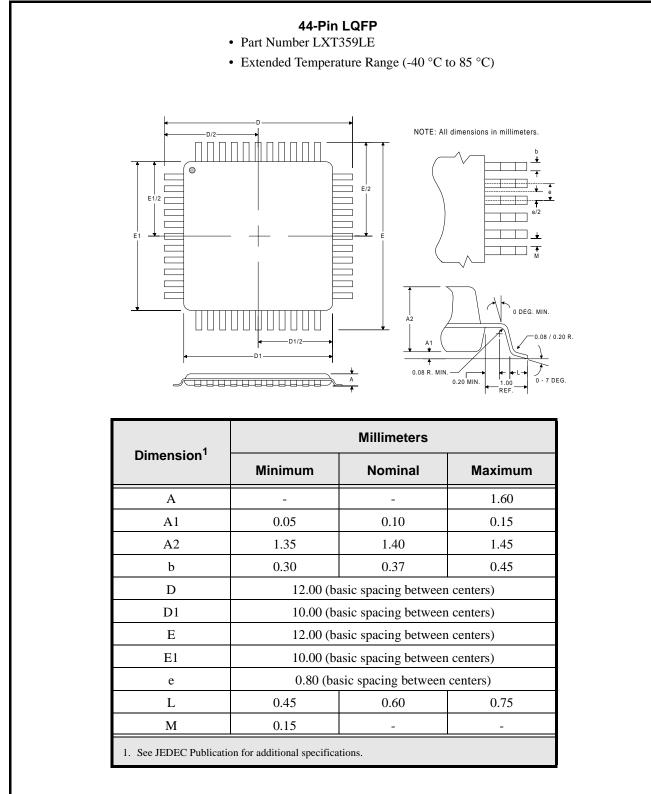

- Available in 28-pin PLCC, 44-pin PQFP and 44-pin LQFP packages

Refer to www.level1.com for most current information.

an Intel company

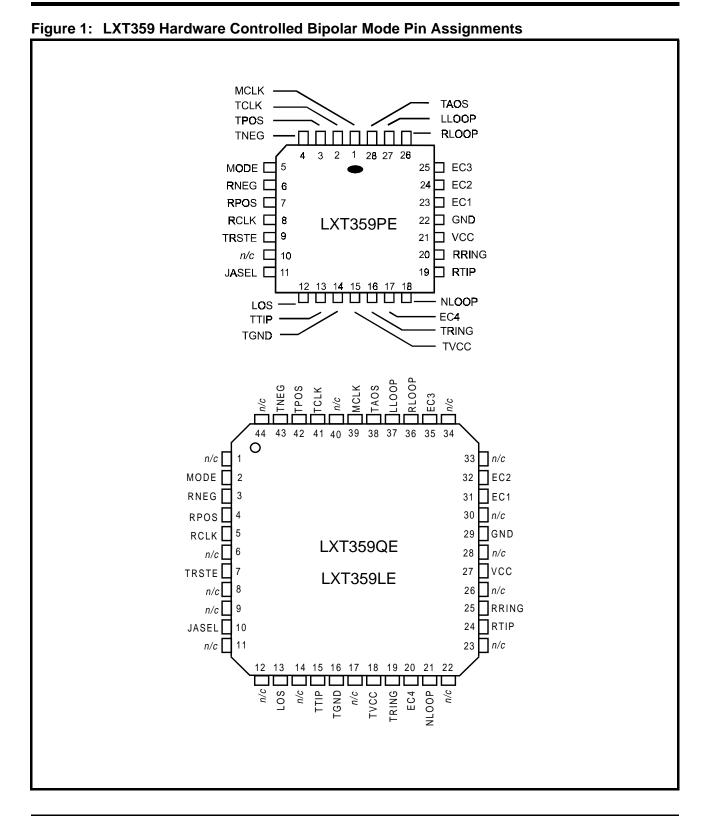

# PIN ASSIGNMENTS AND SIGNAL DESCRIPTIONS

| Pir        | n #          | Pinelor                                                                                                                                    | Bipolar Uninolar |      | n # | Dinelor | Unipolar |  |  |  |  |

|------------|--------------|--------------------------------------------------------------------------------------------------------------------------------------------|------------------|------|-----|---------|----------|--|--|--|--|

| PLCC       | QFP          | Bipolar                                                                                                                                    | Unipolar         | PLCC | QFP | Bipolar | Unipolar |  |  |  |  |

| 1          | 39           | MC                                                                                                                                         | LK               | 13   | 15  | TT      | IP       |  |  |  |  |

| 2          | 41           | TCI                                                                                                                                        | LK               | 14   | 16  | TGI     | ND       |  |  |  |  |

| 3          | 42           | TPOS                                                                                                                                       | TDATA            | 15   | 18  | TVCC    |          |  |  |  |  |

| 4          | 43           | TNEG                                                                                                                                       | INSBPV           | 16   | 19  | TRI     | NG       |  |  |  |  |

| 6          | 3            | RNEG                                                                                                                                       | BPV              | 19   | 24  | RTIP    |          |  |  |  |  |

| 7          | 4            | RPOS                                                                                                                                       | RDATA            | 20   | 25  | RRI     | NG       |  |  |  |  |

| 8          | 5            | RC                                                                                                                                         | LK               | 21   | 27  | VC      | C        |  |  |  |  |

|            | 22 29 GND    |                                                                                                                                            |                  |      |     |         |          |  |  |  |  |

| 1. Data pi | ins change b | 1. Data pins change based on whether external or internal QRSS mode is active. Clock pins remain the same in both Hardware and Host modes. |                  |      |     |         |          |  |  |  |  |

Table 1: LXT359 Clock and Data Pins by Mode<sup>1</sup>

## Table 2: LXT359 Control Pins by Mode

| Pir  | า # | Hardware<br>Modes    | Host Modes           | Pin # |     | Hardw<br>Mode  |  | Host Modes               |  |     |

|------|-----|----------------------|----------------------|-------|-----|----------------|--|--------------------------|--|-----|

| PLCC | QFP | Unipolar/<br>Bipolar | Unipolar/<br>Bipolar | PLCC  | QFP | Unipo<br>Bipol |  | Unipolar/<br>Bipolar     |  |     |

| 5    | 2   | MODE                 | MODE                 | 25    | 35  | EC3            |  | EC3                      |  | SDO |

| 9    | 7   | TRSTE                | TRSTE                | 17    | 20  | EC4            |  | Low                      |  |     |

| 11   | 10  | JASEL                | Low                  | 18    | 21  | NLOOP          |  | NLOOP                    |  |     |

| 12   | 13  | LOS                  | LOS                  | 26    | 36  | RLOOP          |  | $\overline{\mathrm{CS}}$ |  |     |

| 23   | 31  | EC1                  | ĪNT                  | 27    | 37  | LLOOP          |  | SCLK                     |  |     |

| 24   | 32  | EC2                  | SDI                  | 28    | 38  | TAOS           |  | CLKE                     |  |     |

| Pin    | n #             | Symbol       | I/O <sup>2</sup> | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|--------|-----------------|--------------|------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| PLCC   | QFP             | Symbol       | 1/0-             | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| $1^1$  | 39 <sup>1</sup> | MCLK         | DI               | <b>Master Clock</b> . Connect to 1.544 MHz. MCLK input requires an external, independent clock signal to generate internal clocks. Required accuracy is better than $\pm$ 50 ppm with a typical duty cycle of 50%. Upon Loss of Signal (LOS), RCLK is derived from MCLK.                                                                                                                                                                                                                                                                                 |

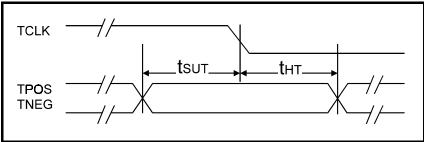

| $2^1$  | 41 <sup>1</sup> | TCLK         | DI               | <b>Transmit Clock</b> . 1.544 MHz input. Transceiver samples TPOS and TNEG on the falling edge of TCLK                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| 3<br>4 | 42<br>43        | TPOS<br>TNEG | DI               | <b>Transmit Data – Positive and Negative</b> . In the Bipolar I/O mode, these pins are the positive and negative sides of a bipolar input pair. Data to be transmitted onto the twisted-pair line is input at these pins. Table 4 describes Unipolar Mode functions.                                                                                                                                                                                                                                                                                     |

| 51     | 2               | MODE         | DI               | <ul> <li>Mode Select. Connecting MODE Low puts the LXT359 in the Hardware Mode. In Hardware Mode, the serial interface is disabled and hardwired pins are used to control configuration and report status.</li> <li>Connecting MODE to Midrange<sup>3</sup> activates the Hardware Mode and enables the B8ZS encoder/decoder and Unipolar Mode.</li> <li>Connecting MODE High puts the LXT359 in the Host Mode. In the Host Mode, the serial interface controls the LXT359 and displays its status.</li> </ul>                                           |

| 6<br>7 | 3<br>4          | RNEG<br>RPOS | DO               | Receive Data – Negative and Positive. In the Bipolar I/O mode, these pins<br>are the positive and negative sides of a bipolar output pair. Data recovered<br>from the line interface is output on these pins. A signal on RNEG corresponds<br>to receipt of a negative pulse on RTIP/RRING. A signal on RPOS corre-<br>sponds to receipt of a positive pulse on RTIP/RRING.<br>RNEG/RPOS outputs are Non-Return-to-Zero. Both outputs are stable and<br>valid on the rising edge of RCLK. Refer to Table 4 for Unipolar Mode func-<br>tion descriptions. |

| 8      | 5               | RCLK         | DO               | <b>Recovered Clock</b> . The clock recovered from the line input signal is output on this pin. Under LOS conditions there is a smooth transition from the RCLK signal (derived from the recovered data) to the MCLK signal at the RCLK output.                                                                                                                                                                                                                                                                                                           |

| 9      | 7               | TRSTE        | DI               | <ul> <li>Tristate. Connecting TRSTE High forces all output pins to a high impedance state.</li> <li>Connecting TRSTE Low sets LXT359 to the Hardware Bipolar Mode.</li> <li>Connecting TRSTE to Midrange<sup>3</sup> enables the Unipolar Mode. (See Table 4 for Unipolar function descriptions.)</li> </ul>                                                                                                                                                                                                                                             |

| 10     | _               | n/c          | -                | No connection. Leave this pin floating.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

## Table 3: LXT359 Hardware Controlled Bipolar Mode Signal Descriptions

1. These pins do not change function as the operating mode changes. Tables 4 and 5 do not describe these pins.

2. I/O column entries: DI = Digital Input; DO = Digital Output; DI/O = Digital Input/Output; AI = Analog Input; AO = Analog Output.

3. Midrange is a voltage level such that 2.3 V  $\leq$  Midrange  $\leq$  2.7 V or the pin may float.

4. Pins 1, 6, 8, 9, 11, 12, 14, 17, 22, 23, 26, 28, 30, 33, 34, 40, and 44 are not connected (*n/c*).

| Pir             | n #             | Symbol | uo <sup>2</sup>  | Description                                                                                                                                                                                                                                                                                |  |  |

|-----------------|-----------------|--------|------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| PLCC            | QFP             | Symbol | I/O <sup>2</sup> | Description                                                                                                                                                                                                                                                                                |  |  |

|                 |                 |        |                  | Jitter Attenuation Select. Selects jitter attenuation location.                                                                                                                                                                                                                            |  |  |

| 11              | 10              | JASEL  | DI               | Connecting JASEL High activates the jitter attenuator in the receive path.<br>Connecting JASEL Low activates the jitter attenuator in the transmit path.                                                                                                                                   |  |  |

|                 |                 |        |                  | Connecting JASEL to Midrange <sup>3</sup> disables jitter attenuation.                                                                                                                                                                                                                     |  |  |

| 12              | 13              | LOS    | DO               | <b>Loss of Signal Indicator</b> . LOS goes High on receipt of 175 consecutive spaces and returns Low when the received signal reaches a mark density of 12.5% (determined by receipt of 16 marks within a sliding window of 128 bits with fewer than 100 consecutive zeros).               |  |  |

|                 |                 |        |                  | The transceiver outputs received marks on RPOS and RNEG even when LOS is High.                                                                                                                                                                                                             |  |  |

| 13 <sup>1</sup> | 15 <sup>1</sup> | TTIP   | AO               | <b>Transmit Tip and Ring</b> . Differential Driver Outputs. These outputs are designed to drive a 50 - 200 $\Omega$ load. The transformer and line matching resis-                                                                                                                         |  |  |

| 16 <sup>1</sup> | 19 <sup>1</sup> | TRING  | AO               | tors should be selected to give the desired pulse height and return loss perf<br>mance.                                                                                                                                                                                                    |  |  |

| $14^{1}$        | 16 <sup>1</sup> | TGND   |                  | Ground return for the transmit drivers power supply TVCC.                                                                                                                                                                                                                                  |  |  |

| 15 <sup>1</sup> | 18 <sup>1</sup> | TVCC   | DI               | +5 VDC Power Supply input for the transmit drivers. TVCC must not vary from VCC by more than $\pm 0.3$ V.                                                                                                                                                                                  |  |  |

| 17              | 20              | EC4    | DI               | <b>Equalization Control 4</b> . Used along with EC3-1 pins for Pulse Equalization and LBO settings.                                                                                                                                                                                        |  |  |

|                 |                 |        |                  | Network Loopback Detection. If the LXT359 is configured to detect Net-                                                                                                                                                                                                                     |  |  |

| 18 <sup>1</sup> | 21 <sup>1</sup> | NLOOP  | DO               | work Loopback (NLOOP) (by connecting the RLOOP pin to Midrange <sup>3</sup> ), this pin goes High when an Inband Network Loopback has been activated by the reception of a 00001 pattern for five seconds. NLOOP is reset by reception of 001 for five seconds, or by activation of RLOOP. |  |  |

| 19 <sup>1</sup> | 24 <sup>1</sup> | RTIP   | AI               | <b>Receive Tip and Ring</b> . The AMI signal received from the line is applied at these pins. A 1:1 transformer is required. Data and clock from the signal                                                                                                                                |  |  |

| $20^{1}$        | 25 <sup>1</sup> | RRING  | AI               | applied at these pins are recovered and output on the RPOS/RNEG, and RCLK pins.                                                                                                                                                                                                            |  |  |

| 21 <sup>1</sup> | 27 <sup>1</sup> | VCC    |                  | +5 VDC Power Supply for all circuits except the transmit drivers. (Transmit drivers are supplied by TVCC.)                                                                                                                                                                                 |  |  |

| $22^{1}$        | 29 <sup>1</sup> | GND    |                  | Ground return for power supply VCC.                                                                                                                                                                                                                                                        |  |  |

| 23              | 31              | EC1    |                  | <b>Equalization Control 1-3</b> . EC1-3 (along with the EC4 pin) define the Pulse                                                                                                                                                                                                          |  |  |

| 24              | 32              | EC2    | DI               | Equalization, Line Build Outs and Equalizer Gain Limit settings. See Table 6 for additional details.                                                                                                                                                                                       |  |  |

| 25              | 35              | EC3    |                  |                                                                                                                                                                                                                                                                                            |  |  |

| 1 1             | • • •           | 1 6    | a                | ating mode changes. Tables 4 and 5 do not describe these nins                                                                                                                                                                                                                              |  |  |

## Table 3: LXT359 Hardware Controlled Bipolar Mode Signal Descriptions - continued

1. These pins do not change function as the operating mode changes. Tables 4 and 5 do not describe these pins.

2. I/O column entries: DI = Digital Input; DO = Digital Output; DI/O = Digital Input/Output; AI = Analog Input; AO = Analog Output. 3. Midrange is a voltage level such that 2.3 V  $\leq$  Midrange  $\leq$  2.7 V or the pin may float.

4. Pins 1, 6, 8, 9, 11, 12, 14, 17, 22, 23, 26, 28, 30, 33, 34, 40, and 44 are not connected (*n/c*).

| Pir      | n #           | Symbol            | I/O <sup>2</sup> | Description                                                                                                                                                                                                                                                                                                                                                                    |

|----------|---------------|-------------------|------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| PLCC     | QFP           | Symbol            | 1/0-             | Description                                                                                                                                                                                                                                                                                                                                                                    |

| 26       | 36            | RLOOP             | DI               | <b>Remote Loopback.</b> When held High, the clock and data inputs from the framer (TPOS/TNEG or TDATA) are ignored and the data received from the twisted-pair line is transmitted back onto the line at the RCLK frequency. During remote loopback, the device ignores the in-line encoders/decoders. Connecting this pin to Midrange enables Network Loopback. See Figure 6. |

| 27       | 37            | LLOOP             | DI               | <b>Local Loopback</b> . When held High, the data on TPOS and TNEG loops back digitally to RPOS and RNEG outputs (through JA if enabled). Connecting this pin to Midrange <sup>3</sup> enables Analog Loopback (TTIP and TRING are looped back to RTIP and RRING). See Figures 3, 4, and 5.                                                                                     |

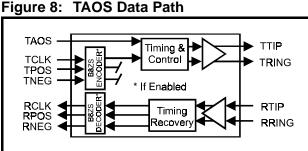

| 28       | 38            | TAOS              | DI               | <b>Transmit All Ones</b> . When held High the transmit data inputs are ignored and the LXT359 transmits a stream of 1's at the TCLK frequency. (If TCLK is not supplied, MCLK is the transmit clock reference.) TAOS is inhibited during Remote Loopback. Connecting this pin to Midrange enables QRSS pattern generation and detection. See Figure 3 and 8.                   |

| 1. These | pins do not o | change function a | s the oper       | ating mode changes. Tables 4 and 5 do not describe these pins.                                                                                                                                                                                                                                                                                                                 |

#### Table 3: LXT359 Hardware Controlled Bipolar Mode Signal Descriptions - continued

2. I/O column entries: DI = Digital Input; DO = Digital Output; DI/O = Digital Input/Output; AI = Analog Input; AO = Analog Output.

3. Midrange is a voltage level such that 2.3 V  $\leq$  Midrange  $\leq$  2.7 V or the pin may float.

4. Pins 1, 6, 8, 9, 11, 12, 14, 17, 22, 23, 26, 28, 30, 33, 34, 40, and 44 are not connected (*n/c*).

## Table 4: LXT359 Hardware Controlled Unipolar Mode Signal Assignments<sup>1</sup>

| Pir                                                                                                                                                                          | h # | Symbol                                  | I/O <sup>2</sup> | Description                                                                                                                                                                                                            |  |  |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|-----------------------------------------|------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| PLCC                                                                                                                                                                         | QFP | Symbol                                  | 1/0-             | Description                                                                                                                                                                                                            |  |  |

| 3                                                                                                                                                                            | 42  | TDATA                                   | DI               | <b>Transmit Data</b> . Unipolar input for data to be transmitted onto the twisted-pair line.                                                                                                                           |  |  |

| 4                                                                                                                                                                            | 43  | INSBPV                                  | DI               | <b>Insert Bipolar Violation</b> . This pin is sampled on the falling edge of TCLK to control Bipolar Violation Insertions in the transmit data stream. A Low-to-High transition is required to insert subsequent BPVs. |  |  |

| 6                                                                                                                                                                            | 3   | BPV                                     | DO               | <b>Bipolar Violation.</b> BPV goes High to report receipt of a bipolar violation from the line. This is an NRZ output, valid on the rising edge of RCLK.                                                               |  |  |

| 74RDATADOReceive Data.RDATA is a unipolar NRZ output of data recovered from the<br>line interface. In Hardware Mode RDATA is stable and valid on the rising<br>edge of RCLK. |     |                                         |                  |                                                                                                                                                                                                                        |  |  |

|                                                                                                                                                                              |     | oins not shown in<br>: DI = Digital Inp |                  | see Table 3.<br>Digital Output; DI/O = Digital Input/Output; AI = Analog Input; AO = Analog Output.                                                                                                                    |  |  |

| Pin        | #           | Symbol                   | I/O <sup>1</sup> | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|------------|-------------|--------------------------|------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| PLCC       | QFP         | Symbol                   | 1/0.             | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

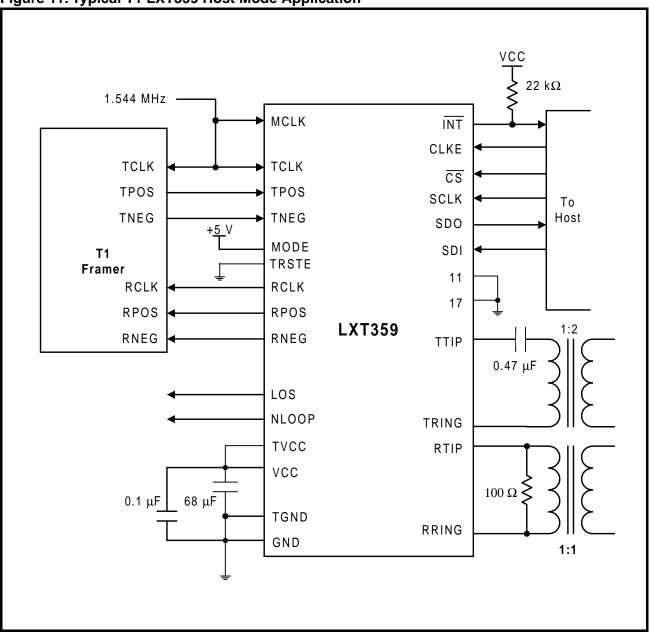

| 5          | 2           | MODE                     | DI               | <b>Mode</b> . Connecting MODE High puts the LXT359 in Host Mode. In Host Mode, the serial interface controls the LXT359 and displays its status.                                                                                                                                                                                                                                                                                                                                                                                   |

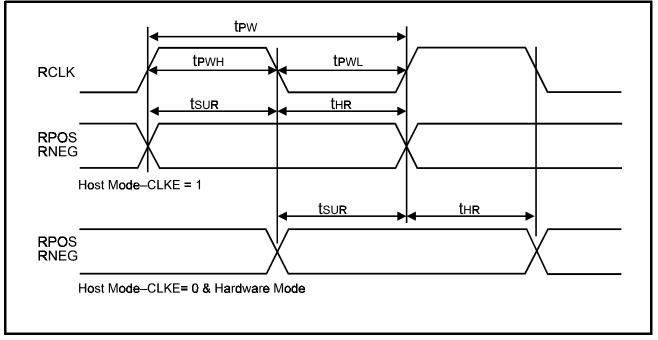

| 6<br>7     | 3 4         | RNEG<br>RPOS             | DO               | <b>Received Data–Negative and Positive</b> . In the Bipolar I/O Mode, these pins are the negative and positive sides of a bipolar output pair. The transceiver outputs the data recovered from the line interface on these pins. A signal on RNEG corresponds to receipt of a negative pulse on RTIP/RRING. A signal on RPOS corresponds to receipt of a positive signal on RTIP/RRING. RNEG/RPOS outputs are Non-Return-to-Zero (NRZ). CLKE determines the clock edge at which these outputs are stable and valid. See Figure 14. |

| 9          | 7           | TRSTE                    | DI               | <b>Tristate</b> . Connecting TRSTE High forces all output pins to high-impedance state. Connect this pin Low for normal operation.                                                                                                                                                                                                                                                                                                                                                                                                 |

| 10         | -           | n/c                      | -                | Not connected.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| 11         | 10          | n/c                      | -                | Connect Low.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| 17         | 20          | n/c                      | _                | Connect Low.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| 18         | 21          | NLOOP                    | DO               | <b>Network Loopback</b> . This pin goes High when an Inband Network Loopback has been activated.                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| 23         | 31          | INT                      | DO               | <b>Interrupt</b> (Active Low–Maskable). $\overline{INT}$ goes Low to flag the host when the LOS, NLOOP or AIS changes state. $\overline{INT}$ is an open drain output which requires a connection to power supply VCC through a resistor. Reset $\overline{INT}$ by writing a one to the respective bit in the Interrupt Clear Register.                                                                                                                                                                                           |

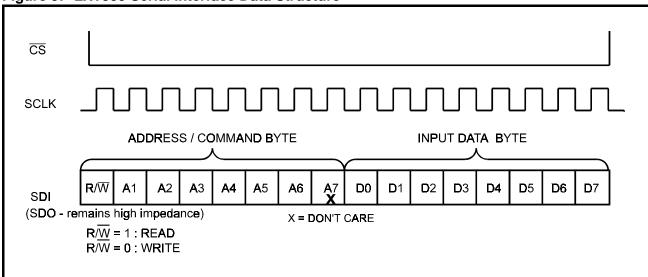

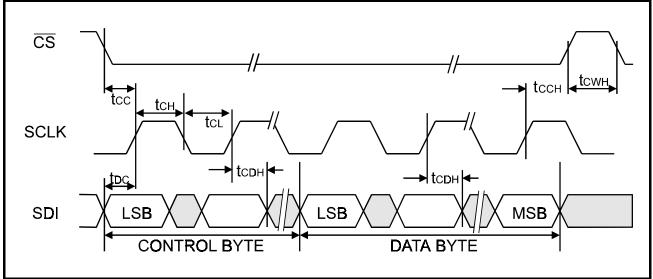

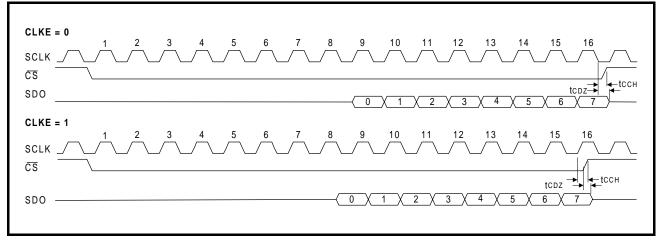

| 24         | 32          | SDI                      | DI               | <b>Serial Data Input</b> . Input port for the 16-bit serial address/command and data word. The LXT359 samples SDI on the rising edge of SCLK. See Figures 15 and 16.                                                                                                                                                                                                                                                                                                                                                               |

| 25         | 35          | SDO                      | DO               | <b>Serial Data Output</b> . If CLKE is High, SDO is valid on the rising edge of SCLK. If CLKE is Low, SDO is valid on the falling edge of SCLK. This pin goes to a high-impedance state when the serial port is being written to or when $\overline{CS}$ is High. See Figure 16.                                                                                                                                                                                                                                                   |

| 26         | 36          | $\overline{\mathrm{CS}}$ | DI               | <b>Chip Select</b> (Active Low). This input is used to access the serial interface. For each read or write operation, $\overline{CS}$ must transition from High to Low, and remain Low.                                                                                                                                                                                                                                                                                                                                            |

| 27         | 37          | SCLK                     | DI               | <b>Serial Clock</b> . This clock is used to write data to or read data from the serial interface registers. The clock frequency can be any rate up to 1.544 MHz.                                                                                                                                                                                                                                                                                                                                                                   |

| 28         | 38          | CLKE                     | DI               | <b>Clock Edge</b> . Setting CLKE High causes RPOS and RNEG to be valid on the falling edge of RCLK, with SDO valid on the rising edge of SCLK. Setting CLKE Low makes RPOS and RNEG valid on the rising edge of RCLK and SDO valid on the falling edge of SCLK.                                                                                                                                                                                                                                                                    |

| 1. I/O col | umn entries | s: DI = Digital Ir       | put; DO =        | Digital Output; DI/O = Digital Input/Output; AI = Analog Input; AO = Analog Output.                                                                                                                                                                                                                                                                                                                                                                                                                                                |

## Table 5: LXT359 Host Controlled Bipolar Mode Signal Assignments

## FUNCTIONAL DESCRIPTION

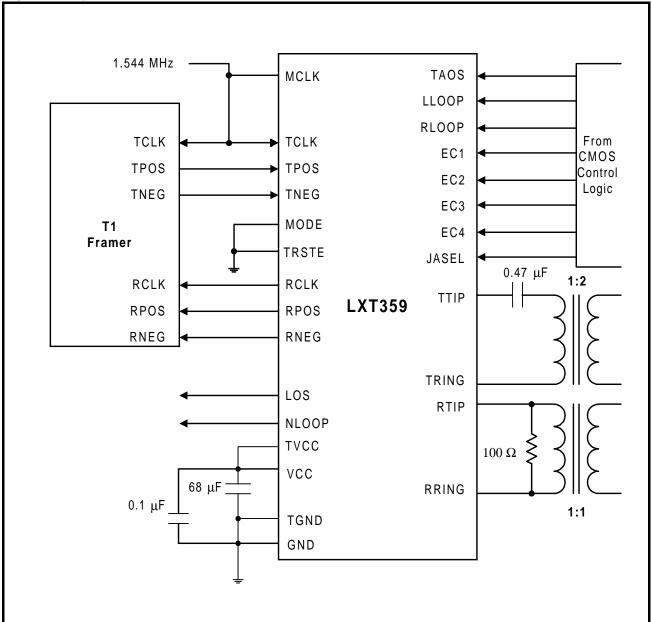

The LXT359 is a fully integrated PCM transceiver for long or short-haul, 1.544 Mbps (T1) applications allowing full-duplex transmission of digital data over existing twisted-pair installations. It interfaces with two twisted-pair lines (one pair each for transmit and receive) through standard pulse transformers and appropriate resistors.

The figure on the front page of this Data Sheet shows a block diagram of the LXT359. Control of the chip is via either a serial microprocessor port or, in Hardware Mode, via individual pin settings. It also provides a high-precision, crystal-less jitter attenuator. The user may place it in the transmit or receive path, or bypass it completely.

The transceiver meet or exceed FCC and AT&T specifications for CSU and DSX-1 applications, as well as ANSI T1, requirements.

# Initialization

During power up, the transceiver remains static until the power supply reaches approximately 3 V. On crossing this threshold, the device begins a 32 ms reset cycle to calibrate the Phase Lock Loops (PLL). The transceiver uses a reference clock to calibrate the PLL; the transmitter reference is TCLK, and the receiver reference clock is MCLK. MCLK is mandatory for chip operation and must be an independent free running jitter free reference clock.

## **Reset Operation**

Reset clears and sets all registers to 0 and resets the status and state machines for LOS and NLOOP blocks. In Hardware Mode, holding pins RLOOP, LLOOP and TAOS High for at least one clock cycle resets the device. Writing a 1 to the bit CR2.RESET commands reset in Host Mode. Allow 32 ms for the device to settle after removing all reset conditions.

# Transmitter

## **Digital Data Interface**

Input data for transmission onto the line is clocked serially into the device at the TCLK rate. TPOS and TNEG are the bipolar data inputs. TDATA accepts unipolar data. (Setting the TRSTE pin to Midrange enables Hardware Unipolar Mode.) Input data may pass through either the Jitter Attenuator or B8ZS encoder or both. Bit CR1.ENCENB = 1 enables B8ZS encoding in Host Mode. In Hardware Mode, connecting the MODE pin to Midrange selects zero suppression coding. The transmit clock (TCLK) supplies input synchronization. The Test Specifications section defines the transmit timing requirements for TCLK and the Master Clock (MCLK).

## **Output Drivers**

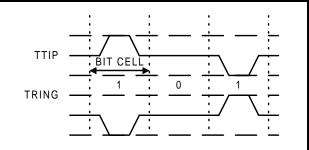

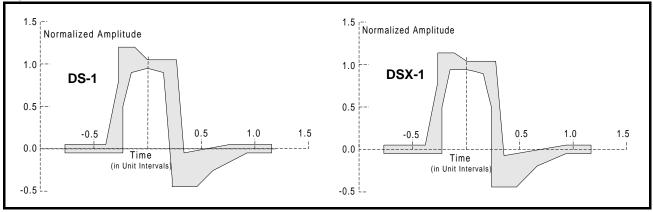

The transceivers transmit data as a 50% line code as shown in Figure 2. Activating the line driver only during a mark reduces power consumption. The output driver is disabled during transmission of a space. Biasing of the transmit DC level is on-chip.

## Idle Mode

Transmit Idle Mode is a normal operational mode (as opposed to modes) which allows multiple transceivers to be connected to a single line for redundant applications. TTIP and TRING remain in a high impedance state when TCLK is not present. Remote or Dual Loopback, TAOS or any internal transmit patterns temporarily disable the high impedance state as will detection of Network Loop Up code in the receive direction.

## **Pulse Shape**

The Equalizer Control inputs (EC4-1) determine the transmitted pulse shape as specified in Table 6. In Host Mode, the I/O port controls the ECx values. In Hardware Mode, four individual pins provide the ECx inputs.

Shaped pulses meeting various T1 specifications are applied to the AMI line driver for transmission onto the line at TTIP and TRING. The transceivers produce DSX-1 pulses for short-haul T1 applications (settings from 0 dB to +3.0 dB), D-4 channel bank pulses for short-haul T1 appli-

cations and DS1 pulses for long-haul T1 applications (settings from 0 dB to -22.5 dB). Refer to the Test Specifications section for pulse mask specifications.

# Receiver

A 1:1 transformer provides the interface to the twisted-pair line. Recovered data is output at RPOS/RNEG (RDATA in Unipolar Mode), and the recovered clock is output at RCLK. The Test Specifications section shows receiver timing.

# **Receive Equalizer**

The receive equalizer processes the signal received at RTIP and RRING. The equalizer control (ECx) input pins or register bits determine the maximum gain applied at the equalizer. With EC1 Low, up to 36 dB of gain may be applied. When EC1 is High, 26 dB is the gain limit to provide an increased noise margin in shorter loop operations.

The receiver can accurately recover signals with up to 36 dB of cable attenuation (from 2.4 V).

## **Data Recovery**

The transceiver filters the equalized signal and applies it to the peak detector and data slicers. The peak detector samples the inputs and determines the maximum value of the received signal. The data slicers are set at 50% of the peak value to ensure optimum signal-to-noise performance.

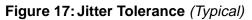

After processing through the data slicers, the received signal goes to the data and timing recovery section, then to the B8ZS decoder (if selected) and to the receive monitor. The data and timing recovery circuits provide input jitter tolerance significantly better than required by AT&T Pub 62411. See the Test Specifications section.

## **Digital Data Interface**

In either Host or Hardware Control Mode the recovered data goes to the Loss of Signal (LOS) Monitor. The jitter attenuator circuit may be enabled or disabled in the receive data path or the transmit path. Received data may be routed to the B8ZS decoder (if selected). Finally, the device may send the digital data to the framer as either unipolar or bipolar data.

When transmitting unipolar data to the framer, the device reports receiving bipolar violations by driving the BPV pin High.

# Jitter Attenuation

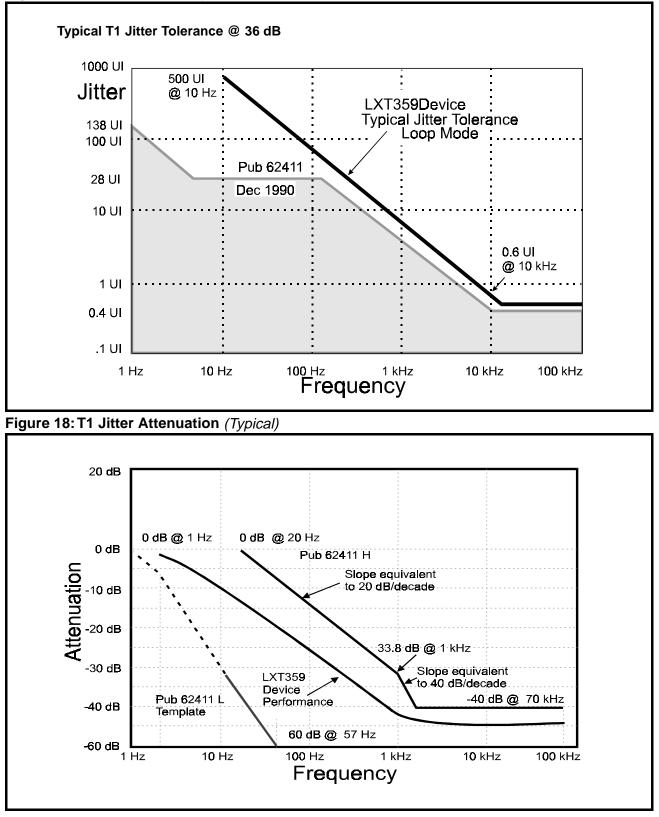

A Jitter Attenuation Loop (JAL) with an Elastic Store (ES) provides jitter attenuation as shown in the Test Specifications section. The JAL requires no special circuitry, such as an external quartz crystal or high-frequency clock (higher than the line rate). Its timing reference is the master clock, MCLK.

In Hardware Control Mode the ES is a 32 x 2-bit register. Setting the JASEL pin High places the JA circuitry in the received data path; setting JASEL Low places the JA in the transmit data path; tying it to Midrange disables the JA.

In Host Mode, bit CR1.JASEL0 enables or disables the JA circuit. With bit CR1.JASEL0 = 1, bit CR1.JASEL1 controls the JA circuit placement (see Table 11).

The device clocks data into the ES using either TCLK or Receiver Recovered Clock depending on whether the JA circuitry is in the transmit or receive data path, respectively. Data is shifted out of the elastic store using the dejittered clock from the JAL. When the FIFO is within two bits of overflowing or underflowing, the ES adjusts the output clock by  $1/_8$  of a bit period. The ES produces an average delay of 16 bits in the associated data path. When the Jitter Attenuator is in the receive path, the output RCLK transitions smoothly to MCLK in the event of an LOS condition.

| EC4 | EC3        | EC2 | EC1 <sup>1</sup> | Function                 | Pulse               | Cable    | Gain  | Coding <sup>2</sup> |

|-----|------------|-----|------------------|--------------------------|---------------------|----------|-------|---------------------|

| 0   | 0          | 0   | 0                | T1 Long Haul             | 0.0 dB pulse        | 100 Ω TP | 36 dB | B8ZS                |

| 0   | 0          | 1   | 0                | T1 Long Haul             | -7.5 dB pulse       | 100 Ω TP | 36 dB | B8ZS                |

| 0   | 1          | 0   | 0                | T1 Long Haul             | -15.0 dB pulse      | 100 Ω TP | 36 dB | B8ZS                |

| 0   | 1          | 1   | 0                | T1 Long Haul             | -22.5 dB pulse      | 100 Ω TP | 36 dB | B8ZS                |

| 0   | 0          | 0   | 1                | T1 Long Haul             | 0.0 dB pulse        | 100 Ω TP | 26 dB | B8ZS                |

| 0   | 0          | 1   | 1                | T1 Long Haul             | -7.5 dB pulse       | 100 Ω TP | 26 dB | B8ZS                |

| 0   | 1          | 0   | 1                | T1 Long Haul             | -15.0 dB pulse      | 100 Ω TP | 26 dB | B8ZS                |

| 0   | 1          | 1   | 1                | T1 Long Haul             | -22.5 dB pulse      | 100 Ω TP | 26 dB | B8ZS                |

| 1   | 0          | 0   | 1                | D4 Short Haul            | 6V pulse            | 100 Ω TP | 12 dB | B8ZS                |

| 1   | 0          | 1   | 1                | T1 Short Haul            | 0-133 ft / 0.6 dB   | 100 Ω TP | 12 dB | B8ZS                |

| 1   | 1          | 0   | 0                | T1 Short Haul            | 133-266 ft / 1.2 dB | 100 Ω TP | 12 dB | B8ZS                |

| 1   | 1          | 0   | 1                | T1 Short Haul            | 266-399 ft / 1.8 dB | 100 Ω TP | 12 dB | B8ZS                |

| 1   | 1          | 1   | 0                | T1 Short Haul            | 399-533 ft / 2.4 dB | 100 Ω TP | 12 dB | B8ZS                |

| 1   | 1          | 1   | 1                | T1 Short Haul            | 533-655 ft / 3.0 dB | 100 Ω TP | 12 dB | B8ZS                |

|     | 1 sets the |     | qualizer gai     | n (EGL) during T1 long-ł | aul operation.      |          |       |                     |

## Table 6: Equalizer Control Input Settings

2. When enabled.

# **Diagnostic Mode Operation**

Diagnostic modes as shown in Table 7. In Hardware Mode, the diagnostic modes are selected by a combination of pin settings. In Host Mode, the diagnostic modes are selected by writing appropriate bits in the Diagnostic Control Register.

| Diagnostia Mada                                | Availat  | Availability <sup>1</sup> |                       |  |  |

|------------------------------------------------|----------|---------------------------|-----------------------|--|--|

| Diagnostic Mode                                | Hardware | Host                      | Maskable <sup>2</sup> |  |  |

| Loopback Modes                                 |          |                           |                       |  |  |

| Local Loopback (LLOOP)                         | Yes      | Yes                       | No                    |  |  |

| Analog Loopback (ALOOP)                        | Yes      | Yes                       | No                    |  |  |

| Remote Loopback (RLOOP)                        | Yes      | Yes                       | No                    |  |  |

| In-band Network Loopback (NLOOP)               | Yes      | Yes                       | Yes                   |  |  |

| Dual Loopback (DLOOP)                          | Yes      | Yes                       | No                    |  |  |

| Internal Data Pattern Generation and Detection | n        |                           |                       |  |  |

| Transmit All Ones (TAOS)                       | Yes      | Yes                       | No                    |  |  |

| In-band Loop up/down Code Generator            | No       | Yes                       | No                    |  |  |

| Error Insertion and Detection                  | ····     |                           |                       |  |  |

| Bipolar Violation Insertion (INSBPV)           | Yes      | Yes                       | No                    |  |  |

| Bipolar Violation Detection (BPV)              | Yes      | Yes                       | No                    |  |  |

| Alarm Condition Monitoring                     |          |                           |                       |  |  |

| Receive Loss of Signal (LOS) Monitoring        | Yes      | Yes                       | Yes                   |  |  |

#### Table 7: Diagnostic Mode Availability

2. Host Control Mode allows interrupt masking by writing a "1" to the corresponding bit in the Interrupt Clear Register. Hardware Control Mode has no interrupt masking feature.

# Loopback Modes

## Local Loopback

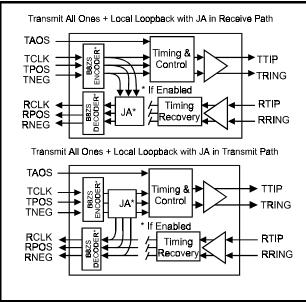

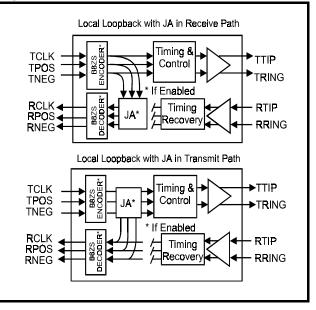

See Figures 3 and 4. In Hardware Mode, Local Loopback (LLOOP) is selected by tying LLOOP High; in Host Mode, by setting CR2.ELLOOP to 1. LLOOP inhibits the receiver circuits. The transmit clock and data inputs (TCLK and TPOS/TNEG or TDATA) loop back through the jitter attenuator (if enabled) and show up at RCLK and RPOS/RNEG or RDATA. Note that during LLOOP, the JASEL input is strictly an Enable/Disable control, i.e. it does not affect the placement of the JAL. If JA is enabled, it is active in the loopback circuit.

The transmitter circuits are unaffected by LLOOP. LXT359 transmits the TPOS/TNEG or TDATA inputs (or a stream of 1's if TAOS is asserted) normally. When used in this mode, the transceiver can function as a stand-alone jitter attenuator.

## Figure 3: TAOS with LLOOP (JA Selected)

#### Figure 4: Local Loopback (JA Selected)

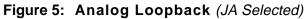

## Analog Loopback

See Figure 5. Analog Loopback (ALOOP) exercises the maximum number of functional blocks. ALOOP operation disconnects the RTIP/RRING inputs from the line and routes the transmit outputs back into the receive inputs. This tests the encoders/decoders, jitter attenuator, transmitter, receiver and timing recovery sections. In Hardware Mode, tying pin 27 to Midrange commands Analog Loopback; in Host Mode, writing a 1 to bit CR2.EALOOP enables the function. The ALOOP function overrides all other loopback modes.

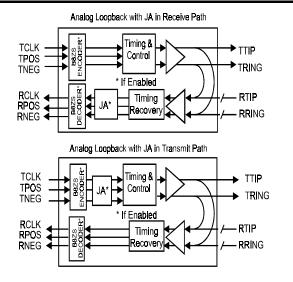

## **Remote Loopback**

See Figure 6. In Remote Loopback (RLOOP) mode, the device ignores the transmit data and clock inputs (TCLK and TPOS/TNEG or TDATA), and bypasses the in-line encoders/decoders. The RPOS/RNEG or RDATA outputs loop back through the transmit circuits to TTIP and TRING at the RCLK frequency. The RLOOP command does not affect the receiver circuits which continue to output the RCLK and RPOS/RNEG or RDATA signals received from the twisted-pair line. In Host Mode, command RLOOP by writing a 1 to bit CR2.ERLOOP. In Hardware Mode, RLOOP is commanded by setting pin 26 High.

## **Network Loopback**

Network Loopback (NLOOP) can be initiated only when the Network Loopback detect function is enabled. In Host Mode, writing a 1 to CR2.ENLOOP enables NLOOP detection. In Hardware Mode, setting RLOOP to Midrange enables Network Loopback detection.

With NLOOP detection enabled, the receiver looks for the NLOOP data patterns (00001 = enable, 001 = disable) in the input data stream. When the receiver detects an NLOOP enable data pattern repeated for a minimum of five seconds, the device enables RLOOP. The device responds to both framed and unframed NLOOP patterns. Once NLOOP detection is enabled at the chip and activated by the appropriate data pattern, it is identical to Remote Loopback (RLOOP). NLOOP is disabled by receiving the 001 pattern for five seconds, or by activating RLOOP or ALOOP, or by disabling NLOOP detection. The device goes into Dual Loopback Mode (DLOOP) in the case where it detects both the NLOOP and LLOOP functions.

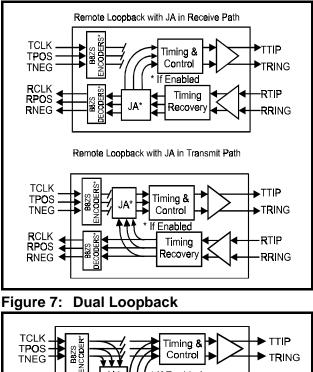

## **Dual Loopback**

See Figure 7. To select Dual Loopback (DLOOP), set both RLOOP and LLOOP High in Hardware Mode or set bits CR2.ERLOOP and CR2.ELLOOP to 1 in Host Mode. In DLOOP mode, the transmit clock and data inputs (TCLK and TPOS/TNEG or TDATA) loop back through the Jitter Attenuator (unless disabled) to RCLK and RPOS/RNEG or RDATA. The data and clock recovered from the twisted-pair line loop back through the transmit circuits to TTIP and TRING without jitter attenuation.

#### Figure 6: Remote Loopback (JA Selected)

If Enabled

Timing

Recover

RTIP

RRING

# Internal Pattern Generation and Detection

JA\*

## **Transmit All Ones**

See Figure 8. In Transmit All Ones (TAOS) Mode the transceiver ignores the TPOS and TNEG inputs and transmits a continuous stream of 1's at the TCLK frequency. (With no TCLK, the TAOS output clock is MCLK.) This can be used as the Alarm Indication Signal (AIS–also called the Blue Alarm). In Host Mode, TAOS is commanded by writing a 1 to bit CR2.ETAOS. In Hardware Mode setting pin 28 High does so. Both TAOS and Local Loopback can occur simultaneously as shown in Figure 3, but Remote Loopback inhibits TAOS. When both TAOS and LLOOP are active, TCLK and TPOS/TNEG loop back to RCLK and RPOS/RNEG through the jitter attenuator (if enabled), and an all ones pattern goes to TTIP/TRING.

# In-Band Network Loop Up or Down

## **Code Generator**

In Host Mode, LXT359 can transmit in-band Network Loop Up or Loop Down code. The Loop Up code is 00001; Loop Down code is 001. A Loop Up code transmission occurs when Control Register #2 bits EPAT0 = 1 and EPAT1 = 0. A Loop Down code transmission requires that both EPAT0 and EPAT1 = 1.

# Error Insertion and Detection

## **Bipolar Violation Insertion (INSBPV)**

In Unipolar Mode, both Hardware and Host Modes provide for Bipolar Violation Insertion (INSBPV). Choosing Unipolar Mode configures pin 4 as INSBPV. Bipolar violation insertion requires a Low-to-High transition on INSBPV. Sampling occurs on the falling edge of TCLK. When INSBPV goes High a BPV is inserted on the next available mark except in the four following situations:

- Zero suppression (B8ZS) is not violated

- If LLOOP and TAOS are both active, the BPV is looped back to RNEG/BPV indicator and the line driver transmits all ones with no violation

- BPV insertion is disabled with RLOOP (remote loopback) active

- BPV insertion is disabled with NLOOP asserted (pin 10 High)

With the LXT359 configured to transmit internally generated data patterns (QRSS or NLOOP), a BPV can be inserted on the transmit pattern independent of whether the device is in the unipolar or bipolar mode of operation.

# Alarm Condition Monitoring

## Loss of Signal (LOS)

The count increments with each received 0 and the counter resets to 0 on receipt of a 1. When the count reaches n=0s, the LOS flag goes High, and the MCLK replaces the recovered clock at the RCLK output in a smooth transition.

When the received signal has 12.5% 1's (16 marks in a sliding 128-bit period, with fewer than 100 consecutive 0s), the LOS flag returns Low and the recovered clock replaces MCLK at the RCLK output in another smooth transition.

During LOS, the device sends received data to the RPOS/ RNEG pins (or RDATA in Unipolar Mode). LXT359 reports an LOS condition on the LOS pin in Hardware Mode. In Host Mode, the LOS bit in the Performance Status Register goes High to indicate an LOS condition and will interrupt the host controller if so programmed.

# **Operating Modes**

The LXT359 operates in either Hardware or (Serial Port) Host Mode. In the Hardware Mode, individual pins control the transceiver.

The logic level at the MODE pin sets the mode of operation. In Host Mode, a microprocessor controls the device through a data interface.

## Hardware Mode Operation

The LXT359 operates in Hardware Mode when MODE is set to Midrange or Low. In Hardware Mode individual pins access and control the transceiver. The outputs (RPOS/ RNEG or RDATA) are valid on the rising edge of RCLK.

There are some advanced functions provided only in Host Mode. Interrupt ( $\overline{INT}$ ) and CLKE functions are some of the features available in Host Mode.

| Input             | to Pin <sup>1</sup> | Mode of Operation |          |          |         |                           |                            |                             |  |  |  |

|-------------------|---------------------|-------------------|----------|----------|---------|---------------------------|----------------------------|-----------------------------|--|--|--|

| Mode              | TRSTE               | Hardware          | Software | Unipolar | Bipolar | AMI<br>Encoder<br>Decoder | B8ZS<br>Encoder<br>Decoder | All<br>Outputs<br>Tristated |  |  |  |

| Low               | Low                 | On                | Off      | Off      | On      | Off <sup>3</sup>          | Off                        | No                          |  |  |  |

| Low               | High                | On                | Off      | Off      | On      | Off <sup>3</sup>          | Off                        | Yes                         |  |  |  |

| Low               | Open                | On                | Off      | On       | Off     | On                        | Off                        | No                          |  |  |  |

| High <sup>2</sup> | Low                 | Off               | On       | Х        | Х       | Х                         | Х                          | No                          |  |  |  |

| High <sup>2</sup> | High                | Off               | On       | Х        | Х       | Х                         | Х                          | Yes                         |  |  |  |

| High <sup>2</sup> | Open                | Off               | On       | Х        | Х       | Х                         | Х                          | No                          |  |  |  |

| Open              | Low                 | On                | Off      | On       | Off     | Off                       | On                         | No                          |  |  |  |

| Open              | High                | On                | Off      | On       | Off     | Off                       | On                         | Yes                         |  |  |  |

| Open              | Open                | On                | Off      | On       | Off     | Off                       | On                         | No                          |  |  |  |

#### Table 8: Control and Operational Mode Selection for LXT359 Transceiver

1. Open is either a midrange voltage or the pin is floating.

2. In Software Mode, the contents of register CR1 determine the operation mode.

3. Encoding is done externally.

## **Host Mode Operation**

The LXT359 operates in Host Mode when MODE is set High. In Host Mode a microprocessor accesses and controls the transceiver through a data port using the internal registers. The outputs (RPOS/RNEG or RDATA) are valid on the rising edge of RCLK.

The host processor/controller can completely configure the device as well as get a full diagnostic/status report through the SIO or PIO. Only the clocks and data for Bipolar Mode and BPV/Logic Error insertions for Unipolar need to be provided directly to the input pins. Similarly, the recovered clock, data, and BPV are available only at output pins. All other mode settings and diagnostic information are available through the data port.

Table 9 shows the address used by the SIO to access each register on the LXT359. Table 10 summarizes the control and status registers and labels each bit they contain. Tables 11 through 15 identify the bits in each register.

| Register           | Address <sup>1</sup> |                        |

|--------------------|----------------------|------------------------|

| Name               | Abbr                 | Serial Port<br>(A7-A1) |

| Control #1         | CR1                  | x010000                |

| Control #2         | CR2                  | x010001                |

| Interrupt Clear    | ICR                  | x010011                |

| Transition Status  | TSR                  | x010100                |

| Performance Status | PSR                  | x010101                |

| Equalizer Status   | ESR                  | x010110                |

#### Table 9: Serial Port Register Addresses

| Register |                          | Bit                                  |                                                              |                                                                                                                                                   |                                                                                                                                                                                                                                   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                                                                                                                                                                                                                                                                                           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |  |

|----------|--------------------------|--------------------------------------|--------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|