### **Preliminary Data Sheet**

### **Product Features**

- Complies fully with Revision 2.0 of the *PCI Local Bus Specification*.

- Supports two 32-bit PCI buses

- Provides maximum clock frequency of 33 megahertz

- Provides concurrent primary and secondary bus operation

- Conditionally forwards the following transactions:

- Memory read and write transactions in either direction

- —I/O read and write transactions in either direction

- Configuration read and write transactions in the downstream direction

- Configuration write transactions to special cycles in either direction

- Supports memory transaction filtering through two programmable memory address regions-one prefetchable and one non-prefetchable

- Supports read prefetching for memory read transactions

- Provides up to eight dwords (32 bytes) of write posting for memory write transactions

- Provides I/O transaction filtering through one programmable memory I/O address region

- Provides ISA-mode for I/O transaction filtering

- Provides two programmable video graphics adapter (VGA) bits that support forwarding of VGA memory and I/O addresses, or forwarding of VGA palette I/O writes

- Provides master latency timers and target wait timers, for each PCI interface, which limit the amount of latency on either bus

- Provides concurrent resource lock operation

- Propagates locks across the 21050

- Provides seven secondary PCI bus clock outputs

- Enables the following central functions through s\_cfn\_l input pin for secondary bus:

- Programmable rotating arbitration function supporting up to six secondary bus masters

- —Secondary PCI bus parking at the 21050

- Provides pins for buffer empty status and write posting control

- Supports perr and serr signals with error checking functionality

.Notice: This document contains preliminary information on new products in production. The specifications are subject to change without notice. Verify with your local Intel sales office that you have the latest datasheet before finalizing a design.

Order Number: 278139-001 September 1998

Information in this document is provided in connection with Intel products. No license, express or implied, by estoppel or otherwise, to any intellectual property rights is granted by this document. Except as provided in Intel's Terms and Conditions of Sale for such products, Intel assumes no liability whatsoever, and Intel disclaims any express or implied warranty, relating to sale and/or use of Intel products including liability or warranties relating to fitness for a particular purpose, merchantability, or infringement of any patent, copyright or other intellectual property right. Intel products are not intended for use in medical, life saving, or life sustaining applications.

Intel may make changes to specifications and product descriptions at any time, without notice.

Designers must not rely on the absence or characteristics of any features or instructions marked "reserved" or "undefined." Intel reserves these for future definition and shall have no responsibility whatsoever for conflicts or incompatibilities arising from future changes to them.

The 21050 PCI-to-PCI Bridge may contain design defects or errors known as errata which may cause the product to deviate from published specifications. Current characterized errata are available on request.

Contact your local Intel sales office or your distributor to obtain the latest specifications and before placing your product order.

Copies of documents which have an ordering number and are referenced in this document, or other Intel literature may be obtained by calling 1-800-548-4725 or by visiting Intel's website at http://www.intel.com.

Copyright © Intel Corporation, 1998

\*Third-party brands and names are the property of their respective owners.

| 1.0 | Introdu           | uction   |                    |                                                                                             | 1    |

|-----|-------------------|----------|--------------------|---------------------------------------------------------------------------------------------|------|

|     | 1.1<br>1.2<br>1.3 | Audier   | nce                | ation                                                                                       | 1    |

|     | 1.4               |          | -                  | ion                                                                                         |      |

|     | 1.5               | Archite  | ecture Ove         | rview                                                                                       | 4    |

| 2.0 | 21050             | Pin Ass  | ignment            |                                                                                             | 5    |

|     | 2.1               | Signal   | Types              |                                                                                             | 6    |

|     | 2.2               |          |                    | Pin Assignment List                                                                         |      |

|     | 2.3               | Numer    | ric 21050 F        | Pin Assignment List                                                                         | 9    |

| 3.0 | Signal            | Descrip  | tion               |                                                                                             | . 13 |

|     | 3.1               | Primar   | v PCI Bus          | Signals                                                                                     | . 14 |

|     | 3.2               |          |                    | Bus Signals                                                                                 |      |

|     | 3.3               |          | •                  | Arbiter Signals                                                                             |      |

|     | 3.4               |          | •                  | d Miscellaneous Signals                                                                     |      |

| 4.0 | Function          | onal Des | scription          |                                                                                             | . 19 |

|     | 4.1               | PCI Bu   | us Interfac        | es                                                                                          | . 19 |

|     | 4.2               | Primar   | y PCI Bus          | Interface                                                                                   | . 19 |

|     |                   | 4.2.1    | Seconda            | ary PCI Bus Interface                                                                       | . 19 |

|     | 4.3               | PCI Ad   |                    | ase                                                                                         |      |

|     |                   | 4.3.1    | Linear In          | crement Address Mode                                                                        | . 20 |

|     |                   | 4.3.2    | Address            | and Data Stepping                                                                           | . 20 |

|     |                   | 4.3.3    |                    | dressing                                                                                    |      |

|     | 4.4               |          |                    | evsel) Generation                                                                           |      |

|     | 4.5               | Transa   |                    | varding                                                                                     |      |

|     |                   | 4.5.1    |                    | tion Support                                                                                |      |

|     |                   | 4.5.2    | Data Pat           | th                                                                                          | . 23 |

|     |                   | 4.5.3    | Write Tra          | ansactions                                                                                  | . 23 |

|     |                   |          | 4.5.3.1            | Non-Posted Write Transactions                                                               |      |

|     |                   |          | 4.5.3.2            | Use of Non-Posted Write Transactions                                                        |      |

|     |                   |          | 4.5.3.3            | Posted Write Transactions                                                                   |      |

|     |                   |          | 4.5.3.4            | Use of Posted Write Transactions                                                            |      |

|     |                   |          | 4.5.3.5            | Write Boundaries                                                                            |      |

|     |                   |          | 4.5.3.6            | Conversion of Memory Write and Invalidate Transactions Fast Back-to-Back Write Transactions |      |

|     |                   | 4.5.4    | 4.5.3.7<br>Pood Tr | ansactions                                                                                  |      |

|     |                   | 4.5.4    | 4.5.4.1            | Non-Prefetchable Reads                                                                      | _    |

|     |                   |          | 4.5.4.2            | The Use of Non-Prefetchable Reads                                                           |      |

|     |                   |          | 4.5.4.3            | Prefetchable Reads                                                                          |      |

|     |                   |          | 4.5.4.4            | The Use of Prefetchable Reads                                                               |      |

|     |                   |          | 4.5.4.5            | Read Boundaries                                                                             |      |

|     |                   | 4.5.5    | Configur           | ation Transactions                                                                          | . 34 |

|     |                   |          | 4.5.5.1            | Type 0 Configuration Transactions                                                           |      |

|     |                   |          | 4.5.5.2            | Type 1 Configuration Transactions                                                           |      |

|     |                   |          | 4.5.5.3            | Type 1 to Type 0 Conversion                                                                 |      |

|      |        | 4.5.5.4 Type 1 to Type 1 Forwarding                       |    |

|------|--------|-----------------------------------------------------------|----|

|      | 4.5.6  | Special Cycles                                            |    |

|      | 4.5.7  | Interrupt Acknowledge                                     |    |

| 4.6  |        | ction Termination                                         |    |

| 4.0  | 4.6.1  | Initiator Termination                                     |    |

|      | 4.0.1  | 4.6.1.1 21050 as Target                                   |    |

|      |        | 4.6.1.2 21050 as Target                                   |    |

|      | 4.6.2  | Target Termination                                        |    |

|      | 7.0.2  | 4.6.2.1 Target Termination Initiated by Target            |    |

|      |        | 4.6.2.2 Target Termination Initiated by 21050             |    |

| 4.7  | Addres | s Decoding                                                |    |

|      | 4.7.1  | Memory Address Decoding                                   |    |

|      |        | 4.7.1.1 Memory Transaction Forwarding Based on Address    | 00 |

|      |        | Ranges                                                    | 50 |

|      |        | 4.7.1.2 Disabling a Memory Address Range                  |    |

|      |        | 4.7.1.3 VGA Frame Buffer Support                          |    |

|      |        | 4.7.1.4 Dual Transaction Addressing                       |    |

|      | 4.7.2  | I/O Address Decoding                                      | 51 |

|      |        | 4.7.2.1 I/O Transaction Forwarding Based on Address Range |    |

|      |        | 4.7.2.2 Disabling the I/O Address Range                   | 51 |

|      |        | 4.7.2.3 ISA Mode                                          |    |

|      | 4.7.3  | VGA I/O Support                                           |    |

|      |        | 4.7.3.1 VGA Mode                                          |    |

|      |        | 4.7.3.2 VGA Palette Snooping                              |    |

| 4.8  |        | y                                                         |    |

|      | 4.8.1  | Master Latency Timer                                      |    |

|      | 4.8.2  | Target Wait Timer                                         |    |

|      | 4.8.3  | Burst Limit Counter                                       |    |

| 4.9  | Deadlo | ck Avoidance                                              |    |

|      | 4.9.1  | Read Operations                                           |    |

|      | 4.9.2  | Posted Write Operations                                   |    |

|      | 4.9.3  | Non-Posted Write Operations                               |    |

| 4.10 | Data S | ynchronization                                            | 56 |

| 4.11 |        | ve Access                                                 |    |

|      |        | Acquiring Exclusive Access                                |    |

|      |        | Maintaining Exclusive Access                              |    |

|      |        | Ending Exclusive Access                                   |    |

|      | 4.11.4 | 21050 as a Locked Target                                  | 61 |

| 4.12 |        | andling                                                   |    |

|      | 4.12.1 | Address Parity Errors                                     | 62 |

|      |        | Data Parity Errors on Initiator Bus                       |    |

|      | 4.12.3 | Data Parity Errors on Target Bus                          | 63 |

|      | 4.12.4 | Other Errors                                              | 64 |

| 4.13 | PCI Bu | s Arbitration                                             | 65 |

|      | 4.13.1 | Primary PCI Bus Arbitration                               | 65 |

|      | 4.13.2 | Secondary PCI Bus Arbitration                             | 65 |

|      |        | 4.13.2.1 Secondary Bus Arbiter Protocol                   | 66 |

|      |        | 4.13.2.2 Priority Schemes                                 |    |

|      |        | 4.13.2.3 Request Mask Timer                               |    |

|      |        | 4.13.2.4 Secondary Bus Arbiter Disabled                   | 67 |

|                |        |             | 4.13.2.5 Secondary Bus Parking                                                      | . 67 |

|----------------|--------|-------------|-------------------------------------------------------------------------------------|------|

|                | 4.14   |             |                                                                                     |      |

|                | 4.15   |             |                                                                                     |      |

|                |        |             | Primary Reset                                                                       |      |

|                |        |             | Secondary Reset                                                                     |      |

|                |        |             | Chip Reset                                                                          |      |

|                | 4.16   | Buffer      | Control                                                                             | . 69 |

| 5.0            | Config | uration F   | Register Description                                                                | . 71 |

|                | 5.1    | Predef      | ined Header Space Register Description                                              | . 72 |

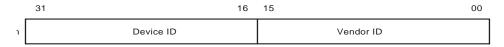

|                |        | 5.1.1       | Device ID and Vendor ID Register                                                    |      |

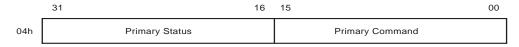

|                |        | 5.1.2       | Primary Status and Primary Command Register                                         | . 72 |

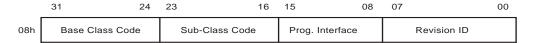

|                |        | 5.1.3       | Class Code/Programming Interface/Revision ID Register                               |      |

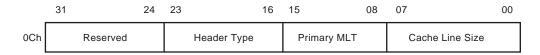

|                |        | 5.1.4       | Primary Master Latency Timer/Cache Line Size/Header Type                            | . 74 |

|                |        | 5.1.5       | Reserved Registers (10-14 Hex)                                                      | . 74 |

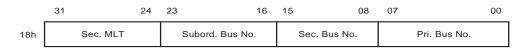

|                |        | 5.1.6       | Primary Bus Number/Secondary Bus Number/Subordinate Bus                             |      |

|                |        |             | Number/Secondary Master Latency Timer Register                                      |      |

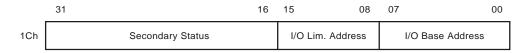

|                |        | 5.1.7       | I/O Base Address/I/O Limit Address/Secondary Status Register                        |      |

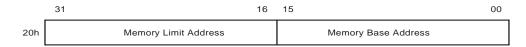

|                |        | 5.1.8       | Memory Base Address/Memory Limit Address Register                                   | . 77 |

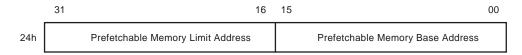

|                |        | 5.1.9       | Prefetchable Memory Base Address/Prefetchable Memory Limit                          | 70   |

|                |        | <b>5440</b> | Address Register                                                                    |      |

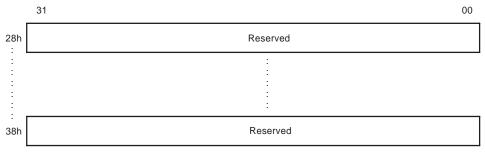

|                |        | 5.1.10      | Reserved Registers (28-38 Hex)                                                      |      |

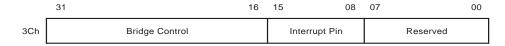

|                | 5.2    | 5.1.11      | Interrupt Pin/Bridge Control Registernentation-Specific 21050 Register Descriptions |      |

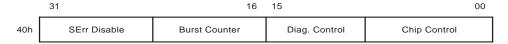

|                | 5.2    | 5.2.1       | Chip Control/Diagnostic Control/Burst Limit Counter/serr Disable                    | . 00 |

|                |        | J.Z. I      | Register                                                                            | 80   |

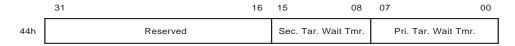

|                |        | 5.2.2       | Primary Target Wait Timer/Secondary Target Wait Timer Register                      |      |

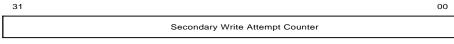

|                |        | 5.2.3       | Secondary Write Attempt Counter Register                                            |      |

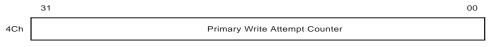

|                |        | 5.2.4       | Primary Write Attempt Counter Register                                              |      |

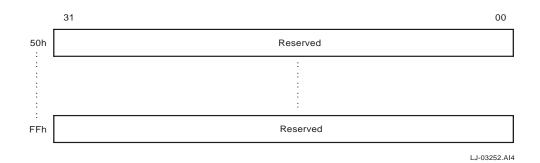

|                |        | 5.2.5       | Reserved Registers (50h-FFh)                                                        |      |

| 6.0            | Diagno | stics an    | d Test Mechanisms                                                                   | 85   |

| 0.0            | 6.1    |             | ins and Nand Tree Implementation                                                    |      |

|                | 0.1    | 6.1.1       | Diagnostic Control Register                                                         |      |

|                |        |             |                                                                                     |      |

| 7.0            | 21050  | Specific    | ations                                                                              | . 87 |

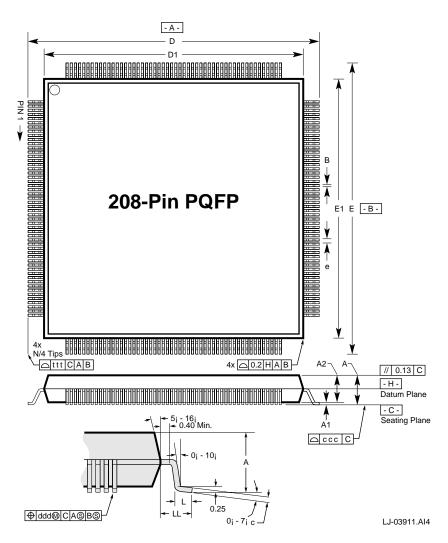

|                | 7.1    | Mecha       | nical Specifications                                                                | . 87 |

|                |        | 7.1.1       | 21050 Package                                                                       |      |

|                |        | 7.1.2       | Absolute Maximum Ratings                                                            |      |

|                | 7.2    |             | cal Specifications                                                                  |      |

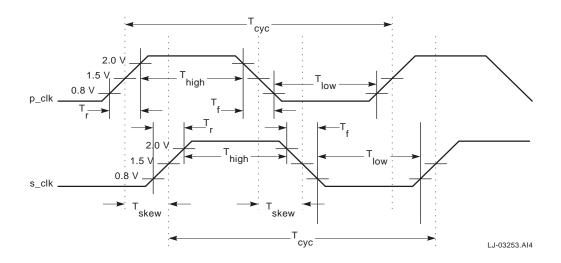

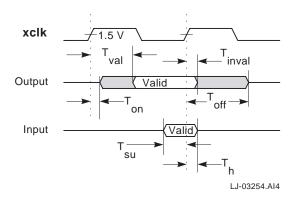

|                | 7.3    |             | ce Signal AC Electrical Specifications                                              |      |

|                |        | 7.3.1       | Interface Signal AC Timing Specifications                                           |      |

|                |        | 7.3.2       | Input Signal AC Timing Specifications                                               | . 91 |

| <b>Figures</b> |        |             |                                                                                     |      |

|                | 1-1    | 21050       | PCI-to-PCI Bridge on the System Board                                               | 2    |

|                | 1-1    |             | PCI-to-PCI Bridge with Option Cards                                                 |      |

|                | 1-3    |             | PCI-to-PCI Bridge Block Diagram                                                     |      |

|                | 2-1    |             | Pinout Diagram                                                                      |      |

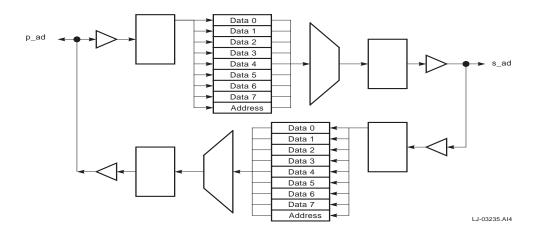

|                | 4-1    |             | Data Path                                                                           |      |

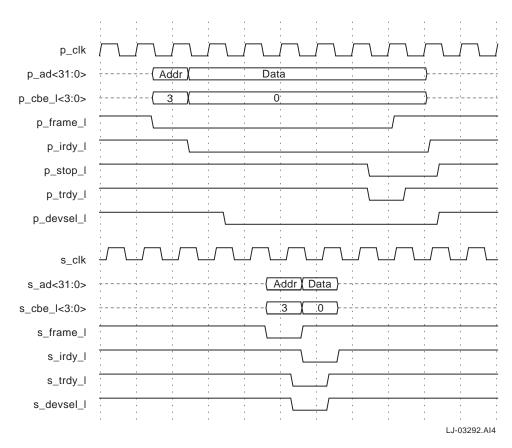

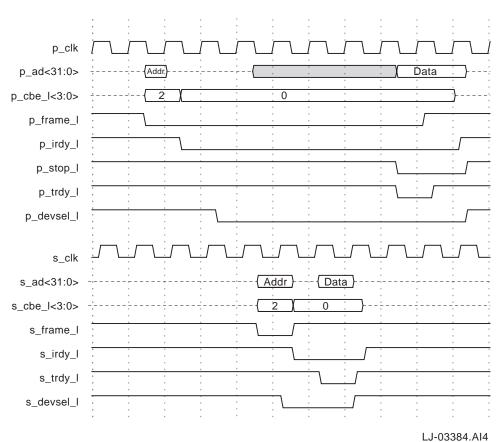

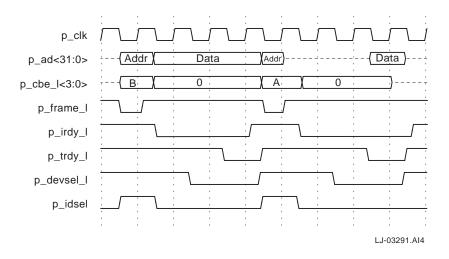

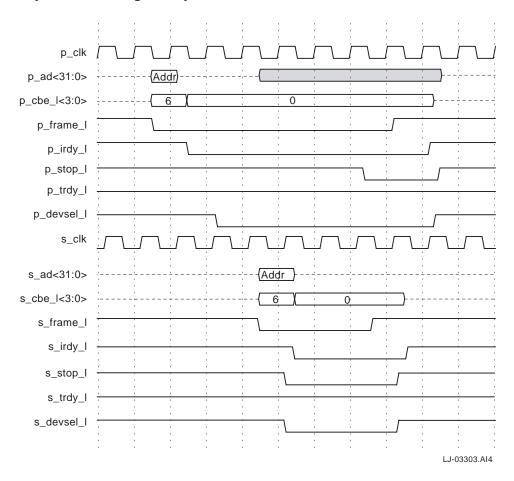

|               | 4-2  | I/O Write Timing                                                          | 24   |

|---------------|------|---------------------------------------------------------------------------|------|

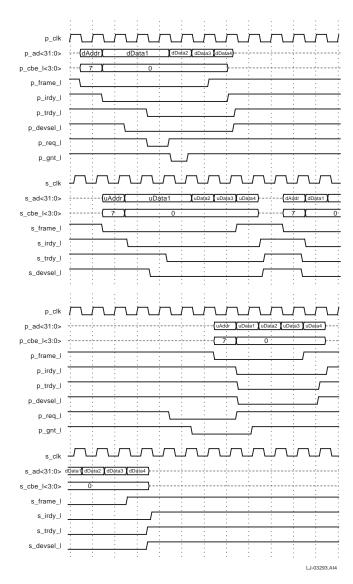

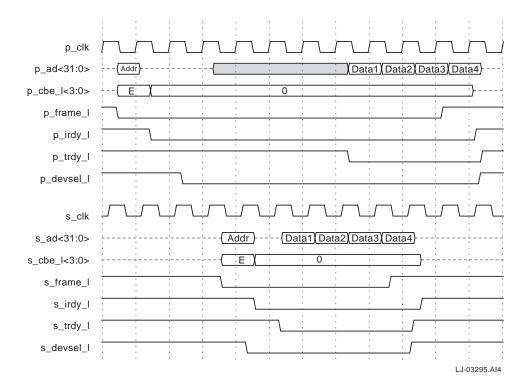

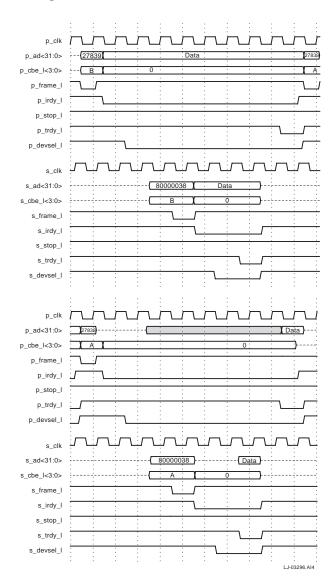

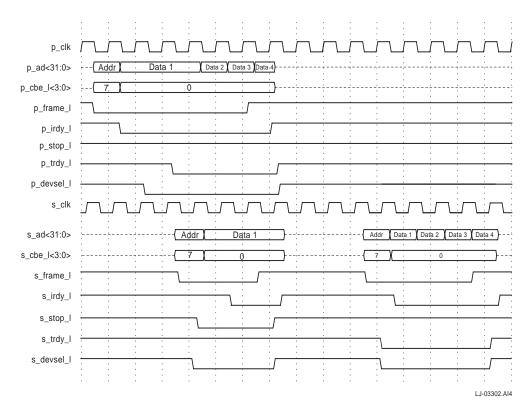

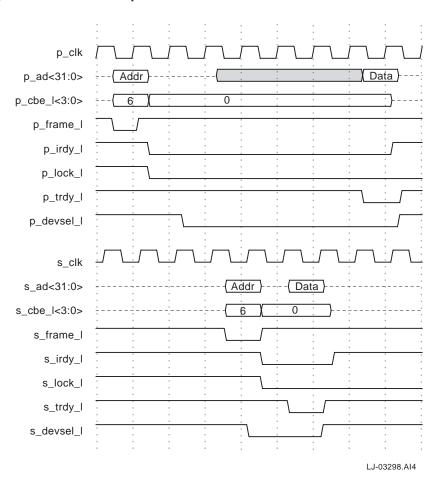

|               | 4-3  | Simultaneous Upstream and Downstream Posted Memory Writes                 | 26   |

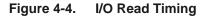

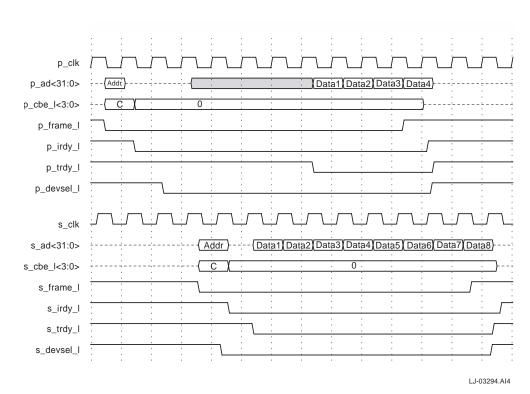

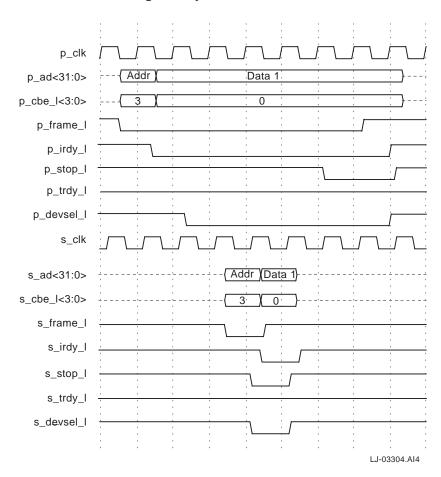

|               | 4-4  | I/O Read Timing                                                           | 29   |

|               | 4-5  | Memory Read with Prefetching up to Cache Line Boundary                    | 31   |

|               | 4-6  | Memory Read multiple with Extra Prefetching                               | . 32 |

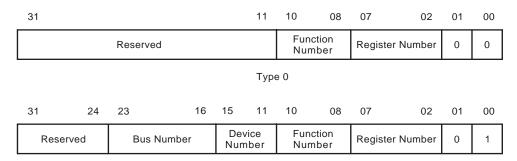

|               | 4-7  | Configuration Address Formats                                             | 34   |

|               | 4-8  | Type 0 Configuration Write Access and Configuration Read Access           | 35   |

|               | 4-9  | Type 1 to Type 0 Configuration Write and Read                             | 37   |

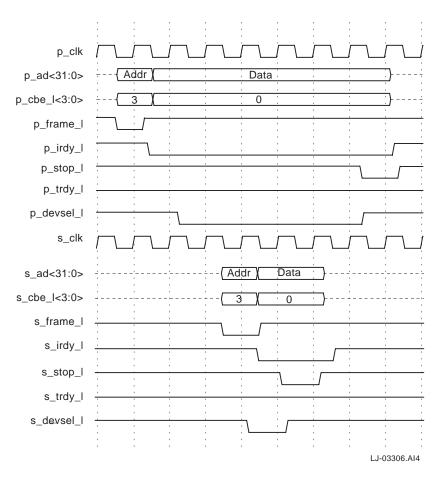

|               | 4-10 | Type 1 Configuration Write to Special Cycle Downstream                    | 39   |

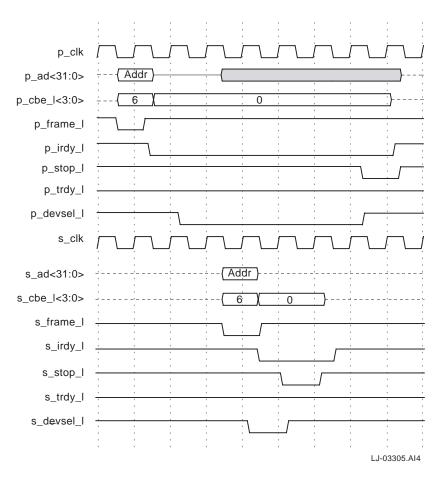

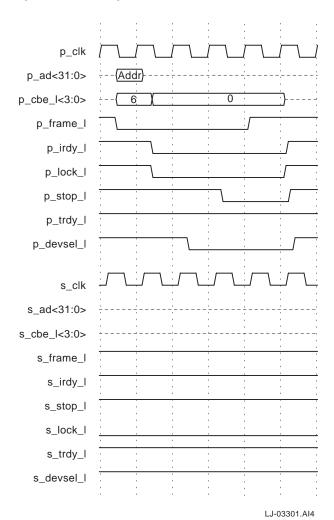

|               | 4-11 | I/O Write with Target Abort                                               | . 43 |

|               | 4-12 | Downstream Memory Read with Target Abort                                  | 44   |

|               | 4-13 | Non-Posted I/O Write with Target Retry                                    | . 45 |

|               | 4-14 | Memory Read with Target Retry                                             | . 46 |

|               | 4-15 | Posted Write with Target Retry                                            | . 48 |

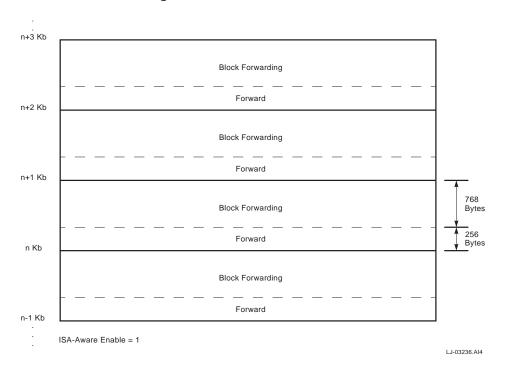

|               | 4-16 | Downstream I/O Forwarding in ISA Mode                                     |      |

|               | 4-17 | Memory Read with Lock Acquisition                                         | 57   |

|               | 4-18 | Read with Lock Acquisition Attempt                                        | . 58 |

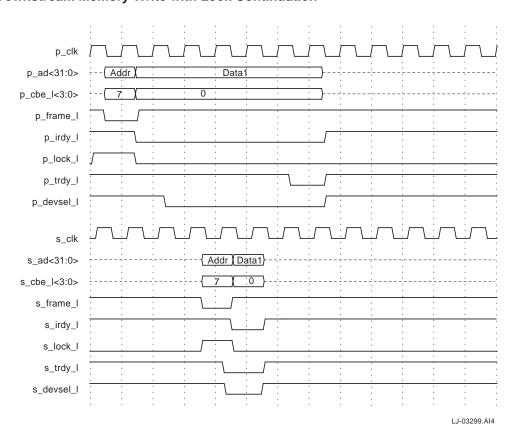

|               | 4-19 | Downstream Memory Write with Lock Continuation                            | . 59 |

|               | 4-20 | Memory Write with End of Lock                                             | 61   |

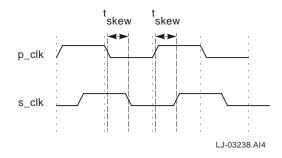

|               | 4-21 | p_clk and s_clk Relative Timing                                           | . 67 |

|               | 5-1  | Configuration Space Map                                                   | 71   |

|               | 7-1  | Package Dimensions                                                        | 88   |

|               | 7-2  | p_clk and s_clk AC Timing                                                 |      |

|               | 7-3  | AC Timing Waveforms                                                       | . 92 |

| Tables        |      |                                                                           |      |

| <b>Tables</b> |      |                                                                           |      |

|               | 1-1  | Major Sub-Blocks of the 21050                                             |      |

|               | 2-2  | Alphabetic Pin Assignment List (Sheet 1 of 4)                             |      |

|               | 2-3  | Numeric Pin Assignment List (Sheet 1 of 4)                                |      |

|               | 3-4  | Signal Types                                                              |      |

|               | 3-5  | Primary OCI Bus Signals (Sheet 1 of 2)                                    |      |

|               | 3-6  | Secondary PCI Bus Signals (Sheet 1 of 2)                                  |      |

|               | 3-7  | Secondary Bus Arbiter Signals                                             |      |

|               | 3-8  | Clock, Reset and Miscellaneous Signals (Sheet 1 of 2)                     |      |

|               | 4-1  | xcbe_I Commands                                                           |      |

|               | 4-2  | Transaction Forwarding and Filtering                                      |      |

|               | 4-3  | Device Number to s_ad Signal Mapping                                      | . 36 |

|               | 4-4  | Data Parity Errors Signals for Forwarded Transactions                     |      |

|               | 4-5  | p_serr_I Assertion Conditions                                             |      |

|               | 5-1  | Device ID and Vendor ID Register                                          |      |

|               | 5-2  | Primary Status and Primary Command Register (Sheet 1 of 2)                |      |

|               | 5-3  | Class Code/Programming Interface/Revision ID Register                     |      |

|               | 5-4  | Primary Master Latency Timer/Cache Line Size/Header Type Register         |      |

|               | 5-5  | Reserved Registers (10–14 Hex)                                            | . 75 |

|               | 5-6  | Primary Bus Number/Secondary Bus Number/Subordinate Bus                   |      |

|               |      | Number/Secondary Master Latency Timer                                     |      |

|               | 5-7  | I/O Base Address/I/O Limit Address/Secondary Status Registers             |      |

|               | 5-8  | Memory Base Address/Memory Limit Address Register                         |      |

|               | 5-9  | Prefetchable Memory Base Addr./Prefetchable Memory Limit Addr. Register . |      |

|               | 5-10 | Reserved Registers (28–38 Hex)                                            | 79   |

| 5-11 | Interrupt Pin/Bridge Controller Register (Sheet 1 of 2)                   | 79 |

|------|---------------------------------------------------------------------------|----|

| 5-12 | Chip Control/Diagnostic Control/Burst Limit Counter/serr Disable Register | 80 |

| 5-13 | Primary Target Wait Timer/Secondary Target Wait Timer Register            | 81 |

| 5-14 | Secondary Write Attempt Counter Register                                  | 82 |

| 5-15 | Primary Write Attempt Counter Register                                    | 82 |

| 5-16 | Reserved Registers (50h – FFh)                                            | 83 |

| 7-1  | Lead Counts and Dimensional Attributes                                    | 87 |

| 7-2  | Absolute Maximum Ratings                                                  |    |

| 7-3  | Functional Operating Range                                                | 89 |

| 7-4  | DC Specifications                                                         | 89 |

| 7-5  | Shared Signal Output Parameters                                           | 89 |

| 7-6  | p_clk and s_clk AC Timing                                                 | 90 |

| 7-7  | Input Signal AC Timings                                                   | 91 |

| 7-8  | xrst Timing Specifications                                                | 92 |

# 1.0 Introduction

# 1.1 Purpose

This data sheet describes the 21050 PCI-to-PCI bridge chip (21050). The 21050 expands the electrical capacity of all PCI systems. The 21050 allows motherboard designers to add more PCI devices or more PCI option card slots than a single PCI bus can support. Option card designers can use the 21050 to implement multiple device PCI option cards.

This document is not intended to describe the details of PCI protocol.

### 1.2 Audience

This document is for chip designers who need to expand the electrical capacity of their PCI bus architectures.

# 1.3 Manual Organization

This datasheet consists of the following:

- Chapter 1.0, "Introduction" is an overview of the 21050.

- Chapter 2.0, "21050 Pin Assignment" lists the 21050 pin assignment in alphabetic and numeric order.

- Chapter 3.0, "Signal Description" provides a description of pin signals.

- Chapter 4.0, "Functional Description" describes chip functions, including bus interfaces, transaction types, transaction termination, address decoding, arbitration, and other functions.

- Chapter 5.0, "Configuration Register Description" provides programmer reference information about configuration space registers.

- Chapter 6.0, "Diagnostics and Test Mechanisms" provides diagnostics information.

- Chapter 7.0, "21050 Specifications" lists the mechanical and electrical characteristics of the chip.

# 1.4 General Description

The 21050 has two PCI interfaces. The primary PCI interface connects directly to the PCI bus closest to the host CPU. The secondary PCI interface creates a new and independent PCI bus. The primary function of the bridge is to allow transactions to occur between a master on one PCI bus and a target on the other PCI bus.

The 21050 also allows the two PCI buses to operate independently. A master and a target located on the same PCI bus can communicate with each other even if the other PCI bus is busy. As a result, the 21050 can isolate traffic between devices on one PCI bus from devices on other PCI buses. This is a major benefit to system performance in some applications such as multimedia.

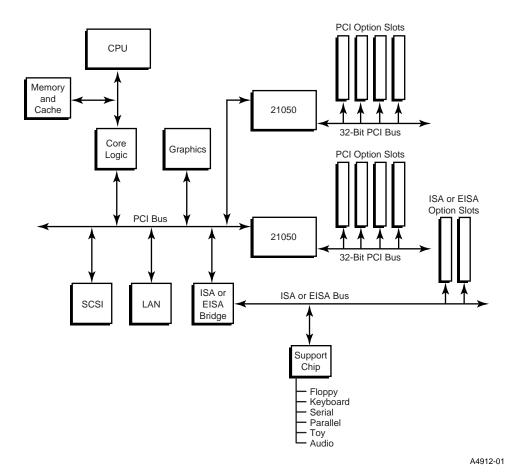

The 21050 can extend a system beyond the electrical loading limits of a single PCI bus. Each new PCI bus created by the addition of a 21050 provides support for additional electrical loads. Motherboard designers can use the 21050 to add more PCI devices or PCI option card connectors to the motherboard. Figure 1-1 shows the 21050 on the system board.

Figure 1-1. 21050 PCI-to-PCI Bridge on the System Board

**Preliminary Datasheet**

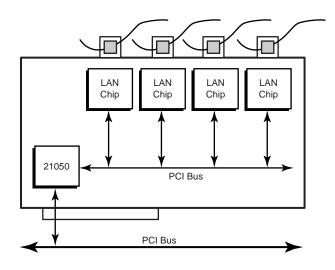

Option card designers can use a 21050 to implement multiple device PCI option cards. Without a 21050, you can attach only one PCI device to the PCI option connector (the *PCI Local Bus Specification*, Revision 2.1 restricts PCI option cards to a single connection per PCI signal in the option card connector). In this application, the 21050 creates an independent PCI bus on the option card to which many devices can be attached.

Figure 1-2 shows the 21050 with option cards.

Figure 1-2. 21050 PCI-to-PCI Bridge with Option Cards

A4913-01

### 1.5 Architecture Overview

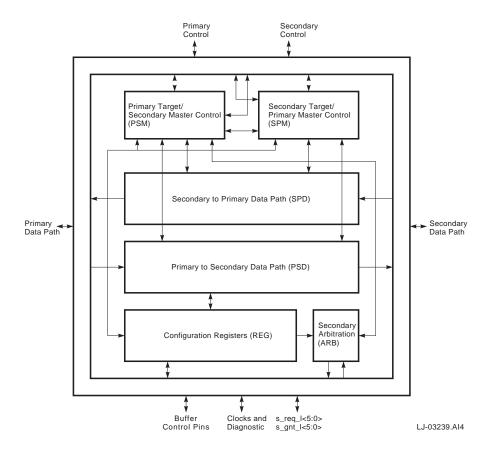

Figure 1-3 shows the major functions of the 21050, and Table 1-1 describes the major sub-blocks. The 21050 is packaged in a 208-pin plastic quad flat-pack.

Figure 1-3. 21050 PCI-to-PCI Bridge Block Diagram

Table 1-1. Major Sub-Blocks of the 21050

| Block | Description                                                                                                                                                                                                                           |

|-------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| PSM   | Machine and control logic for all transactions initiated on the primary interface, whether the transaction is intended for the 21050 itself or a target on the secondary side of the 21050.                                           |

| SPM   | Machine and control logic for all transactions initiated on the secondary interface. All such transactions are intended for a target on the primary interface, since 21050 registers are not accessible from the secondary interface. |

| SPD   | Data path for data received on the secondary interface and driven on the primary interface. Used for writes initiated on the secondary PCI bus or reads initiated on the primary PCI bus.                                             |

| PSD   | Data path for data received on the primary interface and driven on the secondary interface. Used for writes initiated on the primary PCI bus or reads initiated on the secondary PCI bus.                                             |

| REG   | Configuration registers and corresponding control logic. Accessible from the primary interface only.                                                                                                                                  |

| ARB   | Logic for secondary bus arbitration. Receives s_req_[5:0], as well as the PPB secondary bus request, and drives one of the s_gnt_[5:0] lines or the PPB secondary bus grant.                                                          |

# 2.0 21050 Pin Assignment

The 21050 is divided into three main functions:

- Primary PCI bus interface that interacts with the bus closest to the CPU

- Secondary PCI bus interface that interacts with the bus that is farther from the CPU

- Power supply and miscellaneous functions

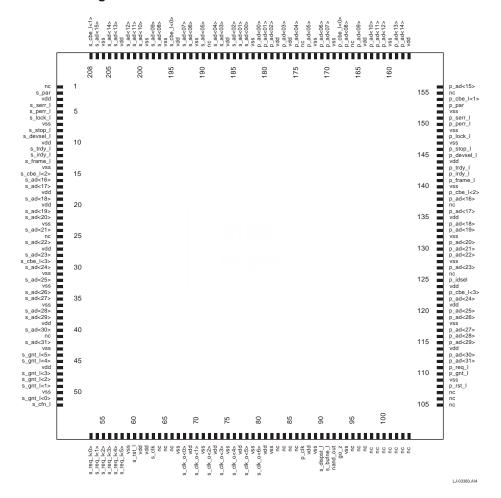

Figure 2-1 shows the 21050 signals, and the 21050 pin assignments are listed in alphabetic and numeric order at the end of this chapter.

Figure 2-1. 21050 Pinout Diagram

**Preliminary Datasheet**

# 2.1 Signal Types

The following table defines the 21050 signal types referred to in this chapter.

| Signal Type | Definition                                                                                |

|-------------|-------------------------------------------------------------------------------------------|

| I           | Standard input only.                                                                      |

| 0           | Standard output only.                                                                     |

| ts          | Tristate bidirectional.                                                                   |

| sts         | Sustained tristate. Active low signal must be pulled high for one cycle when deasserting. |

| od          | Standard open drain.                                                                      |

| Р           | Power or ground.                                                                          |

# 2.2 Alphabetic 21050 Pin Assignment List

Table 2-2 lists the 21050 pins in alphabetic order.

Table 2-2. Alphabetic Pin Assignment List (Sheet 1 of 4)

| Pin <sup>1</sup> | Pin Number | Туре | Pin <sup>1</sup> | Pin Number | Туре |

|------------------|------------|------|------------------|------------|------|

| go_z             | 93         | 1    | nc               | 104        |      |

| nand_out         | 92         | 0    | nc               | 105        |      |

| nc               | 1          |      | nc               | 106        |      |

| nc               | 25         |      | nc               | 107        |      |

| nc               | 41         |      | nc               | 126        |      |

| nc               | 64         |      | nc               | 105        |      |

| nc               | 65         |      | nc               | 137        |      |

| nc               | 66         |      | nc               | 155        |      |

| nc               | 83         |      | nc               | 166        |      |

| nc               | 84         |      | nc               | 174        |      |

| nc               | 85         |      | nc               | 189        |      |

| nc               | 86         |      | p_ad<00>         | 181        | ts   |

| nc               | 95         |      | p_ad<01>         | 180        | ts   |

| nc               | 96         |      | p_ad<02>         | 179        | ts   |

| nc               | 97         |      | p_ad<03>         | 177        | ts   |

| nc               | 98         |      | p_ad<04>         | 175        | ts   |

| nc               | 99         |      | p_ad<05>         | 173        | ts   |

| nc               | 100        |      | p_ad<06>         | 171        | ts   |

| nc               | 101        |      | p_ad<07>         | 170        | ts   |

| nc               | 102        |      | p_ad<08>         | 167        | ts   |

| nc               | 103        |      | p_ad<09>         | 165        | ts   |

Table 2-2. Alphabetic Pin Assignment List (Sheet 2 of 4)

| Pin <sup>1</sup> | Pin Number | Туре | Pin <sup>1</sup> | Pin Number | Туре |

|------------------|------------|------|------------------|------------|------|

| p_ad<10>         | 163        | ts   | p_stop_l         | 146        | sts  |

| p_ad<11>         | 162        | ts   | p_trdy_l         | 143        | sts  |

| p_ad<12>         | 161        | ts   | s_ad<00>         | 183        | ts   |

| p_ad<13>         | 159        | ts   | s_ad<01>         | 184        | ts   |

| p_ad<14>         | 158        | ts   | s_ad<02>         | 185        | ts   |

| p_ad<15>         | 156        | ts   | s_ad<03>         | 187        | ts   |

| p_ad<16>         | 138        | ts   | s_ad<04>         | 188        | ts   |

| p_ad<17>         | 136        | ts   | s_ad<05>         | 190        | ts   |

| p_ad<18>         | 134        | ts   | s_ad<06>         | 192        | ts   |

| p_ad<19>         | 133        | ts   | s_ad<07>         | 193        | ts   |

| p_ad<20>         | 131        | ts   | s_ad<08>         | 197        | ts   |

| p_ad<21>         | 130        | ts   | s_ad<09>         | 198        | ts   |

| p_ad<22>         | 129        | ts   | s_ad<10>         | 200        | ts   |

| p_ad<23>         | 127        | ts   | s_ad<11>         | 201        | ts   |

| p_ad<24>         | 122        | ts   | s_ad<12>         | 202        | ts   |

| p_ad<25>         | 120        | ts   | s_ad<14>         | 205        | ts   |

| p_ad<26>         | 119        | ts   | s_ad<15>         | 207        | ts   |

| p_ad<27>         | 117        | ts   | s_ad<16>         | 16         | ts   |

| p_ad<28>         | 116        | ts   | s_ad<17>         | 17         | ts   |

| p_ad<29>         | 115        | ts   | s_ad<18>         | 19         | ts   |

| p_ad<30>         | 113        | ts   | s_ad<19>         | 21         | ts   |

| p_ad<31>         | 112        | ts   | s_ad<20>         | 22         | ts   |

| p_cbe_l<0>       | 168        | ts   | s_ad<21>         | 24         | ts   |

| p_cbe_l<1>       | 154        | ts   | s_ad<22>         | 26         | ts   |

| p_cbe_l<2>       | 139        | ts   | s_ad<23>         | 28         | ts   |

| p_cbe_l<3>       | 123        | ts   | s_ad<24>         | 30         | ts   |

| p_clk            | 87         | I    | s_ad<25>         | 32         | ts   |

| p_devsel_l       | 145        | sts  | s_ad<26>         | 34         | ts   |

| p_frame_l        | 141        | sts  | s_ad<27>         | 35         | ts   |

| p_gnt_l          | 110        | I    | s_ad<28>         | 37         | ts   |

| p_idsel          | 125        | I    | s_ad<29>         | 38         | ts   |

| p_irdy_l         | 142        | sts  | s_ad<30>         | 40         | ts   |

| p_lock_l         | 148        | sts  | s_ad<31>         | 42         | ts   |

| p_par            | 153        | ts   | s_bufne_l        | 91         | 0    |

| p_perr_l         | 150        | sts  | s_cbe_l<0>       | 195        | ts   |

| p_req_l          | 111        | ts   | s_cbe_l<1>       | 208        | ts   |

| p_rst_l          | 108        | I    | s_cbe_l<2>       | 15         | ts   |

| p_serr_l         | 151        | od   | s_cbe_l<3>       | 29         | ts   |

Table 2-2. Alphabetic Pin Assignment List (Sheet 3 of 4)

| Pin <sup>1</sup> | Pin Number | Туре | Pin <sup>1</sup> | Pin Number | Туре |

|------------------|------------|------|------------------|------------|------|

| s_cfn_l          | 52         | I    | vdd              | 20         | Р    |

| s_clk            | 63         | I    | vdd              | 61         | Р    |

| s_clk_o<0>       | 68         | 0    | vdd              | 124        | Р    |

| s_clk_o<1>       | 70         | 0    | vdd              | 176        | Р    |

| s_clk_o<2>       | 72         | 0    | vdd              | 3          | Р    |

| s_clk_o<3>       | 74         | 0    | vdd              | 10         | Р    |

| s_clk_o<4>       | 76         | 0    | vdd              | 18         | Р    |

| s_clk_o<5>       | 78         | 0    | vdd              | 27         | Р    |

| s_clk_o<6>       | 80         | 0    | vdd              | 39         | Р    |

| s_devsel_l       | 9          | sts  | vdd              | 46         | Р    |

| s_dispst_l       | 90         | I    | vdd              | 62         | Р    |

| s_frame_l        | 13         | sts  | vdd              | 69         | Р    |

| s_gnt_l<5>       | 44         | ts   | vdd              | 73         | Р    |

| s_gnt_l<4>       | 45         | ts   | vdd              | 77         | Р    |

| s_gnt_l<3>       | 47         | ts   | vdd              | 81         | Р    |

| s_gnt_l<2>       | 48         | ts   | vdd              | 88         | Р    |

| s_gnt_l<1>       | 49         | ts   | vdd              | 114        | Р    |

| s_gnt_l<0>       | 51         | ts   | vdd              | 121        | Р    |

| s_irdy_l         | 12         | sts  | vdd              | 135        | Р    |

| s_lock_l         | 6          | sts  | vdd              | 144        | Р    |

| s_par            | 2          | ts   | vss              | 82         | Р    |

| s_perr_l         | 5          | sts  | vss              | 94         | Р    |

| s_req_l<0>       | 53         | I    | vss              | 109        | Р    |

| s_req_l<1>       | 54         | I    | vss              | 118        | Р    |

| s_req_l<2>       | 55         | I    | vss              | 128        | Р    |

| s_req_l<3>       | 56         | I    | vss              | 59         | Р    |

| s_req_l<4>       | 57         | I    | vss              | 67         | Р    |

| s_req_l<5>       | 58         | I    | vss              | 71         | Р    |

| s_rst_l          | 60         | 0    | vss              | 75         | Р    |

| s_serr_l         | 4          | I    | vss              | 79         | Р    |

| s_stop_l         | 8          | sts  | vss              | 43         | Р    |

| s_trdy_l         | 11         | sts  | vss              | 50         | Р    |

| vdd              | 157        | Р    | vss              | 132        | Р    |

| vdd              | 164        | Р    | vss              | 140        | Р    |

| vdd              | 178        | Р    | vss              | 147        | Р    |

| vdd              | 186        | Р    | vss              | 152        | Р    |

| vdd              | 194        | Р    | vss              | 160        | Р    |

| vdd              | 203        | Р    | vss              | 169        | Р    |

Table 2-2. Alphabetic Pin Assignment List (Sheet 4 of 4)

| Pin <sup>1</sup> | Pin Number | Туре | Pin <sup>1</sup> | Pin Number | Туре |

|------------------|------------|------|------------------|------------|------|

| VSS              | 33         | Р    | vss              | 172        | Р    |

| VSS              | 89         | Р    | vss              | 182        | Р    |

| VSS              | 149        | Р    | vss              | 191        | Р    |

| vss              | 196        | Р    | vss              | 199        | Р    |

| vss              | 7          | Р    | vss              | 206        | Р    |

| vss              | 14         | Р    | vss              | 31         | Р    |

| VSS              | 23         | Р    | vss              | 36         | Р    |

<sup>&</sup>lt;sup>1.</sup> nc—Do not connect these pins on the board.

# 2.3 Numeric 21050 Pin Assignment List

Table 2-3 lists the 21050 pins in numeric order.

Table 2-3. Numeric Pin Assignment List (Sheet 1 of 4)

| Pin <sup>1</sup> | Pin Number | Туре | Pin <sup>1</sup> | Pin Number | Туре |

|------------------|------------|------|------------------|------------|------|

| nc               | 1          |      | s_ad<21>         | 24         | ts   |

| s_par            | 2          | ts   | nc               | 25         |      |

| vdd              | 3          | Р    | s_ad<22>         | 26         | ts   |

| s_serr_l         | 4          | I    | vdd              | 27         | Р    |

| s_perr_l         | 5          | sts  | s_ad<23>         | 28         | ts   |

| s_lock_l         | 6          | sts  | s_cbe_l<3>       | 29         | ts   |

| vss              | 7          | Р    | s_ad<24>         | 30         | ts   |

| s_stop_l         | 8          | sts  | vss              | 31         | Р    |

| s_devsel_l       | 9          | sts  | s_ad<25>         | 32         | ts   |

| vdd              | 10         | Р    | vss              | 33         | Р    |

| s_trdy_l         | 11         | sts  | s_ad<26>         | 34         | ts   |

| s_irdy_l         | 12         | sts  | s_ad<27>         | 35         | ts   |

| s_frame_l        | 13         | sts  | vss              | 36         | Р    |

| vss              | 14         | Р    | s_ad<28>         | 37         | ts   |

| s_cbe_l<2>       | 15         | ts   | s_ad<29>         | 38         | ts   |

| s_ad<16>         | 16         | ts   | vdd              | 39         | Р    |

| s_ad<17>         | 17         | ts   | s_ad<30>         | 40         | ts   |

| vdd              | 18         | Р    | nc               | 41         |      |

| s_ad<18>         | 19         | ts   | s_ad<31>         | 42         | ts   |

| vdd              | 20         | Р    | vss              | 43         | Р    |

| s_ad<19>         | 21         | ts   | s_gnt_l<5>       | 44         | ts   |

| s_ad<20>         | 22         | ts   | s_gnt_l<4>       | 45         | ts   |

Table 2-3. Numeric Pin Assignment List (Sheet 2 of 4)

| Pin <sup>1</sup> | Pin Number | Туре | Pin <sup>1</sup> | Pin Number | Туре |

|------------------|------------|------|------------------|------------|------|

| vss              | 23         | Р    | vdd              | 46         | Р    |

| s_gnt_l<3>       | 47         | ts   | vdd              | 73         | Р    |

| s_gnt_l<2>       | 48         | ts   | s_clk_o<3>       | 74         | 0    |

| s_gnt_l<1>       | 49         | ts   | vss              | 75         | Р    |

| vss              | 50         | Р    | s_clk_o<4>       | 76         | 0    |

| s_gnt_l<0>       | 51         | ts   | vdd              | 77         | Р    |

| s_cfn_l          | 52         | I    | s_clk_o<5>       | 78         | 0    |

| s_req_l<0>       | 53         | ts   | vss              | 79         | Р    |

| s_req_l<1>       | 54         | 1    | s_clk_o<6>       | 80         | 0    |

| s_req_l<2>       | 55         | 1    | vdd              | 81         | Р    |

| s_req_l<3>       | 56         | I    | vss              | 82         | Р    |

| s_req_l<4>       | 57         | I    | nc               | 83         |      |

| s_req_l<5>       | 58         | I    | nc               | 84         |      |

| vss              | 59         | Р    | nc               | 85         |      |

| s_rst_l          | 60         | 0    | nc               | 86         |      |

| vdd              | 61         | Р    | p_clk            | 87         | I    |

| vdd              | 62         | Р    | vdd              | 88         | Р    |

| s_clk            | 63         | 1    | vss              | 89         | Р    |

| nc               | 64         |      | s_dispst_l       | 90         | I    |

| nc               | 65         |      | s_bufne_l        | 91         | 0    |

| nc               | 66         |      | nand_out         | 92         | 0    |

| vss              | 67         | Р    | go_z             | 93         | I    |

| s_clk_o<0>       | 68         | 0    | vss              | 94         | Р    |

| vdd              | 69         | 0    | nc               | 95         |      |

| s_clk_o<1>       | 70         | 0    | nc               | 96         |      |

| vss              | 71         | Р    | nc               | 97         |      |

| s_clk_o<2>       | 72         | 0    | nc               | 98         |      |

| nc               | 99         |      | p_idsel          | 125        | ts   |

| nc               | 100        |      | nc               | 126        |      |

| nc               | 101        |      | p_ad<23>         | 127        | ts   |

| nc               | 102        |      | vss              | 128        | Р    |

| nc               | 103        |      | p_ad<22>         | 129        | ts   |

| nc               | 104        |      | p_ad<21>         | 130        | ts   |

| nc               | 105        |      | p_ad<20>         | 131        | ts   |

| nc               | 106        |      | vss              | 132        | Р    |

| nc               | 107        |      | p_ad<19>         | 133        | ts   |

| p_rst_l          | 108        | 1    | p_ad<18>         | 134        | ts   |

| vss              | 109        | Р    | vdd              | 135        | Р    |

Table 2-3. Numeric Pin Assignment List (Sheet 3 of 4)

| Pin <sup>1</sup> | Pin Number | Туре | Pin <sup>1</sup> | Pin Number | Туре |

|------------------|------------|------|------------------|------------|------|

| p_gnt_l          | 110        | 1    | p_ad<17>         | 136        | ts   |

| p_req_l          | 111        | ts   | nc               | 137        | Р    |

| p_ad<31>         | 112        | ts   | p_ad<16>         | 138        | ts   |

| p_ad<30>         | 113        | ts   | p_cbe_l<2>       | 139        | ts   |

| vdd              | 114        | Р    | vss              | 140        | Р    |

| p_ad<29>         | 115        | ts   | p_frame_l        | 141        | sts  |

| p_ad<28>         | 116        | ts   | p_irdy_l         | 142        | sts  |

| p_ad<27>         | 117        | ts   | p_trdy_l         | 143        | sts  |

| VSS              | 118        | Р    | vdd              | 144        | Р    |

| p_ad<26>         | 119        | ts   | p_devsel_l       | 145        | sts  |

| p_ad<25>         | 120        | ts   | p_stop_l         | 146        | sts  |

| vdd              | 121        | Р    | vss              | 147        | Р    |

| p_ad<24>         | 122        | ts   | p_lock_l         | 148        | sts  |

| p_cbe_l<3>       | 123        | ts   | vss              | 149        | Р    |

| vdd              | 124        | Р    | p_perr_l         | 150        | sts  |

| p_serr_l         | 151        | od   | p_ad<04>         | 175        | ts   |

| VSS              | 152        | Р    | vdd              | 176        | Р    |

| p_par            | 153        | ts   | p_ad<03>         | 177        | ts   |

| p_cbe_l<1>       | 154        | ts   | vdd              | 178        | Р    |

| nc               | 155        |      | p_ad<02>         | 179        | ts   |

| p_ad<15>         | 156        | ts   | p_ad<01>         | 180        | ts   |

| vdd              | 157        | Р    | p_ad<00>         | 181        | ts   |

| p_ad<14>         | 158        | ts   | vss              | 182        | Р    |

| p_ad<13>         | 159        | ts   | s_ad<00>         | 183        | ts   |

| VSS              | 160        | Р    | s_ad<01>         | 184        | ts   |

| p_ad<12>         | 161        | ts   | s_ad<02>         | 185        | ts   |

| p_ad<11>         | 162        | ts   | vdd              | 186        | Р    |

| p_ad<10>         | 163        | ts   | s_ad<03>         | 187        | ts   |

| vdd              | 164        | Р    | s_ad<04>         | 188        | ts   |

| p_ad<09>         | 165        | ts   | nc               | 189        |      |

| nc               | 166        |      | s_ad<05>         | 190        | ts   |

| p_ad<08>         | 167        | ts   | vss              | 191        | Р    |

| p_cbe_l<0>       | 168        | ts   | s_ad<06>         | 192        | ts   |

| VSS              | 169        | Р    | s_ad<07>         | 193        | ts   |

| p_ad<07>         | 170        | ts   | vdd              | 194        | Р    |

| p_ad<06>         | 171        | ts   | s_cbe_l<0>       | 195        | ts   |

| VSS              | 172        | Р    | vss              | 196        | Р    |

| p_ad<05>         | 173        | ts   | s_ad<08>         | 197        | ts   |

# Table 2-3. Numeric Pin Assignment List (Sheet 4 of 4)

| Pin <sup>1</sup> | Pin Number | Туре | Pin <sup>1</sup> | Pin Number | Туре |

|------------------|------------|------|------------------|------------|------|

| nc               | 174        |      | s_ad<09>         | 198        | ts   |

|                  |            |      |                  |            |      |

| vss              | 199        | Р    | s_ad<11>         | 201        | ts   |

| s_ad<10>         | 200        | ts   | s_ad<12>         | 202        | ts   |

<sup>1.</sup> nc—Do not connect these pins on the board.

# 3.0 Signal Description

This chapter contains a detailed description of 21050 signals. Signals are divided into four major functions:

- · Primary PCI bus

- · Secondary PCI bus

- · Secondary bus arbiter

- Clocks, reset, and miscellaneous

Note:

The \_l symbol at the end of a signal name indicates that the active, or asserted state occurs when the signal is at a low-voltage level. If the \_l symbol is not present after the signal name, then the signal is asserted at the high voltage level.

The following table describes the signal types referred to in this chapter.

### Table 3-4. Signal Types

| Signal Type | Definition                                                                                |

|-------------|-------------------------------------------------------------------------------------------|

| I           | Standard input only.                                                                      |

| 0           | Standard output only.                                                                     |

| ts          | Tristate bidirectional.                                                                   |

| sts         | Sustained tristate. Active low signal must be pulled high for one cycle when deasserting. |

| od          | Standard open drain.                                                                      |

| Р           | Power or ground.                                                                          |

# 3.1 Primary PCI Bus Signals

The following table describes the primary PCI bus signals.

Table 3-5. Primary OCI Bus Signals (Sheet 1 of 2)

| Signal Name  | Туре | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|--------------|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| p_ad<31:0>   | ts   | Primary PCI interface address/data. These signals represent a multiplexed PCI address and data bus. During an address phase of a transaction, p_ad<31:0> contains a physical byte address. During subsequent data phases, p_ad<31:0> contains data. A PCI bus transaction consists of one or two address phases followed by one or more data phases.                                                                                                                                          |

| p_cbe_l<3:0> | ts   | Primary PCI interface command/byte enables. These signals are multiplexed bus command and byte enables. During an address phase of a transaction, p_cbe_l<3:0> contains the bus command that defines the type of PCI transaction. During data phases, p_cbe_l<3:0> contains byte enables dictating which byte lanes carry valid data. p_cbe_l<0> applies to byte 0; p_cbe_l<3> applies to byte 3.                                                                                             |

| p_frame_l    | sts  | Primary PCI interface cycle frame. p_frame_I is driven by the initiator of the transaction to indicate the beginning and duration of an access on the primary PCI bus. p_frame_I assertion indicates the beginning of an access. While p_frame_I is asserted, data transfers continue. The deassertion of p_frame_I indicates the final data phase. The bridge samples p_frame_I as an input and also drives p_frame_I when acting as the initiator of a transaction on the primary PCI bus.  |

| p_trdy_l     | sts  | Primary PCI interface target ready. This signal indicates the target's ability to complete the current data phase of a transaction on the primary PCI bus. The bridge drives p_trdy_I when acting as a target on the primary PCI bus and samples p_trdy_I when acting as an initiator on the primary PCI bus.                                                                                                                                                                                 |

| p_irdy_l     | sts  | Primary PCI interface initiator ready. This signal indicates the initiator's ability to complete the current data phase of a transaction on the primary PCI bus. The ridge drives p_irdy_l when acting as an initiator on the primary PCI bus and samples p_irdy_l when acting as a target on the primary PCI bus.                                                                                                                                                                            |

| p_stop_l     | sts  | Primary PCI interface stop indicator. This signal indicates that the current target is requesting the bus initiator to stop the current transaction on the primary PCI bus. The bridge drives p_stop_I when acting as a target on the primary PCI bus and samples p_stop_I when acting as an initiator on the primary PCI bus.                                                                                                                                                                |

| p_lock_l     | sts  | Primary PCI interface resource lock. Indicates an atomic operation that may require multiple transactions to complete. Resources in the bridge cannot be locked, but the bridge does propagate locks across the bridge. The bridge samples p_lock_I when acting as a target on the primary PCI bus and drives p_lock_I when acting as an initiator on the primary PCI bus on behalf of a master on the secondary bus.                                                                         |

| p_idsel      | I    | Initialization device select. Used as a chip select during configuration read and write commands. If p_idsel is detected asserted and the transaction is a Type 0 configuration command, then the bridge responds as a target to the transaction by asserting p_devsel_l.                                                                                                                                                                                                                     |

| p_devsel_I   | sts  | Primary PCI interface device select. Asserted by the bridge through positive decoding of the address on p_ad<31:0>. When it is accepting a transaction for an internal configuration access or when it is forwarding a transaction across the bridge. The bridge samples p_devsel_I when it is acting as an initiator on the primary PCI bus, and expects p_devsel_I to be asserted within five cycles of p_frame_I assertion. Otherwise, the transaction is terminated with an master abort. |

Table 3-5. Primary OCI Bus Signals (Sheet 2 of 2)

| Signal Name | Туре | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|-------------|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| p_par       | ts   | Primary PCI interface parity. Even parity, calculated on 36 bits composed of p_ad<31:0> and p_cbe_l<3:0>. The p_par signal is generated for all address and data phases and is valid one clock cycle after valid data or address is driven on p_ad<31:0>. The p_par signal is driven and tristated identically to p_ad, except that it is delayed one clock cycle. The p_par signal is driven by the bridge when acting as an initiator during address phases and write data phases. The p_par signal is driven by the bridge when acting as a target during read data phases. The p_par signal is sampled as an input during all address phases, and when acting as a target during write data phases. |

| p_serr_l    | od   | Primary PCI interface system error. Can be pulsed by any device residing on the primary PCI bus that detects a system error condition. The bridge can be enabled to assert p_serr_I as a result of address parity error detection, special cycle data parity error, s_serr_I assertion, master aborts or target aborts during posted writes, data parity error during posted writes, and undelivered posted write data.                                                                                                                                                                                                                                                                                 |

| p_perr_l    | sts  | Primary PCI interface parity error detected. Asserted when a data parity error is detected, and corresponds to p_par driven one clock cycle earlier. The bridge asserts p_perr_I when it detects a write data parity error when acting as a target, or a read data parity error when acting as an initiator.                                                                                                                                                                                                                                                                                                                                                                                            |

| p_req_l     | ts   | Primary PCI bus request. Asserted by the bridge to indicate to the bus arbiter that it wants to use the primary PCI bus.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| p_gnt_l     | ı    | Primary PCI bus grant. When asserted, indicates to the bridge that access to the primary PCI bus is granted. The bridge can start a transaction as soon as p_gnt_l is asserted and the bus is idle.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

# 3.2 Secondary PCI Bus Signals

The following table describes the secondary PCI bus signals.

Table 3-6. Secondary PCI Bus Signals (Sheet 1 of 2)

| Signal Name  | Туре | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|--------------|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| s_ad<31:0>   | ts   | Secondary PCI interface address/data. These signals represent a multiplexed PCI address and data bus. During an address phase of a transaction, s_ad<31:0> contains a physical byte address. During subsequent data phases, s_ad<31:0> contains data. A PCI-to-PCI bridge transaction consists of one or two address phases followed by one or more data phases.                                                                                                                             |

| s_cbe_I<3:0> | ts   | Secondary PCI interface command/byte enables. These signals represent multiplexed bus command and byte enables. During an address phase of a transaction, s_cbe_l<3:0> contains the bus command defining the type of PCI transaction. During data phases, s_cbe_l<3:0> contains byte enables dictating which byte lanes carry valid data. s_cbe_l<0> applies to byte 0; s_cbe_l<3> applies to byte 3.                                                                                        |

| s_frame_l    | sts  | Secondary PCI interface cycle frame. Driven by the initiator of the transaction to indicate the beginning and duration of an access on the secondary PCI bus. The assertion of s_frame_l indicates the beginning of an access. While s_frame_l is asserted, data transfers continue. The deassertion of s_frame_l indicates the final data phase. The bridge samples s_frame_l as an input and also drives s_frame_l when acting as the initiator of a transaction on the secondary PCI bus. |

Table 3-6. Secondary PCI Bus Signals (Sheet 2 of 2)

| Signal Name | Туре | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|-------------|------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| s_trdy_l    | sts  | Secondary PCI interface target ready. This signal indicates the target agent's ability to complete the current data phase of a transaction on the secondary PCI bus. The bridge drives s_trdy_I when acting as a target on the secondary PCI bus and samples s_trdy_I when acting as an initiator on the secondary PCI bus.                                                                                                                                                                                                                                                                                                                                                                    |

| s_irdy_l    | sts  | Secondary PCI interface initiator ready. This signal indicates the initiator's ability to complete the current data phase of a transaction on the secondary PCI bus. The bridge drives s_irdy_I when acting as an initiator on the secondary PCI bus and samples s_irdy_I when acting as a target on the secondary PCI bus.                                                                                                                                                                                                                                                                                                                                                                    |

| s_stop_l    | sts  | Secondary PCI interface stop indicator. This signal indicates that the current target is requesting the bus initiator to stop the current transaction on the secondary PCI bus. The bridge drives s_stop_I when acting as a target on the secondary PCI bus and samples s_stop_I when acting as an initiator on the secondary PCI bus.                                                                                                                                                                                                                                                                                                                                                         |

| s_lock_l    | sts  | Secondary PCI interface resource lock. Indicates an atomic operation that may require multiple transactions to complete. The bridge cannot be locked, but it does propagate locks across the bridge. The bridge samples s_lock_I when acting as a target on the secondary PCI bus and may drive s_lock_I when acting as an initiator on the secondary PCI bus on behalf of a master on the primary bus.                                                                                                                                                                                                                                                                                        |

| s_devsel_l  | sts  | Secondary PCI interface device select. Asserted by the bridge through positive decoding of the address on s_ad<31:0>. When it is forwarding a transaction upstream across the bridge. The bridge samples s_devsel_I when it is acting as an initiator on the secondary PCI bus, and expects s_devsel_I to be asserted within five cycles of s_frame_I assertion. Otherwise, the transaction is terminated with a master abort.                                                                                                                                                                                                                                                                 |

| s_par       | ts   | Secondary PCI interface parity. Even parity calculated on 36 bits composed of s_ad<31:0> and s_cbe_l<3:0>. The s_par signal is generated for all address and data phases and is valid one clock cycle after valid data or address is driven on s_ad. The s_par signal is driven and tristated identically to s_ad, except that it is delayed clock cycle. The s_par signal is driven by the bridge when acting as an initiator during address phases and write data phases. The s_par signal is driven by the bridge when acting as a target during read data phases. The s_par signal is sampled as an input during all address phases, and when acting as a target during write data phases. |

| s_serr_l    | I    | Secondary PCI interface system error. Can be pulsed by any device residing on the secondary PCI bus that detects a system error condition. The bridge does not assert s_serr_I as an output. The bridge can be enabled to detect assertion of s_serr_I as an input and cause p_serr_I to assert as a result.                                                                                                                                                                                                                                                                                                                                                                                   |

| s_perr_l    | sts  | Secondary PCI interface parity error detected. Asserted when a data parity error is detected, and corresponds to s_par driven one clock cycle earlier. The bridge asserts s_perr_I when it detects a write data parity error when acting as a target, or a read data parity error when acting as an initiator.                                                                                                                                                                                                                                                                                                                                                                                 |

# 3.3 Secondary Bus Arbiter Signals

The following table describes the secondary bus arbiter signals.

### Table 3-7. Secondary Bus Arbiter Signals

| Signal Name  | Туре | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |