# Pin Descriptions

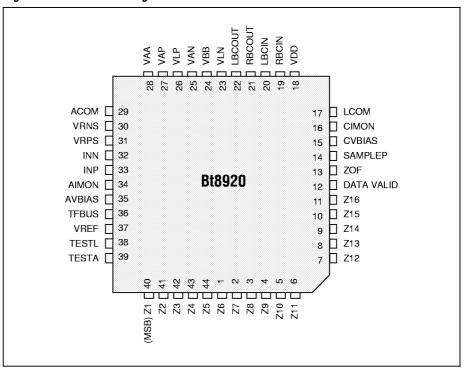

The Bt8920 pin locations are shown in Figure 1 and listed in Table 1. The functional pin assignments are listed in Table 2.

Figure 1. Bt8920 Pin Configuration

Table 1. Bt8920 Pin Assignments

| Pin    | Pin Label                | I/0 <sup>1</sup> | Pin       | Pin Label                  | I/0 <sup>1</sup> | Pin      | Pin Label | I/0 <sup>1</sup> |

|--------|--------------------------|------------------|-----------|----------------------------|------------------|----------|-----------|------------------|

| 1      | Z6                       | 0                | 16        | CIMON                      | Α                | 31       | VRPS      | 0                |

| 2      | Z7                       | 0                | 17        | LCOM                       | Р                | 32       | INN       | А                |

| 3      | Z8                       | 0                | 18        | VDD                        | Р                | 33       | INP       | А                |

| 4      | Z9                       | 0                | 19        | RBCIN                      | А                | 34       | AIMON     | А                |

| 5      | Z10                      | 0                | 20        | LBCIN                      | А                | 35       | AVBIAS    | А                |

| 6      | Z11                      | 0                | 21        | RBCOUT                     | Α                | 36       | TFBUS     | 0                |

| 7      | Z12                      | 0                | 22        | LBCOUT                     | Α                | 37       | VREF      | А                |

| 8      | Z13                      | 0                | 23        | VLN                        | Р                | 38       | TESTL     | ı                |

| 9      | Z14                      | 0                | 24        | VBB                        | Р                | 39       | TESTA     | ı                |

| 10     | Z15                      | 0                | 25        | VAN                        | Р                | 40       | Z1 (MSB)  | 0                |

| 11     | Z16                      | 0                | 26        | VLP                        | Р                | 41       | Z2        | 0                |

| 12     | DATA VALID               | 0                | 27        | VAP                        | Р                | 42       | Z3        | 0                |

| 13     | ZOF                      | 0                | 28        | VAA                        | Р                | 43       | Z4        | 0                |

| 14     | SAMPLEP                  |                  | 29        | ACOM                       | Р                | 44       | Z5        | 0                |

| 15     | CVBIAS                   | Α                | 30        | VRNS                       | 0                |          |           |                  |

| 1. The | e coding used in the I/O | column is        | A: analog | function, O: output, I: ir | put, and P:      | power or | ground.   |                  |

**Table 2. Hardware Signal Definitions** (1 of 2)

| Pin Label  | Signal Name           | I/0 <sup>1</sup> | Definition                                                                                                                                  |

|------------|-----------------------|------------------|---------------------------------------------------------------------------------------------------------------------------------------------|

| Z1:16      | Digital Output Data   | 0                | 16-bit data bus. Z1 = MSB.                                                                                                                  |

| ZOF        | Digital Data Output   | 0                | ADC overflow/underflow bit.                                                                                                                 |

| DATA VALID | Digital Data Output   | 0                | End of conversion bit. Conversion ends on rising edge.                                                                                      |

| SAMPLEP    | Digital Convert Clock | 1                | ADC clock signal. Conversion starts on falling edge.                                                                                        |

| VDD        | Digital Supply        | Р                | Logic power supply.                                                                                                                         |

| LCOM       | Digital Ground        | Р                | Logic ground.                                                                                                                               |

| RBCIN      | Charge Pump           | А                | A 2.2 $\mu\text{F}$ capacitor should be connected between the RBCIN and RBCOUT pins.                                                        |

| LBCIN      | Charge Pump           | A                | A 2.2 $\mu\text{F}$ capacitor should be connected between the LBCIN and LBCOUT pins.                                                        |

| RBCOUT     | Charge Pump           | А                | A 2.2 $\mu\text{F}$ capacitor should be connected between the RBCIN and RBCOUT pins.                                                        |

| LBCOUT     | Charge Pump           | А                | A 2.2 $\mu\text{F}$ capacitor should be connected between the LBCIN and LBCOUT pins.                                                        |

| VLN        | Digital Bypass Low    | Р                | Negative logic supply bypass. A 6.8 $\mu F$ capacitor in parallel with a 0.1 $\mu F$ capacitor to LCOM should be used to decouple this pin. |

Brooktree\*

**Table 2. Hardware Signal Definitions** (2 of 2)

| Pin Label | Signal Name                       | I/0 <sup>1</sup> | Definition                                                                                                                                                                                                  |

|-----------|-----------------------------------|------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| VBB       | Substrate                         | Р                | This pin should be connected to VAN.                                                                                                                                                                        |

| VAN       | Analog Bypass Low                 | Р                | Negative analog supply bypass. A 6.8 $\mu$ F capacitor in parallel with a 0.1 $\mu$ F capacitor to ACOM should be used to decouple this pin. This pin should be isolated from VLN by a 5 $\Omega$ resistor. |

| VLP       | Digital Bypass High               | Р                | Positive logic supply bypass. A 6.8 μF capacitor in parallel with a 0.1 μF capacitor to LCOM should be used to decouple this pin.                                                                           |

| VAP       | Analog Bypass High                | Р                | Positive analog supply bypass. A 6.8 $\mu$ F capacitor in parallel with a 0.1 $\mu$ F capacitor to ACOM should be used to decouple this pin. This pin should be isolated from VLP by a 5 $\Omega$ resistor. |

| VAA       | Analog Supply                     | Р                | A 6.8 $\mu$ F capacitor in parallel with a 0.1 $\mu$ F capacitor to ACOM should be used to decouple this pin. This pin should be isolated from VDD by a 5 $\Omega$ resistor.                                |

| ACOM      | Analog ground                     | Р                | Analog ground.                                                                                                                                                                                              |

| VRNS      | Negative Reference<br>Bypass      | 0                | Flash bypass. A 6.8 μF capacitor in parallel with a 0.1 μF capacitor to ACOM should be used to decouple the end of the flash resistor.                                                                      |

| VRPS      | Positive Reference Bypass         | 0                | Flash bypass. A 6.8 μF capacitor in parallel with a 0.1 μF capacitor to ACOM should be used to decouple the end of the flash resistor.                                                                      |

| INN       | Analog Signal Negative            | Α                | Analog input. INN is the input ground reference.                                                                                                                                                            |

| INP       | Analog Signal Positive            | Α                | Analog input. INP is the analog data signal input.                                                                                                                                                          |

| AIMON     | Amplifier Current Resistor        | Α                | Current monitor resistor. AIMON = 47 $k\Omega$ connected to ACOM.                                                                                                                                           |

| CIMON     | Convert Timing Resistor           | Α                | Current monitor resistor. CIMON = 98 k $\Omega$ for E1, 120 K $\Omega$ for T1, connected to ACOM                                                                                                            |

| AVBIAS    | Analog Bias Decoupling            | Α                | Bias decoupling. A 0.1 $\mu\text{F}$ capacitor should be connected from this pin to ACOM.                                                                                                                   |

| CVBIAS    | Convert Timing Bias<br>Decoupling | Α                | Bias decoupling. A 0.1 $\mu\text{F}$ capacitor should be connected from this pin to ACOM.                                                                                                                   |

| TFBUS     | Factory Test Pin                  | 0                | Test pin. This pin should be left unconnected.                                                                                                                                                              |

| VREF      | Voltage Reference                 | Α                | Voltage reference decoupling. This is a low current pin not intended to drive external circuits.                                                                                                            |

| TESTA     | Factory Test Pin                  | I                | This pin should be connected LCOM.                                                                                                                                                                          |

| TESTL     | Factory Test Pin                  | ı                | This pin should be connected LCOM.                                                                                                                                                                          |

Brooktree<sup>®</sup> 3

## **Functional Description**

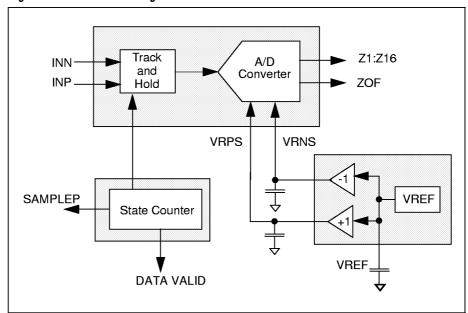

A block diagram for the Bt8920 is shown in Figure 2.

Figure 2. Bt8920 Block Diagram

The SAMPLEP pin initializes the ADC and starts the conversion cycle. The analog input is fed to an on-chip track and hold (T/H) which holds the analog signal on the falling edge of SAMPLEP. DATA VALID goes low at the commencement of the conversion cycle, and goes high when the conversion is complete. The digital data is then output. The T/H goes into the track mode as soon as DATA VALID goes high. The output of the ADC is offset binary (see Table 3 below). All internal supplies and references are derived from an externally supplied +5V and GND.

Table 3. Bt8920 Digital Output Code

| Analog Input | Digital Code        |

|--------------|---------------------|

| +VRPS        | 1111 1111 1111 1111 |

| VCEN         | 1000 0000 0000 0000 |

| -VRNS        | 0000 0000 0000 0000 |

4 Brooktree®

#### **Applications**

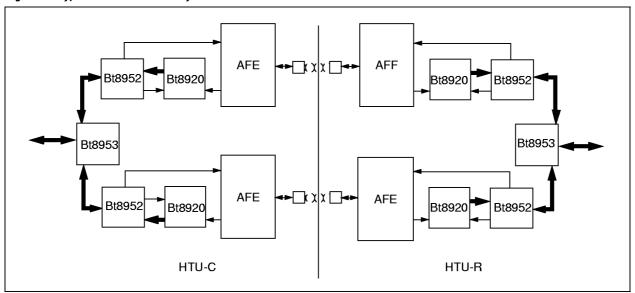

The Bt8920 is primarily intended for use in communications. Figure 3 shows a typical configuration for use with the Bt8952 and Bt8953 in an HDSL application.

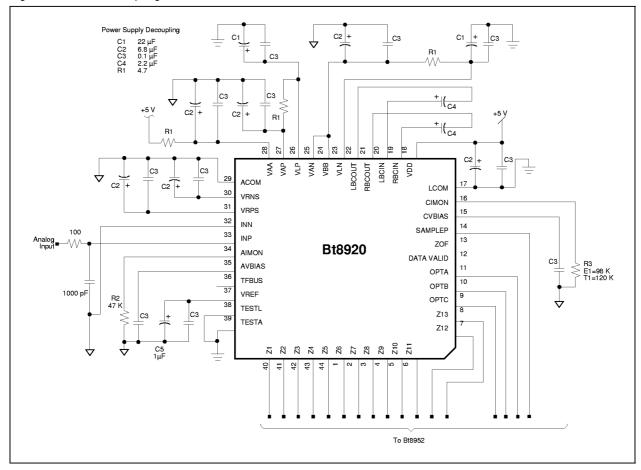

Some important layout considerations are required to obtain the maximum performance from the Bt8920 (see Figure 4). Due to the high resolution of the part, and the combination of on-board power supply and reference generation, adequate power supply decoupling is essential. It is recommended that all the power pins be decoupled by a 6.8  $\mu F$  tantalum capacitor in parallel with a 0.1  $\mu F$  ceramic capacitor. The on-board analog power supplies, VAP and VAN, should be isolated from their digital counterparts, VLP and VLN, by a small series resistor of nominally 5  $\Omega$ . Also the analog power supply VAA should be isolated from VDD by a 5  $\Omega$  resistor. To minimize digital cross talk to the analog signal, it is recommended that separate ground planes be used for ACOM and LCOM. A short connection between the two ground planes should be made under the Bt8920 connecting the ACOM pin directly to the LCOM pin, thus ensuring there are no DC offsets between the two grounds.

Figure 3. Typical HDSL Two-Pair System

Figure 4. Bt8920 Decoupling

The output of the reference generator, VREF, has minimal drive capability and should not be used without buffering as a reference for any external circuits. A 1  $\mu F$  tantalum capacitor in parallel with a 0.1  $\mu F$  ceramic capacitor should be used to decouple this pin.

Due to the nature of the analog input, it is desirable to isolate it from the preceding analog stage. This can be accomplished with a simple RC filter of 100  $\Omega$  and 1000 pF in series with the analog input.

The current control resistor, CIMON, controls the speed of conversion. To obtain optimum performance this resistor should be set to the recommended value (121 k $\Omega$  for 400 ksps, 97.6 k $\Omega$  for 600 ksps).

Brooktree\*

#### Absolute Maximum Ratings

Table 4. Bt8920 Absolute Maximum Ratings

| Parameter             | Symbol                           | Value            | Unit |

|-----------------------|----------------------------------|------------------|------|

| Supply Voltage        | V <sub>AA</sub> /V <sub>DD</sub> | -0.3 to +7.0     | V    |

| Digital Input Voltage | V <sub>IH</sub> /V <sub>IL</sub> | -0.5 to VDD +0.5 | V    |

| Analog Input Voltage  |                                  | ±3.0             | V    |

| Operating Temperature | TA                               | -40 to +85       | °C   |

| Storage Temperature   | T <sub>STG</sub>                 | -55 to +150      | °C   |

| Vapor Phase Soldering | T <sub>VSOL</sub>                | 220              | °C   |

Stresses above those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. This is a stress rating only and functional operation of the device at these or any other conditions above those listed in the operational sections of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability. This device employs high-impedance CMOS devices on all signal pins. It should be handled as an ESD-sensitive device. Voltage on any signal pin that exceeds the power supply voltage by more than +0.5 V can induce destructive latchup.

#### **Recommended Operating Conditions**

Table 5. Bt8920 Recommended Operating Ratings

| Parameter                     | Symbol                           | Min                     | Тур | Max                     | Symbol  |

|-------------------------------|----------------------------------|-------------------------|-----|-------------------------|---------|

| Power Supply                  | V <sub>AA</sub> /V <sub>DD</sub> | 4.75                    | 5   | 5.25                    | V       |

| Analog Signal Input           | INP<br>INN                       | V <sub>RNS</sub><br>-10 | 0   | V <sub>RPS</sub><br>+10 | V<br>mV |

| Ambient Operating Temperature | T <sub>A</sub>                   | -40                     |     | +85                     | °C      |

#### **DC Characteristics**

Table 6. Bt8920 DC Specification

| Parameter                              | Symbol           | Min                  | Тур  | Max                 | Units        |

|----------------------------------------|------------------|----------------------|------|---------------------|--------------|

| A/D Resolution                         |                  | 16                   |      |                     | Bits         |

| A/D Accuracy                           | 1                |                      |      |                     | I            |

| Integral Linearity                     | IL               |                      |      | ±1.0                | LSB@ 13 bits |

| Differential Linearity                 | DL               |                      |      | ±0.8                | LSB@ 13 bits |

| Gain Error                             |                  |                      |      | tbd                 | dB           |

| Analog Input                           |                  |                      |      |                     |              |

| DC Input Impedance                     | R <sub>IN</sub>  |                      | 100  |                     | MΩ           |

| Input Capacitance                      | C <sub>IN</sub>  |                      | 80   |                     | pF           |

| Voltage Reference Outputs              |                  |                      |      |                     |              |

| Reference Voltage                      | V <sub>REF</sub> | 1.65                 | 1.75 | 1.90                | ٧            |

| Positive Reference Bypass              | V <sub>RPS</sub> | 1.65                 |      | 1.90                | ٧            |

| Negative Reference Bypass              | V <sub>RNS</sub> | -1.90                |      | -1.65               | ٧            |

| Mid Range Voltage                      | V <sub>CEN</sub> | tbd                  | 0    | tbd                 | ٧            |

| Analog Bypass High                     | V <sub>AP</sub>  |                      | 2.9  |                     | ٧            |

| Analog Bypass Low                      | V <sub>AN</sub>  |                      | -2.9 |                     | V            |

| Digital Bypass High                    | V <sub>LP</sub>  |                      | 2.9  |                     | V            |

| Digital Bypass Low                     | V <sub>LN</sub>  |                      | -2.9 |                     | ٧            |

| Substrate Bypass                       | V <sub>BB</sub>  |                      | -2.9 |                     | ٧            |

| Digital Input                          |                  |                      |      |                     |              |

| Input High Voltage                     | V <sub>IH</sub>  | 0.8xV <sub>DD</sub>  |      |                     | V            |

| Input Low Voltage                      | V <sub>IL</sub>  |                      |      | 0.2xV <sub>DD</sub> | V            |

| Input High Leakage                     | I <sub>IH</sub>  |                      | 1.0  |                     | μΑ           |

| Input Low Leakage                      | I <sub>IL</sub>  |                      | -1.0 |                     | μА           |

| Input Capacitance                      | C <sub>IN</sub>  |                      | 3    |                     | pF           |

| Digital Outputs                        |                  |                      |      |                     |              |

| Output High Voltage<br>(IOH = -400 μA) | V <sub>OH</sub>  | V <sub>DD</sub> -0.8 |      |                     | V            |

| Output Low Voltage<br>IOL = 400 μA)    | V <sub>OL</sub>  |                      |      | 0.4                 | V            |

| Power Supply Current                   | 1                |                      |      | 60                  | mA           |

| Power Dissipation                      |                  |                      | 250  |                     | mW           |

#### AC Characteristics

Table 7. Bt8920 AC Specifications

| <b>Max</b><br>-75 | Min      | Тур | Max        | Units    |

|-------------------|----------|-----|------------|----------|

| <b>–</b> 75       |          |     |            |          |

| -58               |          |     | -75<br>-58 | dB<br>dB |

| 0.02              |          |     | 0.02       | %        |

|                   | 70<br>38 |     |            | dB<br>dB |

|                   | 0.02     | 70  | 70         | 70       |

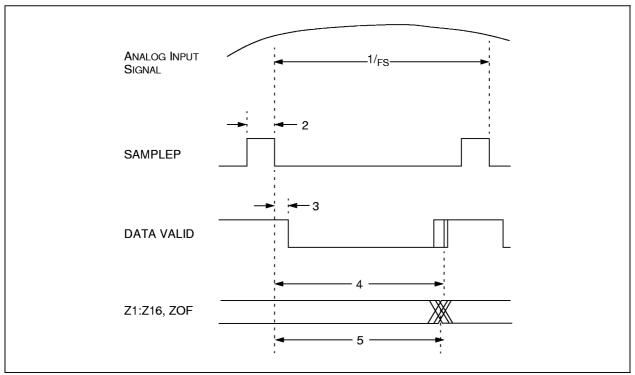

## **Switching Characteristics**

Table 8. ADC Timing Specifications

|   |                                  |                      | Bt8920EPJ<br>(400 ksps) <sup>1</sup> |     |     | Bt8920EPJ600<br>(600 ksps) <sup>1</sup> |     |     |       |

|---|----------------------------------|----------------------|--------------------------------------|-----|-----|-----------------------------------------|-----|-----|-------|

| % | Parameter                        | Symbol               | Min                                  | Тур | Max | Min                                     | Тур | Max | Units |

| 1 | Conversion Rate                  | Fs                   |                                      |     | 392 |                                         |     | 584 | ksps  |

| 2 | SAMPLEP Pulse Width High         | tpw(H) <sub>SP</sub> | 100                                  |     | 200 | 100                                     |     | 160 | ns    |

| 3 | SAMPLEP Low to Data Valid<br>Low | tp                   |                                      | 60  |     |                                         | 60  |     | ns    |

| 4 | Convert Time                     | t <sub>C</sub>       | 1.0                                  |     | 2.3 | 1.0                                     |     | 1.6 | μs    |

| 5 | SAMPLEP Low to Data Out          | t <sub>D</sub>       | 1.0                                  |     | 2.2 | 1.0                                     |     | 1.5 | μs    |

|   | Aperture Jitter                  | t <sub>AJ</sub>      |                                      | 10  |     |                                         | 10  |     | ps    |

For 600 ksps timing AIMON = 47 k $\Omega$ , CIMON = 97.6 k $\Omega$  (1%)

Figure 5. ADC Timing

Brooktree\* 10

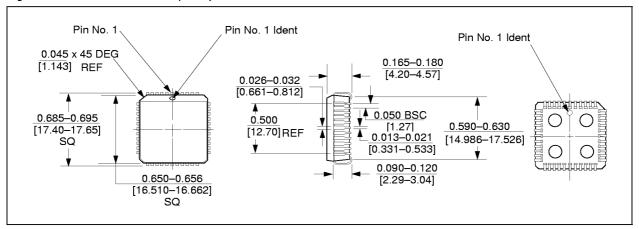

### Package Drawing

Figure 6. 44-Pin Plastic J-Lead (PLCC)

Notes—Unless otherwise specified:

- 1. Dimensions are in inches [milimeters]

- 2. Controlled dimensions are in inches