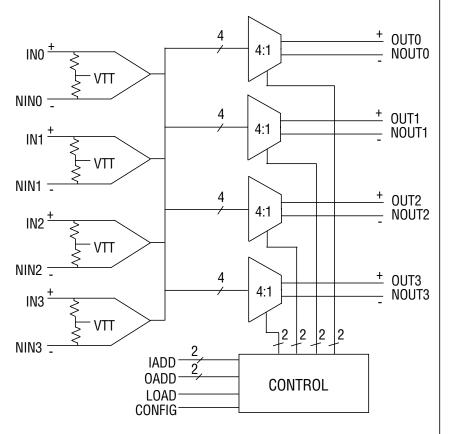

The TQ8004 is a non-blocking 4 X 4 digital crosspoint switch capable of data rates greater than 2.7 Gigabits per second per port. Utilizing a fully differential data path from input to output, the TQ8004 offers a high data rate with exceptional fidelity. The symmetrical switching and noise rejection characteristics inherent in differential logic result in low jitter, low crosstalk and minimum signal skew. The TQ8004 is ideal for high speed data switching applications, as well as high fidelity buffering or protection switching.

The non-blocking architecture uses 4 fully independent 4:1 multiplexers, allowing each input port to be independently programmed to any output port.

# TQ8004

# 2.7 Gbit/sec 3.3V 4x4 Digital Crosspoint Switch

#### Features

- 2.7 Gb/s port data bandwidth

- Single 3.3V power supply

- · Fully differential data path

- Non-blocking architecture

- Differential PECL I/O TTL control inputs

- On-chip input termination

- Low jitter and channel to channel signal skew

- Double configuration latches

- Small 28-pin TSSOP package

### **Applications**

- Telecom/Datacom/Video switching

- Fanout buffering

- Protection Switching

#### TQ8004

# Circuit Description

#### **Data inputs**

The 4 input channels are differential PECL compatible, referenced to VDD = 3.3V power supply (LVPECL). All LVPECL inputs have on-chip 50 Ohm termination to VTT.

For AC coupled designs an internal bias generator can be used to supply the VTT voltage. An on-chip voltage divider generates the VTT voltage at VDD-1.3V with an impedance of 800 Ohms. Due to the high impedance of the internal VTT source it is suited only for AC coupled input schemes.

For DC coupled designs VTT needs to be externally supplied, nominally at VDD-2.0V for LVPECL systems. Note that the external source needs to be able to sink current.

If any inputs are unused, terminate one side of any unused input pair to GND through a 500 Ohm or smaller resistor. This will prevent unwanted oscillations.

#### **Data outputs**

The 4 output channels are differential PECL and are designed to be terminated through 50 Ohm to VDD-2.0V. Unused outputs can be left unterminated.

#### **Control** inputs

The control inputs are TTL compatible. Unconnected inputs will default to a logic HI level.

#### Switch configuration

The switch is configured by programming each output to a specific input. Each of the 4 output channels have two sets of program store latches. The first, or program latch, stores a new input configuration prior to application to the switch core. The second, or

configuration latch, stores the current input configuration which is applied to the switch core. The use of two sets of program storage latches allows for a new set of input configurations to be loaded simultaneously without disturbing the existing configuration.

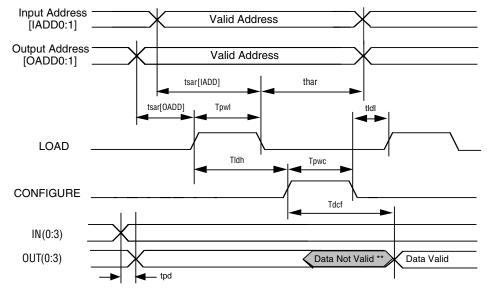

The address of the desired output is applied to OADD(0:1). The input address is applied to IADD(0:1). The input address defines which input port connects to the selected output port. The new configuration is loaded into the program latches by asserting the LOAD signal high and is latched when LOAD is de-asserted.

The process is repeated for each new output port configuration. Only the output ports which are to receive a new input port configuration need to be programmed in this manner. The new configurations are not applied to the switch core at this time.

After all of the new configurations have been loaded into the program latches, the CONFIGURE input is asserted high and the data in the program latches is loaded into the configuration latches. The data is latched when CONFIGURE is de-asserted. Data integrity is maintained on output ports not receiving a new configuration

The switch core receives the new configuration immediately following the assertion of CONFIGURE. The integrity of the data on any re-configured output port is unknown for a period  $t_{dcf}$  from the time CONFIGURE is asserted.

The LOAD and CONFIGURE inputs can be asserted simultaneously. In this mode, the new configuration will be applied to the switch when LOAD is asserted.

Summary of the IADD(0:1) and OADD(0:1):

| IADD1 | IADD0 | Input | OADD1 OADD0 Output |  |

|-------|-------|-------|--------------------|--|

| 0     | 0     | INO   | 0 0 OUTO           |  |

| 0     | 1     | IN1   | 0 1 OUT1           |  |

| 1     | 0     | IN2   | 1 0 OUT2           |  |

| 1     | 1     | IN3   | 1 1 0UT3           |  |

### **Specifications**

Specifications subject to change without notice

Table 1. Absolute Maximum Ratings<sup>4</sup>

| Parameter                       | Condition | Symbol             | Minimum | Nominal | Maximum               | Unit |

|---------------------------------|-----------|--------------------|---------|---------|-----------------------|------|

| Storage Temperature             |           | T <sub>store</sub> | -65     |         | 150                   | °C   |

| Junction Temperature            |           | T <sub>CH</sub>    | -65     |         | 150                   | °C   |

| Case Temperature w/bias         | (1)       | T <sub>C</sub>     | 0       |         | 100                   | °C   |

| Supply Voltage                  | (2)       | $V_{DD}$           | 0       |         | 5.5                   | V    |

| Voltage to any input            | (2)       | V <sub>in</sub>    | -0.5    |         | V <sub>DD</sub> + 0.5 | V    |

| Voltage to any output           | (2)       | V <sub>out</sub>   | -0.5    |         | V <sub>DD</sub> + 0.5 | V    |

| Current to any LVTTL input      | (2)       | l <sub>in</sub>    | -1.0    |         | 1.0                   | mA   |

| Current to any LVPECL input     | (2)       | l <sub>in</sub>    | -65     |         | 65                    | mA   |

| Current from any output         | (2)       | l <sub>out</sub>   |         |         | 40.0                  | mA   |

| Power Dissipation of output (3) |           | P <sub>out</sub>   |         |         | 50.0                  | mW   |

Notes: 1. Tc is measured at case top.

<sup>2.</sup> All voltages are measured with respect to GND (OV) and are continuous.

<sup>3.</sup> Pout =  $(V_{DD} - V_{out}) \times I_{out}$ .

<sup>4.</sup> Absolute maximum ratings, as detailed in this table, are the ratings beyond which the device's performance may be impaired and/or permanent damage to the device may occur.

### TQ8004

Table 2. Recommended Operating Conditions 3

| Symbol            | Parameter                              | Min  | Тур                   | Max  | Units | Notes |

|-------------------|----------------------------------------|------|-----------------------|------|-------|-------|

| T <sub>A</sub>    | Operating Temperature                  | 0    | _                     | 85   | °C    | 1     |

| $V_{DD}$          | Supply Voltage                         | 3.14 | _                     | 3.47 | V     |       |

| I <sub>DD</sub>   | Current Positive Supply                |      |                       | 300  |       | mA    |

| V <sub>TT</sub>   | Load Termination Supply Voltage        |      | V <sub>DD</sub> – 2.0 |      | V     | 2     |

| R <sub>LOAD</sub> | Output Termination Load Resistance     |      | 50                    |      | Ω     | 2     |

| $\Theta_{JA}$     | Thermal Resistance Junction to Ambient |      | 40                    |      |       | °C/W  |

Notes: 1. Package thermal pad to be soldered to PCB.

Table 3. DC Characteristics—PECL I/O <sup>3</sup>

| Parameter                           | Condition | Symbol             | Minimum               | Nominal | Maximum                | Unit |

|-------------------------------------|-----------|--------------------|-----------------------|---------|------------------------|------|

| Input common mode voltage range     |           | V <sub>ICOM</sub>  | $V_{DD} - 1500$       | _       | $V_{DD} - 1100$        | mV   |

| Input differential voltage (pk-pk)  | (1)       | V <sub>IDIFF</sub> | 600                   | _       | 2400                   | mV   |

| Output common mode voltage range    | 1         | V <sub>OCOM</sub>  | V <sub>DD</sub> -1500 | _       | V <sub>DD</sub> – 1100 | mV   |

| Output differential voltage (pk-pk) | (1,2)     | V <sub>ODIFF</sub> | 1200                  | _       | 2400                   | mV   |

| Input termination resistance        |           | R <sub>IN</sub>    |                       | 50      |                        | Ohm  |

| Input capacitance                   |           | C <sub>IN</sub>    | _                     | 2.5     | _                      | pF   |

| Output capacitance                  |           | $C_OUT$            | _                     | 2.5     | _                      | pF   |

| ESD breakdown rating                |           | V <sub>ESD</sub>   | 1000                  | _       | _                      | V    |

Table 4. DC Characteristics—TTL Inputs<sup>3</sup>

| Parameter            | Condition            | Symbol           | Minimum | Nominal | Maximum  | Unit |

|----------------------|----------------------|------------------|---------|---------|----------|------|

| Input HIGH voltage   |                      | $V_{IH}$         | 2.0     | _       | $V_{DD}$ | V    |

| Input LOW voltage    |                      | V <sub>IL</sub>  | 0       | _       | 0.8      | V    |

| Input HIGH current   | V <sub>IH(MAX)</sub> | I <sub>IH</sub>  | _       | _       | 200      | uA   |

| Input LOW current    | V <sub>IL(MIN)</sub> | I <sub>IL</sub>  | -400    | -200    | _        | uA   |

| Input capacitance    |                      | C <sub>IN</sub>  | _       | 2.5     | _        | pF   |

| ESD breakdown rating |                      | V <sub>ESD</sub> | 1000    | _       | _        | V    |

Notes (Tables 3 and 4):

<sup>2.</sup> The  $V_{TT}$  and  $R_{LOAD}$  combination is subject to maximum output current and power restrictions. Note that the value shown is for DC coupled LVPECL I/O.

<sup>3.</sup> Functionality and/or adherence to electrical specifications is not implied when the device is subjected to conditions that exceed, singularly or in combination, the operating range specified.

<sup>1.</sup> Differential Input Peak-Peak = 2| Vin - NVin |

<sup>2.</sup>  $R_{LOAD} = 50$  ohms to  $V_{TT} = V_{DD} - 2.0V$ .

<sup>3.</sup> Specifications apply over recommended operating ranges.

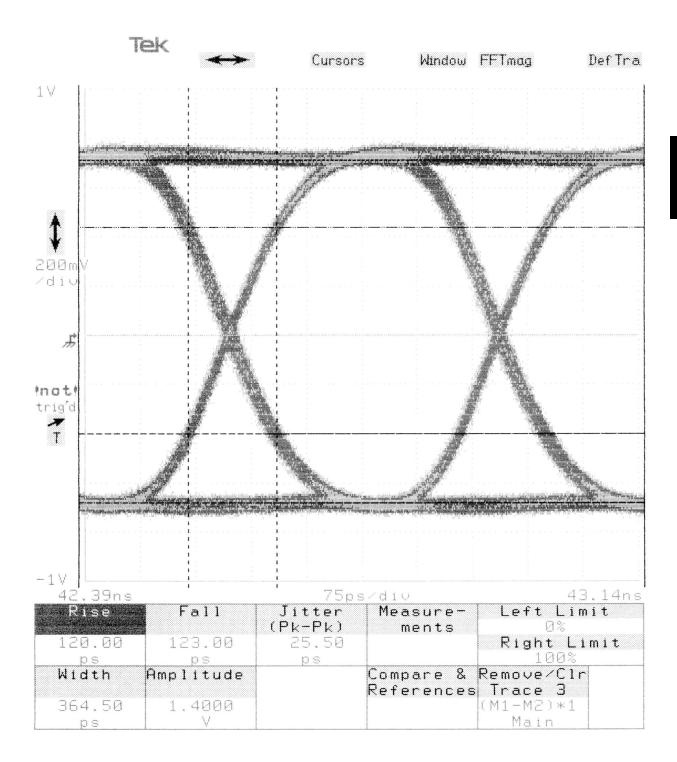

Table 5. AC Characteristics

| Parameter                 | Condition | Symbol              | Minimum | Nominal | Maximum | Unit |

|---------------------------|-----------|---------------------|---------|---------|---------|------|

| Maximum Data Rate/port    |           |                     | 2.7     |         |         | Gb/s |

| Minimum Input pulse width | (1)       | T <sub>pw</sub>     | 370     | _       | _       | ps   |

| Rise/Fall time 20-80%     |           | T <sub>r/f</sub>    | _       | _       | 150     | ps   |

| Channel Propagation Delay | (1)       | T <sub>pd</sub>     | _       | _       | 1.0     | ns   |

| Ch-to-Ch Prop. Delay Skew | (1)       | T <sub>skew</sub>   |         | 100     |         | ps   |

| Jitter (pk-pk)            | (2)       | T <sub>jitter</sub> | _       | 25      | _       | ps   |

Notes: 1. Measured at crossing point of true and complement 2. Crossing of (On) - (NOn) measured with  $2^{23} - 1$  PRBS, measured over extended time.

Figure 1. Timing Diagram

<sup>\*\*</sup> Data remains valid on outputs with unchanged configurations

Table 6. Timing Specifications

| Symbol           | Parameter                   | Minimum | Maximum | Unit |

|------------------|-----------------------------|---------|---------|------|

| t <sub>sar</sub> | Address to Load Set-up time | 2       |         | ns   |

| t <sub>har</sub> | Address to Load Hold Time   | 2       |         | ns   |

| t <sub>pwl</sub> | Min. Load pulse width       | 5       |         | ns   |

| t <sub>ldh</sub> | Load to Configure delay     | 0       |         | ns   |

| t <sub>idi</sub> | Configure to Load delay     | 2       |         | ns   |

| t <sub>pwc</sub> | Min. Configure pulse width  | 5       |         | ns   |

| t <sub>dcf</sub> | Configure to Data Valid     |         | 20      | ns   |

# TQ8004

Table 7. TQ8004 Pin Descriptions

| Signal            | Type Pin Number   |        | Description                                                |  |  |

|-------------------|-------------------|--------|------------------------------------------------------------|--|--|

| Control and Confi |                   |        |                                                            |  |  |

| CONFIGURE         | TTL Input         | 17     | Active High. Enables transfer of data from program latches |  |  |

|                   |                   |        | to configuration latches.                                  |  |  |

| LOAD              | TTL Input         | 16     | Active High. Enables program latches to accept new input   |  |  |

|                   |                   |        | address based upon which output is selected using          |  |  |

|                   |                   |        | OADD inputs. Latches address data on de-assertion.         |  |  |

| Input Address Co  |                   |        |                                                            |  |  |

| IADD0             | TTL Input         | 27     | Input address LSB                                          |  |  |

| IADD1             | TTL Input         | 28     | Input address MSB                                          |  |  |

| Output Address C  | ontrol            |        |                                                            |  |  |

| OADD0             | TTL Input         | 14     | Output address LSB                                         |  |  |

| OADD1             | TTL Input         | 13     | Output address MSB                                         |  |  |

| Output Ports      |                   |        |                                                            |  |  |

| OUTO,NOUTO        | DPECL Output      | 19,18  | True and Complement Differential PECL Data Out             |  |  |

|                   |                   |        | Addressed by $OADD(0:1) = 00$                              |  |  |

| OUT1,NOUT1        | DPECL Output      | 21,20  | True and Complement DPECL Data Out                         |  |  |

|                   |                   |        | Addressed by $OADD(0:1) = 01$                              |  |  |

| OUT2,NOUT2        | DPECL Output      | 23,22  | True and Complement DPECL Data Out                         |  |  |

|                   |                   |        | Addressed by $OADD(0:1) = 10$                              |  |  |

| OUT3,NOUT3        | DPECL Output      | 25,24  | True and Complement DPECL Data Out                         |  |  |

|                   |                   |        | Addressed by $OADD(0:1) = 11$                              |  |  |

| Input Ports       |                   |        |                                                            |  |  |

| INO,NINO          | DPECL Input       | 10,11  | True and Complement DPECL Data In.                         |  |  |

|                   |                   |        | Addressed by $IADD(0:1) = 00$                              |  |  |

| IN1,NIN1          | DPECL Input       | 8,9    | True and Complement DPECL Data In                          |  |  |

|                   |                   |        | Addressed by $IADD(0:1) = 01$                              |  |  |

| IN2,NIN2          | DPECL Input       | 6,7    | True and Complement DPECL Data In                          |  |  |

|                   | •                 |        | Addressed by $IADD(0:1) = 10$                              |  |  |

| IN3,NIN3          | DPECL Input       | 4,5    | True and Complement DPECL Data In                          |  |  |

|                   | •                 |        | Addressed by $IADD(0:1) = 11$                              |  |  |

| Power Pins        |                   |        |                                                            |  |  |

| Signal            | Description       |        | Pin Number                                                 |  |  |

| VTT               | Input Termination | Supply | 2                                                          |  |  |

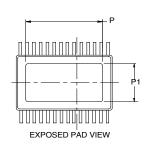

| VDD               | +3.3V Power Supp  | oly    | 1, 15, 26, Package Down Paddle (required)                  |  |  |

| GND               | Ground Supply     |        | 3, 12                                                      |  |  |

Figure 2. Typical Output Eye with 2<sup>23</sup>-1 PRBS data at 2.7 Gb/s

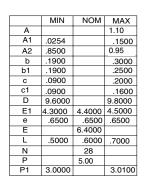

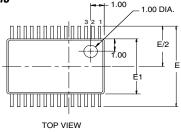

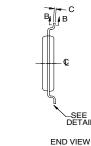

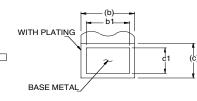

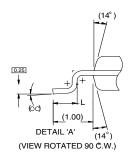

Figure 3. TSSOP Mechanical Dimensions

Note: All dimensions in millimeters (mm).

SEATING PLANE

SECTION "B-B"

\_SEE DETAIL "A"

Moisture Level Rating 3 per

JEDEC Standard J-STD-020A

SIDE VIEW

### **Ordering Information**

## T08004

## 2.7Gbit/sec 4x4 Crosspoint Switch

#### Additional Information

For latest specifications, additional product information, worldwide sales and distribution locations, and information about TriQuint:

Web: www.triquint.com Tel: (503) 615-9000 Email: sales@tqs.com Fax: (503) 615-8900

For technical questions and additional information on specific applications:

#### Email: applications@tqs.com

The information provided herein is believed to be reliable; TriQuint assumes no liability for inaccuracies or omissions. TriQuint assumes no responsibility for the use of this information, and all such information shall be entirely at the user's own risk. Prices and specifications are subject to change without notice. No patent rights or licenses to any of the circuits described herein are implied or granted to any third party. TriQuint does not authorize or warrant any TriQuint product for use in life-support devices and/or systems.

Copyright © 2001 TriQuint Semiconductor, Inc. All rights reserved.

Revision 1.0.A May 2001