# What Does It Do?

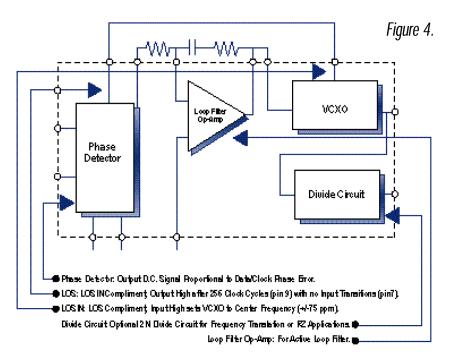

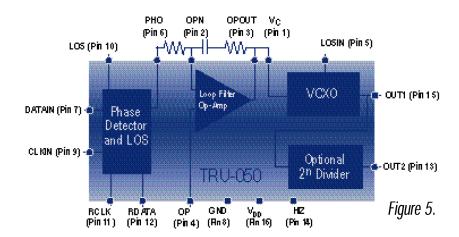

Vectron International's TRU-050 module is a user-configured, phase-locked loop (PLL) solution designed to simplify a wide variety of clock recovery and data retiming, frequency translation and clock smoothing applications. The device features a phase-lock loop ASIC with a quartz stabilized VCXO for superior stability and jitter performance. This highly integrated module provides unsurpassed performance, reliability and quality. The proprietary ASIC device includes a refined Phase Detector, a Loop Filter Op-Amp, a Loss of Signal Alarm with Clock Return to Nominal feature, a VCXO circuit, and an optional 2<sup>n</sup> divided output.

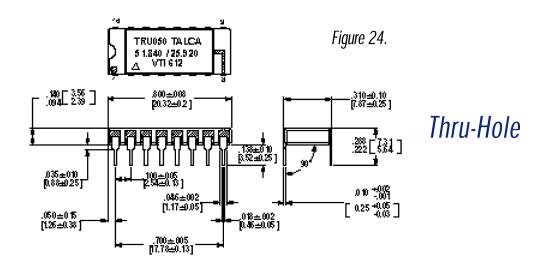

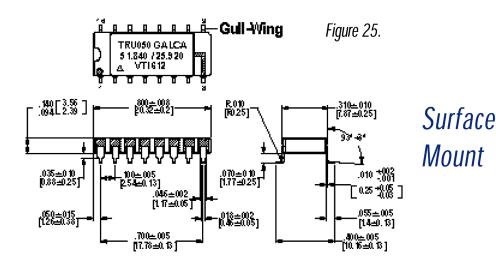

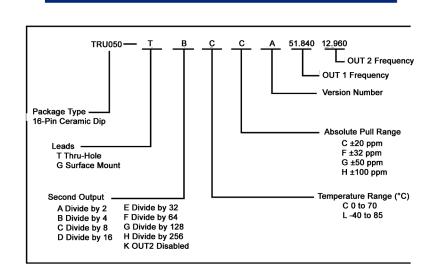

The ASIC and quartz resonator are housed in a hermetic 16-pin DIL ceramic package with optional thru-hole or surface mount leads. The VCXO frequency (OUT1) and division factor (OUT2) are factory set in accordance with customer specifications. PLL response is optimized for each application by the selection of three external passive components. Software is available from Vectron to aid in loop filter component selection and loop response modeling.

#### Features:

PLL with quartz stabilized VCXO

Output jitter less than 20 ps

Loss of signal (LOS) alarm

Return to nominal clock upon LOS

Input data rates from 8 kb/s to 65 Mb/s

Surface mount option

Tri-state output

User defined PLL loop response

NRZ data compatible

Robust hermetic ceramic package

Single or +5.0 V supply (+3.3V option available)

#### Benefits:

Flexible modular solution

Reduce design time

Increase circuit reliability

Less board space

Reduces component count

# What is the main benefit of the TRU-050?

It's a single drop-in Quartz Stabilized PLL solution.

#### What's Inside?

What Does It Do? Pages 3-5

How Is It Built? Pages 6-11

How Does It Perform? Pages 12-14

How Is It Used? Pages 15-18

How Is It Packaged? How Is It Ordered? Page 19

- 1. For input RZ data, Manchester encoded data, and input clock recovery applications, the output clock must run at two times the input rate to ensure that the input is clocked correctly. Since the output clock has a maximum frequency of 65.536 MHz, these inputs are limited to a maximum rate of 32.768 MHz.

- 2. OUT2 is a binary submultiple of OUT1, or it may be disabled.

- 3. A 3.3 volt supply option is also available.

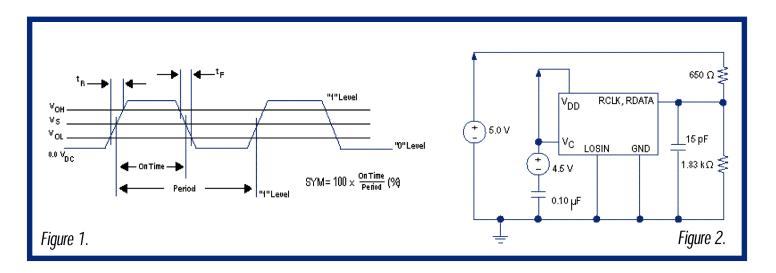

- 4. Figure 1 defines these parameters. Figure 2 illustrates the equivalent five-gate MTTL load and operating conditions under which these parameters are specified and tested.

- 5. Symmetry is the ON TIME/PERIOD in percent with  $V_S = 1.4 \text{ V}$  for TTL, per figure 1.

- 6. A loss of signal (LOS) indicator is set to a logic high if no transitions are detected at DATAIN after 256 clock cycles. As soon as a transition occurs at DATAIN, LOS is set to a logic low.

- 7. Accuracy at room temperature. Stability over temperature is typically ± 20 ppm.

| Parameter                                                | Symbol             | Min                  | Max     | Unit          |

|----------------------------------------------------------|--------------------|----------------------|---------|---------------|

| Input NRZ Data Rates                                     | DATAIN             | 0.008                | 65.536  | MHz           |

| Input RZ Data and Clock Rates <sup>1</sup>               | DATAIN             | 0.008                | 32.768  | MHz           |

| Nominal Output Frequency                                 |                    |                      |         |               |

| Output 1                                                 | OUT1               | 12.0                 | 65.536  | MHz           |

| Output 2 <sup>2</sup>                                    | OUT2               | 0.05                 | 32.768  | MHz           |

| Supply Voltage <sup>3</sup>                              | V <sub>DD</sub>    | 4.5                  | 5.5     | V             |

| Supply Current (V <sub>DD</sub> = 5.5 V)                 | I <sub>DD</sub>    | 25                   | 63      | mА            |

| Output Voltage Levels (V <sub>DD</sub> = 4.5 V)          |                    |                      |         |               |

| Output Logic High <sup>4</sup>                           | v <sub>oh</sub>    | 2.5                  |         | V             |

| Output Logic Low <sup>4</sup>                            | v <sub>OL</sub>    | -                    | 0.5     | V             |

| Transition Times: <sup>4</sup>                           |                    |                      |         |               |

| Rise Time (0.5 V to 2.5 V)                               | t <sub>R</sub>     | 0.5                  | 5       | ns            |

| Fall Time (2.5 V to 0.5 V)                               | t <sub>F</sub>     | 0.5                  | 5       | ns            |

| Symmetry or Duty cycle <sup>5</sup>                      |                    |                      |         |               |

| Output 1                                                 | SYM 1              | 40                   | 60      | %             |

| Output 2                                                 | SYM 2              | 45                   | 55      | %             |

| Recovered Clock                                          | R <sub>CLK</sub>   | 40                   | 60      | %             |

| Input Data                                               |                    |                      |         |               |

| Input Logic High                                         | $v_{IH}$           | 2.0                  |         | V             |

| Input Logic Low                                          | $v_{IL}$           | -                    | 0.8     | V             |

| Control Voltage Bandwith (-3 dB, VC = 2.50 V)            | BW                 | 50                   |         | kHz           |

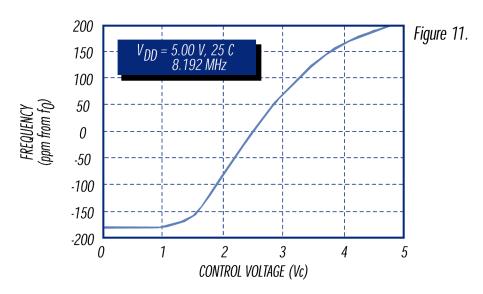

| Sensitivity @ VC = VO                                    | ΔF/ΔV <sub>C</sub> | See Fig              | ure 11. | ppm/V         |

| Loss of Signal Indication <sup>6</sup>                   | LOS                |                      |         |               |

| Output Logic High                                        | v <sub>OH</sub>    | 2.5                  |         | V             |

| Output Logic Low                                         | $v_{OL}$           | -                    | 0.5     | V             |

| Nominal Output Frequency on Loss of Signal: <sup>7</sup> |                    |                      |         |               |

| Output 1                                                 | OUT1               | -75 ppm              | 75 ppm  | ppm from fo 1 |

| Output 2                                                 | OUT2               | -75 ppm              | 75 ppm  | ppm from fo 2 |

| Phase Detector Gain                                      | K <sub>D</sub>     | -0.53 x Data Density |         | V/rad         |

Table 1.

| Pin | Symbol            | Function                                                                                                                                                                                                                                                                    |  |  |

|-----|-------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| 1   | $v_{\mathcal{C}}$ | Control voltage input to internal voltage controlled crystal oscillator (VCXO).                                                                                                                                                                                             |  |  |

| 2   | OPN               | Negative input terminal to internal operational amplifier.                                                                                                                                                                                                                  |  |  |

| 3   | ОРОИТ             | Output terminal of internal operational amplifier.                                                                                                                                                                                                                          |  |  |

| 4   | OPP               | Positive input terminal to internal operational amplifier.                                                                                                                                                                                                                  |  |  |

| 5   | LOSIN             | With LOSIN set to a logic high, the external input to the VCXO (VC) is disabled and the VCXO returns to it's nominal center frequency. With LOSIN set to logic low, the external input to the VCXO is enabled. The LOSIN input has an internal pull-down resistor.          |  |  |

| 6   | PHO PHO           | Output signal produced by phase detector.                                                                                                                                                                                                                                   |  |  |

| 7   | DATAIN            | Input data stream to phase detector (TLL switching thresholds).                                                                                                                                                                                                             |  |  |

| 8   | GND               | Circuit and cover ground.                                                                                                                                                                                                                                                   |  |  |

| 9   | CLKIN             | Input clock signal to phase detector (TTL switching thresholds).                                                                                                                                                                                                            |  |  |

| 10  | LOS               | Loss of signal indicator is set to a logic high if no transitions are<br>detected at DATAIN after 256 clock cycles. As soon as a transition<br>occurs at DATAIN, LOS is set to a logic low.                                                                                 |  |  |

| 11  | RCLK              | ΠL compatible recovered clock.                                                                                                                                                                                                                                              |  |  |

| 12  | RDATA             | ΠL compatible recovered data stream.                                                                                                                                                                                                                                        |  |  |

| 13  | ОИТ2              | Divided version of internal VCXO output clock (TTL).                                                                                                                                                                                                                        |  |  |

| 14  | HIZ               | When set to a logic low, output pins OUT1, OUT2, RCLK, and RDATA buffers are set to high-impedance state. When set to a logic high or no connect, the device functions and output pins OUT1, OUT2, RCLK, and RDATA are active. This input has an internal pull-up resistor. |  |  |

| 15  | OUT1              | Output clock of internal VCXO (TTL).                                                                                                                                                                                                                                        |  |  |

| 16  | v <sub>cc</sub>   | +5.0 V ±10% supply voltage (+3.3 V option available).                                                                                                                                                                                                                       |  |  |

Table 2.

Why would someone buy a TRU-050?

To save design time, reduce component count, conserve board space, and optimize manufacturing efficiency.

# How Is It Built?

The TRU-050 is a user-configured phase-locked loop (PLL) integrated circuit. It includes a voltage controlled crystal oscillator (VCXO), an operational amplifier, a phase detector, and additional integrated functions for use in digital synchronization applications. These applications include timing recovery and data pulse restoration for data signals, clock frequency translation and smoothing, synchronous distributed clock networks, and clock frequency synthesis.

#### What is the output of the phase detector?

The TRU-050 phase detector output is a DC signal, under locked conditions, and is nominally 2.5 Volts. The phase error (which is typically a pulse for digital phase detectors) is converted to a DC level, making it easy to design the loop filter.

#### How long does the TRU-050 take to detect a loss of signal?

If there are no transitions on DATAIN for a period of 256 clock cycles, LOS is set to a logic 1. LOS is reset to logic 0 as soon as there are DATAIN transitions.

#### TRU-050 Elements

#### Phase Detector

The phase detector is designed to accept an NRZ data stream at DATAIN (Pin 7- refer to figure 5), but may be used for clock signals and other data types. The input buffers are designed to switch at a TTL switching threshold of 1.4 V.

The phase detector's inputs are:

- DATAIN (Pin 7) the input clock or NRZ data signal

- CLKIN (Pin 9) the clock signal feedback from the VCXO output OUT1 or OUT2

#### And the outputs are:

- RCLK (Pin 11) the regenerated clock signal

- RDATA (Pin 12) the retimed data signal

- PHO (Pin 6) the phase detector output

- LOS (Pin 10) a loss of signal detector

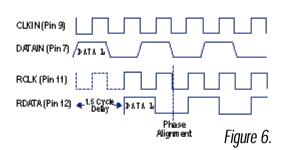

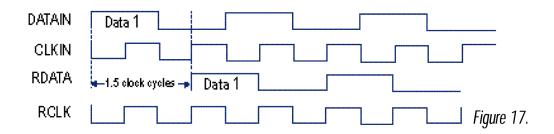

The phase relationship between the regenerated clock signal, RCLK (Pin 11), and the regenerated data signal, RDATA (Pin 12), is shown in figure 6.

The falling edge of RCLK is coincident with the center of the regenerated NRZ RDATA pulse. Figure 6 shows a 1010 data stream with a 100% data transition density. In general, this will not be the case and input data will have fewer data transitions. However, the phase detector will still seek

to align the falling edge of the RCLK signal with the center of each RDATA pulse.

For applications where the input clock or data signal, DATAIN, is very low in frequency (<200kHz), clock information may pass through the phase detector because of its finite low pass characteristic. In applications such as this, an additional pole may be necessary in the loop filter to attenuate these AC components prior to the VCXO input. Please contact Vectron's Applications Engineering staff for further detail.

# How is it manufactured?

The TRU-050 is assembled in "state of the art" class 100 and class 10,000 clean rooms using leading edge, high volume automation equipment and advanced ASIC technology.

#### Phase Detector Gain Calculation

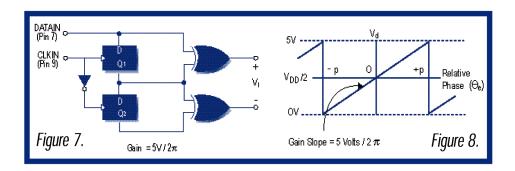

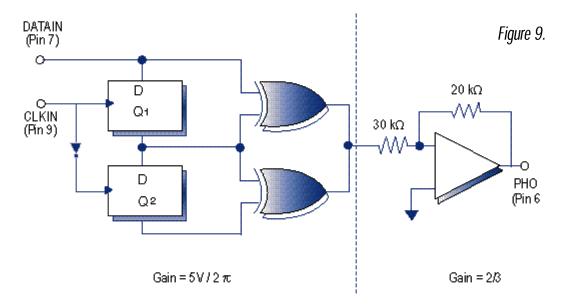

The schematic diagram (figure 7) shows a simplified representation of the phase detector's basic error generation function. The actual circuit is more complex and includes circuitry to reduce the TRU-050's dependence on input data duty-cycle. In general, the TRU-050 is insensitive to duty cycle and duty cycle changes. This circuit provides a output ( $V_D$ ) DC level which is proportional to the relative phase of DATAIN (Pin 7) and CLKIN (Pin 9). A plot of the output ( $V_D$ ) versus relative phase is shown in figure 8. The slope of the output ( $V_D$ ) versus relative phase ( $O_e$ ) is  $5V/2\pi$ .

The phase detector block also includes an output gain stage which should be considered when calculating the gain of the complete phase detector block. This gain stage has a gain of 2/3, and converts the differential signal to a single-ended DC output.

Phase Detector Gain =  $[5V/2\pi] * [2/3] * D = 0.53 * D$

Where D = input data transition density. For example D = 1 for 100% transition density (e.g., clock signal) and D = 0.5 for 50% transition density (e.g., balanced NRZ data).

#### LOS and LOSIN

The LOS circuit provides an output alarm flag when the DATAIN input signal is lost. The LOS output is set "logic high" after 256 consecutive CLKIN periods with no DATAIN transitions. This signal can then be used to either flag external alarm circuits and/or drive the TRU-050's LOSIN circuit. When the LOSIN input is set "logic high," the loop filter op-amp output is set mid supply to facilitate fast lockup when DATAIN is restored. In addition, the VCXO control voltage is internally set to hold the VCXO at its nominal frequency (±75 ppm). When LOSIN is low or has no connection, the VCXO's control voltage input is enabled (LOSIN has an internal pull-down resistor).

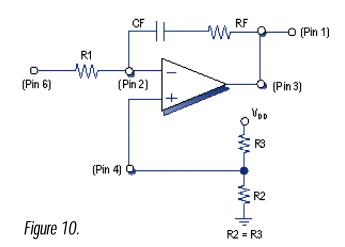

### Loop Filter

Although various loop filter configurations may be considered, most TRU-050 applications use the basic integrator filter of figure 10. This type of filter provides high DC gain to ensure proper clock and data alignment. The ratio of R1 to RF sets midband gain and can be used to adjust the loop bandwidth. The time constant, set by RF and

CF, should be selected to be about one decade below the open loop bandwidth to provide good phase margin. The reference for the noninverting input is set at midsupply by R2 and R3. Software is available to help in the selection of R1, CF and RF.

TRU-050 VCXO Frequency Deviation vs. Control Voltage

#### **VCXO**

The TRU-050's VCXO is a varactor-tuned crystal oscillator which produces an output frequency controlled by a control voltage,  $V_c$ . The tracking range of the VCXO is specified as absolute pull range (APR) when ordered. An APR of  $\pm 50$  ppm guarantees that the TRU-050 can track an input source frequency with  $\pm 50$  ppm stability over all operating conditions, including temperature, time, power supply and load variations. The value of  $V_c$  is varied between 0.5 V to 4.5 V to achieve the specified APR. A typical frequency versus  $V_c$  curve for the VCXO in the TRU-050 is shown in figure 11. When designing PLLs, the VCXO gain (kV in Hz/V or rad/Vs) is an important parameter. As a rule of thumb, the frequency deviation for the TRU-050 VCXO is 300 ppm over the 1 V to 4 V range  $V_c$ .

For example, a 10 MHz VCXO has an average gain of 1000 Hz/V. The peak value of kV is about twice this value at approximately 2.5 V, and one half this value at 1 V and 4 V.

For many loop calculations, the gain is expressed in rad/Vs which would be  $2\pi$  (100 ppm \* f<sub>0</sub>/Vs) for the previous example.

# How is quality assured?

In addition to

extensive testing,

the basic design

consists of a few

highly engineered,

robust components;

quality is further

assured by advanced

ceramic packaging

and fully automated

assembly.

# Oscillator Aging

Any crystal stabilized oscillator typically exhibits a small shift in output frequency during aging. The major factors which lead to this shift are changes in the mechanical stress on the crystal and mass-loading of foreign material on the crystal.

As the oscillator ages, relaxation of the crystal mounting stress or transfer of environmental stress through the package to the crystal mounting arrangement can lead to frequency variations. Vectron has minimized these two effects through the use of a miniature AT-cut strip resonator crystal which allows a superior mounting arrangement and results in minimal relaxation and almost negligible environmental stress transfer.

Mass-loading on the crystal generally results in a frequency decrease and is typically due to out-gassing of material within a hermetic package or from contamination by external material in a non-hermetic package. Vectron has minimized the impact of mass loading by ensuring hermetic integrity and minimizing out-gassing by limiting the number of internal components through the use of ASIC technology.

Under normal operating conditions with an operating temperature of 40°C, the TRU-050 will typically exhibit 2 ppm aging in the first year of operation. The device will then exhibit 1 ppm aging the following year with a logarithmic decline each year thereafter.

#### I'm not familiar with APR. Could you explain it in more detail?

APR is the guaranteed frequency error (in ppm) the VCXO can track. This takes the guesswork out of the total pull range which drifts and is affected by temperature, aging, power supply etc. Every TRU-050 is tested for pull range over the operating temperature range, making it one of the most reliable devices on the market.

# What's the difference between OUT1 and OUT2?

OUT1 is the direct output from the VCXO and is limited to frequencies in the 12 MHz to 65 MHz range.

OUT2 is an optional 2<sup>n</sup> divided VCXO output. The divide ratio is factory set at 2, 4, 8, ... or 2<sup>n</sup>, up to 256.

### Absolute Pull Range

Absolute pull range (APR) is specified by the fourth character of the product code (see figure 26). APR is the minimum guaranteed frequency shift from  $f_0$  over variations in temperature, aging, power supply and load. Both frequency and environment limit the specified APR. The total pull range for the VCXO contained in the TRU-050 is typically between 200 ppm and 400 ppm. A 50 ppm APR TRU-050 fully tracks a 50 ppm source oscillator or any other 50 ppm reference over the operating temperature range, life of the product, power supply and measurement variations.

## Output Divider Circuit

An internal 2<sup>n</sup> divided output is available at OUT2. The value of n varies from 1 to 8 and is set during manufacture. This provides divide ratios from 2 to 256. A "no output" option may also be selected to minimize power usage and jitter.

**Divider Note:** The frequency of OUT1 is the fundamental frequency of the VCXO used in the TRU-050. The lowest frequency VCXO (OUT1) available in the TRU-050 is 12 MHz, and the highest frequency is 65.536 MHz. Therefore, the frequency range of OUT1 is between 12 MHz and 65.536 MHz. Since OUT2 is a division of OUT1 and can vary from OUT1  $\div$  2 to OUT1  $\div$  256, OUT2 ranges from 46.875 kHz (12 MHz  $\div$  256) to 32.768 MHz (65.536 MHz  $\div$  2). Lower frequency inputs may be supplied to the phase detector of the TRU-050, but an external divider in the feedback loop is required. With an external divider in the feedback loop, clock and data signals down to 8 kHz can be used as phase detector inputs.

Tel: 1-88-VECTRON-1 e-mail: vectron@vectron.com

### Handling Precautions

Although protection circuitry has been designed into this device, proper precautions should be taken to avoid exposure to electrostatic discharge (ESD) during handling and mounting. Vectron employs a human body model (HBM) and a charged device model (CDM) for ESD susceptibility testing and protection design evaluation. ESD voltage thresholds are dependent on the circuit parameters used to define the mode. Although no industry-wide standard has been adopted for CDM, a standard HBM (resistance = 1500  $\Omega$ , capacitance = 100 pF) is widely used and therefore can be used for comparison purposes. The HBM ESD threshold presented here was obtained using these circuit parameters.

| MODEL          | ESD Threshold, Minimum | Unit |

|----------------|------------------------|------|

| Charged Device | 2000                   | V    |

| Human Body     | 2000*                  | V    |

<sup>\*</sup> MIL-STD-883D, Method 3015, Class 1

Table 3.

# How is it packaged?

The TRU-050 is a very robust product which is assembled on an automated manufacturing line. It is packaged in a 16-pin, ceramic DIP with a seam-welded step lid, hermetically sealed for long term reliability. Options include thru-hole and surface mount terminals and an extended temperature range. Tape and reel packaging is also available.

# How Does It Perform?

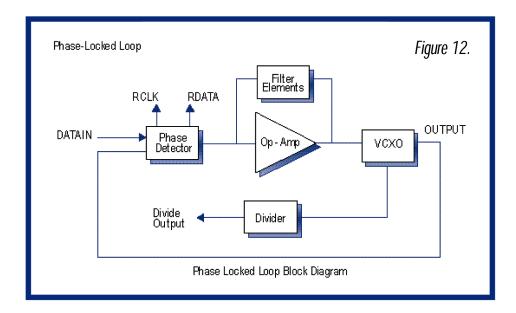

A typical PLL is illustrated in figure 12. Be advised that many textbook equations describing loop dynamics, such as capture range or lockin time, are based on ideal systems. Such equations may not be accurate for real systems with nonlinearities, DC offsets and noise. A PLL is a feedback system which forces the output frequency to lockin both phase and frequency to the fundamental frequency of the input signal.

When initially out of lock, the output of the phase detector is proportional to the difference in frequency between the two phase detector inputs. This beat note varies the output frequency of the VCXO, and in a properly designed phase-locked loop, the loop action forces V<sub>C</sub> to the correct value to bring the system into lock.

A designer's primary concern is to select a loop filter that ensures lockin and stability, while providing adequate filtering of input signal noise or jitter. An initial design starts with a known DATAIN signal and an output specification. An initial analysis of the open loop gain response provides insight into the response of the system.

Using figure 12, the open loop gain is:

$$G(s) = \frac{Kp \ kV \ AV(s)}{sN}$$

Where:

Kp is the phase detector gain in V/rad (-0.53 x Data Density).

kV is the VCXO gain constant in Rad/Vs.

AV(s) is the loop filter transfer function.

N is the divide ratio.

1/s converts the VCXO frequency output to a phase output.

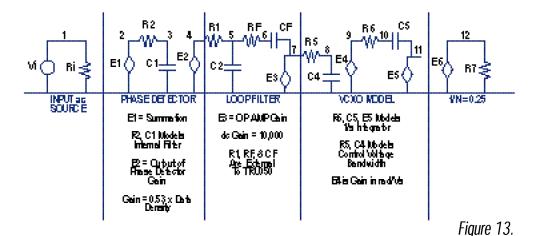

The open loop gain may be plotted and varied using the SPICE model provided in figure 13. The gain, frequency, and loop filter configurations may be varied to producedesired responses. In the first-order phase-locked loop, where AV(s) and N equal 1, the gain curve has a 20 dB/decade slope with unity gain at:

$$f = \frac{kV Kp}{2\pi}$$

where kV is in rad/Vs.

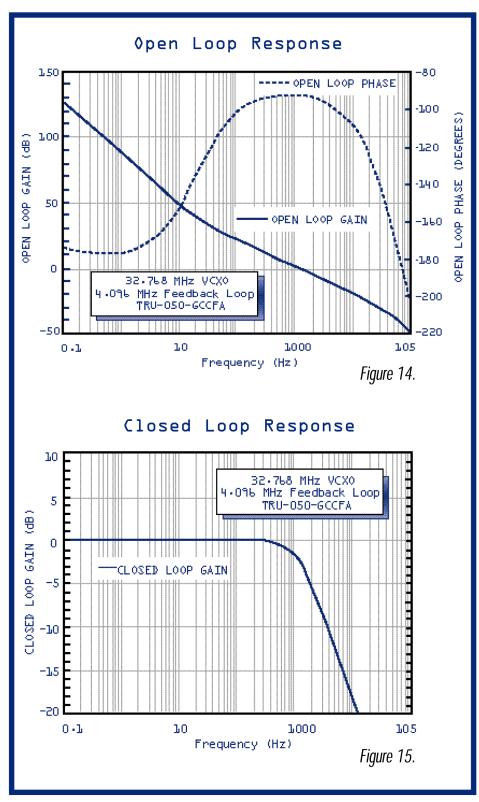

The first-order open loop gain has a constant phase shift of 90 degrees. However, other frequency poles are present in the loop due to the op-amp's limited bandwidth and gain, the phase detector and the VCXO modulation bandwidth (these poles are included in the SPICE model). The loop's bandwidth is approximately equal to the closed loop bandwidth and can be used to assess the stability, lockin range and filtering characteristics of the loop. The loop acts as a bandpass filter centered at the clock frequency, just as if a tank circuit were used to filter the input clock or data stream.

However, the filter Q of the TRU-050 is much greater than that of a tank circuit and typically ranges from 1,000 to 20,000. The PLL tracks input phase jitter inside the loop bandwidth while jitter is attenuated outside the loop bandwidth. Converting the SPICE model (figure 13) to a closed loop illustrates the jitter transfer function shown in figure 15. In general, the PLL rapidly locks those signals with an initial frequency difference (relative to CLKIN) that is within the loop's bandwidth. Lockin time is longer for lower bandwidth loops and may be degraded by jitter or by poor input duty cycle.

#### Simulated Results

The SPICE model just described can be used to determine the component values necessary to produce a desired loop filter bandwidth, its jitter transfer function and its open loop response for a given application. Alternatively, simulation results can be obtained using Vectron's "TRU-050 Loop Filter Calculation" software. This software runs from DOS and will also provide the user with loop filter component values R1, RF and CF (see figure 15) based on desired loop filter bandwidth, data type, data density, damping factor and data frequency. For assistance with your specific application, or to receive a copy of Vectron's "TRU-050 Loop Filter Calculation" software, please contact Vectron's Application Engineering staff.

#### SPICE Model

```

*****TRU050 ac Loop Model

vi l D ac l

ri 1 0 1k

*****Phase Detector

el 2 0 1 0 1

(for closed loop response use:

el 2 0 1 12 1)

r2 2 3 30k

cl 3 0 60p

*****Phase Detector Gain =

0.53 * Data Density

e2 4 0 3 0 •265

***

*****Loop Filter

rl 4 5 lOk

c2 5 0 10p

rF 5 6 40k

cF 6 7 .lu

e3 7 0 5 0-10000

*****VCX0

******Input Bandwidth = 50 kHz

r5 7 8 160k

c4 & 0 20p

******VCX0 Gain 2π Hz/V

*****Example 100 ppm *

30.72 MHz * 2 * \pi

e4 9 0 8 0 19300

*****L/s Model

r6 9 10 1000

c5 l0 ll .00l

e5 ll 0 l0 0-le6

*****Divide by N

eP 75 0 77 0 7

r8 12 0 1k

```

#### SPICE Simulated Results

- \* Phase margin is 87.0° at 1000.0 Hz

- \* Open loop gain margin is -3.92e+01 at 60000.0 Hz

- \* Closed loop jitter bandwidth (-3 dB) is 1500 Hz.

- \* The maximum value of the closed loop gain is D.11614dB at a frequency of 65.000 Hz

- \* Damping factor = 4.0

- \* Rl = 13.5 kohm

- RF = 79.6 k ohm

- CF = 0.10 µF

- Data density = 100%

- VCXO FREQ = 32.768 MHz

- \* Feedback divider = 8

# How Is It Used?

#### **Applications**

The three key applications for the TRU-050 are clock recovery of digital data, frequency translation and clock smoothing. These timing needs are required by a wide variety of markets such as telecommunications, datacommunications, digital video and audio, telemetry, test equipment and sensing.

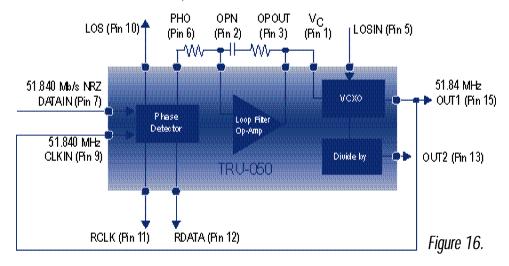

# Clock Recovery and Data Retiming

The TRU-050 was designed to recover a clock imbedded in an NRZ data signal, and retime it with a data pattern. In this application, the VCXO frequency is exactly the same as the NRZ data rate and the outputs are taken off Pin 11 (Recovered Clock) and Pin 12 (Recovered Data). The diagram below shows a typical circuit.

Figure 17 shows the relationship between DATAIN (Pin 7) and CLKIN (Pin 9) under locked conditions. The rising edge of the CLKIN is centered to the DATAIN pulse.

Relationship of RCLK (Pin 11) and RDATA (Pin 12). The falling edge of the Recovered Clock is in the middle of the data pattern and should be used to clock the data into the next part of the circuit. There is a one and a half cycle delay (frequency of Pin 9) between DATAIN and RDATA. Therefore a 10 MHz signal would have a 150 nS delay between DATAIN and RDATA plus additional circuit delays, which are typically 9 nS.

# Is Vectron ISO registered?

Yes! Vectron's quality system was registered to ISO 9001 in October 1996.

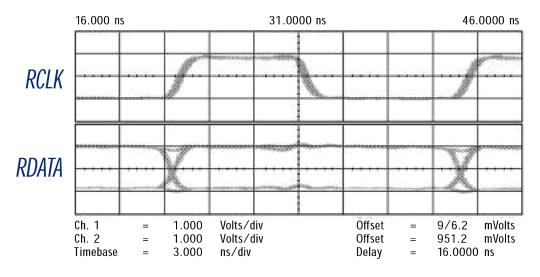

Eye Diagram for TRU-050 @ 51.84 MHz

The falling edge of RCLK is centered with respect to RDATA

Figure 18.

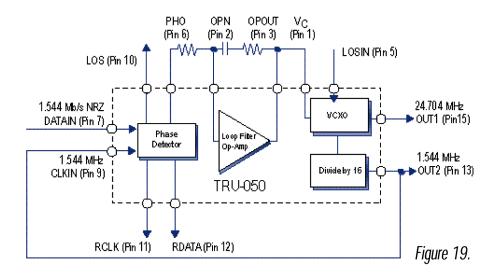

# Timing Recovery Using OUT2

Due to the limitations in crystal size, the lowest frequency from OUT1 is 12 MHz. For applications below this frequency, the internal divide-by can be used (Note: an additional external divide-by can also be used). An application for 1.544 MHz clock recovery is shown in figure 19.

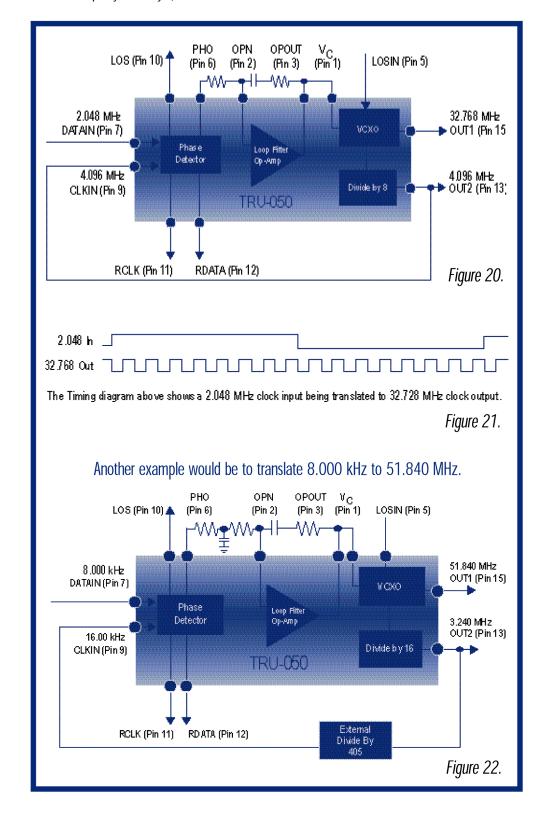

### Frequency Translation

The TRU-050 is most commonly used for frequency translation. For example, in a telecommunications application, when a 2.048 MHz reference clock is multiplied to 32.768 MHz, a very clean 32.768 MHz clock would then be output to other circuits.

Generally, the TRU-050 is specified in terms of NRZ input. Since the TRU-050's phase detector was designed for NRZ data, other inputs such as a clock signal should be considered as an equivalent 1010...NRZ pattern.

If the DATAIN input to the phase detector is a clock signal, the VCXO, or the divided VCXO output fed back to CLKIN, must be twice the DATAIN rate. In figure 20, the 2.048 MHz system reference clock can be treated as a 4.096 MHz NRZ data stream with a data density of 100%. Therefore, the feedback frequency in the PLL would be 4.096 MHz (the 32.768 MHz clock frequency divided by 8).

Can I get application assistance?

Absolutely! Just call 1-88-VECTRON-1

For applications where the DATAIN is very low in frequency (roughly <200 kHz), clock information may pass through the phase detector because of its finite low pass characteristics. In applications such as this, an additional pole may be necessary in the loop filter to attenuate these AC components prior to the VCXO input (note the capacitor to ground in figure 22). Please contact Vectron's Applications Engineering staff for further detail.

#### Clock Smoothing Example

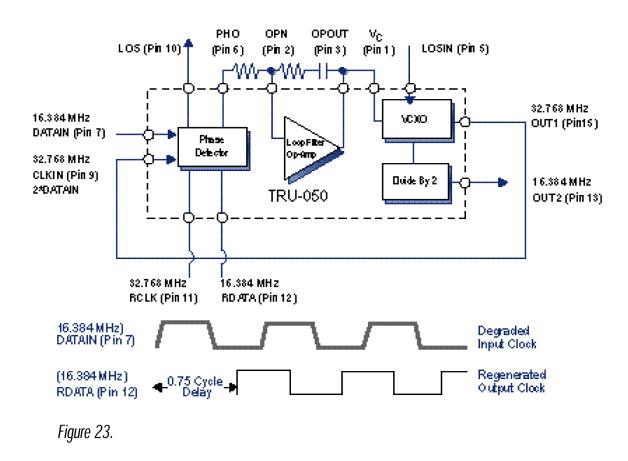

The third common application of the TRU-050 is for the Regeneration or "Smoothing" of a degraded input clock signal. In this application, the TRU-050 accepts a degraded input clock signal and regenerates the signal to square up the rising and falling edges and remove unwanted jitter. The output is then a clean quartz locked representation of the degraded input signal. Figure 23 illustrates a common example of a clock signal regeneration application. In this example, a degraded 16.384 MHz clock signal is smoothed using the TRU-050. The 16.384 MHz clock is fed into DATAIN (Pin 7). The signal is then regenerated, and a smoothed representation of the signal is available at RDATA (Pin 11).

It is important to note that the signal fed back from OUT1 (Pin 15) to CLKIN (Pin 9) is twice the frequency of the degraded input signal at DATAIN (Pin 7). This is because the TRU-050 was originally designed for input NRZ data patterns. Since an NRZ data pattern has one transition per bit, and its associated clock has two transitions per bit, the TRU-050 phase detector requires twice as many transitions at CLKIN (Pin 9) when compared to DATAIN (Pin 7). In the case of an input clock signal, CLKIN (Pin 9) must be twice the frequency of DATAIN (Pin 7). For a 16.384 MHz clock smoothing application, a TRU-050 with a 32.768 MHz OUT1 should be specified.

# How Is It Packaged?

**Questions?** Give us a call: 1-88-VECTRON-1

# How Is It Ordered?

| Standard frequencies* (MHz) Using OUT1 |        |        |        |        |        |        |  |

|----------------------------------------|--------|--------|--------|--------|--------|--------|--|

| 12.032                                 | 12.288 | 12.624 | 13.824 | 16.000 | 16.128 | 16.384 |  |

| 16.777                                 | 16.896 | 17.920 | 18.432 | 18.936 | 20.000 | 20.480 |  |

| 22.1184                                | 22.579 | 24.576 | 24.704 | 25.000 | 25.248 | 28.000 |  |

| 30.720                                 | 32.000 | 32.768 | 33.330 | 34.368 | 38.880 | 40.000 |  |

| 41.2416                                | 41.943 | 44.736 | 47.457 | 49.152 | 49.408 | 50.000 |  |

| 51.840                                 | 65.536 | 19.440 |        | 40.960 |        |        |  |

| Standard frequencies* (MHz) Using OUT2 |         |        |         |         |        |        |  |

|----------------------------------------|---------|--------|---------|---------|--------|--------|--|

| 1.000                                  | 1.024   | 1.544  | 2.048   | 3.088   | 3.240  | 4.032  |  |

| 4.096                                  | 4.1925  | 4.224  | 5.592   | 6.016   | 6.144  | 6.312  |  |

| 6.480                                  | 6.912   | 7.680  | 8.000   | 8.192   | 8.448  | 8.960  |  |

| 9.486                                  | 9.720   | 10.000 | 10.240  | 11.0592 | 12.352 | 12.500 |  |

| 12.960                                 | 14.000  | 16.000 | 16.384  | 16.665  | 19.440 | 20.000 |  |

| 20.6208                                | 20.9715 | 22.368 | 23.7285 | 24.576  | 24.704 | 25.920 |  |

| 32.768                                 |         |        |         |         |        |        |  |

\*Other frequencies available upon request.

Table 4.