# REALTEK SINGLE CHIP SINGLE PORT 10/100MBPS FAST ETHERNET PHYCEIVER RTL8201(L)

| 1. Features                                                    |      |

|----------------------------------------------------------------|------|

| 2. General Description                                         | 2    |

| 3. Block Diagram                                               | 3    |

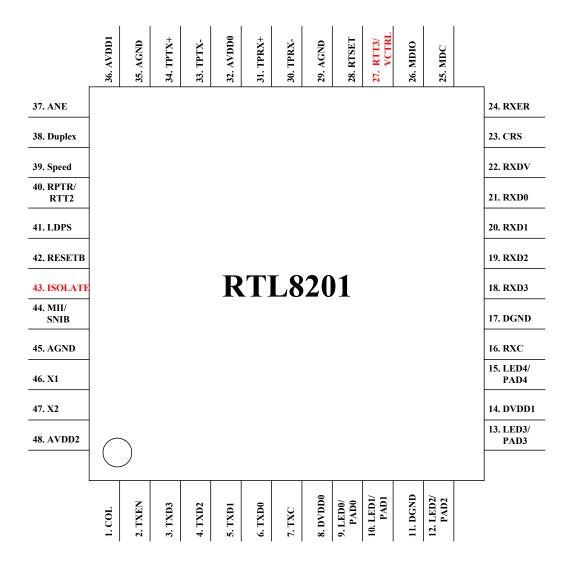

| 4. Pin Assignments                                             | 4    |

| 5. Pin Description                                             | 5    |

| 5.1 100 Mbps MII & PCS Interface                               | 5    |

| 5.2 Serial Network Interface (SNI)                             | 5    |

| 5.3 Clock Interface                                            | 5    |

| 5.4 100Mbps Network Interface                                  | 6    |

| 5.5 Device Configuration Interface                             | 6    |

| 5.6 LED Interface/PHY Address Config                           | 6    |

| 5.7 Reset and Test pins                                        | 6    |

| 5.8 Power and Ground pins                                      |      |

| 6. Register Descriptions                                       | 7    |

| 6.1 Register 0 Basic Mode Control                              | 7    |

| 6.2 Register 1 Basic Mode Status                               |      |

| 6.3. Register 2 PHY Identifier 1                               |      |

| 6.4. Register 3 PHY Identifier 2                               | . 10 |

| 6.5. Register 4 Auto-negotiation Advertisement                 | . 11 |

| 6.6 Register 5 Auto-Negotiation Link Partner Ability           | . 12 |

| 6.7 Register 6 Auto-negotiation Expansion (ANER)               | . 14 |

| 6.8 Register 16 Nway Setup (NSR)                               |      |

| 6.9 Register 17 Loopback, Bypass, Receiver Entor Mask (LBREMR) |      |

| 6.10 Register 18 RX_ER Counter (REC)                           | . 15 |

| 6.11 Register 19 10Mbps Network Interface Configuration        |      |

| 6.12 Register 20 PHY 1_1                                       | . 15 |

| 6.13 Register 21 PHY 1_2                                       | . 16 |

|                                                                |      |

|    | 6.13 Register 22 PHY 2                                       | 16 |

|----|--------------------------------------------------------------|----|

|    | 6.14 Register 23 Twister_1                                   | 16 |

|    | 6.15 Register 24 Twister 2                                   |    |

| 7. | Functional Description                                       |    |

|    | 7.1 MII and Management Interface                             |    |

|    | 7.2 Auto-negotiation and Parallel Detection                  |    |

|    | 7.3 Flow control support                                     |    |

|    | 7.4 Hardware Configuration and Auto-negotiation              |    |

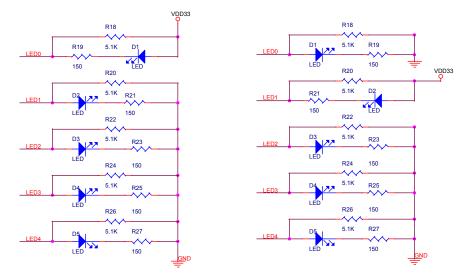

|    | 7.5 LED and PHY Address Configuration                        | 20 |

|    | 7.6 Serial Network Interface                                 |    |

|    | 7.7 Power Down, Link Down, Power Saving, and Isolation Modes | 21 |

|    | 7.8 Media Interface                                          | 21 |

|    | 7.8.1 100Base Tx/Rx                                          |    |

|    | 7.8.2 10Base Tx/Rx                                           |    |

|    | 7.9 Repeater Mode Operation                                  | 22 |

|    | 7.10 Reset, Power, and Transmit Bias                         |    |

| 8. | Electrical Characteristics                                   |    |

|    | 8.1 D.C. Characteristics                                     | 23 |

|    | 8.1.1. Absolute Maximum Ratings                              | 23 |

|    | 8.1.2. Operating Conditions                                  | 23 |

|    | 8.1.3. Power Dissipation                                     | 23 |

|    | 8.1.4 Supply Voltage: Vcc                                    | 23 |

|    | 8.2 A.C. Characteristics                                     |    |

|    | 8.2.1 Transmission Without Collision                         |    |

|    | 8.2.2 Reception Without Error                                |    |

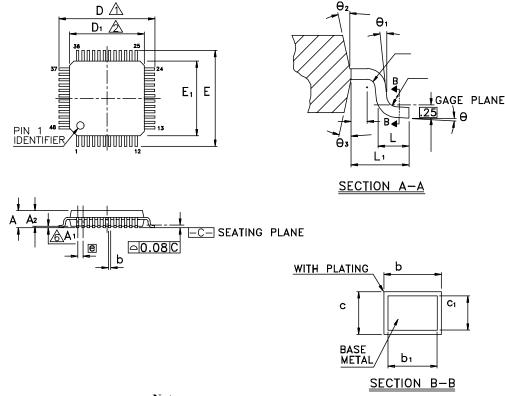

| 9. | Mechanical Dimensions                                        | 25 |

|    |                                                              |    |

# 1. Features

The Realtek RTL8201(L) is a Fast Ethernet Phyceiver with MII interface to the MAC chip. It provides the following features:

- Supports MII interface

- Supports 10/100Mbps operation

- Supports half/full duplex operation

- IEEE 802.3/802.3u compliant

- Supports IEEE 802.3u clause 28 auto negotiation

- Supports power down mode

- Supports operation under Link Down Power Saving mode

- Supports repeater mode

- Speed/duplex/auto negotiation adjustable

- 3.3V operation with 5V signal tolerance

- Low operation power consumption

- Adaptive Equalization

- 25MHz crystal/oscillator as clock source

- Multiple network status LED support

- Supports 7-wire SNI (Serial Network Interface) interface

- Flow control ability support to co-work with MAC (by MDC/MDIO)

- 48-pin LQFP package

### 2. General Description

The RTL8201(L) is a single-port Phyceiver with an MII (Media Independent Interface). It implements all 10/100M Ethernet Physical-layer functions including the Physical Coding Sublayer (PCS), Physical Medium Attachment (PMA), Twisted Pair Physical Medium Dependent Sublayer (TP-PMD), 10Base-Tx Encoder/Decoder and Twisted Pair Media Access Unit (TPMAU). It is fabricated with an advanced CMOS process to meet low voltage and low power requirements.

The RTL8201(L) can be used as a Network Interface Adapter, MAU, CNR, ACR, Ethernet Hub, Ethernet Switch. Additionally, it can be used in any embedded system with an Ethernet MAC that needs a twisted pair physical connection.

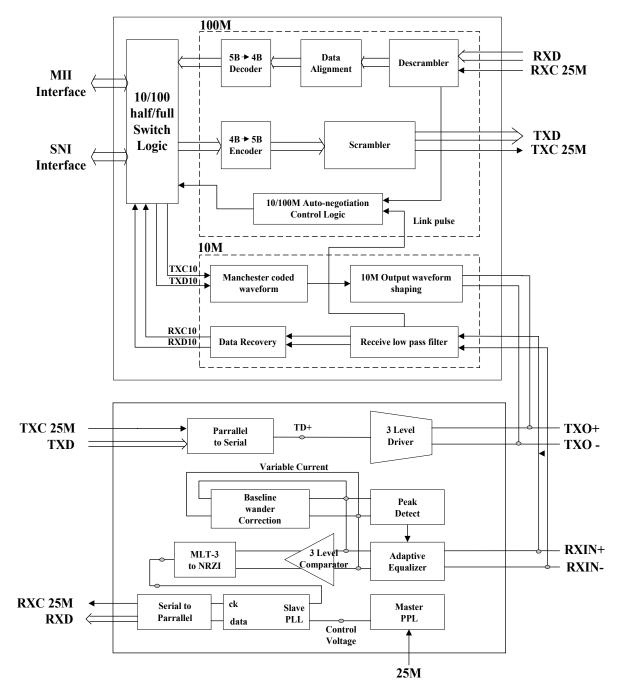

## 3. Block Diagram

# **5.** Pin Description

#### 5.1 100 Mbps MII & PCS Interface

| Symbol   | Туре | Pin(s) No.     | Description                                                                                                                                                                                                         |  |

|----------|------|----------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| TXC      | 0    | 7              | <b>Transmit Clock:</b> This pin provides a continuous clock as a timing reference for TXD[3:0] and TXEN.                                                                                                            |  |

| TXEN     | Ι    | 2              | <b>Transmit Enable:</b> The input signal indicates the presence of a valid nibble data on TXD[3:0].                                                                                                                 |  |

| TXD[3:0] | Ι    | 3, 4, 5, 6     | <b>Transmit Data:</b> MAC will source TXD[03] synchronous with TXC when TXEN is asserted.                                                                                                                           |  |

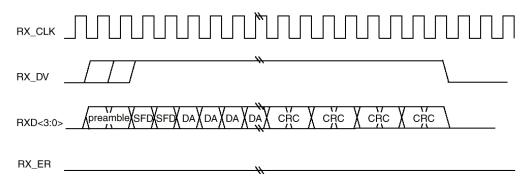

| RXC      | 0    | 16             | <b>Receive Clock:</b> This pin provides a continuous clock reference for RXDV and RXD[03] signals. RXC is 25MHz in the 100Mbps mode and 2.5Mhz in the 10Mbps mode.                                                  |  |

| COL      | 0    | 1              | Collision Detected: COL is asserted high when a collision is detected on the media.                                                                                                                                 |  |

| CRS      | I/O  | 23             | Carrier Sense: This pin's signal is asserted high if the media is not in IDEL state.                                                                                                                                |  |

| RXDV     | 0    | 22             | <b>Receive Data Valid:</b> This pin's signal is asserted high when received data is present on the RXD[3:0] lines; the signal is deasserted at the end of the packet. The signal is valid on the rising of the RXC. |  |

| RXD[3:0] | 0    | 18, 19, 20, 21 | <b>Receive Data:</b> These are the four parallel receive data lines aligned on the nibble boundaries driven synchronously to the RXC for reception by the external physical unit (PHY).                             |  |

| RXER     | 0    | 24             | <b>Receive error:</b> if any 5B decode error occurred such as invalid J/K, T/R, invalid symbol, this pin will go high                                                                                               |  |

| MDC      | Ι    | 25             | <b>Management Data Clock:</b> This pin provides a clock synchronous to MDIO, which may be asynchronous to the transmit TXC and receive RXC clocks.                                                                  |  |

| MDIO     | I/O  | 26             | <b>Management Data Input/Output:</b> This pin provides the bi-directional signal used to transfer management information.                                                                                           |  |

#### 5.2 Serial Network Interface (SNI) 10Mbps only

| Symbol | Туре | Pin(s) No. | Description                                             |

|--------|------|------------|---------------------------------------------------------|

| COL    | 0    | 1          | Collision Detect                                        |

| RXD0   | 0    | 21         | Received Serial Data                                    |

| CRS    | 0    | 23         | Carrier Sense                                           |

| RXC    | 0    | 16         | Receive Clock: Resolved from received data              |

| TXD0   | Ι    | 6          | Transmit Serial Data                                    |

| TXC    | 0    | 7          | Transmit Clock: Generate by PHY                         |

| TXEN   | Ι    | 2          | Transmit Enable: For MAC to indicate transmit operation |

#### **5.3 Clock Interface**

| Symbol | Туре | Pin(s) No. | Description                                                              |

|--------|------|------------|--------------------------------------------------------------------------|

| X2     | 0    | 47         | <b>25Mhz Crystal Output:</b> This pin provides the 25MHz crystal output. |

| X1     | Ι    | 46         | <b>25Mhz Crystal Input:</b> This pin provides the 25MHz crystal input.   |

#### 5.4 100Mbps Network Interface

| Symbol | Туре | Pin(s) No. | Description                                                              |

|--------|------|------------|--------------------------------------------------------------------------|

| TPTX+  | 0    | 34         | Transmit Output                                                          |

| TPTX-  | 0    | 33         |                                                                          |

| RTSET  | Ι    | 28         | Transmit bias resistor connection: This pin should be pulled to GND by a |

|        |      |            | 2.0K resistor.                                                           |

| TPRX+  | Ι    | 31         | Receive input                                                            |

| TPRX-  | Ι    | 30         |                                                                          |

#### **5.5 Device Configuration Interface**

| Symbol     | Туре | Pin(s) No. | Description                                                                  |  |

|------------|------|------------|------------------------------------------------------------------------------|--|

| ISOLATE    | Ι    | 43         | Set high to isolate the RTL8201(L) from the MAC. This will also isolate the  |  |

|            |      |            | MDC/MDIO management interface. In this mode, the power consumption is        |  |

|            |      |            | minimum.                                                                     |  |

| RPTR/RTT2  | Ι    | 40         | Set high to put the RTL8201(L) into repeater mode. In test mode, this pin is |  |

|            |      |            | re-defined as RTT2.                                                          |  |

| SPEED      | Ι    | 39         | Set high to put the RTL8201(L) into 100Mbps operation                        |  |

| DUPLEX     | Ι    | 38         | Set high to enable full duplex                                               |  |

| ANE        | Ι    | 37         | Set high to enable Auto-negotiation mode, set low to force mode              |  |

| LDPS       | Ι    | 41         | Set high to put the RTL8201(L) into LDPS mode,                               |  |

| MII/SNIB/T | Ι    | 44         | Pull high to set the RTL8201(L) into MII mode operation                      |  |

| XD5(test)  |      |            |                                                                              |  |

#### 5.6 LED Interface/PHY Address Config

| Symbol    | Туре | Pin(s) No. | Description      |

|-----------|------|------------|------------------|

| LED0/PAD0 | 0    | 9          | Link LED         |

| LED1/PAD1 | 0    | 10         | Full Duplex LED  |

| LED2/PAD2 | 0    | 12         | Link 10/ACT LED  |

| LED3/PAD3 | 0    | 13         | Link 100/ACT LED |

| LED4/PAD4 | 0    | 15         | Collision LED    |

#### 5.7 Reset and Test pins

| Symbol    | Туре | Pin(s) No. | Description                                                          |

|-----------|------|------------|----------------------------------------------------------------------|

| RTT3/CTRL | 0    | 27         | Currently a test pin, this pin may be utilized for future functions. |

| RESETB    | Ι    | 42         | <b>RESETB:</b> Setting low to reset the chip.                        |

#### 5.8 Power and Ground pins

| Symbol | Туре | Pin(s) No. | Description                                                             |  |

|--------|------|------------|-------------------------------------------------------------------------|--|

| AVDD0  | Р    | 32         | Analog power: 3.3V power supply for analog circuit; should be well      |  |

|        |      |            | decoupled                                                               |  |

| AVDD1  | Р    | 36         | Analog power: 3.3V power supply for analog circuit; should be well      |  |

|        |      |            | decoupled                                                               |  |

| AVDD2  | Р    | 48         | 3.3V power supply for PLL, should be well decoupled and use a bead with |  |

|        |      |            | 1000hm @ 100MHz to connect to analog power                              |  |

| AGND   | Р    | 29,35,45   | Analog Ground: Should be connected to a larger GND plane                |  |

| DVDD0  | Р    | 8          | Digital Power: 3.3V power supply for digital circuit.                   |  |

| DVDD1  | Р    | 14         | <b>Digital Power:</b> 3.3V power supply for digital circuit.            |  |

| DGND   | Р    | 11,17      | Digital Ground: Should be connected to a larger GND plane               |  |

2002-01-18

# **6.** Register Descriptions

This section will describe definitions and usage for each of the registers available in the RTL8201. The first six registers of the MII are defined by the MII specification. Other registers are defined by Realtek Semiconductor Corp. for internal use and are reserved for specific uses.

| Register | Description                                    | Default (h) |

|----------|------------------------------------------------|-------------|

| 0        | Basic Mode Control Register                    | 3100        |

| 1        | Basic Mode Status Register                     | 7849        |

| 2        | PHY Identifier 1 Register                      | 0000        |

| 3        | PHY Identifier 2 Register                      | 8201        |

| 4        | Auto-negotiation Advertisement Register        | 1E1         |

| 5        | Auto-negotiation Link Partner Ability Register | 80          |

| 6        | Auto-negotiation Expansion Register            | 0           |

#### 6.1 Register 0 Basic Mode Control

| Address | Name     | Description/Usage                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | Default/Attribute |

|---------|----------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------|

| 0:<15>  | Reset    | <b>Reset:</b> This bit sets the status and control registers of the PHY in a default state. In order to reset the RTL8201L by software control, a '1' must be written to bit 15 using an MII write operation. The bit clears itself after the reset process is complete, and does not need to be cleared using a second MII write. Writes to other Control register bits will have no effect until the reset process is completed, which requires approximately 1us. Writing a '0' to this bit has no effect. Because this bit is self clearing after a few cycles from a write operation, it will return a '0' when read. | 0, RW             |

|         |          | 1: Software reset<br>0: Normal operation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                   |

| 0:<14>  | Loopback | <b>Loopback:</b> This bit enables loopback of transmit data nibbles TXD<3:0> to the receive data path. The RTL8201L may be placed into loopback mode by writing a '1' to bit 14. Loopback mode may be cleared either by writing a '0' to bit 14 or by resetting the chip. When this bit is read, it will return a '1' when the chip is in software-controlled loopback mode, otherwise it will return a '0'.                                                                                                                                                                                                               | 0, RW             |

|         |          | 1: Enable loopback<br>0: Normal operation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                   |

| 0:<13>  | Spd_Set  | <b>Speed Set:</b> This bit can set the network speed. If Auto-negotiation is enabled, this bit has no effect on speed selection. However, if Auto-negotiation is disabled by software control, the operating speed of the RTL8201L can be forced by writing the appropriate value to bit 13. Writing a '1' to this bit forces 100Base-X operation, while writing a '0' forces 10Base-T operation. When this bit is read, it returns the value of the software controlled forced speed selection only.                                                                                                                      | 1, RW             |

|         |          | 1: 100Mbps<br>0: 10Mbps                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                   |

|         |          | When 100Base-FX mode is enabled, this bit=1, and this bit is read only.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                   |

| 0:<12>  | Auto<br>Negotiation<br>Enable | Auto Negotiation Enable: Auto-negotiation can be disabled by either<br>hardware or software control. This bit can enable/disable the Nway<br>auto-negotiation function. If the ANEN input pin is driven to a logic '0',<br>Auto-negotiation is disabled by software control. When<br>Auto-negotiation is disabled in this manner, writing a '1' to the same bit<br>of the control register or resetting the chip will re-enable<br>Auto-negotiation. Writing to this bit has no effect when<br>Auto-negotiation has been disabled by hardware control. When read,<br>this bit will return the value most recently written to this location, or '1'<br>if it has not been written since the last chip reset.<br>1: Enable auto-negotiation; bits 0:<13> and 0:<8> will be ignored<br>0: Disable auto-negotiation; bits 0:<13> and 0:<8> will determine the<br>link speed and the data transfer mode, respectively | 1, RW |

|---------|-------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|

| 0:<11>  | Power Down                    | When 100Base-FX mode is enabled, this bit=0, and this bit is read only.<br><b>Power Down:</b> The RTL8201L supports a low power mode which is<br>intended to decrease power consumption. This bit turns down the power<br>of the PHY chip including internal crystal oscillator circuit. The MDC,<br>MDIO is still alive for accessing the MAC.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 0, RW |

|         |                               | Writing a '1' will enable power down mode, and writing a '0' will<br>return the RTL8201L to normal operation. When read, this register will<br>return a '1' when in power down mode, and a '0' during normal<br>operation.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |       |

|         |                               | 1: Power down<br>0: Normal operation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |       |

| 0:<10>  | Reserved                      | <b>Reserved:</b> Ignore the output of the RTL8201L when these bits are read.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |       |

| 0:<9>   | Restart Auto<br>Negotiation   | <b>Restart Auto Negotiation:</b> Bit 9 is a self-clearing bit that allows the Nway auto-negotiation process to be restarted, regardless of the current status of the Auto-negotiation state machine. In order for this bit to have an effect, Auto-negotiation must be enabled. Writing a '1' to this bit restarts Auto-negotiation while writing a '0' to this bit has no effect. When this bit is read, it will always return a '0'.                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 0, RW |

|         |                               | 1: Re-start auto-negotiation<br>0: Normal operation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |       |

| 0:<8>   | Duplex Mode                   | <b>Duplex Mode:</b> By default, the RTL8201L powers up in half duplex mode. The chip can be forced into full duplex mode by writing a '1' to bit 8 while Auto-negotiation is disabled. Half duplex mode can be resumed either by writing a '0' to bit 8 or by resetting the chip. When Nway is enabled, this bit reflects the results of the Auto-negotiation, and is in a read only mode. When Nway is disabled, this bit can be set through the SMI, and is in a read/write mode. When 100FX is enabled, this bit can be set through the SMI or FX_DUPLEX pin and is in a read/write mode. This bit sets the duplex mode if auto negotiation is disabled (bit 0:<12>=0).                                                                                                                                                                                                                                       | 1, RW |

|         |                               | 1: Full duplex<br>0: Normal operation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |       |

| 0:<7:0> | Reserved                      | After auto negotiation completes, this bit will reflect the duplex status.<br><b>Reserved Bits:</b> All reserved MII register bits must be written as '0' at all times. Ignore the RTL8201L output when these bits are read.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |       |

### 6.2 Register 1 Basic Mode Status

| Address  | Name                            | Description/Usage                                                                                                                                                                                                                                                                | Default/Attribute |

|----------|---------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------|

| 1:<15>   | 100Base-T4                      | <ul> <li>100Base_T4: The RTL8201L supports the 100Base-T4 function. If the chip is set to operate in this mode, this bit will return a '1' when read.</li> <li>1: Enable 100Base-T4 support</li> <li>0: Suppress 100Base-T4 support</li> </ul>                                   | 0, RO             |

| 1:<14>   | 100Base_TX_<br>FD               | <b>100Base_TX_FD:</b> The RTL8201L is capable of operating in 100Base-TX full duplex mode. If the chip is set to operate in this mode, this bit will return a '1' when read.                                                                                                     | 1, RO             |

| 1:<13>   | 100BASE TX                      | 1: Enable 100Base-TX full duplex support<br>0: Suppress 100Base-TX full duplex support<br><b>100Base TX HD:</b> The RTL8201L is capable of operating in                                                                                                                          | 1, RO             |

|          | HD <sup>–––</sup>               | <ul><li>100Base-TX half duplex mode. If the chip is set to operate in this mode, this bit will return a '1' when read.</li><li>1: Enable 100Base-TX half duplex support</li></ul>                                                                                                |                   |

| 1:<12>   | 10Base_T_FD                     | 0: Suppress 100Base-TX half duplex support<br><b>10Base_T_FD:</b> The RTL8201L is capable of operating in 10Base-T full<br>duplex mode. If the chip is set to operate in this mode, this bit will<br>return a '1' when read.                                                     | 1, RO             |

|          |                                 | 1: Enable 10Base-T full duplex support<br>0: Suppress 10Base-T full duplex support                                                                                                                                                                                               |                   |

| 1:<11>   | 10_Base_T_HD                    | <b>10Base_T_HD:</b> The RTL8201L is capable of operating in 10Base-T half duplex mode. If the chip is set to operate in this mode, this bit will return a '1' when read.                                                                                                         | 1, RO             |

|          |                                 | 1: Enable 10Base-T half duplex support<br>0: Suppress 10Base-T half duplex support                                                                                                                                                                                               |                   |

| 1:<10:6> | Reserved                        | <b>Reserved:</b> Ignore the output of the RTL8201L when these bits are read.                                                                                                                                                                                                     |                   |

| 1:<5>    | Auto<br>Negotiation<br>Complete | <b>Auto-negotiate Complete:</b> Bit 5 will return a '1' if the Auto-negotiation process has been completed and the contents of registers 4 and 5 are valid.                                                                                                                      | 0, RO             |

|          |                                 | <ol> <li>Auto-negotiation process completed</li> <li>Auto-negotiation process not completed</li> </ol>                                                                                                                                                                           |                   |

| 1:<4>    | Remote Fault                    | <b>Remote Fault:</b> The PHY will return a '1' in bit 4 when its Link Partner has signaled a far-end fault condition. When a far end fault occurs, the bit will be latched at '1' and will remain so until the register is read and the remote fault condition has been cleared. | 0, RO             |

|          |                                 | <ol> <li>Remote fault condition detected (cleared on read)</li> <li>No remote fault condition detected</li> </ol>                                                                                                                                                                |                   |

|          |                                 | When in 100Base-FX mode, this bit means an in-band signal Far-End-Fault is detected.                                                                                                                                                                                             |                   |

| 1:<3>    | Auto<br>Negotiation             | <b>Auto-Negotiation Ability:</b> The RTL8201L is capable of performing IEEE Auto-negotiation, and will return a '1' when bit 4 is read, regardless of whether or not the Auto-negotiation function has been disabled.                                                            | 1, RO             |

|          |                                 | <ol> <li>Link had not been experienced fail state</li> <li>Link had been experienced fail state</li> </ol>                                                                                                                                                                       |                   |

| 1:<2> | Link Status            | Link Status: The RTL8201L will return a '1' on bit 2 when the link<br>state machine is in Link Pass, indicating that a valid link has been<br>established. Otherwise, it will return '0'. When a link failure occurs<br>after the link pass state has been entered, the Link Status bit will be<br>latched at '0' and will remain so until the bit is read. After the bit is<br>read, it becomes '1' if the Link Pass state has been entered again.<br>1: Valid link established | 0, RO |

|-------|------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|

| 1:<1> | Jabber Detect          | <ul> <li>0: No valid link established</li> <li>Jabber Detect: The RTL8201L will return a '1' on bit 1 if a jabber condition has been detected. After the bit is read, or if the chip is reset, it reverts to '0'. This is for 10Base-T only.</li> <li>1: Jabber condition detected</li> <li>0: No jabber condition detected</li> </ul>                                                                                                                                           | 0, RO |

| 1:<0> | Extended<br>Capability | <ul> <li>Extended Capability: The RTL8201L supports extended capability registers, and will return a '1' when bit 0 is read. Several extended registers have been implemented in the RTL8208, and their bit functions are defined later in this section.</li> <li>1: Extended register capability</li> <li>0: Basic register capability only</li> </ul>                                                                                                                          | 1, RO |

#### 6.3. Register 2 PHY Identifier 1

The PHY Identifier Registers #1 and #2 together form a unique identifier for the PHY section of this device. The Identifier consists of a concatenation of the Organizationally Unique Identifier (OUI), the vendor's model number and the model revision number. A PHY may return a value of zero in each of the 32 bits of the PHY Identifier if desired. The PHY Identifier is intended to support network management.

| Address  | Name   | Description/Usage                                | Default/Attribute |

|----------|--------|--------------------------------------------------|-------------------|

| 2:<15;0> | PHYID1 | PHY identifier ID for software recognize RTL8201 | 0000, RO          |

### 6.4. Register 3 PHY Identifier 2

| Address  | Name   | Description/Usage                                | Default/Attribute |

|----------|--------|--------------------------------------------------|-------------------|

| 3:<15;0> | PHYID2 | PHY identifier ID for software recognize RTL8201 | 8201, RO          |

### 6.5. Register 4 Auto-negotiation Advertisement

#### (ANAR)

This register contains the advertised abilities of this device as they will be transmitted to its link partner during Auto-negotiation.

| Auto-negotiat<br>Address | Name     | Description/Usage                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | Default/Attribute |

|--------------------------|----------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------|

| 4:<15>                   | NP       | <b>Next Page:</b> The RTL8201L does not implement the Next Page function, so bit 15 will always return a '0' when read.                                                                                                                                                                                                                                                                                                                                                                     | 0, RO             |

|                          |          | 0: Transmitting the primary capability data page<br>1: Transmitting the protocol specific data page                                                                                                                                                                                                                                                                                                                                                                                         |                   |

| 4:<14>                   | ACK      | Acknowledge: Because the Next Page function is not implemented, bit 14 will always return a '0' when read.                                                                                                                                                                                                                                                                                                                                                                                  | 0, RO             |

|                          |          | <ol> <li>Acknowledge reception of link partner capability data word</li> <li>Do not acknowledge reception</li> </ol>                                                                                                                                                                                                                                                                                                                                                                        |                   |

| 4:<13>                   | RF       | <b>Remote Fault:</b> Bit 13 returns a value of '1' when the RTL8201L has detected a remote fault. The RTL8201L advertises this information, but does not act upon it.                                                                                                                                                                                                                                                                                                                       | 0, RW             |

|                          |          | <ol> <li>Advertise remote fault detection capability</li> <li>Do not advertise remote fault detection capability</li> </ol>                                                                                                                                                                                                                                                                                                                                                                 |                   |

| 4:<12:11>                | Reserved | <b>Reserved:</b> Ignore the output of the RTL8201L when these bits are read.                                                                                                                                                                                                                                                                                                                                                                                                                |                   |

| 4:<10>                   | Pause    | <b>Pause:</b> The use of this bit is independent of the negotiated data rate, medium, or link technology. Setting this bit indicates the availability of additional DTE capabilities when full duplex operation is in use. This bit is used by one MAC to communicate Pause Capability to its Link Partner and has no effect on PHY operation.                                                                                                                                              | 0, RW             |

|                          |          | 1: Flow control is supported by local node<br>0: Flow control is NOT supported by local node                                                                                                                                                                                                                                                                                                                                                                                                |                   |

| 4:<9>                    | T4       | <b>100Base-T4:</b> This bit advertises the ability to the Link Partner that the RTL8201L can operate in 100Base-T4 mode. Writing a '0' to this bit will suppress the transmission of this ability to the Link Partner. Resetting the chip will restore the default value. The default value is '1' and writing a '1' will set this bit to '1'. Reading this bit will return the last written value or the default value if no write has been completed since the last reset.                | 0, RO             |

|                          |          | 1: 100Base-T4 is supported by local node<br>0: 100Base-T4 not supported by local node                                                                                                                                                                                                                                                                                                                                                                                                       |                   |

| 4:<8>                    | TXFD     | <b>100Base-TX-FD:</b> This bit advertises the ability to the Link Partner that the RTL8201L can operate in 100Base-TX full duplex mode. Writing a '0' to this bit will suppress the transmission of this ability to the Link Partner. Resetting the chip will restore the default value. The default value is '1' and writing a '1' will set this bit to '1'. Reading this bit will return the last written value or the default value if no write has been completed since the last reset. | 1, RW             |

|                          |          | 1: 100Base-TX full duplex is supported by local node<br>0: 100Base-TX full duplex not supported by local node                                                                                                                                                                                                                                                                                                                                                                               |                   |

| 4:<7>                    | TX       | <b>100Base-TX:</b> This bit advertises the ability to the Link Partner that the RTL8201L can operate in 100Base-TX half duplex mode. Writing a '0' to this bit will suppress the transmission of this ability to the Link Partner. Resetting the chip will restore the default value. The default value is '1' and writing a '1' will set this bit to '1'. Reading this bit will return the last written value or the default value if no write has been completed since the last reset.    | 1, RW             |

|                          |          | <ol> <li>1: 100Base-TX is supported by local node</li> <li>0: 100Base-TX not supported by local node</li> </ol>                                                                                                                                                                                                                                                                                                                                                                             |                   |

| 4:<6>   | 10FD     | <ul> <li>10Base-T-FD: This bit advertises the ability to the Link Partner that the RTL8201L can operate in 10Base-T full duplex mode. Writing a '0' to this bit will suppress the transmission of this ability to the Link Partner. Resetting the chip will restore the default value. The default value is '1' and writing a '1' will set this bit to '1'. Reading this bit will return the last written value or the default value if no write has been completed since the last reset.</li> <li>1: 10Base-T full duplex supported by local node</li> </ul> | 1, RW       |

|---------|----------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------|

| 4:<5>   | 10       | 0: 10Base-T full duplex not supported by local node<br><b>10Base-T:</b> This bit advertises the ability to the Link Partner that the<br>RTL8201L can operate in 10Base-T half duplex mode. Writing a '0' to<br>this bit will suppress the transmission of this ability to the Link Partner.<br>Resetting the chip will restore the default value. The default value is '1'<br>and writing a '1' will set this bit to '1'. Reading this bit will return the<br>last written value or the default value if no write has been completed<br>since the last reset. | 1, RW       |

| 4:<4:0> | Selector | <ul> <li>1: 10Base-T is supported by local node</li> <li>0: 10Base-T not supported by local node</li> <li>Selector Field: This field reflects the binary encoded selector supported by this node. Bits 4:0 contain a fixed value of &lt;00001&gt;, representing</li> </ul>                                                                                                                                                                                                                                                                                    | <00001>, RW |

|         |          | CSMA/CD, is specified. This indicates that the chip belongs to the 802.3 class of PHY transceivers. No other protocols are supported.                                                                                                                                                                                                                                                                                                                                                                                                                         |             |

# 6.6 Register 5 Auto-Negotiation Link Partner Ability (ANLPAR)

This register contains the advertised abilities of the Link Partner as received during Auto-negotiation. The content changes after the successful Auto-negotiation if Next-pages are supported.

| Address   | Name     | Description/Usage                                                                                                                                                                                                                                                                                         | Default/Attribute |

|-----------|----------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------|

| 5:<15>    | NP       | <b>Next Page:</b> Bit 15 returns a value of '1' when the Link Partner implements the Next Page function and has Next Page information that it wants to transmit. However, since the RTL8201L does not implement the Next Page function, it ignores the Next Page bit, except to copy it to this register. | 0, RO             |

|           |          | 0: Transmitting the primary capability data page<br>1: Transmitting the protocol specific data page                                                                                                                                                                                                       |                   |

| 5:<14>    | ACK      | Acknowledge: Bit 14 is used by Auto-negotiation to indicate that a device has successfully received its Link Partner's Link Code Word.                                                                                                                                                                    | 0, RO             |

|           |          | 1: Link partner acknowledges reception of local node's capability data word<br>0: No acknowledgement                                                                                                                                                                                                      |                   |

| 5:<13>    | RF       | <ul> <li>Remote Fault: Bit 13 returns a value of '1' when the Link Partner signals that it has detected a remote fault. The RTL8201L advertises this information, but does not act upon it.</li> <li>1: Link partner is indicating a remote fault</li> </ul>                                              | 0, RO             |

|           |          | 0: Link partner does not indicate a remote fault                                                                                                                                                                                                                                                          |                   |

| 5:<12:11> | Reserved | <b>Reserved:</b> Ignore the output of the RTL8201L when these bits are read.                                                                                                                                                                                                                              |                   |

| 5:<10>    | Pause    | <ul> <li>Pause: Indicates that the Link Partner pause bit is set.</li> <li>1: Flow control is supported by Link partner</li> <li>0: Flow control is NOT supported by Link partner</li> </ul>                                                                                                              | 0, RO             |

| 5:<9>     | T4       | <b>100Base-T4:</b> This bit indicates that the Link Partner can support 100Base-T4 mode. This bit is cleared any time Auto-negotiation is restarted or the RTL8201L is reset.                                                                                                                             | 0, RO             |

|           |          | <ol> <li>1: 100Base-T4 is supported by link partner</li> <li>0: 100Base-T4 not supported by link partner</li> </ol>                                                                                                                                                                                       |                   |

| 5:<8>   | TXFD     | <b>100Base-TX-FD:</b> This bit indicates that the Link Partner can support 100Base-TX full duplex mode. This bit is cleared any time Auto-negotiation is restarted or the RTL8201L is reset.                                                                                                                    | 0, RO       |

|---------|----------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------|

|         |          | 1: 100Base-TX full duplex is supported by link partner<br>0: 100Base-TX full duplex not supported by link partner                                                                                                                                                                                               |             |

| 5:<7>   | TX       | <b>100Base-TX:</b> This bit indicates that the Link Partner can support 100Base-TX half duplex mode. This bit is cleared any time Auto-negotiation is restarted or the RTL8201L is reset.                                                                                                                       | 1, RO       |

|         |          | <ol> <li>1: 100Base-TX is supported by link partner</li> <li>0: 100Base-TX not supported by link partner</li> </ol>                                                                                                                                                                                             |             |

|         |          | This bit will also be set after the link in 100Base is established by parallel detection and the RTL8201L Nway function is enabled but the link partner does not support Nway.                                                                                                                                  |             |

| 5:<6>   | 10FD     | <b>10Base-T-FD:</b> This bit indicates that the Link Partner can support 10Base-T full duplex mode. This bit is cleared any time Auto-negotiation is restarted or the RTL8201L is reset.                                                                                                                        | 0, RO       |

|         |          | 1: 10Base-T full duplex is supported by link partner<br>0: 10Base-T full duplex not supported by link partner                                                                                                                                                                                                   |             |

| 5:<5>   | 10       | <b>10Base-T:</b> This bit indicates that the Link Partner can support 10Base-T half duplex mode. This bit is cleared any time Auto-negotiation is restarted or the RTL8201L is reset.                                                                                                                           | 0, RO       |

|         |          | <ol> <li>10Base-T is supported by link partner</li> <li>10Base-T not supported by link partner</li> </ol>                                                                                                                                                                                                       |             |

|         |          | This bit will also be set after the link in 10Base is established by parallel detection and the RTL8201L Nway function is enabled but the link partner does not support Nway.                                                                                                                                   |             |

| 5:<4:0> | Selector | <b>Selector Field:</b> Bits 4:0 reflect the value of the Link Partner's selector field. These bits are cleared any time Auto-negotiation is restarted or the chip is reset, and generally reflect the value of <0001>, representing CSMA/CD, is specified, indicating that the Link Partner is an 802.3 device. | <00000>, RO |

Note that the values are only guaranteed to be valid once Auto-negotiation has successfully completed, as indicated by bit 5 of the MII Status Register.

#### 6.7 Register 6 Auto-negotiation Expansion (ANER)

This register contains additional status for NWay auto-negotiation.

| Address  | Name       | Description/Usage                                                                                                                                                                                                                                                                                                                                   | Default/Attribute |

|----------|------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------|

| 6:<15:5> | Reserved   | <b>Reserved:</b> Ignore the output of the RTL8201L when these bits are read. This bit is always set to 0.                                                                                                                                                                                                                                           |                   |

| 6:<4>    | MLF        | <b>Multiple Link Fault:</b> Status indicating if a multiple link fault has occurred. Bit 4 is a read-only bit that gets latched high when a multiple link fault occurs in the Auto-negotiation state machine. For further details, please consult the IEEE standard. The bit is reset to '0' after the register is read, or when the chip is reset. | 0, RO             |

|          |            | 1: Fault occurred<br>0: No fault occurred                                                                                                                                                                                                                                                                                                           |                   |

| 6:<3>    | LP_NP_ABLE | Link Partner Next Page Able: Status indicating if the link partner<br>supports Next Page negotiation. Bit 3 returns a '1' when the Link<br>Partner has Next Page capabilities. It has the same value as bit 15 of the<br>Link Partner Ability Register.                                                                                             | 0, RO             |

|          |            | 1: Supported<br>0: Not supported                                                                                                                                                                                                                                                                                                                    |                   |

| 6:<2>    | NP_ABLE    | <b>Local Next Page Able:</b> This bit indicates if the local node is able to send additional Next Pages. The RTL8201L does not have Next Page capabilities, so it will always return a '0' when bit 2 is read.                                                                                                                                      | 0, RO             |

| 6:<1>    | PAGE_RX    | <b>Page Received:</b> This bit is set high when a new Link Code Word Page has been received from the Link Partner, checked and acknowledged. This bit is cleared when the link is lost or the chip is reset. It is automatically cleared when the auto-negotiation link partner's ability register (register 5) is read by management.              | 0, RO             |

| 6:<0>    | LP_NW_ABLE | <b>Link Partner Auto-Negotiation Able:</b> Bit 0 returns a '1' when the Link Partner is known to have Auto-negotiation capabilities. Before any Auto-negotiation information is exchanged, or if the Link Partner does not comply with IEEE Auto-negotiation, the bit returns a value of '0'.                                                       | 0, RO             |

|          |            | <ol> <li>Link partner supports Nway auto-negotiation</li> <li>Link partner does not support Nway auto-negotiation</li> </ol>                                                                                                                                                                                                                        |                   |

#### 6.8 Register 16 Nway Setup (NSR)

| Address    | Name     | Description/Usage                                      | Default/Attribute |

|------------|----------|--------------------------------------------------------|-------------------|

| 16:<15:12> | Reserved | Ignore the results of these bits when read.            |                   |

| 16:<11>    | ENNWLE   | 1: LED4 Pin indicates linkpulse                        | 0, RW             |

| 16:<10>    | Testfun  | 1: Auto-neg speeds up internal timer                   | 0, RW             |

| 16:<9>     | NWLPBK   | 1: Set Nway to loopback mode.                          | 0, RW             |

| 16:<8:3>   | Reserved | Ignore the results of these bits when read.            |                   |

| 16:<2>     | FLAGABD  | 1: Auto-neg experienced ability detect state           | 0, RO             |

| 16:<1>     | FLAGPDF  | 1: Auto-neg experienced parallel detection fault state | 0, RO             |

| 16:<0>     | FLAGLSC  | 1: Auto-neg experienced link status check state        | 0, RO             |

#### 6.9 Register 17 Loopback, Bypass, Receiver Error Mask (LBREMR)

| Address  | Name                                 | Description/Usage                                                             | Default/Attribute |  |  |

|----------|--------------------------------------|-------------------------------------------------------------------------------|-------------------|--|--|

| 17:<15>  | RPTR                                 | Set to 1 to put the RTL8201(L) into repeater mode                             | 0, RW             |  |  |

| 17:<14>  | BP_4B5B                              | Assertion of this bit allows bypassing of the 4B/5B & 5B/4B encoder.          | 0, RW             |  |  |

| 17:<13>  | BP_SCR                               | Assertion of this bit allows bypassing of the scrambler/descrambler.          | 0, RW             |  |  |

| 17:<12>  | LDPS                                 | Set to 1 to enable Link Down Power Saving mode                                | 0, RW             |  |  |

| 17:<11>  | AnalogOFF                            | Set to 1 to power down analog function of transmitter and receiver.           | 0, RW             |  |  |

| 17:<10>  | Reserved                             | Ignore the results of this bit when read.                                     |                   |  |  |

| 17:<9:8> | LB<1:0>                              | LB<1:0> are register bits for loopback control as defined below:              | <0, 0>, RW        |  |  |

|          |                                      | 1) 0 0 for normal mode;                                                       |                   |  |  |

|          |                                      | 2) 0 1 for PHY loopback;                                                      |                   |  |  |

|          |                                      | 3) 1 0 for twister loopback                                                   |                   |  |  |

| 17:<7>   | F_Link_100                           | Used to logic force good link in 100Mbps for diagnostic purposes.             | 1, RW             |  |  |

| 17:<6:5> | Reserved                             | Ignore the results of these bits when read.                                   |                   |  |  |

| 17:<4>   | CODE_err                             | Assertion of this bit causes a code error detection to be reported.           | 0, RW             |  |  |

| 17:<3>   | PME_err                              | Assertion of this bit causes a pre-mature end error detection to be reported. | 0, RW             |  |  |

| 17:<2>   | LINK_err                             | Assertion of this bit causes a link error detection to be reported.           | 0, RW             |  |  |

| 17:<1>   | PKT_err                              | Assertion of this bit causes a detection of packet errors due to 722 ms       | 0, RW             |  |  |

|          |                                      | time-out to be reported.                                                      |                   |  |  |

| 17:<0>   | RWPara                               | Parameter access enable, set 1 to access register 20~24                       | 0, RW             |  |  |

| 6.10 Re  | 6.10 Register 18 RX_ER Counter (REC) |                                                                               |                   |  |  |

| A .].]   | NI                                   |                                                                               | D.f               |  |  |

| Address   | Name    | Description/Usage                                                   | Default/Attribute |

|-----------|---------|---------------------------------------------------------------------|-------------------|

| 18:<15:0> | RXERCNT | This 16-bit counter increments by 1 for each valid packet received. | H'[0000], RW      |

#### 6.11 Register 19 10Mbps Network Interface Configuration

| Address   | Name     | Description/Usage                                                                                                           | Default/Attribute |

|-----------|----------|-----------------------------------------------------------------------------------------------------------------------------|-------------------|

| 19:<15:6> | Reserved | Ignore the results of these bits when read.                                                                                 |                   |

| 19:<5>    | LD       | This bit is the active low TPI link disable signal. When low TPIstilltransmit link pulses and TPI stays in good link state. | 1, RW             |

| 19:<4:2>  | Reserved | Ignore the results of these bits when read.                                                                                 |                   |

| 19:<1>    | HBEN     | Heart beat enable                                                                                                           | 1, RW             |

| 19:<0>    | JBEN     | <ol> <li>Enable jabber function</li> <li>Disable jabber function</li> </ol>                                                 | 1, RW             |

## 6.12 Register 20 PHY 1\_1

| Address   | Name   | Description/Usage                          | Default/Attribute |

|-----------|--------|--------------------------------------------|-------------------|

| 20:<15:0> | PHY1_1 | PHY 1 register (functions as RTL8139C<78>) | R/W               |

# 6.13 Register 21 PHY 1\_2

| Address   | Name   | Description/Usage                          | Default/Attribute |

|-----------|--------|--------------------------------------------|-------------------|

| 21:<15:0> | PHY1_2 | PHY 1 register (functions as RTL8139C<78>) | R/W               |

#### 6.13 Register 22 PHY 2

| Address  | Name    | Description/Usage                                               | Default/Attribute |

|----------|---------|-----------------------------------------------------------------|-------------------|

| 22<15:8> | PHY2_76 | PHY2 register for cable length test (functions as RTL8139C<76>) | RO                |

| 22:<7:0> | PHY2_80 | PHY2 register for PLL select (functions as RTL8139C<80>)        | R/W               |

#### 6.14 Register 23 Twister\_1

| Address   | Name | Description/Usage                            | Default/Attribute |

|-----------|------|----------------------------------------------|-------------------|

| 23:<15:0> | TW_1 | Twister register (functions as RTL8139C<7c>) | R/W               |

#### 6.15 Register 24 Twister\_2

| Address   | Name | Description/Usage                            | Default/Attribute |

|-----------|------|----------------------------------------------|-------------------|

| 24:<15:0> | TW_2 | Twister register (functions as RTL8139C<7c>) | R/W               |

#### 7. Functional Description

The RTL8201(L) Phyceiver is a physical layer device that integrates 10Base-T and 100Base-TX functions and some extra power manage features into a 48 pin single chip which is used in 10/100 Fast Ethernet applications. This device supports the following functions:

- > MII interface with MDC/MDIO management interface to communicate with MAC

- IEEE 802.3u clause 28 Auto-Negotiation ability

- > Flow control ability support to cooperate with MAC

- > Speed, duplex, auto-negotiation ability configurable by hard wire or MDC/MDIO.

- ➢ Flexible LED configuration.

- > 7-wire SNI(Serial Network Interface) support, works only on 10Mbps mode.

- Power Down mode support

- ➢ 4B/5B transform

- Scrambling/De-scrambling

- NRZ to NRZI, NRZI to MLT3

- Manchester Encode and Decode for 10 BaseT operation

- Clock and Data recovery

- Adaptive Equalization

#### 7.1 MII and Management Interface

To set the RTL8201(L) for MII mode operation, pull MII/SNIB pin high and properly set the ANE, SPEED, and DUPLEX pins.

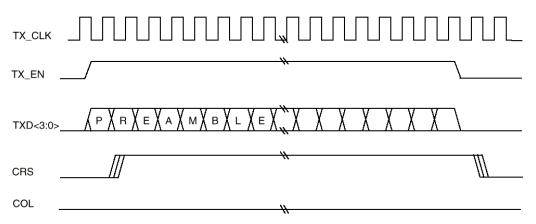

The MII (Media Independent Interface) is an 18-signal interface which is described in IEEE 802.3u supplying a standard interface between PHY and MAC layer. This interface operates in two frequencies – 25Mhz and 2.5Mhz to support 100Mbps/10Mbps bandwidth for both the transmit and receive function. While transmitting packets, the MAC will first assert the TXEN signal and change byte data into 4 bits nibble and pass to the PHY by TXD[0..3]. PHY will sample TXD[0..] synchronously with TXC — the transmit clock signal supplied by PHY – during the interval TXEN is asserted. While receiving a packet, the PHY will assert the RXEN signal, pass the received nibble data RXD[0..3] clocked by RXC, which is recovered from the received data. CRS and COL signals are used for collision detection and handling.

The MAC layer device can control PHY by the MDC/MDIO management interface, but for proper operation, the PHY address needs to be well configured so the management command can be delivered to the PHY. The MDC can be software generated to clock the 1 bit serial data stream to/from the MDIO to access the registers of the PHY.

In 100Base-TX mode, when decoded signal in 5B is not IDLE, the CRS signal will assert and when 5B is recognized as IDLE it will be de-asserted. In 10Base-T mode, CRS will assert when the 10M preamble been confirmed and will be de-asserted when the IDLE pattern been confirmed.

The RXDV signal will be asserted when decoded 5B are /J/K/and will be deasserted if the 5B are /T/R/or IDLE in 100Mbps mode. In 10Mbps mode, the RXDV signal is the same as the CRS signal.

The RTL8201(L) does not use the TXER signal and will not affect the transmit function.

#### 7.2 Auto-negotiation and Parallel Detection