#### Features

• High Performance:

|                 |                                   | -6   | к    | -7   | ΥK   | -7   | Units |

|-----------------|-----------------------------------|------|------|------|------|------|-------|

| f <sub>CK</sub> | Clock<br>Frequency                | 166  | 133  | 143  | 133  | 143  | MHz   |

| t <sub>СК</sub> | Clock Cycle                       | 6    | 7.5  | 7    | 7.5  | 7    | ns    |

| CL              | CAS Latency                       | CL=3 | CL=2 | CL=3 | CL=2 | CL=3 | CKs   |

| t <sub>AC</sub> | Clock Access<br>Time <sup>1</sup> |      | —    |      | —    | —    | ns    |

| t <sub>AC</sub> | Clock Access<br>Time <sup>2</sup> | 5.4  | 5.4  | 5.4  | 5.4  | 5.4  | ns    |

Terminated load. See AC Characteristics on page 16.

Unterminated load. See AC Characteristics on page 16.

- Single Pulsed RAS Interface

- Fully Synchronous to Positive Clock Edge

- Four Banks controlled by BS0/BS1 (Bank Select)

## Description

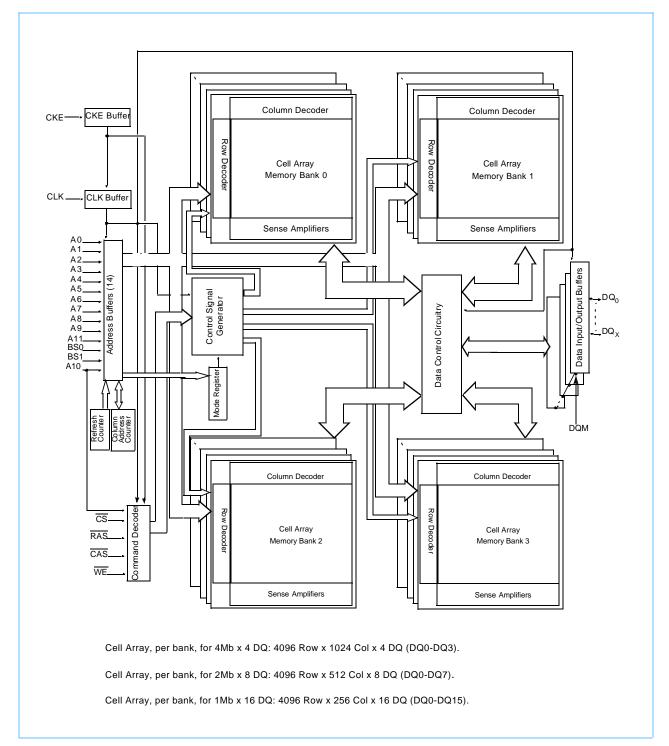

The NT5SV16M4DT, NT5SV8M8DT, and NT5SV4M16DT are four-bank Synchronous DRAMs organized as 4Mbit x 4 I/O x 4 Bank, 2Mbit x 8 I/O x 4 Bank, and 1Mbit x 16 I/O x 4 Bank, respectively. These synchronous devices achieve high-speed data transfer rates of up to 200MHz by employing a pipeline chip architecture that synchronizes the output data to a system clock. The chip is fabricated with NTC' s advanced 64Mbit single transistor CMOS DRAM process technology.

The device is designed to comply with all JEDEC standards set for synchronous DRAM products, both electrically and mechanically. All of the control, address, and data input/output (I/O or DQ) circuits are synchronized with the positive edge of an externally supplied clock.

RAS, CAS, WE, and CS are pulsed signals which are examined at the positive edge of each externally applied clock (CK). Internal chip operating modes are defined by combinations of these signals and a command decoder initiates the necessary timings for each operation. A fourteen bit address bus accepts address data in the conventional RAS/CAS mul-

- Programmable CAS Latency: 2, 3

- Programmable Burst Length: 1, 2, 4, 8, Full page

- Programmable Wrap: Sequential or Interleave

- Multiple Burst Read with Single Write Option

- Automatic and Controlled Precharge Command

- Data Mask for Read/Write control (x4, x8)

- Dual Data Mask for byte control (x16)

- Auto Refresh (CBR) and Self Refresh

- Suspend Mode and Power Down Mode

- Standard Power operation

- 4096 refresh cycles/64ms

- Random Column Address every CK (1-N Rule)

- Single 3.3V ? 0.3V Power Supply

- LVTTL compatible

- Package: 54-pin 400 mil TSOP-Type II

tiplexing style. Twelve row addresses (A0-A11) and two bank select addresses (BS0, BS1) are strobed with RAS. Eleven column addresses (A0-A9) plus bank select addresses and A10 are strobed with CAS. Column address A9 is dropped on the x8 device, and column addresses A8 and A9 are dropped on the x16 device.

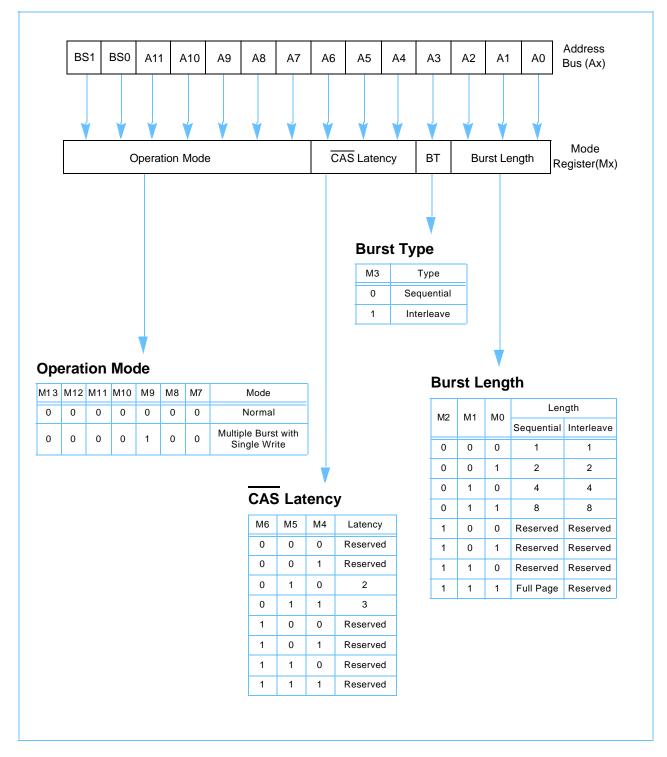

Prior to any access operation, the  $\overline{CAS}$  latency, burst length, and burst sequence must be programmed into the device by address inputs A0-A11, BS0, BS1 during a mode register set cycle. In addition, it is possible to program a multiple burst sequence with single write cycle for write through cache operation.

Operating the four memory banks in an interleave fashion allows random access operation to occur at a higher rate than is possible with standard DRAMs. A sequential and gapless data rate of up to 200MHz is possible depending on burst length, CAS latency, and speed grade of the device. Simultaneous operation of both decks of a stacked device is allowed, depending on the operation being done. Auto Refresh (CBR) and Self Refresh operation are supported.

Pin Assignments for Planar Components (Top View)

|                         |                         | 1Mbit x 16 1/0<br>NT5SV4         |                                  |                         |                          |  |

|-------------------------|-------------------------|----------------------------------|----------------------------------|-------------------------|--------------------------|--|

|                         |                         | 2Mbit x 8 I/C<br>NT5SV8          | BM8DT                            |                         |                          |  |

|                         |                         | 4Mbit x 4 I/0<br>NT5SV1          |                                  |                         |                          |  |

|                         |                         | 54-pin Plastic T                 |                                  |                         |                          |  |

| V <sub>DD</sub>         | V <sub>DD</sub>         | V <sub>DD</sub> [ 27             | 28 ] V <sub>SS</sub>             | V <sub>SS</sub>         | V <sub>SS</sub>          |  |

| A2<br>A3                | A2<br>A3                | A2 [ 25<br>A3 [ 26               | 30 ] A5<br>29 ] A4               | A5<br>A4                | A5<br>A4                 |  |

| A1                      | A1                      | A1 🛛 24                          | 31 🛛 A6                          | A6                      | A6                       |  |

| A10/AP<br>A0            | A10/AP<br>A0            | A10/AP [ 22<br>A0 [ 23           | 33   A8<br>32   A7               | A8<br>A7                | A8<br>A7                 |  |

| BS1<br>A10/AP           | BS1                     | BS1 [ 21                         | 34 ] A9                          | A9                      | A9                       |  |

| BS0                     | BS0                     | BS0 [ 20                         | 35 🛛 A11                         | A11                     | A11                      |  |

|                         |                         |                                  | 36 ] NC                          | NC                      | NC                       |  |

| CAS<br>RAS              | CAS<br>RAS              | CAS [ 17<br>RAS [ 18             | 38 ] CK<br>37 ] CKE              | CK<br>CKE               | CK<br>CKE                |  |

| WE                      | WE                      |                                  | 39 ] DQM                         | DQM                     | UDQM                     |  |

| LDQM                    | NC                      | NC [ 15                          | 40 ] NC                          | NC                      | NC                       |  |

| V <sub>DD</sub>         | V <sub>DD</sub>         | V <sub>DD</sub> [ 14             | 42   NC<br>41   V <sub>SS</sub>  | V <sub>SS</sub>         | V <sub>SS</sub>          |  |

| V <sub>SSQ</sub><br>DQ7 | V <sub>SSQ</sub><br>NC  | V <sub>SSQ</sub> [ 12<br>NC [ 13 | 43   V <sub>DDQ</sub><br>42   NC | V <sub>DDQ</sub><br>NC  | V <sub>DDQ</sub><br>DQ8  |  |

| DQ6                     | DQ3                     | DQ1 [ 11                         | 44 ] DQ2                         | DQ4                     | DQ9                      |  |

| DQ5                     | NC                      | NC [ 10                          | 45 🛛 NC                          | NC                      | DQ10                     |  |

| V <sub>DDQ</sub>        | V <sub>DDQ</sub>        | V <sub>DDQ</sub> [ 9             | 46 ] V <sub>SSQ</sub>            | V <sub>SSQ</sub>        | V <sub>SSQ</sub>         |  |

| DQ3<br>DQ4              | NC<br>DQ2               |                                  | 48   NC<br>47   NC               | DQ5                     | DQ12<br>DQ11             |  |

| V <sub>SSQ</sub><br>DQ3 | V <sub>SSQ</sub>        | V <sub>SSQ</sub> [ 6<br>NC [ 7   | 49   V <sub>DDQ</sub><br>48   NC | V <sub>DDQ</sub><br>NC  | V <sub>DDQ</sub><br>DQ12 |  |

| DQ2                     | DQ1                     | DQ0 [ 5                          | 50 ] DQ3                         | DQ6                     | DQ13                     |  |

| DQ1                     | NC                      | NC E 4                           | 51 ] NC                          | NC                      | DQ14                     |  |

| DQ0<br>V <sub>DDQ</sub> | DQ0<br>V <sub>DDQ</sub> | NC [ 2<br>V <sub>DDQ</sub> [ 3   | 53 ] NC<br>52 ] V <sub>SSQ</sub> | DQ7<br>V <sub>SSQ</sub> | DQ15<br>V <sub>SSQ</sub> |  |

#

## **Pin Description**

| СК       | Clock Input           | DQ0-DQ15         | Data Input/Output     |

|----------|-----------------------|------------------|-----------------------|

| CKE      | Clock Enable          | DQM, LDQM, UDQM  | Data Mask             |

| CS       | Chip Select           | V <sub>DD</sub>  | Power (+3.3V)         |

| RAS      | Row Address Strobe    | V <sub>SS</sub>  | Ground                |

| CAS      | Column Address Strobe | V <sub>DDQ</sub> | Power for DQs (+3.3V) |

| WE       | Write Enable          | V <sub>SSQ</sub> | Ground for DQs        |

| BS1, BS0 | Bank Select           | NC               | No Connection         |

| A0 - A11 | Address Inputs        | —                | —                     |

# Input/Output Functional Description

| Symbol                            | Туре             | Polarity         | Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|-----------------------------------|------------------|------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| CLK                               | Input            | Positive<br>Edge | The system clock input. All of the SDRAM inputs are sampled on the rising edge of the clock.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| CKE                               | Input            | Active High      | Activates the CLK signal when high and deactivates the CLK signal when low. By deactivating the<br>clock, CKE low initiates the Power Down mode, Suspend mode, or the Self Refresh mode.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| cs                                | Input            | Active Low       | CS enables the command decoder when low and disables the command decoder when high. When the command decoder is disabled, new commands are ignored but previous operations continue.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| RAS, CAS,<br>WE                   | Input            | Active Low       | When sampled at the positive rising edge of the clock, $\overline{CAS}$ , $\overline{RAS}$ , and $\overline{WE}$ define the operation to be executed by the SDRAM.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| BS0, BS1                          | Input            | —                | Selects which bank is to be active.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| A0 - A11                          | Input            | —                | During a Bank Activate command cycle, A0-A11 defines the row address (RA0-RA11) when sampled at<br>the rising clock edge.<br>During a Read or Write command cycle, A0-A9 defines the column address (CA0-CA9) when sampled<br>at the rising clock edge.<br>A10 is used to invoke auto-precharge operation at the end of the burst read or write cycle. If A10 is<br>high, auto-precharge is selected and BS0, BS1 defines the bank to be precharged. If A10 is low, auto-<br>precharge is disabled.<br>During a Precharge command cycle, A10 is used in conjunction with BS0, BS1 to control which bank(s)<br>to precharge. If A10 is high, all banks will be precharged regardless of the state of BS. If A10 is low,<br>then BS0 and BS1 are used to define which bank to precharge. |

| DQ0 - DQ15                        | Input-<br>Output | —                | Data Input/Output pins operate in the same manner as on conventional DRAMs.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| DQM<br>LDQM<br>UDQM               | Input            | Active High      | The Data Input/Output mask places the DQ buffers in a high impedance state when sampled high. In x16 products, LDQM and UDQM control the lower and upper byte I/O buffers, respectively. In Read mode, DQM has a latency of two clock cycles and controls the output buffers like an output enable. DQM low turns the output buffers on and DQM high turns them off. In Write mode, DQM has a latency of zero and operates as a word mask by allowing input data to be written if it is low but blocks the write operation if DQM is high.                                                                                                                                                                                                                                             |

| V <sub>DD</sub> , V <sub>SS</sub> | Supply           | _                | Power and ground for the input buffers and the core logic.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| V <sub>DDQ</sub> V <sub>SSQ</sub> | Supply           | —                | Isolated power supply and ground for the output buffers to provide improved noise immunity.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

## NT5SV16M4DT NT5SV8M8DT NT5SV4M16DT

# 64Mb Synchronous DRAM

# **Ordering Information**

| Organization | Part Number    |                       | Speed Grade   |               | Power  | Baakaga                  |

|--------------|----------------|-----------------------|---------------|---------------|--------|--------------------------|

| Organization | Fart Number    | Clock Frequenc        | y@CAS Latency | Note          | Supply | Package                  |

|              | NT5SV16M4DT-6K | 166MHz@CL3            | 133MHz@CL2    |               |        |                          |

| 16M x 4      | NT5SV16M4DT-7K | 143MHz@CL3            | 133MHz@CL2    |               |        |                          |

|              | NT5SV16M4DT-7  | 143MHz@CL3            | 100MHz@CL2    | PC133 , PC100 | 3.3 V  |                          |

|              | NT5SV8M8DT-6K  | 166MHz@CL3            | 133MHz@CL2    |               |        |                          |

| 8M x 8       | NT5SV8M8DT-7K  | 143MHz@CL3            | 133MHz@CL2    |               |        | 400mil 54-PIN<br>TSOP II |

|              | NT5SV8M8DT-7   | 143MHz@CL3            | 100MHz@CL2    |               |        |                          |

|              | NT5SV4M16DT-6K | 166MHz@CL3            | 133MHz@CL2    |               |        |                          |

| 4M x 16      | NT5SV4M16DT-7K | 143MHz@CL3 133MHz@CL2 |               | ]             |        |                          |

|              | NT5SV4M16DT-7  | 143MHz@CL3            | 100MHz@CL2    | ]             |        |                          |

## NT5SV16M4DT NT5SV8M8DT NT5SV4M16DT

## 64Mb Synchronous DRAM

## **Block Diagram**

## Mode Register Operation (Address Input For Mode Set)

© NANYA TECHNOLOGY CORP. All rights reserved. NANYA TECHNOLOGY CORP. reserves the right to change Products and Specifications without notice.

### **Burst Mode Operation**

Burst mode operation is used to provide a constant flow of data to memory locations (write cycle), or from memory locations (read cycle). There are three parameters that define how the burst mode will operate. These parameters include burst sequence, burst length, and operation mode. The burst sequence and burst length are programmable, and are determined by address bits A0 - A3 during the Mode Register Set command. Operation mode is also programmable and is set by address bits A7 - A11, BS0, and BS1.

The burst type is used to define the order in which the burst data will be delivered or stored to the SDRAM. Two types of burst sequences are supported, sequential and interleaved. See the table below.

The burst length controls the number of bits that will be output after a Read Command, or the number of bits to be input after a Write Command. The burst length can be programmed to have values of 1, 2, 4, 8 or full page(actual page length is dependent on organization: x4, x8, or x16). Full page burst operation is only possible using the sequential burst type.

Burst operation mode can be normal operation or multiple burst with single write operation. Normal operation implies that the device will perform burst operations on both read and write cycles until the desired burst length is satisfied. Multiple burst with single write operation was added to support Write Through Cache operation. Here, the programmed burst length only applies to read cycles. All write cycles are single write operations when this mode is selected.

| Burst Length    | Starting Address (A2 A1 A0) | Sequential Addressing (decimal) | Interleave Addressing (decimal) |

|-----------------|-----------------------------|---------------------------------|---------------------------------|

| 2               | x x 0                       | 0, 1                            | 0, 1                            |

| 2               | x x 1                       | 1, 0                            | 1, 0                            |

|                 | x 0 0                       | 0, 1, 2, 3                      | 0, 1, 2, 3                      |

| 4               | x 0 1                       | 1, 2, 3, 0                      | 1, 0, 3, 2                      |

| 4               | x 1 0                       | 2, 3, 0, 1                      | 2, 3, 0, 1                      |

|                 | x 1 1                       | 3, 0, 1, 2                      | 3, 2, 1, 0                      |

|                 | 000                         | 0, 1, 2, 3, 4, 5, 6, 7          | 0, 1, 2, 3, 4, 5, 6, 7          |

|                 | 0 0 1                       | 1, 2, 3, 4, 5, 6, 7, 0          | 1, 0, 3, 2, 5, 4, 7, 6          |

|                 | 0 1 0                       | 2, 3, 4, 5, 6, 7, 0, 1          | 2, 3, 0, 1, 6, 7, 4, 5          |

| 8               | 0 1 1                       | 3, 4, 5, 6, 7, 0, 1, 2          | 3, 2, 1, 0, 7, 6, 5, 4          |

| 8               | 100                         | 4, 5, 6, 7, 0, 1, 2, 3          | 4, 5, 6, 7, 0, 1, 2, 3          |

|                 | 101                         | 5, 6, 7, 0, 1, 2, 3, 4          | 5, 4, 7, 6, 1, 0, 3, 2          |

|                 | 1 1 0                       | 6, 7, 0, 1, 2, 3, 4, 5          | 6, 7, 4, 5, 2, 3, 0, 1          |

|                 | 1 1 1                       | 7, 0, 1, 2, 3, 4, 5, 6          | 7, 6, 5, 4, 3, 2, 1, 0          |

| Full Page(Note) | nnn                         | Cn, Cn+1, Cn+2,                 | Not Supported                   |

## **Burst Length and Sequence**

**Note:** Page length is a function of I/O organization and column addressing.

x4 organization (CA0-CA9); Page Length = 1024 bits

x8 organization (CA0-CA8); Page Length = 512 bits

x16 organization (CA0-CA7); Page Length = 256 bits

## Command Truth Table (See note 1)

|                           |                            | Cł                | ΚE               |    |     |     |    |     | BS0.        |       | A11,          |       |

|---------------------------|----------------------------|-------------------|------------------|----|-----|-----|----|-----|-------------|-------|---------------|-------|

| Function                  | Device State               | Previous<br>Cycle | Current<br>Cycle | CS | RAS | CAS | WE | DQM | B30,<br>BS1 | A10   | A11,<br>A9-A0 | Notes |

| Mode Register Set         | Idle                       | н                 | Х                | L  | L   | L   | L  | Х   |             | OP Co | de            |       |

| Auto (CBR) Refresh        | Idle                       | н                 | н                | L  | L   | L   | н  | Х   | Х           | Х     | Х             |       |

| Entry Self Refresh        | Idle                       | н                 | L                | L  | L   | L   | н  | Х   | Х           | Х     | Х             |       |

| Exit Self Refresh         | Idle (Self-                | L                 | н                | н  | Х   | Х   | Х  | х   | х           | х     | х             |       |

| Exit Sell Refresh         | Refresh)                   | L                 | п                | L  | Н   | н   | н  | ^   | ^           | ^     | ^             |       |

| Single Bank Precharge     | See Current<br>State Table | н                 | х                | L  | L   | н   | L  | х   | BS          | L     | х             | 2     |

| Precharge all Banks       | See Current<br>State Table | н                 | х                | L  | L   | н   | L  | х   | х           | н     | x             |       |

| Bank Activate             | Idle                       | н                 | Х                | L  | L   | н   | н  | Х   | BS          | Row   | Address       | 2     |

| Write                     | Active                     | Н                 | Х                | L  | Н   | L   | L  | Х   | BS          | L     | Column        | 2     |

| Write with Auto-Precharge | Active                     | н                 | Х                | L  | н   | L   | L  | Х   | BS          | н     | Column        | 2     |

| Read                      | Active                     | н                 | Х                | L  | Н   | L   | н  | Х   | BS          | L     | Column        | 2     |

| Read with Auto-Precharge  | Active                     | н                 | Х                | L  | Н   | L   | н  | Х   | BS          | Н     | Column        | 2     |

| Burst Termination         | Active                     | н                 | Х                | L  | н   | н   | L  | Х   | х           | Х     | Х             | 3,8   |

| No Operation              | Any                        | Н                 | Х                | L  | Н   | н   | н  | Х   | Х           | Х     | Х             |       |

| Device Deselect           | Any                        | н                 | Х                | н  | Х   | Х   | Х  | Х   | Х           | Х     | Х             |       |

| Clock Suspend Mode Entry  | Active                     | Н                 | L                | Х  | Х   | Х   | Х  | Х   | Х           | Х     | Х             | 4     |

| Clock Suspend Mode Exit   | Active                     | L                 | н                | Х  | Х   | Х   | Х  | Х   | Х           | Х     | Х             | 4     |

| Data Write/Output Enable  | Active                     | н                 | Х                | Х  | Х   | Х   | Х  | L   | Х           | Х     | Х             | 5     |

| Data Mask/Output Disable  | Active                     | н                 | Х                | Х  | Х   | Х   | Х  | н   | Х           | Х     | Х             | 5     |

| Power Down Mode Entry     | Idle/Active                | н                 |                  | н  | Х   | Х   | Х  | x   | х           | х     | х             | 6, 7  |

| Fower Down Mode Entry     | Iule/Active                | П                 | L                | L  | Н   | н   | н  | ^   | ^           | ^     | ^             | 0, /  |

| Power Down Mode Exit      | Any (Power                 | L                 | Н                | н  | Х   | Х   | Х  | х   | х           | v     | х             | 67    |

| Fower Down Mode EXIT      | Down)                      | L                 | п                | L  | н   | н   | н  | ^   | ^           | Х     | ^             | 6, 7  |

1. All of the SDRAM operations are defined by states of CS, WE, RAS, CAS, and DQM at the positive rising edge of the clock. Operation of both decks of a stacked device at the same time is allowed, depending on the operation being performed on the other deck. Refer to the Current State Truth Table.

2. Bank Select (BS0, BS1): BS0, BS1 = 0,0 selects bank 0; BS0, BS1 = 1,0 selects bank 1; BS0, BS1 = 0,1 selects bank 2; BS0, BS1 = 1,1 selects bank 3.

3. During a Burst Write cycle there is a zero clock delay; for a Burst Read cycle the delay is equal to the CAS latency.

4. During normal access mode, CKE is held high and CK is enabled. When it is low, it freezes the internal clock and extends data Read and Write operations. One clock delay is required for mode entry and exit.

5. The DQM has two functions for the data DQ Read and Write operations. During a Read cycle, when DQM goes high at a clock timing the data outputs are disabled and become high impedance after a two-clock delay. DQM also provides a data mask function for Write cycles. When it activates, the Write operation at the clock is prohibited (zero clock latency).

6. All banks must be precharged before entering the Power Down Mode. (If this command is issued during a burst operation, the device state will be Clock Suspend Mode.) The Power Down Mode does not perform any refresh operations; therefore the device can't remain in this mode longer than the Refresh period (t<sub>REF</sub>) of the device. One clock delay is required for mode entry and exit.

7. A No Operation or Device Deselect Command is required on the next clock edge following CKE going high.

8. Device state is full page burst operation. Use of this command to terminate other burst length operations is illegal.

## **Clock Enable (CKE) Truth Table**

|                         | Cł                | ΚE               |    |     | Co  | mmand |             |          |                                                                     |      |

|-------------------------|-------------------|------------------|----|-----|-----|-------|-------------|----------|---------------------------------------------------------------------|------|

| Current State           | Previous<br>Cycle | Current<br>Cycle | CS | RAS | CAS | WE    | BS0,<br>BS1 | A11 - A0 | Action                                                              | Note |

|                         | н                 | Х                | Х  | Х   | Х   | Х     | Х           | Х        | INVALID                                                             | 1    |

|                         | L                 | н                | н  | Х   | Х   | Х     | х           | х        | Exit Self Refresh with Device Deselect                              | 2    |

|                         | L                 | н                | L  | н   | н   | н     | х           | Х        | Exit Self Refresh with No Operation                                 | 2    |

| Self Refresh            | L                 | н                | L  | н   | н   | L     | Х           | Х        | ILLEGAL                                                             | 2    |

|                         | L                 | н                | L  | н   | L   | х     | Х           | Х        | ILLEGAL                                                             | 2    |

|                         | L                 | н                | L  | L   | Х   | х     | Х           | х        | ILLEGAL                                                             | 2    |

|                         | L                 | L                | х  | Х   | Х   | х     | Х           | х        | Maintain Self Refresh                                               |      |

|                         | н                 | Х                | х  | Х   | Х   | х     | Х           | Х        | INVALID                                                             | 1    |

| Dower Down              | L                 | н                | н  | Х   | Х   | Х     | х           | Х        | Power Down mode exit, all banks idle                                | 2    |

| Power Down              | L                 | н                | L  | Х   | Х   | х     | Х           | Х        | ILLEGAL                                                             | 2    |

|                         | L                 | L                | Х  | Х   | Х   | Х     | х           | Х        | Maintain Power Down Mode                                            |      |

|                         | н                 | н                | н  | Х   | Х   | Х     |             |          |                                                                     | 3    |

|                         | н                 | н                | L  | н   | Х   | х     |             |          | Refer to the Idle State section of the<br>Current State Truth Table | 3    |

|                         | н                 | н                | L  | L   | н   | Х     |             |          |                                                                     | 3    |

|                         | н                 | н                | L  | L   | L   | н     | х           | Х        | CBR Refresh                                                         |      |

|                         | н                 | н                | L  | L   | L   | L     | OP          | Code     | Mode Register Set                                                   | 4    |

| All Banks Idle          | н                 | L                | н  | Х   | Х   | х     |             |          |                                                                     | 3    |

|                         | н                 | L                | L  | н   | Х   | х     |             |          | Refer to the Idle State section of the<br>Current State Truth Table | 3    |

|                         | н                 | L                | L  | L   | н   | х     |             |          |                                                                     | 3    |

|                         | н                 | L                | L  | L   | L   | н     | Х           | х        | Entry Self Refresh                                                  | 4    |

|                         | н                 | L                | L  | L   | L   | L     | OP          | Code     | Mode Register Set                                                   |      |

|                         | L                 | Х                | х  | Х   | Х   | х     | Х           | Х        | Power Down                                                          | 4    |

|                         | н                 | н                | х  | х   | х   | х     | х           | x        | Refer to operations in the Current State<br>Truth Table             |      |

| Any State<br>other than | н                 | L                | Х  | Х   | Х   | х     | Х           | х        | Begin Clock Suspend next cycle                                      | 5    |

| listed above            | L                 | н                | Х  | Х   | Х   | х     | Х           | х        | Exit Clock Suspend next cycle                                       |      |

|                         | L                 | L                | Х  | х   | х   | х     | х           | Х        | Maintain Clock Suspend                                              |      |

1. For the given Current State CKE must be low in the previous cycle.

When CKE has a low to high transition, the clock and other inputs are re-enabled asynchronously. The minimum setup time for CKE (t<sub>CES</sub>) must be satisfied. When exiting power down mode, a NOP command (or Device Deselect Command) is required on the first rising clock after CKE goes high (see page 26).

3. The address inputs depend on the command that is issued. See the Idle State section of the Current State Truth Table for more information.

4. The Precharge Power Down Mode, the Self Refresh Mode, and the Mode Register Set can only be entered from the all banks idle state.

5. Must be a legal command as defined in the Current State Truth Table.

| Current State |    |     |     |    |         | nmand       |                      | Action                                   | Note |

|---------------|----|-----|-----|----|---------|-------------|----------------------|------------------------------------------|------|

|               | CS | RAS | CAS | WE | BS0,BS1 | A11 - A0    | Description          |                                          |      |

|               | L  | L   | L   | L  | OF      | P Code      | Mode Register Set    | Set the Mode Register                    | 2    |

|               | L  | L   | L   | н  | Х       | Х           | Auto or Self Refresh | Start Auto or Self Refresh               | 2, 3 |

|               | L  | L   | н   | L  | BS      | Х           | Precharge            | No Operation                             |      |

|               | L  | L   | н   | н  | BS      | Row Address | Bank Activate        | Activate the specified bank and row      |      |

| Idle          | L  | н   | L   | L  | BS      | Column      | Write w/o Precharge  | ILLEGAL                                  | 4    |

|               | L  | н   | L   | н  | BS      | Column      | Read w/o Precharge   | ILLEGAL                                  | 4    |

|               | L  | н   | н   | L  | Х       | Х           | Burst Termination    | No Operation                             |      |

|               | L  | н   | н   | н  | Х       | Х           | No Operation         | No Operation                             |      |

|               | Н  | Х   | Х   | Х  | Х       | Х           | Device Deselect      | No Operation or Power Down               | 5    |

|               | L  | L   | L   | L  | OF      | P Code      | Mode Register Set    | ILLEGAL                                  |      |

|               | L  | L   | L   | н  | Х       | Х           | Auto or Self Refresh | ILLEGAL                                  |      |

|               | L  | L   | н   | L  | BS      | Х           | Precharge            | Precharge                                | 6    |

|               | L  | L   | н   | н  | BS      | Row Address | Bank Activate        | ILLEGAL                                  | 4    |

| Row Active    | L  | н   | L   | L  | BS      | Column      | Write                | Start Write; Determine if Auto Precharge | 7,   |

|               | L  | н   | L   | н  | BS      | Column      | Read                 | Start Read; Determine if Auto Precharge  | 7,   |

|               | L  | н   | н   | L  | Х       | Х           | Burst Termination    | No Operation                             |      |

| -             | L  | Н   | н   | н  | Х       | Х           | No Operation         | No Operation                             |      |

|               | н  | Х   | Х   | Х  | Х       | Х           | Device Deselect      | No Operation                             |      |

|               | L  | L   | L   | L  | OF      | P Code      | Mode Register Set    | ILLEGAL                                  |      |

|               | L  | L   | L   | н  | Х       | Х           | Auto or Self Refresh | ILLEGAL                                  |      |

|               | L  | L   | н   | L  | BS      | Х           | Precharge            | Terminate Burst; Start the Precharge     |      |

|               | L  | L   | н   | н  | BS      | Row Address | Bank Activate        | ILLEGAL                                  | 4    |

| Read          | L  | н   | L   | L  | BS      | Column      | Write                | Terminate Burst; Start the Write cycle   | 8, 9 |

|               | L  | н   | L   | н  | BS      | Column      | Read                 | Terminate Burst; Start a new Read cycle  | 8, 9 |

|               | L  | н   | н   | L  | Х       | Х           | Burst Termination    | Terminate the Burst                      |      |

|               | L  | н   | н   | н  | Х       | Х           | No Operation         | Continue the Burst                       |      |

|               | н  | Х   | Х   | Х  | Х       | Х           | Device Deselect      | Continue the Burst                       |      |

|               | L  | L   | L   | L  | OF      | P Code      | Mode Register Set    | ILLEGAL                                  |      |

|               | L  | L   | L   | н  | Х       | Х           | Auto or Self Refresh | ILLEGAL                                  |      |

|               | L  | L   | н   | L  | BS      | Х           | Precharge            | Terminate Burst; Start the Precharge     |      |

|               | L  | L   | н   | н  | BS      | Row Address | Bank Activate        | ILLEGAL                                  | 4    |

| Write         | L  | Н   | L   | L  | BS      | Column      | Write                | Terminate Burst; Start a new Write cycle | 8, 9 |

|               | L  | Н   | L   | н  | BS      | Column      | Read                 | Terminate Burst; Start the Read cycle    | 8, 9 |

|               | L  | Н   | н   | L  | Х       | Х           | Burst Termination    | Terminate the Burst                      |      |

|               | L  | Н   | н   | н  | Х       | Х           | No Operation         | Continue the Burst                       |      |

|               | н  | Х   | Х   | Х  | Х       | Х           | Device Deselect      | Continue the Burst                       |      |

#### Current State Truth Table (Part 1 of 3)(See note 1)

1. CKE is assumed to be active (high) in the previous cycle for all entries. The Current State is the state of the bank that the Command is being applied to.

2. All Banks must be idle; otherwise, it is an illegal action.

3. If CKE is active (high) the SDRAM will start the Auto (CBR) Refresh operation, if CKE is inactive (low) than the Self Refresh mode is entered.

4. The Current State refers to only one of the banks. If BS selects this bank then the action is illegal. If BS selects the bank not being referenced by the Current State then the action may be legal depending on the state of that bank.

5. If CKE is inactive (low) then the Power Down mode is entered; otherwise there is a No Operation.

6. The <u>minimum and</u> maximum Active time  $(t_{RAS})$  must be satisfied.

7. The  $\overline{RAS}$  to  $\overline{CAS}$  Delay ( $t_{RCD}$ ) must occur before the command is given.

8. Column address A10 is used to determine if the Auto Precharge function is activated.

9. The command must satisfy any bus contention, bus turn around, and/or write recovery requirements.

10. The command is illegal if the minimum bank to bank delay time  $(t_{\mbox{\scriptsize RRD}})$  is not satisfied.

© NANYA TECHNOLOGY CORP. All rights reserved. NANYA TECHNOLOGY CORP. reserves the right to change Products and Specifications without notice.

#### Current State Truth Table (Part 2 of 3)(See note 1)

| Current State                |    | 1   |     |    |         | nmand       |                      | Action                                           | Note |

|------------------------------|----|-----|-----|----|---------|-------------|----------------------|--------------------------------------------------|------|

|                              | CS | RAS | CAS | WE | BS0,BS1 | A11 - A0    | Description          |                                                  |      |

|                              | L  | L   | L   | L  | OF      | P Code      | Mode Register Set    | ILLEGAL                                          |      |

|                              | L  | L   | L   | н  | Х       | Х           | Auto or Self Refresh | ILLEGAL                                          |      |

|                              | L  | L   | н   | L  | BS      | Х           | Precharge            | ILLEGAL                                          | 4    |

| Read with                    | L  | L   | н   | н  | BS      | Row Address | Bank Activate        | ILLEGAL                                          | 4    |

| Auto Pre-                    | L  | н   | L   | L  | BS      | Column      | Write                | ILLEGAL                                          | 4    |

| charge                       | L  | н   | L   | н  | BS      | Column      | Read                 | ILLEGAL                                          | 4    |

|                              | L  | н   | н   | L  | Х       | Х           | Burst Termination    | ILLEGAL                                          |      |

|                              | L  | н   | н   | н  | Х       | Х           | No Operation         | Continue the Burst                               |      |

|                              | Н  | Х   | Х   | Х  | Х       | Х           | Device Deselect      | Continue the Burst                               |      |

|                              | L  | L   | L   | L  | OF      | P Code      | Mode Register Set    | ILLEGAL                                          |      |

|                              | L  | L   | L   | н  | Х       | Х           | Auto or Self Refresh | ILLEGAL                                          |      |

|                              | L  | L   | н   | L  | BS      | Х           | Precharge            | ILLEGAL                                          | 4    |

|                              | L  | L   | н   | н  | BS      | Row Address | Bank Activate        | ILLEGAL                                          | 4    |

| Write with Auto<br>Precharge | L  | н   | L   | L  | BS      | Column      | Write                | ILLEGAL                                          | 4    |

| riconarge                    | L  | н   | L   | н  | BS      | Column      | Read                 | ILLEGAL                                          | 4    |

| -                            | L  | н   | н   | L  | Х       | Х           | Burst Termination    | ILLEGAL                                          |      |

|                              | L  | н   | н   | н  | Х       | Х           | No Operation         | Continue the Burst                               |      |

|                              | Н  | Х   | Х   | Х  | Х       | Х           | Device Deselect      | Continue the Burst                               |      |

|                              | L  | L   | L   | L  | OF      | P Code      | Mode Register Set    | ILLEGAL                                          |      |

|                              | L  | L   | L   | н  | Х       | Х           | Auto or Self Refresh | ILLEGAL                                          |      |

|                              | L  | L   | н   | L  | BS      | Х           | Precharge            | No Operation; Bank(s) idle after t <sub>RP</sub> |      |

|                              | L  | L   | н   | н  | BS      | Row Address | Bank Activate        | ILLEGAL                                          | 4    |

| Precharging                  | L  | н   | L   | L  | BS      | Column      | Write                | ILLEGAL                                          | 4    |

|                              | L  | н   | L   | н  | BS      | Column      | Read                 | ILLEGAL                                          | 4    |

|                              | L  | н   | н   | L  | Х       | Х           | Burst Termination    | No Operation; Bank(s) idle after t <sub>RP</sub> |      |

|                              | L  | н   | н   | н  | Х       | Х           | No Operation         | No Operation; Bank(s) idle after t <sub>RP</sub> |      |

|                              | Н  | Х   | Х   | Х  | Х       | Х           | Device Deselect      | No Operation; Bank(s) idle after t <sub>RP</sub> |      |

|                              | L  | L   | L   | L  | OF      | P Code      | Mode Register Set    | ILLEGAL                                          |      |

|                              | L  | L   | L   | н  | Х       | Х           | Auto or Self Refresh | ILLEGAL                                          |      |

|                              | L  | L   | н   | L  | BS      | Х           | Precharge            | ILLEGAL                                          | 4    |

| _                            | L  | L   | Н   | Н  | BS      | Row Address | Bank Activate        | ILLEGAL                                          | 4, 1 |

| Row<br>Activating            | L  | Н   | L   | L  | BS      | Column      | Write                | ILLEGAL                                          | 4    |

| Activating                   | L  | Н   | L   | Н  | BS      | Column      | Read                 | ILLEGAL                                          | 4    |

|                              | L  | Н   | Н   | L  | Х       | Х           | Burst Termination    | No Operation; Row Active after t <sub>RCD</sub>  |      |

|                              | L  | Н   | Н   | Н  | Х       | Х           | No Operation         | No Operation; Row Active after t <sub>RCD</sub>  |      |

|                              | Н  | Х   | Х   | Х  | Х       | Х           | Device Deselect      | No Operation; Row Active after t <sub>RCD</sub>  |      |

1. CKE is assumed to be active (high) in the previous cycle for all entries. The Current State is the state of the bank that the Command is being applied to.

2. All Banks must be idle; otherwise, it is an illegal action.

3. If CKE is active (high) the SDRAM will start the Auto (CBR) Refresh operation, if CKE is inactive (low) than the Self Refresh mode is entered.

4. The Current State refers to only one of the banks. If BS selects this bank then the action is illegal. If BS selects the bank not being referenced by the Current State then the action may be legal depending on the state of that bank.

5. If CKE is inactive (low) then the Power Down mode is entered; otherwise there is a No Operation.

6. The minimum and maximum Active time (t<sub>RAS</sub>) must be satisfied.

- 7. The  $\overline{RAS}$  to  $\overline{CAS}$  Delay (t<sub>RCD</sub>) must occur before the command is given.

- 8. Column address A10 is used to determine if the Auto Precharge function is activated.

- 9. The command must satisfy any bus contention, bus turn around, and/or write recovery requirements.

- 10. The command is illegal if the minimum bank to bank delay time ( ${\rm t}_{\rm RRD}$ ) is not satisfied.

#### Current State Truth Table (Part 3 of 3)(See note 1)

| Current State       |    |     |     |    |         | nmand       |                      | Action                                          | Note |

|---------------------|----|-----|-----|----|---------|-------------|----------------------|-------------------------------------------------|------|

|                     | CS | RAS | CAS | WE | BS0,BS1 | A11 - A0    | Description          |                                                 |      |

|                     | L  | L   | L   | L  | OF      | P Code      | Mode Register Set    | ILLEGAL                                         |      |

|                     | L  | L   | L   | н  | Х       | Х           | Auto or Self Refresh | ILLEGAL                                         |      |

|                     | L  | L   | н   | L  | BS      | Х           | Precharge            | ILLEGAL                                         | 4    |

|                     | L  | L   | н   | н  | BS      | Row Address | Bank Activate        | ILLEGAL                                         | 4    |

| Write<br>Recovering | L  | н   | L   | L  | BS      | Column      | Write                | Start Write; Determine if Auto Precharge        | 9    |

| recording           | L  | н   | L   | н  | BS      | Column      | Read                 | Start Read; Determine if Auto Precharge         | 9    |

|                     | L  | н   | н   | L  | Х       | Х           | Burst Termination    | No Operation; Row Active after t <sub>DPL</sub> |      |

|                     | L  | н   | н   | н  | Х       | Х           | No Operation         | No Operation; Row Active after t <sub>DPL</sub> |      |

|                     | н  | Х   | Х   | Х  | Х       | Х           | Device Deselect      | No Operation; Row Active after t <sub>DPL</sub> |      |

|                     | L  | L   | L   | L  | OF      | P Code      | Mode Register Set    | ILLEGAL                                         |      |

|                     | L  | L   | L   | н  | Х       | Х           | Auto or Self Refresh | ILLEGAL                                         |      |

|                     | L  | L   | н   | L  | BS      | Х           | Precharge            | ILLEGAL                                         | 4    |

| Write<br>Recovering | L  | L   | н   | н  | BS      | Row Address | Bank Activate        | ILLEGAL                                         | 4    |

| with                | L  | н   | L   | L  | BS      | Column      | Write                | ILLEGAL                                         | 4,   |

| Auto Pre-           | L  | н   | L   | н  | BS      | Column      | Read                 | ILLEGAL                                         | 4,   |

| charge              | L  | н   | н   | L  | Х       | Х           | Burst Termination    | No Operation; Precharge after t <sub>DPL</sub>  |      |

|                     | L  | н   | н   | н  | Х       | Х           | No Operation         | No Operation; Precharge after t <sub>DPL</sub>  |      |

|                     | Н  | Х   | Х   | Х  | Х       | Х           | Device Deselect      | No Operation; Precharge after t <sub>DPL</sub>  |      |

|                     | L  | L   | L   | L  | OF      | P Code      | Mode Register Set    | ILLEGAL                                         |      |

|                     | L  | L   | L   | н  | Х       | Х           | Auto or Self Refresh | ILLEGAL                                         |      |

|                     | L  | L   | н   | L  | BS      | Х           | Precharge            | ILLEGAL                                         |      |

|                     | L  | L   | н   | Н  | BS      | Row Address | Bank Activate        | ILLEGAL                                         |      |

| Refreshing          | L  | н   | L   | L  | BS      | Column      | Write                | ILLEGAL                                         |      |

|                     | L  | н   | L   | н  | BS      | Column      | Read                 | ILLEGAL                                         |      |

|                     | L  | н   | н   | L  | Х       | Х           | Burst Termination    | No Operation; Idle after t <sub>RC</sub>        |      |

|                     | L  | н   | н   | н  | Х       | Х           | No Operation         | No Operation; Idle after t <sub>RC</sub>        |      |

|                     | н  | Х   | Х   | Х  | Х       | Х           | Device Deselect      | No Operation; Idle after t <sub>RC</sub>        |      |

|                     | L  | L   | L   | L  | OF      | P Code      | Mode Register Set    | ILLEGAL                                         |      |

|                     | L  | L   | L   | Н  | Х       | Х           | Auto or Self Refresh | ILLEGAL                                         |      |

|                     | L  | L   | н   | L  | BS      | Х           | Precharge            | ILLEGAL                                         |      |

| Mode                | L  | L   | Н   | Н  | BS      | Row Address | Bank Activate        | ILLEGAL                                         |      |

| Register            | L  | н   | L   | L  | BS      | Column      | Write                | ILLEGAL                                         |      |

| Accessing           | L  | н   | L   | Н  | BS      | Column      | Read                 | ILLEGAL                                         |      |

|                     | L  | н   | н   | L  | Х       | Х           | Burst Termination    | ILLEGAL                                         |      |

|                     | L  | н   | н   | Н  | Х       | Х           | No Operation         | No Operation; Idle after two clock cycles       |      |

|                     | н  | Х   | Х   | Х  | Х       | Х           | Device Deselect      | No Operation; Idle after two clock cycles       |      |

1. CKE is assumed to be active (high) in the previous cycle for all entries. The Current State is the state of the bank that the Command is being applied to.

2. All Banks must be idle; otherwise, it is an illegal action.

3. If CKE is active (high) the SDRAM will start the Auto (CBR) Refresh operation, if CKE is inactive (low) than the Self Refresh mode is entered.

4. The Current State refers to only one of the banks. If BS selects this bank then the action is illegal. If BS selects the bank not being referenced by the Current State then the action may be legal depending on the state of that bank.

5. If CKE is inactive (low) then the Power Down mode is entered; otherwise there is a No Operation.

6. The minimum and maximum Active time (t<sub>RAS</sub>) must be satisfied.

- 7. The  $\overline{RAS}$  to  $\overline{CAS}$  Delay (t<sub>RCD</sub>) must occur before the command is given.

- 8. Column address A10 is used to determine if the Auto Precharge function is activated.

- 9. The command must satisfy any bus contention, bus turn around, and/or write recovery requirements.

- 10. The command is illegal if the minimum bank to bank delay time ( ${\rm t}_{\rm RRD}$ ) is not satisfied.

## **Absolute Maximum Ratings**

| Symbol           | Parameter                       | Rating                       | Units | Notes |

|------------------|---------------------------------|------------------------------|-------|-------|

| V <sub>DD</sub>  | Power Supply Voltage            | -0.3 to +4.6                 | V     | 1     |

| V <sub>DDQ</sub> | Power Supply Voltage for Output | -0.3 to +4.6                 | V     | 1     |

| V <sub>IN</sub>  | Input Voltage                   | -0.3 to V <sub>DD</sub> +0.3 | V     | 1     |

| V <sub>OUT</sub> | Output Voltage                  | -0.3 to V <sub>DD</sub> +0.3 | V     | 1     |

| Τ <sub>Α</sub>   | Operating Temperature (ambient) | 0 to +70                     | ?C    | 1     |

| T <sub>STG</sub> | Storage Temperature             | -55 to +125                  | ?C    | 1     |

| PD               | Power Dissipation               | 1.0                          | W     | 1     |

| IOUT             | Short Circuit Output Current    | 50                           | mA    | 1     |

1. Stresses greater than those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. This is a stress rating only and functional operation of the device at these or any other conditions above those indicated in the operational sections of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect reliability.

## Recommended DC Operating Conditions (T<sub>A</sub> = 0?C to 70?C)

| Cumbal           | Deservator                |      | Rating | Units                 | Notoo |      |

|------------------|---------------------------|------|--------|-----------------------|-------|------|

| Symbol           | ol Parameter Min. Typ.    |      | Max.   | Units                 | Notes |      |

| V <sub>DD</sub>  | Supply Voltage            | 3.0  | 3.3    | 3.6                   | V     | 1    |

| V <sub>DDQ</sub> | Supply Voltage for Output | 3.0  | 3.3    | 3.6                   | V     | 1    |

| VIH              | Input High Voltage        | 2.0  | —      | V <sub>DD</sub> + 0.3 | V     | 1, 2 |

| V <sub>IL</sub>  | Input Low Voltage         | -0.3 | _      | 0.8                   | V     | 1, 3 |

2.  $V_{IH}$  (max) =  $V_{DD}$  + 1.2V for pulse width ?5ns. 3.  $V_{IL}$  (min) =  $V_{SS}$  - 1.2V for pulse width ?5ns.

## Capacitance (T<sub>A</sub> = 25?C, f = 1MHz, V<sub>DD</sub> = 3.3V ? 0.3V)

| Symbol         | Parameter                                                        | Min. | Тур | Max. | Units |

|----------------|------------------------------------------------------------------|------|-----|------|-------|

| C              | Input Capacitance (A0-A11, BS0, BS1, CS, RAS, CAS, WE, CKE, DQM) | 2.5  | 3.0 | 3.8  | pF    |

| Ч              | Input Capacitance (CK)                                           | 2.5  | 2.8 | 3.5  | pF    |

| С <sub>О</sub> | Output Capacitance (DQ0 - DQ15)                                  | 4.0  | 4.5 | 6.5  | pF    |

# DC Electrical Characteristics (T<sub>A</sub> = 0 to +70 °C, V<sub>DD</sub> = 3.3V ?0.3V)

| Symbol            | Parameter                                                                                             | Min. | Max. | Units |

|-------------------|-------------------------------------------------------------------------------------------------------|------|------|-------|

| I <sub>I(L)</sub> | Input Leakage Current, any input (0.0V ? $V_{IN}$ ? $V_{DD}$ ), All Other Pins Not Under Test = 0V    | -1   | +1   | ?A    |

| I <sub>O(L)</sub> | Output Leakage Current<br>(D <sub>OUT</sub> is disabled, 0.0V ? V <sub>OUT</sub> ? V <sub>DDQ</sub> ) | -1   | +1   | ?A    |

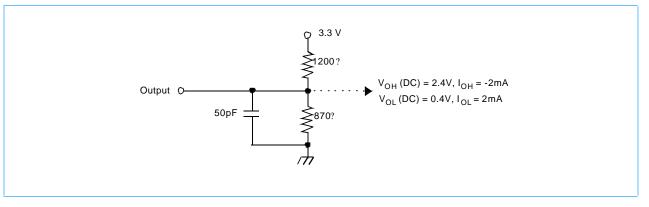

| V <sub>OH</sub>   | Output Level (LVTTL)<br>Output "H" Level Voltage ( <sub>IOUT</sub> = -2.0mA)                          | 2.4  | _    | v     |

| V <sub>OL</sub>   | Output Level (LVTTL)<br>Output "L" Level Voltage (I <sub>OUT</sub> = +2.0mA)                          | —    | 0.4  | V     |

# **DC Output Load Circuit**

## Operating, Standby, and Refresh Currents (T<sub>A</sub> = 0 to +70 °C, V<sub>DD</sub> = 3.3V °0.3V)

| Parameter                                           | Symbol             | Test Condition                                                                                                     | -6K   | -7K   | -7    | Unito   | Notas   |

|-----------------------------------------------------|--------------------|--------------------------------------------------------------------------------------------------------------------|-------|-------|-------|---------|---------|

| Parameter                                           | Symbol             | lest Condition                                                                                                     | (6ns) | (7ns) | (7ns) | Units   | Notes   |

| Operating Current                                   | I <sub>CC1</sub>   | 1 bank operation $t_{RC}$ = $t_{RC}(min), \ t_{CK}$ = min Active-Precharge command cycling without burst operation | 60 55 |       | mA    | 1, 2, 3 |         |

| Precharge Standby Current                           | I <sub>CC2P</sub>  | $\frac{CKE}{CS} ? V_{IL}(max), t_{CK} = min, \\ \frac{CKE}{CS} = V_{IH}(min)$                                      |       | 1     |       | mA      | 1       |

| in Power Down Mode                                  | I <sub>CC2PS</sub> | $\frac{CKE}{CS} ? V_{IL}(max), t_{CK} = Infinity, \\ \frac{CS}{CS} = V_{IH}(min)$                                  |       | 1     |       | mA      | 1       |

| Precharge Standby Current<br>in Non-Power Down Mode | I <sub>CC2N</sub>  | $\frac{CKE}{CS} ? V_{IH}(min), t_{CK} = min,$<br>$\frac{CKE}{CS} = V_{IH} (min)$                                   |       | 10    |       | mA      | 1, 5    |

|                                                     | I <sub>CC2NS</sub> | CKE ? V <sub>IH</sub> (min), t <sub>CK</sub> = Infinity,                                                           |       | 5     |       | mA      | 1, 7    |

| No Operating Current<br>(Active state: 4 bank)      | I <sub>CC3N</sub>  | $\frac{CKE}{CS} ? V_{IH}(min), t_{CK} = min,$<br>$\frac{CKE}{CS} = V_{IH} (min)$                                   |       | 30    |       | mA      | 1, 5    |

| (Active State: 4 Dalik)                             | I <sub>CC3P</sub>  | CKE ? V <sub>IL</sub> (max), t <sub>CK</sub> = min,                                                                |       | 9     |       | mA      | 1, 6    |

| Operating Current (Burst<br>Mode)                   | I <sub>CC4</sub>   | $t_{CK}$ = min,<br>Read/ Write command cycling,<br>Multiple banks active, gapless data,<br>BL = 4                  | 75    | 7     | 0     | mA      | 1, 3, 4 |

| Auto (CBR) Refresh Current                          | I <sub>CC5</sub>   | t <sub>CK</sub> = min, t <sub>RC</sub> = t <sub>RC</sub> (min)<br>CBR command cycling                              | 120   | 11    | 10    | mA      | 1       |

| Self Refresh Current                                | I <sub>CC6</sub>   | CKE ? 0.2V                                                                                                         |       | 1     |       | mA      | 1       |

1. Currents given are valid for a single device. The total current for a stacked device depends on the operation being performed on the other deck.

2. These parameters depend on the cycle rate and are measured with the cycle determined by the minimum value of  $t_{CK}$  and  $t_{RC}$ . Input signals are changed up to three times during  $t_{RC}$  (min).

3. The specified values are obtained with the output open.

4. Input signals are changed once during  $t_{CK}(min)$ .

5. Input signals are changed once during three clock cycles.

6. Active Standby Current will be higher if Clock Suspend is entered during a burst read cycle (add 1mA per DQ).

7. Input signals are stable.

#### NT5SV16M4DT NT5SV8M8DT NT5SV4M16DT

## 64Mb Synchronous DRAM

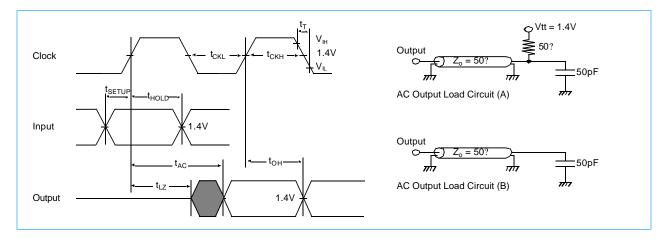

## **AC Characteristics** (T<sub>A</sub> = 0 to +70?C, V<sub>DD</sub> = 3.3V ??0.3V)

- 1. An initial pause of 200?s, with DQM and CKE held high, is required after power-up. A Precharge All Banks command must be given followed by a minimum of two Auto (CBR) Refresh cycles before or after the Mode Register Set operation.

- 2. The Transition time is measured between  $V_{IH}$  and  $V_{IL}$  (or between  $V_{IL}$  and  $V_{IH})$

- In addition to meeting the transition rate specification, the clock and CKE must transit between V<sub>IH</sub> and V<sub>IL</sub> (or between V<sub>IL</sub> and V<sub>IH</sub>) in a monotonic manner.

- 4. Load Circuit A: AC timing tests have  $V_{IL} = 0.4$  V and  $V_{IH} = 2.4$  V with the timing referenced to the 1.40V crossover point

- 5. Load Circuit A: AC measurements assume  $t_T = 1.0$ ns.

- 6. Load Circuit B: AC timing tests have  $V_{IL} = 0.8$  V and  $V_{IH} = 2.0$  V with the timing referenced to the 1.40V crossover point 7. Load Circuit B: AC measurements assume to 1.2 m

- 7. Load Circuit B: AC measurements assume  $t_T = 1.2ns$ .

## **AC Characteristics Diagrams**

### **Clock and Clock Enable Parameters**

| Symbol               | Parameter                                       | -6   | δK   | -7   | -7K  |      | 7    | Units | Notes |

|----------------------|-------------------------------------------------|------|------|------|------|------|------|-------|-------|

| Symbol               | Falanietei                                      | Min. | Max. | Min. | Max. | Min. | Max. | Units | Notes |

| t <sub>CK3</sub>     | Clock Cycle Time, CAS Latency = 3               | 6    | 1000 | 7    | 1000 | 7    | 1000 | ns    |       |

| t <sub>CK2</sub>     | Clock Cycle Time, $\overline{CAS}$ Latency = 2  | 7.5  | 1000 | 7.5  | 1000 | 10   | 1000 | ns    |       |

| t <sub>AC3 (A)</sub> | Clock Access Time, $\overline{CAS}$ Latency = 3 | —    | —    | —    | —    | —    | —    | ns    | 1     |

| t <sub>AC2 (A)</sub> | Clock Access Time, CAS Latency = 2              | —    | —    | —    | —    | —    | —    | ns    | 1     |

| t <sub>AC3 (B)</sub> | Clock Access Time, CAS Latency = 3              | -    | 5.4  | —    | 5.4  | —    | 5.4  | ns    | 2     |

| t <sub>AC2 (B)</sub> | Clock Access Time, $\overline{CAS}$ Latency = 2 | —    | 5.4  | —    | 5.4  | —    | 6    | ns    | 2     |

| t <sub>CKH</sub>     | Clock High Pulse Width                          | 2.5  | —    | 2.5  | —    | 3    | —    | ns    |       |

| t <sub>CKL</sub>     | Clock Low Pulse Width                           | 2.5  | —    | 2.5  | —    | 3    | —    | ns    |       |

| tCES                 | Clock Enable Set-up Time                        | 1.5  | —    | 1.5  | —    | 2    | —    | ns    |       |

| t <sub>CEH</sub>     | Clock Enable Hold Time                          | 0.8  | —    | 0.8  | —    | 1    | —    | ns    |       |

| t <sub>SB</sub>      | Power down mode Entry Time                      | 0    | 6    | 0    | 7    | 0    | 7.5  | ns    |       |

| t <sub>T</sub>       | Transition Time (Rise and Fall)                 | 0.5  | 10   | 0.5  | 10   | 0.5  | 10   | ns    |       |

1. Access time is measured at 1.4V. See AC Characteristics: notes 1, 2, 3, 4, 5 and load circuit A.

2. Access time is measured at 1.4V. See AC Characteristics: notes 1, 2, 3, 6, 7 and load circuit B.

## **Common Parameters**

| Symbol           | Parameter                           | -1  | -6K  |      | -7K  |      | -7   |       | Notes |

|------------------|-------------------------------------|-----|------|------|------|------|------|-------|-------|

| Symbol           |                                     |     | Max. | Min. | Max. | Min. | Max. | Units | NOLES |

| t <sub>CS</sub>  | Command Setup Time                  | 1.5 | -    | 1.5  | —    | 1.5  | —    | ns    |       |

| t <sub>CH</sub>  | Command Hold Time                   | 0.8 | —    | 0.8  | —    | 0.8  | —    | ns    |       |

| t <sub>AS</sub>  | Address and Bank Select Set-up Time | 1.5 | —    | 1.5  | —    | 1.5  | —    | ns    |       |

| t <sub>AH</sub>  | Address and Bank Select Hold Time   | 0.8 | —    | 0.8  | —    | 0.8  | —    | ns    |       |

| t <sub>RCD</sub> | RAS to CAS Delay                    | 15  | —    | 15   | —    | 20   | —    | ns    | 1     |

| t <sub>RC</sub>  | Bank Cycle Time                     | 48  | —    | 52   | —    | 63   | —    | ns    | 1     |

| t <sub>RAS</sub> | Active Command Period               | 36  | 100K | 37   | 100K | 42   | 100K | ns    | 1     |

| t <sub>RP</sub>  | Precharge Time                      | 15  | —    | 15   | —    | 20   | —    | ns    | 1     |

| t <sub>RRD</sub> | Bank to Bank Delay Time             | 12  | -    | 14   | —    | 14   | —    | ns    | 1     |

1. These parameters account for the number of clock cycle and depend on the operating frequency of the clock, as follows: the number of clock cycles = specified value of timing / clock period (count fractions as a whole number).

## Mode Register Set Cycle

| Symbol           | ol Parameter                 |      | -6K  |      | -7K  |      | 7    | Units |  |

|------------------|------------------------------|------|------|------|------|------|------|-------|--|

| Cymbol           |                              | Min. | Max. | Min. | Max. | Min. | Max. | onits |  |

| t <sub>RSC</sub> | Mode Register Set Cycle Time | 12   | —    | 14   | —    | 14   | —    | ns    |  |

## NT5SV16M4DT NT5SV8M8DT NT5SV4M16DT

## 64Mb Synchronous DRAM

## **Read Cycle**

| Symbol           | /mbol Parameter                 |      | -6K  |      | -7K  |      | -7   |       | Notes |

|------------------|---------------------------------|------|------|------|------|------|------|-------|-------|

| Symbol           | Symbol Parameter                | Min. | Max. | Min. | Max. | Min. | Max. | Units | NOLES |

| +                | Data Out Hold Time              |      | —    | —    | —    | —    | —    | ns    | 1     |

| t <sub>он</sub>  |                                 | 3    | —    | 3    | —    | 3    | —    | ns    | 2, 4  |

| t <sub>LZ</sub>  | Data Out to Low Impedance Time  |      | —    | 0    | —    | 0    | —    | ns    |       |

| t <sub>HZ3</sub> | Data Out to High Impedance Time | 2.7  | 5.4  | 2.7  | 5.4  | 2.7  | 5.4  | ns    | 3     |

| t <sub>HZ2</sub> | Data Out to High Impedance Time | 2.7  | 5.4  | 2.7  | 5.4  | 3    | 6    | ns    | 3     |

| t <sub>DQZ</sub> | DQM Data Out Disable Latency    | 2    | _    | 2    | _    | 2    | _    | СК    |       |

1. AC Output Load Circuit A.

2. AC Output Load Circuit B.

3. Referenced to the time at which the output achieves the open circuit condition, not to output voltage levels.

4. Data Out Hold Time with no load must meet 1.8ns (-5K, -7K, -75B).

# **Refresh Cycle**

| Symbol            | Parameter              | -6   | -6K  |      | -7K  |      | 7    | Units | Notes |

|-------------------|------------------------|------|------|------|------|------|------|-------|-------|

| Symbol            | Falameter              | Min. | Max. | Min. | Max. | Min. | Max. | Units | Notes |

| t <sub>REF</sub>  | Refresh Period         | —    | 64   | —    | 64   | —    | 64   | ms    | 1     |

| t <sub>SREX</sub> | Self Refresh Exit Time | 10   | —    | 10   | —    | 10   | —    | ns    |       |

|                   |                        |      |      |      |      |      |      |       |       |

1. 4096 auto refresh cycles.

# Write Cycle

| Symbol            | Parameter                                  | -6  | iκ   | -7   | ΥK   | -    | 7    | Units |

|-------------------|--------------------------------------------|-----|------|------|------|------|------|-------|

| Symbol            |                                            |     | Max. | Min. | Max. | Min. | Max. | Units |

| t <sub>DS</sub>   | Data In Set-up Time                        | 1.5 | —    | 1.5  | —    | 1.5  | —    | ns    |

| t <sub>DH</sub>   | Data In Hold Time                          | 0.8 | —    | 0.8  | —    | 0.8  | —    | ns    |

| t <sub>DPL</sub>  | Data input to Precharge                    | 12  | —    | 14   | —    | 14   | —    | ns    |

| t <sub>WR</sub>   | Write Recovery Time                        | 12  | —    | 14   | —    | 14   | —    | ns    |

| t <sub>DAL3</sub> | Data In to Active Delay<br>CAS Latency = 3 | 5   | —    | 5    | —    | 5    | —    | СК    |

| t <sub>DAL2</sub> | Data In to Active Delay<br>CAS Latency = 2 | 4   | —    | 4    | —    | 4    | —    | СК    |

| t <sub>DQW</sub>  | DQM Write Mask Latency                     | 0   | —    | 0    | —    |      | —    | СК    |

# **Clock Frequency and Latency**

| Symbol           | Parameter                 | -6  | бК  | -7  | 'K  | -   | 7   | Units |

|------------------|---------------------------|-----|-----|-----|-----|-----|-----|-------|

| f <sub>ск</sub>  | Clock Frequency           | 166 | 133 | 143 | 133 | 143 | 100 | MHz   |

| t <sub>CK</sub>  | Clock Cycle Time          | 6   | 7.5 | 7   | 7.5 | 7   | 10  | ns    |

| t <sub>AA</sub>  | CAS Latency               | 3   | 2   | 3   | 2   | 3   | 2   | СК    |

| t <sub>RP</sub>  | Precharge Time            | 3   | 2   | 3   | 2   | 3   | 2   | СК    |

| t <sub>RCD</sub> | RAS to CAS Delay          | 3   | 2   | 3   | 2   | 3   | 2   | СК    |

| t <sub>RC</sub>  | Bank Cycle Time           | 9   | 7   | 9   | 7   | 9   | 7   | СК    |

| t <sub>RAS</sub> | Minimum Bank Active Time  | 6   | 5   | 6   | 5   | 6   | 5   | СК    |

| t <sub>DPL</sub> | Data In to Precharge      | 2   | 2   | 2   | 2   | 2   | 2   | СК    |

| t <sub>DAL</sub> | Data In to Active/Refresh | 5   | 4   | 5   | 4   | 5   | 4   | СК    |

| t <sub>RRD</sub> | Bank to Bank Delay Time   | 2   | 2   | 2   | 2   | 2   | 2   | СК    |

| t <sub>WL</sub>  | Write Latency             | 0   | 0   | 0   | 0   | 0   | 0   | СК    |

| t <sub>DQW</sub> | DQM Write Mask Latency    | 0   | 0   | 0   | 0   | 0   | 0   | СК    |

| t <sub>DQZ</sub> | DQM Data Disable Latency  | 2   | 2   | 2   | 2   | 2   | 2   | СК    |

| t <sub>CSL</sub> | Clock Suspend Latency     | 1   | 1   | 1   | 1   | 1   | 1   | СК    |

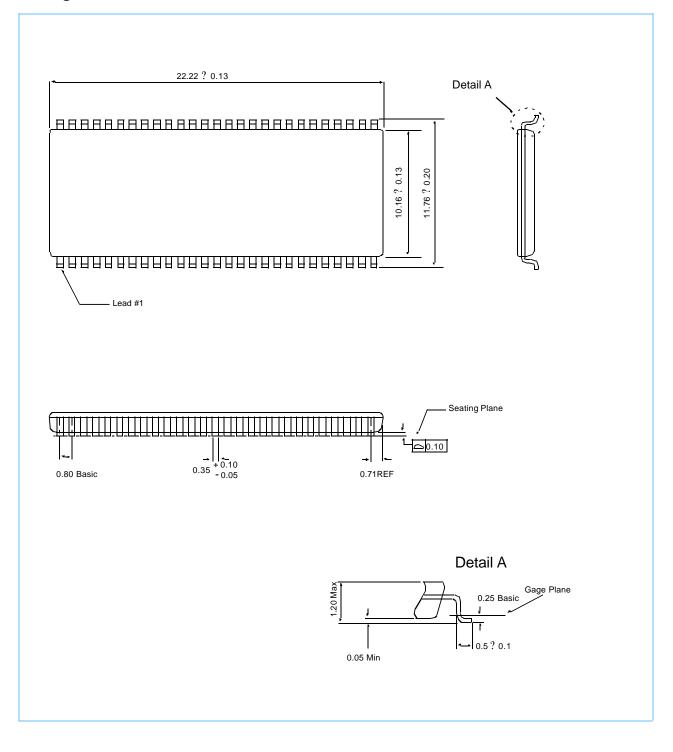

## Package Dimensions (400mil; 54 lead; Thin Small Outline Package)

| REV   | 1.1 |

|-------|-----|