# ACT<sup>™</sup> 2 Family FPGAs

#### **Features**

- Up to 8000 Gate Array Gates (20,000 PLD equivalent gates)

- Replaces up to 200 TTL Packages

- Replaces up to eighty 20-Pin PAL® Packages

- Design Library with over 500 Macro Functions

- Single-Module Sequential Functions

- Wide-Input Combinatorial Functions

- Up to 1232 Programmable Logic Modules

- Up to 998 Flip-Flops

- Datapath Performance at 105 MHz

- 16-Bit Accumulator Performance to 39 MHz

- Two In-Circuit Diagnostic Probe Pins Support Speed Analysis to 50 MHz

- Two High-Speed, Low-Skew Clock Networks

- I/O Drive to 10 mA

- Nonvolatile, User Programmable

- Logic Fully Tested Prior to Shipment

- 1.0-micron CMOS Technology

# **Product Family Profile**

| Device                                                                                                           | A1225A                                      | A1240A                                      | A1280A                                                  |

|------------------------------------------------------------------------------------------------------------------|---------------------------------------------|---------------------------------------------|---------------------------------------------------------|

| Capacity Gate Array Equivalent Gates PLD Equivalent Gates TTL Equivalent Packages 20-Pin PAL Equivalent Packages | 2,500                                       | 4,000                                       | 8,000                                                   |

|                                                                                                                  | 6,250                                       | 10,000                                      | 20,000                                                  |

|                                                                                                                  | 63                                          | 100                                         | 200                                                     |

|                                                                                                                  | 25                                          | 40                                          | 80                                                      |

| Logic Modules                                                                                                    | 451                                         | 684                                         | 1,232                                                   |

| S-Modules                                                                                                        | 231                                         | 348                                         | 624                                                     |

| C-Modules                                                                                                        | 220                                         | 336                                         | 608                                                     |

| Flip-Flops (maximum)                                                                                             | 382                                         | 568                                         | 998                                                     |

| Routing Resources Horizontal Tracks/Channel Vertical Tracks/Channel PLICE Antifuse Elements                      | 36                                          | 36                                          | 36                                                      |

|                                                                                                                  | 15                                          | 15                                          | 15                                                      |

|                                                                                                                  | 250,000                                     | 400,000                                     | 750,000                                                 |

| User I/Os (maximum)                                                                                              | 83                                          | 104                                         | 140                                                     |

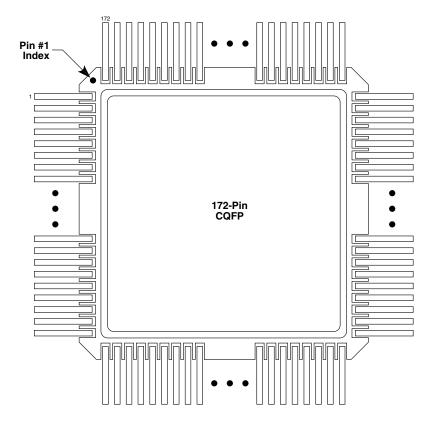

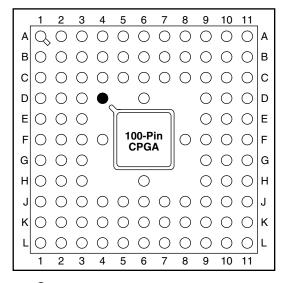

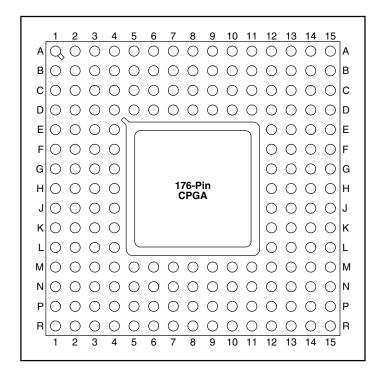

| Packages <sup>1</sup>                                                                                            | 100 CPGA<br>100 PQFP<br>100 VQFP<br>84 PLCC | 132 CPGA<br>144 PQFP<br>176 TQFP<br>84 PLCC | 176 CPGA<br>160 PQFP<br>176 TQFP<br>84 PLCC<br>172 CQFP |

| Performance <sup>2</sup> 16-Bit Prescaled Counters 16-Bit Loadable Counters 16-Bit Accumulators                  | 105 MHz                                     | 100 MHz                                     | 85 MHz                                                  |

|                                                                                                                  | 70 MHz                                      | 69 MHz                                      | 67 MHz                                                  |

|                                                                                                                  | 39 MHz                                      | 38 MHz                                      | 36 MHz                                                  |

#### Notes:

- 1. See the "Product Plan" on page 3 for package availability.

- 2. Performance is based on '-2' speed devices at commercial worst-case operating conditions using PREP Benchmarks, Suite #1, Version 1.2, dated 3-28-93, any analysis is not endorsed by PREP.

## **Description**

The ACT<sup>TM</sup> 2 family represents Actel's second generation of field programmable gate arrays (FPGAs). The ACT 2 family presents a two-module architecture, consisting of C-modules and S-modules. These modules are optimized for both combinatorial and sequential designs. Based on Actel's patented channeled array architecture, the ACT 2 family provides significant enhancements to gate density and performance while maintaining downward compatibility with the ACT 1 design environment and upward compatibility with the ACT 3 design environment. The devices are implemented in silicon gate, 1.0-µm, two-level metal CMOS, and employ Actel's PLICE<sup>®</sup> antifuse

technology. This revolutionary architecture offers gate array design flexibility, high performance, and fast

time-to-production with user programming. The ACT 2 family is supported by the Designer and Designer Advantage Systems, which offers automatic pin assignment, validation of electrical and design rules, automatic placement and routing, timing analysis, user programming, and diagnostic probe capabilities. The systems are supported on the following platforms:  $386/486^{\rm TM}$  PC, Sun , and HP workstations. The systems provide CAE interfaces to the following design environments: Cadence, Viewlogic , Mentor Graphics , and OrCAD .

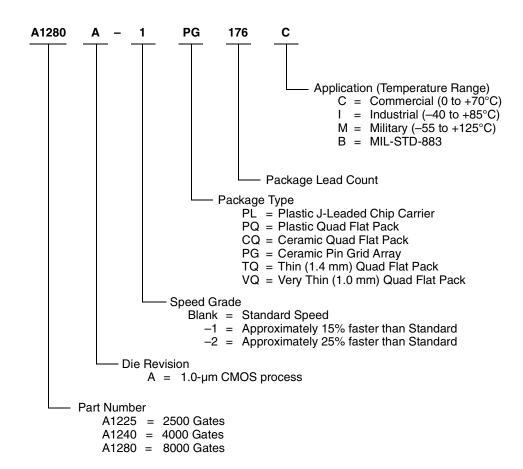

# **Ordering Information**

2 v4.0

Downloaded from Elcodis.com electronic components distributor

# **Product Plan**

|                                                                                       | Speed    | Grade*   |          | Application |          |          |          |

|---------------------------------------------------------------------------------------|----------|----------|----------|-------------|----------|----------|----------|

|                                                                                       | Std      | -1       | -2       | С           | I        | M        | В        |

| A1225A Device                                                                         |          |          |          |             |          |          |          |

| 100-pin Ceramic Pin Grid Array (PG)                                                   | <b>'</b> | ~        | <b>~</b> | <b>V</b>    | _        | _        | _        |

| 100-pin Plastic Quad Flat Pack (PQ)<br>100-pin Very Thin (1.0 mm) Quad Flat Pack (VQ) | <b>V</b> | ~        | <b>V</b> | V           | <b>~</b> | _        | _        |

| 84-pin Plastic Leaded Chip Carrier (PL)                                               | •        | ~        | •        | ~           | ~        | _        | _        |

| A1240A Device                                                                         |          |          |          |             |          |          |          |

| 132-pin Ceramic Pin Grid Array (PG)<br>176-pin Thin (1.4 mm) Quad Flat Pack (TQ)      | <b>V</b> | <b>V</b> | <b>V</b> | <i>V</i>    | _        | <i>'</i> | <i>'</i> |

| 144-pin Plastic Quad Flat Pack (PQ)                                                   | <b>/</b> | ~        | <b>✓</b> | ~           | •        | _        | _        |

| 84-pin Plastic Leaded Chip Carrier (PL)                                               | •        | ~        | •        | ~           | ~        | _        | _        |

| A1280A Device                                                                         |          |          |          |             |          |          |          |

| 176-pin Ceramic Pin Grid Array (PG) 176-pin Thin (1.4 mm) Quad Flat Pack (TQ)         | V<br>V   | V V      | <i>V</i> | V<br>V      |          | <b>/</b> | <b>~</b> |

| 160-pin Plastic Quad Flat Pack (PQ) 172-pin Ceramic Quad Flat Pack (CQ)               | <i>v</i> | ~        | <i>V</i> | <i>V</i>    | <i>-</i> | ~        | ~        |

$Contact\ your\ Actel\ sales\ representatives\ for\ product\ availability.$

Applications: C = CommercialAvailability:  $\checkmark$  = Available \*Speed Grade: -1 = Approx. 15% faster than Standard I = Industrial

M = Military

B = MIL-STD-883 -2 = Approx. 25% faster than Standard

P = Planned — = Not Planned

# **Device Resources**

|                  |                  |       |         | User I/Os |         |         |         |         |        |         |         |         |

|------------------|------------------|-------|---------|-----------|---------|---------|---------|---------|--------|---------|---------|---------|

| Davisa           | Lania            |       |         | CPGA      |         |         | PQFP    |         | PLCC   | CQFP    | TQFP    | VQFP    |

| Device<br>Series | Logic<br>Modules | Gates | 176-pin | 132-pin   | 100-pin | 160-pin | 144-pin | 100-pin | 84-pin | 172-pin | 176-pin | 100-pin |

| A1225A           | 451              | 2500  |         | _         | 83      |         | _       | 83      | 72     |         | _       | 83      |

| A1240A           | 684              | 4000  | _       | 104       | _       | _       | 104     | _       | 72     | _       | 104     | _       |

| A1280A           | 1232             | 8000  | 140     | _         | _       | 125     | _       | _       | 72     | 140     | 140     | _       |

# **Operating Conditions**

### Absolute Maximum Ratings<sup>1</sup>

Free air temperature range

| Symbol           | Parameter                               | Limits                       | Units |

|------------------|-----------------------------------------|------------------------------|-------|

| V <sub>CC</sub>  | DC Supply Voltage                       | -0.5 to +7.0                 | V     |

| VI               | Input Voltage                           | -0.5 to V <sub>CC</sub> +0.5 | V     |

| Vo               | Output Voltage                          | $-0.5$ to $V_{\rm CC}$ +0.5  | V     |

| I <sub>IO</sub>  | I/O Source/Sink<br>Current <sup>2</sup> | ±20                          | mA    |

| T <sub>STG</sub> | Storage Temperature                     | -65 to +150                  | °C    |

#### Notes:

- 1. Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. Exposure to absolute maximum rated conditions for extended periods may affect device reliability. Device should not be operated outside the Recommended Operating Conditions.

- 2. Device inputs are normally high impedance and draw extremely low current. However, when input voltage is greater than  $V_{\rm CC}$  + 0.5 V or less than GND 0.5 V, the internal protection diode will be forward biased and can draw excessive current.

### **Recommended Operating Conditions**

| Parameter                         | Commercia<br>I | Industria<br>I | Military       | Units            |

|-----------------------------------|----------------|----------------|----------------|------------------|

| Temperature<br>Range <sup>1</sup> | 0 to +70       | -40 to<br>+85  | -55 to<br>+125 | °C               |

| Power<br>Supply<br>Tolerance      | ±5             | ±10            | ±10            | %V <sub>CC</sub> |

#### Note:

1. Ambient temperature  $(T_A)$  is used for commercial and industrial; case temperature  $(T_C)$  is used for military.

## **Electrical Specifications**

|                                                  | Com                                                                                                                                                                                                                                               | mercial                                                                                                                                                                                                                                                                                                                                                                                                                                     | Ind  | ustrial                                               | Mi                                                    | litary                                                |                                                       |

|--------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|-------------------------------------------------------|-------------------------------------------------------|-------------------------------------------------------|-------------------------------------------------------|

| Parameter                                        | Min.                                                                                                                                                                                                                                              | Max.                                                                                                                                                                                                                                                                                                                                                                                                                                        | Min. | Max.                                                  | Min.                                                  | Max.                                                  | Units                                                 |

| $(I_{OH} = -10 \text{ mA})^2$                    | 2.4                                                                                                                                                                                                                                               |                                                                                                                                                                                                                                                                                                                                                                                                                                             |      |                                                       |                                                       |                                                       | V                                                     |

| $(I_{OH} = -6 \text{ mA})$                       | 3.84                                                                                                                                                                                                                                              |                                                                                                                                                                                                                                                                                                                                                                                                                                             |      |                                                       |                                                       |                                                       | V                                                     |

| $(I_{OH} = -4 \text{ mA})$                       |                                                                                                                                                                                                                                                   |                                                                                                                                                                                                                                                                                                                                                                                                                                             | 3.7  |                                                       | 3.7                                                   |                                                       | V                                                     |

| $(I_{OL} = 10 \text{ mA})^2$                     |                                                                                                                                                                                                                                                   | 0.5                                                                                                                                                                                                                                                                                                                                                                                                                                         |      |                                                       |                                                       |                                                       | V                                                     |

| (I <sub>OL</sub> = 6 mA)                         |                                                                                                                                                                                                                                                   | 0.33                                                                                                                                                                                                                                                                                                                                                                                                                                        |      | 0.40                                                  |                                                       | 0.40                                                  | ٧                                                     |

|                                                  | -0.3                                                                                                                                                                                                                                              | 0.8                                                                                                                                                                                                                                                                                                                                                                                                                                         | -0.3 | 0.8                                                   | -0.3                                                  | 0.8                                                   | V                                                     |

|                                                  | 2.0                                                                                                                                                                                                                                               | V <sub>CC</sub> + 0.3                                                                                                                                                                                                                                                                                                                                                                                                                       | 2.0  | V <sub>CC</sub> + 0.3                                 | 2.0                                                   | V <sub>CC</sub> + 0.3                                 | V                                                     |

| īme t <sub>R</sub> , t <sub>F</sub> <sup>2</sup> |                                                                                                                                                                                                                                                   | 500                                                                                                                                                                                                                                                                                                                                                                                                                                         |      | 500                                                   |                                                       | 500                                                   | ns                                                    |

| nce <sup>2, 3</sup>                              |                                                                                                                                                                                                                                                   | 10                                                                                                                                                                                                                                                                                                                                                                                                                                          |      | 10                                                    |                                                       | 10                                                    | pF                                                    |

| I <sub>CC</sub> <sup>4</sup> (typical = 1 mA)    |                                                                                                                                                                                                                                                   | 2                                                                                                                                                                                                                                                                                                                                                                                                                                           |      | 10                                                    |                                                       | 20                                                    | mA                                                    |

| 5                                                | -10                                                                                                                                                                                                                                               | 10                                                                                                                                                                                                                                                                                                                                                                                                                                          | -10  | 10                                                    | -10                                                   | 10                                                    | μΑ                                                    |

|                                                  | $\frac{(I_{OH} = -10 \text{ mA})^2}{(I_{OH} = -6 \text{ mA})}$ $\frac{(I_{OH} = -4 \text{ mA})}{(I_{OL} = 10 \text{ mA})^2}$ $\frac{(I_{OL} = 6 \text{ mA})}{(I_{OL} = 6 \text{ mA})}$ Time $t_R$ , $t_F^2$ $\frac{1}{I_{CC}^4}$ (typical = 1 mA) | $\begin{array}{c c} \textbf{Parameter} & \textbf{Min.} \\ \hline & (I_{OH} = -10 \text{ mA})^2 & 2.4 \\ \hline & (I_{OH} = -6 \text{ mA}) & 3.84 \\ \hline & (I_{OH} = -4 \text{ mA}) \\ \hline & (I_{OL} = 10 \text{ mA})^2 \\ \hline & (I_{OL} = 6 \text{ mA}) \\ \hline & & -0.3 \\ \hline & & 2.0 \\ \hline \\ \text{Time } t_{R}, t_{F}^2 \\ \\ \text{nce}^{2, 3} \\ \hline & I_{CC}^4 \text{ (typical = 1 mA)} \\ \hline \end{array}$ |      | $\begin{array}{c ccccccccccccccccccccccccccccccccccc$ | $\begin{array}{c ccccccccccccccccccccccccccccccccccc$ | $\begin{array}{c ccccccccccccccccccccccccccccccccccc$ | $\begin{array}{c ccccccccccccccccccccccccccccccccccc$ |

#### Notes:

- 1. Only one output tested at a time.  $V_{CC} = min$ .

- 2. Not tested, for information only.

- 3. Includes worst-case 176 CPGA package capacitance.  $V_{OUT} = 0 \text{ V}, f = 1 \text{ MHz}.$

- 4. All outputs unloaded. All inputs =  $V_{CC}$  or GND, typical  $I_{CC}$  = 1 mA.  $I_{CC}$  limit includes  $I_{PP}$  and  $I_{SV}$  during normal operation.

- 5.  $V_{OUT}$ ,  $V_{IN} = V_{CC}$  or GND.

# **Package Thermal Characteristics**

The device junction to case thermal characteristic is  $\theta$ jc, and the junction to ambient air characteristic is  $\theta$ ja. The thermal characteristics for  $\theta$ ja are shown with two different air flow rates.

Maximum junction temperature is 150°C.

A sample calculation of the absolute maximum power dissipation allowed for a PQFP 160-pin package at commercial temperature is as follows:

$$\frac{\text{Max. junction temp. (°C) - Max. commercial temp.}}{\theta ja \text{ (°C/W)}} = \frac{150^{\circ}\text{C} - 70^{\circ}\text{C}}{33^{\circ}\text{C/W}} = 2.4 \text{ W}$$

| Package Type                             | Pin Count | θјс | θja<br>Still Air | θja<br>300 ft/min | Units |

|------------------------------------------|-----------|-----|------------------|-------------------|-------|

| Ceramic Pin Grid Array                   | 100       | 5   | 35               | 17                | °C/W  |

|                                          | 132       | 5   | 30               | 15                | °C/W  |

|                                          | 176       | 8   | 23               | 12                | °C/W  |

| Ceramic Quad Flat Pack                   | 172       | 8   | 25               | 15                | °C/W  |

| Plastic Quad Flat Pack <sup>1</sup>      | 100       | 13  | 48               | 40                | °C/W  |

|                                          | 144       | 15  | 40               | 32                | °C/W  |

|                                          | 160       | 15  | 38               | 30                | °C/W  |

| Plastic Leaded Chip Carrier <sup>2</sup> | 84        | 12  | 37               | 28                | °C/W  |

| Very Thin Quad Flat Pack <sup>3</sup>    | 100       | 12  | 43               | 35                | °C/W  |

| Thin Quad Flat Pack <sup>4</sup>         | 176       | 15  | 32               | 25                | °C/W  |

#### Notes:(Maximum Power in Still Air)

- 1. Maximum Power Dissipation for PQFP packages are 1.9 Watts (100-pin), 2.3 Watts (144-pin), and 2.4 Watts (160-pin).

- 2. Maximum Power Dissipation for PLCC packages is 2.7 Watts.

- 3. Maximum Power Dissipation for VQFP packages is 2.3 Watts.

- 4. Maximum Power Dissipation for TQFP packages is 3.1 Watts.

#### **Power Dissipation**

$$P = [I_{CC} standby + I_{CC} active] * V_{CC} + I_{OL} * V_{OL} * N + I_{OH} * (V_{CC} - V_{OH}) * M$$

Where:

$I_{CC}$  standby is the current flowing when no inputs or outputs are changing.

I<sub>CC</sub> active is the current flowing due to CMOS switching.

I<sub>OL</sub>, I<sub>OH</sub> are TTL sink/source currents.

V<sub>OL</sub>, V<sub>OH</sub> are TTL level output voltages.

N equals the number of outputs driving TTL loads to  $V_{\rm OL}$ .

M equals the number of outputs driving TTL loads to V<sub>OH</sub>.

An accurate determination of N and M is problematical because their values depend on the family type, design details, and on the system I/O. The power can be divided into two components: static and active.

#### **Static Power Component**

Actel FPGAs have small static power components that result in lower power dissipation than PALs or PLDs. By integrating multiple PALs/PLDs into one FPGA, an even greater reduction in board-level power dissipation can be achieved.

The power due to standby current is typically a small component of the overall power. Standby power is calculated below for commercial, worst case conditions.

$$\begin{array}{lll} I_{CC} & V_{CC} & Power \\ 2 \text{ mA} & 5.25 V & 10.5 \text{ mW} \end{array}$$

The static power dissipated by TTL loads depends on the number of outputs driving high or low and the DC load current. Again, this value is typically small. For instance, a 32-bit bus sinking 4 mA at 0.33 V will generate 42 mW with all outputs driving low, and 140 mW with all outputs driving high. The actual dissipation will average somewhere between as I/Os switch states with time.

#### **Active Power Component**

Power dissipation in CMOS devices is usually dominated by the active (dynamic) power dissipation. This component is frequency dependent, a function of the logic and the external I/O. Active power dissipation results from charging internal chip capacitances of the interconnect, unprogrammed antifuses, module inputs, and module outputs, plus external capacitance due to PC board traces

v4.0 5

and load device inputs. An additional component of the active power dissipation is the totem-pole current in CMOS transistor pairs. The net effect can be associated with an equivalent capacitance that can be combined with frequency and voltage to represent active power dissipation.

#### **Equivalent Capacitance**

The power dissipated by a CMOS circuit can be expressed by the Equation 1.

Power (

$$\mu W$$

) =  $C_{EQ} * V_{CC}^2 * F$  (1)

Where:

$C_{\text{EQ}}$  is the equivalent capacitance expressed in pF.

V<sub>CC</sub> is the power supply in volts.

F is the switching frequency in MHz.

Equivalent capacitance is calculated by measuring ICC active at a specified frequency and voltage for each circuit component of interest. Measurements have been made over a range of frequencies at a fixed value of VCC. Equivalent capacitance is frequency independent so that the results may be used over a wide range of operating conditions. Equivalent capacitance values are shown below.

#### **CFO** Values for Actel FPGAs

| Modules ( $C_{EQM}$ )                   | 5.8  |

|-----------------------------------------|------|

| Input Buffers ( $C_{EQI}$ )             | 12.9 |

| Output Buffers ( $C_{EQO}$ )            | 23.8 |

| Routed Array Clock Buffer Loads (Croch) | 3.9  |

To calculate the active power dissipated from the complete design, the switching frequency of each part of the logic must be known. Equation 2 shows a piece-wise linear summation over all components.

$$\begin{aligned} & Power = V_{CC}^{2} * \left[ (m * C_{EQM} * f_{m})_{modules} + (n * C_{EQI} * f_{n})_{inputs} \right. \\ & + (p * (C_{EQO} + C_{L}) * f_{p})_{outputs} + 0.5 * (q_{1} * C_{EQCR} * f_{q1})_{routed\_Clk1} + (r_{1} * f_{q1})_{routed\_Clk1} + 0.5 * (q_{2} * C_{EQCR} * f_{q2})_{routed\_Clk2} \\ & + (r_{2} * f_{q2})_{routed\_Clk2} \right] \end{aligned} \tag{2}$$

Where:

m = Number of logic modules switching at fm

n = Number of input buffers switching at fn

p = Number of output buffers switching at fp

q1 = Number of clock loads on the first routed array clock

q2 = Number of clock loads on the second routed array clock

$r_1$  = Fixed capacitance due to first routed array clock

r<sub>2</sub> = Fixed capacitance due to second routed array clock

$C_{EQM} \ = \ Equivalent$  capacitance of logic modules in pF

$C_{EQI}$  = Equivalent capacitance of input buffers in pF

$C_{EQO}$  = Equivalent capacitance of output buffers in pF

$C_{EQCR}$  = Equivalent capacitance of routed array clock in

рF

$C_L$  = Output lead capacitance in pF

$f_m$  = Average logic module switching rate in MHz

$f_n$  = Average input buffer switching rate in MHz

$f_{\rm p}$  = Average output buffer switching rate in MHz

$f_{01}$  = Average first routed array clock rate in MHz

$f_{q2}$  = Average second routed array clock rate in MHz

# Fixed Capacitance Values for Actel FPGAs (pF)

|             | r1          | r2          |

|-------------|-------------|-------------|

| Device Type | routed_Clk1 | routed_Clk2 |

| A1225A      | 106         | 106.0       |

| A1240A      | 134         | 134.2       |

| A1280A      | 168         | 167.8       |

#### **Determining Average Switching Frequency**

To determine the switching frequency for a design, you must have a detailed understanding of the data input values to the circuit. The following guidelines are meant to represent worst-case scenarios so that they can be generally used to predict the upper limits of power dissipation. These guidelines are as follows:

| Logic Modules (m)                                 | 80% of modules                 |

|---------------------------------------------------|--------------------------------|

| Inputs switching (n)                              | # inputs/4                     |

| Outputs switching (p)                             | # outputs/4                    |

| First routed array clock loads $(q_1)$            | 40%of<br>sequential<br>modules |

| Second routed array clock loads $(q_2)$           | 40%of<br>sequential<br>modules |

| Load capacitance ( $\mathrm{C_L}$ )               | $35~\mathrm{pF}$               |

| Average logic module switching rate $(f_m)$       | F/10                           |

| Average input switching rate (f <sub>n</sub> )    | F/5                            |

| Average output switching rate $(f_p)$             | F/10                           |

| Average first routed array clock rate $(f_{q1})$  | F                              |

| Average second routed array clock rate $(f_{q2})$ | • F/2                          |

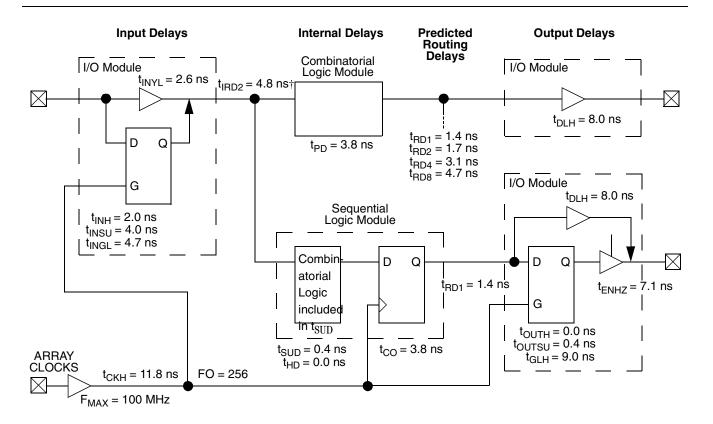

# **ACT 2 Timing Model\***

$*Values\ shown\ for\ A1240A-2\ at\ worst-case\ commercial\ conditions.$

† Input Module Predicted Routing Delay

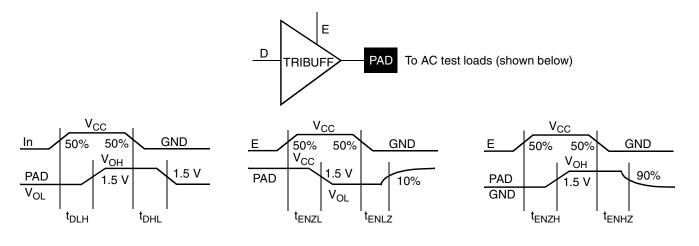

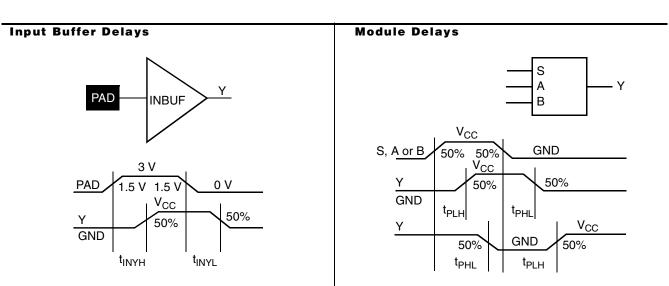

#### **Parameter Measurement**

#### **Output Buffer Delays**

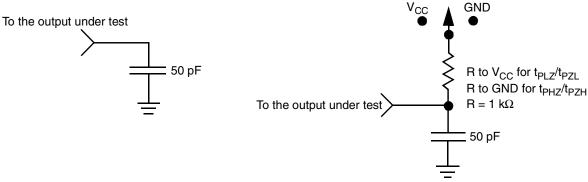

## **AC Test Loads**

Load 1 (Used to measure propagation delay)

Load 2 (Used to measure rising/falling edges)

# **Sequential Module Timing Characteristics**

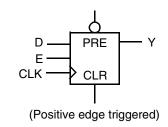

# Flip-Flops and Latches

**Note:** D represents all data functions involving A, B, and S for multiplexed flip-flops.

# **Sequential Timing Characteristics (continued)**

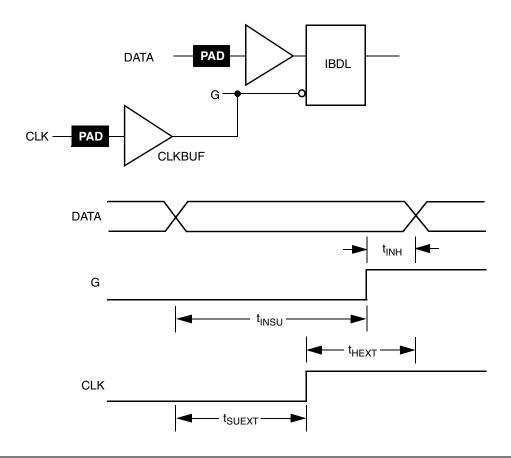

## **Input Buffer Latches**

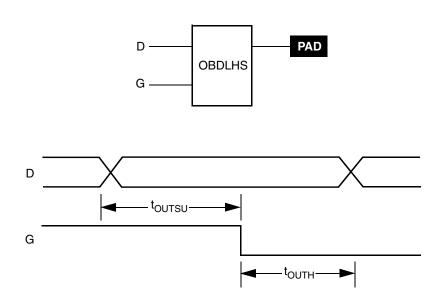

# **Output Buffer Latches**

# Timing Derating Factor (Temperature and Voltage)

|                                              | Indu | strial | М    | ilitary |

|----------------------------------------------|------|--------|------|---------|

|                                              | Min. | Max.   | Min. | Max.    |

| (Commercial Minimum/Maximum Specification) x | 0.69 | 1.11   | 0.67 | 1.23    |

# Timing Derating Factor for Designs at Typical Temperature ( $T_J$ = 25°C) and Voltage (5.0 V)

| (Commercial Maximum Specification) x | 0.85 |

|--------------------------------------|------|

|--------------------------------------|------|

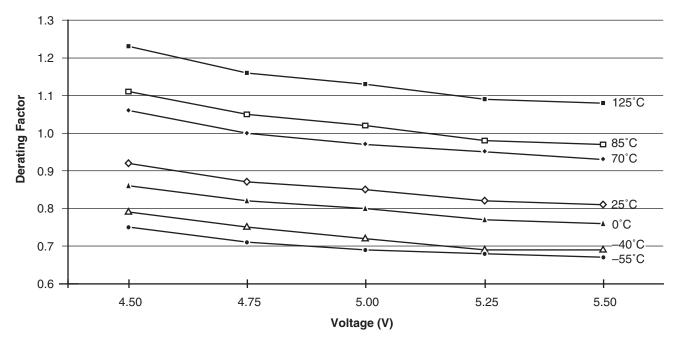

# Temperature and Voltage Derating Factors (normalized to Worst-Case Commercial, $T_J = 4.75 \text{ V}$ , $70^{\circ}\text{C}$ )

|      | -55  | -40  | 0    | 25   | 70   | 85   | 125  |

|------|------|------|------|------|------|------|------|

| 4.50 | 0.75 | 0.79 | 0.86 | 0.92 | 1.06 | 1.11 | 1.23 |

| 4.75 | 0.71 | 0.75 | 0.82 | 0.87 | 1.00 | 1.05 | 1.16 |

| 5.00 | 0.69 | 0.72 | 0.80 | 0.85 | 0.97 | 1.02 | 1.13 |

| 5.25 | 0.68 | 0.69 | 0.77 | 0.82 | 0.95 | 0.98 | 1.09 |

| 5.50 | 0.67 | 0.69 | 0.76 | 0.81 | 0.93 | 0.97 | 1.08 |

# Junction Temperature and Voltage Derating Curves (normalized to Worst-Case Commercial, $T_J = 4.75V$ , $70^{\circ}$ C)

Note: This derating factor applies to all routing and propagation delays.

# **A1225A Timing Characteristics**

# (Worst-Case Commercial Conditions, $V_{CC} = 4.75 \text{ V}$ , $T_J = 70^{\circ}\text{C}$ )

| Logic Module       | e Propagation Delays <sup>1</sup>          | '–2' \$ | Speed | '–1' S | Speed | 'Std' Speed |      |       |

|--------------------|--------------------------------------------|---------|-------|--------|-------|-------------|------|-------|

| Parameter          | Description                                | Min.    | Max.  | Min.   | Max.  | Min.        | Max. | Units |

| $t_{PD1}$          | Single Module                              |         | 3.8   |        | 4.3   |             | 5.0  | ns    |

| $t_{CO}$           | Sequential Clk to Q                        |         | 3.8   |        | 4.3   |             | 5.0  | ns    |

| $t_{GO}$           | Latch G to Q                               |         | 3.8   |        | 4.3   |             | 5.0  | ns    |

| $t_{RS}$           | Flip-Flop (Latch) Reset to Q               |         | 3.8   |        | 4.3   |             | 5.0  | ns    |

| Predicted Ro       | outing Delays <sup>2</sup>                 |         |       |        |       |             |      |       |

| t <sub>RD1</sub>   | FO=1 Routing Delay                         |         | 1.1   |        | 1.2   |             | 1.4  | ns    |

| t <sub>RD2</sub>   | FO=2 Routing Delay                         |         | 1.7   |        | 1.9   |             | 2.2  | ns    |

| t <sub>RD3</sub>   | FO=3 Routing Delay                         |         | 2.3   |        | 2.6   |             | 3.0  | ns    |

| t <sub>RD4</sub>   | FO=4 Routing Delay                         |         | 2.8   |        | 3.1   |             | 3.7  | ns    |

| t <sub>RD8</sub>   | FO=8 Routing Delay                         |         | 4.4   |        | 4.9   |             | 5.8  | ns    |

| Sequential T       | iming Characteristics <sup>3,4</sup>       |         |       |        |       |             |      |       |

| t <sub>SUD</sub>   | Flip-Flop (Latch) Data Input<br>Setup      | 0.4     |       | 0.4    |       | 0.5         |      | ns    |

| $t_{HD}$           | Flip-Flop (Latch) Data Input Hold          | 0.0     |       | 0.0    |       | 0.0         |      | ns    |

| t <sub>SUENA</sub> | Flip-Flop (Latch) Enable Setup             | 8.0     |       | 0.9    |       | 1.0         |      | ns    |

| t <sub>HENA</sub>  | Flip-Flop (Latch) Enable Hold              | 0.0     |       | 0.0    |       | 0.0         |      | ns    |

| t <sub>WCLKA</sub> | Flip-Flop (Latch) Clock Active Pulse Width | 4.5     |       | 5.0    |       | 6.0         |      | ns    |

| t <sub>WASYN</sub> | Flip-Flop (Latch) Asynchronous Pulse Width | 4.5     |       | 5.0    |       | 6.0         |      | ns    |

| $t_A$              | Flip-Flop Clock Input Period               | 9.4     |       | 11.0   |       | 13.0        |      | ns    |

| t <sub>INH</sub>   | Input Buffer Latch Hold                    | 0.0     |       | 0.0    |       | 0.0         |      | ns    |

| t <sub>INSU</sub>  | Input Buffer Latch Setup                   | 0.4     |       | 0.4    |       | 0.5         |      | ns    |

| t <sub>OUTH</sub>  | Output Buffer Latch Hold                   | 0.0     |       | 0.0    |       | 0.0         |      | ns    |

| t <sub>OUTSU</sub> | Output Buffer Latch Setup                  | 0.4     |       | 0.4    |       | 0.5         |      | ns    |

| $f_{MAX}$          | Flip-Flop (Latch) Clock<br>Frequency       |         | 105.0 |        | 90.0  |             | 75.0 | MHz   |

#### Notes:

- 1. For dual-module macros, use  $t_{PDI} + t_{RDI} + t_{PDn}$ ,  $t_{CO} + t_{RDI} + t_{PDn}$  or  $t_{PDI} + t_{RDI} + t_{SUD}$ , whichever is appropriate.

- 2. Routing delays are for typical designs across worst-case operating conditions. These parameters should be used for estimating device performance. Post-route timing analysis or simulation is required to determine actual worst-case performance. Post-route timing is based on actual routing delay measurements performed on the device prior to shipment.

- 3. Data applies to macros based on the S-module. Timing parameters for sequential macros constructed from C-modules can be obtained from the DirectTime Analyzer utility.

- 4. Setup and hold timing parameters for the Input Buffer Latch are defined with respect to the PAD and the D input. External setup/hold timing parameters must account for delay from an external PAD signal to the G inputs. Delay from an external PAD signal to the G input subtracts (adds) to the internal setup (hold) time.

# **A1225A Timing Characteristics (continued)**

# (Worst-Case Commercial Conditions)

| Input Module       | e Propagation Delays          |                     | '–2' \$     | Speed          | '–1' \$     | Speed          | 'Std'       | Speed          |           |

|--------------------|-------------------------------|---------------------|-------------|----------------|-------------|----------------|-------------|----------------|-----------|

| Parameter          | Description                   |                     | Min.        | Max.           | Min.        | Max.           | Min.        | Max.           | Unit<br>s |

| t <sub>INYH</sub>  | Pad to Y High                 |                     |             | 2.9            |             | 3.3            |             | 3.8            | ns        |

| $t_{INYL}$         | Pad to Y Low                  |                     |             | 2.6            |             | 3.0            |             | 3.5            | ns        |

| t <sub>INGH</sub>  | G to Y High                   |                     |             | 5.0            |             | 5.7            |             | 6.6            | ns        |

| t <sub>INGL</sub>  | G to Y Low                    |                     |             | 4.7            |             | 5.4            |             | 6.3            | ns        |

| Input Module       | e Predicted Routing Delay     | ′s <sup>1</sup>     |             |                |             |                |             |                |           |

| t <sub>IRD1</sub>  | FO=1 Routing Delay            |                     |             | 4.1            |             | 4.6            |             | 5.4            | ns        |

| t <sub>IRD2</sub>  | FO=2 Routing Delay            |                     |             | 4.6            |             | 5.2            |             | 6.1            | ns        |

| t <sub>IRD3</sub>  | FO=3 Routing Delay            |                     |             | 5.3            |             | 6.0            |             | 7.1            | ns        |

| t <sub>IRD4</sub>  | FO=4 Routing Delay            |                     |             | 5.7            |             | 6.4            |             | 7.6            | ns        |

| t <sub>IRD8</sub>  | FO=8 Routing Delay            |                     |             | 7.4            |             | 8.3            |             | 9.8            | ns        |

| Global Clock       | k Network                     |                     |             |                |             |                |             |                |           |

| t <sub>CKH</sub>   | Input Low to High             | FO = 32<br>FO = 256 |             | 10.2<br>11.8   |             | 11.0<br>13.0   |             | 12.8<br>15.7   | ns        |

| t <sub>CKL</sub>   | Input High to Low             | FO = 32<br>FO = 256 |             | 10.2<br>12.0   |             | 11.0<br>13.2   |             | 12.8<br>15.9   | ns        |

| t <sub>PWH</sub>   | Minimum Pulse Width<br>High   | FO = 32<br>FO = 256 | 3.4<br>3.8  |                | 4.1<br>4.5  |                | 4.5<br>5.0  |                | ns        |

| $t_{PWL}$          | Minimum Pulse Width Low       | FO = 32<br>FO = 256 | 3.4<br>3.8  |                | 4.1<br>4.5  |                | 4.5<br>5.0  |                | ns        |

| t <sub>CKSW</sub>  | Maximum Skew                  | FO = 32<br>FO = 256 |             | 0.7<br>3.5     |             | 0.7<br>3.5     |             | 0.7<br>3.5     | ns        |

| t <sub>SUEXT</sub> | Input Latch External<br>Setup | FO = 32<br>FO = 256 | 0.0<br>0.0  |                | 0.0<br>0.0  |                | 0.0<br>0.0  |                | ns        |

| t <sub>HEXT</sub>  | Input Latch External<br>Hold  | FO = 32<br>FO = 256 | 7.0<br>11.2 |                | 7.0<br>11.2 |                | 7.0<br>11.2 |                | ns        |

| t <sub>P</sub>     | Minimum Period                | FO = 32<br>FO = 256 | 7.7<br>8.1  |                | 8.3<br>8.8  |                | 9.1<br>10.0 |                | ns        |

| $f_{MAX}$          | Maximum Frequency             | FO = 32<br>FO = 256 |             | 130.0<br>125.0 |             | 120.0<br>115.0 |             | 110.0<br>100.0 | MHz       |

Note:

<sup>1.</sup> These parameters should be used for estimating device performance. Optimization techniques may further reduce delays by 0 to 4 ns. Routing delays are for typical designs across worst-case operating conditions. Post-route timing analysis or simulation is required to determine actual worst-case performance. Post-route timing is based on actual routing delay measurements performed on the device prior to shipment.

# **A1225A Timing Characteristics (continued)**

# (Worst-Case Commercial Conditions)

| Output Modu       | ıle Timing                            | '–2' S | Speed | '–1' § | Speed | 'Std' | Speed |       |

|-------------------|---------------------------------------|--------|-------|--------|-------|-------|-------|-------|

| Parameter         | Description                           | Min.   | Max.  | Min.   | Max.  | Min.  | Max.  | Units |

| TTL Output N      | TTL Output Module Timing <sup>1</sup> |        |       |        |       |       |       |       |

| t <sub>DLH</sub>  | Data to Pad High                      |        | 8.0   |        | 9.0   |       | 10.6  | ns    |

| $t_{DHL}$         | Data to Pad Low                       |        | 10.1  |        | 11.4  |       | 13.4  | ns    |

| $t_{\text{ENZH}}$ | Enable Pad Z to High                  |        | 8.9   |        | 10.0  |       | 11.8  | ns    |

| $t_{ENZL}$        | Enable Pad Z to Low                   |        | 11.6  |        | 13.2  |       | 15.5  | ns    |

| t <sub>ENHZ</sub> | Enable Pad High to Z                  |        | 7.1   |        | 8.0   |       | 9.4   | ns    |

| $t_{ENLZ}$        | Enable Pad Low to Z                   |        | 8.3   |        | 9.5   |       | 11.1  | ns    |

| t <sub>GLH</sub>  | G to Pad High                         |        | 8.9   |        | 10.2  |       | 11.9  | ns    |

| t <sub>GHL</sub>  | G to Pad Low                          |        | 11.2  |        | 12.7  |       | 14.9  | ns    |

| $d_{TLH}$         | Delta Low to High                     |        | 0.07  |        | 0.08  |       | 0.09  | ns/pF |

| $d_THL$           | Delta High to Low                     |        | 0.12  |        | 0.13  |       | 0.16  | ns/pF |

| CMOS Outpu        | ıt Module Timing <sup>1</sup>         |        |       |        |       |       |       |       |

| t <sub>DLH</sub>  | Data to Pad High                      |        | 10.1  |        | 11.5  |       | 13.5  | ns    |

| $t_{DHL}$         | Data to Pad Low                       |        | 8.4   |        | 9.6   |       | 11.2  | ns    |

| $t_{\text{ENZH}}$ | Enable Pad Z to High                  |        | 8.9   |        | 10.0  |       | 11.8  | ns    |

| $t_{ENZL}$        | Enable Pad Z to Low                   |        | 11.6  |        | 13.2  |       | 15.5  | ns    |

| $t_{ENHZ}$        | Enable Pad High to Z                  |        | 7.1   |        | 8.0   |       | 9.4   | ns    |

| $t_{ENLZ}$        | Enable Pad Low to Z                   |        | 8.3   |        | 9.5   |       | 11.1  | ns    |

| $t_{GLH}$         | G to Pad High                         |        | 8.9   |        | 10.2  |       | 11.9  | ns    |

| $t_{GHL}$         | G to Pad Low                          |        | 11.2  |        | 12.7  |       | 14.9  | ns    |

| $d_TLH$           | Delta Low to High                     |        | 0.12  |        | 0.13  |       | 0.16  | ns/pF |

| $d_THL$           | Delta High to Low                     |        | 0.09  |        | 0.10  |       | 0.12  | ns/pF |

Note:

<sup>1.</sup> Delays based on 50 pF loading.

$<sup>2. \</sup>quad SSO\ information\ can\ be\ found\ at\ http://www.actel.com/support/appnotes/appnotes\_design.html \#board.$

# **A1240A Timing Characteristics**

(Worst-Case Commercial Conditions,  $V_{CC} = 4.75 \text{ V}$ ,  $T_J = 70^{\circ}\text{C}$ )

| Logic Modu         | le Propagation Delays <sup>1</sup>            | ' <b>–2</b> ' \$ | Speed | '–1' S | peed | 'Std' | Speed |       |

|--------------------|-----------------------------------------------|------------------|-------|--------|------|-------|-------|-------|

| Parameter          | Description                                   | Min.             | Max.  | Min.   | Max. | Min.  | Max.  | Units |

| t <sub>PD1</sub>   | Single Module                                 |                  | 3.8   |        | 4.3  |       | 5.0   | ns    |

| $t_{CO}$           | Sequential Clk to Q                           |                  | 3.8   |        | 4.3  |       | 5.0   | ns    |

| $t_{GO}$           | Latch G to Q                                  |                  | 3.8   |        | 4.3  |       | 5.0   | ns    |

| t <sub>RS</sub>    | Flip-Flop (Latch) Reset to Q                  |                  | 3.8   |        | 4.3  |       | 5.0   | ns    |

| Predicted R        | outing Delays <sup>2</sup>                    |                  |       |        |      |       |       |       |

| t <sub>RD1</sub>   | FO=1 Routing Delay                            |                  | 1.4   |        | 1.5  |       | 1.8   | ns    |

| t <sub>RD2</sub>   | FO=2 Routing Delay                            |                  | 1.7   |        | 2.0  |       | 2.3   | ns    |

| t <sub>RD3</sub>   | FO=3 Routing Delay                            |                  | 2.3   |        | 2.6  |       | 3.0   | ns    |

| t <sub>RD4</sub>   | FO=4 Routing Delay                            |                  | 3.1   |        | 3.5  |       | 4.1   | ns    |

| t <sub>RD8</sub>   | FO=8 Routing Delay                            |                  | 4.7   |        | 5.4  |       | 6.3   | ns    |

| Sequential 7       | Fiming Characteristics <sup>3, 4</sup>        |                  |       |        |      |       |       |       |

| t <sub>SUD</sub>   | Flip-Flop (Latch) Data Input<br>Setup         | 0.4              |       | 0.4    |      | 0.5   |       | ns    |

| t <sub>HD</sub>    | Flip-Flop (Latch) Data Input<br>Hold          | 0.0              |       | 0.0    |      | 0.0   |       | ns    |

| t <sub>SUENA</sub> | Flip-Flop (Latch) Enable Setup                | 0.8              |       | 0.9    |      | 1.0   |       | ns    |

| t <sub>HENA</sub>  | Flip-Flop (Latch) Enable Hold                 | 0.0              |       | 0.0    |      | 0.0   |       | ns    |

| t <sub>WCLKA</sub> | Flip-Flop (Latch) Clock Active Pulse Width    | 4.5              |       | 6.0    |      | 6.5   |       | ns    |

| t <sub>WASYN</sub> | Flip-Flop (Latch)<br>Asynchronous Pulse Width | 4.5              |       | 6.0    |      | 6.5   |       | ns    |

| $t_A$              | Flip-Flop Clock Input Period                  | 9.8              |       | 12.0   |      | 15.0  |       | ns    |

| t <sub>INH</sub>   | Input Buffer Latch Hold                       | 0.0              |       | 0.0    |      | 0.0   |       | ns    |

| t <sub>INSU</sub>  | Input Buffer Latch Setup                      | 0.4              |       | 0.4    |      | 0.5   |       | ns    |

| t <sub>OUTH</sub>  | Output Buffer Latch Hold                      | 0.0              |       | 0.0    |      | 0.0   |       | ns    |

| toutsu             | Output Buffer Latch Setup                     | 0.4              |       | 0.4    |      | 0.5   |       | ns    |

| $f_{MAX}$          | Flip-Flop (Latch) Clock<br>Frequency          |                  | 100.0 |        | 80.0 |       | 66.0  | MHz   |

#### Notes:

- 1. For dual-module macros, use  $t_{PDI} + t_{RDI} + t_{PDn}$ ,  $t_{CO} + t_{RDI} + t_{PDn}$  or  $t_{PDI} + t_{RDI} + t_{SUD}$ , whichever is appropriate.

- 2. Routing delays are for typical designs across worst-case operating conditions. These parameters should be used for estimating device performance. Post-route timing analysis or simulation is required to determine actual worst-case performance. Post-route timing is based on actual routing delay measurements performed on the device prior to shipment.

- 3. Data applies to macros based on the S-module. Timing parameters for sequential macros constructed from C-modules can be obtained from the DirectTime Analyzer utility.

- 4. Setup and hold timing parameters for the Input Buffer Latch are defined with respect to the PAD and the D input. External setup/hold timing parameters must account for delay from an external PAD signal to the G inputs. Delay from an external PAD signal to the G input subtracts (adds) to the internal setup (hold) time.

v4.0 15

# **A1240A Timing Characteristics (continued)**

# (Worst-Case Commercial Conditions)

| Input Modul        | le Propagation Delays       |                     | '–2' \$     | Speed          | '–1' <b>'</b> | Speed          | 'Std'        | Speed        |       |

|--------------------|-----------------------------|---------------------|-------------|----------------|---------------|----------------|--------------|--------------|-------|

| Parameter          | Description                 |                     | Min.        | Max.           | Min.          | Max.           | Min.         | Max.         | Units |

| t <sub>INYH</sub>  | Pad to Y High               |                     |             | 2.9            |               | 3.3            |              | 3.8          | ns    |

| $t_{INYL}$         | Pad to Y Low                |                     |             | 2.6            |               | 3.0            |              | 3.5          | ns    |

| t <sub>INGH</sub>  | G to Y High                 |                     |             | 5.0            |               | 5.7            |              | 6.6          | ns    |

| t <sub>INGL</sub>  | G to Y Low                  |                     |             | 4.7            |               | 5.4            |              | 6.3          | ns    |

| Input Modul        | le Predicted Routing Delays |                     |             |                |               |                |              |              |       |

| t <sub>IRD1</sub>  | FO=1 Routing Delay          |                     |             | 4.2            |               | 4.8            |              | 5.6          | ns    |

| t <sub>IRD2</sub>  | FO=2 Routing Delay          |                     |             | 4.8            |               | 5.4            |              | 6.4          | ns    |

| t <sub>IRD3</sub>  | FO=3 Routing Delay          |                     |             | 5.4            |               | 6.1            |              | 7.2          | ns    |

| t <sub>IRD4</sub>  | FO=4 Routing Delay          |                     |             | 5.9            |               | 6.7            |              | 7.9          | ns    |

| t <sub>IRD8</sub>  | FO=8 Routing Delay          |                     |             | 7.9            |               | 8.9            |              | 10.5         | ns    |

| Global Cloc        | k Network                   |                     |             |                |               |                |              |              |       |

| t <sub>CKH</sub>   | Input Low to High           | FO = 32<br>FO = 256 |             | 10.2<br>11.8   |               | 11.0<br>13.0   |              | 12.8<br>15.7 | ns    |

| t <sub>CKL</sub>   | Input High to Low           | FO = 32<br>FO = 256 |             | 10.2<br>12.0   |               | 11.0<br>13.2   |              | 12.8<br>15.9 | ns    |

| t <sub>PWH</sub>   | Minimum Pulse Width<br>High | FO = 32<br>FO = 256 | 3.8<br>4.1  |                | 4.5<br>5.0    |                | 5.5<br>5.8   |              | ns    |

| t <sub>PWL</sub>   | Minimum Pulse Width Low     | FO = 32<br>FO = 256 | 3.8<br>4.1  |                | 4.5<br>5.0    |                | 5.5<br>5.8   |              | ns    |

| t <sub>CKSW</sub>  | Maximum Skew                | FO = 32<br>FO = 256 |             | 0.5<br>2.5     |               | 0.5<br>2.5     |              | 0.5<br>2.5   | ns    |

| t <sub>SUEXT</sub> | Input Latch External Setup  | FO = 32<br>FO = 256 | 0.0<br>0.0  |                | 0.0<br>0.0    |                | 0.0<br>0.0   |              | ns    |

| t <sub>HEXT</sub>  | Input Latch External Hold   | FO = 32<br>FO = 256 | 7.0<br>11.2 |                | 7.0<br>11.2   |                | 7.0<br>11.2  |              | ns    |

| t <sub>P</sub>     | Minimum Period              | FO = 32<br>FO = 256 | 8.1<br>8.8  |                | 9.1<br>10.0   |                | 11.1<br>11.7 |              | ns    |

| $f_{MAX}$          | Maximum Frequency           | FO = 32<br>FO = 256 |             | 125.0<br>115.0 |               | 110.0<br>100.0 |              | 90.0<br>85.0 | MHz   |

Note:

These parameters should be used for estimating device performance. Optimization techniques may further reduce delays by 0 to 4 ns. Routing delays are for typical designs across worst-case operating conditions. Post-route timing analysis or simulation is required to determine actual worst-case performance. Post-route timing is based on actual routing delay measurements performed on the device prior to shipment.

# **A1240A Timing Characteristics (continued)**

# (Worst-Case Commercial Conditions)

| Output Modu       | ile Timing                    | ' <b>–2</b> ' \$ | Speed | '–1' \$ | Speed | 'Std' | Speed |       |

|-------------------|-------------------------------|------------------|-------|---------|-------|-------|-------|-------|

| Parameter         | Description                   | Min.             | Max.  | Min.    | Max.  | Min.  | Max.  | Units |

| TTL Output N      | Module Timing <sup>1</sup>    |                  |       |         |       |       |       |       |

| t <sub>DLH</sub>  | Data to Pad High              |                  | 8.0   |         | 9.0   |       | 10.6  | ns    |

| $t_{DHL}$         | Data to Pad Low               |                  | 10.1  |         | 11.4  |       | 13.4  | ns    |

| $t_{\text{ENZH}}$ | Enable Pad Z to High          |                  | 8.9   |         | 10.0  |       | 11.8  | ns    |

| $t_{\text{ENZL}}$ | Enable Pad Z to Low           |                  | 11.7  |         | 13.2  |       | 15.5  | ns    |

| $t_{\text{ENHZ}}$ | Enable Pad High to Z          |                  | 7.1   |         | 8.0   |       | 9.4   | ns    |

| $t_{ENLZ}$        | Enable Pad Low to Z           |                  | 8.4   |         | 9.5   |       | 11.1  | ns    |

| t <sub>GLH</sub>  | G to Pad High                 |                  | 9.0   |         | 10.2  |       | 11.9  | ns    |

| $t_{GHL}$         | G to Pad Low                  |                  | 11.2  |         | 12.7  |       | 14.9  | ns    |

| $d_TLH$           | Delta Low to High             |                  | 0.07  |         | 0.08  |       | 0.09  | ns/pF |

| $d_THL$           | Delta High to Low             |                  | 0.12  |         | 0.13  |       | 0.16  | ns/pF |

| CMOS Outpu        | ıt Module Timing <sup>1</sup> |                  |       |         |       |       |       |       |

| t <sub>DLH</sub>  | Data to Pad High              |                  | 10.2  |         | 11.5  |       | 13.5  | ns    |

| $t_{DHL}$         | Data to Pad Low               |                  | 8.4   |         | 9.6   |       | 11.2  | ns    |

| t <sub>ENZH</sub> | Enable Pad Z to High          |                  | 8.9   |         | 10.0  |       | 11.8  | ns    |

| $t_{ENZL}$        | Enable Pad Z to Low           |                  | 11.7  |         | 13.2  |       | 15.5  | ns    |

| $t_{\text{ENHZ}}$ | Enable Pad High to Z          |                  | 7.1   |         | 8.0   |       | 9.4   | ns    |

| $t_{ENLZ}$        | Enable Pad Low to Z           |                  | 8.4   |         | 9.5   |       | 11.1  | ns    |

| t <sub>GLH</sub>  | G to Pad High                 |                  | 9.0   |         | 10.2  |       | 11.9  | ns    |

| $t_{GHL}$         | G to Pad Low                  |                  | 11.2  |         | 12.7  |       | 14.9  | ns    |

| $d_{TLH}$         | Delta Low to High             |                  | 0.12  |         | 0.13  |       | 0.16  | ns/pF |

| $d_THL$           | Delta High to Low             |                  | 0.09  |         | 0.10  |       | 0.12  | ns/pF |

Note:

<sup>1.</sup> Delays based on 50 pF loading.

$<sup>2. \</sup>quad SSO\ information\ can\ be\ found\ at\ http://www.actel.com/support/appnotes/appnotes\_design.html \#board.$

# **A1280A Timing Characteristics**

# (Worst-Case Commercial Conditions, $V_{CC} = 4.75 \text{ V}$ , $T_J = 70^{\circ}\text{C}$ )

| Logic Module Propagation Delays <sup>1</sup> |                                            | '–2' \$ | Speed | ' <b>–</b> 1' S | Speed | 'Std' S | Speed |       |

|----------------------------------------------|--------------------------------------------|---------|-------|-----------------|-------|---------|-------|-------|

| Parameter                                    | Description                                | Min.    | Max.  | Min.            | Max.  | Min.    | Max.  | Units |

| t <sub>PD1</sub>                             | Single Module                              |         | 3.8   |                 | 4.3   |         | 5.0   | ns    |

| t <sub>CO</sub>                              | Sequential Clk to Q                        |         | 3.8   |                 | 4.3   |         | 5.0   | ns    |

| t <sub>GO</sub>                              | Latch G to Q                               |         | 3.8   |                 | 4.3   |         | 5.0   | ns    |

| t <sub>RS</sub>                              | Flip-Flop (Latch) Reset to Q               |         | 3.8   |                 | 4.3   |         | 5.0   | ns    |

| Predicted Ro                                 | outing Delays <sup>2</sup>                 |         |       |                 |       |         |       |       |

| t <sub>RD1</sub>                             | FO=1 Routing Delay                         |         | 1.7   |                 | 2.0   |         | 2.3   | ns    |

| t <sub>RD2</sub>                             | FO=2 Routing Delay                         |         | 2.5   |                 | 2.8   |         | 3.3   | ns    |

| t <sub>RD3</sub>                             | FO=3 Routing Delay                         |         | 3.0   |                 | 3.4   |         | 4.0   | ns    |

| t <sub>RD4</sub>                             | FO=4 Routing Delay                         |         | 3.7   |                 | 4.2   |         | 4.9   | ns    |

| t <sub>RD8</sub>                             | FO=8 Routing Delay                         |         | 6.7   |                 | 7.5   |         | 8.8   | ns    |

| Sequential Ti                                | iming Characteristics <sup>3,4</sup>       |         |       |                 |       |         |       |       |

| t <sub>SUD</sub>                             | Flip-Flop (Latch) Data Input<br>Setup      | 0.4     |       | 0.4             |       | 0.5     |       | ns    |

| t <sub>HD</sub>                              | Flip-Flop (Latch) Data Input Hold          | 0.0     |       | 0.0             |       | 0.0     |       | ns    |

| t <sub>SUENA</sub>                           | Flip-Flop (Latch) Enable Setup             | 0.8     |       | 0.9             |       | 1.0     |       | ns    |

| t <sub>HENA</sub>                            | Flip-Flop (Latch) Enable Hold              | 0.0     |       | 0.0             |       | 0.0     |       | ns    |

| t <sub>WCLKA</sub>                           | Flip-Flop (Latch) Clock Active Pulse Width | 5.5     |       | 6.0             |       | 7.0     |       | ns    |

| t <sub>WASYN</sub>                           | Flip-Flop (Latch) Asynchronous Pulse Width | 5.5     |       | 6.0             |       | 7.0     |       | ns    |

| t <sub>A</sub>                               | Flip-Flop Clock Input Period               | 11.7    |       | 13.3            |       | 18.0    |       | ns    |

| t <sub>INH</sub>                             | Input Buffer Latch Hold                    | 0.0     |       | 0.0             |       | 0.0     |       | ns    |

| t <sub>INSU</sub>                            | Input Buffer Latch Setup                   | 0.4     |       | 0.4             |       | 0.5     |       | ns    |

| t <sub>OUTH</sub>                            | Output Buffer Latch Hold                   | 0.0     |       | 0.0             |       | 0.0     |       | ns    |

| t <sub>outsu</sub>                           | Output Buffer Latch Setup                  | 0.4     |       | 0.4             |       | 0.5     |       | ns    |

| f <sub>MAX</sub>                             | Flip-Flop (Latch) Clock<br>Frequency       |         | 85.0  |                 | 75.0  |         | 50.0  | MHz   |

#### Notes:

- 1. For dual-module macros, use  $t_{PDI} + t_{RDI} + t_{PDn}$ ,  $t_{CO} + t_{RDI} + t_{PDn}$ , or  $t_{PDI} + t_{RDI} + t_{SUD}$ , whichever is appropriate.

- 2. Routing delays are for typical designs across worst-case operating conditions. These parameters should be used for estimating device performance. Post-route timing analysis or simulation is required to determine actual worst-case performance. Post-route timing is based on actual routing delay measurements performed on the device prior to shipment.

- 3. Data applies to macros based on the S-module. Timing parameters for sequential macros constructed from C-modules can be obtained from the DirectTime Analyzer utility.

- 4. Setup and hold timing parameters for the Input Buffer Latch are defined with respect to the PAD and the D input. External setup/hold timing parameters must account for delay from an external PAD signal to the G inputs. Delay from an external PAD signal to the G input subtracts (adds) to the internal setup (hold) time.

# **A1280A Timing Characteristics (continued)**

# (Worst-Case Commercial Conditions)

| Input Modu         | le Propagation Delays       |                     | ' <b>–2</b> ' § | Speed         | '–1' \$      | Speed        | 'Std'        | Speed        |       |

|--------------------|-----------------------------|---------------------|-----------------|---------------|--------------|--------------|--------------|--------------|-------|

| Parameter          | Description                 |                     | Min.            | Max.          | Min.         | Max.         | Min.         | Max.         | Units |

| t <sub>INYH</sub>  | Pad to Y High               |                     |                 | 2.9           |              | 3.3          |              | 3.8          | ns    |

| $t_{INYL}$         | Pad to Y Low                |                     |                 | 2.7           |              | 3.0          |              | 3.5          | ns    |

| t <sub>INGH</sub>  | G to Y High                 |                     |                 | 5.0           |              | 5.7          |              | 6.6          | ns    |

| t <sub>INGL</sub>  | G to Y Low                  |                     |                 | 4.8           |              | 5.4          |              | 6.3          | ns    |

| Input Modu         | le Predicted Routing Delays | 1                   |                 |               |              |              |              |              |       |

| t <sub>IRD1</sub>  | FO=1 Routing Delay          |                     |                 | 4.6           |              | 5.1          |              | 6.0          | ns    |

| $t_{\text{IRD2}}$  | FO=2 Routing Delay          |                     |                 | 5.2           |              | 5.9          |              | 6.9          | ns    |

| $t_{\text{IRD3}}$  | FO=3 Routing Delay          |                     |                 | 5.6           |              | 6.3          |              | 7.4          | ns    |

| t <sub>IRD4</sub>  | FO=4 Routing Delay          |                     |                 | 6.5           |              | 7.3          |              | 8.6          | ns    |

| t <sub>IRD8</sub>  | FO=8 Routing Delay          |                     |                 | 9.4           |              | 10.5         |              | 12.4         | ns    |

| Global Cloc        | k Network                   |                     |                 |               |              |              |              |              |       |

| t <sub>CKH</sub>   | Input Low to High           | FO = 32<br>FO = 384 |                 | 10.2<br>13.1  |              | 11.0<br>14.6 |              | 12.8<br>17.2 | ns    |

| t <sub>CKL</sub>   | Input High to Low           | FO = 32<br>FO = 384 |                 | 10.2<br>13.3  |              | 11.0<br>14.9 |              | 12.8<br>17.5 | ns    |

| t <sub>PWH</sub>   | Minimum Pulse Width<br>High | FO = 32<br>FO = 384 | 5.0<br>5.8      |               | 5.5<br>6.4   |              | 6.6<br>7.6   |              | ns    |

| t <sub>PWL</sub>   | Minimum Pulse Width Low     | FO = 32<br>FO = 384 | 5.0<br>5.8      |               | 5.5<br>6.4   |              | 6.6<br>7.6   |              | ns    |

| t <sub>CKSW</sub>  | Maximum Skew                | FO = 32<br>FO = 384 |                 | 0.5<br>2.5    |              | 0.5<br>2.5   |              | 0.5<br>2.5   | ns    |

| t <sub>SUEXT</sub> | Input Latch External Setup  | FO = 32<br>FO = 384 | 0.0<br>0.0      |               | 0.0<br>0.0   |              | 0.0<br>0.0   |              | ns    |

| t <sub>HEXT</sub>  | Input Latch External Hold   | FO = 32<br>FO = 384 | 7.0<br>11.2     |               | 7.0<br>11.2  |              | 7.0<br>11.2  |              | ns    |

| t <sub>P</sub>     | Minimum Period              | FO = 32<br>FO = 384 | 9.6<br>10.6     |               | 11.2<br>12.6 |              | 13.3<br>15.3 |              | ns    |

| $f_{MAX}$          | Maximum Frequency           | FO = 32<br>FO = 384 |                 | 105.0<br>95.0 |              | 90.0<br>80.0 |              | 75.0<br>65.0 | MHz   |

Note:

These parameters should be used for estimating device performance. Optimization techniques may further reduce delays by 0 to 4 ns. Routing delays are for typical designs across worst-case operating conditions. Post-route timing analysis or simulation is required to determine actual worst-case performance. Post-route timing is based on actual routing delay measurements performed on the device prior to shipment.

# **A1280A Timing Characteristics (continued)**

# (Worst-Case Commercial Conditions)

| Output Modu       | ıle Timing                            | '–2' Sp | eed  | '–1' Sp | eed  | 'Std' S | peed |       |

|-------------------|---------------------------------------|---------|------|---------|------|---------|------|-------|

| Parameter         | Description                           | Min.    | Max. | Min.    | Max. | Min.    | Max. | Units |

| TTL Output I      | TTL Output Module Timing <sup>1</sup> |         |      |         |      |         |      |       |

| t <sub>DLH</sub>  | Data to Pad High                      |         | 8.1  |         | 9.0  |         | 10.6 | ns    |

| $t_{DHL}$         | Data to Pad Low                       |         | 10.2 |         | 11.4 |         | 13.4 | ns    |

| $t_{\text{ENZH}}$ | Enable Pad Z to High                  |         | 9.0  |         | 10.0 |         | 11.8 | ns    |

| t <sub>ENZL</sub> | Enable Pad Z to Low                   |         | 11.8 |         | 13.2 |         | 15.5 | ns    |

| t <sub>ENHZ</sub> | Enable Pad High to Z                  |         | 7.1  |         | 8.0  |         | 9.4  | ns    |

| t <sub>ENLZ</sub> | Enable Pad Low to Z                   |         | 8.4  |         | 9.5  |         | 11.1 | ns    |

| t <sub>GLH</sub>  | G to Pad High                         |         | 9.0  |         | 10.2 |         | 11.9 | ns    |

| t <sub>GHL</sub>  | G to Pad Low                          |         | 11.3 |         | 12.7 |         | 14.9 | ns    |

| $d_{TLH}$         | Delta Low to High                     |         | 0.07 |         | 0.08 |         | 0.09 | ns/pF |

| $d_THL$           | Delta High to Low                     |         | 0.12 |         | 0.13 |         | 0.16 | ns/pF |

| CMOS Outpu        | ıt Module Timing <sup>1</sup>         |         |      |         |      |         |      |       |

| t <sub>DLH</sub>  | Data to Pad High                      |         | 10.3 |         | 11.5 |         | 13.5 | ns    |

| t <sub>DHL</sub>  | Data to Pad Low                       |         | 8.5  |         | 9.6  |         | 11.2 | ns    |

| t <sub>ENZH</sub> | Enable Pad Z to High                  |         | 9.0  |         | 10.0 |         | 11.8 | ns    |

| t <sub>ENZL</sub> | Enable Pad Z to Low                   |         | 11.8 |         | 13.2 |         | 15.5 | ns    |

| t <sub>ENHZ</sub> | Enable Pad High to Z                  |         | 7.1  |         | 8.0  |         | 9.4  | ns    |

| t <sub>ENLZ</sub> | Enable Pad Low to Z                   |         | 8.4  |         | 9.5  |         | 11.1 | ns    |

| t <sub>GLH</sub>  | G to Pad High                         |         | 9.0  |         | 10.2 |         | 11.9 | ns    |

| t <sub>GHL</sub>  | G to Pad Low                          |         | 11.3 |         | 12.7 |         | 14.9 | ns    |

| $d_TLH$           | Delta Low to High                     |         | 0.12 |         | 0.13 |         | 0.16 | ns/pF |

| $d_THL$           | Delta High to Low                     |         | 0.09 |         | 0.10 |         | 0.12 | ns/pF |

#### Note: