# MXT3010

**Reference Manual**

Version 4.1

**Order Number: 100108-05**

#### October 1999

Copyright (c) 1999 by Maker Communications, Inc. All rights reserved.

Printed in the United States of America.

The information in this document is believed to be correct, however, the information can change without notice. Maker Communications, Inc. disclaims any responsibility for any consequences resulting from the use of the information contained in this document.

The hardware, software, and the related documentation is provided with RESTRICTED RIGHTS. Use, duplication, or disclosure by the U.S. Government is subject to restrictions as set forth in subparagraph (c)(1) (ii) of The Rights in Technical Data and Computer Program Product clause at DFARS 252.227-7013 or subparagraphs (c)(1) and (2) of the Commercial Computer Software-Restricted Rights at 48 CFR 52.227-19, as applicable.

Contractor/manufacturer is: Maker Communications, Inc. 73 Mount Wayte Avenue, Framingham, MA 01702

CellMaker and BridgeMaker are registered trademarks of Maker Communications, Inc. AccessMaker, High-Intensity Communications Processor, High-Intensity Communications Processing, PortMaker, Octave, and SimMaker are trademarks of Maker Communications, Inc. All other trademarks are owned by their respective companies.

This manual supercedes and obsoletes the following Maker Communications publications:

100108-03 - MXT3010 Reference Manual, dated June 1999 100108-04 - MXT3010 Reference Manual, dated October 1999

# **CONTENTS**

| Preface xxi |                                                                    |   |

|-------------|--------------------------------------------------------------------|---|

|             | Maker Products xxi                                                 |   |

|             | Using this manual xxiii                                            |   |

|             | Contacting Maker Support Services xxiv                             |   |

|             | Changes Installed in This Version of the Manual xxv                | * |

| Section 1   | Subsystems 1                                                       |   |

| CHAPTER 1   | Introduction 3                                                     |   |

|             | MXT3010 features 4                                                 |   |

|             | MXT3010 subsystems 5                                               |   |

|             | What information is in this manual 6                               |   |

| CHAPTER 2   | The SWAN Processor 9                                               |   |

|             | The SWAN advantage 10<br>SWAN's instructions and address spaces 10 |   |

Instruction execution 13 Instruction space organization 14 Instruction cache 15 SWAN processor instruction classes - 18 Arithmetic Logic Unit (ALU) instructions 19 **Branch instructions** 19 Registers 21 Flag registers 24 HEC generation and check circuit 25 The Cell Scheduling System 27 **CHAPTER 3** How the Cell Scheduling System works 28 Data transmission - servicing and scheduling 31 Servicing 31 Scheduling 32 Pacing the transmission rate of cells 37 Programming the Cell Scheduling System 38 Guaranteeing the availability of a location in the Connection ID table 41 The PUSHC/POPC instruction buffer 42 POPC, PUSHC, POPF, and PUSHF instruction operation 42 POPC and PUSHC timing 42 POPF and PUSHF timing 42 Connection ID table and Scoreboard addressing 43 Initializing the Scoreboard 45 Selecting a Scoreboard size 45 Supporting multiple Scoreboard sections 46 The Fast Memory Interface **CHAPTER 4** 47 SWAN processor accesses to Fast Memory 48 Loading 48 Storing 50 Cell Scheduling System accesses to Fast Memory 51 SWAN executable fetches from Fast Memory 51 Fast Memory configurations 52 Memory sizes supported 52 RAM selection and configuration 53

Mode 0 operation53Mode 1 operation54Bus contention avoidance55Fast Memory sequence diagrams56

#### CHAPTER 5

#### The Cell Buffer RAM 59

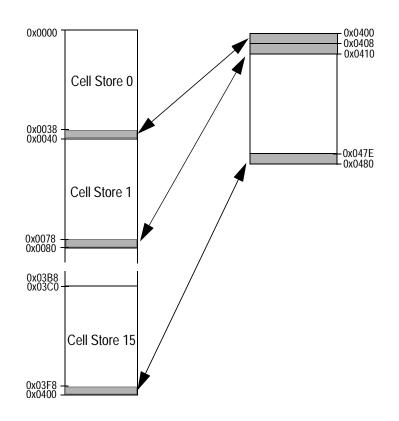

Internal cell storage in the Cell Buffer RAM60Cell Buffer RAM memory construction64Cell Buffer RAM access67

#### CHAPTER 6

#### *The UTOPIA port* 69

UTOPIA port interface overview 70 Features 70 Operating modes 71 UTOPIA cell formats 74 Receive cell flow 77 UTOPIA receiver counters 78 Transmit cell flow 82 UTOPIA transmitter counters 84 The TXBUSY counter 84 The TXFULL counter 86 CRC10 generation and checking support 87 Multi-PHY support 88 Receive Header Reduction hardware 91 UTOPIA port configuration summary 93 UTOPIA port sequence diagrams 94

CHAPTER 7

#### The Port1 and Port2 Interfaces 97

Port interface overview 98

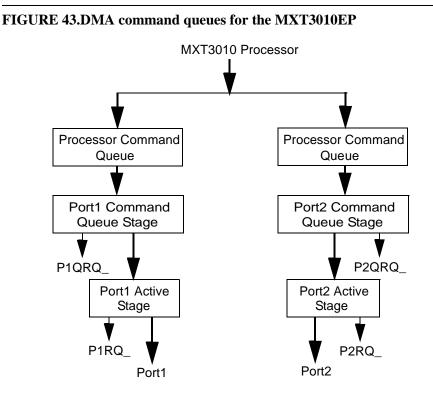

The Port DMA command queues 100

Port1 and Port2 DMA command queues 100

Testing DMA Controller queues with the ESS bits 101

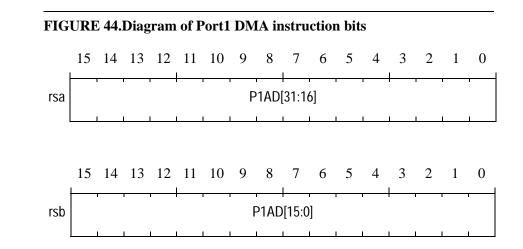

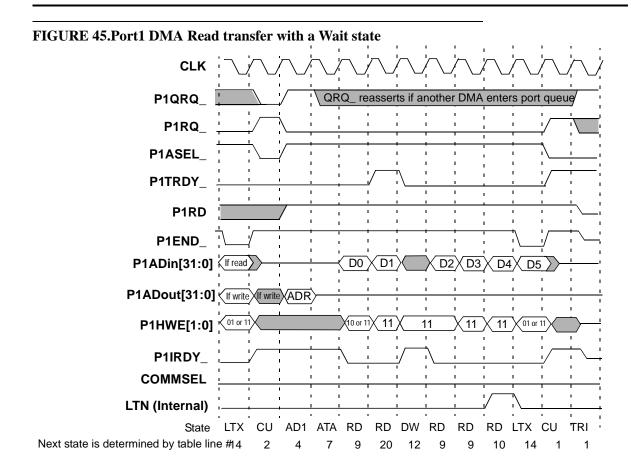

Port Controller features 103

The Cyclical Redundancy Check 32 generator for Port1 103

Cyclical Redundancy Check operation acceleration 104

Silent transfers 105

*Post-increment option on rla operations* 107 Data alignment 107 Byte manipulations on Port1 108 Post-DMA Operation Directives (PODs) 109 Burst and non-burst operation (Port2) 109 Port Operations 110 Port1 basic protocol 110 The Port1 control state machine 113 Communication register I/O transfers 133 Port2 basic protocol 137 *The Port2 control state machine* 142 Port2 DMA non-burst-mode read transfers 150 Port2 DMA non-burst-mode write transfers 154 Additional Port1 and Port2 Design Information 156 Arbitrating access to Port1 156 Simplified Port2 interfaces 157 Bus driving, turnaround, and bus parking 158 Data Alignment 159 Transfer complete 161 Byte Count zero 161 External DMA cycle abort (P1ABORT\_) 163 Endian-ness 164 Port1 and Port2 Reference Designs 169 P1MemMaker 169 P2MemMaker 172

CHAPTER 8

Communications 177

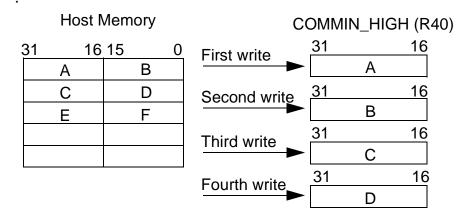

The COMMIN/COMMOUT register 178 Interchip communications 180

Section 2

### Register and Instruction Reference 183

Registers 183 Instructions 185 Instruction description notations 188

#### CHAPTER 9

#### Registers 189

Register types 189 Software registers 189 Hardware registers 190 Specifying registers in SWAN instructions 190 Initializing software and hardware registers 191 R32 General Purpose - 0000 193 R33 General Purpose - FFFF 194 R34 General Purpose - FF00 195 R35 196 General Purpose - 0040 R36-write Bit Bucket register 197 R37-R39 General Purpose registers 198 R40-R41 Host Communication registers 199 R42-read External State Signals (ESS) register 200 R42-write Mode Configuration register 201 R43-read Fast Memory Bit Swap register (R42w[8]=0) 203 R43-read Special Features register (R42w[8]=1) 204 R43-write UTOPIA Control FIFO register 205 R44-R47 CRC32PRX and CRC32PRY registers 207 R48-R51 Local Address registers (rla) 208 R52 Alternate Byte Count/ID register 209 R53 Instruction Base Address register 210 R54-R55 Programmable Interval Timer registers 211 R56 Fast Memory Data register 212 R57-read Sparse Event/ICS register 213 R57-write Sparse Event/ICS register (Set/Clear) 214 **R58** Fast Memory Shadow register 215 R59 Branch register 216 R60 The Cell Scheduling System (CSS) Configuration register 217 R61-read Scheduled Address register 218 R62 The UTOPIA Configuration register 219 R63 The System register 221

**CHAPTER 10**

#### Arithmetic Logic Unit Instructions 223

Addressing modes 223

| Triadic       | register 223                                        |

|---------------|-----------------------------------------------------|

| Immediate 224 |                                                     |

| Overflow      | flag 225                                            |

| Instruction   | n options 226                                       |

| Modulo        | arithmetic 226                                      |

|               | tic memory updates 228                              |

|               | anching 228                                         |

| ADD           | Add Registers 234                                   |

| ADDI          | Add Register and Immediate 235                      |

| AND           | And Registers 236                                   |

| ANDI          | And Register and Immediate 237                      |

| CMP           | Compare Two Registers 238                           |

| CMPI          | Compare Register and Immediate 239                  |

| CMPP          | Compare Two Registers with Previous 240             |

| CMPPI         | Compare Register and Immediate with<br>Previous 241 |

| FLS           | Find Last Set 242                                   |

| LIMD          | Load Immediate 243                                  |

| MAX           | Maximum of Two Registers 244                        |

| MAXI          | Maximum of Register and Immediate 245               |

| MIN           | Minimum of Two Registers 246                        |

| MINI          | Minimum of Register and Immediate 247               |

| OR            | Or Registers 248                                    |

| ORI           | Or Register and Immediate 249                       |

| SFT           | Shift Signed Amount 250                             |

| SFTA          | Shift Right Arithmetic 251                          |

| SFTAI         | Shift Right Arithmetic Immediate 252                |

| SFTC          | Shift Left Circular 253                             |

| SFTCI         | Shift Circular Immediate 254                        |

| SFTRI/SF      | TLI Shift Right or Left Immediate 255               |

| SUB           | Subtract Registers 256                              |

| SUBI          | Subtract Register and Immediate 257                 |

| XOR           | XOR Registers 258                                   |

| XORI          | XOR Register and Immediate 259                      |

|               | C                                                   |

**CHAPTER 11**

#### Branch Instructions 261

General Branch instruction information 262

|            | Introduction 262<br>Target address 262<br>Condition code (ESS Field) 263<br>The logical state identifier (S-Bit) 264<br>Committed slot instructions 264<br>The Conditional operator (C-bit) 265<br>Subroutine linking 268<br>Counter system operation 269<br>BF Branch Fast Memory Shadow<br>Register 270<br>BFL Branch Fast Memory Shadow<br>Register and Link 271<br>BI Branch Immediate 272<br>BIL Branch Immediate and Link 273<br>BR Branch Register 274       |                                 |

|------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------|

|            | BRL Branch Register and Link 275                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                 |

| CHAPTER 12 | Cell Scheduling Instructions277Cell Scheduling System target address277POPCService Schedule278POPFPOP Fast279PUSHCSchedule280PUSHFPush Fast281                                                                                                                                                                                                                                                                                                                      |                                 |

| CHAPTER 13 | Direct Memory Access Instructions<br>General DMA instruction information 284<br>Introduction 284<br>Op codes for DMA instructions 284<br>The RLA increment bit (i-bit) 285<br>The Byte Count instruction field option (BC) 286<br>The Control instruction field option 287<br>DMA1R Direct Memory Operation - Port1 Read<br>DMA1W Direct Memory Operation - Port1 Write<br>DMA2R Direct Memory Operation - Port2 Read<br>DMA2W Direct Memory Operation - Port2 Read | 283<br>289<br>290<br>291<br>292 |

| CHAPTER 14 | Load and Store Fast Memory<br>Instructions 293                                                                                                                                                                                                                                                                                                                                                                    |

|------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|            | <ul> <li>General information for Load and Store Fast Memory<br/>instructions 294</li> <li>Introduction 294</li> <li>Transfer size (the #HW field) 295</li> <li>Fast Memory address (the rsa and rsb fields) 296</li> <li>Address masking (the Z-bit) 296</li> <li>Destination register (the rd field) 299</li> <li>Linking (the LNK bit) 299</li> <li>Instructions for accelerating CRC operations 305</li> </ul> |

|            | Alternate address (the adr field) 306<br>Hardware register (reg field) 307<br>Least significant bits (the lsbs field) 307                                                                                                                                                                                                                                                                                         |

|            | LMFM   Load Multiple from Fast Memory   308                                                                                                                                                                                                                                                                                                                                                                       |

|            | SHFMStore Halfword to Fast Memory311SRHStore Register Halfword312                                                                                                                                                                                                                                                                                                                                                 |

| CHAPTER 15 | Load and Store Internal RAM<br>Instructions 313                                                                                                                                                                                                                                                                                                                                                                   |

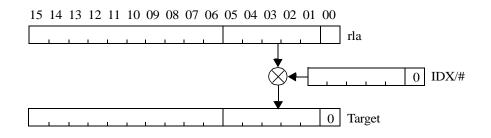

|            | General information for Load and Store internal RAM<br>instructions 314<br>Introduction 314<br>Register load address (rla field) 314<br>The index field (IDX) 315                                                                                                                                                                                                                                                 |

|            | Byte swap support 319<br>The Swap field 319                                                                                                                                                                                                                                                                                                                                                                       |

|            | LD Load Register 321                                                                                                                                                                                                                                                                                                                                                                                              |

|            | LDD Load Double Register 322                                                                                                                                                                                                                                                                                                                                                                                      |

|            | STStore Register323STDStore Double Register324                                                                                                                                                                                                                                                                                                                                                                    |

| CHAPTER 16 | Swan Instruction Reference Examples 325                                                                                                                                                                                                                                                                                                                                                                           |

|            | Add and Subtract examples 326<br>Branch examples 328                                                                                                                                                                                                                                                                                                                                                              |

|            | Load and Store Fast Memory examples 331                                                                                                                                                                                                                                                                                                                                                                           |

|            | Load and Store Internal RAM examples 332<br>Logical examples 334<br>Shift examples 335<br>Miscellaneous examples 338             |

|------------|----------------------------------------------------------------------------------------------------------------------------------|

| Section 3  | Signal Descriptions and Electrical                                                                                               |

|            | Characteristics 341                                                                                                              |

| CHAPTER 17 | Timing 343                                                                                                                       |

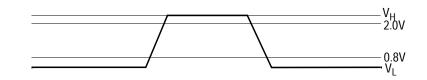

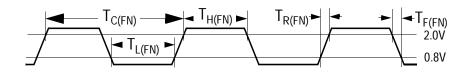

|            | MXT3010EP timing - general information 343<br>Definition of switching levels 343<br>Input clock details 344                      |

|            | MXT3010EP Fast Memory interface timing 345                                                                                       |

|            | MXT3010EP UTOPIA interface timing 348                                                                                            |

|            | MXT3010EP Port1 timing 352                                                                                                       |

|            | MXT3010EP Port2 timing 356<br>MXT3010EP miscellaneous control signal timing 359                                                  |

|            | MXT3010EP Reset timing 360                                                                                                       |

|            | MXT3010EP Fast Memory interface operation 364                                                                                    |

|            | MXT3010EP JTAG operation 365                                                                                                     |

| CHAPTER 18 | Pin Information 367                                                                                                              |

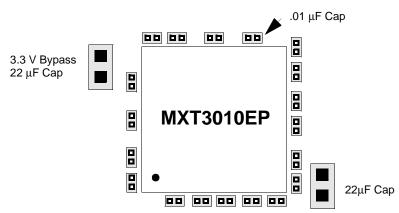

|            | MXT3010EP pinout 368                                                                                                             |

|            | MXT3010EP signal descriptions 369                                                                                                |

|            | MXT3010EP JTAG/PLL pin termination 377<br>MXT3010EP pin listing 378                                                              |

|            | I/O pad reference 381                                                                                                            |

| CHAPTER 19 | Electrical Parameters 383                                                                                                        |

|            | MXT3010EP maximum ratings and operating conditions 384<br>DC electrical characteristics 385<br>AC electrical characteristics 385 |

|            | MXT3010EP power sequencing 386                                                                                                   |

|            | Overview 386<br>Damage to I/O pad metal 387<br>I/O pad latch-up 389                                                                                                                                                                                                                                                                                                                                                              |

|------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|            | MXT3010EP PLL considerations 390<br>Overview 390                                                                                                                                                                                                                                                                                                                                                                                 |

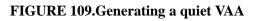

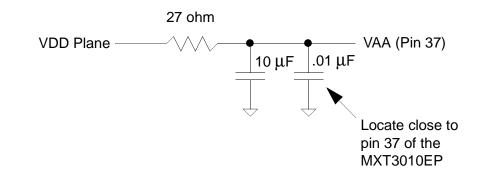

|            | VAA decoupling 391<br>General decoupling 392                                                                                                                                                                                                                                                                                                                                                                                     |

|            | Reference clock jitter 393                                                                                                                                                                                                                                                                                                                                                                                                       |

|            | Circuit design goals 394                                                                                                                                                                                                                                                                                                                                                                                                         |

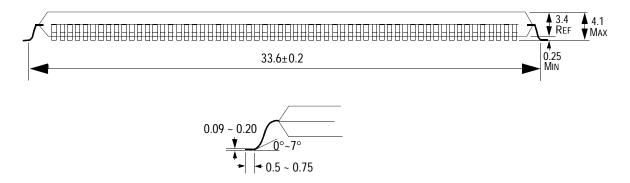

| CHAPTER 20 | Mechanical and Thermal Information 395                                                                                                                                                                                                                                                                                                                                                                                           |

|            | MXT3010EP mechanical/thermal information 396                                                                                                                                                                                                                                                                                                                                                                                     |

| APPENDIX A | Acronyms 399                                                                                                                                                                                                                                                                                                                                                                                                                     |

| APPENDIX B | Device Initialization 401                                                                                                                                                                                                                                                                                                                                                                                                        |

|            | <ul> <li>Initializing the MXT3010EP 402</li> <li>Downloading firmware 402</li> <li>How the system determines the boot path 402</li> <li>How the application uses the output pins 403</li> <li>How the code set is structured 404</li> <li>How to boot 405</li> <li>Limitations on the size of boot code 407</li> <li>Initializing the Mode Configuration register 408</li> <li>Restrictions on starting addresses 409</li> </ul> |

| APPENDIX C | Quick Reference 411                                                                                                                                                                                                                                                                                                                                                                                                              |

|            | Hardware register summary 412                                                                                                                                                                                                                                                                                                                                                                                                    |

|            | ALU instruction field summary 413                                                                                                                                                                                                                                                                                                                                                                                                |

|            | Shift amount summary 414                                                                                                                                                                                                                                                                                                                                                                                                         |

|            | Branch instruction field summary 416                                                                                                                                                                                                                                                                                                                                                                                             |

|            | DMA instruction field summary 417                                                                                                                                                                                                                                                                                                                                                                                                |

|            | Instruction summary 418                                                                                                                                                                                                                                                                                                                                                                                                          |

### **List of Figures**

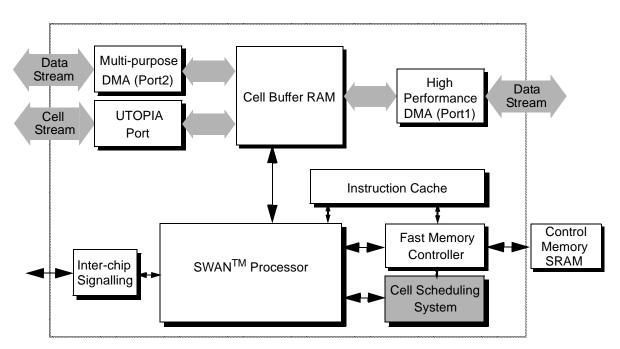

- FIGURE 1. MXT3010 and surrounding system devices 5

- FIGURE 2. SWAN processor address spaces and access instructions 11

- FIGURE 3. SWAN instruction space 14

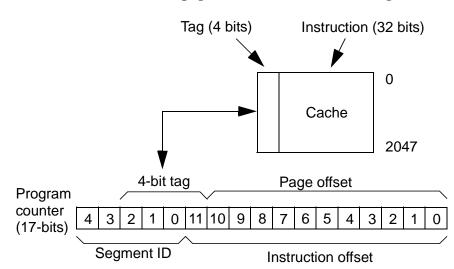

- FIGURE 4. Formation of the page offset and the instruction tag 16

- FIGURE 5. Target address format in Fast Memory 20

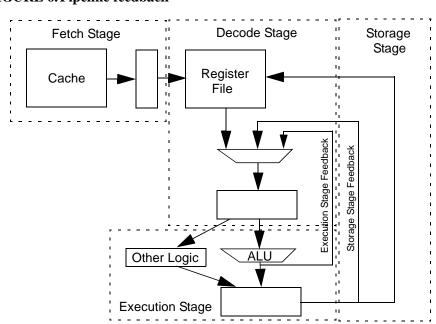

- FIGURE 6. Pipeline feedback 22

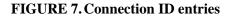

- FIGURE 7. Connection ID entries 30

- FIGURE 8. Servicing and scheduling 34

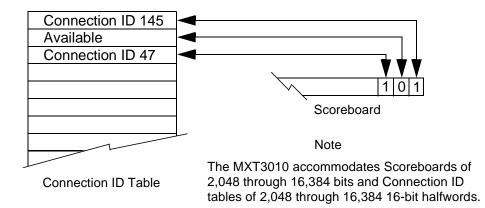

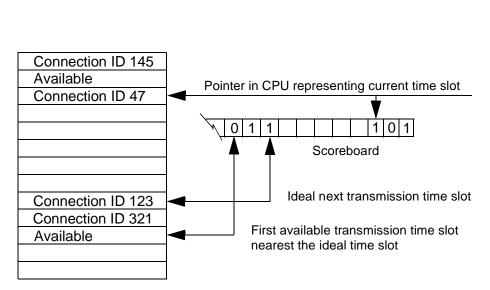

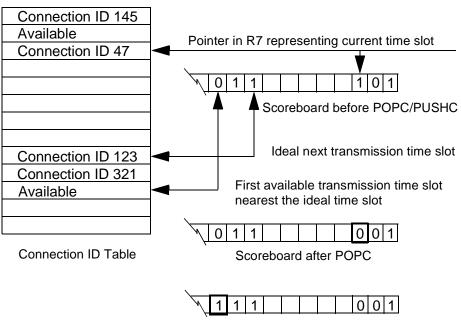

- FIGURE 9. Scoreboard operation 38

- FIGURE 10. Connection ID table address generation 44

- FIGURE 11. Scoreboard address generation 44

- FIGURE 12. Load Fast Memory instruction 48

- FIGURE 13. Store Fast Memory instruction 50

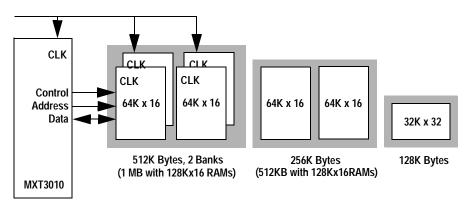

- FIGURE 14. Fast Memory SRAM options 52

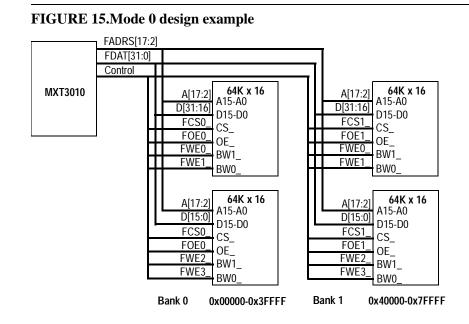

- FIGURE 15. Mode 0 design example 54

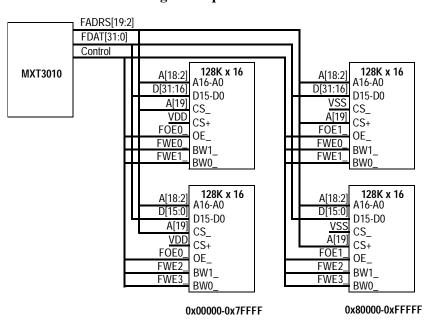

- FIGURE 16. Mode 1 design example 55

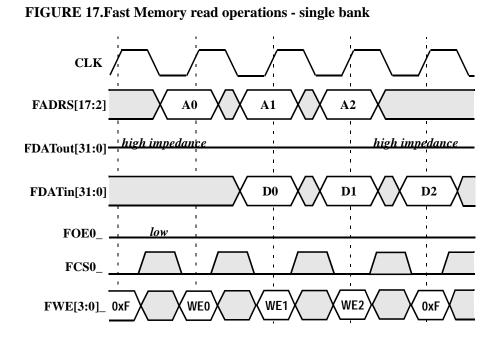

- FIGURE 17. Fast Memory read operations single bank 56

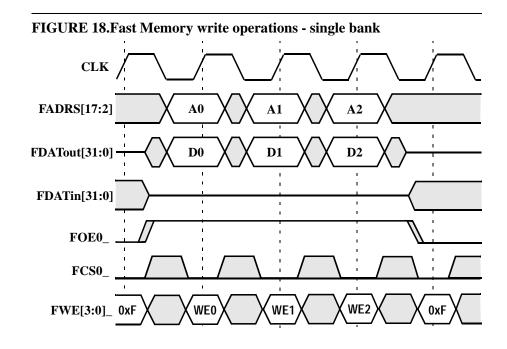

- FIGURE 18. Fast Memory write operations single bank 57

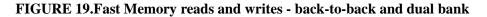

- FIGURE 19. Fast Memory reads and writes back-to-back and dual bank 57

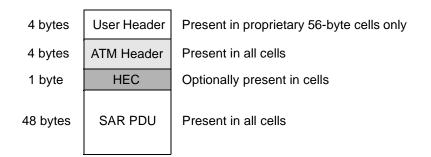

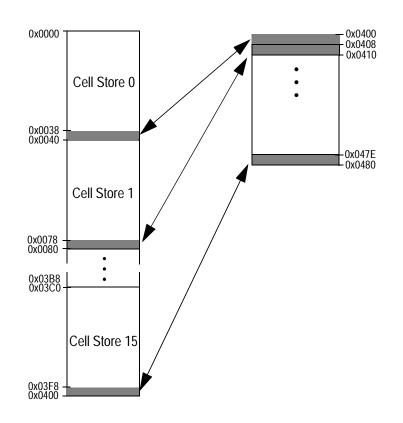

- FIGURE 20. Cell Buffer RAM organization 61

- FIGURE 21. Cell fields defined 62

- FIGURE 22. Receive cell organization: 52-byte and 56-byte cells 63

- FIGURE 23. Gather method accesses 66

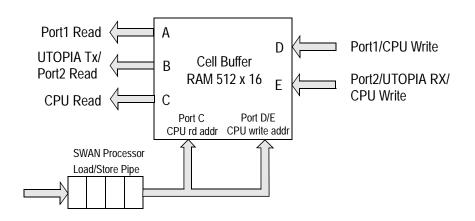

- FIGURE 24. Cell Buffer RAM access 67

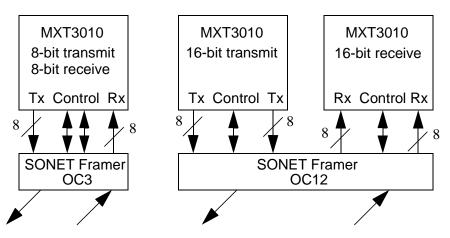

- FIGURE 25. The UTOPIA port: 8/8 and 16-bit modes 72

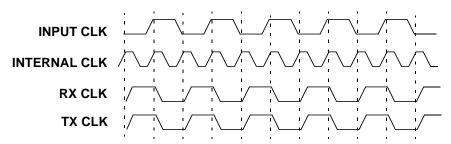

- FIGURE 26. Clock phases for RX/TX CLK = 1/2 Internal Clock 73

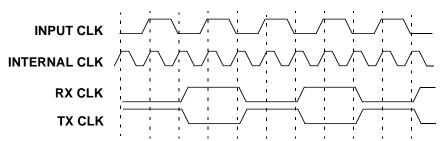

- FIGURE 27. Clock phases for RX/TX CLK = 1/4 Internal Clock 73

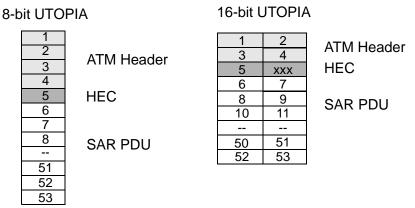

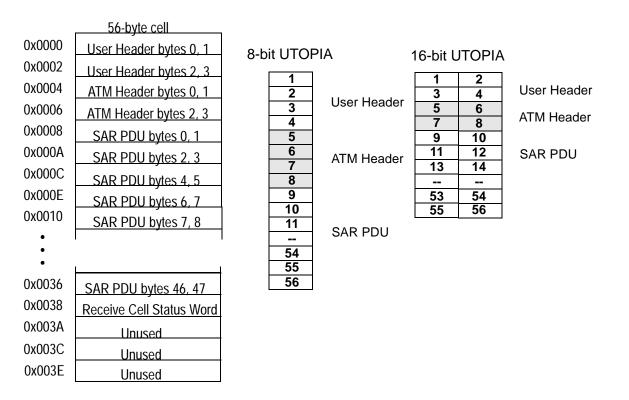

- FIGURE 28. UTOPIA 8-bit and 16-bit cell formats 74

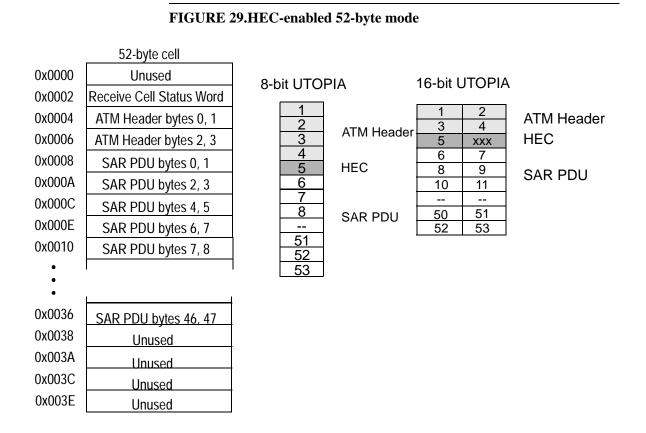

- FIGURE 29. HEC-enabled 52-byte mode 75

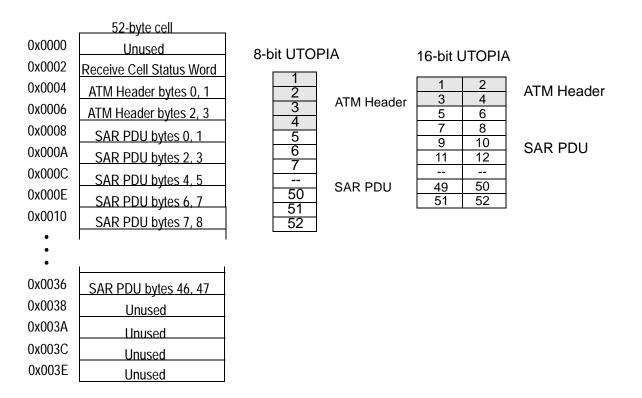

- FIGURE 30. HEC-disabled 52-byte mode 75

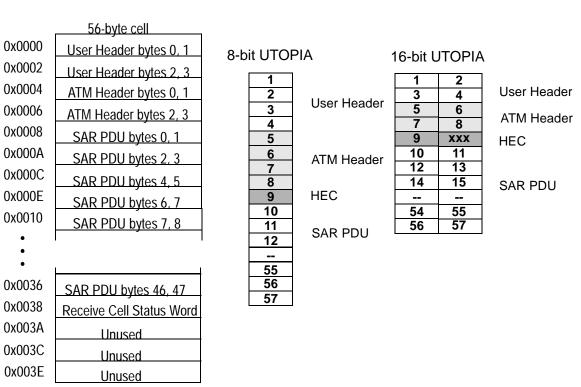

- FIGURE 31. HEC-enabled 56-byte mode 76

- FIGURE 32. HEC-disabled 56-byte mode 76

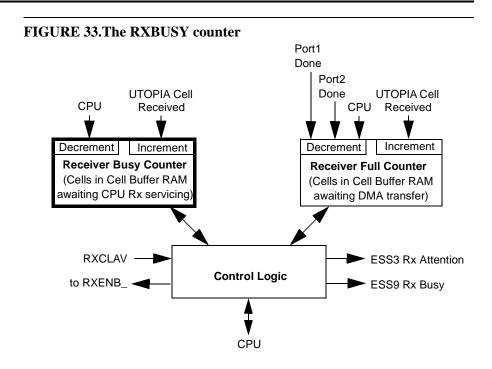

- FIGURE 33. The RXBUSY counter 79

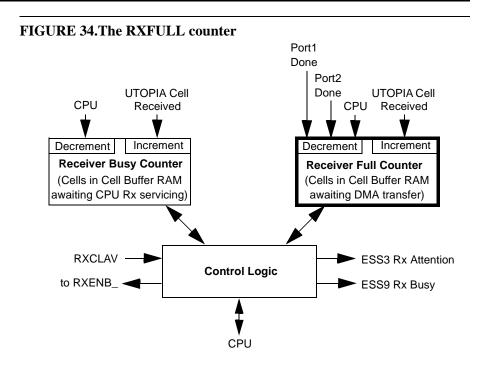

- FIGURE 34. The RXFULL counter 81

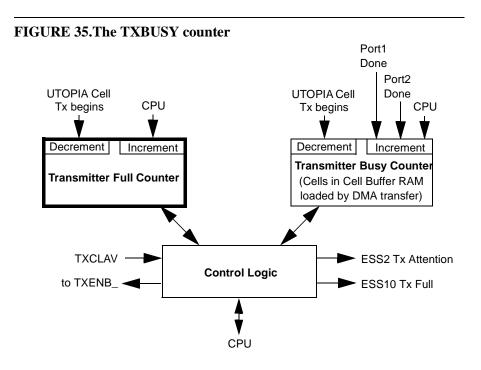

- FIGURE 35. The TXBUSY counter 84

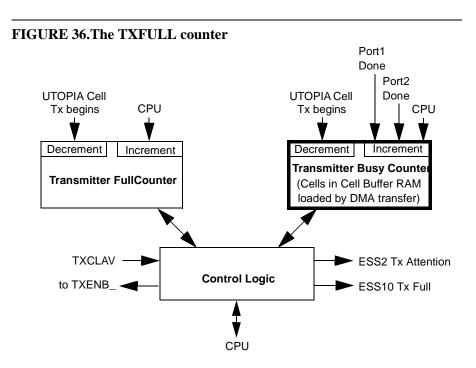

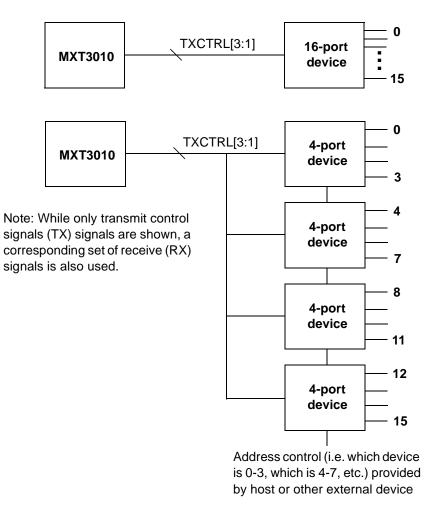

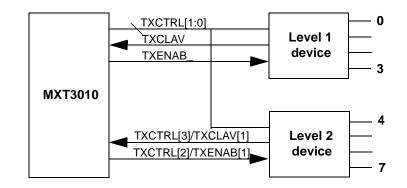

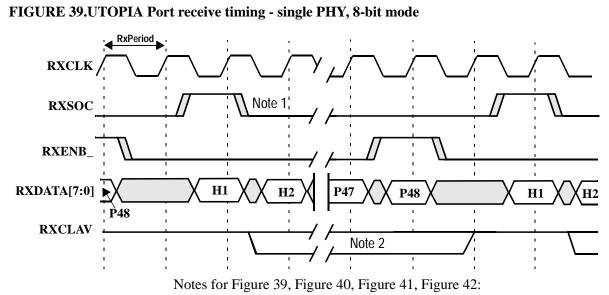

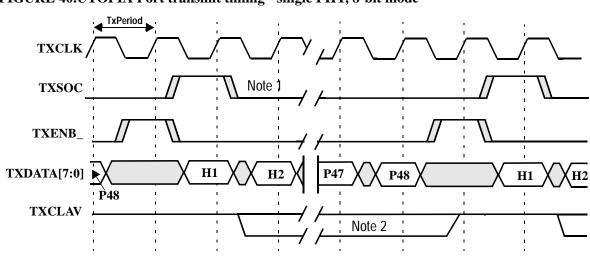

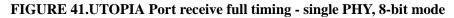

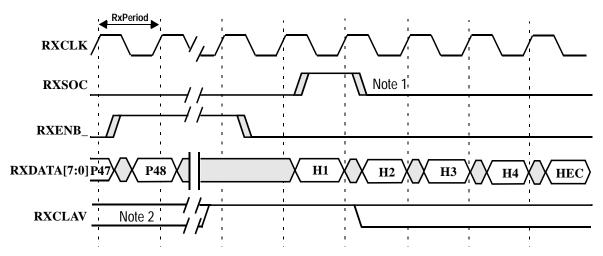

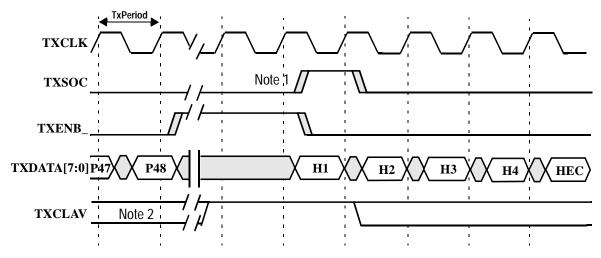

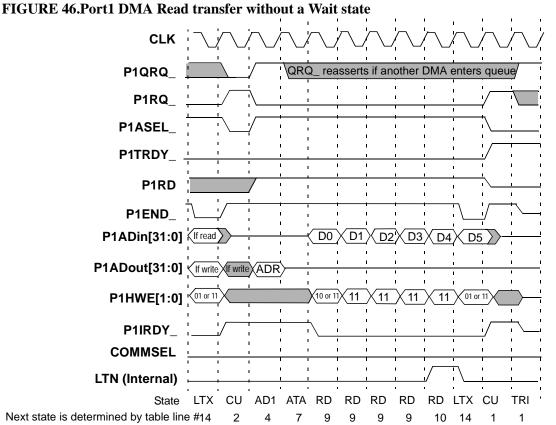

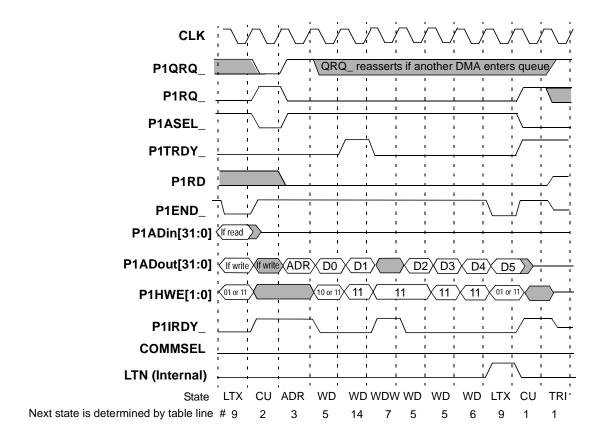

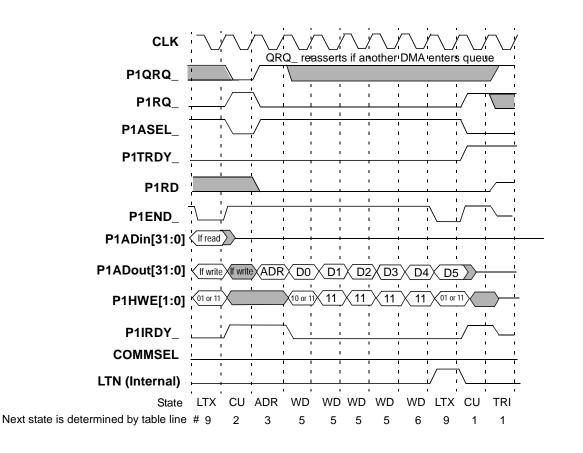

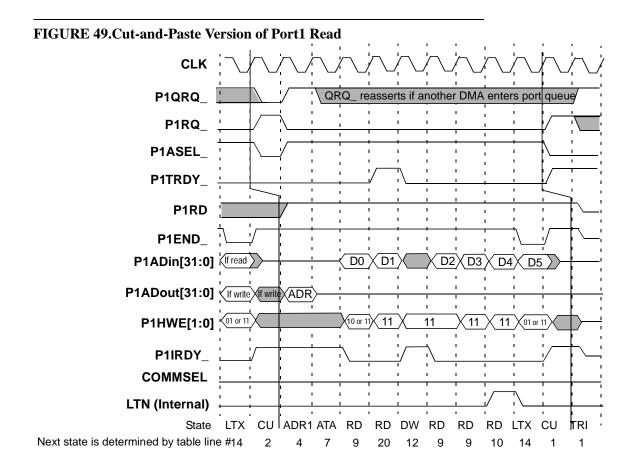

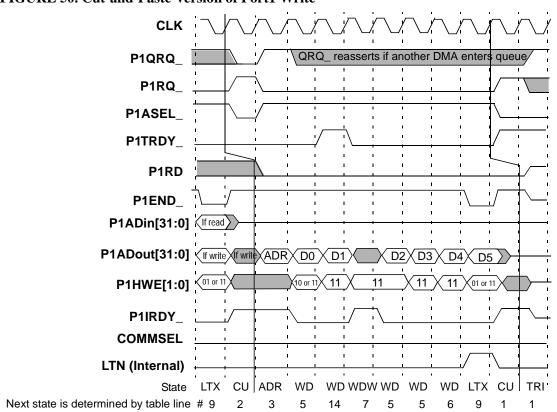

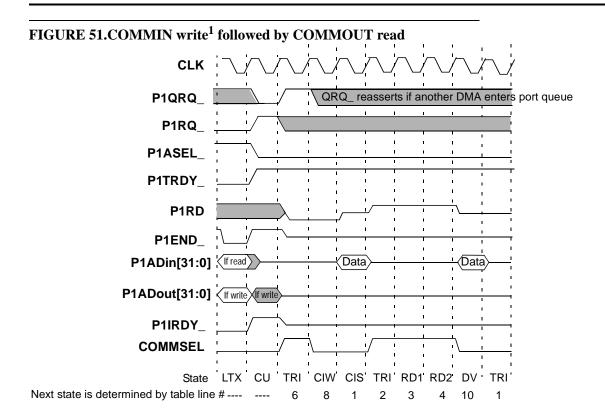

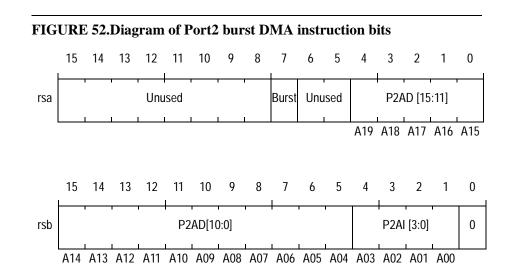

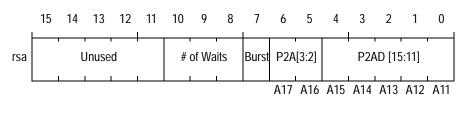

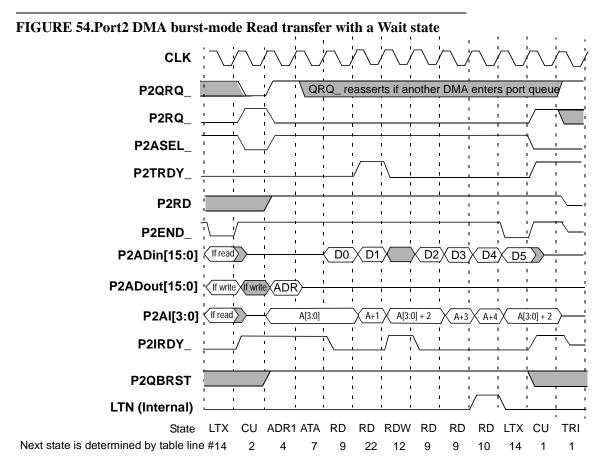

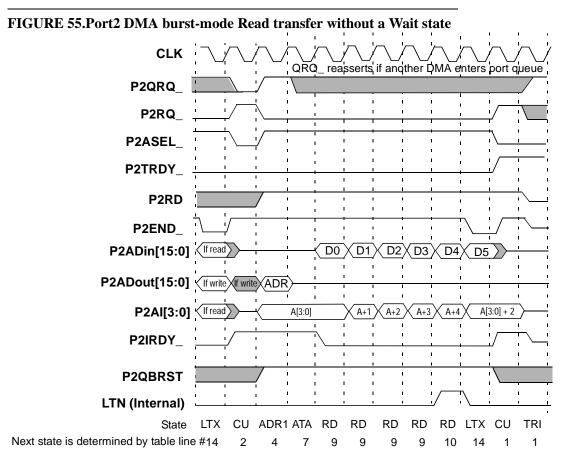

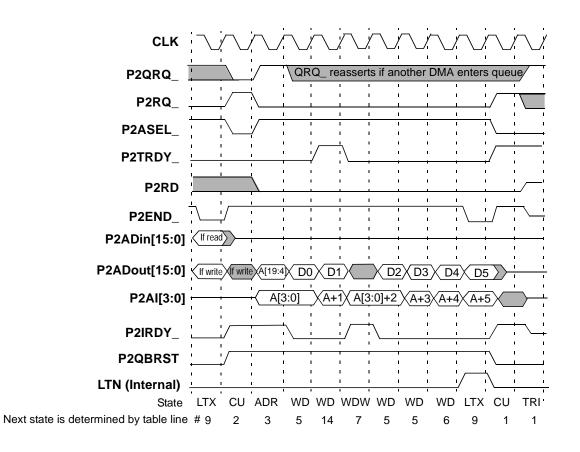

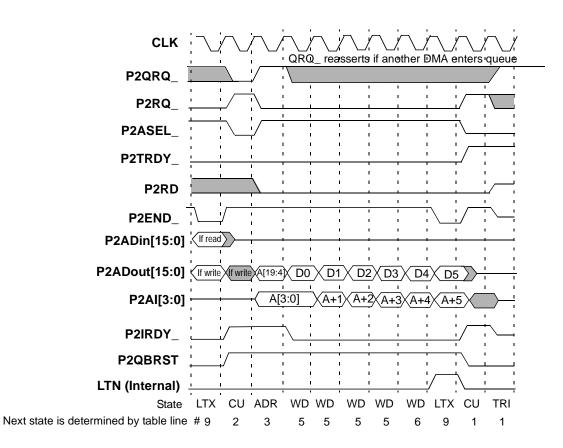

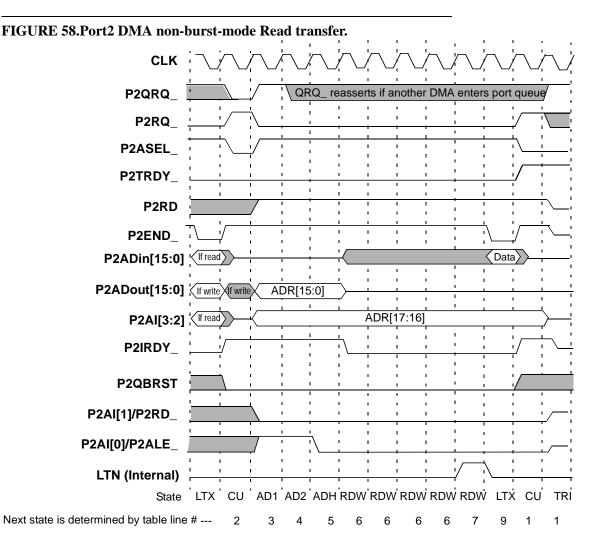

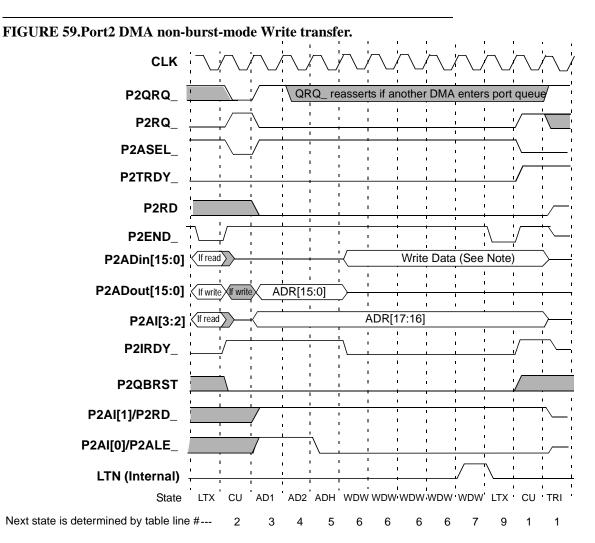

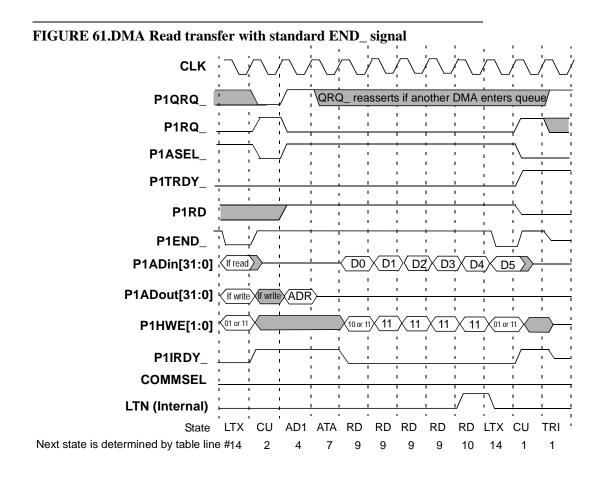

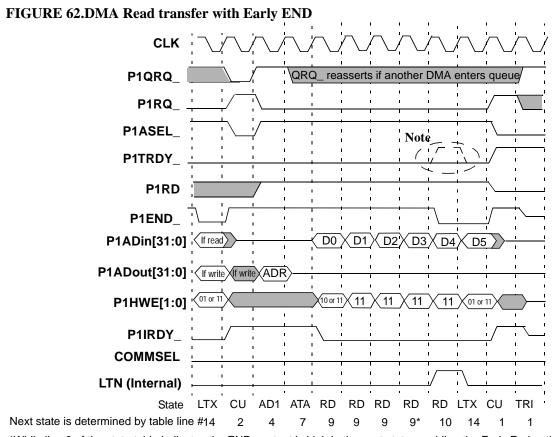

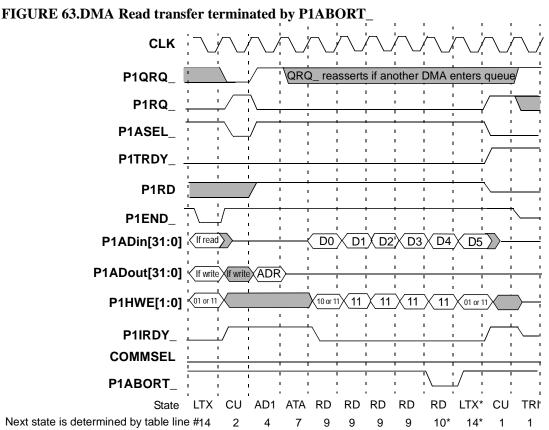

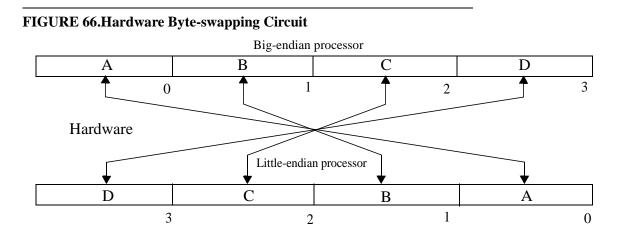

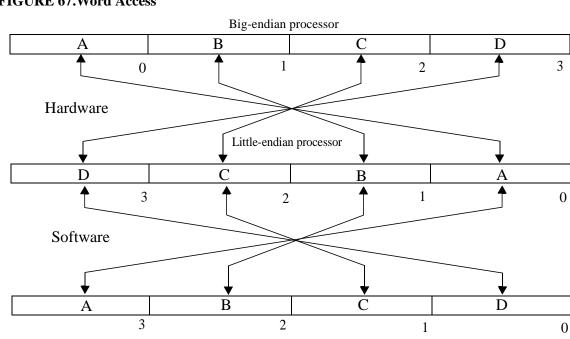

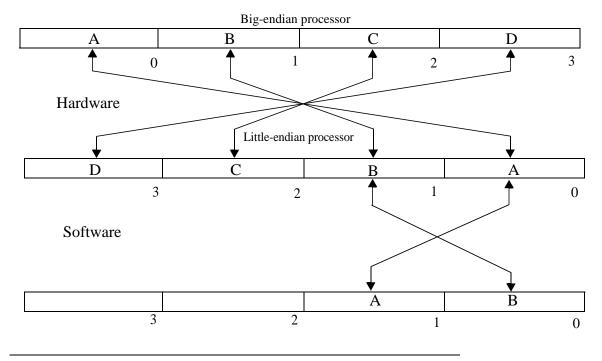

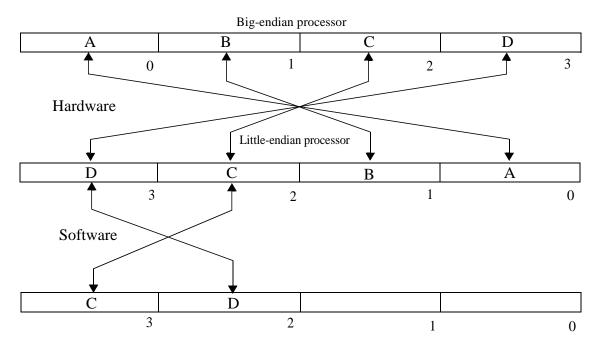

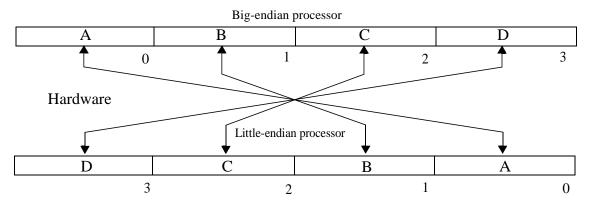

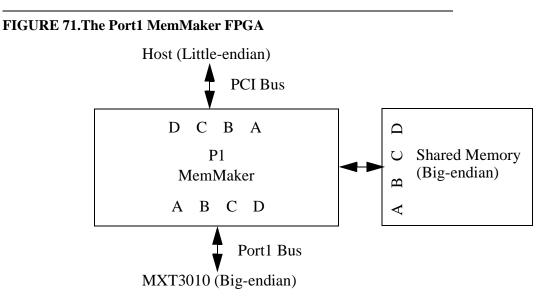

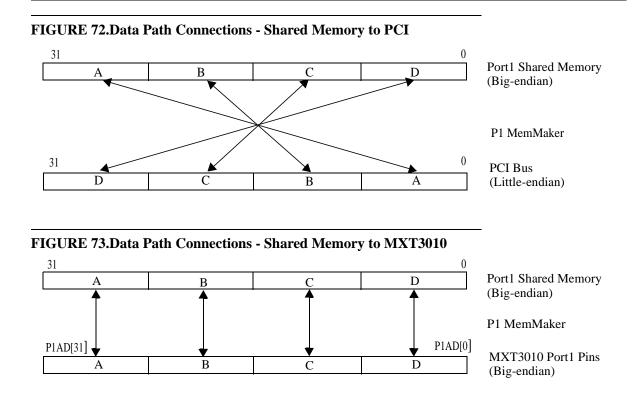

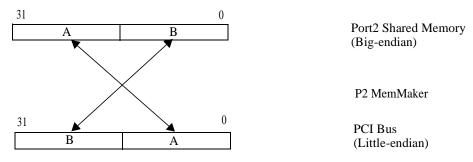

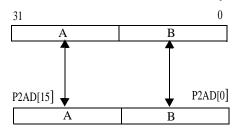

FIGURE 36. The TXFULL counter 85 FIGURE 37. Level 2 PHY configurations 89 FIGURE 38. Mixed Level 1 and Level 2 PHY configuration 90 FIGURE 39. UTOPIA Port receive timing - single PHY, 8-bit mode 94 FIGURE 40. UTOPIA Port transmit timing - single PHY, 8-bit mode 95 FIGURE 41. UTOPIA Port receive full timing - single PHY, 8-bit mode 95 FIGURE 42. UTOPIA Port transmit full timing - single PHY, 8-bit mode 95 FIGURE 43. DMA command queues for the MXT3010EP 100 FIGURE 44. Diagram of Port1 DMA instruction bits 111 FIGURE 45. Port1 DMA Read transfer with a Wait state 119 FIGURE 46. Port1 DMA Read transfer without a Wait state 122 FIGURE 47. Port1 DMA Write transfer with a Wait state 127 FIGURE 48. Port1 DMA Write transfer without a Wait state 130 FIGURE 49. Cut-and-Paste Version of Port1 Read 131 FIGURE 50. Cut-and-Paste Version of Port1 Write 132 FIGURE 51. COMMIN write followed by COMMOUT read 134 FIGURE 52. Diagram of Port2 burst DMA instruction bits 137 FIGURE 53. Diagram of Port2 non-burst DMA instruction bits 139 FIGURE 54. Port2 DMA burst-mode Read transfer with a Wait state 144 FIGURE 55. Port2 DMA burst-mode Read transfer without a Wait state 145 FIGURE 56. Port2 DMA burst-mode write transfer with a Wait state 148 FIGURE 57. Port2 DMA burst-mode write transfer without a Wait state 149 FIGURE 58. Port2 DMA non-burst-mode Read transfer. 151 FIGURE 59. Port2 DMA non-burst-mode Write transfer. 155 FIGURE 60. System example for Port1 bus. 156 FIGURE 61. DMA Read transfer with standard END\_ signal 161 FIGURE 62. DMA Read transfer with Early END 162 FIGURE 63. DMA Read transfer terminated by P1ABORT\_ 163 FIGURE 64. Most Significant Byte is the Lowest Address ("Big-endian") 164 FIGURE 65. Least Significant Byte is the Lowest Address ("Little-endian") 164 FIGURE 66. Hardware Byte-swapping Circuit 165 FIGURE 67. Word Access 166 FIGURE 68. 16-bit xxx0 Access 167 FIGURE 69. 16-bit xxx2 Access 167 FIGURE 70. Byte Access 168 FIGURE 71. The Port1 MemMaker FPGA 171 FIGURE 72. Data Path Connections - Shared Memory to PCI 172

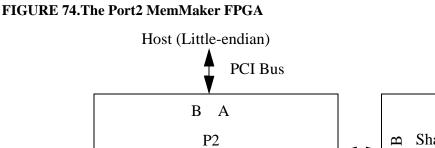

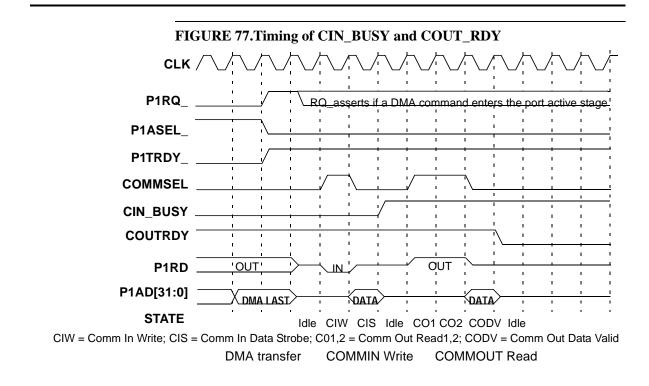

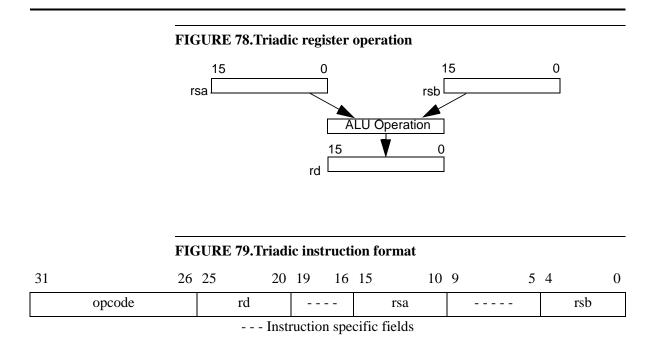

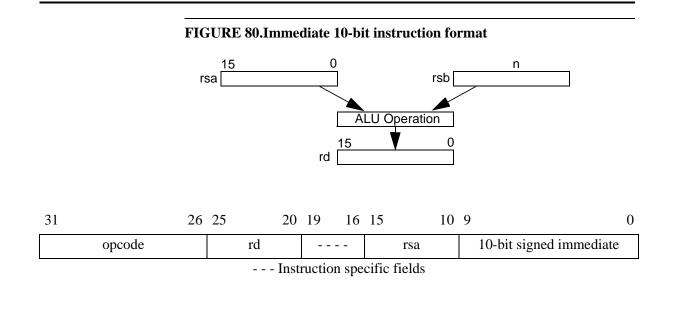

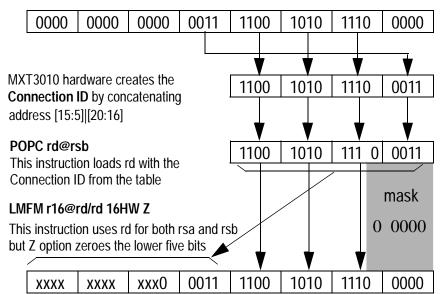

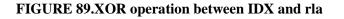

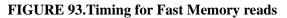

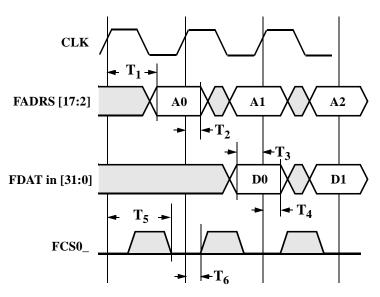

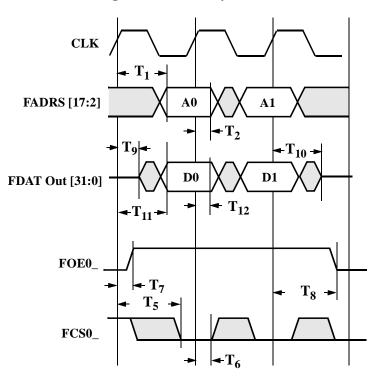

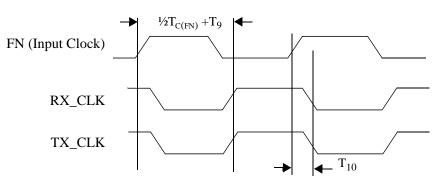

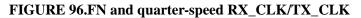

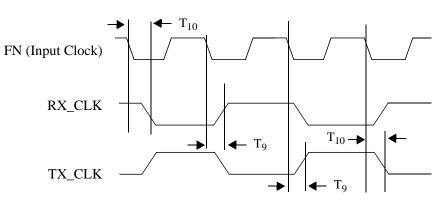

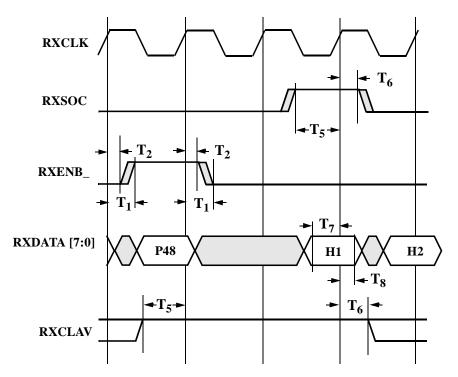

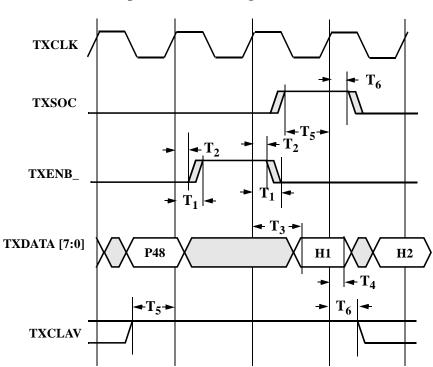

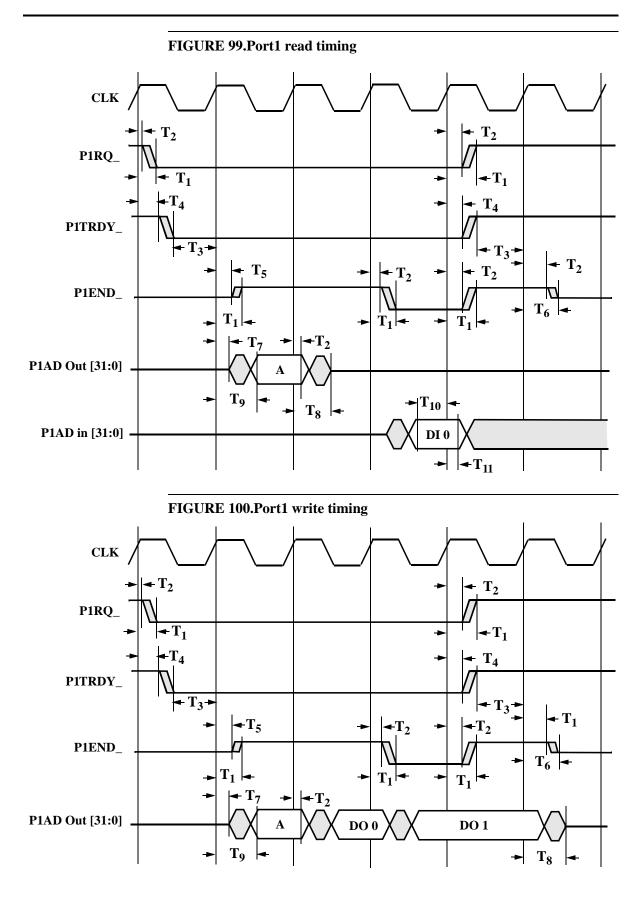

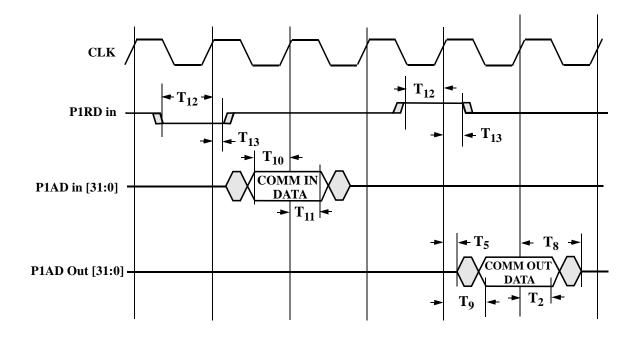

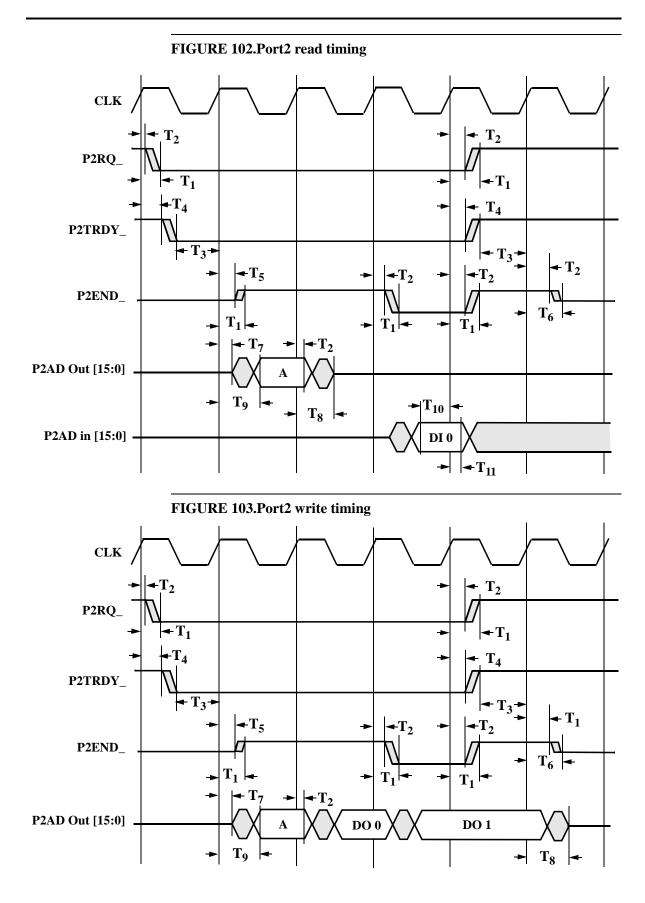

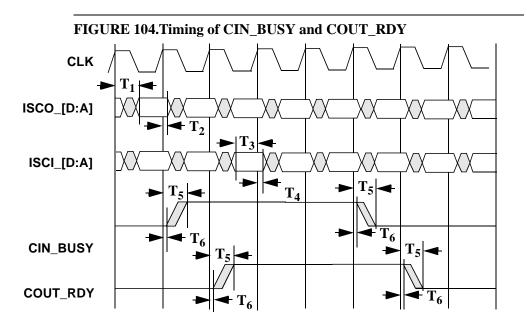

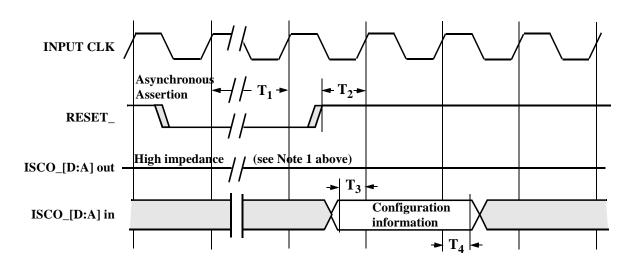

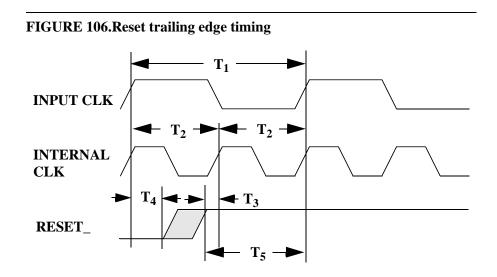

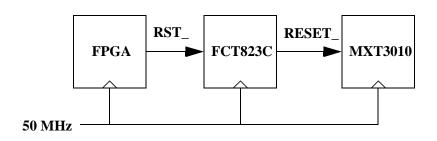

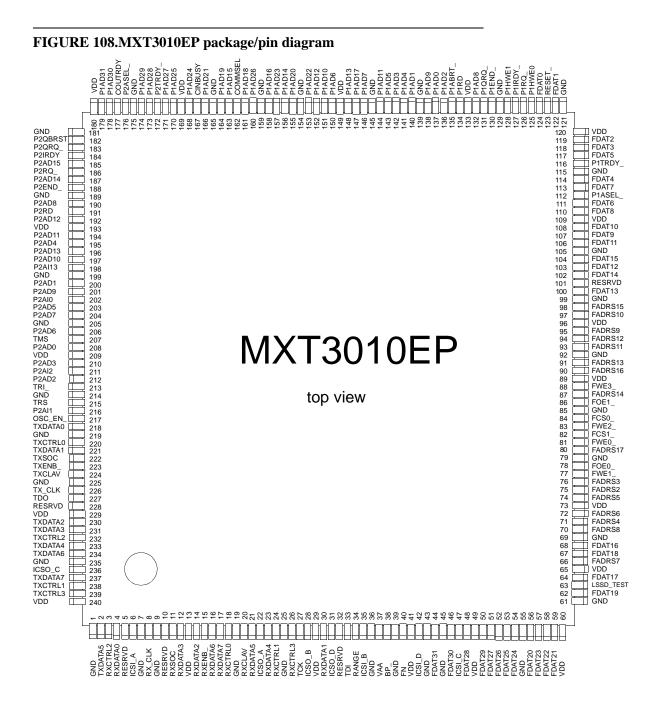

FIGURE 73. Data Path Connections - Shared Memory to MXT3010 172 FIGURE 74. The Port2 MemMaker FPGA 174 FIGURE 75. Data Path Connections - Shared Memory to PCI 174 FIGURE 76. Data Path Connections - Shared Memory to MXT3010 175 FIGURE 77. Timing of CIN\_BUSY and COUT\_RDY 180 FIGURE 78. Triadic register operation 224 FIGURE 79. Triadic instruction format 224 FIGURE 80. Immediate 10-bit instruction format 225 FIGURE 81. Immediate 6-bit instruction format 225 FIGURE 82. Branch instruction format (simplified) 262 FIGURE 83. Target address format in Fast Memory 262 FIGURE 84. DMA instruction format (simplified) 284 FIGURE 85. Control field format) 287 FIGURE 86. Z-bit usage example 298 FIGURE 87. Simplified Channel Descriptors 300 FIGURE 88. Channel Descriptor for LMFM and UM example 302 FIGURE 89. XOR operation between IDX and rla 316 FIGURE 90. Gather method accesses 318 FIGURE 91. Switching level voltages 343 FIGURE 92. Input clock waveform (pin FN) 344 FIGURE 93. Timing for Fast Memory reads 347 FIGURE 94. Timing for Fast Memory writes 347 FIGURE 95. FN and half-speed RX\_CLK/TX\_CLK 348 FIGURE 96. FN and quarter-speed RX\_CLK/TX\_CLK 348 FIGURE 97. UTOPIA port receive timing 350 FIGURE 98. UTOPIA port transmit timing 351 FIGURE 99. Port1 read timing 354 FIGURE 100.Port1 write timing 354 FIGURE 101.COMMIN register write, COMMOUT register read timing 355 FIGURE 102.Port2 read timing 358 FIGURE 103.Port2 write timing 358 FIGURE 104. Timing of CIN\_BUSY and COUT\_RDY 359 FIGURE 105.MXT3010EP reset timing 361 FIGURE 106.Reset trailing edge timing 362 FIGURE 107.Reset timing circuit 363 FIGURE 108.MXT3010EP package/pin diagram 368 FIGURE 109.Generating a quiet VAA 392

| FIGURE 110.MXT3010EP decoupling capacitor location   | 393 |

|------------------------------------------------------|-----|

| FIGURE 111.MXT3010EP package/pin diagram - top view  | 396 |

| FIGURE 112.MXT3010EP package/pin diagram - side view | 397 |

### **List of Tables**

| Table 1  | SWAN processor instruction classes 18                                |

|----------|----------------------------------------------------------------------|

| Table 2  | Methods of specifying the branch target field 21                     |

| Table 3  | Hardware registers requiring one instruction delay 23                |

| Table 4  | Hardware registers requiring two instruction delays 24               |

| Table 5  | Scoreboard sectioning control 29                                     |

| Table 6  | Connection ID table address bits 44                                  |

| Table 7  | Scoreboard address bits 44                                           |

| Table 8  | Comparison of Mode 0 and Mode 1 operation 53                         |

| Table 9  | UTOPIA Configuration control of the Cell Buffer RAM 60               |

| Table 10 | Cell field functions 62                                              |

| Table 11 | UTOPIA port data bus width selection 71                              |

| Table 12 | UTOPIA port Tx and Rx pin utilization in 16-bit mode 71              |

| Table 13 | Cell length and HEC control 72                                       |

| Table 14 | UTOPIA port clock selection 73                                       |

| Table 15 | Bit assignments for multi-PHY operation 88                           |

| Table 16 | Receive Header Reduction control 91                                  |

| Table 17 | Receive Header Reduction enable bit 92                               |

| Table 18 | UTOPIA configuration information 93                                  |

| Table 19 | Characteristics of Port1 and Port2 98                                |

| Table 20 | ESS Bits for DMA Controller status 102                               |

| Table 21 | Example of DMA Controller status bit utilization 102                 |

| Table 22 | Specification of the CRCX/CRCY instruction field option 103          |

| Table 23 | Valid and invalid first, mid-cell, and last transfers. 108           |

| Table 24 | Port 1 DMA instruction bit mapping 111                               |

| Table 25 | Signals to control Port1 transfers 112                               |

| Table 26 | State table for the Port1 DMA burst read state machine 118           |

| Table 27 | State table for the Port1 DMA burst write state machine 126          |

| Table 28 | State table for Port1 communication I/O state machine 133            |

| Table 29 | Port2 burst DMA instruction bit mapping 137                          |

| Table 30 | Another view of Port2 burst DMA instruction bit mapping 138          |

| Table 31 | Port2 non-burst DMA instruction bit mapping 139                      |

| Table 32 | Another view of Port2 non-burst DMA instruction bit mapping 140      |

| Table 33 | Signals to control Port2 transfers 141                               |

| Table 34 | State table for the Port2 DMA burst-mode read state machine 143      |

| Table 35 | State table for the Port2 DMA burst write state machine 147          |

| Table 36 | State table for the Port2 DMA non-burst-mode read state machine 150  |

| Table 37 | State table for the Port2 DMA non-burst-mode write state machine 154 |

| Table 38 | Comparison of Big-endian and Little-endian Read Operations 165       |

| Table 39 | Accesses With Hardware and Software Swaps, 32-bit 166                |

| Table 40 | Accesses With Hardware and Software Swaps, 32-bit and 16-bit 168     |

- Table 41Accesses With Hardware and Software Swaps, 32-bit, 16-bit, and 8-bit 168

- Table 42Definitions of CIN\_BUSY and COUT\_RDY 178

- Table 43ICSI pins 180

- Table 44 ICSO pins 181

- Table 45Hardware registers 184

- Table 46Alphabetical list of instructions 186

- Table 47Abbreviations used in SWAN instructions 188

- Table 48Field abbreviations 190

- Table 49Hardware registers 191

- Table 50Signal utilization for 1-PHY and 2-PHY modes 220

- Table 51Modulo arithmetic options227

- Table 52ALU Branch Conditions for all instructions except Compare and Min/Max in-<br/>structions 230

- Table 53ALU Branch Conditions for Compare and Min/Max instructions 230

- Table 54Methods of specifying the Branch target field 263

- Table 55External State Signals register (R42) bits 264

- Table 56Use of the S-bit 264

- Table 57Use of the Conditional and Nullify operators 266

- Table 58Example conditional branch, condition satisfied 266

- Table 59Example conditional branch, condition not met 267

- Table 60Example unconditional branch 267

- Table 61

Example conditional operator, conditional branch, condition satisfied 267

- Table 62Example conditional operator, conditional branch, condition not satisfied 268

- Table 63Example Branch with link, and return 269

- Table 64The CSO field 269

- Table 65Op codes for DMA instructions 284

- Table 66Use of Bit 26 285

- Table 67Timing chart for accessing rla after a DMA 286

- Table 68Use of the BC field 286

- Table 69Use of the Control byte 288

- Table 70Load Fast Memory instruction format294

- Table 71Store Fast Memory instruction format294

- Table 72Use of the rsa and rsb fields 296

- Table 73Use of the Z-bit 296

- Table 74Limits on #HW when linking to rd 300

- Table 75Memory alignment requirements 304

- Table 76Use of the adr field 306

- Table 77Use of the reg field 307

- Table 78Restrictions on access to rd registers after LMFM 309

- Table 79Load internal RAM instruction format 314

- Table 80Store internal RAM instruction format314

- Table 81Use of the rla field 315

- Table 82Byte-swapping Load instructions 320

| Table 83  | Byte-swapping Store instructions 320                                     |

|-----------|--------------------------------------------------------------------------|

| Table 84  | Input clock timing parameters 344                                        |

| Table 85  | Fast Memory timing for the Maker MXT3010EP 346                           |

| Table 86  | UTOPIA timing for Maker MXT3010EP 349                                    |

| Table 87  | Delay of UTOPIA clocks relative to MXT3010EP internal clock (CLK) 350    |

| Table 88  | Port1 timing table 353                                                   |

| Table 89  | Port2 timing table 357                                                   |

| Table 90  | Miscellaneous control signal timing 359                                  |

| Table 91  | MXT3010EP reset timing 361                                               |

| Table 92  | MXT3010EP RESET_ timing parameters 362                                   |

| Table 93  | MXT3010EP Port1 signal descriptions 370                                  |

| Table 94  | MXT3010EP Port2 signal descriptions 371                                  |

| Table 95  | UTOPIA port signal description 372                                       |

| Table 96  | MXT3010EP Fast Memory controller signal description 373                  |

| Table 97  | MXT3010EP inter-chip and communication registers signal description 374  |

| Table 98  | MXT3010EP miscellaneous clock, control, and test signal descriptions 375 |

| Table 99  | Power and ground pin descriptions 376                                    |

| Table 100 | MXT3010EP pin terminations 377                                           |

| Table 101 | MXT3010EP pin listing 378                                                |

| Table 102 | I/O pad types 381                                                        |

| Table 103 | Absolute maximum ratings (VSS = $0V$ ) 384                               |

| Table 104 | Recommended operating conditions 384                                     |

| Table 105 | DC Electrical characteristics 385                                        |

| Table 106 | MXT3010EP package summary 397                                            |

| Table 107 | Selecting boot mode with ISCO_A and ICSO_B 403                           |

| Table 108 | User code set's four fields 404                                          |

| Table 109 | Bootstrap starting addresses for Fast Memory mode 1 409                  |

| Table 110 | Hardware registers 412                                                   |

| Table 111 | MODx fields 413                                                          |

| Table 112 | abc fields 413                                                           |

| Table 113 | AE field 413                                                             |

| Table 114 | UM field 413                                                             |

| Table 115 | Shift amount chart for SFT, SFTLI, and SFTRI 414                         |

| Table 116 | Shift amount chart for SFTC and SFTCI 414                                |

| Table 117 | Shift amount chart for SFTA 415                                          |

| Table 118 | Shift amount chart for SFTAI 415                                         |

| Table 119 | The CSO field 416                                                        |

| Table 120 | The ESS field (condition codes) 416                                      |

| Table 121 | The S-bit field 416                                                      |

| Table 122 | The C-bit field 416                                                      |

| Table 123 | Use of the I-bit 417                                                     |

| Table 124 | Use of the BC field 417                                                  |

| Table 125 | Use of the Control byte 417                                              |

|           | <b>,</b>                                                                 |

Table 126Instruction summary 418

## Preface

### Maker Products

| Integrated<br>Circuits | Maker Communications delivers a wide range of ATM solutions<br>based on the <b>MXT3010</b> cell processing engine and the <b>MXT3020</b><br>circuit interface coprocessor. The MXT3010 is a high-perfor-<br>mance programmable cell processor engine specifically designed<br>to handle ATM cell manipulation and transmission at data rates up<br>to 622 Mb/s. The MXT3020 is an ATM circuit interface coproces-<br>sor for the MXT3010 cell processor. It provides flexible inter-<br>working between Time Division Multiplexed (TDM) links and the<br>ATM network. |

|------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Software<br>Solutions  | The MXT3010 and MXT3020 are complemented with a series of software applications that provide standard cell processing func-<br>tionality. <b>CellMaker®-155</b> and <b>CellMaker®-622</b> execute on an MXT3010 and provide ATM Adaptation Layer 5 (AAL5) Seg-<br>mentation and Reassembly (SAR) at data rates of 155 Mb/s and 622 Mb/s, respectively. <b>AccessMaker™</b> executes on an MXT3010 with up to four attached MXT3020 coprocessors. It                                                                                                                   |

provides cell processing functions for both packet and circuit interworking to support multiple services concurrently including AAL1, AAL5, IMA, and cell relay.

Development Tools Maker Communications offers a full suite of development tools for the MXT3010 Cell Processor including Verilog models of the chips, the **WASM** assembler, CellMaker Simulator (**CSIM**), and Graphical CellMaker Simulator (**GCSIM**). CSIM is a Verilog-based simulator that provides a tightly controlled and fully observable environment to execute and debug both processor applications and external host programs before running them on the target hardware. Maker also provides two development boards. CSIM is complemented with a graphical post processor, GCSIM. The **MXT3016** is a 32-bit, PCI bus-based development board used to test 622Mb/s applications. The **MXT3025** is a 32bit, PCI bus-based evaluation board used to test OC-3 ATM (MXT3010) and T1 (MXT3020) applications.

### Using this manual

This section provides information on the conventions used within this manual.

Typographical This document uses the following typographical conventions when describing features of the hardware and software, user-machine interactions, and variables.

- Commands appear in mixed case, for example Write\_Channel\_Map.

- Instruction mnemonics appear in uppercase, for example the SUBBI instruction.

- User input appears in **bold monospace font**.

- System output and code examples appear in monospace font.

- Variables, such as user-definable names, appear in *italics*.

#### Instruction syntax All the instructions use the following syntax:

- Required values appear between (parentheses).

- Optional values appear between [square brackets].

- Optional descriptions appear in lowercase.

- Literal descriptions appear in UPPERCASE.

- Numbers are denoted by pound signs, #.

- A string of options from which you can only choose one appear as follows: [option1 | option2 | option3]

- A string of options from which you can choose one or all the options appear as follows: [option1] [option2] [option3]

- Bits which should be written as zeroes and ignored on reads appear as *Reserved*

Terminology Common acronyms and abbreviations are defined in "Acronyms" on page 399 and not in the text. In addition, this manual uses the following term as defined:

*Packets* refer to Local Area Network (LAN) information and *frames* refer to circuit information.

### **Contacting Maker Support Services**

Maker Communications, Inc. has the following forums for communicating ideas, questions, and reporting problems:

- Sales and customer support 508-628-0622

- Product support support@maker.com

- Product inquires info@maker.com

- Facsimile 508-628-0256

- Web www.maker.com

### Changes Installed in This Version of the Manual

| Change Bars | Change bars are provided to indicate revisions made since the previous publication of the manual.                                                                                                                                                                                                                                                                                                                                         |

|-------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Changes     | 1. Additional text has been added to "Register access rules" on page 22, and to the paragraph before that, concerning the use of LD and LDD between accesses to rla registers. Cross references to this warning have been added to "Avoiding stale rla values" on page 315, to "LD Load Register" on page 321, to "LDD Load Double Register" on page 322, and to all hardware register descriptions in CHAPTER 9 "Registers" on page 189. |

|             | <ol> <li>Figure 95, "FN and half-speed RX_CLK/TX_CLK," on<br/>page 348 and Figure 96, "FN and quarter-speed RX_CLK/<br/>TX_CLK," on page 348 have been added to show the rela-<br/>tionship of UTOPIA clocks to FN.</li> </ol>                                                                                                                                                                                                            |

|             | <b>3.</b> Figure 22, "Receive cell organization: 52-byte and 56-byte cells," on page 63 has been modified to correctly identify User Header bytes 2 and 3 in the 56-byte cell format.                                                                                                                                                                                                                                                     |

|             | <b>4.</b> The description of "LIMD Load Immediate" on page 243 has been corrected to indicate that the immediate is loaded into register <i>rd</i> , not register <i>rsa</i> .                                                                                                                                                                                                                                                            |

|             | 5. Table 47, "Abbreviations used in SWAN instructions," on page 188 has been modified to generalize the definition of <i>usi</i> .                                                                                                                                                                                                                                                                                                        |

|             | 6. The caption of Figure 89 on page 316 has been corrected to indicate that it applies to XOR rather than OR.                                                                                                                                                                                                                                                                                                                             |

|             | 7. A typographic error ("3020" vs "3010") in the description of out-of-bag floor life in "MXT3010EP mechanical/thermal information" on page 396 has been corrected.                                                                                                                                                                                                                                                                       |

|             | 8. The note that explains the enabling/disabling of "R54-R55 Programmable Interval Timer registers" on page 211 has been changed.                                                                                                                                                                                                                                                                                                         |

## Section 1 Subsystems

This section is composed of eight chapters. It provides an overview of the MXT3010 ATM cell processing engine and its major functional subsystems.

### CHAPTER 1 Introduction

The MXT3010 is Maker Communication's innovative, programmable ATM cell processing engine. The MXT3010 is built around Maker Communication's SWAN processor and specifically designed for use in high-speed ATM cell-processing applications. The MXT3010 delivers throughput at hard-wired speeds while maintaining all of the benefits of programmable approaches.

### MXT3010 features

MXT3010-based systems are insulated against changes in ATM standards because firmware modifications can accommodate these changes. The MXT3010 can:

- Scale across both performance and application ranges.

- Run at speeds ranging from 1.5 Mb/s up to 622 Mb/s.

- Handle the ATM Forum's Traffic Management 4.0 Available Bit Rate (ABR) service specification.

- Operate as a self-contained device managing concurrent Constant Bit Rate (CBR), Variable Bit Rate (VBR), and ABR connections, which frees host processing resources for other tasks.

- Support rate-based and Quantum Flow Control-based ABR services with algorithmic implementation of traffic shaping.

- Perform in ATM layer processing applications.

The MXT3010 has a high speed glueless interface to Fast Memory (SRAM) for storage of instructions and control structures, two high-performance data interfaces, and a UTOPIA Level 2 compliant interface.

The MXT3010 device, packaged in a 240-pin plastic quad flat package, is available in three speed grades, 100 MHz, 80 MHz and 66 MHz. Full electrical and mechanical details are provided in Section 3 of this manual.

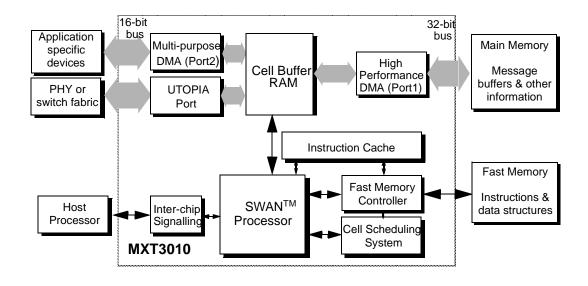

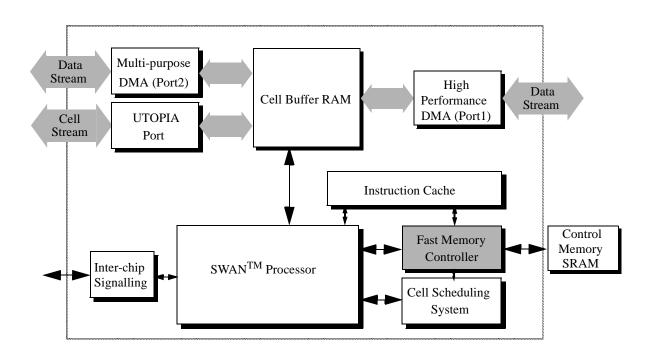

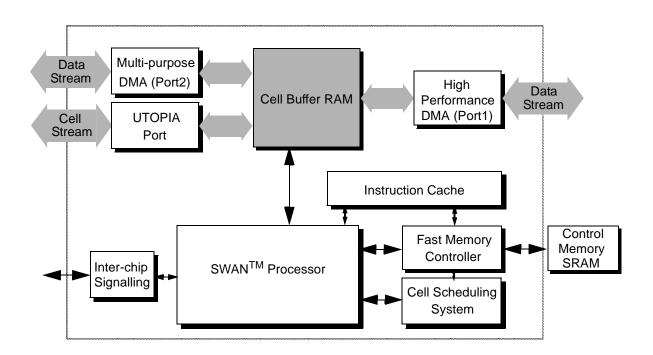

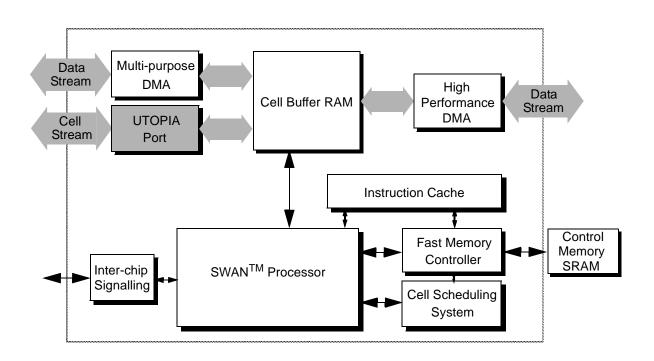

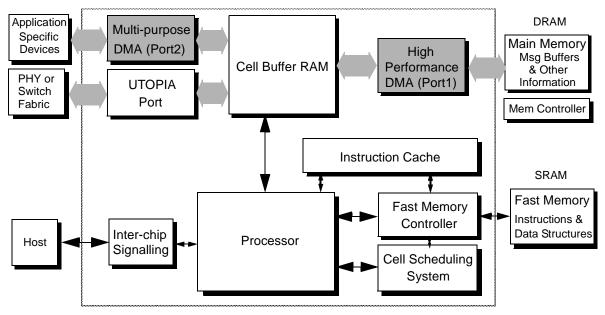

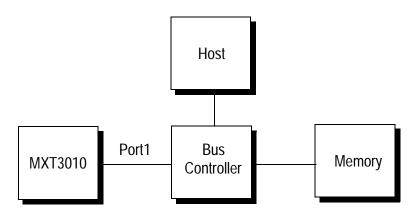

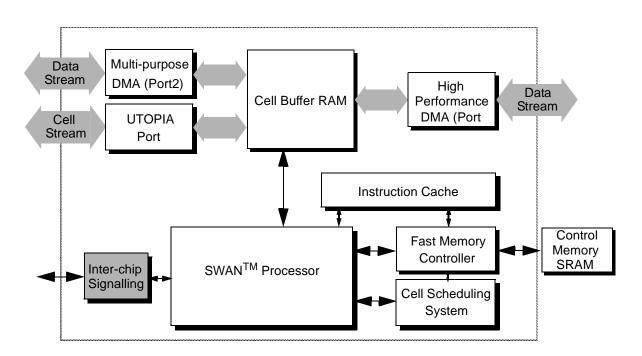

Figure 1 shows the MXT3010's internal subsystems and their relationship to devices found in a typical ATM application.

FIGURE 1. MXT3010 and surrounding system devices

### MXT3010 subsystems

While the SWAN processor is the heart of the MXT3010, the device also uses a series of subsystems or hardware agents created to handle ATM-specific tasks. Not only do these subsystems off-load many time-critical functions from the SWAN processor, but they also operate simultaneously with the SWAN processor and with each other, achieving a high degree of parallelism. The subsystems include:

- The Cell Scheduling System (CSS), a hardware-based traffic-shaping subsystem that allows concurrent shaping of dissimilar traffic types.

- The Fast Memory port that provides low latency access to external Channel Descriptors, program code, traffic shaping memory, and the look up tables used for Available Cell Rate calculations.

- The Cell Buffer RAM that buffers cells in both the transmit and receive directions.

|                                        | • The UTOPIA port that provides connection to an ATM net-<br>work via a UTOPIA Level 2 Multi-PHY interface.                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|----------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                                        | • The Port1 and Port2 interfaces: Port1 is a high performance 32-bit DMA host system interface and Port2 is a general purpose 16-bit DMA interface.                                                                                                                                                                                                                                                                                                                                                                                          |

| How the<br>subsystems work<br>together | The Cell Scheduling System, the Fast Memory port, the Cell<br>Buffer RAM, and the port interfaces utilize "dispatched"<br>instructions that operate outside of the CPU such that the SWAN<br>processor does not stall while the instruction is being executed.<br>Not only do dispatched instructions not interfere with the<br>SWAN, but those associated with different subsystems do not<br>interfere with each other, thus permitting simultaneous opera-<br>tion of several dispatched instructions within independent sub-<br>systems. |

|                                        | Although the Cell Scheduling System relies on the SWAN pro-                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

cessor for direction on required traffic patterns, the CSS manages the traffic-shaping functions of the ATM task. This CSS function provides all of the benefits of algorithmic traffic shaping without decreasing overall performance.

### What information is in this manual

This reference manual includes three sections: "Subsystems", "Register and Instruction Reference," and "Signal Descriptions and Electrical Characteristics." Also included are Appendix A "Acronyms," Appendix B "Device Initialization," and Appendix C "Quick Reference." The "Subsystems" section includes information on:

- The SWAN processor

- The Cell Scheduling System

- The Fast Memory port

- The Cell Buffer RAM

- The UTOPIA port

- The Port1 and Port2 interfaces

- Interchip communications

The "Register and Instruction Reference" section describes the software and hardware registers within the SWAN processor, and includes bit assignments and functions for all of the hardware registers. The "Register and Instruction Reference" section also describes instructions in functional groups and provides an alphabetical list of instructions within each group.

The "Signal Descriptions and Electrical Characteristics" section includes information on:

- Timing information

- Pin out and pin listing

- Signal descriptions

- Electrical parameters

- PLL details

- Thermal characteristics

- Mechanical information

7

Introduction

### CHAPTER 2 The SWAN Processor

The SWAN processor is used in network protocol processing applications. This chapter describes how the SWAN processor functions and provides functional descriptions of Arithmetic Logic Unit (ALU) and Branch instructions of the SWAN processor.

MXT3010 Reference Manual

Downloaded from **Elcodis.com** electronic components distributor

### The SWAN advantage

The SWAN processor was designed using Reduced Instruction Set Computer (RISC) and Complex Instruction Set Computer (CISC) design techniques. By combining the high pipeline speeds of a RISC processor with the instruction set power of a CISC processor, the SWAN processor attains the level of performance required to process a 622 Mb/s ATM cell stream.

#### SWAN's instructions and address spaces

In addition to utilizing an advanced RISC/CISC design, the SWAN processor employs highly efficient instructions and address spaces optimized for ATM applications.

#### Instruction features

- The ALU instructions include a memory update feature that can write the results of an ALU operation back into a memory location linked to the destination register.

- The ALU instructions include an integral branching capability that can perform a branch within the ALU instruction cycle if the results of the ALU operation meet selected criteria.

- The ALU instructions can perform modulo arithmetic operations, selectable from 1 bit to 16 bits (full ALU width).

- The Branch instructions can test the status of more than a dozen internal hardware points and two external pins.

- Branch instructions and ALU branching facilities can be programmed to eliminate the performance penalties normally exacted by branch failures in pipeline architectures.

- The Cell Scheduling System provides a powerful set of cell scheduling instructions.

- DMA operations are dispatched with a single instruction, and those for Port1 include flexible CRC capabilities.

- Load and Store instructions include indexing and byteswapping capability.

#### Address spaces

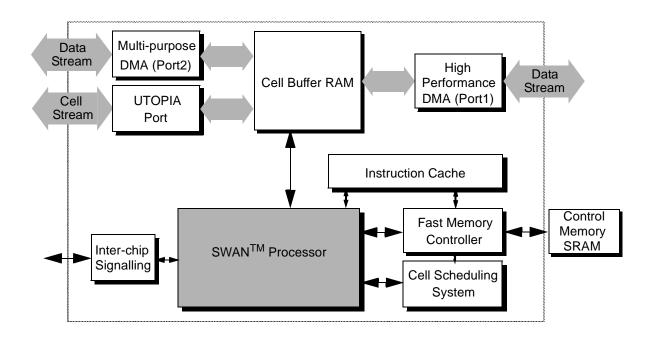

The architecture of the SWAN processor, a big-endian design, provides several independent address spaces. The processor accesses each space with instructions specifically designed for optimal performance. Figure 2 shows these address spaces and the instructions which access them. The circled numbers in the figure correspond to the explanatory paragraphs which follow.

FIGURE 2. SWAN processor address spaces and access instructions

1. Instruction Space - 128K Words

The SWAN processor executes instructions stored in Fast Memory. Fast Memory instructions are prefetched and optionally cached in a direct mapped on-chip cache to accelerate execution. A 17-bit Program Counter (allowing up to 128K instructions) identifies the current instruction. The processor executes instructions in a four stage instruction pipeline. The four stages -- Fetch, Decode, Execute and Store -- utilize scoreboarding and feedback to ensure proper operation, minimize stalls, and safeguard against illegal instruction sequences. The Decode stage of the pipeline is the current Program Counter value.

**2.** Control Memory Space - 1MByte (includes instruction space)

Fast Memory also provides a low latency store for control structures such as descriptors for the applications objects (VC descriptors, packet descriptors). The SWAN register set is tightly coupled to this control memory space through special purpose instructions -- Load Multiple from Fast Memory (LMFM) and Store Halfword to Fast Memory (SHFM). See "Load and Store Fast Memory Instructions" on page 293.

A powerful extension to ALU operations, linking, dynamically associates Fast Memory with the register set. These instructions virtually eliminate the context switching overhead that limits the performance of off-the-shelf processors in ATM systems. See "Automatic memory updates" on page 228.

3. On-Chip Cell Buffer RAM - 1Kbytes

The Cell Buffer RAM on the MXT3010 provides the SWAN processor with low latency access to cells in the ATM data flow and to control information from the host. A flexible Load/Store instruction paradigm provides an efficient memory-register manipulation mechanism. In addition to byte swapping, the extended load/store operations include an indexing method to facilitate control structure parsing. See "Load and Store Internal RAM Instructions" on page 313. This multi-port RAM is accessible to the UTOPIA, Port1 and Port2 DMA engine as well as the SWAN. Since it is truly multi-ported, it provides very low latency access to all arbiters. See "Direct Memory Access Instructions" on page 283.

On-Chip Cell Scheduling System Scoreboard RAM -2Kbytes

The Cell Scheduling System uses an on-chip RAM to accelerate cell scheduling operations. When not used by the CSS, this RAM is accessible to the SWAN processor through the Load/Store instructions and may be used as general purpose memory. See "The Cell Scheduling System" on page 27.

## Instruction execution

All SWAN instructions, except *dispatched instructions*, execute in a single clock cycle. Dispatched instructions include Load Multiple Fast Memory (LMFM), the cell scheduling instructions (PUSHC, POPC), the DMA instructions (DMA1, DMA2), and the load and store double instructions (LDD, STD). Dispatched instructions require more than one cycle to complete, but their execution occurs outside of the CPU such that the processor can accomplish other tasks while dispatched instructions execute.

Since the input clock is doubled in frequency by an on-chip PLL, the SWAN processor executes instructions at twice the frequency of the input clock. Like other high performance RISC processors, the SWAN utilizes a multi-stage pipeline. Delayed branching techniques ensure that Branch instructions also operate at an effective rate of one instruction per cycle by preventing pipeline delays.

MXT3010 Reference Manual

## Instruction space organization

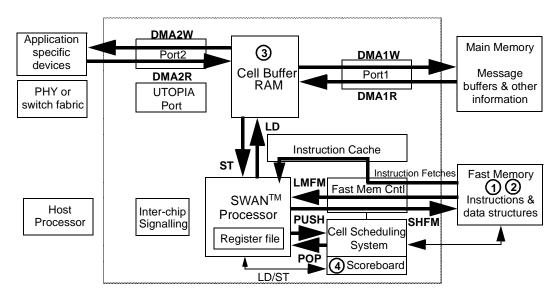

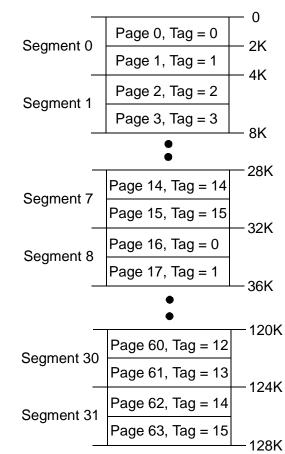

The SWAN supports an instruction space of 128K 32-bit instructions, which must be 4-byte aligned. The instruction space spans 32 Segments of 4K instructions each. Figure 3 shows the SWAN instruction space.

Notes: 1. The tag numbers wrap every 32K instructions

2. Page size is defined by the instruction cache size. Therefore, the MXT3010 EP has sixty-four 2K pages.

Segments are defined by the branching range of the instruction set. Since the Branch instruction has a 12 bit instruction address range, it may jump anywhere within a 4K segment. See "Target field" on page 20.

## Instruction cache

The internal Instruction Cache is 2048 instructions. The cache is a direct-mapped cache, with each 32-bit entry having an independent 4-bit tag. There are no separate *valid* bits for the cache entries. At device initialization time, all of the cache tags are written to 0xF. After the micro-boot routine downloads the firmware, the SWAN processor jumps to the specified starting address. The address must not map onto a cache tag of 0xF, as these fetches would cause incorrect cache hits. For simplicity's sake, consider the code space of 32K instructions as an executable space of 30K instructions and with a top 2K of instructions inaccessible for execution.

#### Cache organization and mapping

The line size of the MXT3010 cache (i.e. the amount of cache replaced on a cache miss) is 1 instruction. Each entry in the cache is therefore a single instruction. Each entry or instruction in the cache is 'tagged' with a 4 bit value that represents the cache page. As shown in Figure 3 on page 14, each 4K instruction segment contains two 2K cache pages.

The NC (No-Cache) bit in the Instruction Base Address register (R53) disables the cache. If this bit is set (one), the SWAN fetches all instructions from Fast Memory, and these instructions are not stored in the on-chip cache. Since the Fast Memory interface runs at 1/2 of the processor speed, it delivers an instruction every other cycle. Therefore, while running out of Fast Memory, the SWAN will stall, at a minimum, every other cycle.

While NC is clear (zero), the cache is enabled. When the SWAN fetches an instruction, the tag of the cache entry at the page offset of the instruction is compared with the tag of the instruction address. Figure 4 details the formation of the page offset and the instruction tag.

MXT3010 Reference Manual

#### FIGURE 4. Formation of the page offset and the instruction tag

Note: The Instruction Offset is a word offset, as opposed to a byte offset. The byte instruction address in Fast Memory will be ((Segment\_ID << 14)+ (Instruction Offset << 2))

If the instruction tag matches the corresponding cache tag, a cache hit has been achieved and the cache returns the instruction within a single cycle. The processor continues execution without stalling. However, if the tag does not match, a cache miss has occurred and the instruction must be fetched from Fast Memory. This will cause a processor stall as it awaits the instruction. Once Fast Memory returns the instruction, it is stored in the cache and the tag is updated. Because the cache line size is a single instruction, only a single instruction is replaced in the cache on a cache miss. Subsequent cache misses may replace other instructions in the cache. With an empty cache, such as when exiting the bootstrap, every instruction must be fetched from Fast Memory. Therefore, every other cycle will be a stall as the cache is cold filled.

The firmware designer controls which segments are cacheable. The NC bit in the Instruction Base Address register (R53) controls the cache and is typically modified by firmware when a code path jumps off the current segment. The firmware must ensure that for each cache tag value (0x0-0xE), only a single

cache page is made cacheable. Otherwise, stale cache entries prevent proper operation. The SWAN's bootstrap program preloads a tag of 0xF into all cache entries at initialization. It is recommended that no cacheable code be placed at a location with a tag of 0xF.

#### Using the Cache

Code that is always executed, referred to as the 'fast path', should be placed in cacheable space, preferably within a single cache page. Infrequently executed code (slow path) and performance insensitive code (for example, initialization code) should be located in non-cacheable segments. Maker's development tools provide code location features.

Many applications do not require more than 2K instructions. In this case, the application may be located on a single cache page. The entire page will be mapped into cache. Obviously, this will provide an optimal level of performance. However, it is not a requirement, as a program can easily jump to a new segment using the following instruction sequence:

LIMD R53 new-segment BI offset\_in\_new\_segment n

#### Instruction prefetch

The SWAN architecture is highly pipelined. The hardware may prefetch instructions from Fast Memory in anticipation of execution. These prefetches may be cached. However, changes in program flow (branches) may prevent the instructions from being executed. This behavior is expected and does not cause improper operation. Prefetches are mentioned here to alert the user that fetches from Fast Memory do not correlate exactly to the sequence of the Program Counter.

MXT3010 Reference Manual

#### Observing cached program flow

When the processor is executing out of cache, it does not need to access Fast Memory. However, if Fast Memory is not being used, the MXT3010 presents the program counter address on the Fast Memory address lines. This helps to monitor code execution from cache.

## SWAN processor instruction classes

The SWAN processor includes powerful 32-bit instructions in six functional areas or classes. Descriptions of each class of instruction are divided into two sections — one which describes the subsystem that uses that instruction and one which describes the bit utilization and format for each instruction. These descriptions appear in the chapters listed in Table 1.

| Functional Area                                    | Subsystem Description                          | Instruction Description                                      |

|----------------------------------------------------|------------------------------------------------|--------------------------------------------------------------|

| Arithmetic Logic<br>Unit Instructions              | "The SWAN Proces-<br>sor" (this chapter)       | "Arithmetic Logic Unit<br>Instructions" on page 223          |

| Branch Instructions                                | "The SWAN Proces-<br>sor" (this chapter)       | "Branch Instructions" on page 261                            |

| Cell Scheduling<br>Instructions                    | "The Cell Scheduling<br>System" on page 27     | "Cell Scheduling Instruc-<br>tions" on page 277              |

| Direct Memory<br>Access Instructions               | "The Port1 and Port2<br>Interfaces" on page 97 | "Direct Memory Access<br>Instructions" on page 283           |

| Load and Store Inter-<br>nal RAM Instruc-<br>tions | "The Cell Buffer<br>RAM" on page 59            | "Load and Store Internal<br>RAM Instructions" on<br>page 313 |

| Load and Store Fast<br>Memory Instructions         | "The Fast Memory<br>Interface" on page 47      | "Load and Store Fast<br>Memory Instructions" on<br>page 293  |

TABLE 1.

SWAN processor instruction classes

# Arithmetic Logic Unit (ALU) instructions

| Basic ALU<br>instructions    | The SWAN processor instruction set includes a complete suite<br>of arithmetic, logical, and shifting instructions implemented in a<br>high performance ALU. The format of a typical ALU instruction<br>is shown below:                                                                                                                                                                                                                                                                                                                           |

|------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                              | ADD (rsa, rsb) rd [MODx][abc][AE][UM]                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|                              | In the example shown, input data is stored in rsa and rsb, while<br>the result is delivered to register rd. The notations shown in<br>square brackets represent the special features that optimize the<br>SWAN ALU for ATM cell processing. These features, referred<br>to as instruction field options (IFOs), include the modulo field<br>(MODx), the ALU branch condition field (abc), the always exe-<br>cute bit (AE), and the update memory feature (UM). For more<br>information see "Arithmetic Logic Unit Instructions" on<br>page 223. |

|                              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |