## 50E D 4496204 0025643 602 **III**HIT3 HD61104,HD61104A (Dot Matrix Liquid Crystal Graphic **Display Column Driver**) 7-52-13-07

#### Description

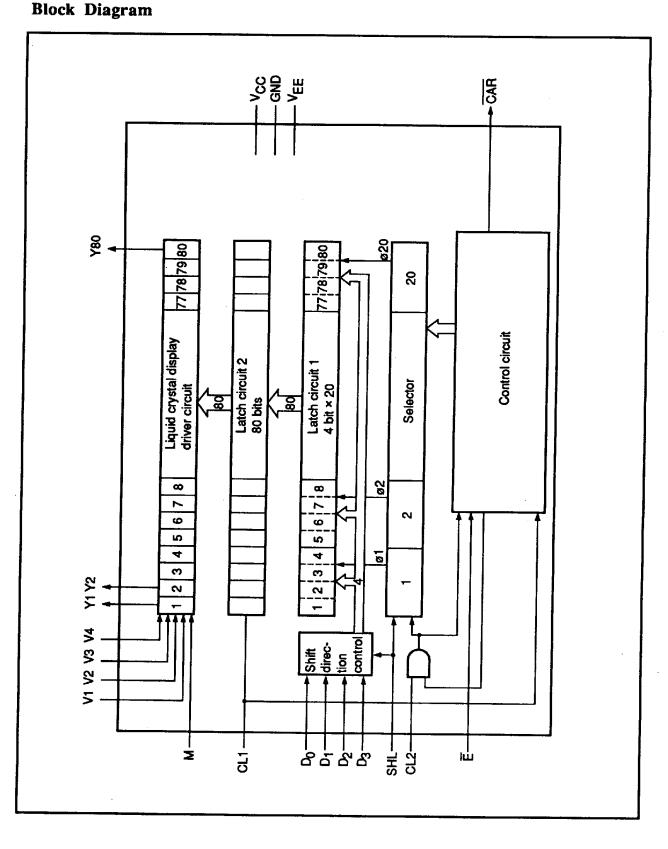

HD61104, HD61104A is a column (segment) driver for large-area dot matrix liquid crystal graphic display systems.

#### **Features**

- Display duty cycle: 1/64-1/200

- Internal liquid crystal display driver: 80 drivers

- 4-bit bus, bidirectional shift data transfer

- Cascade connection with enable format

- Data transfer rate: 3.5 MHz

- Power supply for logic circuit:  $5 V \pm 10\%$

- Power supply for LCD drive circuits : 10 to 26 V (HD61104) 10 to 28 V (HD61104A)

- Standby function

- CMOS process

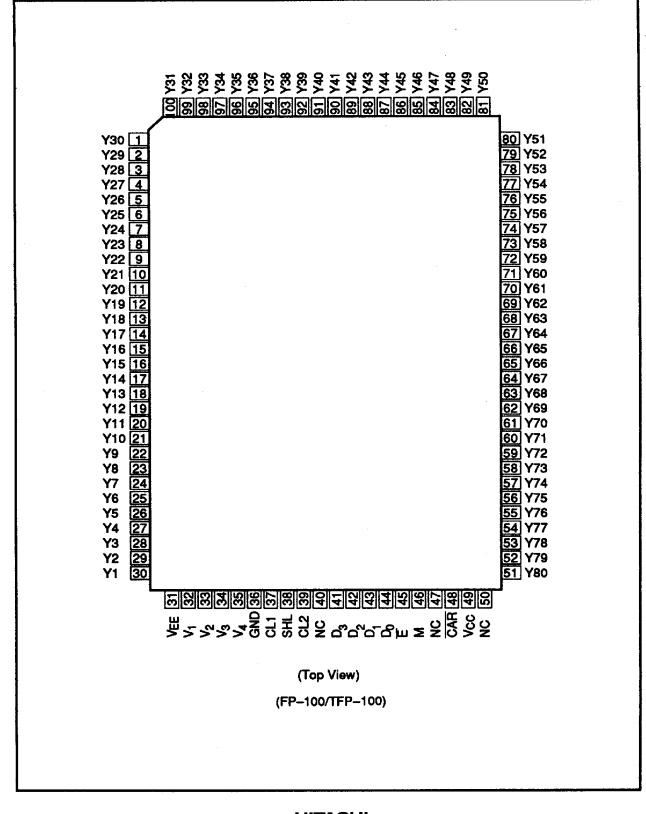

- 100-pin flat plastic package

### **Ordering Information**

| Type No.  | LCD Driving<br>Level (V) | Package                             |

|-----------|--------------------------|-------------------------------------|

| HD61104   | +10 to +26               | 100 pin plastic<br>QFP (FP-100)     |

| HD61104A  | +10 to +28V              | _                                   |

| HD61104TF | +10 to +28V              | 100 pin plastic T-<br>QFP (TFP-100) |

### Absolute Maximum Ratings

| ltem                 |          | Symbol           | Value                             | Unit | Note |

|----------------------|----------|------------------|-----------------------------------|------|------|

| Supply voltage (1)   |          | V <sub>CC</sub>  | -0.3 to +7.0                      | v    | 2    |

| Supply voltage (2)   | HD61104  | V <sub>EE</sub>  | $V_{CC} = 28.0$ to $V_{CC} = 0.3$ | v    |      |

|                      | HD61104A | V <sub>EE</sub>  | $V_{CC}$ – 28.5 to $V_{CC}$ + 0.3 |      |      |

| Terminal voltage (1) |          | V <sub>T1</sub>  | -0.3 to V <sub>CC</sub> + 0.3     | v    | 2, 3 |

| Terminal voltage (2) |          | V <sub>T2</sub>  | $V_{EE} = 0.3$ to $V_{CC} = 0.3$  | v    | 4    |

| Operating temperatur | 9        | T <sub>opr</sub> | -20 to +75                        | °C   |      |

| Storage temperature  |          | T <sub>stg</sub> | -55 to +125                       | °C   |      |

Notes: 1. LSIs may be permanently destroyed if used beyond the absolute maximum ratings. In ordinary operation, it is desirable to use them within the limits of electrical characteristics, because using them beyond these conditions may cause malfunction and poor reliability.

2. All voltage values are referenced to GND = 0 V.

- 3. Applies to input terminals, SHL, CL1, CL2, D0-D3, E, and M.

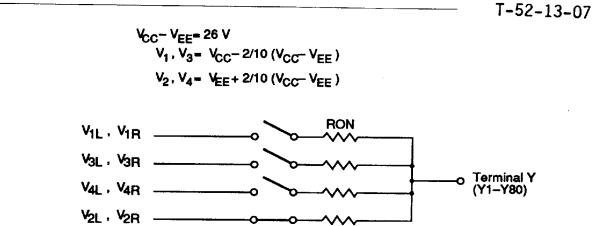

- 4. Applies to V1, V2, V3, and V4. Must maintain

$V_{CC} \ge V_1 \ge V_3 \ge V_4 \ge V_2 \ge V_{FE}$

Connect a protection resister of 15  $\Omega \pm$  10% to each terminal in series.

#### HITACHI

## 50E D 🗰 4496204 0025644 549 🗰 HIT3

#### **Pin Arrangement**

#### T-52-13-07

### HITACHI

Hitachi America, Ltd. • Hitachi Plaza • 2000 Sierra Point Pkwy. • Brisbane, CA 94005-1819 • (415) 589-8300 321

## HD61104, HD61104A

T-52-13-07

#### HITACHI

322 Hitachi America, Ltd. • Hitachi Plaza • 2000 Sierra Point Pkwy. • Brisbane, CA 94005-1819 • (415) 589-8300

#### **Electrical Characteristics**

T-52-13-07

**DC** Characteristics

$(V_{CC} = 5 V \pm 10\%, \text{ GND} = 0 V, V_{CC} - V_{EE} = 10 \text{ to } 26 V \text{ (HD61104)}, V_{CC} - V_{EE} = 10$ to 28 V (HD61104A), Ta = -20 to  $+75^{\circ}C$ )

| Item                    | Symbol           | Min                   | Тур | Max                 | Unit | <b>Test</b> Condition                           | Note   |

|-------------------------|------------------|-----------------------|-----|---------------------|------|-------------------------------------------------|--------|

| Input high voltage      | VIH              | $0.7 \times V_{CC}$   |     | V <sub>CC</sub>     | V    |                                                 | 1      |

| Input low voltage       | V <sub>IL</sub>  | 0                     |     | $0.3 \times V_{OC}$ | V    |                                                 | 1      |

| Output high voltage     | VOH              | V <sub>CC</sub> - 0.4 |     |                     | V    | l <sub>OH</sub> = – 400 µA                      | 2      |

| Output low voltage      | VOL              |                       |     | 0.4                 | V    | l <sub>OL</sub> = 400 μA                        | 2      |

| Driver on resistance    | RON              |                       | 102 | 7.5                 | kΩ   | V <sub>EE</sub> = -1 0V,Load<br>current =100 μA | 5      |

| Input leakage current   | l <sub>IL1</sub> | -1                    |     | 1                   | μA   | $V_{IN} = 0$ to $V_{CC}$                        | 1      |

| Input leakage current   | I <sub>IL2</sub> | -25                   |     | 25                  | μA   | $V_{IN} = V_{EE}$ to $V_{CC}$                   | 3      |

| Dissipation current (1) | IGND             |                       |     | 2.0                 | mA   |                                                 | 4      |

| Dissipation current (2) | leε              |                       |     | 0.2                 | mA   | HD61104                                         | 4      |

|                         |                  |                       |     | 0.4                 |      | HD61104A                                        |        |

| Dissipation current (3) | IST              |                       |     | 100                 | μA   |                                                 | 4<br>5 |

Notes: 1. Applies to CL1, CL2, SHL, E, M, and D<sub>0</sub>-D<sub>3</sub>.

- Applies to CAR. 2.

- 3. Applies to  $V_1$ ,  $V_2$ ,  $V_3$ , and  $V_4$ .

- 4. Specified when display data is transferred under following conditions: CL2 frequency fcp2 = 2.5 MHz (data transfer rate) fcp1 = 14.0 kHz (data latch frequency) CL1 frequency f<sub>M</sub> = 35 Hz (frame frequency/2) M frequency Display duty ratio 1/200 Specified when  $V_{IH} = V_{CC}$ ,  $V_{IL} = GND$  and no load on outputs. currents between V<sub>CC</sub> and GND

- IGND: currents between  $V_{CC}$  and  $V_{EE}$ l<sub>EE</sub>:

- 5. Currents between  $V_{CC}$  and GND at standby ( $\overline{E}$  input = high).

- 6. Resistance between terminal Y (one of Y1 to Y80) and terminal V (one of V1, V2, V3, and V4) when load current flows through one of the terminals Y1 to Y80. This value is specified under the following conditions:

#### HITACHI

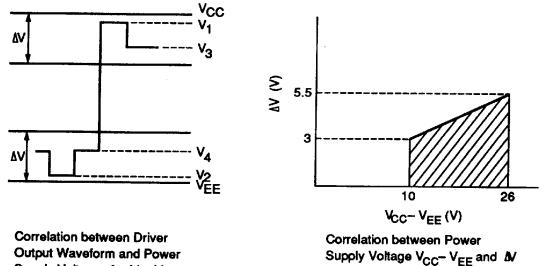

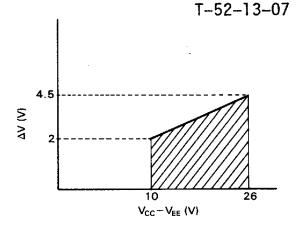

The following is a description of the range of power supply voltage for liquid crystal display drives. Apply positive voltage to V<sub>1</sub> and V<sub>3</sub>, and negative voltage to V<sub>2</sub> and V<sub>4</sub>, within the  $\Delta V$  range. This range allows stable impedance on driver output (R<sub>ON</sub>). Notice that  $\Delta V$  depends on power supply voltage  $V_{CC} - V_{EE}$ .

**Output Waveform and Power** Supply Voltages for Liquid **Crystal Display Drive**

#### HITACHI

324 Hitachi America, Ltd. • Hitachi Plaza • 2000 Sierra Point Pkwy. • Brisbane, CA 94005-1819 • (415) 589-8300

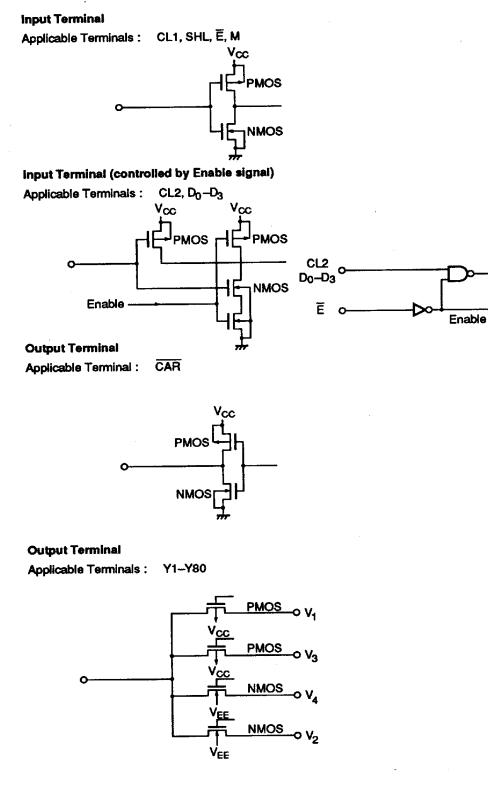

## **Terminal Configuration**

T-52-13-07

Hitachi America, Ltd. • Hitachi Plaza • 2000 Sierra Point Pkwy. • Brisbane, CA 94005-1819 • (415) 589-8300 325

Powered by ICminer.com Electronic-Library Service CopyRight 2003

0

## HD61104, HD61104A

T-52-13-07 -

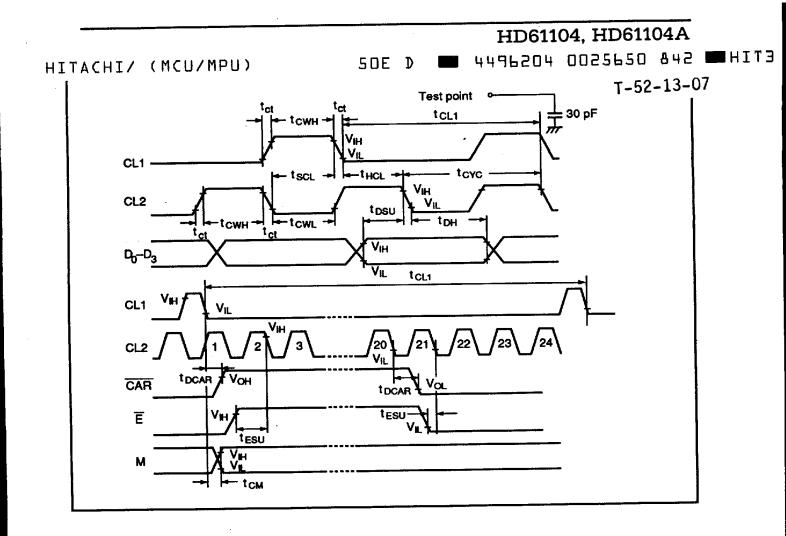

# AC Characteristics ( $V_{CC} = 5 V \pm 10\%$ , GND = 0 V, Ta = -20 to $\pm 75^{\circ}$ C)

| Item                    | Symbol            | Min                   | Тур      | Max      | Unit | Note     |

|-------------------------|-------------------|-----------------------|----------|----------|------|----------|

| Clock cycle time        | tcyc              | 285                   |          |          | ns   |          |

| Clock high level width  | tсwн              | 110                   |          |          | ns   |          |

| Clock low level width   | tcwL              | 110                   | _        | _        | ns   | ·· , ,   |

| Clock setup time        | tSCL              | 80                    |          | <u> </u> | ns   |          |

| Clock hold time         | tHCL              | 80                    | <u> </u> |          | ns   |          |

| Clock rise/fail time    | tст               |                       |          | 30       | ns   |          |

| Data setup time         | tDSU              | 80                    | _        |          | ns   |          |

| Data hold time          | <sup>t</sup> DH   | 80                    | <u> </u> |          | ns   |          |

| E setup time            | tesu              | 75                    |          | _        | ns   |          |

| Output delay time       | <sup>1</sup> DCAR | _                     |          | 180      | ns   | 1        |

| M phase difference time | tсм               | _                     |          | 300      | ns   | <u> </u> |

| CL1 cycle time          | t <sub>CL1</sub>  | t <sub>CYC</sub> × 10 |          |          | ns   |          |

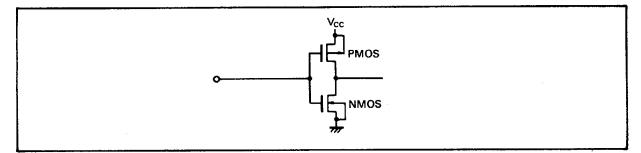

Note: 1. The following load circuit is connected for specification:

## HITACHI

#### HITACHI

|                                  | CU/MPU)                |     | 50           | ED                                    | 4496204 00                                                     | 25651 789                                      |

|----------------------------------|------------------------|-----|--------------|---------------------------------------|----------------------------------------------------------------|------------------------------------------------|

| Terminal<br>Name                 | Number of<br>Terminals | 1/0 | Connected to | Functions                             |                                                                | T-52-13-07                                     |

| V <sub>CC</sub>                  | 1                      |     | Power        | V <sub>CC</sub> – GND:                | Power supply for                                               | internal logic                                 |

| gnd<br>V <sub>ee</sub>           | 1                      |     | supply       | V <sub>CC</sub> -V <sub>EE</sub> :    | Power supply for                                               | LCD drive circuit                              |

| V <sub>1</sub>                   | 4                      |     | Power        | Power supply                          | for liquid crystal drive                                       | Э.                                             |

| V <sub>2</sub><br>V <sub>3</sub> |                        |     | supply       |                                       | ection level                                                   |                                                |

| <u>V4</u>                        |                        |     |              | V <sub>3</sub> , V <sub>4</sub> : nor | -selection level                                               |                                                |

| Y1-Y80                           | 80                     | 0   | LCD          | Liquid crystal                        | driver outputs.                                                |                                                |

|                                  |                        |     |              | Selects one of                        | the 4 levels, $V_1$ , $V_2$ ,                                  | V <sub>3</sub> , and V <sub>4</sub> . Relation |

|                                  |                        |     |              | among output                          | level, M, and display                                          | data (D) is as follow:                         |

|                                  |                        |     |              |                                       | M <u>1</u> 0                                                   |                                                |

|                                  |                        |     |              |                                       | D _ 1 0 1                                                      | 0                                              |

|                                  |                        |     |              | Dut <sub>l</sub><br>leve              | out  V <sub>1</sub>  V <sub>2</sub>  V <sub>3</sub>  <br>      | V4                                             |

| м                                | 1                      | I   | Controller   | Switch signal t<br>AC.                | o convert liquid cryst                                         | al drive waveform int                          |

| CL1                              | 1                      | 1   | Controller   | Latch clock of                        | display data (falling e                                        | dge triggered).                                |

|                                  |                        |     |              | Synchronized                          | with the fall of CL1, lic<br>conding to the display            | quid crystal driver                            |

| CL2                              | 1                      | 1   | Controller   | Shift clock of d                      | isplay data (D).                                               |                                                |

|                                  | ······                 |     |              | Falling edge tri                      | ggered.                                                        |                                                |

| D <sub>0</sub> D <sub>3</sub>    | 4                      | I.  | Controller   | Input of 4-bit di                     | splay data (D)                                                 | - <u> </u>                                     |

|                                  |                        |     |              | D                                     | Liquid Crystal<br>Driver Output                                | Liquid Crystal<br>Display                      |

|                                  |                        |     |              | 1<br>(High level)                     | Selection<br>level                                             | On                                             |

|                                  |                        |     |              | 0<br>(Low level)                      | Non-selection                                                  | Off                                            |

|                                  |                        |     |              | Truth table (Po                       | sitive logic)                                                  |                                                |

|                                  |                        |     |              | SHL                                   | Input data and latch                                           | n circuit 1                                    |

|                                  |                        |     |              | 0                                     | $\underline{D_3 \rightarrow 1 \rightarrow 5 \rightarrow 9} - $ | → 73 → 77                                      |

|                                  |                        |     |              |                                       | $D_2 \rightarrow 2 \rightarrow 6 \rightarrow 10 - $            |                                                |

|                                  |                        |     |              |                                       | $\underline{D_1 \rightarrow 3 \rightarrow 7 \rightarrow 11} -$ | - → 75 → 79                                    |

|                                  |                        |     |              |                                       |                                                                |                                                |

#### HITACHI

328 Hitachi America, Ltd. • Hitachi Plaza • 2000 Sierra Point Pkwy. • Brisbane, CA 94005-1819 • (415) 589-8300

| Terminal<br>Name | Number of<br>Terminals                | 1/0 | Connected<br>to           | Function              | T-52-13-07                                                                                                                            |  |  |  |

|------------------|---------------------------------------|-----|---------------------------|-----------------------|---------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

|                  | · · · · · · · · · · · · · · · · · · · |     |                           | Truth table           | (Positive logic) (cont)                                                                                                               |  |  |  |

|                  |                                       |     |                           | SHL                   | Input data and latch circuit 1                                                                                                        |  |  |  |

|                  |                                       |     |                           | 1                     | $D_3 \rightarrow 80 \rightarrow 76 \rightarrow 72 \rightarrow 8 \rightarrow 4$                                                        |  |  |  |

|                  |                                       |     |                           |                       | $D_2 \rightarrow 79 \rightarrow 75 \rightarrow 71 \rightarrow 7 \rightarrow 3$                                                        |  |  |  |

|                  |                                       |     |                           |                       | $D_1 \rightarrow 78 \rightarrow 74 \rightarrow 70 \rightarrow 6 \rightarrow 2$                                                        |  |  |  |

|                  |                                       |     |                           |                       | $D_0 \rightarrow 77 \rightarrow 73 \rightarrow 69 \rightarrow 5 \rightarrow 1$                                                        |  |  |  |

|                  |                                       |     |                           |                       | hen SHL = 0, the data that is input to D <sub>3</sub> is<br>each bit of the latch circuit 1 in order of $1 \rightarrow 5 \rightarrow$ |  |  |  |

| SHL              | 1                                     | 1   | V <sub>CC</sub> or GND    | Selects a s           | hift direction of display data.                                                                                                       |  |  |  |

| Ē                | 1                                     | I   | GND or the                | Enable inpu           | ut.                                                                                                                                   |  |  |  |

|                  | terminal CAR<br>of the<br>HD61104     |     |                           | The operati<br>level. | on stops at high level, and is enabled at low                                                                                         |  |  |  |

| CAR              | 1                                     | 0   | Input                     | Enable output.        |                                                                                                                                       |  |  |  |

|                  |                                       |     | terminal E of the HD61104 |                       |                                                                                                                                       |  |  |  |

| NC               | 3                                     |     |                           | Unused. No            | wire should be connected.                                                                                                             |  |  |  |

#### HITACHI

T-52-13-07

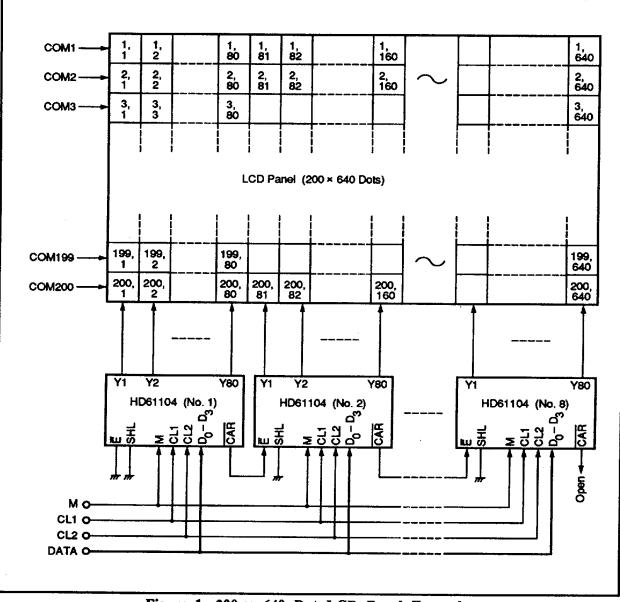

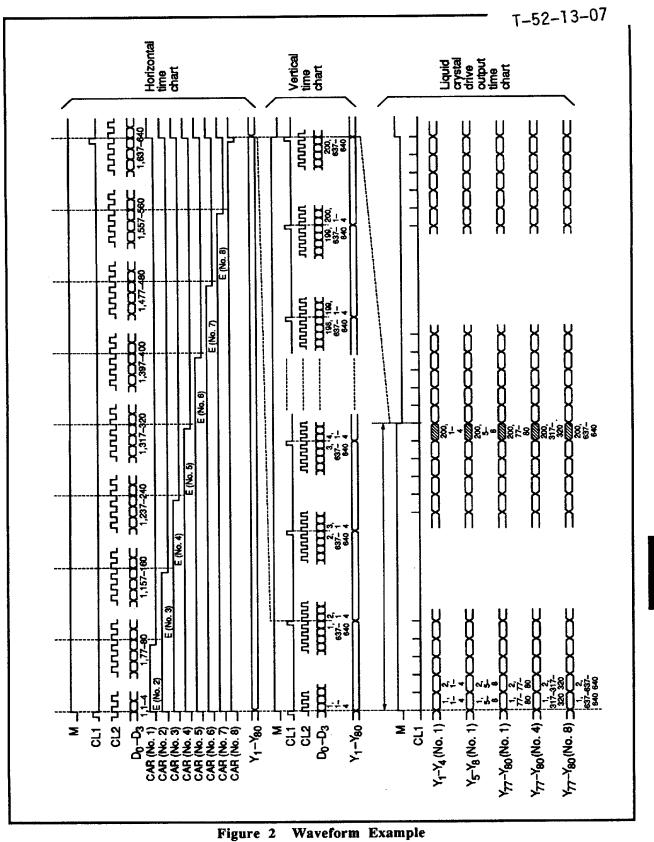

#### **Typical Application**

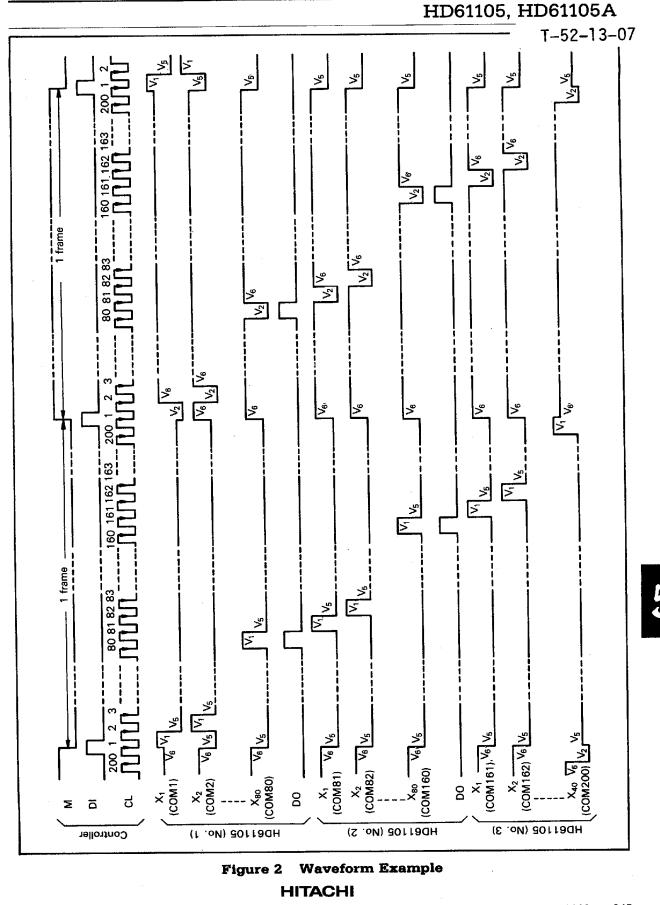

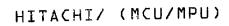

Figure 1 is an LCD panel with  $200 \times 640$  dots on which characters are displayed with 1/200 duty cycle dynamic drive.

Figure 1 200 × 640 Dot LCD Panel Example

Cascade eight HD61104s. Input data to the  $D_0$ — $D_3$  terminals of Nos. 1–8. Connect  $\overline{E}$  of No. 1 to GND. Connect no lines to  $\overline{CAR}$  of No. 8. Connect common signal terminals (COM1–COM200) to the common driver HD61105. (m,n) of LCD panel is the address corresponding to each dot. Figure 2 shows timing.

#### HITACHI

## 50E D ■ 4496204 0025654 498 ■HIT3 HD61104, HD61104A

### HITACHI

Hitachi America, Ltd. • Hitachi Plaza • 2000 Sierra Point Pkwy. • Brisbane, CA 94005-1819 • (415) 589-8300 331

# HD61105, HD61105A - T-52-13-07 (Dot Matrix Liquid Crystal Graphic Display Common Driver)

#### Description

The HD61105, HD61105A is a common signal driver for dot matrix liquid crystal graphic display systems. It provides 80 driver output lines and the impedance is low enough to drive a large screen.

As the HD61105, HD61105A is produced in a CMOS process, it is fit for use in portable battery drive equipments utilizing the liquid crystal display's low power consumption.

#### Features

- Dot matrix liquid crystal graphic display common driver with low impedance

- Internal liquid crystal display driver circuit: 80 circuits

- Display duty ratio factor: 1/64—1/200

- Internal 80-bit shift register

- Power supply for logic circuit:  $5 \pm 10\%$

- Power supply for LCD drive circuits: —10 to 26 V (HD61105)

- 100-pin plastic OFP (FP-100)

#### **Ordering Information**

| Type No.  | LCD Driving<br>Level (V) | Package                                           |

|-----------|--------------------------|---------------------------------------------------|

| HD61105   | 10 to 26                 | 100 pin                                           |

| HD61105A  | 10 to 28                 | <ul> <li>plastic</li> <li>QFP (FP-100)</li> </ul> |

| HD61105TF | 10 to 28                 | 100 pin<br>plastic<br>T-QFP (TFP-100)             |

#### **Pin Arrangement**

#### HITACHI

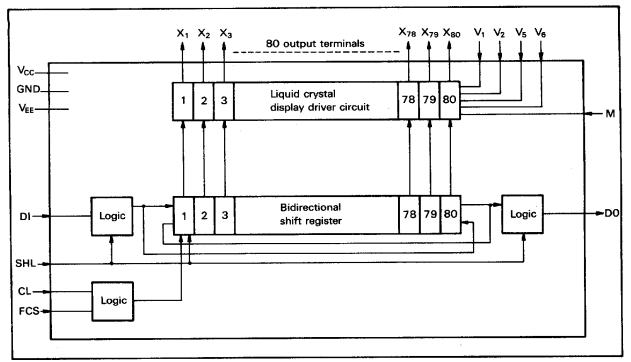

#### **Block Diagram**

T-52-13-07

#### Absolute maximum ratings

| ltem                  |          | Symbol          | Value                                    | Unit | Note |

|-----------------------|----------|-----------------|------------------------------------------|------|------|

| Supply voltage (1)    |          | Vcc             | - 0.3 to + 7.0                           | v    | 2    |

| Supply voltage (2)    | HD61105  | VEE             | $V_{CC} = 28.0 \text{ to } V_{CC} + 0.3$ | v    | 5    |

|                       | HD61105A |                 | $V_{CC} = 28.5$ to $V_{CC} + 0.3$        |      |      |

| Terminal voltage (1)  |          | V <sub>T1</sub> | - 0.3 to V <sub>CC</sub> +0.3            | V    | 2, 3 |

| Terminal voltage (2)  |          | V <sub>T2</sub> | $V_{EE} - 0.3$ to $V_{CC} + 0.3$         | V    | 4, 5 |

| Operating temperature |          | Торг            | - 20 to + 75                             | ٠C   |      |

| Storage temperature   |          | Tstg            | - 55 to + 125                            | °C   |      |

|                       |          |                 |                                          |      |      |

Notes: 1. LSIs may be permanently destroyed if used beyond the absolute maximum ratings. In ordinary operation, it is desirable to use them within the limits of electrical characteristics, because using them beyond these conditions may cause malfunction and poor reliability.

2. All voltage values are referred to GND = 0 V.

3. Applies to input terminals except  $V_1$ ,  $V_2$ ,  $V_5$ , and  $V_6$ .

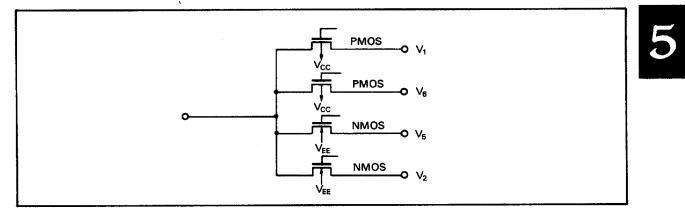

4. Applies to V<sub>1</sub>, V<sub>2</sub>, V<sub>5</sub>, and V<sub>6</sub>. 5. V<sub>CC</sub>  $\ge$  V<sub>1</sub>  $\ge$  V<sub>6</sub>  $\ge$  V<sub>5</sub>  $\ge$  V<sub>2</sub>  $\ge$  V<sub>EE</sub> must be maintained.

#### **HITACHI**

## HITACHI/ (MCU/MPU) HD61105, HD61105A

#### T-52-13-07

#### **Electrical Characteristics**

#### **DC Characteristics**

$(V_{\rm CC}=5~V~\pm~10\%,~GND=0~V,~V_{\rm CC}-V_{\rm EE}=10$  to 26 V (HD61105),  $V_{\rm CC}-V_{\rm EE}=10$  to 28 V (HD61105A),  $T_a=-20$  to  $+~75^{\circ}C)$

| Test item               |                  | Specifications      |     |                     |      |                                                           |      |

|-------------------------|------------------|---------------------|-----|---------------------|------|-----------------------------------------------------------|------|

|                         | Symbol           | Min                 | Тур | Max                 | Unit | Test Condition                                            | Note |

| Input high voltage      | Ин               | $0.7 \times V_{CC}$ |     | Vcc                 | v    |                                                           | 1    |

| Input low voltage       | VIL              | GND                 |     | $0.3 \times V_{CC}$ | v    |                                                           | 1    |

| Output high voltage     | Voн              | Vcc - 0.4           |     |                     | v    | $I_{OH} = -0.4mA$                                         | 2    |

| Output low voltage      | Vol              |                     | _   | 0.4                 | V    | $l_{OL} = 0.4 mA$                                         | 2    |

| Vi—Xj on resistance     | Ron              |                     | _   | 2.0                 | kΩ   | $V_{CC} - V_{EE} = 10 V$<br>Load current<br>± 150 $\mu$ A | 5    |

| Input leakage current   | I <sub>IL1</sub> | - 1.0               | _   | 1.0                 | μA   | $V_{IN} = 0$ to $V_{CC}$                                  | 3    |

| Input leakage current   | l <sub>1L2</sub> | - 25                | _   | 25                  | μA   | $V_{IN} = V_{EE}$ to $V_{CC}$                             | 4    |

| Clock frequency         | f <sub>CL</sub>  |                     | _   | 100                 | kHz  | Transfer clock CL                                         |      |

| Dissipation current (1) | I <sub>GG1</sub> | _                   | _   | 200                 | μA   | at 1/200 duty cycle operation                             | 6    |

| Dissipation current (2) | IEE              | _                   | _   | 100                 | μA   | at 1/200 duty cycle operation                             | 7    |

|                         |                  |                     |     |                     |      |                                                           |      |

Notes: 1. Applies to input terminals FCS, SHL, DI, M, and CL.

- 2. Applies to output terminal of DO.

- 3. Applies to the terminals NC, and the input terminals FCS, SHL, DI, M, and CL.

- 4. Applies to  $V_1$ ,  $V_2$ ,  $V_5$ , and  $V_6$ . No wire should be connected to  $X_1 X_{80}$ .

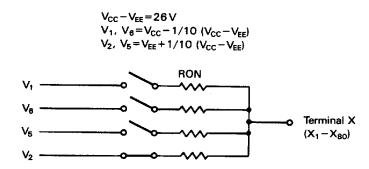

- 5. Resistance value between terminal X (one of  $X_1$  to  $X_{80}$ ) and terminal V (one of  $V_1$ ,  $V_2$ ,  $V_5$ , and  $V_6$ ) when load current is applied to one of terminals  $X_1$  to  $X_{80}$ . This value is specified under the following conditions:

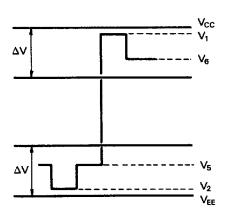

The following is a description of the range of power supply voltage for liquid crystal display drives. Apply positive voltage to  $V_1$  and  $V_5$ , and negative voltage to  $V_2$  and  $V_5$ , within

the  $\triangle V$  range. This range allows stable impedance on driver output (R<sub>ON</sub>). Notice that  $\triangle V$  depends on power supply voltage  $V_{CC}-V_{EE}$ .

#### HITACHI

Correlation between Driver Output Waveform and Power Supply Voltages for Liquid Crystal Display Drive

Correlation between Power Supply Voltage  $V_{CC} - V_{EE}$  and  $\triangle V$

- 6. The currents flowing through the GND terminal. Specified when display data is transferred under following conditions:

- CL frequency

M frequency

Display duty ratio

$V_{IH} = V_{CC}, V_{IL} = GND$

No load on outputs

- fc⊾

- fM

- 7. The currents flowing through the  $V_{EE}$  terminal in the conditions of note 6. No line should be connected to the V terminal.

#### HITACHI

335 Hitachi America, Ltd. • Hitachi Plaza • 2000 Sierra Point Pkwy. • Brisbane, CA 94005-1819 • (415) 589-8300

= 14kHz (data transfer rate) = 35 Hz (frame frequency/2) 1/200

## HD61105, HD61105A

T-52-13-07

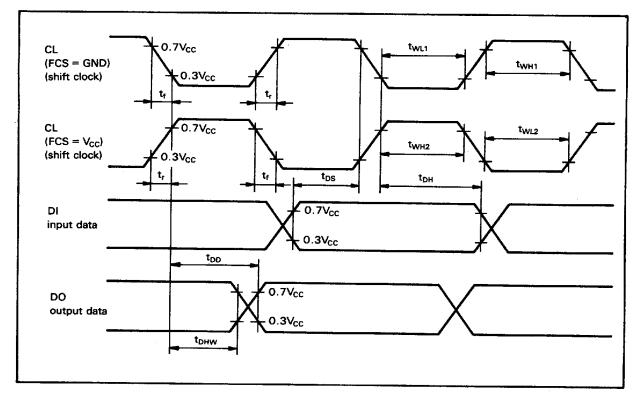

AC Characteristics ( $V_{cc} = 5 V \pm 10\%$ , GND = 0 V,  $T_{e} = -20 to + 75^{\circ}C$ )

| Item                                           | Symbol          | Min | Тур    | Max      | Unit | Note     |

|------------------------------------------------|-----------------|-----|--------|----------|------|----------|

| Clock low level width (FCS = GND)              | twL1            | 5.0 |        |          | μS   |          |

| Clock high level width (FCS = GND)             | twn1            | 125 | ****** |          | ns   |          |

| Clock low level width (FCS = V <sub>CC</sub> ) | twL2            | 125 |        | <u></u>  | ns   |          |

| Clock high level width (FCS = $V_{CC}$ )       | twn2            | 5.0 |        |          | μS   |          |

| Data setup time                                | t <sub>DS</sub> | 100 |        |          | ns   | ÷        |

| Data hold time                                 | t <sub>DH</sub> | 100 |        |          | лs   |          |

| Output delay time                              | t <sub>DD</sub> |     |        | 3.0      | μS   | 1        |

| Output hold time                               | torw            | 100 |        | <u> </u> | ns   |          |

| Clock rise time                                | tr              |     |        | 30       | ns   |          |

| Clock fall time                                | tr              |     |        | 30       | ns   | <u>-</u> |

Note: 1. The following load circuits are connected for specification:

Output terminal ....

30 pF (including jig capacitance)

#### HITACHI

市

T-52-13-07

#### **Terminal Configuration**

#### Input Terminal

Applicable Terminals: DI, CL, SHL, FCS, M

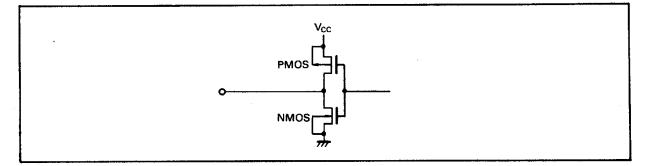

#### **Output Terminal**

Applicable Terminal: DO

#### **Output Terminal**

Applicable Terminals: X1-X80

#### HITACHI

Hitachi America, Ltd. • Hitachi Plaza • 2000 Sierra Point Pkwy. • Brisbane, CA 94005-1819 • (415) 589-8300 337

# HD61105, HD61105A

T-52-13-07

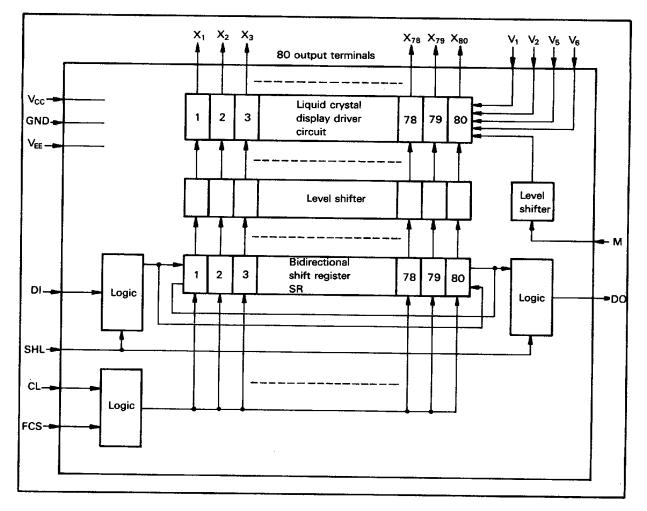

## **Block Diagram**

#### HITACHI

#### HD61105, HD61105A

T-52-13-07

(Positive Logic)

#### **Block Functions**

#### **Bidirectional Shift Register**

This is a 80-bit bidirectional register. The data from the DI terminal is shifted by the shift clock CL. The output terminal DO outputs the last shifted data. In case of serial cascade connection, terminal DO functions as the data input to the next LSI. Terminal SHL selects the data shift direction (table 1), and the terminal FCS selects the shift clock phase (table 2).

#### Liquid Crystal Display Driver Circuit

The combination of the data from the shift register with M signal allows one of the four liquid crystal display driver levels V1, V2, V5, and V6 to be transferred to the output terminals (table 3).

#### Table 1 SHL Truth Table

| SHL | Data Shift Direction                                                                              | <b>.</b> |

|-----|---------------------------------------------------------------------------------------------------|----------|

| 1   | $DI \rightarrow SR1 \rightarrow SR2 \rightarrow SR3$ $SR79 \rightarrow SR80 \rightarrow D0$       |          |

| 0   | $DI \rightarrow SR80 \rightarrow SR79 \rightarrow SR78 \cdots SR2 \rightarrow SR1 \rightarrow DO$ |          |

#### Table 2 FCS Truth Table

| FCS | Shift Clock Phase                 |  |

|-----|-----------------------------------|--|

| 0   | Shifted at the falling edge of CL |  |

| 1   | Shifted at the rising edge of CL  |  |

#### Table 3 M Truth Table

| Data from the Shift Register |   | (Positive Logic) |  |

|------------------------------|---|------------------|--|

|                              | M | Output level     |  |

| 0                            | 0 | V5               |  |

| 1                            | 0 | V1               |  |

| 0                            | 1 | V <sub>6</sub>   |  |

| 1                            | 1 | V2               |  |

#### HITACHI

Hitachi America, Ltd. • Hitachi Plaza • 2000 Sierra Point Pkwy. • Brisbane, CA 94005-1819 • (415) 589-8300 339

Powered by ICminer.com Electronic-Library Service CopyRight 2003

# 5

#### HD61105, HD61105A

#### **HD61105 Terminal Functions** Terminal Number of Connected Name Terminals 1/0 to **Functions** Vcc 1 Power Vcc - GND: Power supply for internal logic GND 1 supply Vcc - VEE: Power supply for LCD drive circuit 1 $V_{EE}$ V<sub>1</sub> 4 Liquid Power supply for liquid crystal drive V2 crystal V1, V2: selection level V5 drive V5, V6: non-selection level V6 level power supply FCS 1 1 Vcc or GND Selects shift clock phase. FCS = $V_{CC}$ Shift register operates at the rise of CL FCS = GND Shift register operates at the fall of CL M 1 E Controller Signal to convert LCD driver signal into AC CL 1 F Controller Shift clock $FCS = V_{CC}$ Shift register operates at the rise of CL FCS = GND Shift register operates at the fall of CL DI 1 L Controller or Shift register data input terminal DO of In case of cascade connection, the terminal DI is connected HD61105 to the terminal DO of the preceding LSI. DO 1 0 Open or Shift register data output terminal DI of In case of cascade connection, the terminal DO is con-HD61105 nected to the terminal DI of the next LSI. SHL 1 Ł Selects shift direction of bidirectional shift register. Vcc or GND SHL Shift Direction Common Scanning Direction Vcc $DI \rightarrow SR1 \rightarrow SR2 \rightarrow SR80$ $X_1 \rightarrow X_{80}$ GND DI → SR80 → SR79 → SR1 $X_{80} \rightarrow X_1$ 80 X1---X80 0 Liquid Liquid crystal display driver output Outputs one of the four liquid crystal display driver levels crystal display $V_1$ , $V_2$ , $V_5$ , and $V_6$ with the combination of the data from the shift register and M signal. Μ 0 Data Output level Data 1: Selection level Data 0: Non-selection level When SHL is V<sub>CC</sub>, X<sub>1</sub> corresponds to COM1 and X<sub>80</sub> corresponds to COM80. When SHL is GND, X<sub>80</sub> corresponds to COM1 and X<sub>1</sub> corresponds to COM80. NC 7 Open Unused. No line should be connected.

#### HITACHI

Hitachi America, Ltd. • Hitachi Plaza • 2000 Sierra Point Pkwy. • Brisbane, CA 94005-1819 • (415) 589-8300

#### T-52-13-07

HD61105, HD61105A T-52-13-07

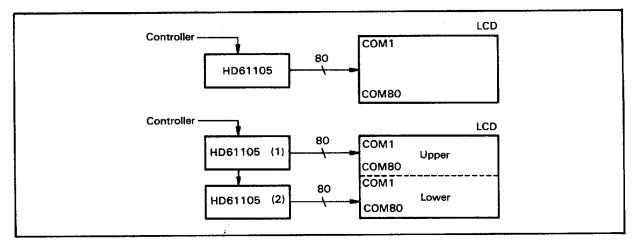

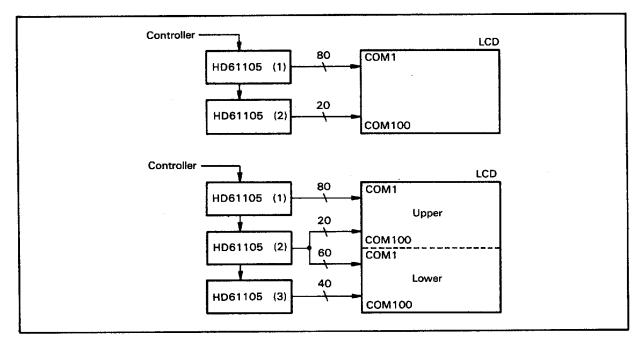

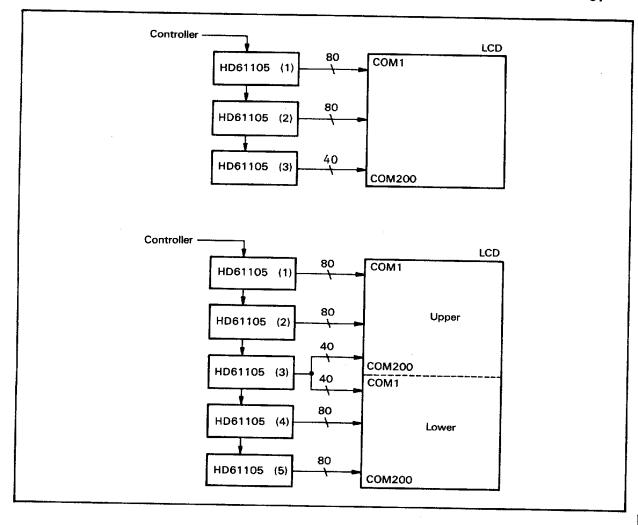

#### Outline of HD61105 System Configuration

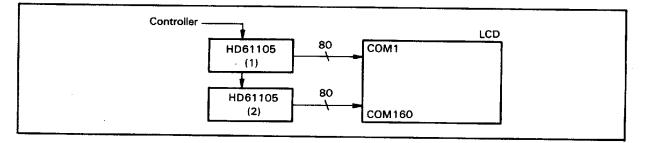

When display duty ratio of LCD is 1/80

When display duty ratio of LCD is 1/100

#### **HITACHI**

## HD61105, HD61105A

T-52-13-07

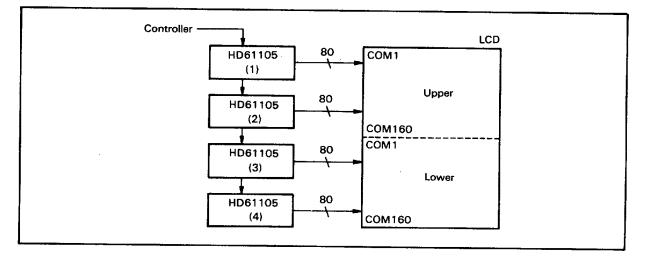

When display duty ratio of LCD is 1/160

#### When display duty ratio of LCD is 1/160

#### **HITACHI**

When display duty ratio of LCD is 1/200

T-52-13-07

5

#### HITACHI

## HD61105, HD61105A

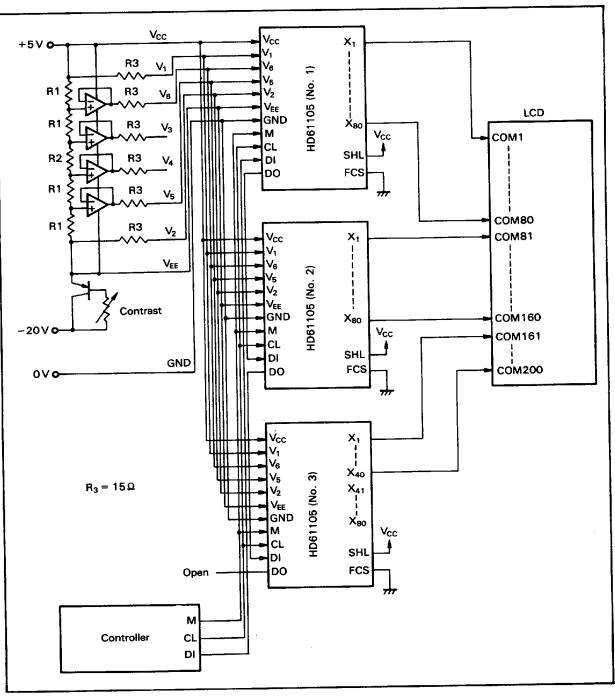

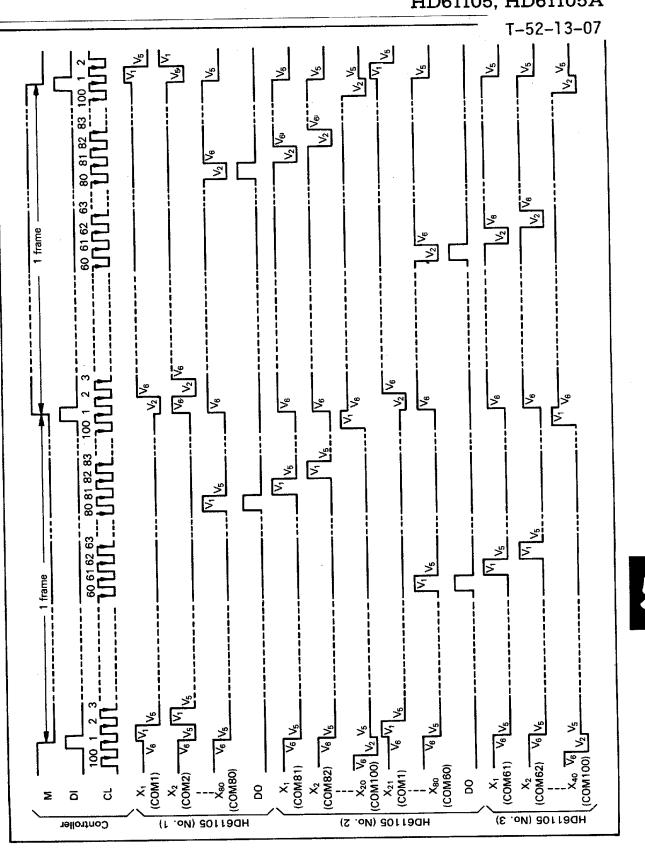

#### **Example of Connection**

1/200 duty ratio

Note: 1. The values of R1 and R2 vary with the LCD panel used. When bias factor is 1/15, the values of R1 and R2 should satisfy  $\frac{R1}{4R1+R2} = \frac{1}{15}$ For example, R1 = 3 K $\Omega$ , R2 = 33 K $\Omega$

Figure 1 Example of Connection (SHL =  $V_{CC}$ , FCS = GND)

#### HITACHI

Hitachi America, Ltd. • Hitachi Plaza • 2000 Sierra Point Pkwy. • Brisbane, CA 94005-1819 • (415) 589-8300

T-52-13-07

#### 50E D 4496204 0025669 9Ъ9 🎟 HIT3

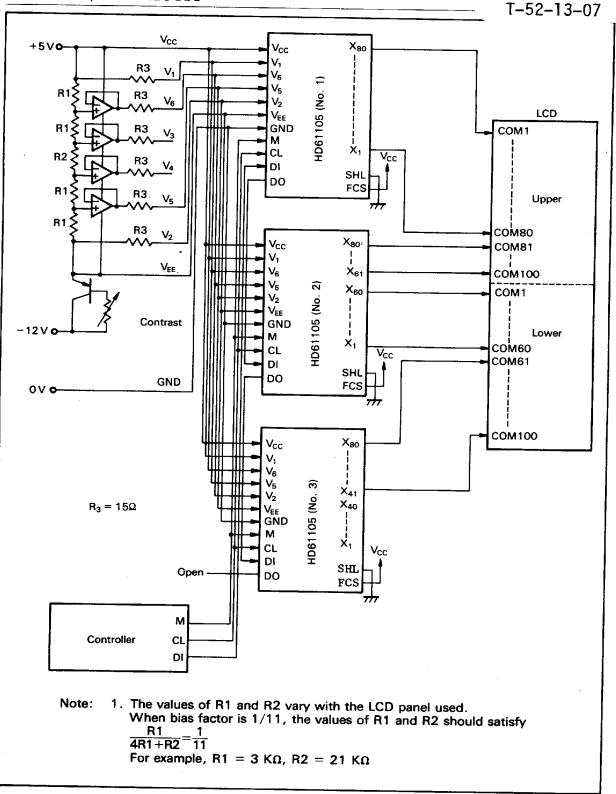

#### HD61105, HD61105A T-52-13-07 Vcc +5V √cc $X_1$ ٧, R3 $V_1$ ٧ĥ ÷ /5 R1≥ R3 HD61105 (No. V<sub>6</sub> V2 1111 LCD $V_{EE}$ GND **R1** COM1 RЗ V₃ м X80 CL Vcc R2 ₹ R3 V4 DI SHL DO FCS R1 Upper R3 V5 R1 сомво R3 $V_2$ X<sub>1</sub> COM81 Vcc ٧ı VEE X<sub>20</sub> COM100 ٧5 3 COM1 X<sub>21</sub> HD61105 (No. ٧, Contrast VEE GND - 12 М COM60 $X_{80}$ CL Vcc Lower COM61 Dł SHL DO GND FCS oν **COM100** Vcc X1 V1 Vв ŝ V5 X<sub>40</sub> HD61105 (No. $R3 = 15\Omega$ V2 $X_{41}$ Vee GND Μ X80 CL Vcc DI SHL Open DO FCS М Controller сι DI Note: 1. The values of R1 and R2 vary with the LCD panel used. When bias factor is 1/11, the values of R1 and R2 should satisfy **R1** $\overline{4R1+R2} = \overline{11}$ For example, $R1 = 3 K\Omega$ , $R2 = 21 K\Omega$

Figure 3 Example of Connection 1 (SHL =  $V_{CC}$ , FCS = GND)

#### **HITACHI**

Hitachi America, Ltd. • Hitachi Plaza • 2000 Sierra Point Pkwy. • Brisbane, CA 94005-1819 • (415) 589-8300 346

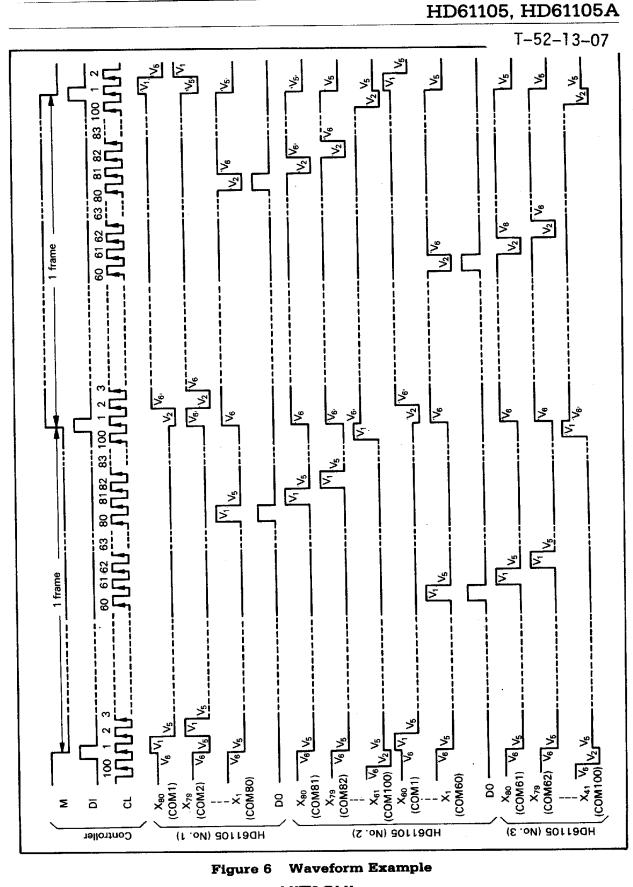

#### Waveform Example Figure 4

#### HITACHI

## HD61105, HD61105A

## 50E D 🖿 4496204 0025671 577 🖿 HITS

Figure 5 Example of Connection 2 (SHL = GND, FCS =  $V_{CC}$ )

#### HITACHI

# HITACHI

Hitachi America, Ltd. • Hitachi Plaza • 2000 Sierra Point Pkwy. • Brisbane, CA 94005-1819 • (415) 589-8300 349