# ES1869 AudioDrive® Solution Product Brief

## DESCRIPTION

The ES1869 AudioDrive® solution is a single, mixed-signal chip that adds 16-bit stereo sound and FM music synthesis to personal computers. It is compliant with the Microsoft® PC 97 and PC 98 specifications and WHQL audio requirements. The ES1869 possesses an embedded microcontroller, an OPL3™ superset ESFM™ music synthesizer, a 16-bit stereo wave ADC and DAC, 16-bit stereo music DAC, MPU-401 UART mode serial port, dual game port, full plug-and-play support, CD-ROM IDE interface, hardware master volume control, two serial port interfaces to external DSP and external wavetable music synthesizer, I²S zoom video interface, DMA control logic with FIFO, and ISA bus interface logic. There are three stereo inputs (typically line, CD audio, and auxiliary line) and a mono microphone input. This single chip can be designed into a motherboard, and add-on card, or integrated into other peripheral cards such as Fax/Modem, VGA, LAN, I/O, etc.

The ES1869 AudioDrive solution can record, compress, and play back voice, sound, and music with built-in mixer controls. It supports full-duplex operation for simultaneous record and playback, using two DMA channels. The ESFM synthesizer has extended capabilities within native mode operation, providing superior sound and power-down capabilities. It is a register-compatible superset to the OPL3 FM synthesizer.

The ES1869 *Audio*Drive solution supports the full ISA plug-and-play standard. It provides plug-and-play configuration for logical devices: audio, ESFM synthesizer, game port, MPU-401, IDE CD-ROM, MODEM, and an additional user-defined device. The MPU-401 serial port is for interfacing to an external MIDI device.

The integrated 3D audio effects processor uses **Spatializer**® VBX<sup>™</sup> technology, provided by Desper Products, Inc. a subsidiary of Spatializer Audio Laboratories, Inc. This processor expands the sound field emitted by two speakers to create a resonant 3D sound environment.

The speakerphone application can be implemented either by digital interface through the DSP serial port, or by analog interface through Mono-In and Mono-Out.

A DSP serial interface in the ES1869 allows an external DSP to take over ADC or DAC resources.

The ES1869 *Audio*Drive solution supports telegaming architecture with headsets and includes data paths for host-based acoustic echo cancellation processing.

Advanced power management features include suspend/resume from disk or host-independent self-timed power-down and automatic wake-up. The ES1869 is compliant with the ACPI standard.

The ES1869 is available in an industry-standard 100-pin plastic quad flat pack (PQFP) package.

# **FEATURES**

- Single, high-performance, mixed-signal, 16-bit stereo VLSI chip

- · High-quality, OPL3 superset ESFM music synthesizer

- IDE CD-ROM interface

- High-performance DMA supports demand transfer and F-type

## **Plug and Play Features**

- On-chip plug-and-play support for audio, joystick port, FM, MODEM, MPU-401, CD-ROM, and a user-defined I/O device

- Software address mapping with software chip select, plus 3

DMA and 6 IRQ selections for motherboard implementation

- Internal configuration data for audio plug-and-play support

- Serial interface for plug-and-play resource EEPROM

## **Record and Playback Features**

- Record, compress, and play back voice, sound, and music

- 16-bit stereo ADC and DAC

- Programmable independent sample rates from 4 kHz to 48.0 kHz for record and playback

- Full-duplex operation for simultaneous record and playback

- 2- and 3-button hardware volume control for up, down, and mute

#### **Inputs and Outputs**

- Stereo inputs for line-in, auxiliary A (CD audio), and auxiliary B, and a mono input for microphone

- MPU-401 (UART mode) interface for wavetable synthesizers and MIDI devices

- Integrated dual game port

- I<sup>2</sup>S zoom video port interface with a sample rate up to 48 kHz for MPEG audio

- Serial port interface to external DSP (e.g., AT&T, TI, API, and MWAVE)

- Separate mono input (MONO\_IN) and mono output (MONO\_OUT) for telegaming

#### Mixer Features

- 7-channel mixer with stereo inputs for line, CD audio, auxiliary line, music synthesizer, digital audio (wave files), and mono inputs for microphone and speakerphone

- Programmable 6-bit logarithmic master volume control

#### **Powe**

- Advanced power management with self-timed power-down, automatic wake-up, and suspend/resume to and from disk

- Supports 3.3V or 5.0V operation

# Compatibility

- Supports PC games and applications for SoundBlaster™ and SoundBlaster Pro™

- Meets PC 97/PC 98 and WHQL specifications

ESS Technology, Inc. SAM0113-030601

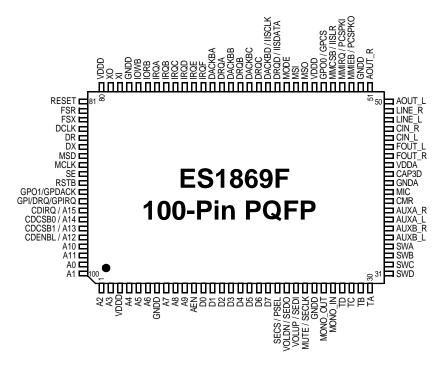

# **PINOUT**

Figure 1 shows the ES1869 printout diagram.

Figure 1 ES1869 Pinout Diagram

# **ES1869 PIN DESCRIPTIONS**

Table 1 lists the ES1869 pin descriptions.

Table 1 ES1869 Pin Descriptions

| Names    | Pin Numbers                | 1/0 | Descriptions                                                                                                        |  |

|----------|----------------------------|-----|---------------------------------------------------------------------------------------------------------------------|--|

| A[11:0]  | 1, 2, 6:4, 10:8,<br>97:100 | I   | Address inputs from the ISA bus.                                                                                    |  |

| VDDD     | 3, 57, 80                  | I   | Digital supply voltage (4.5 to 5.5V).                                                                               |  |

| GNDD     | 7, 24, 52, 77              | I   | Digital ground.                                                                                                     |  |

| AEN      | 11                         | I   | Active-low address enable from the ISA bus.                                                                         |  |

| D[7:0]   | 12:19                      | I/O | Bidirectional data bus. These pins have weak pull-up devices to prevent these inputs from floating when not driven. |  |

| PSEL     | 20                         | I   | This pin selects the PnP ROM device used:  0 Internal ROM  1 93LC66 – 512 x 8, 9 address bits.                      |  |

| SECS     |                            | I/O | Serial EEPROM CS. This is an input pin during RESET.                                                                |  |

| SEDO     | 21                         | I   | Data output pin of external PnP serial EEPROM.                                                                      |  |

| VOLDN    | 21                         | I   | Active-low volume decrease button input with internal pull-up.                                                      |  |

| SEDI     | 22                         | 0   | Data input pin to external PnP serial EEPROM.                                                                       |  |

| VOLUP    | 22                         | I   | Active-low volume increase button input with internal pull-up.                                                      |  |

| MUTE     | 23                         | I   | Active-low mute toggle button input with internal pull-up.                                                          |  |

| SECLK    | 23                         | 0   | External serial EEPROM clock output for PnP.                                                                        |  |

| MONO_OUT | 25                         | 0   | Mono output with source select and volume control (including mute). This pin can drive an external 5k ohm load.     |  |

| MONO_IN  | 26                         | I   | Mono input to mixer and ADC. Has an internal pull-up to CMR.                                                        |  |

2 SAM0113-030601 ESS Technology, Inc.

Table 1 ES1869 Pin Descriptions (Continued)

| Names               | Pin Numbers | I/O | Descriptions                                                                                                                                                                                                                                                                                                                                         |  |

|---------------------|-------------|-----|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| T(A-D)              | 27:30       | I/O | Joystick timer pins. These pins connect to the X-Y positioning variable resistors for the two joysticks.                                                                                                                                                                                                                                             |  |

| SW(A-D)             | 31:34       | I   | Active-low, joystick switch setting inputs. These SW pins have an internal pull-up resistor.                                                                                                                                                                                                                                                         |  |

| AUXB_L,<br>AUXB_R   | 35, 36      | I   | Auxiliary inputs, left and right. AUXB_L and AUXB_R have internal pull-up resistors to CMR.                                                                                                                                                                                                                                                          |  |

| AUXA_L,<br>AUXA_R   | 37, 38      | I   | Auxiliary inputs, left and right. AUXA_L and AUXA_R have internal pull-up resistors to CMR. Normally intended for connection to an internal or external CD-ROM analog output.                                                                                                                                                                        |  |

| CMR                 | 39          | 0   | Common mode reference voltage (2.25 $\pm$ 5%). This pin should be bypassed to analog ground with a 47- $\mu$ F electrolytic capacitor with a 0.1- $\mu$ F capacitor in parallel.                                                                                                                                                                     |  |

| MIC                 | 40          | I   | Microphone input. MIC has an internal pull-up resistor to CMR.                                                                                                                                                                                                                                                                                       |  |

| GNDA                | 41          | I   | Analog ground.                                                                                                                                                                                                                                                                                                                                       |  |

| CAP3D               | 42          | I   | Bypass capacitor to analog ground for 3D effect.                                                                                                                                                                                                                                                                                                     |  |

| VDDA                | 43          | I   | Analog supply voltage (4.5 to 5.5V). Should be greater than or equal to VDDD –0.3V.                                                                                                                                                                                                                                                                  |  |

| FOUT_L,<br>FOUT_R   | 44, 45 O    |     | Filter outputs, left and right. AC-coupled externally to CIN_L and CIN_R to remove DC offsets. These outputs have internal series resistors of about 5k ohms. Capacitors to analog ground on these pins can be used to create a low-pass filter pole that removes switching noise introduced by the switched-capacitor filters.                      |  |

| CIN_L, CIN_R        | 46, 47      | I   | Capacitive coupled inputs, left and right. These inputs have internal pull-up resistors to CMR of approximately 50k ohms.                                                                                                                                                                                                                            |  |

| LINE_L, LINE_R      | 48, 49      | I   | Line inputs, left and right. LINE_L and LINE_R have internal pull-up resistors to CMR.                                                                                                                                                                                                                                                               |  |

| AOUT_L,<br>AOUT_R   | 50, 51      | 0   | Line-level stereo outputs, left and right. Can drive a 10k ohm load.                                                                                                                                                                                                                                                                                 |  |

| MMIEB <sup>0</sup>  | <b>5</b> 2  | I   | Modem interrupt enable active-low input. Generated from the modem UART.                                                                                                                                                                                                                                                                              |  |

| PCSKPO <sup>1</sup> | - 52        | 0   | PC speaker analog output.                                                                                                                                                                                                                                                                                                                            |  |

| MMIRQ º             |             | I   | Modem interrupt request active-high input.                                                                                                                                                                                                                                                                                                           |  |

| PCSPKI 1            | 53          | I   | Normally low digital PC speaker input. This signal is converted to an analog signal with volume control and appears on analog output PCSPKO.                                                                                                                                                                                                         |  |

| IISLR <sup>1</sup>  | - 55        | I   | Left/right strobe for I2S interface. This pin has a pull-down.                                                                                                                                                                                                                                                                                       |  |

| MMCSB 0             | - 55        | 0   | Output from ES1869 for the modem CSB.                                                                                                                                                                                                                                                                                                                |  |

| GPCS                |             | 0   | If selected by the PnP logic, pin 56 becomes an active-high chip select for external general-purpose device.                                                                                                                                                                                                                                         |  |

| GPO0                | - 56        | 0   | The GPO0 output that is set low by external reset and thereafter programmable by system software for power management or other applications                                                                                                                                                                                                          |  |

| MSO                 | 58          | 0   | MIDI serial data output.                                                                                                                                                                                                                                                                                                                             |  |

| MSI                 | 59          | ı   | MIDI serial input. Schmitt trigger input with internal pull-up resistor.                                                                                                                                                                                                                                                                             |  |

| MODE                | 60          | I   | Mode function pin. Connect to either GNDD or VDDD to select the function of the groups of multiple function pins set apart below.                                                                                                                                                                                                                    |  |

| DRQD º              | - 61        | 0   | Tri-state output. Optional 16-bit DMA request for IDE interface.                                                                                                                                                                                                                                                                                     |  |

| IISDATA 1           | 01          | I   | Serial data for I <sup>2</sup> S interface. This pin has a pull-down.                                                                                                                                                                                                                                                                                |  |

| DACKBD <sup>0</sup> | - 62        | I   | Optional 16-bit DMA acknowledge for IDE interface.                                                                                                                                                                                                                                                                                                   |  |

| IISCLK <sup>1</sup> | 02          | I   | Serial shift clock for I <sup>2</sup> S interface. This pin has a pull-down.                                                                                                                                                                                                                                                                         |  |

| DRQ(A-C)            | 63, 65, 75  | 0   | Three (A,B,C) active-high DMA requests to the ISA bus. Unselected DRQ outputs are high impedance. When DMA is not active, the selected DRQ output has a pull-down device that holds the DRQ line inactive unless another device that shares the same DRQ line can source enough current to make the DRQ line active. DRQs are software configurable. |  |

| DACKB(A-C)          | 64, 66, 68  | I   | Three (A, B, C) active-low DMA acknowledge inputs.                                                                                                                                                                                                                                                                                                   |  |

| IRQ(A-F)            | 69:74       | 0   | Six (A, B, C, D, E, F) active-high interrupt requests to the ISA bus. Unselected IRQ outputs are high impedance. IRQs are software configurable.                                                                                                                                                                                                     |  |

| IORB                | 75          | I   | Active-low read strobe from the ISA bus.                                                                                                                                                                                                                                                                                                             |  |

| IOWB                | 76          | I   | Active-low write strobe from the ISA bus.                                                                                                                                                                                                                                                                                                            |  |

| XI                  | 78          | I   | Crystal oscillator input. Connect to external 14.318-MHz crystal or clock source with CMOS levels.                                                                                                                                                                                                                                                   |  |

| XO                  | 79          | 0   | Crystal oscillator output. Connect to external 14.318-MHz crystal.                                                                                                                                                                                                                                                                                   |  |

Table 1 ES1869 Pin Descriptions (Continued)

| Names                 | Pin Numbers        | I/O | Descriptions                                                                                                                                 |  |

|-----------------------|--------------------|-----|----------------------------------------------------------------------------------------------------------------------------------------------|--|

| RESET                 | 81                 | I   | Active-high reset from the ISA bus.                                                                                                          |  |

| FSR                   | 82                 | I   | Input with internal pull-down. Frame sync for receive data from external DSP. Programmable for active-high or active-low.                    |  |

| FSX                   | 83                 | ı   | Input with internal pull-down. Frame sync for transmit request from external DSP. Programmable for active-high or active-low.                |  |

| DCLK                  | 84                 | I   | Input with internal pull-down. Serial data clock from external DSP. Typically 2.048 MHz.                                                     |  |

| DR                    | 85                 | I   | Input with internal pull-down. Data receive pin from external DSP.                                                                           |  |

| DX                    | 86                 | 0   | Tri-state output. Data transmit to external DSP. High impedance when not transmitting.                                                       |  |

| MSD                   | 87                 | I   | Input with internal pull-down. Music serial data from external ES689/ES69x wavetable music synthesizer.                                      |  |

| MCLK                  | 88                 | I   | Input with internal pull-down. Music serial clock from external ES689/ES69x wavetable music synthesizer.                                     |  |

| SE                    | 89                 | ı   | Input with internal pull-down. Active-high to enable serial mode, (i.e., enables an external DSP to control analog resources of the ES1869). |  |

| RSTB                  | 90                 | 0   | Inverted RESET output.                                                                                                                       |  |

| GPDACK                |                    | 0   | Active-low DMA acknowledge output to general-purpose device that uses DMA.                                                                   |  |

| GPO1                  | 91                 | 0   | Output that is set high by external reset and thereafter programmable by system software for power management or other applications.         |  |

| GPDRQ                 |                    | I   | DMA request output from general-purpose device that uses DMA.                                                                                |  |

| GPI                   | 92                 | I   | General-purpose input option.                                                                                                                |  |

| GPIRQ                 |                    | ı   | Interrupt request output from the general-purpose device.                                                                                    |  |

| CDIRQ 0               | 93                 | I   | Interrupt request input from the IDE interface.                                                                                              |  |

| CDCSB0 0              | 94                 | 0   | Active-low IDE interface chip select #0.                                                                                                     |  |

| CDCSB1 º              | 95                 | 0   | Active-low IDE interface chip select #1.                                                                                                     |  |

| CDENBL 0              | 96                 | 0   | Active-low IDE data bus transceiver enable.                                                                                                  |  |

| A[15:12] <sup>1</sup> | 93:96              | I   | Address inputs from the ISA bus.                                                                                                             |  |

| 0: Pins enabled       | by MODE = 0 (pin 6 | 0). |                                                                                                                                              |  |

<sup>0:</sup> Pins enabled by MODE = 0 (pin 60).

## ORDERING INFORMATION

| Part Number | Description           | Package      |

|-------------|-----------------------|--------------|

| ES1869F     | AudioDrive Controller | 100-pin PQFP |

ESS Technology, Inc. 48401 Fremont Blvd. Fremont, CA 94538 Tel: (510) 492-1088 Fax: (510) 492-1898

No part of this publication may be reproduced, stored in a retrieval system, transmitted, or translated in any form or by any means, electronic, mechanical, manual, optical, or otherwise, without the prior written permission of ESS Technology, Inc.

$\hbox{ESS Technology, Inc. makes no representations or} \\ \text{warranties regarding the content of this document.}$

All specifications are subject to change without prior notice.

ESS Technology, Inc. assumes no responsibility for any errors contained herein.

(P) U.S. patents pending.

AudioDrive is a registered trademark of ESS Technology, Inc.

ESFM is a trademark of ESS Technology, Inc.

Certain audio features of this product manufactured under a license from Desper Products, Inc., <u>Spatializer</u> and the <u>circle-in-square device</u> are trademarks owned by Desper Products, Inc. U. S. Patent numbers #4,308,423. #4,355,203, #5,412,731.

All other trademarks are owned by their respective holders and are used for identification purposes only.

<sup>1:</sup> Pins enabled by MODE = 1 (pin 60).