# RC96V24DP

# Single Device Data/Fax Modem Data Pump

The Rockwell RC96V24DP is a low power, V.22 bis 2400 bps data/fax modem data pump in a single VLSI package. The RC2324DPL is identical to the RC96V24DP except fax modes are not provided. In this document, all references to the RC96V24DP also apply to the RC2324DPL except for the fax modes and as otherwise noted.

The modem operates over the public switched telephone network (PSTN), as well as on point-to-point leased lines.

The modem supports data modes meeting the requirements specified in CCITT recommendations V.22 bis, V.22, V.23, and V.21, as well as Bell 212A and Bell 103.

The modem supports fax modes meeting the requirements specified in CCITT V.29, V.27 ter, and V.21 channel 2 synchronous.

Internal HDLC support eliminates the need for an external serial input/output (SIO) device or comparable functions in the host controller in products incorporating error correction and T.30 protocols.

The modem includes two CMOS VLSI functions – a digital signal processor (DSP) and an integrated analog function (IA). The RC96V24DP integrates these functions into a single 68-pin plastic leaded chip carrier (PLCC).

Detailed hardware and software interface information is described in the Designer's Guide (Order No. 822).

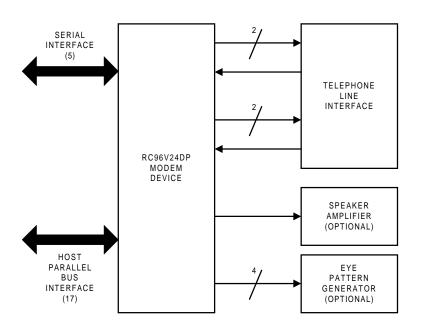

#### **Functional Block Diagram**

#### **Product Features**

- · Single CMOS VLSI device

- Low power requirements

- Single voltage: + 5 Vdc ±5%

- Operating: 300 mW (typical)

- Sleep: 15 mW (typical)

- 2-wire operation

- Full- duplex (FDX) for data modes

- Half-duplex (HDX) for fax modes

- · Data configurations:

- V.22 bis, V.22, V.23, V.21

- Bell 212A, Bell 103

- Fax configurations (RC96V24DP):

- V.29, V.27 ter, V.21 Channel 2

- Voice mode

- DTMF detection

- Receive dynamic range: -9 dBm to -43 dBm

- Transmit level: -10 dBm ±1 dB using internal hybrid circuit; attentuation selectable in 1 dB steps

- · Multi-mode data/fax detection support

- V.22 bis fallback/fall-forward -2400/1200 bps

- Serial data: synchronous and asynchronous

- Parallel data: synchronous (including HDLC) and asynchronous

- · Programmable ring detect

- Programmable dialer

- Programmable tone detect bandpass filters

- Adjustable speaker output to monitor received signal

- Diagnostics

- Host bus interface memory for configuration, control, and parallel data; 8086 microprocessor bus compatible

- 5-pin serial data interface; TTL compatible

- Equalization

- Adaptive equalizer in receiver

- Selectable and programmable fixed compromise equalizers in both receiver and transmitter

- Loopback configurations

- Local analog, local digital, and remote digital

- Answer and originate handshake in data modes

- Training sequences for fax modes

- Leased line operation

D96V24DSA

Rockwell Semiconductor Systems

#### **Ordering Information**

| Marketing Number | Manufacturing Number | Package      |

|------------------|----------------------|--------------|

| RC96V24DP        | R6653-12             | 68 pin PLCC  |

| RC96V24DP        | R6653-17             | 100 pin PQFP |

| RC9624DP         | R6653-16             | 68 pin PLCC  |

| RC9624DP         | R6653-21             | 100 pin PQFP |

| RC2324DPL        | R6653-15             | 68 pin PLCC  |

| RC2324DPL        | R6653-20             | 100 pin PQFP |

#### NOTE:

RC2324DPL does not support fax capabilities. RC9624DP does not support voice.

Copyright © 1998 Rockwell Semiconductor Systems, Inc. All rights reserved.

Print date: September 1998

Rockwell Semiconductor Systems, Inc. reserves the right to make changes to its products or specifications to improve performance, reliability, or manufacturability. Information furnished is believed to be accurate and reliable. However, no responsibility is assumed for its use; nor for any infringement of patents or other rights of third parties which may result from its use. No license is granted by its implication or otherwise under any patent or intellectual property rights of Rockwell Semiconductor Systems, Inc.

Rockwell Semiconductor Systems, Inc. products are not designed or intended for use in life support appliances, devices, or systems where malfunction of a Rockwell Semiconductor Systems, Inc. product can reasonably be expected to result in personal injury or death. Rockwell Semiconductor Systems, Inc. customers using or selling Rockwell Semiconductor Systems, Inc. products for use in such applications do so at their own risk and agree to fully indemnify Rockwell Semiconductor Systems, Inc. for any damages resulting from such improper use or sale.

Specifications are subject to change without notice.

PRINTED IN THE UNITED STATES OF AMERICA

# 1.0 Functional Description

#### 1.1 Overview

The Rockwell RC96V24DP is a low power, V.22 bis 2400 bps data/fax modem data pump in a single VLSI package.

## 1.2 Technical Specifications

#### 1.2.1 Configurations And Rates

The selectable modem configurations, along with the corresponding signaling (baud) rates and data rates, are listed in Table 1-1 (CONF bits).

Note: Bit names refer to control or status bits in DSP interface memory which are set or reset by the host processor (see Table 3-1 and Table 3-2).

### 1.2.2 Data Encoding

The data encoding conforms to CCITT recommendations V.29, V.27 ter, V.22 bis, V.22, V.23, or V.21, or to Bell 212A or 103, depending on the selected configuration.

#### 1.2.3 Tone Generation

**Answer Tone:** A CCITT ( $2100 \pm 15 \text{ Hz}$ ) or Bell ( $2225 \pm 10 \text{ Hz}$ ) answer tone can be generated.

**Guard Tone:** A1800  $\pm$ 20 Hz guard tone can be generated (enabled by the GTE bit).

**DTMF Tones:** Dual tone multi-frequency (DTMF) tones can be generated with a frequency accuracy of  $\pm 1.5\%$ .

**User Defined Tones:** A user-defined single or dual tone can be generated from 200 Hz to 3000 Hz  $\pm$ 5 Hz.

#### 1.2.4 Tone Detection

**Answer Tone and Call Progress Tones:** Tones can be detected as follows:

- Call progress frequency range:  $340 \pm 5$  Hz to  $640 \pm 5$ Hz

- Answer tone frequency ranges: CCITT ( $2100 \pm 15$ Hz), Bell ( $2225 \pm 10$  Hz), or Bell FSK originate tone ( $1270 \pm 10$  Hz)

- Detection range: -9 dBm to -43 dBm

- Default detection threshold: -43 dBm

- Response time:  $75 \pm 2$  ms

- The passband and tone detect threshold can be changed in DSP RAM.

#### V.23 and V21 Tones: Tones can be detected as follows:

- V.23 forward channel mark:  $1300 \pm 10 \text{ Hz}$

- V.23 backward channel mark:  $390 \pm 10 \text{ Hz}$

- V.21 high band mark (1650  $\pm$ 10 Hz) or low band mark (980  $\pm$ 10 Hz)

- Detection range: -9 dBm to -43 dBm

- Default detection threshold: -43 dBm

- Response time:  $25 \pm 2$  ms

The passbands and tone detect thresholds can also be changed in the DSP RAM.

#### 1.2.4.1 DTMF Detection

The modem can detect a valid DTMF tone pair (indicated by DTDET) and load a corresponding hexadecimal code into the modem interface memory (DTDIG).

#### 1.2.4.2 Equalizers

Equalization functions are incorporated that improve performance when operating over low quality lines.

**Automatic Adaptive Equalizer.** An automatic adaptive equalizer in the receiver compensates for transmission line amplitude and group delay distortion. Updating of the taps can be enabled or disabled (EQFZ bit). The equalizer taps can also be reset (EQRES bit).

**Fixed Compromise Equalizers.** Fixed compromise equalizers are provided in the transmitter and receiver. The equalizers are programmable in DSP RAM.

#### 1.2.4.3 Transmit Level

The transmitter output level is  $-10 \text{ dBm} \pm 1 \text{ dB}$  using the internal hybrid circuit. The attentuation is selectable from 0 dBm to -15 dBm in 1 dB steps (TLVL bits).

#### 1.2.4.4 Transmit Timing

Transmitter timing is selectable between internal ( $\pm 0.01\%$ ), external, or loopback (TXCLK bits). When external clock is selected, the external clock rate must equal the desired data rate  $\pm 0.01\%$  with a duty cycle of  $50 \pm 20\%$ .

#### 1.2.4.5 Scrambler/ Descrambler

The modem incorporates a self-synchronizing scrambler/descrambler satisfying the applicable CCITT or Bell requirement. The scrambler and descrambler can be enabled or disabled (SDIS and DDIS bits, respectively).

1.2 Technical Specifications

**1.2.4.6 Receive Level** The receiver satisfies performance requirements for a received line signal from

-9 dBm to -43 dBm. The default RLSD turn-on and RLSD turn-off thresholds are

-43 dBm and -48 dBm, respectively. The RLSD threshold levels are

programmable in DSP RAM.

**1.2.4.7 Receiver Timing** The modem can track a frequency error up to  $\pm 0.03\%$  in the associated transmit

timing source.

**1.2.4.8 Carrier** The modem can track a frequency offset up to  $\pm 7$  Hz in the received carrier with

**Recovery** less than a 0.2 dB degradation in bit error rate (BER).

#### Table 1-1. Configurations, Signaling and Data Rates

|                                          |                   |                      | er Carrier<br>(Hz) ±0.01% | Data Rate<br>(bps)                    | Baud                 | Bits Per    | Constella-<br>tion | Sample<br>Rate       |

|------------------------------------------|-------------------|----------------------|---------------------------|---------------------------------------|----------------------|-------------|--------------------|----------------------|

| Configuration                            | Modulation        | Answer <sup>2</sup>  | Originate <sup>2</sup>    | ±0.01%                                | (Symbols/<br>Sec)    | Symbol      | Points             | (Samples/<br>Sec)    |

| Data Modes                               |                   |                      |                           |                                       |                      |             |                    |                      |

| V.22 bis                                 | QAM               | 2400                 | 1200                      | 2400 <sup>3</sup>                     | 600                  | 4           | 16                 | 7200                 |

| V.22                                     | DPSK              | 2400<br>2400         | 1200<br>1200              | 1200 <sup>3</sup><br>600 <sup>3</sup> | 600<br>600           | 2<br>1      | 4<br>2             | 7200<br>7200         |

| Bell 212A                                | DPSK              | 2400                 | 1200                      | 1200 <sup>3</sup>                     | 600                  | 2           | 4                  | 7200                 |

| Bell 103                                 | FSK               | 2225 M<br>2025 S     | 1270 M<br>1070 S          | 0-300 <sup>4</sup>                    | 0-300 <sup>4</sup>   | 1           | 1                  | 7200                 |

| V.21                                     | FSK               | 1650 M<br>1850 S     | 980 M<br>1180 S           | 0-300 <sup>4</sup>                    | 0-300 <sup>4</sup>   | 1           | 1                  | 7500                 |

| V.23 Forward<br>Channel <sup>5</sup>     | FSK               | 1300 M<br>2100 S     | 1300 M<br>2100 S          | 1200                                  | 1200                 | 1           | 1                  | 9600 <sup>5</sup>    |

| V.23 Backward<br>Channel <sup>5</sup>    | FSK               | 390 M<br>450 S       | 390 M<br>450 S            | 75                                    | 75                   | 1           | 1                  | 7200                 |

| Fax Modes <sup>6</sup>                   |                   |                      |                           |                                       |                      |             |                    |                      |

| V.29                                     | QAM<br>QAM<br>QAM | 1700<br>1700<br>1700 | 1700<br>1700<br>1700      | 9600<br>7200<br>4800                  | 2400<br>2400<br>2400 | 4<br>3<br>2 | 16<br>8<br>4       | 9600<br>7200<br>9600 |

| V.27 ter                                 | DPSK<br>DPSK      | 1800<br>1800         | 1800<br>1800              | 4800<br>2400                          | 1600<br>1200         | 3<br>2      | 8<br>4             | 9600<br>9600         |

| V.21 channel 2                           | FSK               | 1650 M<br>1850 S     | 1650 M<br>1850 S          | 300                                   | 300                  | 1           | 1                  | 9600                 |

| Dial/Call<br>Progress Mode               |                   |                      |                           |                                       | 600                  |             |                    | 7200                 |

| Tone Generator/<br>Tone Detector<br>Mode |                   |                      |                           |                                       | 600                  |             |                    | 7200                 |

Notes:

(1) Modulation legend: QAM Quadrature Amplitude Modulation

DPSK Differential Phase Shift Keying

FSK Frequency Shift Keying

- (2) M indicates a mark condition; S indicates a space condition.

- (3) Synchronous accuracy = ±0.01%; asynchronous accuracy = -2.5% to +1.0% (+2.3% if extended overspeed is selected).

- (4) Value is upper limit for serial (e.g. 0-300).

- (5) RC2324DPL only.

- (6) RC96V24DP only.

- (7) 9600 samples per sec in V.23 FDX Tx75/Rx1200; 7200 samples per second in V.23 FDX Tx1200/Rx75.

Table 1-2. Dial Digits/Tone Pairs

| Dial Digit | Tone 1 (Hz) | Tone 2 (Hz) |

|------------|-------------|-------------|

| 1          | 697         | 1209        |

|            |             |             |

| 2          | 697         | 1336        |

|            |             |             |

| 3          | 697         | 1447        |

|            |             |             |

| 4          | 770         | 1209        |

| 5          | 770         | 1336        |

| 6          | 770         | 1447        |

| 7          | 852         | 1209        |

| 8          | 852         | 1336        |

| 9          | 852         | 1477        |

| 0          | 941         | 1336        |

| *          | 941         | 1209        |

| #          | 941         | 1477        |

| Spare B    | 967         | 1633        |

#### 1.2.4.9 RTS-CTS Turn-On and Turn-Off Sequences

RTS ON to CTS ON and RTS OFF to CTS OFF response times are listed in Table 1-3.

In V.21, the transmitter turns off within 10 ms after RTS goes OFF. For V.29, the turn-off sequence consists of approximately 5 ms of remaining data and scrambled ones followed by a 50 ms period of no transmitted energy.

For V.27 ter, the turn-off sequence consists of approximately 7 ms of remaining data and scrambled ones at 1200 baud or approximately 7.5 ms of data and scrambled ones at 1600 baud followed by a 20 ms period of no transmitted energy.

#### 1.2.5 Serial or Parallel Interface

The TPDM bit selects serial or parallel interface.

Serial Interface. The five hardware lines (RXD, TXD, TDCLK, RDCLK, and XTCLK) are supported by four control and status bits in the interface memory (CTS, DSR, RTS, and RLSD).

Parallel Interface. A 8086-compatible parallel microprocessor bus is supported.

#### 1.2.6 Voice Mode

**Transmit Voice.** Transmit voice samples can be sent to the modern digital-to-analog converter (DAC) from the host through the transmit data buffer.

**Receive Voice.** Received voice samples from the modem analog-to-digital converter (ADC) can be read by the host from the receive data buffer.

### 1.2.7 Asynchronous Conversion

Asynchronous mode is selected by the ASYNC bit. The asynchronous character format is 1 start bit, 5 to 8 data bits (WDSZ bits), an optional parity bit (PARSL and PEN bits), and 1 or 2 stop bits (STB bit). Valid character size, including all bits, is 7, 8, 9, 10 or 11 bits per character.

Table 1-3. RTS-CTS Response Times

| Configuration                                                         | Turn On<br>Time | Turn Off<br>Time |

|-----------------------------------------------------------------------|-----------------|------------------|

| Data Modes                                                            |                 |                  |

| V.22 bis, V.22, and Bell 212A (CC bit = 0)                            | ≤ 2 ms          | ≤ 2 ms           |

| V.22 bis, V.22, and Bell 212A (CC bit =1)                             | 270 ms          | ≤ 2 ms           |

| V.21 and Bell 103                                                     | 2-5 ms          | 10 ms            |

| V.23 (RC96V24DP and RC2324DPL only)                                   | 11 ms           | ≤ 2 ms           |

| Fax Modes (RC96V24DP only)<br>Echo Protector Tone Disabled (NV25 = 1) |                 |                  |

| V.29 (All speeds)                                                     | 253 ms          | ≤ 2 ms           |

| V.27 4800                                                             | 898 ms          | ≤ 2 ms           |

| V.27 2400                                                             | 1133 ms         | 9 ms             |

| V.21                                                                  | 20 ms           | 4 ms             |

| Echo Protector Tone Enabled (NV25 = 0)                                |                 |                  |

| V.29 (All speeds)                                                     | 253 ms          | ≤ 2 ms           |

| V.27 4800                                                             | 1103 ms         | ≤ 2 ms           |

| V.27 2400                                                             | 1338 ms         | 9 ms             |

| V.21                                                                  | 3095 ms         | 4 ms             |

**Signalling Rate Range.** Signalling rate range is selectable by the EXOS bit:

- Basic range: +1% to -2.5%

- Extended overspeed range: +2.3% to -2.5%

Break. Break is handled as described in V.22 bis.

1.2 Technical Specifications

#### 1.2.7.1 Power and Environmental Requirements

The power requirements are specified in Table 1-4. The environmental specifications are listed in Table 1-5.

Table 1-4. Modem Power Requirements

| Voltage  | Mode      | Current (Typ)<br>@ 25°C | Current (Max)<br>@ 0°C |

|----------|-----------|-------------------------|------------------------|

| 5VDC ±5% | Operating | 60 mA                   | 90 mA                  |

|          | Sleep     | 3 mA                    | 4.5 mA                 |

Note: Input voltage ripple  $\leq$  0.1 volts peak-to-peak. The amplitude of any frequency between 20 kHz and 150 kHz must be less than 500 microvolts peak.

Table 1-5. Modem Environmental Specifications

| Parameter         | Specification                                                                      |

|-------------------|------------------------------------------------------------------------------------|

| Temperature       |                                                                                    |

| Operating         | 0° C to 70° C (32° F to 158° F)                                                    |

| Storage           | -40° C to 80° C (-40° F to 176° F)                                                 |

| Relative Humidity | Up to 90% noncondensing, or a wet bulb temperature up to 35° C, whichever is less. |

| Altitude          | -200 feet to +10,000 feet                                                          |

1.2 Technical Specifications

# 2.0 Hardware Interface

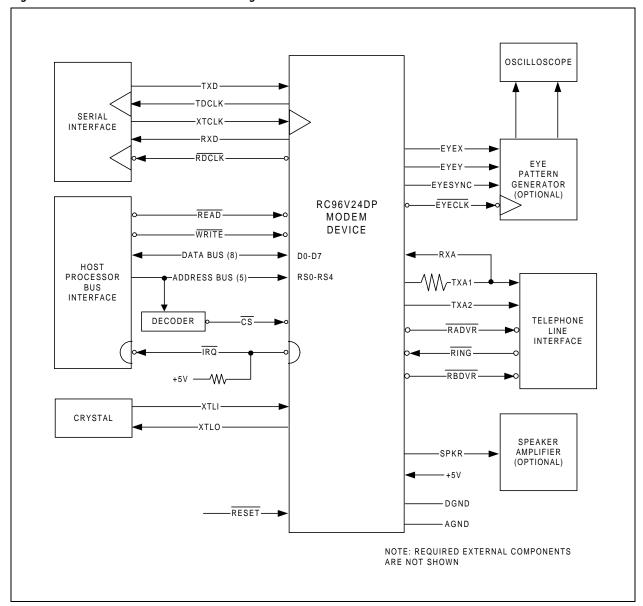

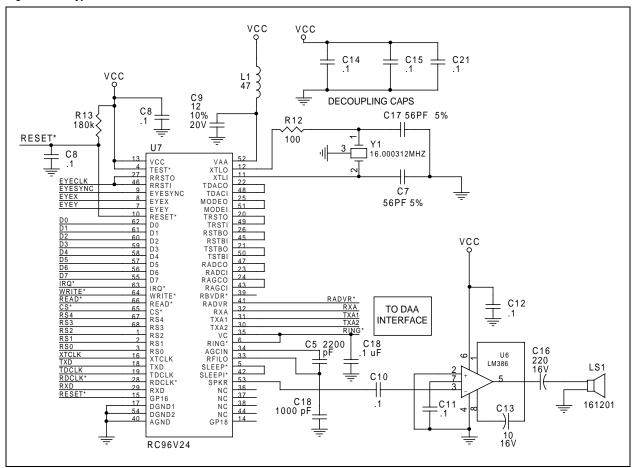

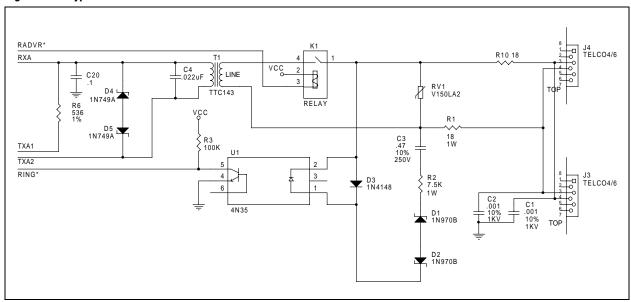

The modem functional hardware interface signals are shown in Figure 2-1. In this diagram, any point that is active low is represented by a small circle at the signal point.

Edge triggered inputs are denoted by a small triangle (e.g., TDCLK). Open-Collector (open-source or open-drain) outputs are denoted by a small half-circle (e.g.,  $\overline{IRQ}$ ). Active low signals are overscored (e.g.,  $\overline{POR}$ ).

A dock intended to activate logic on its rising edge (low-to-high transition) is called active low (e.g.,  $\overline{RDCLK}$ ), while a clock Intended to activate logic on its falling edge (high-to-low transition) is called active high (e.g., TDCLK). When a clock input is associated with a small circle, the input activates on a falling edge. If no circle is shown, the input activates on a rising edge.

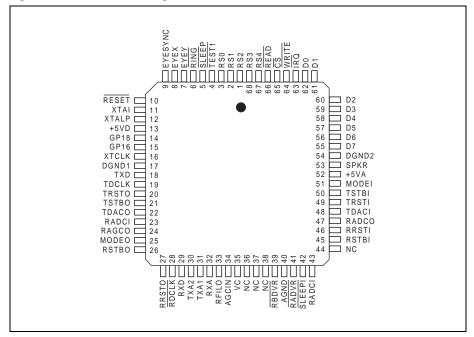

The modem pin assignments are shown in Figure 2-2. The pin assignments are listed by pin number in Table 2-1.

The hardware interface signal functions are summarized by major interface in Table 2-2.

The digital and analog interface characteristics are defined in Table 2-3 and Table 2-4, respectively.

2.0 Hardware Interface RC96V24DP

Figure 2-1. RC9623DP Functional Interface Signals

RC96V24DP 2.0 Hardware Interface

Single Device Data/Modem Data Pump

Figure 2-2. RC9623DP Pin Signals

Table 2-1. RC9623DP Modem Device Pin Signals

| Pin Number | Signal Name | I/O Type |

|------------|-------------|----------|

| 1          | RS2         | IA       |

| 2          | RS1         | IA       |

| 3          | RS0         | IA       |

| 4          | TEST1       |          |

| 5          | SLEEP       | OA       |

| 6          | RING        |          |

| 7          | EYEY        | ОВ       |

| 8          | EYEX        | ОВ       |

| 9          | EYESYNC     | ОВ       |

| 10         | RESET       | ID       |

| 11         | XTLI        | IE       |

| 12         | XTL0        | ОВ       |

| 13         | +5VD        |          |

| 14         | GP18        | OA       |

Rockwell D96V24DSA 2-3

2.0 Hardware Interface RC96V24DP

Table 2-1. RC9623DP Modem Device Pin Signals (Continued)

| Pin Number | Signal Name | I/O Type |

|------------|-------------|----------|

| 15         | GP16        | OA       |

| 16         | XTCLK       | IA       |

| 17         | DGND1       |          |

| 18         | TXD         | IA       |

| 19         | TDCLK       | OA       |

| 20         | TRST0       | MI       |

| 21         | TSTB0       | MI       |

| 22         | TDACO       | MI       |

| 23         | RADCI       | MI       |

| 24         | RAGCO       | MI       |

| 25         | MODEO       | MI       |

| 26         | RSTB0       | MI       |

| 27         | RRST0       | MI       |

| 28         | RDCLK       | OA       |

| 29         | RXD         | OA       |

| 30         | TXA2        | O(DD)    |

| 31         | TXA1        | O(DD)    |

| 32         | RXA         | I(DA)    |

| 33         | RFIL0       | MI       |

| 34         | AGCIN       | MI       |

| 35         | VC          |          |

| 36         | NC          |          |

| 37         | NC          |          |

| 38         | NC          |          |

| 39         | RBDVR       | OD       |

| 40         | AGND        |          |

| 41         | RADRV       | OD       |

| 42         | SLEEP1      | IA       |

| 43         | RAGCI       | MI       |

| 44         | NC          |          |

| 45         | RSTBI       | MI       |

RC96V24DP 2.0 Hardware Interface

Single Device Data/Modem Data Pump

Table 2-1. RC9623DP Modem Device Pin Signals (Continued)

| Pin Number | Signal Name | I/O Type |

|------------|-------------|----------|

| 46         | RRSTI       | MI       |

| 47         | RADCO       | MI       |

| 48         | TDACI       | MI       |

| 49         | TRSTI       | MI       |

| 50         | TSTBI       | MI       |

| 51         | MODE1       | MI       |

| 52         | +5VA        |          |

| 53         | SPKR        | O(0F)    |

| 54         | DGND2       |          |

| 55         | D7          | IA/OB    |

| 56         | D6          | IA/OB    |

| 57         | D5          | IA/OB    |

| 58         | D4          | IA/OB    |

| 59         | D3          | IA/OB    |

| 60         | D2          | IA/OB    |

| 61         | D1          | IA/OB    |

| 62         | D0          | IA/OB    |

| 63         | ĪRQ         | 00       |

| 64         | WRITE       | IA       |

| 65         | CS          | IA       |

| 66         | READ        | IA       |

| 67         | RS4         | IA       |

| 68         | RS3         | IA       |

#### Notes:

- (1) MI = Modem Interconnection

- (2) NC = No connection (may have internal connection; leave pin disconnected (open).

- (3) I/O types are described in Table 2-3 (digital signals) and Table 2-4 (analog signals).

Table 2-2. Hardware Interface Signal Definitions

2.0 Hardware Interface

| Label | I/O Type | Signal/Definition                                                                                                                                                                                                                                                                                                                                    |

|-------|----------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|       |          | OVERHEAD SIGNALS                                                                                                                                                                                                                                                                                                                                     |

| XTLI  | IEOB     | Crystal/Clock In and Crystal Out. The DSP must be connected to an external crystal circuit consisting of a 24.00014 MHz crystal and two capacitors. Alternatively, XTLI, may be driven with a buffered clock (e.g., square wave generator) or a sine wave oscillator.                                                                                |

| RESET | ID       | <b>Reset.</b> The active low RESET input resets the internal modem logic. Upon transition of RESET from low-to-high, the DSP interface memory bits are set to the default values.                                                                                                                                                                    |

| +5VD  | PWR      | +5V Digital Supply. +5V ±5% is required.                                                                                                                                                                                                                                                                                                             |

| +5VA  | PWR      | +5V Analog Supply. +5V ±5% is required.                                                                                                                                                                                                                                                                                                              |

| DGND  | GND      | Digital Ground.                                                                                                                                                                                                                                                                                                                                      |

| DGND  | GND      | Analog Ground.                                                                                                                                                                                                                                                                                                                                       |

|       |          | SERIAL INTERFACE                                                                                                                                                                                                                                                                                                                                     |

|       |          | Five TTL-level hardware interface circuits implement a CCITT V.24-compatible serial data interface with control signals provided through the DSP interface memory.                                                                                                                                                                                   |

| RDCLK | OA       | <b>Receive Data Clock.</b> In synchronous mode, the modem outputs a Receive Data Clock $(\overline{RDCLK})$ in the form of 50 ±1% duty cycle square wave. The low-to-high transitions of this output coincide with the center of received data bits.                                                                                                 |

| TDCLK | OA       | <b>Transmit Data Clock.</b> In synchronous mode, the modem outputs a Transmit Data Clock (TDCLK). The TDCLK clock frequency is data rate $\pm 0.01\%$ with a duty cycle of 50 $\pm 1\%$ .                                                                                                                                                            |

| XTCLK | IA       | External Transmit Clock. In synchronous mode, an external transmit data clock input (XTCLK) can be supplied.                                                                                                                                                                                                                                         |

| RXD   | OA       | <b>Received Data.</b> The modem presents received serial data on the Received Data (RXD) output and to the interface memory Receive Data Register (RBUFFER) in both serial and parallel modes.                                                                                                                                                       |

| TXD   | IA       | <b>Transmitted Data.</b> The modem obtains serial data to be transmitted on the TXD input in serial mode, or from the interface memory Transmit Data Register (TBUFFER) in parallel mode. (See TPDM bit.)                                                                                                                                            |

|       |          | PARALLEL MICROPROCESSOR INTERFACE                                                                                                                                                                                                                                                                                                                    |

|       |          | Address, data, control and interrupt hardware interface signals implement an 8086-compatible parallel microprocessor interface to a host processor. This parallel interface allows the host to change modem configuration, read or write channel and diagnostic data, and supervise modem operation by writing control bits and reading status bits. |

| D0-D7 | IA/OA    | <b>Data Lines.</b> Eight bidirectional data lines (DO-D7) provide parallel transfer of data between the host and the modem.                                                                                                                                                                                                                          |

| CS    | IA       | <b>Chip Select.</b> The active low Chip Select ( $\overline{\text{CS}}$ ) input enables parallel data transfer over the microprocessor bus.                                                                                                                                                                                                          |

RC96V24DP 2.0 Hardware Interface

Table 2-2. Hardware Interface Signal Definitions (Continued)

| Label         | I/O Type | Signal/Definition                                                                                                                                                                                                                                                                                                                                                                                       |

|---------------|----------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|               |          | PARALLEL MICROPROCESSOR INTERFACE (con't)                                                                                                                                                                                                                                                                                                                                                               |

| RS0-RS4       | IA       | Register Select Lines. The five active high Register Select inputs (RSO - RS4) address Interface memory registers in the modem when $\overline{\text{CS}}$ is low. These lines are typically connected to address lines AO-A4 to address one of 32 8-bit internal interface memory registers (00-1F). The selected register can be read from, or written into, via the 8-bit parallel data bus (DO-D7). |

| READ<br>WRITE | IAIA     | Read Enable and Write Enable. Reading or writing is controlled by the host pulsing either READ or WRITE input low, respectively, during the microprocessor bus access cycle.                                                                                                                                                                                                                            |

|               |          | During a write cycle, data from the data bus is copied into the addressed DSP interlace memory register, with high and low bus levels representing one and zero bit states, respectively.                                                                                                                                                                                                               |

| ĪRQ           | OA       | Interrupt Request. The IRQ output structure is an open-drain field-effect-transistor (FET). The IRQ output can be enabled in the interface memory to allow immediate indication of change of conditions in the modem. The use of IRQ is optional depending upon modem application.                                                                                                                      |

|               |          | HYBRID CIRCUIT                                                                                                                                                                                                                                                                                                                                                                                          |

| TXA1<br>TXA2  | O(DF)    | <b>Transmit Analog 1 and 2.</b> The TXA1 and TXA2 outputs are differential outputs 180 degrees out of phase with each other.                                                                                                                                                                                                                                                                            |

| RXA           | I(DA)    | <b>Receive Analog.</b> RXA is a single-ended receive data input from the telephone line interface or an optional external hybrid circuit.                                                                                                                                                                                                                                                               |

| VC            | OA       | <b>Centerpoint Voltage.</b> VC is a +2.5 VDC centerpoint voltage which serves as the internal 'analog ground' reference point.                                                                                                                                                                                                                                                                          |

|               |          | TELEPHONE LINE INTERFACE                                                                                                                                                                                                                                                                                                                                                                                |

| RADVR         | OD       | Relay A Driver. RADVR is an open drain output which can directly drive a relay with greater than 360 Q coil resistance and having a 'must operate' voltage of no greater than 4.0 VDC.                                                                                                                                                                                                                  |

|               |          | The RADVR output is controlled by the state of the RA bit, except in pulse dial mode.  When RA is a 1, the RADVR output is active which applies current to the relay coil.                                                                                                                                                                                                                              |

|               |          | In a typical application, RADVR is connected to the normally open Off-Hook relay. In this case, RADVR active closes the Off-Hook relay to connect the modem to the telephone line.                                                                                                                                                                                                                      |

| RBDVR         | OD       | <b>Relay B Driver.</b> RBDVR is an open drain output which can directly drive a relay with greater than 360 Q coil resistance and having a 'must operate' voltage of no greater than 4.0 VDC.                                                                                                                                                                                                           |

|               |          | RBDVR output is controlled by the state of the RB bit. When RB is a 1, the RBDVR output is active which applies current to the relay coil.                                                                                                                                                                                                                                                              |

|               |          | In a typical application, RBDVR is connected to the normally closed Talk/Data relay. In this case, RBDVR active opens the relay to disconnect the handset from the telephone line.                                                                                                                                                                                                                      |

| RING          | IA       | <b>Ring Frequency.</b> A low-going edge on the RING input initiates a ring frequency measurement. A valid ring detection is indicated by the RI bit.                                                                                                                                                                                                                                                    |

Table 2-2. Hardware Interface Signal Definitions (Continued)

| Label                      | I/O Type | Signal/Definition                                                                                                                                                                                                                                                                                                                                                                                                                |

|----------------------------|----------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                            |          | SPEAKER INTERFACE                                                                                                                                                                                                                                                                                                                                                                                                                |

| SPKR                       | O(DF)    | Speaker Analog Output. The SPKR output reflects the received analog input signal. The SPKR on/off and three levels of attenuation are controlled by interface memory bits. When the speaker is turned off, the SPKR output is clamped to the voltage at the VC pin. The SPKR output can drive an impedance as low as 300 ohms. In a typical application, the SPKR output is an input to an external LM386 audio power amplifier. |

|                            |          | SLEEP MODE SIGNALS                                                                                                                                                                                                                                                                                                                                                                                                               |

| SLEEP<br>SLEEP1            | OA<br>IA | Sleep Mode Output and Sleep Mode Input. SLEEP output high indicates the DSP is operating in its normal mode. SLEEP low indicates that the DSP is in the sleep mode. This signal must be connected to the SLEEP1 input to power down the IA in the sleep mode. SLEEP can also be used to control power to other devices (e.g., as a speaker enable).                                                                              |

|                            |          | DIAGNOSTIC SIGNALS                                                                                                                                                                                                                                                                                                                                                                                                               |

|                            |          | Four signals provide the timing and data necessary to create an oscilloscope quadrature eye pattern. The eye pattern is simply a display of the received baseband constellation. By observing this constellation, common line disturbances can usually be identified.                                                                                                                                                            |

| EYEX,<br>EYEY              | OB       | Eye Pattern Data X and Eye Pattern Data Y. The EYEX and EYEY outputs provide two serial bit streams containing data for display on the oscilloscope horizontal (X) axis and vertical (Y) axis, respectively. This serial digital data can be converted to analog form using two shift registers and two digital-to-analog converters (DACs).                                                                                     |

| EYECLK<br>(RRST0)          | OA       | <b>Eye Pattern Clock.</b> EYECLK is a clock for use by the serial-to-parallel converters. The EYECLK output is a 7200/9600 Hz clock.                                                                                                                                                                                                                                                                                             |

| EYESYNC                    | ОВ       | <b>Eye Pattern Sync.</b> EYESYNC is a strobe for word synchronization. The falling edge of EYESYNC may be used to transfer the 8-bit word from the shift register to a holding register. Digital-to-analog conversion can then be performed for driving the X and Y inputs of an oscilloscope.                                                                                                                                   |

|                            |          | MODEM INTERCONNECT                                                                                                                                                                                                                                                                                                                                                                                                               |

| RFIL0                      | MI       | <b>Receive Filter Output.</b> RFILO is the output of the internal receive analog filter which must be connected to AGCIN through a 0.1 μF, 20%, DC decoupling capacitor.                                                                                                                                                                                                                                                         |

| AGCIN                      | MI       | Receive AGC Gain Amplifier Input. See RFILO.                                                                                                                                                                                                                                                                                                                                                                                     |

| MODEO (DSP)<br>MODEI (IA)  | MI       | Mode Control. Serial IA mode control bits. Direct modem interconnect line.                                                                                                                                                                                                                                                                                                                                                       |

| TDACO (DSP),<br>TDACI (IA) | MI       | <b>Transmitter DAC Signal.</b> Transmitter serial digital DAC signal. Direct modem interconnect line.                                                                                                                                                                                                                                                                                                                            |

| TSTBO (DSP),<br>TSTBI (IA) | MI       | <b>Transmitter Strobe.</b> Transmitter 576 kHz digital timing reference. Direct modem interconnect line.                                                                                                                                                                                                                                                                                                                         |

| TRSTO (DSP),<br>TRSTI (IA) | MI       | <b>Transmitter Reset.</b> Transmitter 7200/9600 Hz digital timing reference. Direct modem interconnect line.                                                                                                                                                                                                                                                                                                                     |

RC96V24DP 2.0 Hardware Interface

Single Device Data/Modem Data Pump

Table 2-2. Hardware Interface Signal Definitions (Continued)

| Label                      | I/O Type | Signal/Definition                                                                                  |

|----------------------------|----------|----------------------------------------------------------------------------------------------------|

|                            |          | MODEM INTERCONNECT (con't)                                                                         |

| RADCI (DSP),<br>RADCO (IA) | MI       | Receiver ADC Signal. Receiver serial digital ADC signal. Direct modem interconnect line.           |

| RAGCO (DSP),<br>RAGCI (IA) | MI       | Receiver AGC Signal. Receiver serial digital AGC signal. Direct modem interconnect line.           |

| RSRBO (DSP),<br>RSRBI (IA) | MI       | <b>Receiver Strobe.</b> Receiver 576 kHz digital timing reference. Direct modem interconnect line. |

| RRSTO (DSP),<br>RRSTI (IA) | MI       | Receiver Reset. Receiver 7200/9600 Hz digital timing reference. Direct modem interconnect line.    |

Table 2-3. Digital Interface Characteristics

| 2.0<br>.8 (Vcc)<br>-0.3<br>- |                    | Vcc<br>Vcc<br>0.8<br>-400 | Vdc<br>Vdc<br>µA<br>Vdc | Vcc = 5.25V<br>I <sub>LOAD</sub> = -100 μA                       |

|------------------------------|--------------------|---------------------------|-------------------------|------------------------------------------------------------------|

| -0.3<br>-                    |                    | Vcc 0.8 -400 -            | μА                      |                                                                  |

| _                            | -                  | -400<br>-                 | μА                      |                                                                  |

| 3.5                          | -                  | _                         |                         |                                                                  |

| 3.5                          |                    | _                         | Vdc                     | L OAD = -100 HA                                                  |

| 3.5                          | -                  | _                         |                         | L 04D = -100 HA                                                  |

|                              |                    | Vcc                       |                         | $I_{LOAD} = 0 \text{ mA}$                                        |

|                              |                    |                           | Vdc                     |                                                                  |

| -<br>-<br>-                  | -                  | 0.4<br>0.4<br>0.75        |                         | $I_{LOAD}$ = 1.6 mA<br>$I_{LOAD}$ = 0.8 mA<br>$I_{LOAD}$ = 15 mA |

| -                            | -                  | ±10                       | μА                      | V <sub>IN</sub> = 0.4 to Vcc -1                                  |

|                              |                    |                           | mW                      |                                                                  |

| -                            | 300<br>15          | 450<br>22.5               |                         |                                                                  |

|                              | <u>-</u><br>-<br>- |                           | - 300 450<br>- 15 22.5  | - 300 450 mW                                                     |

Rockwell D96V24DSA 2-9

2.0 Hardware Interface RC96V24DP

Table 2-4. Analog Interface Characteristics

| Name       | Туре   | Characteristic          |

|------------|--------|-------------------------|

| RXA        | I (DA) | 1458 type op amp input  |

| TXA1, TXA2 | 0 (DD) | 1458 type op amp output |

| SPKR       | 0 (DF) | 1458 type op amp output |

# 3.0 Software Interface

## 3.1 Interface Memory

The DSP communicates with the host by means of a dual-port, interface memory The interface memory in the DSP contains thirty-two 8-bit registers, labeled register 00 through 1F. Each register can be read from, or written into, by both the host and the DSP. The host communicates with the DSP interface memory via the microprocessor bus.

The host can control modem operation by writing control bits to DSP interface memory and writing parameter values to DSP RAM through the interface memory. The host can monitor modem operation by reading status bits from DSP interface memory and reading parameter values from DSP RAM through interface memory.

# 3.2 Interface Memory Map

A memory map of DSP interface memory identifying the contents of the 32 addressable registers is shown in Table 3-1. These 8-bit registers may be read or written during any host read or write cycle. In order to operate on a single bit or group of bits in a register, the host must read a register then mask out unwanted data. When writing a single bit or group of bits in a register, the host must perform a read-modify-write operation. That is, the host must read the entire register, set or reset the necessary bits without altering the other register bits, then write the unaffected and modified bits back into the interface memory register.

## 3.3 Interface Memory Bit Functions

Table 3-2 summarizes the functions of the individual bits in the interface memory. Bits in the interface memory are referred to using the format Z:Q. The register number is denoted by Z (00 through iF) and the bit number is located by Q (0 through 7, where 0 = LSB).

Table 3-1. Interface Memory Map

| Register            | Register         | Bit                            |                |             |             |            |            |       |        |  |  |

|---------------------|------------------|--------------------------------|----------------|-------------|-------------|------------|------------|-------|--------|--|--|

| Function            | Address<br>(Hex) | 7                              | 6              | 5           | 4           | 3          | 2          | 1     | 0      |  |  |

|                     | 1F               | NSIA                           | NCIA           | _           | NSIE        | NEWS       | NCIE       | _     | NEWC   |  |  |

| Interrupt Handling  | 1E               | TDBIA                          | RDBIA          | TDBIE       | -           | TDBE       | RDBIE      | _     | RDBF   |  |  |

|                     | 1D               | XACC                           | _              | _           | _           | IOX        | XCRD       | XWT   | XCR    |  |  |

|                     | 1C               | X RAM ADDRESS (XADD)           |                |             |             |            |            |       |        |  |  |

|                     | 1B               | YACC                           | _              | _           | _           | _          | YCRD       | YWT   | YCR    |  |  |

| RAM Access,         | 1A               |                                | l              | ١           | RAM ADDI    | RESS (YADD | )          | l     | I      |  |  |

| Control and Status  | 19               |                                |                | Х           | RAM DATA    | MSB (XDAN  | <b>1</b> ) |       |        |  |  |

|                     | 18               |                                |                | >           | K RAM DATA  | LSB (XDAL  | .)         |       |        |  |  |

|                     | 17               |                                |                | Υ           | RAM DATA    | MSB (YDAN  | 1)         |       |        |  |  |

|                     | 16               |                                |                | ١           | / RAM DATA  | LSB (YDAL  | .)         |       |        |  |  |

| -                   | 15               | _                              | _              | -           | -           | _          | -          | _     | -      |  |  |

| _                   | 14               | _                              | _              | _           | _           | -          | _          | _     | -      |  |  |

| Combinal            | 13               |                                | TLVL VOL TXCLK |             |             |            |            |       |        |  |  |

| Control             | 12               | CONFIGURATION (CONF)           |                |             |             |            |            |       |        |  |  |

| Transmit Data       | 11               | _                              | _              | _           | _           | _          | _          | _     | TXP    |  |  |

| Buffer              | 10               | TRANSMIT DATA BUFFER (TBUFFER) |                |             |             |            |            |       |        |  |  |

|                     | 0F               | RLSD                           | FED            | CTS         | DSR         | RI         | TM         | SYNCD | FLAGS  |  |  |

|                     | 0E               | RTDET                          | BRKD           | PE          | FE          | 0E         |            | SPEED |        |  |  |

| Ctatua              | 0D               | _                              | PNDET          | S1DET       | SCR1        | U1DET      | SADET      | _     | -      |  |  |

| Status              | 0C               | EDET                           | -              | -           | -           |            | DT         | DIG   |        |  |  |

|                     | 0B               | TONEA                          | TONEB          | TONEC       | ATV25       | ATBELL     | PNSUC      | DTDET | BEL103 |  |  |

|                     | 0A               | -                              | _              | _           | -           | -          | _          | _     | CRCS   |  |  |

|                     | 09               | NV25                           | CC             | DTMF        | ORG         | LL         | DATA       | _     | SLEEP  |  |  |

|                     | 80               | ASYNC                          | TPDM           | _           | DDIS        | TRFZ       | _          | RTRN  | RTS    |  |  |

|                     | 07               | RDLE                           | RDL            | L2ACT       | -           | L3ACT      | RB         | RA    | ABORT  |  |  |

| Control             | 06               | BRKS                           | EXOS           | PAI         | RSL         | PEN        | STB        | WE    | SZ     |  |  |

| Control             | 05               | _                              | _              | _           | TXSQ        | CEQE       | RCEQ       | TXVOC | _      |  |  |

|                     | 04               | EQRES                          | SWRES          | _           | -           | EQFZ       | IFIX       | AGCFZ | CRFZ   |  |  |

|                     | 03               | NRZIE                          | HDLC           | SPLIT       | -           | ARC        | SDIS       | GTE   | -      |  |  |

|                     | 02               | _                              | _              | -           | _           | _          | -          | _     | _      |  |  |

| Danning Data Duffer | 01               | _                              | _              | -           | _           | _          | _          | _     | RXP    |  |  |

| Receive Data Buffer | 00               |                                | 1              | RECE        | IVE DATA BI | JFFER (RBU | FFER)      | 1     | 1      |  |  |

| Note: '-' in the BI | T columns inc    | licates reser                  | ved for mod    | em use only |             |            |            |       |        |  |  |

Table 3-2. Interface Memory Bit Functions

|        | Location | Name/Description                                                                                     |  |  |

|--------|----------|------------------------------------------------------------------------------------------------------|--|--|

| ABORT  | 07:0     | HDLC Abort. Controls sending of continuous mark in HDLC mode.                                        |  |  |

| AGCFZ  | 04:1     | AGC Freeze. inhibits updating of the receiver AGC.                                                   |  |  |

| ARC    | 03:3     | Automatic Rate Change Enable. Enables automatic on-line rate change sequence.                        |  |  |

| ASYNC  | 08:7     | Asynchronous/Synchronous. Selects asynchronous or synchronous data mode.                             |  |  |

| ATBELL | OB:3     | Bell Answer Tone Detected. Reports detection status of 2225 Hz answer tone.                          |  |  |

| ATV25  | OB:4     | V25 Answer Tone Detected. Reports detection status of 2100 Hz answer tone.                           |  |  |

| BEL103 | OB:0     | Bell 103 Mark Frequency Detected. Reports detection status of 1270 Hz Bell 103 mark.                 |  |  |

| BRKD   | 0E:6     | Break Detected. Reports receipt status of continuous space.                                          |  |  |

| BRKS   | 06:7     | Break Sequence. Controls sending of continuous space in parallel asynchronous mode.                  |  |  |

| CC     | 09:6     | Controlled Carrier. Selects controlled or constant carrier mode.                                     |  |  |

| CEQ    | 05:3     | <b>Compromise Equalizer Enable</b> . Enables the transmit passband digital compromise equalizer.     |  |  |

| CONF   | 12:0-7   | Modem Configuration Select. Selects the modem operating mode.                                        |  |  |

| CRCS   | 0A:0     | CRC Sending. Reports the sending status of the CRC (2 bytes) in HDLC mode.                           |  |  |

| CRFZ   | 04:0     | <b>Carrier Recovery Freeze</b> . Disables update of the receiver's carrier recovery phase lock loop. |  |  |

| CTS    | 0F:5     | Clear to Send. Reports that the training sequence has been completed (see TPDM).                     |  |  |

| DATA   | 09:2     | Data Mode. Selects idle or data mode.                                                                |  |  |

| DDIS   | 08:4     | Descrambler Disable. Disables the receiver's descrambler circuit.                                    |  |  |

| DSR    | 0F:4     | Data Set Ready. Reports the data transfer state.                                                     |  |  |

| DTDET  | OB:1     | DTMF Digit Detected. Reports that a valid DTFM digit has been detected.                              |  |  |

| DTDIG  | 00:0-3   | Detected DTMF Digit. Contains the hexadecimal code of the detected DTMF digit.                       |  |  |

| DTMF   | 09:5     | DTMF Dial Select. Selects either DTMF or pulse dialing in the dial mode.                             |  |  |

| EDET   | 00:7     | <b>Early DTMF Detect</b> . Reports detection of the high group frequency of the DTMF tone pair.      |  |  |

| EQFZ   | 04:3     | Equalizer Freeze. inhibits the update of the receiver's adaptive equalizer taps.                     |  |  |

| EQRES  | 04:7     | Equalizer Reset. Resets the receiver adaptive equalizer taps to zero.                                |  |  |

| EX0S   | 06:6     | Extended Overspeed. Selects extended overspeed mode in asynchronous mode.                            |  |  |

| FE     | 0E:4     | Framing Error. Reports framing error detection or detection of an ABORT sequence.                    |  |  |

| FED    | 0F:6     | Fast Energy Detected. Reports energy above the turn-on threshold is being detected.                  |  |  |

#### 3.3 Interface Memory Bit Functions

Table 3-2. Interface Memory Bit Functions (Continued)

| Mnemonic | Memory<br>Location | Name/Description                                                                                                                                                                                                                                                             |  |  |  |

|----------|--------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| FLAGS    | OF:0               | <b>Flag Sequence</b> . Reports transmission status of the Flag sequence in HDLC mode, or transmission of a constant mark in parallel asynchronous mode.                                                                                                                      |  |  |  |

| GTE      | 03:1               | <b>Guard Tone Enable</b> . Enables transmission of the 1800 Hz guard tone (CCITT configuration only).                                                                                                                                                                        |  |  |  |

| HDLC     | 03:6               | High Level Data Link Control. Enables HDLC protocol support in parallel data mode.                                                                                                                                                                                           |  |  |  |

| IFIX     | 04:2               | Eye Fix. Forces EYEX and EYEY serial data to be rotated equalizer output.                                                                                                                                                                                                    |  |  |  |

| IOX      | 1D:3               | I/O Register Select. Specifies that the X RAM ADDRESS (XADD) is an internal I/O register address.                                                                                                                                                                            |  |  |  |

| L2ACT    | 07:5               | <b>Loop 2 (Local Digital Loopback) Activate</b> . Selects connection of the receiver's digital output Internally to the transmitter's digital input (locally activated digital loopback).                                                                                    |  |  |  |

| L3ACT    | 07:3               | Loop 3 (Local Analog Loopback) Activate. Selects connection of the transmitter's analog output Internally to the receiver's analog input (local analog loopback).                                                                                                            |  |  |  |

| LL       | 09:3               | Leased Line. Selects leased line data mode or handshake mode.                                                                                                                                                                                                                |  |  |  |

| NCIA     | 1F:6               | <b>NEWC Interrupt Active</b> . Reports that the cause of an interrupt request was completion of a configuration change. (See NEWC and NCIE.)                                                                                                                                 |  |  |  |

| NCIE     | 1F:2               | <b>NEWC interrupt Enable</b> . Enables the assertion of $\overline{IRQ}$ and the setting of the NCIA bit.                                                                                                                                                                    |  |  |  |

| NEWC     | I F:0              | <b>New Configuration</b> . Initiates a new configuration; cleared by the modem upon completion of configuration change. This bit can cause $\overline{\text{IRQ}}$ to be asserted. (See NCIE and NCIA.)                                                                      |  |  |  |

| NEWS     | 1F:3               | New Status. Reports the detection of a change In selected status bits. This bit can cause $\overline{\mbox{IRQ}}$ to be asserted. (See NSIE and NSIA.)                                                                                                                       |  |  |  |

| NSIA     | 1F:7               | <b>NEWS Interrupt Active</b> . Reports that the cause of an interrupt request was a status change. (See NEWS and NSIE.)                                                                                                                                                      |  |  |  |

| NSIE     | 1F:4               | <b>NEWS interrupt Enable</b> . Enables the assertion of $\overline{IRQ}$ and the setting of the NSIA b (See NEWS.)                                                                                                                                                           |  |  |  |

| NV25     | 09:7               | <b>Disable V.25 Answer Sequence (Data Modes), Disable Echo Suppressor Tone (Fax Modes)</b> . Disables the transmitting of the 2100 Hz CCI1T answer tone when a handshake sequence Is initiated In a data mode or disables sending of the echo suppressor tone in a fax mode. |  |  |  |

| 0E       | 0E:3               | Overrun Error. Reports overrun status of the Receiver Data Buffer (RBUFFER).                                                                                                                                                                                                 |  |  |  |

| ORG      | 09:4               | Originate. Selects originate or answer mode.                                                                                                                                                                                                                                 |  |  |  |

| PE       | 0E:5               | Parity Error. Reports parity error status or bad CRC                                                                                                                                                                                                                         |  |  |  |

| PNSUC    | OB:2               | PN Success. Indicates that the receiver has detected the PN portion of the training sequence.                                                                                                                                                                                |  |  |  |

| RA       | 07:1               | Relay A Activate. Activates the RADRV output.                                                                                                                                                                                                                                |  |  |  |

| PARSL    | 06:4.5             | <b>Parity Select</b> . Selects stuff, space, even, or odd parity in the asynchronous parallel data mode.                                                                                                                                                                     |  |  |  |

3.3 Interface Memory Bit Functions

Table 3-2. Interface Memory Bit Functions (Continued)

| Mnemonic | Memory<br>Location | Name/Description                                                                                                                                                     |  |  |  |

|----------|--------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| RB       | 07:2               | Relay B Activate. Activates the RBDVR output.                                                                                                                        |  |  |  |

| RBUFFER  | 00:0-7             | Receive Data Buffer. Contains the received byte of data.                                                                                                             |  |  |  |

| RDBF     | 1E:0               | <b>Receiver Data Buffer Full</b> . Reports the status (full or not full) of the Receiver Data Buffe (RBUFFER). (See RDBIE and RDBIA.)                                |  |  |  |

| RDBIA    | 1E:6               | Receiver Data Buffer interrupt Active. Reports that the cause of an interrupt request Is the Receiver Data Buffer (RBUFFER) full. (See RDBF and RDBIE.)              |  |  |  |

| RDBIE    | I E:2              | Receiver Data Buffer interrupt Enable. Enables the assertion of $\overline{\text{IRQ}}$ and the setting of the RDBIA bit when RBUFFER is full. (See RDBF and RDBIA.) |  |  |  |

| RDL      | 07:6               | Remote Digital Loopback Request. initiates a request for the remote modem to go into digital loop-back.                                                              |  |  |  |

| RDLE     | 07:7               | Remote Digital Loopback Response Enable. Enables the modem to respond to the remote modem's digital loopback request.                                                |  |  |  |

| PEN      | 06:3               | Parity Enable. Enables generation/checking of parity in asynchronous parallel data mode.                                                                             |  |  |  |

| RCEQ     | 05:2               | Receiver Compromise Equalizer Enable. Controls insertion of the receive passband digital compromise equalizer into the receive path.                                 |  |  |  |

| RI       | 0F:3               | Ring Indicator. Reports detection status of a valid ringing signal.                                                                                                  |  |  |  |

| RTDET    | 0E:7               | Retrain Detected. Reports detection status of a retrain request sequence.                                                                                            |  |  |  |

| RTRN     | 08:1               | <b>Retrain</b> . Controls sending of the retrain request or automatic rate change to the remote modem.                                                               |  |  |  |

| RTS      | 08:0               | Request to Send. Requests the transmitter to send data.                                                                                                              |  |  |  |

| RLSD     | 0F:7               | Received Line Signal Detector. Reports detection status of the carrier and the receip valid data.                                                                    |  |  |  |

| RXP      | 01:0               | Received Parity bit. This bit is the received parity bit (or ninth data bit).                                                                                        |  |  |  |

| S1DET    | 00:5               | S1 Sequence Detected. Reports detection status of the S1 sequence.                                                                                                   |  |  |  |

| SADET    | 00:2               | Scrambled Alternating Ones Sequence Detected. Reports detection status of the Scrambled Alternating Ones sequence.                                                   |  |  |  |

| SCR1     | 00:4               | Scrambled Ones Sequence Detected. Reports detection status of Scrambled Ones sequence.                                                                               |  |  |  |

| SDIS     | 03:2               | Scrambler Disable. Disables the transmitter scrambler.                                                                                                               |  |  |  |

| SLEEP    | 09:0               | Sleep Mode. Controls entry Into the SLEEP mode. The modem requires a pulse on the RESET pin to return to normal operation.                                           |  |  |  |

| SPEED    | 0E:0-2             | Speed Indication. Reports the data rate at the completion of a connection.                                                                                           |  |  |  |

| SPLIT    | 03:5               | Extended Overspeed TX/RX Split. Limits transmit data to the basic overspeed rate.                                                                                    |  |  |  |

| STB      | 06:2               | Stop Bit Number. Selects the number of stop bits in asynchronous mode.                                                                                               |  |  |  |

| SWRES    | 04:6               | Software Reset. Causes the modem to reinitialize to Its power turn-on state.                                                                                         |  |  |  |

#### 3.3 Interface Memory Bit Functions

Table 3-2. Interface Memory Bit Functions (Continued)