# SH66P20A

## OTP 4-bit Microcontroller

#### **Features**

■ SH6610C-based single-chip 4-bit microcontroller

■ ROM: 1K X 16 bits

■ RAM: 64 X 4 bits (Data memory)

■ Operation voltage: 2.4V - 6.0V (Typical 3.0V or 5.0V)

■ 12 CMOS bi-directional I/O pins

■ 4-level subroutine nesting (including interrupts)

■ One 8-bit auto re-load timer/counter

■ Warm-up timer for power on reset

■ Powerful interrupt sources:

- Internal interrupt (Timer0)

- External interrupts: PortB & PortC (Falling edge)

■ Oscillator (user option)

- X`tal oscillator: 32.768KHz ~ 4MHz - Ceramic resonator: 400K ~ 4MHz - RC oscillator: 400K ~ 4MHz

- External clock:30K ~ 4MHz

■ Instruction cycle time:

-4/32.768KHz (≈ 122us) for 32.768KHz OSC clock

-4/4MHz (= 1us) for 4MHz OSC clock

■ Two low power operation modes: HALT and STOP

■ OTP type

■ Code protection

■ Built-in watchdog timer

## **General Description**

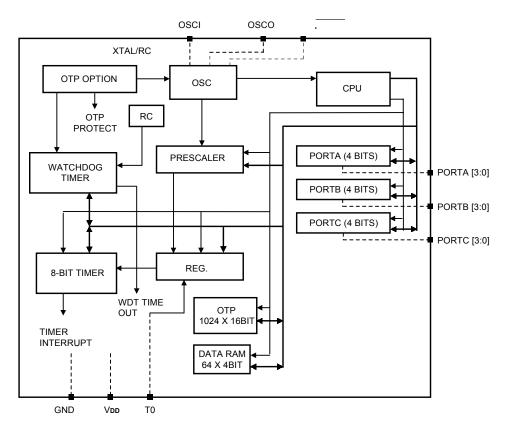

SH66P20A is a 4-bit microcontroller. This chip integrates the SH6610C 4-bit CPU core with SRAM, 1K program ROM, Timer and I/O Port.

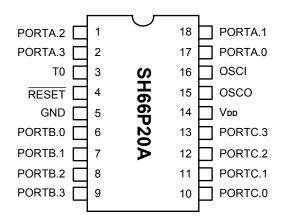

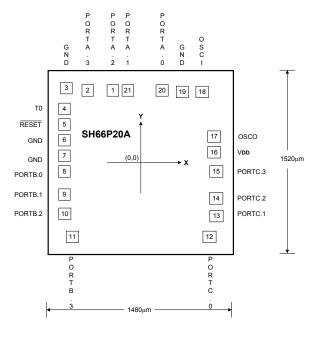

## **Pin Configuration**

1

www.DataSheet4U.com

V2.3

## **Block Diagram**

# **Pin Description**

| Pin No. | Designation | I/O | Description                                                              |

|---------|-------------|-----|--------------------------------------------------------------------------|

| 1 - 2   | PORTA2, 3   | I/O | Bit programmable I/O                                                     |

| 3       | T0          | I   | Timer Clock/Counter (Schmitt Trigger input)                              |

| 4       | RESET       | I   | Reset input (Active Low)                                                 |

| 5       | GND         | Р   | Ground pin                                                               |

| 6 - 9   | PORTB0 - 3  | I/O | Bit programmable I/O, Vector Interrupt (Active falling edge)             |

| 10 - 13 | PORTC0 - 3  | I/O | Bit programmable I/O, Vector Interrupt (Active falling edge)             |

| 14      | VDD         | Р   | Power supply pin                                                         |

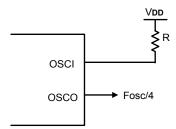

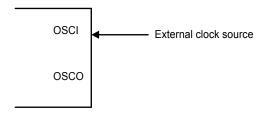

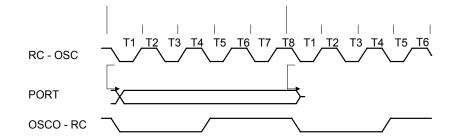

| 15      | osco        | 0   | OSC output pin. There is a signal with a frequency of Fosc/4 for RC mode |

| 16      | OSCI        | I   | OSC input pin can be connected to crystal、ceramic or external resistor   |

| 17 - 18 | PORTA0, 1   | I/O | Bit programmable I/O                                                     |

Note: The all pins excluding pin15 are shared with OTP programming.

#### **Function Description**

#### 1. CPU

The CPU contains the following function blocks: Program Counter, Arithmetic Logic Unit (ALU), Carry Flag, Accumulator, Table Branch Register, Data Pointer (INX, DPH, DPM, and DPL), and Stack.

#### 1.1. PC (Program Counter)

The Program Counter is used to address the 1K program ROM. It consists of 12-bits: Page Register (PC11), and Ripple Carry Counter (PC10, PC9, PC8, PC7, PC6, PC5, PC4, PC3, PC2, PC1, PC0).

The program counter normally increases by one (+1) with every execution of an instruction except in the following cases:

- When executing a jump instruction (such as JMP, BA0, BNC),

- (2) When executing a subroutine call instruction (CALL),

- (3) When an interrupt occurs,

- (4) When the chip is at the INITIAL RESET mode.

The program counter is loaded with data corresponding to each instruction.

#### 1.2. ALU and CY

The ALU performs arithmetic and logic operations. It provides the following functions:

Binary addition/subtraction (ADC, SBC, ADD, SUB, ADI, SBI)

Decimal adjust for addition/subtraction (DAA, DAS) Logic operations (AND, EOR, OR, ANDIM, EORIM, ORIM)

Decision (BA0, BA1, BA2, BA3, BAZ, BNC) Logic Shift (SHR)

The Carry Flag (CY) holds the ALU overflow which the arithmetic operation generates. During an interrupt servicing or call instruction, the carry flag is pushed into the stack and restored back from the stack by the RTNI instruction. It is unaffected by the RTNW instruction.

#### 1.3. Accumulator

The Accumulator is a 4-bit register holding the results of the arithmetic logic unit. In conjunction with the ALU, data transfer between the accumulator and system register, or data memory can be performed.

#### 1.4. Stack

This group of registers is used to save the contents of CY & PC (11 - 0) sequentially with each subroutine call or interrupt. It is organized to 13 bits X 4 levels. The MSB is saved for CY. Four levels are the maximum allowed total for subroutine calls and interrupts.

The contents of Stack are returned sequentially to the PC with the return instructions (RTNI/RTNW). Stack is operated on a first-in, last-out basis. This 4-level nesting includes both subroutine call and interrupt requests. Note that program execution may enter an abnormal state if the number of calls and interrupt requests exceed 4, where then the bottom of stack will be shifted out.

#### 2. ROM

The SH66P20A can address up to 1024 X 16 bit of program area from \$000 to \$3FF. Service routine such as starting vector address.

Vector Address Area (\$000 to \$004)

The program is sequentially executed. There is an area address \$000 through \$004 that is reserved for a special interrupt service routine such as starting vector address.

| Address | Instruction     | Function                       |  |  |  |

|---------|-----------------|--------------------------------|--|--|--|

| \$000H  | JMP instruction | Jump to RESET service routine  |  |  |  |

| \$001H  | NOP             | Reserved                       |  |  |  |

| \$002H  | JMP instruction | Jump to TIMER0 service routine |  |  |  |

| \$003H  | NOP             | Reserved                       |  |  |  |

| \$004H  | JMP instruction | Jump to PBC service routine    |  |  |  |

## 3. RAM

Built-in RAM consists of general-purpose data memory and system register. Direct addressing in one instruction can accessed data memory and system register.

The following is the memory allocation map:

000 - 01F: System register and I/O. 020 - 05F: Data memory (64 X 4 bits).

## The Configuration of System Register

| Address     | Bit3   | Bit2   | Bit1   | Bit0   | R/W | Remarks                                      |

|-------------|--------|--------|--------|--------|-----|----------------------------------------------|

| \$00        | -      | IET0   | -      | IEP    | R/W | Interrupt enable flags                       |

| \$01        | -      | IRQT0  | -      | IRQP   | R/W | Interrupt request flags                      |

| \$02        | -      | TM0.2  | TM0.1  | TM0.0  | R/W | Timer0 Mode register (Prescaler)             |

| \$03        | -      | -      | -      | -      | -   | Reserved                                     |

| \$04        | T0L.3  | T0L.2  | T0L.1  | T0L.0  | R/W | Timer0 load/counter register low digit       |

| \$05        | T0H.3  | T0H.2  | T0H.1  | T0H.0  | R/W | Timer0 load/counter register high digit      |

| \$06        | -      | -      | -      | -      | -   | Reserved                                     |

| \$07        | LPD3   | LPD2   | LPD1   | LPD0   | W   | LPD Control (0AH: Enable, 05H: Disable)      |

| \$08        | PA.3   | PA.2   | PA.1   | PA.0   | R/W | PORTA                                        |

| \$09        | PB.3   | PB.2   | PB.1   | PB.0   | R/W | PORTB                                        |

| \$0A        | PC.3   | PC.2   | PC.1   | PC.0   | R/W | PORTC                                        |

| \$0B - \$0D | -      | -      | -      | -      | -   | Reserved                                     |

| \$0E        | TBR.3  | TBR.2  | TBR.1  | TBR.0  | R/W | Table Branch Register                        |

| \$0F        | INX.3  | INX.2  | INX.1  | INX.0  | R/W | Pseudo index register                        |

| \$10        | DPL.3  | DPL.2  | DPL.1  | DPL.0  | R/W | Data pointer for INX low nibble              |

| \$11        | -      | DPM.0  | DPM.1  | DPM.0  | R/W | Data pointer for INX middle nibble           |

| \$12        | -      | -      | -      | -      | -   | Reserved                                     |

| \$13 - \$15 | -      | -      | -      | -      | -   | Reserved                                     |

| \$16        | PA3OUT | PA2OUT | PA10UT | PA0OUT | W   | Set PORTA to be output port                  |

| \$17        | PB3OUT | PB2OUT | PB1OUT | PB0OUT | W   | Set PORTB to be output port                  |

| \$18        | PC3OUT | PC2OUT | PC10UT | PC0OUT | W   | Set PORTC to be output port                  |

| \$19 - \$1B | -      | -      | -      | -      | -   | Reserved.                                    |

| \$1C        | -      | -      | T0S    | T0E    | W   | Bit0: T0 signal edge, Bit1: T0 signal source |

| \$1D        | -      | -      | -      | -      | -   | Reserved                                     |

| \$1E        | WDT    | -      | -      | -      | W   | Bit3: WDT time-out bit (write one only)      |

| \$1F        | -      | -      | -      | -      | ı   | Reserved                                     |

<sup>\*</sup> System Register \$00 - \$12 (Please refer to "SH6610C User's manual").

#### 4. Low Power Detection (LPD)

The LPD function is to monitor the supply voltage and applies an internal reset in the microcontroller at the time of battery replacement. If the applied circuit satisfies the following conditions, the LPD can be incorporated by software control.

- High reliability is not required

- Power supply voltage VDD = 2.4V to 6.0 V

- Operating ambient temperature  $T_A$  = -20 $^{\circ}$ C to + 70 $^{\circ}$ C

## 4.1. Functions of LPD Circuit

The LPD circuit has the following functions:

- Generates an internal reset signal when VDD ≤ VLPD

- Cancels the internal reset signal when VDD > VLPD

Here, VDD: power supply voltage, VLPD: LPD detect voltage, it is about  $1.9 \pm 0.3 \text{V}$

## 4.2. LPD Control Register

The LPD circuit is controlled by software enable flag

| Address | Bit3 | Bit2 | Bit1 | Bit0 | R/W | Remark                                                                             |

|---------|------|------|------|------|-----|------------------------------------------------------------------------------------|

| \$07    | LPD3 | LPD2 | LPD1 | LPD0 | W   | LPD Enable Control (LPD3 ~ 0):<br>1010: LPD Enable (Default);<br>0101: LPD Disable |

| LPD3 | LPD2 | LPD1 | LPD0 | LPD Enable/Disable flag.               |

|------|------|------|------|----------------------------------------|

| 1    | 0    | 1    | 0    | Enable LPD circuit (Power-on initial). |

| 0    | 1    | 0    | 1    | Disable LPD circuit.                   |

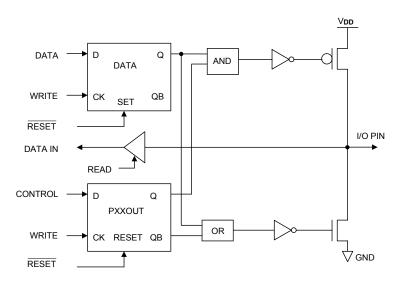

## 5. I/O Ports

The SH66P20A provides 12 I/O pins. When every I/O is used as an input port, the port control register controls ON/OFF of the output buffer. Sections below show the circuit configuration of I/O ports.

Each of these ports contains 4 bits I/O pins. ON/OFF of the output buffer for port can be controlled by the port control register. Port I/O mapping address is shown as follows:

| Address | Bit3     | Bit2     | Bit1     | Bit0     | R/W |

|---------|----------|----------|----------|----------|-----|

| \$08    | PORT A.3 | PORT A.2 | PORT A.1 | PORT A.0 | R/W |

| \$09    | PORT B.3 | PORT B.2 | PORT B.1 | PORT B.0 | R/W |

| \$0A    | PORT C.3 | PORT C.2 | PORT C.1 | PORT C.0 | R/W |

Equivalent circuit for a single I/O pin

## System Register \$16 - \$18

| Address | Bit3   | Bit2   | Bit1   | Bit0   | R/W | Description                 |

|---------|--------|--------|--------|--------|-----|-----------------------------|

| \$16    | PA3OUT | PA2OUT | PA10UT | PA0OUT | W   | Set PORTA to be output port |

| \$17    | PB3OUT | PB2OUT | PB1OUT | PB0OUT | W   | Set PORTB to be output port |

| \$18    | PC3OUT | PC2OUT | PC10UT | PC0OUT | W   | Set PORTC to be output port |

I/O control register:

PAXOUT, PBXOUT, PCXOUT (X = 0, 1, 2, 3)

1: Set I/O as an output buffer

0: Set I/O as an input buffer (initial power-on)

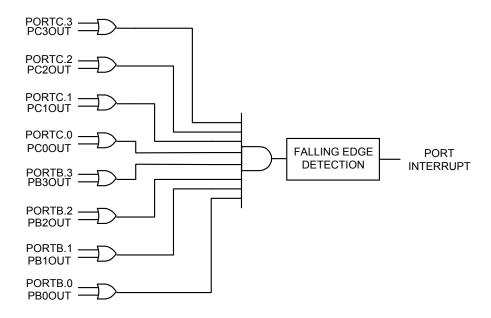

## PORTB & PORTC interrupt

The PORTB and PORTC are used as port interrupt sources. Since PORT I/O is bit programmable I/O, so only the input port can generate an external interrupt. Any one of the PORTB and PORTC input pin transitions from  $V_{DD}$  to GND will generate an interrupt request. And further falling edge transition would not be able to make interrupt request until all of the pins return to  $V_{DD}$ . Following is the port interrupt function block-diagram.

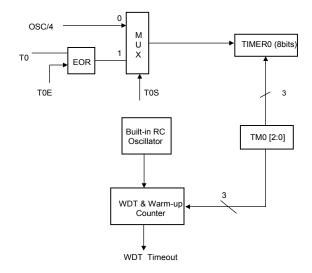

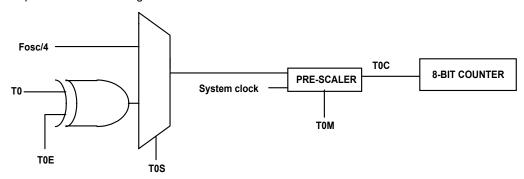

#### 6. T0 & WDT

#### System Register \$1C

| Address | BIT3 | BIT2 | BIT1 | BIT0 | R/W | Remark                                         |

|---------|------|------|------|------|-----|------------------------------------------------|

| \$1C    | ı    | ı    | TOS  | T0E  | W   | Bit0: T0 signal edge<br>Bit1: T0 signal source |

T0E: T0 signal edge.

0: Increment on low-to-high transition T0 pin (initial power-on).

1: Increment on high-to-low transition T0 pin.

T0S: T0 signal source.

0: OSC 1/4 (initial power-on).

1: Transition on T0 pin.

#### T0, OSC1/4 & WDT

## System Register \$1E

| Address | Bit3 | Bit2 | Bit1 | Bit0 | R/W | Remark                                  |

|---------|------|------|------|------|-----|-----------------------------------------|

| \$1E    | WDT  | -    | -    | -    | W   | Bit3: WDT time-out bit (write one only) |

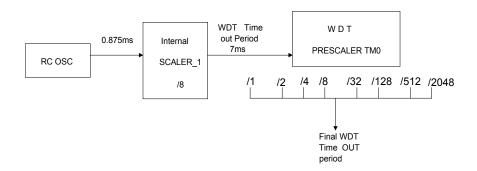

The input clock of watchdog timer is generated by a built-in RC oscillator, so that the WDT will always run even in the STOP mode. SH66P20A generates a RESET condition when watchdog times-out. Watchdog can be enabled or disabled permanently by user option. To prevent it from timing out and generating a device RESET condition, one can write this bit as "1" before timing-out. The WDT has a time-out period of more than 7ms (VDD = 5V). If longer time-out periods are desired, a prescaler with a division ratio of up to 1:2048 can be assigned to the WDT under software controlled by writing to the TM0 register.

# Pre-scaler divide ratio (valid for V<sub>DD</sub> = 5V):

| TM0.2 | TM0.1 | TM0.0 | Prescaler divide ratio    | Timer-out period |

|-------|-------|-------|---------------------------|------------------|

| 1     | 1     | 1     | 1:1                       | 7ms              |

| 1     | 1     | 0     | 1:2                       | 14ms             |

| 1     | 0     | 1     | 1:4                       | 28ms             |

| 1     | 0     | 0     | 1:8                       | 56ms             |

| 0     | 1     | 1     | 1:32                      | 224ms            |

| 0     | 1     | 0     | 1:128                     | 896ms            |

| 0     | 0     | 1     | 1:512                     | 3,584ms          |

| 0     | 0     | 0     | 1:2048 (Power on initial) | 14,336ms         |

#### 7. Timer0

SH66P20A has one 8-bit timer. The time/counter has the following features:

- . 8-bit timer/counter

- . Readable and writable

- . Automatic reloadable counter

- . 8-prescaller scale is available

- . Internal and external clock select

- . Interrupt on overflow from \$FF to \$00

- . Edge select for external event

Following is a simplified timer block diagram:

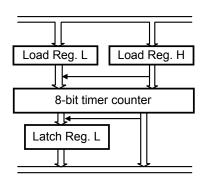

#### 7.1. Configuration and Operation

Timer-0 consists of an 8-bit write-only timer load register (TL0L, TL0H), and an 8-bit read-only timer counter (TC0L, TC0H). The counter and load register both have low order digits and high order digits. The timer counter can be initialized by writing data into the timer load register (TL0L, TL0H). Load register programming: write the low-order digit first and then the high-order digit. The timer counter is loaded with the content of load register automatically when the high order digit is written or counter counts overflow from \$FF to \$00.

Timer Load Register: Since the register H would control the physical READ and WRITE operation. Please follow these rules:

Write Operation:

Low nibble first; High nibble to update the counter. Read Operation:

High nibble first; Low nibble followed.

#### 7.2. Timer0 Interrupt

The timer overflow will generate an internal interrupt request, when the counter counts overflow from \$FF to \$00. If the interrupt enable flag is enabled, then a timer interrupt service routine will proceed. This can also be used to wake CPU from HALT mode.

#### 7.3. Timer0 mode register

The timer can be programmed in several different prescaler ratio by setting Timer Mode register (TM0). The 8-bit counter counts prescaler overflow output pulses. The timer mode registers (TM0) are 3-bit registers used for timer control as shown in table1. These mode registers select the input pulse sources into the timer.

#### Timer 0 Mode Register (\$02)

| TM0.2 | TM0.1 | TM0.0 | Prescaler Divide Ratio | Ratio N        |

|-------|-------|-------|------------------------|----------------|

| 0     | 0     | 0     | /2 <sup>11</sup>       | 2048 (initial) |

| 0     | 0     | 1     | /2 <sup>9</sup>        | 512            |

| 0     | 1     | 0     | /2 <sup>7</sup>        | 128            |

| 0     | 1     | 1     | /2 <sup>5</sup>        | 32             |

| 1     | 0     | 0     | /2 <sup>3</sup>        | 8              |

| 1     | 0     | 1     | /2 <sup>2</sup>        | 4              |

| 1     | 1     | 0     | /21                    | 2              |

| 1     | 1     | 1     | /2 <sup>0</sup>        | 1              |

#### 7.4. External Clock/Event T0 as TMR0 Source

When external clock/event input is used for TM0, it is synchronized with CPU system clock. Therefore the external source must follow certain constrains. The output from T0M multiplex is T0C. It is sampled by system clock in instruction frame cycle. Therefore it is necessary for T0C to be high at least 2 tosc and low at least 2 tosc. When prescaler ratio selects /20, T0C is the same as the system clock input. Therefore the requirement is as follows:

T0H = T0CH = T0 high time

$$\geq 2 \text{ tosc} + \Delta T$$

T0L = T0CL = T0 low time  $\geq 2 \text{ tosc} + \Delta T$

When other prescaler ratio is selected, the TM0 is scaled by the asynchronous ripple counter and so the prescaler output is symmetrical.

Then:

TOC high time = TOC low time =

$$\frac{N*T0}{2}$$

Where

T0 = Timer0 input period N = prescaler value

The requirement is, therefore:

$$\frac{\,\,N^{\star}\,T0}{\,2}\,\,\geq\,\,2\,\,tosc\,+\,\,\Delta T$$

, or  $T0\,\geq\,\,\frac{\,\,4^{\,\star}\,t_{\,\,}osc\,+\,2\,\,\,T}{\,\,N}$

The limitation is applied for T0 period time only. The pulse width is not limited by this equation. It is summarized as follows:

T0 = Timer0 period

$$\geq \frac{4*t_{osc} + 2 T}{N}$$

#### 8. Interrupt

Two interrupt sources are available on for:

- Timer0 overflow interrupt

- Port's falling edge detection interrupt (PBC)

Interrupt Control Bits and Interrupt Service

The interrupt control flags are mapped on \$00 through \$01 of the system register. They can be accessed or tested by program. Those flags are cleared to 0 at initialization by chip reset.

| Address | Bit3 | Bit2  | Bit1 | Bit0 | Remarks                 |

|---------|------|-------|------|------|-------------------------|

| \$00    | -    | IET0  | -    | IEP  | Interrupt enable flags  |

| \$01    | -    | IRQT0 | -    | IRQP | Interrupt request flags |

When IEx is set to 1 and the interrupt request is generated (IRQx is 1), the interrupt will be activated and vector address will be generated from the priority PLA corresponding to the interrupt sources. When an interrupt occurs, the PC and CY flag will be saved into stack memory and jump to interrupt service vector address. After the interrupt occurs, all interrupt enable flags (IEx) are reset to 0 automatically, so when IRQx is 1 and IEx is set to 1 again, the interrupt will be activated and vector address will be generated from the priority PLA corresponding to the interrupt sources.

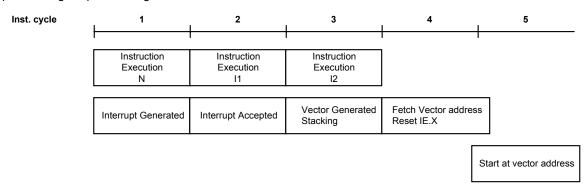

Interrupt Servicing Sequence Diagram:

#### Interrupt Nesting:

During the SH6610C CPU interrupt service, the user can enable any interrupt enable flag before returning from the interrupt. The servicing sequence diagram shows the next interrupt and the next nesting interrupt occurrences. If the interrupt request is ready and the instruction of execution N is IE enable, then the interrupt will start immediately after the next two instruction executions. However, if instruction I1 or instruction I2 disables the interrupt request or enable flag, then the interrupt service will be terminated.

#### System Clock and Oscillator

System clock generator produces the basic clock pulses that provide the system clock with CPU and peripherals. Instruction cycle time

- (1) 4/32.768KHz ( $\approx 122us$ ) for 32.768KHz system clock.

- (2) 4/4MHz (= 1us) for 4MHz system clock.

## Oscillator

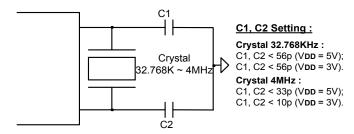

(1) Crystal oscillator: 32.768KHz - 4MHz.

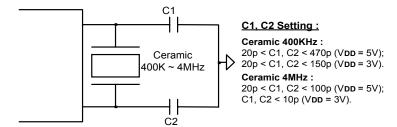

(2) Ceramic resonator: 400KHz - 4MHz.

(3) RC oscillator: 400KHz - 4MHz.

(4) External input clock: 30KHz - 4MHz.

# **Initial State**

| Hardware            | After power on reset |

|---------------------|----------------------|

| Program counter     | \$000                |

| СҮ                  | Undefined            |

| Data memory         | Undefined            |

| System register     | Undefined            |

| AC                  | Undefined            |

| Timer counter       | 0                    |

| Timer load register | 0                    |

| WDT counter         | 0                    |

| WDT prescaler       | 0                    |

| I/O Ports           | Input                |

| TOS TOE             | 00                   |

| WDT                 | 0                    |

| LPD                 | 1010                 |

#### **Instruction Set**

All instructions are one cycle and one word instructions. The characteristics is memory-oriented operation. Arithmetic and Logical Instruction

## **Accumulator Type**

| Mne  | emonic  | Instruction Code    |           | Function                                             |    |

|------|---------|---------------------|-----------|------------------------------------------------------|----|

| ADC  | X (, B) | 00000 0bbb xxx xxxx | AC        | ← Mx + AC + CY                                       | CY |

| ADCM | X (, B) | 00000 1bbb xxx xxxx | AC, Mx    | ← Mx + AC + CY                                       | CY |

| ADD  | X (, B) | 00001 0bbb xxx xxxx | AC        | ← Mx + AC                                            | CY |

| ADDM | X (, B) | 00001 1bbb xxx xxxx | AC, Mx    | ← Mx + AC                                            | CY |

| SBC  | X (, B) | 00010 0bbb xxx xxxx | AC        | ← Mx + -AC + CY                                      | CY |

| SBCM | X (, B) | 00010 1bbb xxx xxxx | AC, Mx    | ← Mx + -AC + CY                                      | CY |

| SUB  | X (, B) | 00011 0bbb xxx xxxx | AC        | ← Mx + -AC + 1                                       | CY |

| SUBM | X (, B) | 00011 1bbb xxx xxxx | AC, Mx    | ← Mx + -AC + 1                                       | CY |

| EOR  | X (, B) | 00100 0bbb xxx xxxx | AC        | $\leftarrow$ Mx $\oplus$ AC                          |    |

| EORM | X (, B) | 00100 1bbb xxx xxxx | AC, Mx    | $\leftarrow$ Mx $\oplus$ AC                          |    |

| OR   | X (, B) | 00101 0bbb xxx xxxx | AC        | ← Mx   AC                                            |    |

| ORM  | X (, B) | 00101 1bbb xxx xxxx | AC, Mx    | ← Mx   AC                                            |    |

| AND  | X (, B) | 00110 0bbb xxx xxxx | AC        | ← Mx & AC                                            |    |

| ANDM | X (, B) | 00110 1bbb xxx xxxx | AC, Mx    | ← Mx & AC                                            |    |

| SHR  |         | 11110 0000 000 0000 | 0 → AC [3 | B]; AC $[0] \rightarrow CY$ ; AC shift right one bit | CY |

## **Immediate Type**

| Mner  | nonic | Instruction Code    | Function                        | Flag Change |

|-------|-------|---------------------|---------------------------------|-------------|

| ADI   | X, I  | 01000 iiii xxx xxxx | AC ← Mx + I                     | CY          |

| ADIM  | X, I  | 01001 iiii xxx xxxx | $AC, Mx \leftarrow Mx + I$      | CY          |

| SBI   | X, I  | 01010 iiii xxx xxxx | AC ← Mx + -I + 1                | CY          |

| SBIM  | X, I  | 01011 iiii xxx xxxx | AC, Mx ← Mx + -I + 1            | CY          |

| EORIM | X, I  | 01100 iiii xxx xxxx | $AC, Mx \leftarrow Mx \oplus I$ |             |

| ORIM  | X, I  | 01101 iiii xxx xxxx | AC, Mx ← Mx   I                 |             |

| ANDIM | X, I  | 01110 iiii xxx xxxx | AC, Mx ← Mx & I                 |             |

<sup>\*</sup> In the assembler ASM66 V1.0, EORIM mnemonic is EORI. However, EORI has the same operation identical with EORIM. Same for the ORIM with respect to ORI, and ANDIM with respect to ANDI.

## **Decimal Adjustment**

| Mnemonic | Instruction Code    | Function                             | Flag Change |

|----------|---------------------|--------------------------------------|-------------|

| DAA X    | 11001 0110 xxx xxxx | AC; Mx ← Decimal adjustment for add. | CY          |

| DAS X    | 11001 1010 xxx xxxx | AC; Mx ← Decimal adjustment for sub. | CY          |

## **Transfer Instruction**

| Mnemonic Instruction Code |                     | Function              | Flag Change |

|---------------------------|---------------------|-----------------------|-------------|

| LDA X (, B)               | 00111 0bbb xxx xxxx | $AC \leftarrow Mx$    |             |

| STA X (, B)               | 00111 1bbb xxx xxxx | Mx ← AC               |             |

| LDI X, I                  | 01111 iiii xxx xxxx | AC, $Mx \leftarrow I$ |             |

## **Control Instruction**

| Mnemonic  | Instruction Code    | Function                                     | Flag Change |

|-----------|---------------------|----------------------------------------------|-------------|

| BAZ X     | 10010 xxxx xxx xxxx | $PC \leftarrow X \text{ if } AC = 0$         |             |

| BNZ X     | 10000 xxxx xxx xxxx | $PC \leftarrow X \text{ if } AC \neq 0$      |             |

| BC X      | 10011 xxxx xxx xxxx | PC ← X if CY = 1                             |             |

| BNC X     | 10001 xxxx xxx xxxx | $PC \leftarrow X \text{ if } CY \neq 1$      |             |

| BA0 X     | 10100 xxxx xxx xxxx | PC ← X if AC (0) = 1                         |             |

| BA1 X     | 10101 xxxx xxx xxxx | PC ← X if AC (1) = 1                         |             |

| BA2 X     | 10110 xxxx xxx xxxx | PC ← X if AC (2) = 1                         |             |

| BA3 X     | 10111 xxxx xxx xxxx | PC ← X if AC (3) = 1                         |             |

| CALLY     | 44000               | ST ← CY; PC + 1                              |             |

| CALL X    | 11000 xxxx xxx xxxx | PC $\leftarrow$ X (Not including p)          |             |

|           |                     | PC ←ST; TBR ← hhhh;                          |             |

| RTNW H; L | 11010 000h hhh IIII | AC ← IIII                                    |             |

| RTNI      | 11010 1000 000 0000 | CY; PC ← ST                                  | CY          |

| HALT      | 11011 0000 000 0000 |                                              |             |

| STOP      | 11011 1000 000 0000 |                                              |             |

| JMP X     | 1110p xxxx xxx xxxx | $PC \qquad \leftarrow X \text{ (Include p)}$ |             |

| TJMP      | 11110 1111 111 1111 | PC ← (PC11-PC8) (TBR) (AC)                   |             |

| NOP       | 11111 1111 111 1111 | No Operation                                 |             |

## Where,

| PC  | Program counter           | I        | Immediate data        |

|-----|---------------------------|----------|-----------------------|

| AC  | Accumulator               | $\oplus$ | Logical exclusive OR  |

| -AC | Complement of accumulator | 1        | Logical OR            |

| CY  | Carry flag                | &        | Logical AND           |

| Mx  | Data memory               | bbb      | RAM bank = 000        |

| р   | ROM page = 0              |          |                       |

| ST  | Stack                     | TBR      | Table Branch Register |

# **OTP Options**

- Oscillator: Crystal Osc, Ceramic resonator or RC oscillator. WDT: Enable or Disable.

## **Absolute Maximum Rating\***

# DC Supply Voltage . . . . . -0.3V to + 7.0V Input/Output Voltage . . . . . . GND -0.2V to V DD + 0.2V Operating Ambient Temperature . . . . -10°C to + 60°C Storage Temperature . . . . -55°C to + 125°C

#### \*Comments

Stresses above those listed under "Absolute Maximum Ratings" may cause permanent damage to this device. These are stress ratings only. Functional operation of this device under these or any other conditions above those indicated in the operational sections of this specification is not implied or intended. Exposure to the absolute maximum rating conditions for extended periods may affect device reliability.

**DC Electrical Characteristics** (VDD = 5.0V GND = 0V, TA = 25°C, Fosc = 4MHz [external clock], unless otherwise specified.)

| Parameter                                        | Symbol | Min.              | Тур | Max.               | Unit | Condition                                                                          |

|--------------------------------------------------|--------|-------------------|-----|--------------------|------|------------------------------------------------------------------------------------|

| Operating Voltage                                | VDD    | 4.5               | 5   | 6                  | V    |                                                                                    |

| Operating Current                                | ЮР     |                   | 1.3 | 1.5                | mA   | All output pins unloaded (Execute NOP instruction)                                 |

| Stand by Current (HALT)                          | ISB1   |                   |     | 300                | μА   | All output pins unload, WDT off<br>LPD off (If WDT on, Isв1 = Isв1 + 20μA)         |

| Stand by Current (HALT)<br>OSC = 32768Hz Crystal | ISB32k |                   |     | 10                 | μΑ   | All output pins unload, WDT off<br>LPD off (If WDT on, ISB32k = I SB1 + 20μA)      |

| Stand by Current (STOP)                          | ISB2   |                   |     | 1                  | μА   | All output pins unloaded,<br>LPD off, WDT off<br>(If WDT on, I sв2 = I sв2 + 20μΑ) |

| Input Low Voltage                                | VIL1   | GND               |     | 0.2 X VDD          | V    | I/O Ports, pins tri-state                                                          |

| Input Low Voltage                                | VIL2   | GND               |     | 0.15 X V <b>DD</b> | V    | RESET, T0                                                                          |

| Input Low Voltage                                | VIL3   | GND               |     | 0.15 X V <b>DD</b> | V    | OSCI (Driven by external clock)                                                    |

| Input High Voltage                               | VIH1   | 0.8 X VDD         |     | VDD                | V    | I/O Ports, pins tri-state                                                          |

| Input High Voltage                               | VIH2   | 0.85 X V <b>D</b> |     | VDD                | V    | RESET, T0                                                                          |

| Input High Voltage                               | VIH3   | 0.85 X V <b>D</b> |     | VDD                | V    | OSCI (Driven by external Clock)                                                    |

| Input Leakage Current                            | lIL1   | -1                |     | 1                  | μА   | I/O Ports, GND < VI/O < VDD                                                        |

| Input Leakage Current                            | lIL2   | -5                |     |                    | μА   | V RESET = GND + 0.25V                                                              |

| Input Leakage Current                            | lIL3   |                   | 1   | 5                  | μА   | VRESET = VDD                                                                       |

| Input Leakage Current                            | lIL4   | -3                | 1   | 3                  | μА   | T0, GND < Vto < Vdd                                                                |

| Input Leakage Current                            | lıL5   | -3                | 1   | 3                  | μΑ   | For OSCI                                                                           |

| Output High Voltage                              | Voн    | VDD - 0.7         |     |                    | V    | I/O Ports, Iон = -10mA<br>OSCO, Iон = -0.7mA                                       |

| Output Low Voltage                               | Vol    |                   |     | GND + 0.6          | V    | I/O Ports, IoL = 20mA<br>OSCO, IoL = 1.6mA                                         |

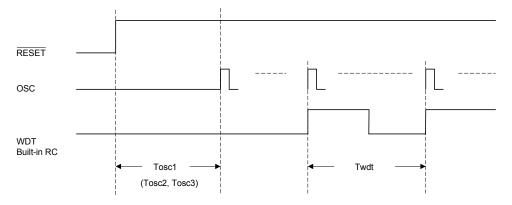

# AC Electrical Characteristics ( $V_{DD}$ = 5.0V GND = 0V, $T_{A}$ = 25 $^{\circ}$ C, $F_{OSC}$ = 4MHz [external clock], unless otherwise specified.)

| Parameter                     | Symbol | Min. | Тур. | Max. | Unit | Condition                                                 |

|-------------------------------|--------|------|------|------|------|-----------------------------------------------------------|

| Oscillator Start Time         | Tosc1  |      |      | 2    | s    | X'tal osc = 32.768KHz                                     |

| Oscillator Start Time         | Tosc2  |      |      | 20   | ms   | Ceramic Osc = 400KHz                                      |

| Oscillator Start Time         | Tosca  |      |      | 2    | ms   | RC Osc = 400KHz                                           |

| Oscillator Start Time         | Тѕт    |      |      | 5    | ms   | WDT RC oscillator = 1/18ms Hz                             |

| WDT Period                    | Тwdт   | 7    | 12   |      | ms   |                                                           |

| Frequency Stability (crystal) | Δ F/F  |      |      | 1    | PPM  | Crystal oscillator: [F(5.0) - F(4.5)]/F(5.0)              |

| Frequency Variation (crystal) | Δ F/F  |      |      | 10   | PPM  | Crystal oscillator: C1 = C2 = 5 - 30P                     |

| Frequency Stability (ceramic) | Δ F/F  |      |      | 0.1  | %    | Ceramic resonator Oscillator:<br>[F(5.0) - F(4.5)]/F(5.0) |

| Frequency Variation (RC)      | Δ F/F  |      |      | 20   | %    | Include supply voltage and chip to chip variation         |

| Temperature Stability (RC)    | Δ F/F  |      |      | 7.5  | %    | RC oscillator: [F(-10°C) - F(60°C)]/F(-10°C)              |

## Notes:

Negative current is defined as the flowing out of the pin.

Max. current into VDD = 50mA.

Max. current out of Vss = 150mA.

Max. output current sunk by any I/O pin = 25mA.

Max. output current sourced by any I/O pin = 20mA.

Max. output current sunk by any I/O port = 50mA.

Max. output current sourced by any I/O port = 40mA.

DC Electrical Characteristics (V<sub>DD</sub> = 3.0V, GND = 0V, T<sub>A</sub> = 25°C, Fosc = 4MHz [external clock], unless otherwise specified)

| Parameter                                   | Symbol | Min.               | Тур | Max.               | Unit     | Condition                                                                       |

|---------------------------------------------|--------|--------------------|-----|--------------------|----------|---------------------------------------------------------------------------------|

| Operating Voltage                           | VDD    | 2.4                | 3   | 4.5                | V        |                                                                                 |

| Operating Current                           | lop    |                    | 0.8 | 1.0                | mA       | All output pins unloaded (Execute NOP instruction)                              |

| Stand by Current (HALT)                     | ISB1   |                    |     | 140                | μА       | All output pins unload, WDT off LPD off (If WDT on, Isв1 = Isв1 + 8μΑ)          |

| Stand by Current (HALT) OSC = 32768 Crystal | SB32k  |                    |     | 5                  | μА       | All output pins unload, WDT off<br>LPD off<br>(If WDT on, Isвx = Isв1 + 8μΑ)    |

| Stand by Current (STOP)                     | ISB2   |                    |     | 1                  | μА       | All output pins unloaded,<br>LPD off<br>WDT off (If WDT on, Isв2x = Isв2 + 8μΑ) |

| Input Low Voltage                           | VIL1   | GND                |     | 0.2 X VDD          | V        | I/O Ports, pins tri-state                                                       |

| Input Low Voltage                           | VIL2   | GND                |     | 0.15 X V <b>DD</b> | V        | RESET, T0                                                                       |

| Input Low Voltage                           | VIL3   | GND                |     | 0.15 X V <b>DD</b> | V        | OSCI (Driven by external clock)                                                 |

| Input High Voltage                          | VIH1   | 0.8 X VDD          |     | VDD                | V        | I/O, Ports, pins tri-state                                                      |

| Input High Voltage                          | VIH2   | 0.85 X V <b>DD</b> |     | VDD                | V        | RESET, T0                                                                       |

| Input High Voltage                          | VIH3   | 0.85 X V <b>DD</b> |     | VDD                | V        | OSCI (Driven by external Clock)                                                 |

| Input Leakage Current                       | lIL1   | -1                 |     | 1                  | μА       | I/O Ports, GND < VI/O < VDD                                                     |

| Input Leakage Current                       | lIL2   | -3.8               |     |                    | μА       | V <sub>RESET</sub> = GND + 0.25V                                                |

| Input Leakage Current                       | IIL3   |                    | 1   | 3.8                | μА       | V <sub>RESET</sub> = VDD                                                        |

| Input Leakage Current                       | lIL4   | -2.3               | 1   | 2.3                | μА       | T0, GND < Vto < Vdd                                                             |

| Input Leakage Current                       | lıL5   | -2.3               | 1   | 2.3                | μА       | For OSCI                                                                        |

| Output High Voltage                         | Voн    | VDD - 0.7          |     |                    | <b>V</b> | I/O Ports, Iон = -7mA<br>OSCO, Iон = -0.7mA                                     |

| Output Low Voltage                          | VoL    |                    |     | GND + 0.4          | V        | I/O Ports, IoL = 8mA<br>OSCO, IoL = 1.0mA                                       |

## AC Electrical Characteristics (VDD = 3.0V, GND = 0V, Ta = $25^{\circ}$ C, Fosc = 4MHz [external clock], unless otherwise specified)

| Parameter                     | Symbol | Min. | Тур | Max. | Unit | Condition                                                 |

|-------------------------------|--------|------|-----|------|------|-----------------------------------------------------------|

| Oscillator Start Time         | Tosc1  |      |     | 3.5  | S    | Crystal Osc = 32.768KHz                                   |

| Oscillator Start Time         | Tosc2  |      |     | 35   | ms   | Ceramic Osc = 400KHz                                      |

| Oscillator Start Time         | Tosc3  |      |     | 5    | ms   | RC Osc = 400KHz                                           |

| Oscillator Start Time         | ТЅТ    |      |     | 8.5  | ms   | WDT RC oscillator = 1/18ms Hz                             |

| WDT Period                    | Twdt   | 7    | 12  |      | ms   |                                                           |

| Frequency Stability (crystal) | Δ F/F  |      |     | 1    | PPM  | Crystal oscillator: [F(3.0)-F(2.7)]/F(3.0)                |

| Frequency Variation (crystal) | Δ F/F  |      |     | 10   | PPM  | Crystal oscillator: C1 = C2 = 5 - 30P                     |

| Frequency Stability (ceramic) | Δ F/F  |      |     | 0.1  | %    | Ceramic resonator Oscillator:<br>[F(3.0) - F(2.7)]/F(3.0) |

| Frequency Variation (RC)      | Δ F/F  |      |     | 20   | %    | Include supply voltage and chip to chip variation         |

| Temperature Stability (RC)    | Δ F/F  |      |     | 7.5  | %    | RC oscillator:[F(-10°C) - F(60°C)]/F(-10°C)               |

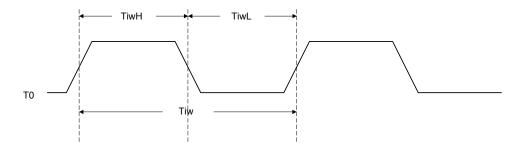

## **AC Characteristics**

| Symbol | Parameter              | Min.            | Тур. | Max. | Unit | Condition                  |

|--------|------------------------|-----------------|------|------|------|----------------------------|

| Tcy    | Instruction cycle time | 1               |      | 122  | μS   |                            |

| Tıw    | T0 input width         | (Tcy + 40)/N    |      |      | ns   | N = Prescaler divide ratio |

| Tiwh   | High pulse width       | 1/2 t <b>ıw</b> |      |      | ns   |                            |

| TIWL   | LOW pulse width        | 1/2 t <b>ıw</b> |      |      | ns   |                            |

# **Timing Waveform**

# **T0 Input Waveform**

# **RC OSCO Timing Waveform**

## **Built-in RC Oscillator**

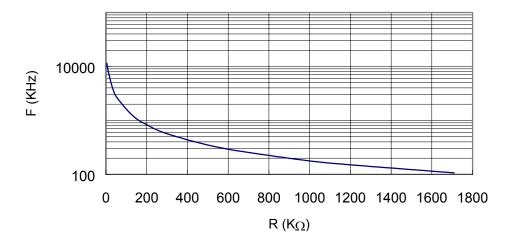

Typical RC oscillator Resistor vs. Frequency: (VDD = 3V, for reference only)

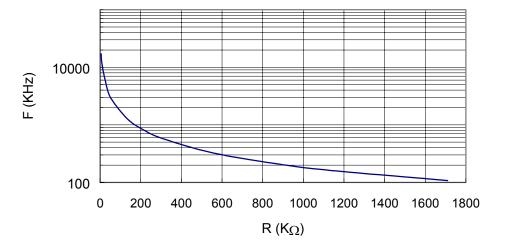

Typical RC oscillator Resistor vs. Frequency: (VDD = 5V, for reference only)

## **Application Circuits (for reference only)**

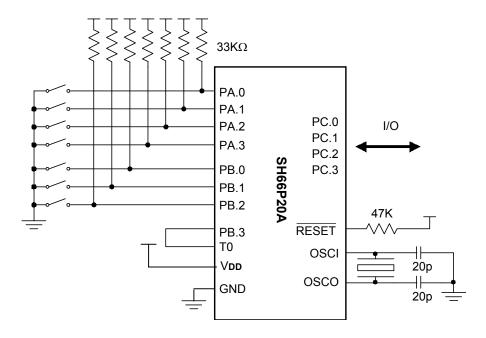

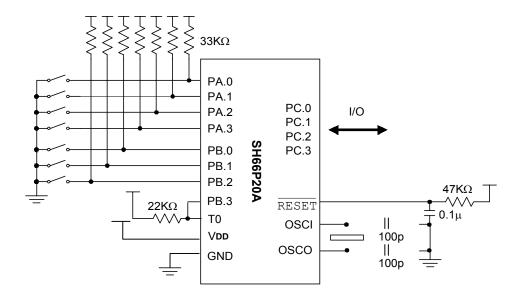

## AP1:

a. Operating voltage: 3.0V.b. Oscillator: Crystal 32.768KHz.

c. PORTA - C: I/O.

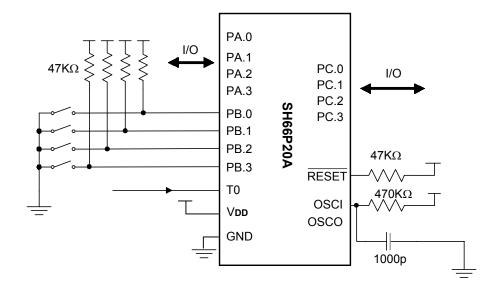

## AP2:

a. Operating voltage: 5.0V.b. Oscillator: Crystal 4MHz.

c. PORTA - C: I/O.

#### AP3:

a. Operating voltage: 5.0V.b. Oscillator: Ceramic 400KHz.

c. PORTA - C: I/O.

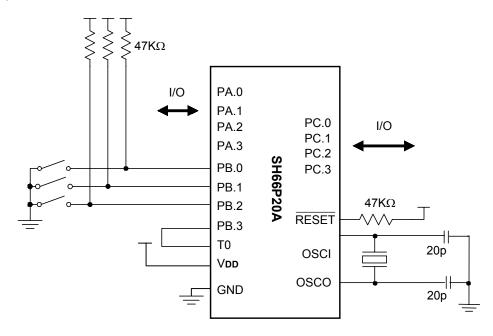

## AP4:

a. Operating voltage: 5.0V.b. Oscillator: RC 400KHz.c. PORTA – C: I/O.

d. Timer0 input: T0.

## AP5:

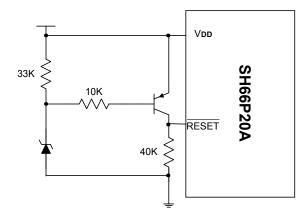

## Reset Protection Circuit 1

RESET will be pulled to GND when VDD goes lower than Zener voltage + 0.7V.

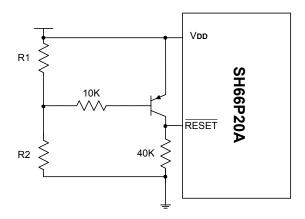

## AP6:

## Reset Protection Circuit 2

RESET will be pulled to GND when (VDD X R1/(R1 + R2)) is lower than 0.7V

# **Bonding Diagram**

unit : μm

| Pad No. | Designation | Х       | Υ       | Pad No. | Designation | Х      | Υ       |

|---------|-------------|---------|---------|---------|-------------|--------|---------|

| 1       | PORTA.2     | -229.80 | 677.60  | 12      | PORTC.0     | 577.95 | -675.65 |

| 2       | PORTA.3     | -480.30 | 677.60  | 13      | PORTC.1     | 664.60 | -397.70 |

| 3       | GND         | -640.10 | 691.20  | 14      | PORTC.2     | 664.60 | -224.10 |

| 4       | T0          | -659.55 | 558.75  | 15      | PORTC.3     | 664.60 | 26.40   |

| 5       | RESET       | -659.55 | 415.75  | 16      | VDD         | 627.30 | 195.40  |

| 6       | GND         | -657.35 | 283.30  | 17      | osco        | 625.40 | 325.40  |

| 7       | GND         | -657.35 | 161.40  | 18      | OSCI        | 422.45 | 645.65  |

| 8       | PORTB.0     | -659.55 | 26.40   | 19      | GND         | 290    | 641.55  |

| 9       | PORTB.1     | -659.55 | -224.10 | 20      | PORTA.0     | 155    | 677.60  |

| 10      | PORTB.2     | -659.55 | -397.70 | 21      | PORTA.1     | -95.50 | 677.60  |

| 11      | PORTB.3     | -592.90 | -675.65 |         |             |        |         |

note: The all GND pins must be connected together outside the chip and the substrate must be connected with GND.

## **Ordering Information**

| Part No.              | Package | Packing |

|-----------------------|---------|---------|

| SH66P20A-yyxxx/018DU  | 18L DIP | Tube    |

| SH66P20AM-yyxxx/018MU | 18L SOP | Tube    |

#### Note:

- "-yyxxx": "yy" means 2 bits option and "xxx" means 3 bits code seriary number. If the product is OTP type and in blank order, those bits should be none.

The data after mark "/" in Part No. block is the package and packing information for ordering.

The size of those package types are showed in "Package Information" (Page27 Page28).

Any other package or packing request, please refer to following table.

| Package |                   | Packing |                                                 |  |

|---------|-------------------|---------|-------------------------------------------------|--|

| D       | DIP R             |         | Normal package size and in tray packing         |  |

| F       | QFP               | U       | Normal package size and in tube packing         |  |

| Н       | CHIP              | Α       | Normal package size and in tape & reel packing  |  |

| J       | CER-DIP           | D       | Larger package size and in tray packing         |  |

| K       | SKINNY            | L       | Larger package size and in tube packing         |  |

| L       | PLCC              | В       | Larger package size and in tape & reel packing  |  |

| М       | SOP               | T       | Smaller package size and in tray packing        |  |

| N       | OTHER             | S       | Smaller package size and in tube packing        |  |

| Ø       | GOOD DIE ON WAFER | N       | Smaller package size and in tape & reel packing |  |

| S       | SOJ               |         |                                                 |  |

| T       | TO92              |         |                                                 |  |

| ٧       | VSOP/TSOP         |         |                                                 |  |

| W       | WAFER             |         |                                                 |  |

| X       | TSSOP             |         |                                                 |  |

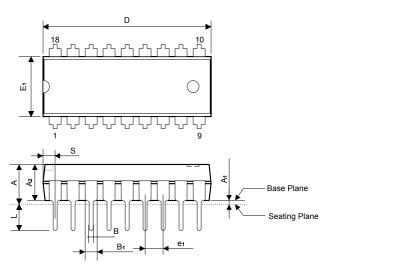

# **Package Information**

DIP 18L Outline Dimensions

unit: inches/mm

| Symbol         | Dimensions in inches    | Dimension in mm         |

|----------------|-------------------------|-------------------------|

| Α              | 0.175 Max.              | 4.45 Max.               |

| <b>A</b> 1     | 0.010 Min.              | 0.25 Min.               |

| A2             | 0.130 ± 0.010           | 3.30 ± 0.25             |

| В              | 0.018 +0.004<br>-0.002  | 0.46 +0.10<br>-0.05     |

| B1             | 0.060 +0.004<br>-0.002  | 1.52 +0.10<br>-0.05     |

| С              | 0.010 +0.004<br>-0.002  | 0.25 +0.10<br>-0.05     |

| D              | 0.900 Typ. (0.920 Max.) | 22.86 Typ. (23.37 Max.) |

| E              | 0.300 ± 0.010           | 7.62 ± 0.25             |

| E <sub>1</sub> | 0.250 Typ. (0.262 Max.) | 6.35 Typ. (6.65 Max.)   |

| <b>e</b> 1     | 0.100 ± 0.010           | 2.54 ± 0.25             |

| L              | 0.130 ± 0.010           | 3.30 ± 0.25             |

| α              | 0° ~ 15°                | 0° ~ 15°                |

| еа             | 0.345 ± 0.035           | 8.76 ± 0.89             |

| S              | 0.055 Max.              | 1.40 Max.               |

## Notes:

- 1. The maximum value of dimension D includes end flash.

- 2. Dimension  $E_1$  does not include resin fins.

- 3. Dimension S includes end flash.

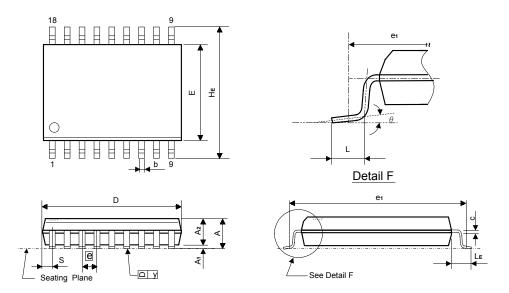

## **SOP 18L Outline Dimensions**

unit: inches/mm

| Symbol     | Dimensions in inches   | Dimensions in mm    |

|------------|------------------------|---------------------|

| Α          | 0.110 Max.             | 2.79 Max.           |

| A1         | 0.004 Min.             | 0.10 Min.           |

| A2         | 0.092 ± 0.005          | 2.33 ± 0.13         |

| b          | 0.016 +0.004<br>-0.002 | 0.41 +0.10<br>-0.05 |

| С          | 0.010 +0.004<br>-0.002 | 0.25 +0.10<br>-0.05 |

| D          | 0.455 ± 0.015          | 11.56 ± 0.38        |

| Е          | 0.295 ± 0.010          | 7.49 ± 0.25         |

| е          | 0.050 ± 0.006          | 1.27 ± 0.15         |

| <b>e</b> 1 | 0.376 NOM.             | 9.50 NOM.           |

| HE         | 0.406 ± 0.012          | 10.31 ± 0.31        |

| L          | 0.030 ± 0.008          | 0.76 ± 0.20         |

| LE         | 0.055 ± 0.008          | 1.40 ± 0.20         |

| S          | 0.037 Max.             | 0.94 Max.           |

| у          | 0.004 Max.             | 0.10 Max.           |

| θ          | 0° ~ 10°               | 0° ~ 10°            |

## Notes:

- 1. The maximum value of dimension D includes end flash.

- 2. Dimension E does not include resin fins.

- 3. Dimension e<sub>1</sub> is for PC Board surface mount pad pitch design reference only.

- 4. Dimension S includes end flash.

# **Data Sheet Revision History**

| Version | Content                                                     | Date      |

|---------|-------------------------------------------------------------|-----------|

| 2.3     | Add package and packing information in ordering information | Jul. 2004 |

| 2.2     | Change RC Frequency Variation to ±20%                       | Apr. 2002 |

| 2.1     | Add Reset Protection Circuit (AP5 and AP6)                  | Feb. 2002 |

| 1.0     | Original                                                    | Jun. 2000 |