# Microprocessor Compatible Monitor Controller

## **FEATURES**

- Synchronous signal processing for use in green monitor applications.

- Easy command interface for external microprocessor controls.

- D/A converters up to 12V output.

- Built-in self-test pattern generator.

- On-chip clock oscillator allows external TTL level clock signal input.

## **GENERAL DESCRIPTION**

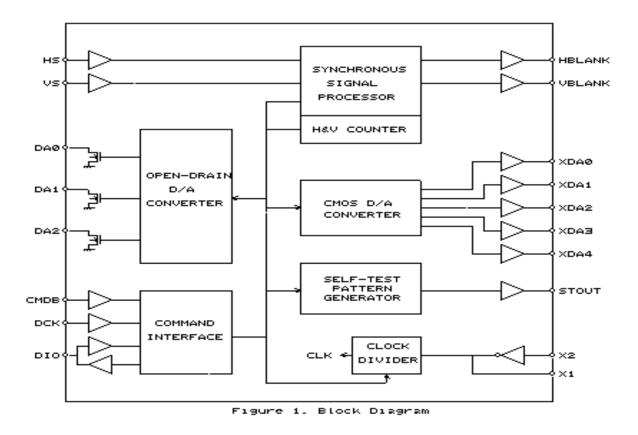

MTV003 is intended for use in digital-controlled, power-conscious (Green) monitor applications. It integrates 4 major function blocks traditionally implemented in discrete parts and provides an easy interface for microprocessor controls. The functional blocks included in MTV003 are: SYNC processing, D/A converters, self-test pattern generator and command interface.

#### **BLOCK DIAGRAM**

This datasheet contains new product information. Myson Technology reserves the rights to modify the product specification without notice. No liability is assumed as a result of the use of this product. No rights under any patent accompany the sale of the product.

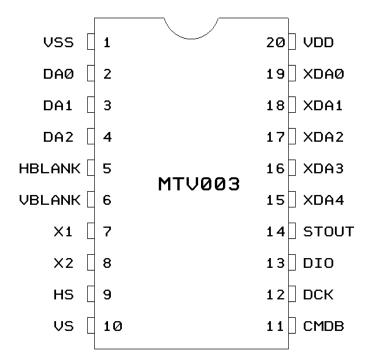

## 1.0 CONNECTION DIAGRAM

(20 PIN PDIP 300 MIL PACKAGE)

## 2.0 PIN DESCRIPTIONS

| Name   | I/O | Pin# | Function                                                                                                                                                                                                                                                                                                                                                                              |

|--------|-----|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| VSS    |     | 1    | Ground (0 V).                                                                                                                                                                                                                                                                                                                                                                         |

| DA0    | 0   | 2    | <b>Open-Drain PWM</b> (Pulse Width Modulation) <b>D/A Converter 0</b> . The output pulse width is programmable by writing data to <b>Reg10</b> with 8-bit resolution to control the pulse width duration from 0 to 255/256. The output frequency is 31.25KHz (or15.625KHz). In applications, the external pull-up resistor can be connected to 12V for the desired full-scale output. |

| DA1    | 0   | 3    | <b>Open-Drain PWM D/A Converter 1</b> . <b>See DA0.</b> The output pulse width is programmable by <b>Reg11</b> .                                                                                                                                                                                                                                                                      |

| DA2    | 0   | 4    | <b>Open-Drain PWM D/A Converter 2</b> . <b>See DA0.</b> The output pulse width is programmable by <b>Reg12</b> .                                                                                                                                                                                                                                                                      |

| HBLANK | 0   | 5    | Horizontal Blank. The pulse width and the delay of HBLANK vs.HS input leading edges are programmable by Reg7 and Reg6, respectively.                                                                                                                                                                                                                                                  |

| VBLANK | 0   | 6    | Vertical Blank. The output pulse width is programmable by Reg9.                                                                                                                                                                                                                                                                                                                       |

| X1     | I/O | 7    | <b>Crystal 1</b> . Used to interface to the oscillator. An 8MHz(or 4MHz) crystal must be connected between this pin and pin X2. An appropriate capacitor to Ground, whose value depends on the specified C <sub>L</sub> of the                                                                                                                                                        |

|        |     |      | crystal, must be connected. This pin can also be used as a direct input when the external oscillator is used.                                                                                                                                                                                                                                                                         |

MTV003 Revision 2.3 07/01/1998

| Name   | I/O | Pin# | Function                                                                                                                             |

|--------|-----|------|--------------------------------------------------------------------------------------------------------------------------------------|

| X2     | 0   | 8    | Crystal 2. See X1. An appropriate capacitor to Ground, whose value                                                                   |

|        |     |      | depends on the specified C <sub>L</sub> of the crystal, must be connected. For the                                                   |

|        |     |      | external clock source, this pin must be tied to Ground.                                                                              |

| HS     | ı   | 9    | Horizontal Sync. Horizontal synchronous signal input. The input level                                                                |

|        |     |      | is TTL compatible with internal 0.2V hysteresis. An internal 50K Ohm                                                                 |

|        |     |      | pull-up resistor is connected to this pin.                                                                                           |

| VS     | I   | 10   | Vertical Sync. Vertical synchronous signal input. The input level is                                                                 |

|        |     |      | TTL compatible with internal 0.2V hysteresis. An internal 50K Ohm                                                                    |

|        |     |      | pull-up resistor is connected to this pin.                                                                                           |

| CMDB   | I   | 11   | Command Interface Enabler. A low active pin which must be forced                                                                     |

|        |     |      | to low in excess of 16 cycles of DCK for 1 successful access of                                                                      |

|        |     |      | command interface. It has an internal 50K Ohm pull-up resistor.                                                                      |

| DCK    | l   | 12   | Command Interface Clock. This pin is used as the timing base for                                                                     |

|        |     |      | command interface. The address or data portion for the serial in (out)                                                               |

|        |     |      | of DIO is recognized by counting the number of DCKs. It has an                                                                       |

| DIO    | 1/0 | 40   | internal 50K Ohm pull-up resistor.                                                                                                   |

| DIO    | I/O | 13   | Command Interface Data. This pin is a bidirectional pin. A                                                                           |

|        |     |      | microprocessor can access any internal command registers through the protocol of the address portion followed by the succeeding data |

|        |     |      | portion. It must complete 16 full DCK cycles for a valid access.                                                                     |

| STOUT  | 0   | 14   | Self-Test Video Output. (for self-test mode) This pin is the video                                                                   |

| 31001  |     | 14   | output pin of the self-test pattern generator. The generator enabler,                                                                |

|        |     |      | pattern modes, output band selection and output enabler are                                                                          |

|        |     |      | programmed by <b>Reg16</b> .                                                                                                         |

| XDA4   | 0   | 15   | CMOS PWM D/A Converter 4. See DA0. The output pulse width can                                                                        |

| 712711 |     |      | be programmed by <b>Reg30</b> . It is a CMOS type output.                                                                            |

| XDA3   | 0   | 16   | CMOS PWM D/A Converter 3. See DA0. The output pulse width can                                                                        |

|        |     |      | be programmed by Reg29. It is a CMOS type output.                                                                                    |

| XDA2   | 0   | 17   | CMOS PWM D/A Converter 2. See DA0. The output pulse width can                                                                        |

|        |     |      | be programmed by Reg28. It is a CMOS type output.                                                                                    |

| XDA1   | 0   | 18   | CMOS PWM D/A Converter 1. See DA0. The output pulse width can                                                                        |

|        |     |      | be programmed by Reg27. It is a CMOS type output.                                                                                    |

| XDA0   | 0   | 19   | CMOS PWM D/A Converter 0. See DA0. The output pulse width can                                                                        |

|        |     |      | be programmed by <b>Reg26</b> . It is a CMOS type output.                                                                            |

| VDD    |     | 20   | Positive Power Supply. +5 volts. 2 decoupling capacitors, 0.1 uF and                                                                 |

|        |     |      | 100 uF, must be connected to VDD and Ground as close to the device                                                                   |

|        |     |      | as possible.                                                                                                                         |

# 3.0 FUNCTIONAL DESCRIPTION

## 3.1 Crystal Oscillator and Clock Generator

The crystal oscillator shall be connected to an 8MHz(or 4MHz) crystal. X1, as shown in Fig.1, can be used as an input source for the external clock or an output clock source to drive the external MCU. All timing specifications are based on the frequency of X1 (or X1 divided by 2).

## 3.2 PWM D/A Converter

There are 2 types of D/A converters with 8-bit resolution: open-drain type (DA0 to DA2) and CMOS type (XDA0 to XDA4). The sampling frequency is 31.25KHz or 15.625KHz, depending on the use of the crystal. The maximum external voltage applied is 12V for the open-drain type, and the output pulse width is programmable

for each converter by setting the corresponding register.

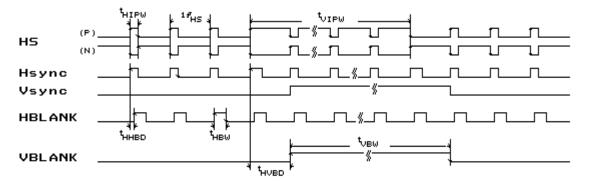

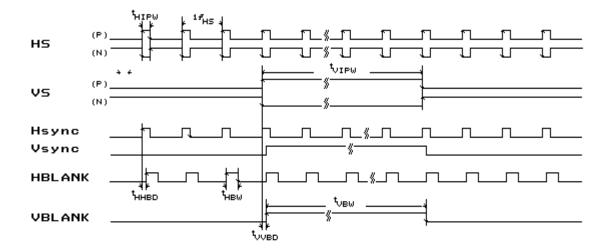

#### 3.3 SYNC Processor

The sync processor contains the following functions: polarity detection, presence detection, H-Freq counter, V-Freq counter and sync signal separation for input SYNC sources (HS and VS). It can be programmed to change the detected polarity status and output polarity of SYNC pins (HBLANK and VBLANK) by using the command interface. The timing diagrams of sync processing are shown as Fig. 2 in section 8.0. The internal SYNC signals (Hsync and Vsync) are extracted from different sources according to the following modes of operation.

|   | Mode           | VS          | HS          | Comment            |

|---|----------------|-------------|-------------|--------------------|

| 1 | Separate(H+V)  | present     | present     | HS = H or H/V sync |

| 2 | Composite(H/V) | not present | present     | HS= H/V sync       |

| 3 | Suspend        | present     | not present | -                  |

| 4 | Off            | not present | not present | -                  |

#### 3.4 H-Freq Table

After the "start H-Freq count" command is issued over 10 ms (for 15.7KHz) and HCFF(H-Freq Count Finished Flag) is set **High**, the H-Freq output (HF9 - HF0) is valid. The output value of H-Freq is calculated using the following formula:

output value =  $[(1/f_{Hfreq(KHz)}) \times 64 \times 4000] / 16$

|    | H-Freq(KHz) | Output value hexade | cimal 11 bits decimal | Tolerance (%)                       |  |

|----|-------------|---------------------|-----------------------|-------------------------------------|--|

| 1  | 15.7        | 3FB                 | 1019                  | 0.0981354                           |  |

| 2  | 18.7        | 357                 | 855                   | 0.1169591                           |  |

| 3  | 21.8        | 2DD                 | 733                   | 0.1364256                           |  |

| 4  | 30          | 215                 | 533                   | 0.1876172                           |  |

| 5  | 31.5        | 1FB                 | 507                   | 0.1972386                           |  |

| 6  | 33.5        | 1DD                 | 477                   | 0.2096436                           |  |

| 7  | 35.5        | 1C2                 | 450                   | 0.222222                            |  |

| 8  | 36.8        | 1B2                 | 434                   | 0.2304147                           |  |

| 9  | 38          | 1A5                 | 421                   | 0.2375297                           |  |

| 10 | 40          | 190                 | 400                   | 0.2500000                           |  |

| 11 | 48          | 14D                 | 333                   | 0.3003003                           |  |

| 12 | 50          | 140                 | 320                   | 0.3125000                           |  |

| 13 | 57          | 118                 | 280                   | 0.3571428<br>0.3759398<br>0.4000000 |  |

| 14 | 60          | 10A                 | 266                   |                                     |  |

| 15 | 64          | 0FA                 | 250                   |                                     |  |

| 16 | 100         | 0A0                 | 160                   | 0.6250000                           |  |

#### 3.5 V-Freq Table

After the "start V-Freq count" command is issued over 120 ms (for 50HZ) and VCFF (V-Freq Count Finish Flag) is set **High**, the V-Freq output (VF8 - VF0) is valid. The output value of V-Freq is calculated according to the following formula:

output value =  $[(4/f_{Vfreq(Hz)}) \times 4000000] / (64 \times 16)$

|    | V-Freq(Hz) | Output value hexade | cimal 9 bits decimal | Tolerance (%) |

|----|------------|---------------------|----------------------|---------------|

| 1  | 20         | 30D                 | 781                  | 0.12804       |

| 2  | 56.25      | 115                 | 277                  | 0.36101       |

| 3  | 59.94      | 104                 | 260                  | 0.38461       |

| 4  | 60         | 104                 | 260                  | 0.38461       |

| 5  | 60.32      | 103                 | 259                  | 0.38610       |

| 6  | 60.53      | 102                 | 258                  | 0.38759       |

| 7  | 66.67      | 0EA                 | 234                  | 0.42735       |

| 8  | 70.069     | 0DE                 | 222                  | 0.45045       |

| 9  | 70.08      | 0DE                 | 222                  | 0.45045       |

| 10 | 72         | 0D9                 | 217                  | 0.46082       |

| 11 | 72.378     | 0D7                 | 215                  | 0.46511       |

| 12 | 72.7       | 0D6                 | 214                  | 0.46728       |

| 13 | 87         | 0B3                 | 179                  | 0.55865       |

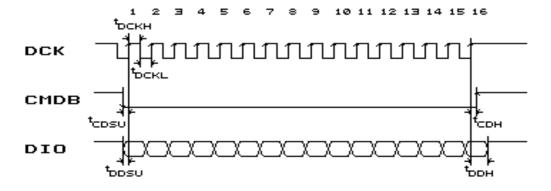

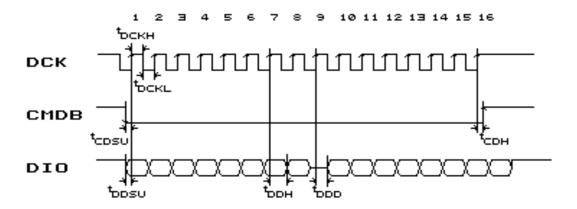

## 3.6 Command Interface

The command interface contains 3 pins. Each transfer of command is comprised of 16 DCK clock periods. The first 8 DCK clocks are for the address and direction of DIO, and the succeeding 8 DCK clocks are for the data. Each transfer is initiated by setting CMDB **Low**. The CMDB pin must be pulled **High** after data transfer is completed.

## - Command Format

B0 - 4 (ADD4 - 0) : Address of the registers.

B5 (W/RB) : Transfer direction, 1=write, 0=read.

B6 - 7 : Reserved.

B8 - 15 (*DA0 - 7*) : Data input when *W/RB*=1. (*DA7 - 0*) Data output when *W/RB*=0.

## - Register Allocation

## a. Read Transfer

|       | Address Portion |      | Data Portion     |           |       |       |                   |          |                 |     |

|-------|-----------------|------|------------------|-----------|-------|-------|-------------------|----------|-----------------|-----|

| Reg # | ADD4-0          | W/RB |                  | DA7 - 0   |       |       |                   |          |                 |     |

|       | B0 - 4          | B5   | B8               | В9        | B10   | B11   | B12               | B13      | B14             | B15 |

| Reg0  | 00000           | 0    | H <sub>pol</sub> | $V_{pol}$ | HSpre | VSpre | HV <sub>pre</sub> | $H_{SI}$ | V <sub>SI</sub> | Х   |

| Reg1  | 00001           | 0    | Х                | Х         | х     | Х     | HCFF              | HF10     | HF9             | HF8 |

| Reg2  | 00010           | 0    | HF7              | HF6       | HF5   | HF4   | HF3               | HF2      | HF1             | HF0 |

| Reg3  | 00011           | 0    | Х                | Х         | Х     | Х     | Х                 | Х        | VCFF            | VF8 |

| Reg4  | 00100           | 0    | VF7              | VF6       | VF5   | VF4   | VF3               | VF2      | VF1             | VF0 |

Table 4

## b. Write Transfer

|       | Address Portion |      |                  | Data Portion     |                  |                  |                  |                  |                   |     |

|-------|-----------------|------|------------------|------------------|------------------|------------------|------------------|------------------|-------------------|-----|

| Reg # | ADD4-0          | W/RB | DA0 - 7          |                  |                  |                  |                  |                  |                   |     |

|       | B0 - 4          | B5   | B8               | В9               | B10              | B11              | B12              | B13              | B14               | B15 |

| Reg0  | 00000           | 1    | х                | Х                | Х                | Х                | Х                | Х                | Х                 | Х   |

| Reg1  | 00001           | 1    | V <sub>pf0</sub> | V <sub>pf1</sub> | H <sub>pf0</sub> | H <sub>pf1</sub> | VB <sub>pl</sub> | HB <sub>pl</sub> | HV <sub>cvs</sub> | Х   |

| Reg2  | 00010           | 1    | Х                | Х                | Х                | Х                | Х                | Х                | Х                 | Х   |

| Reg3  | 00011           | 1    | CLK4M            | TEST             | Х                | Х                | Х                | Х                | Х                 | Х   |

| D 4   | 00400 |   | 1                 |                   |                   |                   |                   |                   |                   |                   |

|-------|-------|---|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|

| Reg4  | 00100 | 1 |                   | Reserved          |                   |                   |                   |                   |                   |                   |

| Reg5  | 00101 | 1 |                   |                   |                   | Res               | erved             |                   |                   |                   |

| Reg6  | 00110 | 1 | HBD0              | HBD1              | HBD2              | HBD3              | HBD4              | HBD5              | HBD6              | HBD7              |

| Reg7  | 00111 | 1 | HBW0              | HBW1              | HBW2              | HBW3              | HBW4              | HBW5              | HBW6              | HBW7              |

| Reg8  | 01000 | 1 |                   |                   |                   | Res               | erved             |                   |                   |                   |

| Reg9  | 01001 | 1 | VBW0              | VBW1              | VBW2              | VBW3              | VBW4              | VBW5              | х                 | VBW7              |

| Reg10 | 01010 | 1 | DA0 <sub>b0</sub> | DA0 <sub>b1</sub> | DA0 <sub>b2</sub> | DA0 <sub>b3</sub> | DA0 <sub>b4</sub> | DA0 <sub>b5</sub> | DA0 <sub>b6</sub> | DA0 <sub>b7</sub> |

| Reg11 | 01011 | 1 | DA1 <sub>b0</sub> | DA1 <sub>b1</sub> | DA1 <sub>b2</sub> | DA1 <sub>b3</sub> | DA1 <sub>b4</sub> | DA1 <sub>b5</sub> | DA1 <sub>b6</sub> | DA1 <sub>b7</sub> |

| Reg12 | 01100 | 1 | DA2 <sub>b0</sub> | DA2 <sub>b1</sub> | DA2 <sub>b2</sub> | DA2 <sub>b3</sub> | DA2 <sub>b4</sub> | DA2 <sub>b5</sub> | DA2 <sub>b6</sub> | DA2 <sub>b7</sub> |

| Reg13 | 01101 | 1 |                   |                   |                   | Res               | erved             |                   |                   |                   |

| Reg14 | 01110 | 1 |                   |                   |                   | Res               | erved             |                   |                   |                   |

| Reg15 | 01111 | 1 |                   |                   |                   |                   | erved             |                   |                   |                   |

| Reg16 | 10000 | 1 | STF               | RT0               | RT1               | ST <sub>bsh</sub> | Selft             | Х                 | Х                 | Х                 |

| Reg17 | 10001 | 1 | х                 | Х                 | х                 | Х                 | Х                 | Х                 | х                 | Х                 |

| Reg18 | 10010 |   |                   |                   |                   |                   |                   |                   |                   |                   |

| l l   | I     |   |                   |                   |                   | Res               | erved             |                   |                   |                   |

| Reg25 | 11001 |   |                   |                   |                   |                   |                   |                   |                   |                   |

| Reg26 | 11010 | 1 | XA0 <sub>b0</sub> | XA0 <sub>b1</sub> | XA0 <sub>b2</sub> | XA0 <sub>b3</sub> | XA0 <sub>b4</sub> | XA0 <sub>b5</sub> | XA0 <sub>b6</sub> | XA0 <sub>b7</sub> |

| Reg27 | 11011 | 1 | XA1 <sub>b0</sub> | XA1 <sub>b1</sub> | XA1 <sub>b2</sub> | XA1 <sub>b3</sub> | XA1 <sub>b4</sub> | XA1 <sub>b5</sub> | XA1 <sub>b6</sub> | XA1 <sub>b7</sub> |

| Reg28 | 11100 | 1 | XA2 <sub>b0</sub> | XA2 <sub>b1</sub> | XA2 <sub>b2</sub> | XA2 <sub>b3</sub> | XA2 <sub>b4</sub> | XA2 <sub>b5</sub> | XA2 <sub>b6</sub> | XA2 <sub>b7</sub> |

| Reg29 | 11101 | 1 | XA3 <sub>b0</sub> | XA3 <sub>b1</sub> | XA3 <sub>b2</sub> | XA3 <sub>b3</sub> | XA3 <sub>b4</sub> | XA3 <sub>b5</sub> | XA3 <sub>b6</sub> | XA3 <sub>b7</sub> |

| Reg30 | 11110 | 1 | XA4 <sub>b0</sub> | XA4 <sub>b1</sub> | XA4 <sub>b2</sub> | XA4 <sub>b3</sub> | XA4 <sub>b4</sub> | XA4 <sub>b5</sub> | XA4 <sub>b5</sub> | XA4 <sub>b7</sub> |

| Reg31 | 11111 | 1 |                   | •                 |                   | Res               | erved             |                   | •                 |                   |

<sup>\*</sup> The above x may represent any data.

#### - Command Descriptions

: Begins the H-Freq count. To read the value in the H-Freq registers, the write command (Reg0) Reg0 (write) needs to be issued first.

: The status of polarity, presence and static level for HS and VS. Reg0 (read)

> 1. Hpol, Vpol = 1 -> positive, = 0 -> negative.2. HSpre, VSpre, HVpre = 1 -> present, = 0 -> not present.  $= 0 \rightarrow low.$ = 1 -> high,3. H<sub>SI</sub>, V<sub>SI</sub>

\* HVpre represents the status of the composite (H/V) presence in HS. Hsl or Vsl is valid only when HSpre or VSpre is not present.

: Hfreq Count Finish flags, Hfreq high bit. Reg1 (read)

> 1. HCFF = 1 -> valid $= 0 \rightarrow not valid.$

2. HF10 - HF8 = 3 high bit of Hfreq.

: Selects the source of VBLANK and controls the polarity status of Hpol, Vpol Reg1 (write) and SYNC output polarity.

> 1. HVcvs = 1 -> VBLANK is extracted from HS.

= 0 -> VBLANK is extracted from VS.

2. HBpl = 1 -> negative HBLANK output, = 0 -> positive HBLANK output. 3. VBpI = 1 -> negative VBLANK output, = 0 -> positive VBLANK output.

\* After power-on, HBpJ and VBpJ shall be initialized to 0.

4. Hpf1, Hpf0 = 0.0 or 1.1 = x, by auto detection. -> Hpol

> = 0.1 $\rightarrow$  force Hpol = 1. = 1.0 $\rightarrow$  force H<sub>pol</sub> = 0.

5. Vpf1, Vpf0 = 0.0 or 1.1 -> Vpol = x, by auto detection.

# MYSON TECHNOLOGY

# MTV003N (MTV003)

```

= 0,1

-> force Vpol

= 1.

= 1.0

-> force Vpol

= 0.

Reg 2 (read)

: H-Freq low byte.

: Begins V-Freq count. To read the value in V-Freq registers, the write command (Reg2) must

Reg 2 (write)

be issued first.

Reg3 (read)

: V-Freq Count Finish flag, V-Freq high bit.

1. VCFF

= 1 -> valid,

= 0 -> not valid.

2. VF8

= the high bit of V-Freq.

Reg3 (write)

: Controls test and clock modes.

1. TEST

= 0

-> Normal mode.

-> Test mode, not allowed in applications.

= 1

2. CLK4M

= 0

-> CLK = X1 divided by 2 (for 8MHz crystal power-on [default]).

-> CLK = X1 (for 4MHz crystal power-on [default]).

= 1

Reg4 (read)

: V-Freq low byte.

Reg4 (write)

: Reserved.

Reg5 (write)

: Reserved.

Reg6 (write)

: Controls the delay of HBLANK output (7 bits).

(HBD7 - 0)

= 10000000

-> Directly bypasses Hsync to output.

= 01000000

-> Min. propagation delay (approximately 300ns).

= 00000000

-> T + 500ns.

= 00000001

-> 2T + 500ns.

-> 64T + 500ns.

= 00111111

Reg7 (write)

: Controls the width of HBLANK output (7 bits).

(HBW7 - 0)

= 10000000

-> Directly bypasses Hsync to output.

= 01000000

-> Min. width (approximately 300ns).

-> T + 500ns.

= 00000000

= 00000001

-> 2T + 500ns.

= 00111111

-> 64T + 500ns.

Reg8 (write)

: Reserved.

Reg9 (write)

: Controls the width of Vblank output (7 bits).

```

(VBW7 - 0)

= 1-000000 -> Directly bypasses Vsync to output. = 0-000000 -> Min. width (approximately 8us).

= 0-000001 -> 16 + 8(us).

= 0-1111111 -> 16 \* 63 + 8(us) = 1.016ms.

**Reg10** (write) : Output pulse width control for DA0.

**Reg11** (write) : Output pulse width control for DA1.

**Reg12** (write) : Output pulse width control for DA2.

Reg13 (write) : Reserved.

Reg14 (write) : Reserved.

Reg15 (write) : Reserved.

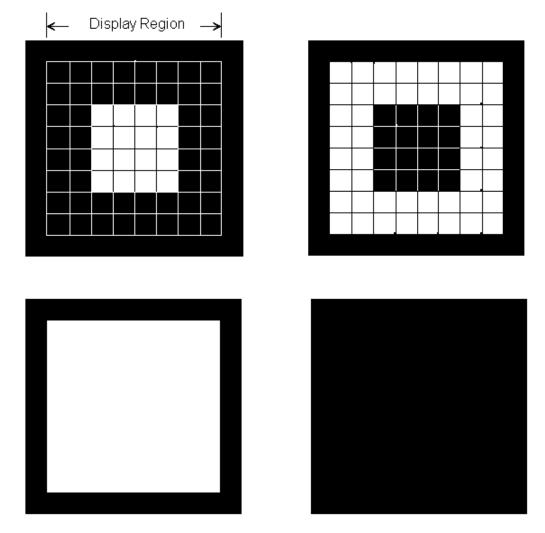

Reg16 (write) : Controls i) enabler, ii) band selection, iii) 4 pattern modes and iv) output enabler

for the self-test pattern generator.

1. Selft = 1 -> Enables generator. = 0 -> Disables generator.

2. STbsh = 1 -> 63.5KHz (horizontal) output selected. = 0 -> 31.75 KHz (horizontal) output selected.

3. RT1, RT0 = 0,0 -> Positive cross-hatch pattern output. = 0,1 -> Negative cross-hatch pattern output.

= 1,0 -> Full white pattern output.= 1,1 -> Full black pattern output.

4. STF= 1 -> Enables STOUT output. -> Disables STOUT output.

Reg17 (write) : Reinitializes all internal registers.

**Reg26** (write) : Output pulse width control for XDA0.

**Reg27** (write) : Output pulse width control for XDA1.

**Reg28** (write) : Output pulse width control for XDA2.

**Reg29** (write) : Output pulse width control for XDA3.

**Reg30** (write) : Output pulse width control for XDA4.

Reg31 (write) : Reserved.

- 2. All D/A converters are centered with a value of **DA7 0**= 10000000, and other registers are initialized with **low** after power-on or a **Reg17** write.

- 3. The duration of power-on initialization is 200ms and **Reg17** write reinitiation is 2.5ms. No register access is allowed during initialization.

<sup>\*1.</sup> The above T = 250ns.

## 4.0 ABSOLUTE MAXIMUM RATINGS

DC Supply Voltage (VDD) -0.3 to 7 V

Voltage with respect to Ground:

All pins except VDD and DA0 to DA2 -0.3 to VDD+ 0.3 V DA0 to DA2 -0.3 to +13.2 V -0.3 to +150  $^{\rm O}$ C Ambient Operating Temperature -65 to +150  $^{\rm O}$ C

## **5.0 OPERATING CONDITIONS**

DC Supply Voltage (VDD) +4.75 V to +5.25 V External D/A Power Supply +5 V to 12 V Operating Temperature 0 to +70 °C

## **6.0 ELECTRICAL CHARACTERISTICS** (Under Operating Conditions)

| Symbol | Parameter                             | Conditions (Notes)                                                                                        | Min.    | Max.        | Unit |

|--------|---------------------------------------|-----------------------------------------------------------------------------------------------------------|---------|-------------|------|

| VIH    | Input High Voltage                    | -<br>(for all input pins)                                                                                 | 2.4     | VDD+<br>0.3 | V    |

| VIL    | Input Low Voltage                     | -<br>(for all input pins)                                                                                 | VSS-0.3 | 0.8         | V    |

| Vон    | Output High Voltage                   | I <sub>OH</sub> = -500 uA<br>(for pins of HBLANK,<br>VBLANK, DIO, Bout, STOUT,<br>XDA4-0)                 | 3.0     | -           | V    |

| VOL    | Output Low Voltage                    | I <sub>OL</sub> = 4 mA<br>(see VOH)                                                                       | -       | 0.5         | V    |

| VDAOL  | Open-Drain D/A Output Low Voltage     | IDAOL = 3 mA<br>(for pins of DA2-0)                                                                       | -       | 0.35        | V    |

| VDAOH  | Open-Drain D/A<br>Output High Voltage | (for pins of DA2-0, pulled up<br>by external 5 to 12V power<br>supply)                                    | 5       | 12          | V    |

| Icc    | Maximum Quiescent<br>Supply Current   | Vin = VDD,<br>lout = 0 uA.<br>(all input pins connected to<br>VDD, all output pins without<br>connection) | -       | 20          | mA   |

# **7.0 SWITCHING CHARACTERISTICS** (Under Operating Conditions and X1=8MHz)

| Symbol            | Parameter                                                                    | Min. | Тур.        | Max.     | Unit |

|-------------------|------------------------------------------------------------------------------|------|-------------|----------|------|

| f <sub>DAO</sub>  | D/A Converter Output Frequency                                               | -    | 31.25       | -        | KHz  |

| fXTAL             | Crystal Frequency                                                            | -    | 8           | -        | MHz  |

| fHS               | HS Input Frequency                                                           | 15   | -           | 100      | KHz  |

| fys               | VS Input Frequency                                                           | 20   | -           | 100      | Hz   |

| tHIPW             | HS Input Pulse Width                                                         | 0.5  | -           | 6.5      | us   |

| tVIPW             | VS Input Pulse Width                                                         | 25   | -           | 2000     | us   |

|                   | HSYNC (Rise) to HBLANK<br>Output Delay<br>(programmed by <b>Reg6</b> )       | 300  | (N+1)xT+500 | 64xT+850 | ns   |

| tHHBD             | HSYNC (Rise) to HBLANK Output Delay (bypass HSYNC to HBLANK Output directly) | -    | -           | 50       | ns   |

|                   | HBLANK Output Width (programmed by <b>Reg7</b> )                             | 300  | (N+1)xT+500 | 64xT+850 | ns   |

| <sup>t</sup> HBW  | HBLANK Output Width (bypass HSYNC to HBLANK Output directly)                 | 0.5  | -           | 7        | us   |

| tHHBJ             | HSYNC to HBLANK Output Jitter                                                | -    | -           | (+/-) 25 | ns   |

|                   | VBLANK Output Width (programmed by <b>Reg9</b> )                             | 16   | (Nx16)+8    | 1016     | us   |

| t/BW              | VBLANK Output Width<br>(bypass VSVNC to VBLANK<br>Output directly)           | 25   | -           | 2000     | us   |

| <sup>t</sup> HVBD | HSYNC to VBLANK Output<br>Delay<br>(H/V mode)                                | -    | 1 H-line    | -        | -    |

| tVVBD             | VS to VBLANK Output Delay (H+V mode)                                         | -    | -           | 50       | ns   |

| tVVBJ             | VSYNC to VBLANK Output Jitter(H+V mode)                                      | -    | -           | (+/-) 25 | ns   |

| <sup>t</sup> HVBJ | HSYNC to VBLANK Output<br>Jitter (H/V mode)                                  | -    | -           | (+/-) 25 | ns   |

| tCDSU             | CMDB to DCK Setup Time                                                       | 200  | -           | -        | ns   |

| tCDH              | CMDB to DCK Hold Time                                                        | 100  | -           | -        | ns   |

| <sup>t</sup> DDSU | DIO to DCK Setup<br>Time (write)                                             | 200  | -           | -        | ns   |

| <sup>t</sup> DDH  | DIO to DCK Hold Time(write)                                                  | 100  | -           | -        | ns   |

| <sup>t</sup> DCKH | DCK High Time                                                                | 200  | -           | -        | ns   |

| <sup>t</sup> DCKL | DCK Low Time                                                                 | 200  | -           | -        | ns   |

| $T_{DDD}$         | DCK to DIO Delay Time(read)                                                  | 100  | -           | -        | ns   |

<sup>\* 1.</sup> The above HSYNC is extracted from HS input and VSYNC is extracted from VS, HS input.

<sup>\* 2.</sup> T = 250ns (1/4MHz) is fixed regardless of whether or not an 8(or 4)MHz crystal is used.

<sup>\* 3.</sup>  $0 \le N \le 63$

## 8.0 TIMING DIAGRAMS

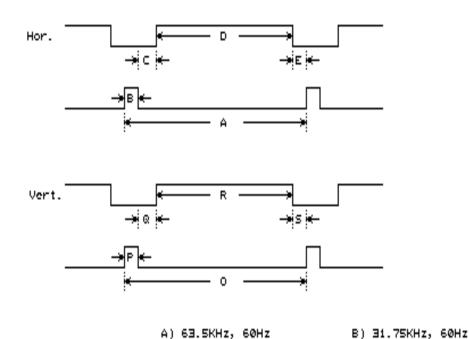

Figure 2. H/V Mode Timing

Figure 3. H+V Mode Timing

Figure 4. Command Interface Write Timing.

Figure 5. Command Interface Read Timing.

Figure 6. 4 Self-Test Patterns

#### MTV003 SELF TEST PATTERN TIMING.

|     |                   | (Absolute time) | (H dots)  | (Absolute time) | (H dots)  |

|-----|-------------------|-----------------|-----------|-----------------|-----------|

| i.  | Hor. total time   | us(A)=15.75     | 1280      | us(A) =31.5     | 640       |

| 2.  | Hor. active time  | us(D)=12.05     | 979.3     | us(D) =24.05    | 488.6     |

| Э.  | Hor. F.P.         | us(E)=0.2       | 16.25     | us(E) =0.45     | 9         |

| 4.  | SYNC pulse width  | us(B)=1.5       | 122       | us(B) =3        | 61        |

| 5.  | Hor. B.P.         | us(C)=2         | 162.54    | us(C) =4        | 81.27     |

|     |                   |                 | (V lines) |                 | (V lines) |

| 6.  | Vert. total time  | ms(0)=16.6635   | 1024      | ms(O)=16.6635   | 480       |

| 7.  | Vent. active time | : ms(R)=15.6555 | 962       | ms(R)=15.6555   | 451       |

| 8.  | Vert. F.P.        | ms(S)=0.063     | 3.87      | ms(S)=0.063     | 1.82      |

| 9.  | SYNC pulse width  | ms(P)=0.063     | 3.87      | ms(P)=0.063     | 1.82      |

| 10. | Vert. B.P.        | ms(Q)=0.882     | 54.2      | ms(Q)=0.882     | 25.4      |

|     |                   |                 |           |                 |           |

₩ 8 x 8 blocks of cross hatch pattern in display region.

Figure 7. Self-Test Timing