# LAN83C171 ADVANCE INFORMATION

# LAN83C171 - EPIC/XF ACPI/PC 97 Compliant Integrated PCI 10/100 Mbps Fast Ethernet Controller

#### **FEATURES**

- IEEE 802.3 Compatible 10/100 Mbps Fast Ethernet Controller

- Fully Compliant Glueless PCI Version 2.1 Bus Interface

- Support Included for CardBus Status Registers

- PCI Universal 3V/5V Output Drives

- Preemptive Interrupt Support for Efficient Network Packet Processing

- High Performance Two Channel Bus Master (132 Mbps)

- Scatter/Gather DMA Capability

- Programmable Burst Length Counter

- ACPI Compliant for

- PCI Bus Class Specification

- Network Device Class Specification

- PC 97 Compliant

- Wake-Up on Magic Packet<sup>™</sup> Detection and/or Network Link-Down Occurrence

- Special Low Power State Mode For Scanning Magic Packets<sup>™</sup> Upon PCI Bus Power Loss

- Supports Chaining of Transmit Packets

- Optional Early Transmit and Early Receive

- Optional Receive Lookahead Buffering Mode

- Automatic Rejection of Runt Packets

- Automatic Retransmission of Collision Frames from Internal Buffer

- Automatic Padding of Short Frames

- 4.5 Kbyte On-Chip Receive Buffer and 1.5 Kbyte On-Chip Transmit Buffer Eliminate Bus Latency Issues

- Optional Variable Depth, 32 Bit Wide External Receive Buffer (0, 16, 32 or 128 Kbytes)

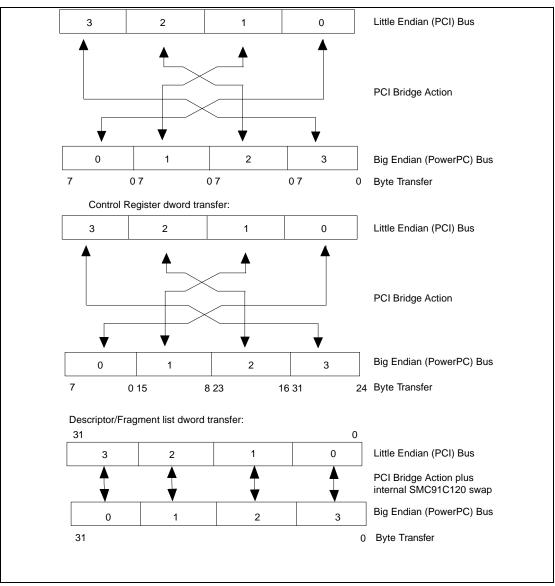

- Big or Little Endian Byte Ordering

- Capable of Supporting 64 Kbyte Expansion Boot Flash RAM

- IEEE Standard MII Interface to Physical Laver

- Interface to LAN83C694 Shares MII Pins

- Serial MII Management Interface

- Serial EEPROM Interface for Storage of LAN Address and Configuration Information

- On-Chip Clock Multiplier

- Low Power Sleep Mode

- Support for Full Duplex Ethernet

- Internal and External Loopback Diagnostic Functions

- Simple I/O Pin Mapping Scheme to Facilitate In-Circuit Test

- Single 5V Power Supply

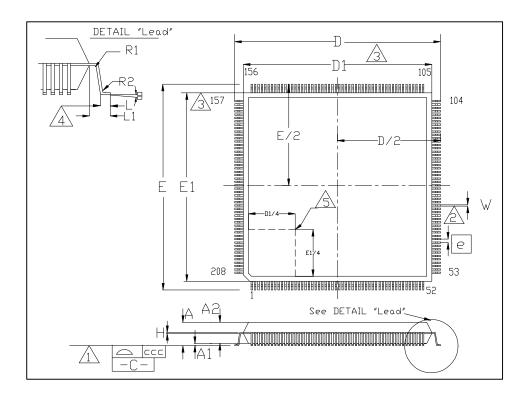

- 208 Pin QFP Package

- Software Drivers to Operate with Major Operating Systems, Including:

- NDIS 3.4 and 5 for Microsoft

- DOS ODI for Novell

#### **GENERAL DESCRIPTION**

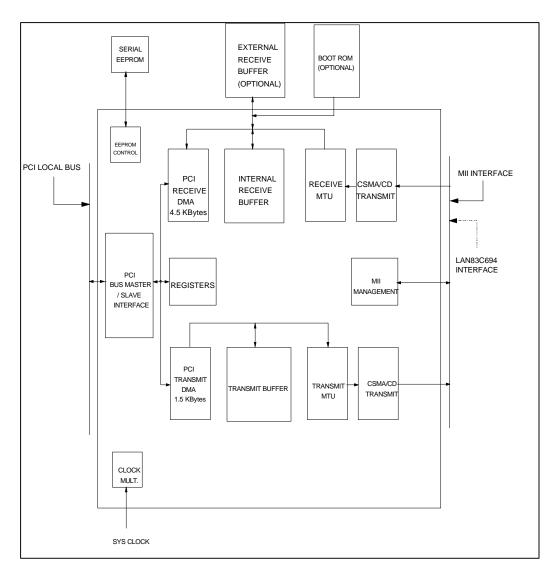

The LAN83C171 EPIC/XF is a high-performance and a low CPU utilization Ethernet network controller designed to interface directly to the PCI Local Bus on one side and to the 802.3 standard Media Independent Interface (MII) on the other side. The network interface can also be configured to communicate directly with the LAN83C694 10BASE-T transceiver.

The LAN83C171 implements 802.3 Media Access Control functions. It is capable of running at Ethernet rates of both 100Mb/s and

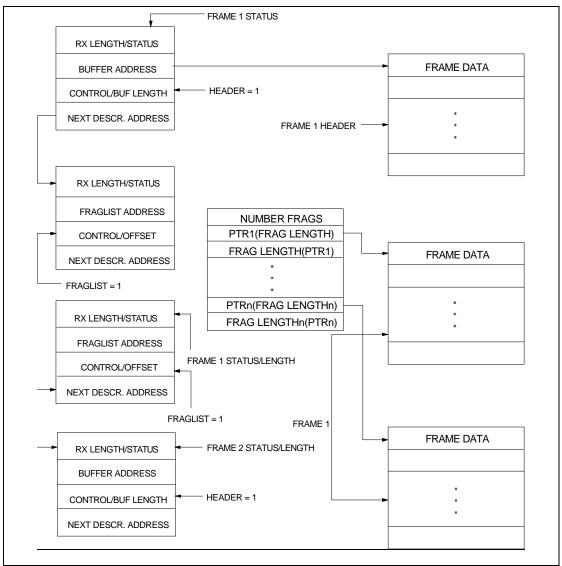

10Mb/s. An MII compliant serial management interface is provided to control external media dependent transceivers. The LAN83C171 is a two channel bus master (one for transmit, one for receive) capable of transferring data at the maximum PCI transfer rate of 132Mbps. The LAN83C171 has several features designed to minimize CPU utilization, including the optional Receive Lookahead Buffering Mode, which eliminates the need to re-copy the data from one host memory location to another.

# **TABLE OF CONTENTS**

| FEATURES                                                  |     |

|-----------------------------------------------------------|-----|

| GENERAL DESCRIPTION                                       |     |

| PIN CONFIGURATION                                         | 5   |

| DESCRIPTION OF PIN FUNCTIONS                              | 6   |

| FUNCTIONAL DESCRIPTION                                    |     |

| PCI INTERFACE                                             | .12 |

| TRANSMIT/RECEIVE ARBITRATION FOR PCI BUS                  | .12 |

| SYSTEM ERRORS                                             | .12 |

| BIG/LITTLE ENDIAN SUPPORT                                 | .12 |

| POWER DOWN MODE                                           |     |

| DMA OPERATION                                             |     |

| TRANSMIT DMA                                              |     |

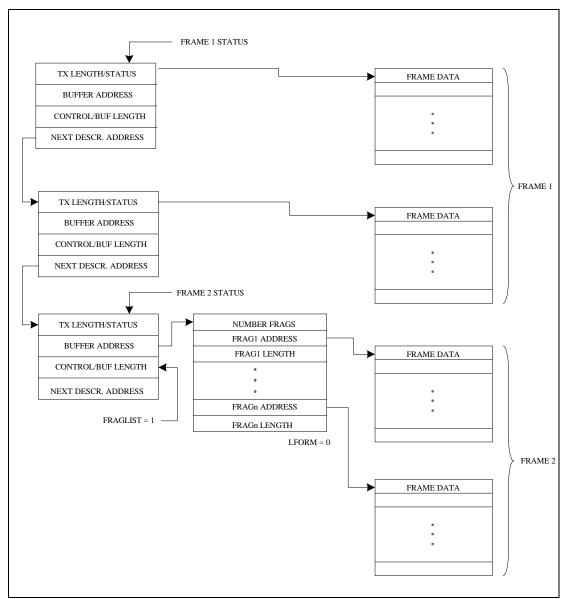

| Direct Queuing Method                                     | .14 |

| Fragment List Method                                      | .16 |

| Interrupting Transmit Chain                               | .18 |

| Transmit Buffer Full                                      |     |

| Transmit Underrun                                         | .18 |

| Exception to Underrun ReTransmission                      | .18 |

| Maximum Transmit Size and Burst Rate                      | .18 |

| RECEIVE DMA                                               | .19 |

| Free Buffer Pool Method                                   |     |

| Adding Receive Buffers to the Pool                        |     |

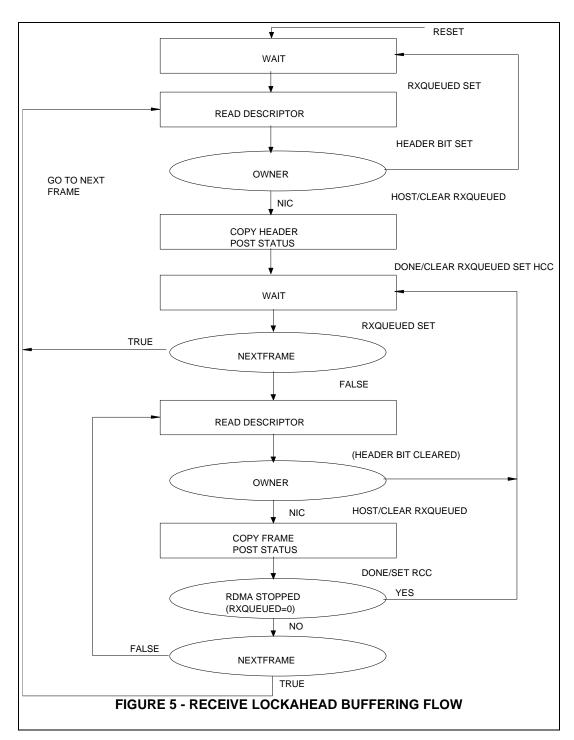

| Receive Lookahead Method                                  |     |

| Stopping the Receive DMA                                  | .25 |

| Maximum Receive Size and Burst Rate                       | .25 |

| MAC OPERATION                                             | .26 |

| MII MANAGEMENT INTERFACE                                  | .32 |

| EEPROM INTERFACE                                          | .32 |

| JUMPER OPTIONS (EEPROM/RAM)                               | .33 |

| Advanced Configuration and Power Interface (ACPI) Support | .33 |

| Wake-Up Events and Notification                           |     |

| EPIC Power States                                         | .34 |

| D3(Cold1) Software Driver Requirements                    | .35 |

| Supporting Power Management Options                       | .35 |

| PME Generates a PCI Bus Interrupt                         | .35 |

| Initial Power-On Reset (POR)                              | .35 |

| Special Power Management Mode                             | .36 |

| POWER DOWN MODE                                           |     |

| SOFT RESET                                                |     |

| CONFIGURATION                                             |     |

| Mapping of Control Functions                              |     |

| Mapping of Flash RAM Functions                            | .37 |

| DMA DESCRIPTOR BITS DESCRIPTION                           | .39 |

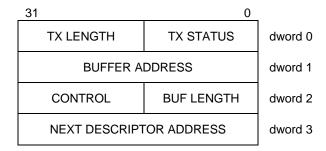

| TRANSMIT DMA DESCRIPTOR BITS DESCRIPTION                  |     |

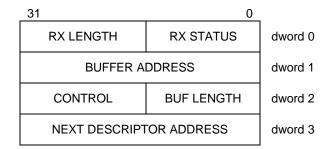

| RECEIVE DMA DESCRIPTOR BITS DESCRIPTION                   |     |

|                                                           |     |

| CONTROL REGISTER MAP/REGISTERS DECODE                     | .43 |

| CONTROL REGISTERS BITS DESCRIPTION           | 45 |

|----------------------------------------------|----|

| PCI CONFIGURATION REGISTERS BITS DESCRIPTION | 64 |

| OPERATIONAL DESCRIPTION                      | 70 |

| Maximum Guaranteed Ratings                   | 70 |

| DC Electrical Characteristics                |    |

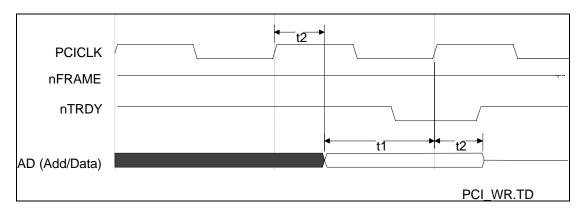

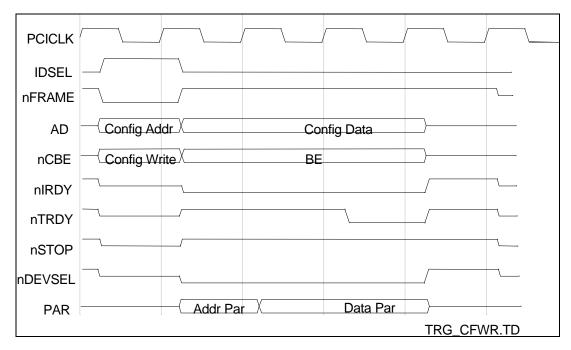

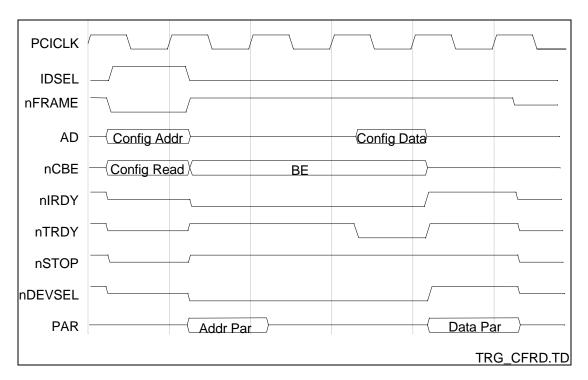

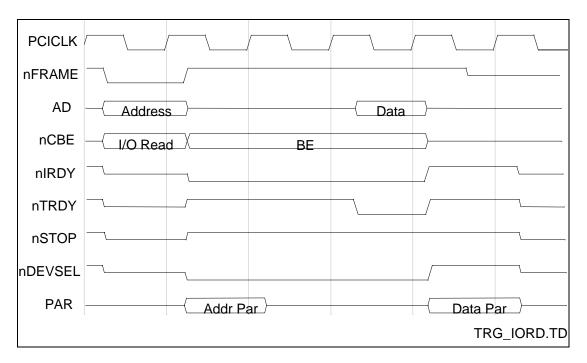

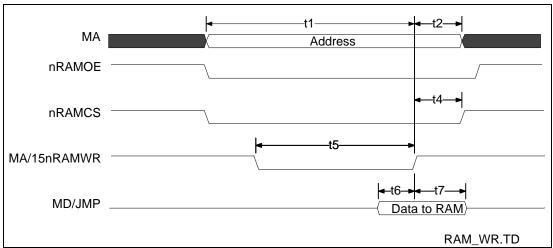

| TIMING DIAGRAMS                              | 72 |

|                                              |    |

80 Arkay Drive Hauppauge, NY 11788 (516) 435-6000 FAX (516) 273-3123

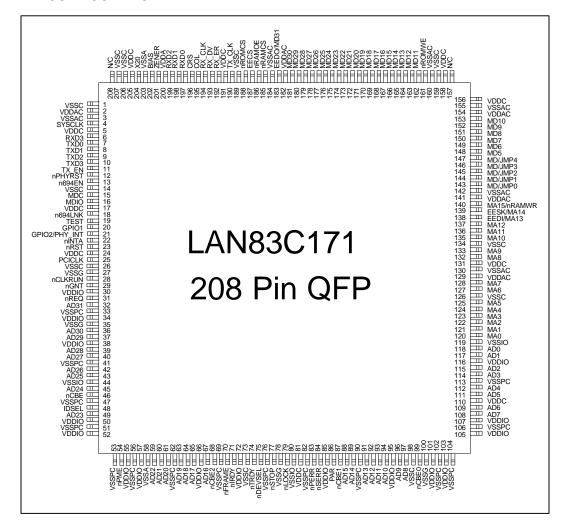

#### PIN CONFIGURATION

# **DESCRIPTION OF PIN FUNCTIONS**

| DESCRIPTION OF PIN FUNCTIONS |         |      |                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |

|------------------------------|---------|------|---------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| PQFP PIN NO.                 | NAME    | I/O  | TYPE                | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |  |

| PCI INTERFACE                |         |      |                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |

| 25                           | PCICLK  | I    | I <sub>PCLK</sub> , | PCI Clock                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |  |

|                              |         |      | dc_lk1              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |

| 23                           | nRST    | I    | I <sub>PCI</sub> ,  | PCI System Reset                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |  |

|                              |         |      | dc_lk1              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |

| 32,36,37,39,40,42,           | AD      | I/O  | IO <sub>PCI</sub> , | PCI Multiplexed Address/Data Bus                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |  |

| 43,45,49,59-61,              |         |      | dc_lk2              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |

| 63-65,67,88,89,              |         |      |                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |

| 91-94,96,97,108,             |         |      |                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |

| 109,111,112,114,             |         |      |                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |

| 115,117,118                  |         |      |                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |

| 46,68,87,99                  | nCBE    | I/O  | IO <sub>PCI</sub> , | PCI Multiplexed Command/Byte                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |  |

|                              |         |      | dc_lk2              | Enable Signals                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |  |

| 86                           | PAR     | I/O  | IO <sub>PCI</sub> , | PCI Parity Signal                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |  |

|                              | .,      | ., 0 | dc_lk2              | l or r array original                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |  |

| 70                           | nFRAME  | I/O  | IO <sub>PCI</sub> , | PCI Cycle Frame Signal                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |  |

|                              |         |      | dc_lk2              | See System States                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |  |

| 71                           | nIRDY   | I/O  | IO <sub>PCI</sub> , | PCI Initiator Ready Signal                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |  |

|                              |         |      | dc_lk2              | l statement to the state of the |  |

| 74                           | nTRDY   | I/O  | IO <sub>PCI</sub> , | PCI Target Ready Signal                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |  |

|                              |         |      | dc_lk2              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |

| 77                           | nSTOP   | I/O  | IO <sub>PCI</sub> , | PCI Cycle Stop Signal                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |  |

|                              |         |      | dc_lk2              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |

| 79                           | nLOCK   | ı    | IO <sub>PCI</sub> , | PCI Lock Signal                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |

|                              |         |      | dc_lk2              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |

| 48                           | IDSEL   | - 1  | I <sub>PCI</sub> ,  | PCI Initiation Device Select Signal.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |  |

|                              |         |      | dc_lk1              | Used as a Chip Select for                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |  |

|                              |         |      |                     | Configuration Reads and Writes                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |  |

| 75                           | nDEVSEL | I/O  | IO <sub>PCI</sub> , | PCI Device Select                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |  |

|                              |         | "    | dc_lk2              | . 5. 55,105 50,000                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |  |

| 31                           | nREQ    | 0    | O <sub>PCI</sub> ,  | PCI Bus Request                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |

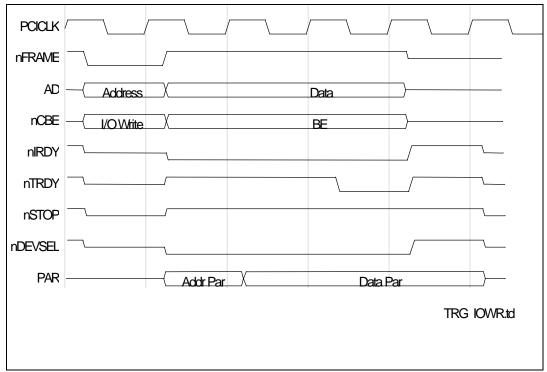

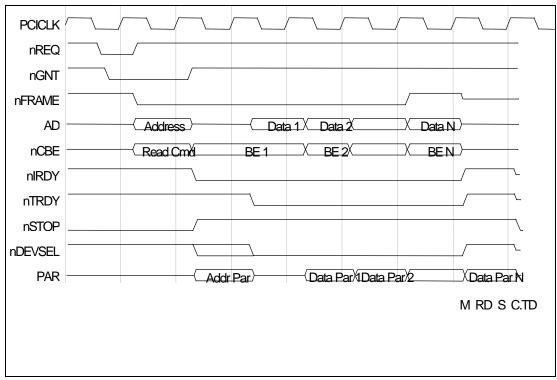

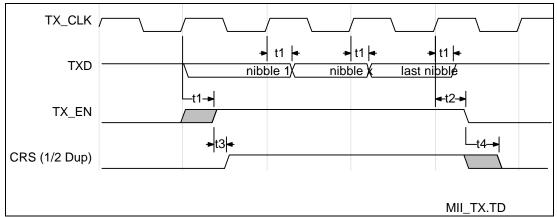

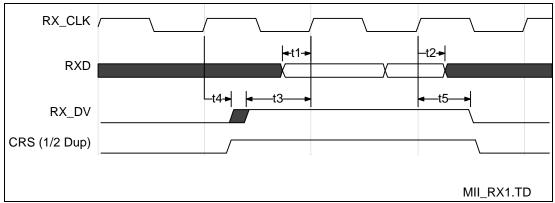

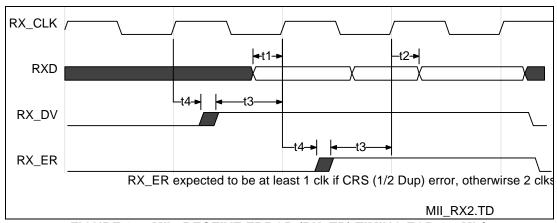

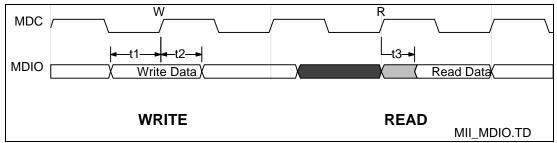

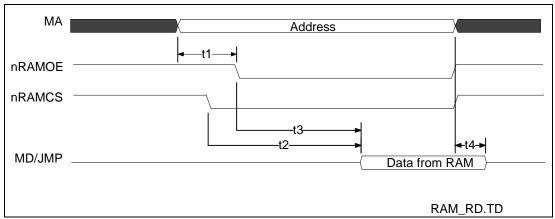

|                              |         |      | dc_lk2              | 111111111111111111111111111111111111111                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |  |