# **COM90C66**

Data Sheet with Erratas for Rev. B and Rev. D devices

# ARCNET® Controller/Transceiver with AT® Interface and On-Chip RAM

#### **FEATURES**

- ARCNET LAN Controller/Transceiver/ Support Logic/Dual-Port RAM

- Integrates SMSC COM90C65 with 16-Bit Data Bus, Dual-Port RAM, and Enhanced Diagnostics Circuitry

- Includes IBM® PC/AT® Bus Interface Circuitry

- Supports 8- and 16-Bit Data Buses

- Full 2K x 8 On-Chip Dual-Port Buffer RAM

- Zero Wait State Arbitration for Most AT Buses

- SMSC COM90C26 Software Compatible

- Command Chaining Enhances Performance

- Supports Memory Mapped and Sequential I/O Mapped Access to the Internal RAM Buffer

- Compatible with the SMSC HYC9058/68/ 88 (COAX and Twisted Pair Drivers)

- Token Passing Protocol with Self Reconfiguration Detection

- Variable Data Length Packets

- 16 Bits CRC Check/Generation

- Includes Address Decoding Circuitry for On-Chip RAM, PROM and I/O

- Supports up to 255 Nodes

- Contains Software Accessible Node ID Register

- Compatible with Various Topologies (Star, Tree, Bus, ...)

- On-Board Crystal Oscillator and Reset Circuitry

- Low Power CMOS, Single +5V Supply

# **GENERAL DESCRIPTION**

The SMSC COM90C66 is a special purpose communications controller for interconnecting processors and intelligent peripherals using the ARCNET Local Area Network. The COM90C66 is unique in that it integrates the core ARCNET logic found in Standard Microsystems' original COM90C26 and COM90C32 with an on-chip 2K x 8 RAM, as well as the 16-bit data bus interface for the IBM PC/AT. Because of the inclusion of the RAM buffer in the COM90C66, a complete ARCNET node can be implemented with only one or two additional ICs (8- or 16-bit applications, respectively) and a media driver circuit. The ARCNET core remains functionally untouched. eliminating validation compatibility concerns. The enhancements exist in the integration and the performance of the

device. Maximum integration has been achieved by including the 2K x 8 RAM buffer on the chip, providing the immediate benefits of a lower device pin count and less board components. The performance is enhanced in four ways: a 16-bit data bus for operation with the IBM PC/AT; a zero wait state arbitration mechanism, due partly to the integration of the RAM buffer onchip; the ability of the device to do consecutive transmissions and receptions via the Command Chaining operation; and improved diagnostics, allowing the user to control the system more efficiently. For most AT compatibles, the device handles zero wait state transfers.

ARCNET is a registered trademark of Datapoint Corporation IBM, AT, PC/AT and Micro Channel are registered trademarks of International Business Machines Corporation

#### **TABLE OF CONTENTS**

| FEATURES                              | 1  |

|---------------------------------------|----|

| GENERAL DESCRIPTION                   | 1  |

| PIN CONFIGURATION                     | 3  |

| DESCRIPTION OF PIN FUNCTIONS          | 4  |

| PROTOCOL DESCRIPTION                  | 9  |

| NETWORK PROTOCOL                      | 9  |

| NETWORK RECONFIGURATION               | 9  |

| BROADCAST MESSAGES                    | 10 |

| EXTENDED TIMEOUT FUNCTION             |    |

| LINE PROTOCOL                         | 10 |

| SYSTEM DESCRIPTION                    | 12 |

| MICROPROCESSOR INTERFACE              | 12 |

| TRANSMISSION MEDIA INTERFACE          |    |

| FUNCTIONAL DESCRIPTION                | 13 |

| MICROSEQUENCER                        | 13 |

| ADDRESS DECODING                      | 19 |

| INTERNAL REGISTERS                    |    |

| INTERNAL RAM                          |    |

| SOFTWARE INTERFACE                    | 29 |

| SOFTWARE COMPATIBILITY CONSIDERATIONS | 31 |

| COMMAND CHAINING                      | 32 |

| RESET DETAILS                         |    |

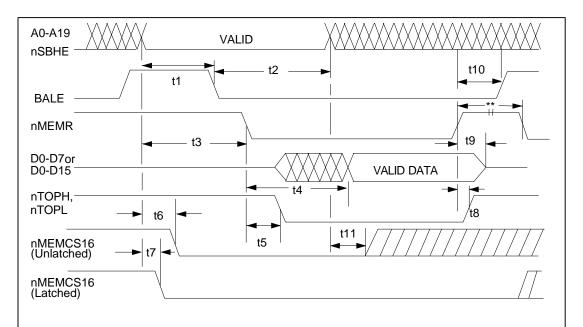

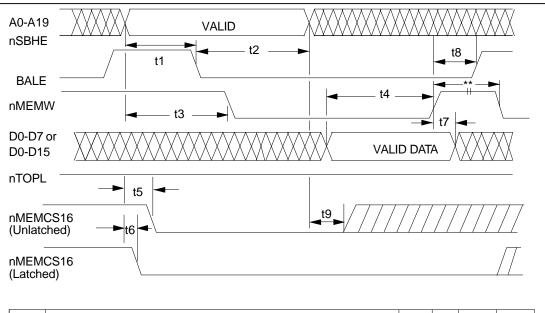

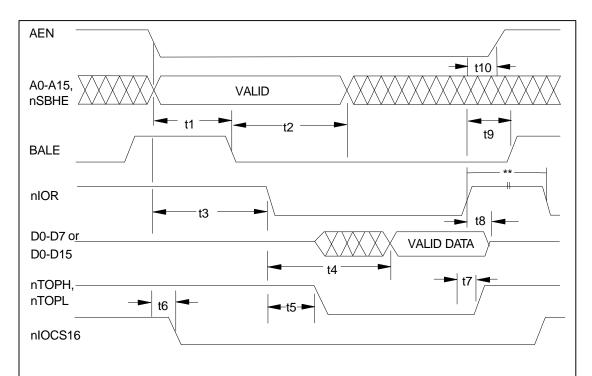

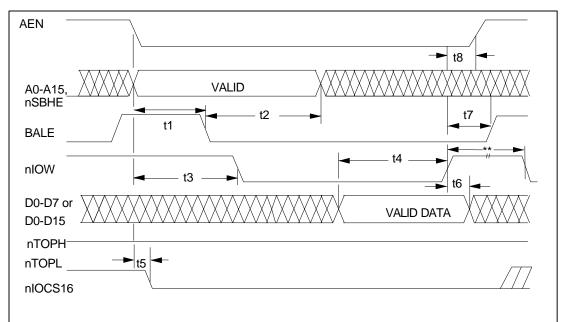

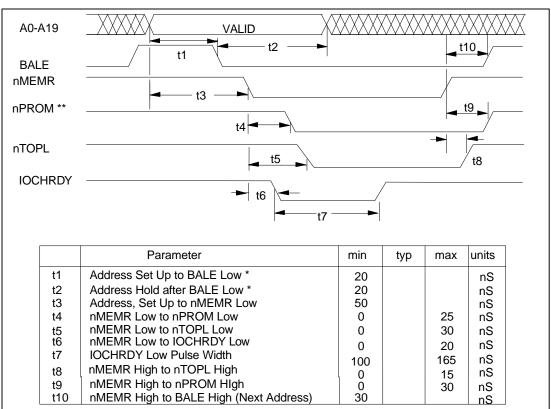

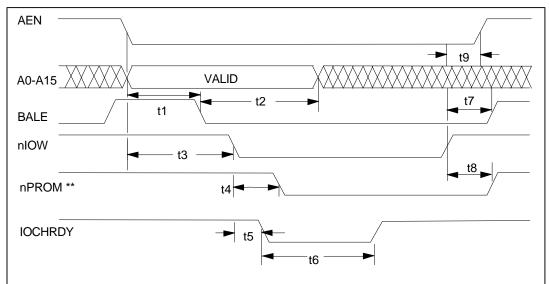

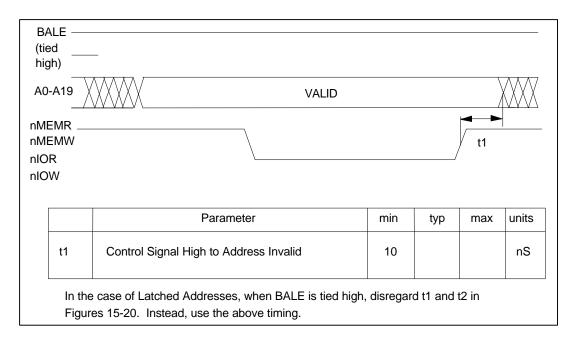

| READ AND WRITE CYCLES                 |    |

| NODE ID LOGIC                         |    |

| TRANSMIT/RECEIVE LOGIC                |    |

| IMPROVED DIAGNOSTICSOSCILLATOR        |    |

|                                       |    |

| OPERATIONAL DESCRIPTION               | 46 |

| MAXIMUM GUARANTEED RATINGS            |    |

| DC CHARACTERISTICS                    | 46 |

| TIMING DIAGRAMS                       | 49 |

Please see Addendum 1 entitled <u>Data Sheet Errata for Revision B COM90C66</u>, which discusses changes to this data sheet which apply to the Revision B device, on Page 62.

Please see Addendum 2 entitled <u>Data Sheet Errata for Revision D COM90C66</u>, which discusses changes to this data sheet which apply to the Revision D device, on Page 64.

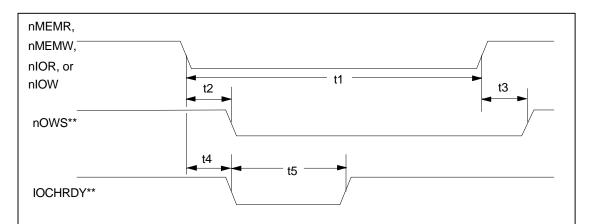

80 Arkay Drive Hauppauge, NY 11788 (516) 435-6000 FAX (516) 273-3123 For other machines, the IOCHRDY signal may be briefly negated to give the device the extra time necessary to support the faster machines. Aside from the implementation of a 16-bit data bus interface, the remaining bus interface logic is identical to that found in the SMSC COM90C65, which contains all the support logic circuitry.

The ARCNET Local Area Network is a token passing network which operates at a 2.5 Mbps data rate. A token passing protocol provides predictable response times because each network event occurs within a known time interval. Throughput can be reliably predeter-

mined based upon the number of nodes and their expected traffic.

The COM90C66 establishes the network configuration and automatically reconfigures the token passing order as new nodes are added or deleted from the network.

The COM90C66 performs address recognition, CRC checking and generation, packet acknowledgement, and other network management functions. The C0M90C66 interfaces directly to the IBM PC/AT or compatibles. The internal 2K x 8 RAM buffer is used to hold up to four data packets with a maximum length of 508 bytes each.

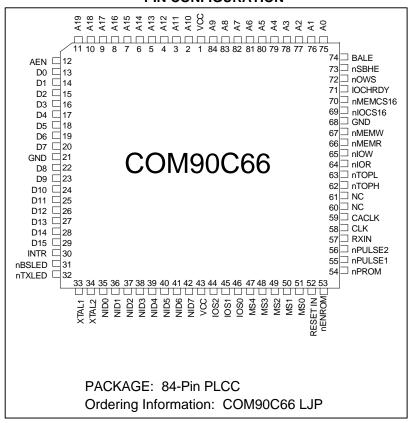

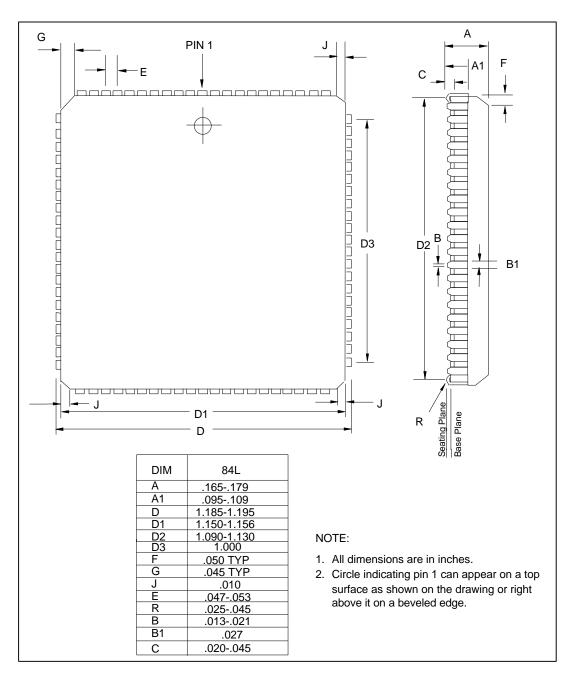

#### **PIN CONFIGURATION**

|                 | I                                    | 1               | <u> </u>                                                                                                                                                                                                                                                                       |  |  |  |  |  |  |  |  |

|-----------------|--------------------------------------|-----------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|--|--|

| PLCC<br>PIN NO. | NAME                                 | SYMBOL          | DESCRIPTION                                                                                                                                                                                                                                                                    |  |  |  |  |  |  |  |  |

|                 | PROCESSOR INTERFACE                  |                 |                                                                                                                                                                                                                                                                                |  |  |  |  |  |  |  |  |

| 75-84, 2-<br>11 | Address 0-19                         | A0-A19          | Input. These signals are connected to the address lines of the host processor and are used to access memory and I/O locations of the COM90C66, as well as to access the external ROM through the COM90C66.                                                                     |  |  |  |  |  |  |  |  |

| 13-20,<br>22-29 | Data 0-15                            | D0-D15          | Input/Output. These signals are used by the host to transmit data to and from the internal registers and buffer memory of the COM90C66 and are connected to weak internal pull-up resistors.                                                                                   |  |  |  |  |  |  |  |  |

| 63, 62          | nTransceiver<br>Direction<br>Control | nTOPL,<br>nTOPH | Output. These active low signals control the data bus transceiver. When these signals are high, data gets sent from the PC to the COM90C66. When these signals are low, data gets sent from the COM90C66 to the PC, or from the PROM to the PC if the PROM signal is also low. |  |  |  |  |  |  |  |  |

| 71              | I/O Channel<br>Ready                 | IOCHRDY         | Output. This signal, when low, is optionally used by the COM90C66 to extend host cycles. This is an open-drain signal. An external pull-up resistor is typically provided by the system.                                                                                       |  |  |  |  |  |  |  |  |

| 12              | Address<br>Enable                    | AEN             | Input. This signal, when low, acts as a qualifier for I/O Address Selection. When the signal is high, I/O decoding is disabled. This signal has no effect on Memory Address Selection.                                                                                         |  |  |  |  |  |  |  |  |

| 74              | Address Latch<br>Enable              | BALE            | Input. The falling edge of this signal is used by the COM90C66 to latch the A0-A19 lines and the nSBHE signal via an internal transparent latch. This signal is connected to a weak internal pull-up resistor.                                                                 |  |  |  |  |  |  |  |  |

| 64              | nl/O Read                            | nIOR            | Input. This active low signal is issued by the host microprocessor to indicate an I/O Read operation. A low level on this pin when the COM90C66 is accessed enables data from the internal registers of the COM90C66.                                                          |  |  |  |  |  |  |  |  |

| 65              | nI/O Write                           | nIOW            | Input. This active low signal is issued by the host microprocessor to indicate an I/O Write operation. A low pulse on this pin when the COM90C66 is accessed enables data from the Data Bus into the internal registers of the COM90C66.                                       |  |  |  |  |  |  |  |  |

| PLCC<br>PIN NO. | NAME                             | SYMBOL   | DESCRIPTION                                                                                                                                                                                                                                                                                |

|-----------------|----------------------------------|----------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                 |                                  |          | DESCRIPTION                                                                                                                                                                                                                                                                                |

| 66              | nMemory Read                     | nMEMR    | Input. This active low signal is issued by the host microprocessor to indicate a Memory Read operation. A low level on this pin when the COM90C66 is accessed enables data from the internal RAM of the COM90C66 or the PROM onto the data bus to be read by the host.                     |

| 67              | nMemory<br>Write                 | nMEMW    | Input. This active low signal is issued by the host microprocessor to indicate a Memory Write operation. A low pulse on this pin when the COM90C66 is accessed enables data from the data bus into the internal RAM of the COM90C66.                                                       |

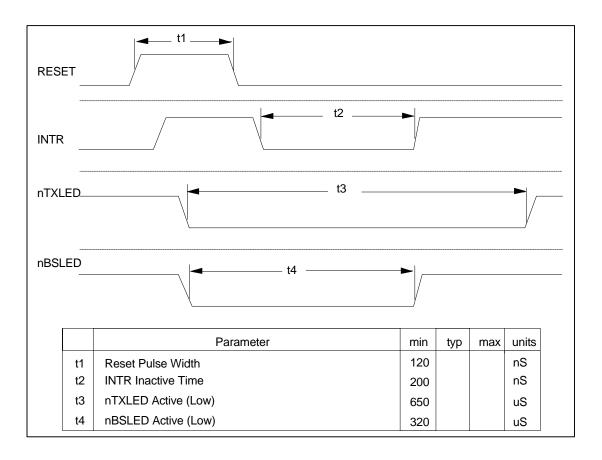

| 52              | Reset In                         | RESETIN  | Input. This active high signal is the power on reset signal from the host. It is used to activate the internal reset circuitry within the COM90C66.                                                                                                                                        |

| 53              | nROM Enable                      | nENROM   | Input. This active low signal enables the decoding of the external PROM. This signal also affects the timing of IOCHRDY and the number of address lines used to decode nMEMCS16. This signal is connected to a weak internal pull-up resistor.                                             |

| 54              | nROM Select                      | nPROM    | Output. This active low signal is issued by the COM90C66 to enable the external 8-bit wide PROM or the external register of the COM90C66.                                                                                                                                                  |

| 30              | Interrupt<br>Request             | INTR     | Output. This active high signal is generated by the COM90C66 when an enabled interrupt condition occurs. INTR returns to its inactive state when the interrupt status condition or the corresponding interrupt mask bit is reset.                                                          |

| 72              | nZero Wait<br>State              | n0WS     | Output. This active low signal is used to force zero wait state access cycles on the IBM PC Bus. This is an opendrain signal. An external pull-up resistor is typically provided by the system.                                                                                            |

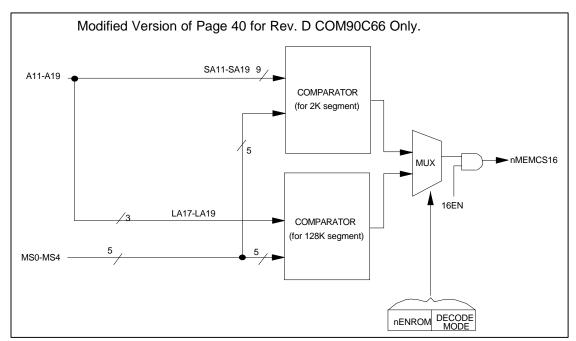

| 70              | nMemory<br>16-Bit Chip<br>Select | nMEMCS16 | Output. This active low signal is used to indicate that the present data transfer is a 16-bit memory cycle. The COM90C66 can be configured to use A19-A17 or A19-A11 to generate nMEMCS16. This is an open-drain signal. An external pull-up resistor is typically provided by the system. |

|                                      |                               | 1                     | <u> </u>                                                                                                                                                                                                                                      |  |  |  |  |

|--------------------------------------|-------------------------------|-----------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| PLCC<br>PIN NO.                      | NAME                          | SYMBOL                | DESCRIPTION                                                                                                                                                                                                                                   |  |  |  |  |

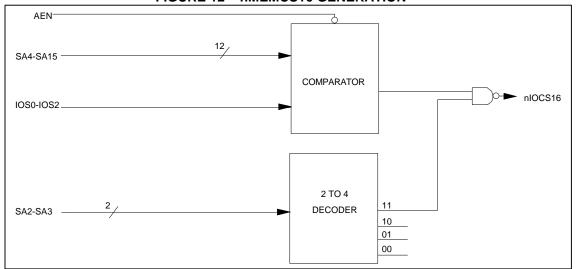

| 69                                   | nl/O 16-Bit<br>Chip Select    | nIOCS16               | Output. This active low signal is used to indicate that the present data transfer is a 16-bit I/O cycle. A15-A2 are used to generate nIOCS16. This is an open-drain signal. An external pull-up resistor is typically provided by the system. |  |  |  |  |

| 73                                   | nSystem Bus<br>High Enable    | nSBHE                 | Input. This active low signal is used to enable the COM90C66 to transfer data on D8-D15 of the Data Bus.                                                                                                                                      |  |  |  |  |

|                                      |                               | TRANSMI               | SSION MEDIA INTERFACE                                                                                                                                                                                                                         |  |  |  |  |

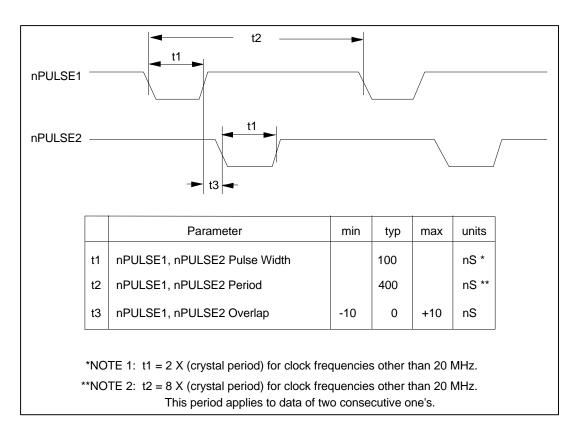

| 56, 55                               | nPulse 2,<br>nPulse 1         | nPULSE 2,<br>nPULSE 1 | Output. These active low signals carry the transmit data information, encoded in pulse format, from the COM90C66 to the LAN Driver.                                                                                                           |  |  |  |  |

| From the LAN Driver to the COM90C66. |                               |                       |                                                                                                                                                                                                                                               |  |  |  |  |

|                                      |                               | N                     | MISCELLANEOUS                                                                                                                                                                                                                                 |  |  |  |  |

| 51-47                                | Memory Base<br>Address Select | MS0-MS4               | Input. These signals are generated by external switches. They are used by the memory decoder to select a block of memory. These signals are connected to weak internal pull-up resistors.                                                     |  |  |  |  |

| 46-44                                | I/O Base<br>Address Select    | IOS0-IOS2             | Input. These signals are generated by external switches. They are used by the I/O decoder to select a block of 16 I/O locations. These signals are connected to weak internal pull-up resistors.                                              |  |  |  |  |

| 35-42                                | Node ID Select                | NID0-NID7             | Input. These signals are generated by external switches. The Node ID code represents the node identification of this particular COM90C66. These signals are connected to weak internal pull-up resistors.                                     |  |  |  |  |

| 32                                   | nTransmit<br>Activity LED     | nTXLED                | Output. This active low signal is used for direct connection to an LED through a resistor to $V_{\text{cc}}$ to indicate transmit activity. This signal has 12mA sink capability.                                                             |  |  |  |  |

| 31                                   | nBoard Select<br>Activity LED | nnBSLED               | Output. This active low signal is used for direct connection to an LED through a resistor to $V_{\text{cc}}$ to indicate board activity. This signal has 12mA sink capability.                                                                |  |  |  |  |

| PLCC<br>PIN NO. | NAME                  | SYMBOL          | DESCRIPTION                                                                                                                                                                                                                           |

|-----------------|-----------------------|-----------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

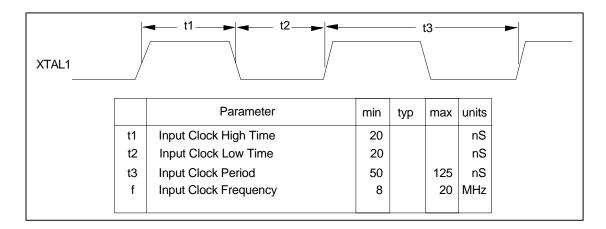

| 33, 34          | Crystal<br>Oscillator | XTAL1,<br>XTAL2 | An external parallel resonant 20 MHz crystal should be connected to these pins. If an external 20 MHz TTL clock is used instead, it must be connected to XTAL1 with a $390\Omega$ pull-up resistor and XTAL2 should be left floating. |

| 59              | CA Clock              | CACLK           | Output. This is the start/stop CA clock and should be left floating for typical operation.                                                                                                                                            |

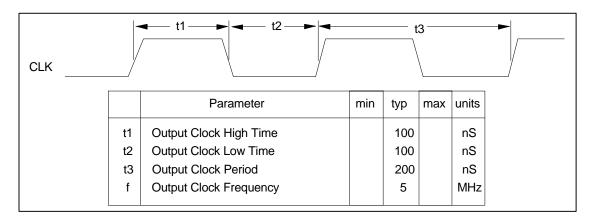

| 58              | Clock                 | CLK             | Output. This is a general purpose 5 MHz clock and should be left floating for typical operation.                                                                                                                                      |

| 1, 43           | Power Supply          | Vcc             | +5 Volt Power Supply pin.                                                                                                                                                                                                             |

| 21, 68          | Ground                | GND             | Ground pins.                                                                                                                                                                                                                          |

| 60-61           | No Connect            | NC              | Make no connection to these pins.                                                                                                                                                                                                     |

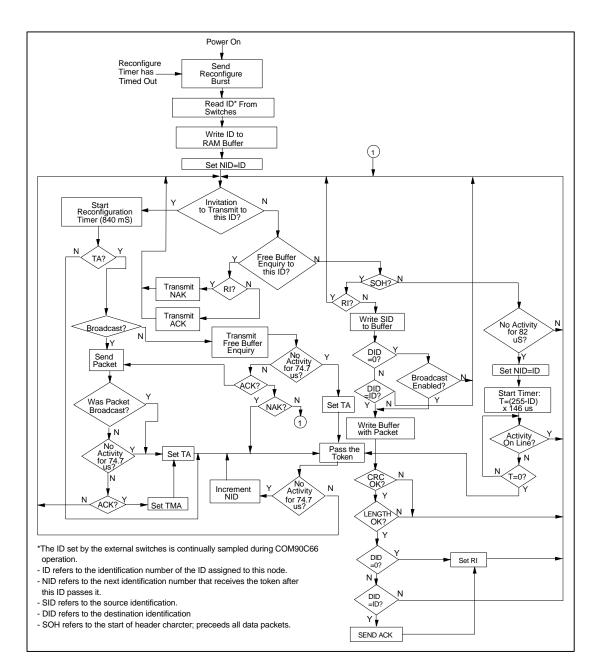

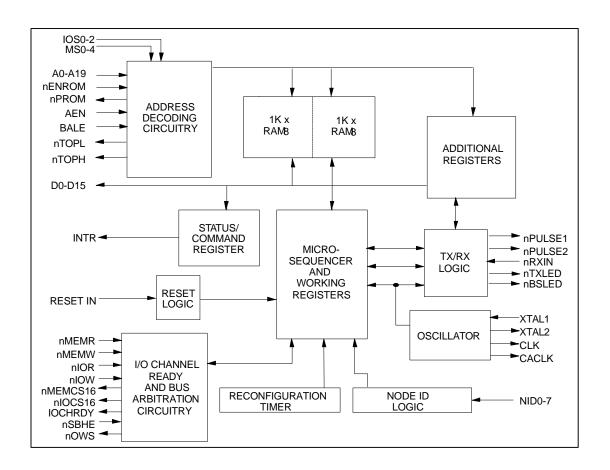

FIGURE 1 - COM90C66 OPERATION

8

#### PROTOCOL DESCRIPTION

#### **NETWORK PROTOCOL**

Communication on the network is based on a token passing protocol. Establishment of the network configuration and management of the network protocol are handled entirely by the COM90C66's internal microcoded sequencer. A processor or intelligent peripheral transmits data by simply loading a data packet and its destination ID into the RAM buffer and issuing a command to enable the transmitter. When the COM90C66 next receives the token, it verifies that the receiving node is ready by first transmitting a FREE BUFFER ENQUIRY message. If the receiving node transmits an ACKnowledge message, the data packet is transmitted followed by a 16-bit CRC. If the receiving node cannot accept the packet (typically its receiver is inhibited), it transmits a Negative AcKnowledgement message and the transmitter passes the token. Once it has been established that the receiving node can accept the packet and transmission is complete, the receiving node will verify the packet. If the packet is received successfully, the receiving node transmits an ACKnowledge message (or nothing if it is received unsuccessfully) allowing the transmitter to set the appropriate status bits to indicate successful or unsuccessful delivery of the packet. An interrupt mask permits the COM90C66 to generate an interrupt to the processor when selected status bits become true. Figure 1 is a flow chart illustrating the internal operation of the COM90C66.

#### **NETWORK RECONFIGURATION**

A significant advantage of the COM90C66 is its ability to adapt to changes on the network. Whenever a new node is activated or deactivated, a NETWORK RECONFIGURATION is performed. When a new COM90C66 is turned on (creating a new active node on the network), or if the COM90C66 has not received an INVITATION TO TRANSMIT for 840 mS, or if a software reset occurs, the device causes a

NETWORK RECONFIGURATION by sending a RECONFIGURE BURST consisting of eight marks and one space repeated 765 times. The purpose of this burst is to terminate all activity on the network. Since this burst is longer than any other type of transmission, the burst will interfere with the next INVITATION TO TRANSMIT, destroy the token and keep any other node from assuming control of the line.

When any COM90C66 senses an idle line for greater than 82 µS, which will only occur when the token is lost, each COM90C66 starts an internal timeout equal to 146 µS times the quantity 255 minus its own ID. It also sets the internally-stored NID (next ID representing the next possible ID node) equal to its own ID. If the timeout expires with no line activity, the COM90C66 starts sending INVITATION TO TRANSMIT with the Destination ID (DID) equal to the currently-stored NID. Within a given network, only one COM90C66 will timeout (the one with the highest ID number). After sending the INVITATION TO TRANSMIT, the COM90C66 waits for activity on the line. If there is no activity for 74.7µS, the COM90C66 increments the NID value and transmits another INVITATION TO TRANSMIT using the NID equal to the DID. If activity appears before the 74.7µS timeout expires, the COM90C66 releases control of the line. During NETWORK RECONFIGURATION, INVITATIONS TO TRANSMIT will be sent to all 256 possible IDs. Each COM90C66 on the network will finally have saved a NID value equal to the ID of the COM90C66 that it released control to. At this point, control is passed directly from one node to the next with no wasted INVITATIONS TO TRANSMIT being sent to IDs not on the network until the next NETWORK RECONFIGURATION occurs. When a node is powered off, the previous node will attempt to pass it the token by issuing an INVITATION TO TRANSMIT. Since this node will not respond, the previous node will timeout and transmit another INVITATION TO TRANSMIT to an incremented ID and eventually a response will be received.

The time required to do a NETWORK RECONFIGURATION depends on the number of nodes in the network, the propagation delay between nodes, and the highest ID number on the network, but will be in the range of 24 to 61 mS

#### **BROADCAST MESSAGES**

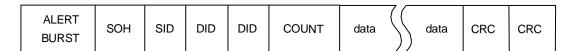

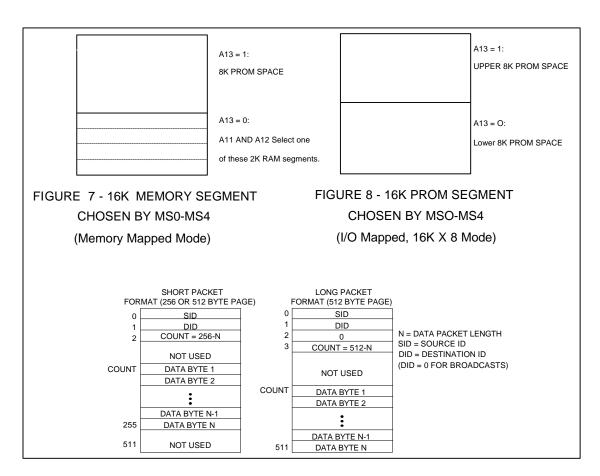

Broadcasting gives a particular node the ability to transmit a data packet to all nodes on the network simultaneously. ID zero is reserved for this feature and no node on the network can be assigned ID zero. To broadcast a message, the transmitting node's processor simply loads the RAM buffer with the data packet and sets the DID equal to zero. Figure 9 illustrates the position of each byte in the packet with the DID residing at address 01 HEX of the current page selected in the TRANSMIT command. Each individual node has the ability to ignore broadcast messages by setting the most significant bit of the ENABLE RECEIVE TO PAGE nn command (see Table 7) to logic "0".

#### **EXTENDED TIMEOUT FUNCTION**

There are three timeouts associated with the COM90C66 operation:

# **Response Time**

The Response Time is equal to the round trip propagation delay between the two furthest nodes on the network plus the maximum turn around time (the time it takes a particular COM90C66 to start sending a message in response to a received message), which is approximately 12.7 µS. The round trip propagation delay is a function of the transmission media and network topology. For a typical system using RG62 coax in a baseband system, a one-way cable propagation delay of 31 µS translates to a distance of about four miles. The flow chart in Figure 1 uses a value of 74.7  $\mu$ S (31 + 31 + 12.7) to determine if any node will respond.

#### **Idle Time**

The Idle Time is associated with a NETWORK RECONFIGURATION. Figure 1 illustrates that during a NETWORK RECONFIGURATION, one node will continually transmit INVITATIONS TO TRANSMIT until it encounters an active node. Every other node on the network must distinguish between this operation and an entirely idle line. During NETWORK RECONFIGURATION, activity will appear on the line every 82  $\mu$ S. This 82  $\mu$ S is equal to the Response Time of 74.7  $\mu$ S plus the time it takes the COM90C66 to retransmit another message (usually another INVITATION TO TRANSMIT).

# **Reconfiguration Time**

If any node does not receive the token within the Reconfiguration Time, the node will initiate a NETWORK RECONFIGURATION.

The ET2 and ET1 bits (bits 3 and 4 of the Configuration Register) allow the network to operate over longer distances than the four miles stated earlier. The logic levels on these bits control the maximum distances over which the COM90C66 can operate by controlling the three timeout values described above. See the description of the ET1 and ET2 bits, found in Table 8, for the table containing the combinations of these bits. It should be noted that for proper network operation, all COM90C66s connected to the same network must have the same Response Time, Idle Time, and Reconfiguration Time.

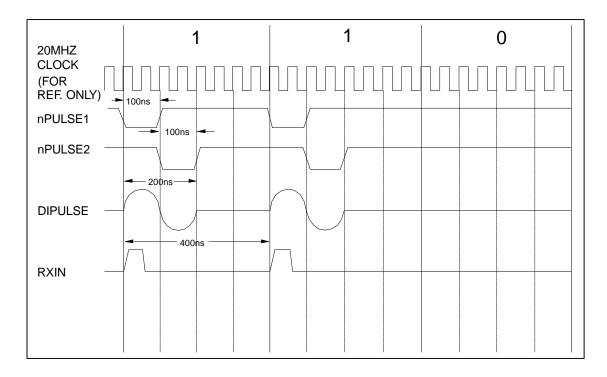

# LINE PROTOCOL

The ARCNET line protocol can be described as isochronous because each byte is preceded by a start interval and ended with a stop interval. Unlike asynchronous protocols, there is a constant amount of time separating each data byte. Each byte takes up exactly 11 clock intervals with a single clock interval being 400 nS in duration. As a result, one byte is

transmitted every 4.4  $\mu$ S and the time to transmit a message can be precisely determined. The line idles in a spacing (logic "0") condition. A logic "0" is defined as no line activity and a logic "1" is defined as a negative pulse of 200 nS duration. A transmission starts with an ALERT BURST consisting of six unit intervals of mark (logic "1"). Eight-bit data characters are then sent with each character preceded by two unit intervals of mark and one unit interval of space. Five types of transmission can be performed as described below:

#### **Invitations To Transmit**

An Invitation To Transmit is used to pass the token from one node to another and is sent by the following sequence:

- An ALERT BURST

- An EOT (End Of Transmission--ASCII code 04 HEX)

- Two (repeated) DID (Destination IDentification) characters

| ALERT |     |     |     |

|-------|-----|-----|-----|

| BURST | EOT | DID | DID |

#### Free Buffer Enquiries

A Free Buffer Enquiry is used to ask another node if it is able to accept a packet of data and is sent by the following sequence:

- An ALERT BURST

- An ENQ (ENQuiry--ASCII code 85 HEX)

- Two (repeated) DID (Destination IDentification) characters

| ALERT |     |     |     |

|-------|-----|-----|-----|

| BURST | ENQ | DID | DID |

#### **Data Packets**

A Data Packet consists of the actual data being sent to another node and is sent by the following sequence:

- An ALERT BURST

- An SOH (Start Of Header--ASCII code 01 HEX)

- An SID (Source IDentification) character

- Two (repeated) DID (Destination IDentification) characters

- A single COUNT character which is the 2's complement of the number of data bytes to follow if a short packet is being sent or 00 HEX followed by a COUNT character which is the 2's complement of the number of data bytes to follow if a long packet is being sent

- N data bytes where COUNT = 256-N (or 512-N for a long packet)

- Two CRC (Cyclic Redundancy Check) characters. The CRC polynomial used is X<sup>16</sup> + X<sup>15</sup> + X<sup>2</sup> + 1.

#### Acknowledgements

An Acknowledgement is used to acknowledge reception of a packet or as an affirmative response to FREE BUFFER ENQUIRIES and is sent by the following sequence:

- An ALERT BURST

- An ACK (ACKnowledgement--ASCII code 86 HEX) character

| ALERT |     |

|-------|-----|

| BURST | ACK |

#### **Negative Acknowledgements**

A Negative Acknowledgement is used as a negative response to FREE BUFFER ENQUIRIES and is sent by the following sequence:

- An ALERT BURST

- A NAK (Negative AcKnowledgement--ASCII code 15 HEX) character

| ALERT |     |

|-------|-----|

| BURST | NAK |

#### SYSTEM DESCRIPTION

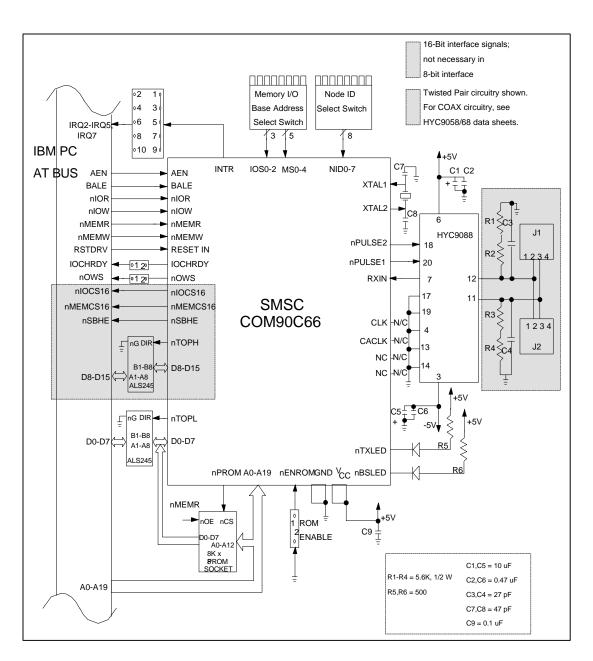

The System Block Diagram shown in Figure 2 illustrates a typical implementation of an ARCNET node using the COM90C66. The only external components required to complete an ARCNET node design are one or two bus transceivers (for 8-bit or 16-bit applications, respectively) and the LAN Driver, making the COM90C66 the most highly-integrated ARCNET solution. The COM90C66 provides for simple interfacing to both sides of the ARCNET system, namely the microprocessor and the transmission media.

#### **MICROPROCESSOR INTERFACE**

The left half of Figure 2 illustrates a typical COM90C66 interface to the PC. The sections outlined in dotted lines represent the portion which distinguishes the 16-bit interface, while the remaining interface exists for both 8-bit and 16-bit applications. The interface consists of a 20-bit address bus, a 16-bit data bus and a control bus. All accesses to the internal RAM, the optional PROM and the internal registers are controlled by the COM90C66.

The microprocessor's address lines are directly connected to the COM90C66. The address decoding circuitry of the COM90C66 monitors the address bus to determine valid accesses to the device.

Figure 2 shows octal bus transceivers utilized as the interface between the microprocessor's data lines and the COM90C66. The transceivers are only necessary when interfacing to a high current drive data bus such as the IBM PC data bus, and may otherwise be omitted. The COM90C66 provides the nTOPL and nTOPH signals which control the direction of the external transceiver(s). The nTOPL signal is also activated during PROM Read Cycles.

The microprocessor's control bus is directly connected to the COM90C66 and is used in access cycle communication between the device and the microprocessor. All accesses support zero wait state arbitration in most machines. The Control Bus has been optimized to support the intricacies of the IBM AT Bus and the EISA Bus.

#### TRANSMISSION MEDIA INTERFACE

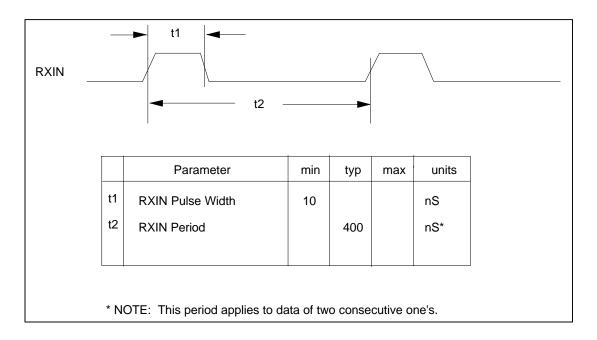

The right half of Figure 2 illustrates the COM90C66 interface to the transmission media used to connect the node to the network. The HYC9058/68/88 may be used to drive the media. During transmission, the COM90C66 transmits a logic "1" by generating two 100 nS non-overlapping negative pulses, nPULSE1 and nPULSE2. These signals are sent to the LAN Driver, which in turn creates a 200 nS dipulse signal on the media. A logic "0" is transmitted by the absence of the two negative pulses, that is, the nPULSE1 and nPULSE2 outputs remain high, therefore there is an absence of a dipulse. During reception the 200 nS dipulse appearing on the media is coupled through the RF transformer of the LAN Driver. A positive pulse at the RXIN pin of the COM90C66 is interpreted as a logic "1". Again, if no dipulse is present, the COM90C66 interprets a logic "0".

Typically, RXIN pulse occur at multiples of 400 nS. The COM90C66 can tolerate distortion of plus or minus 100 nS and still correctly capture the RXIN pulses.

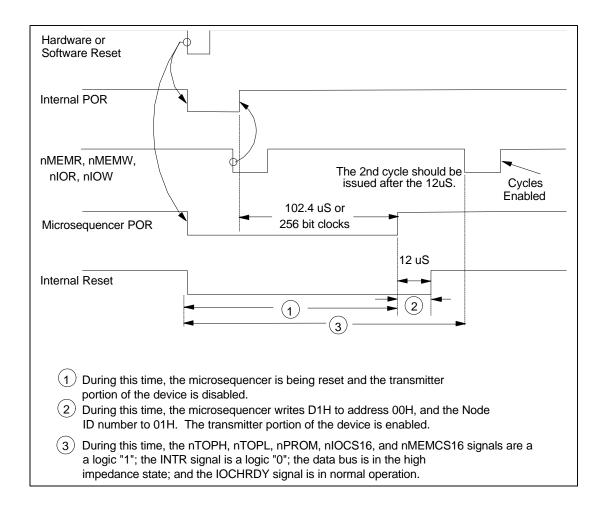

During Reset, the transmitter portion of the COM90C66 is disabled and the nPULSE1 and nPULSE2 pins are inactive high.

The COM90C66 includes the nTXLED and nBSLED signals which, when tied to LEDs, provide indication of transmit and board access activity. In addition, it is possible for the user to completely disable the transmitter through software. These two unique features represent two of the improvements made in the diagnostics of the device. Please see the Improved Diagnostics section of this document for further detail.

#### **FUNCTIONAL DESCRIPTION**

#### **MICROSEQUENCER**

The COM90C66 contains an internal microsequencer which performs all of the control operation necessary to carry out the ARCNET protocol. It consists of a clock generator, a 554 x 8 ROM, a program counter, two instruction registers, an instruction decoder, a no-op generator, jump logic, and reconfiguration logic.

The COM90C66 derives a 5 MHz and a 2.5 MHz clock from the external crystal. These clocks provide the rate at which the instructions are executed within the COM90C66. The 5 MHz clock is the rate at which the program counter operates, while the 2.5 MHz clock is the rate at which the instructions are executed. The microprogram is stored in the ROM and the

instructions are fetched and then placed into the instruction registers. One register holds the op code, while the other holds the immediate data. Once the instruction is fetched, it is decoded by the internal instruction decoder, at which point the COM90C66 proceeds to execute the instruction. When a no-op instruction is encountered, the microsequencer enters a timed loop, in which case the program counter is temporarily stopped until the loop is complete. When a jump instruction is encountered, the program counter is loaded with the jump address from the ROM. The COM90C66 contains an internal reconfiguration timer which interrupts the microsequencer if it has timed out. At this point the program counter is cleared, after which the MYRECON bit of the Diagnostic Status Register is set.

FIGURE 2 - SYSTEM BLOCK DIAGRAM

FIGURE 3 - INTERNAL BLOCK DIAGRAM

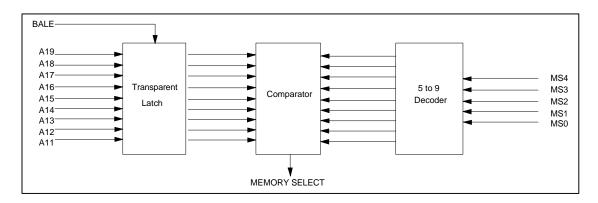

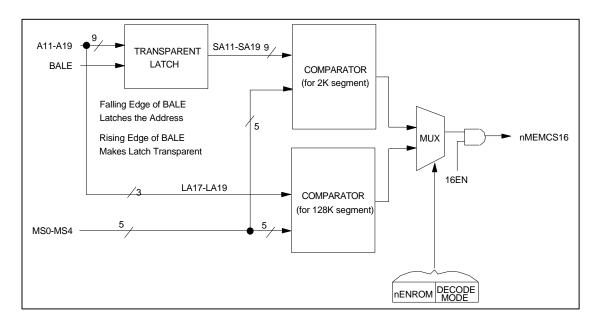

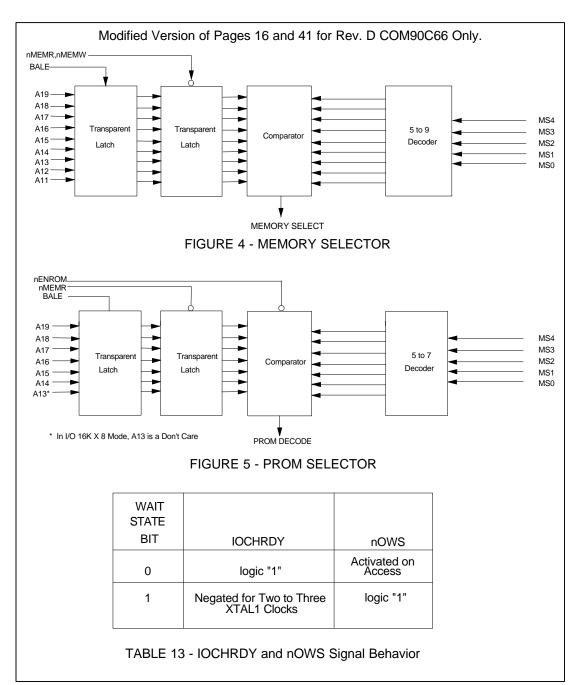

FIGURE 4 - MEMORY SELECTOR

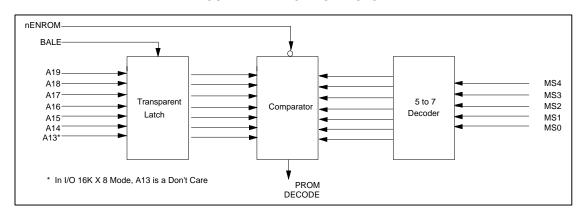

FIGURE 5 – PROM SELECTOR

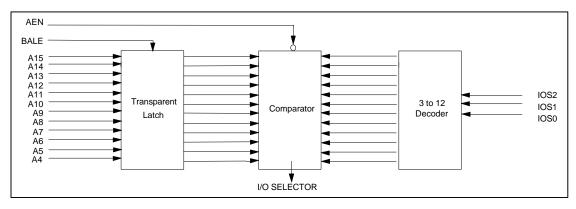

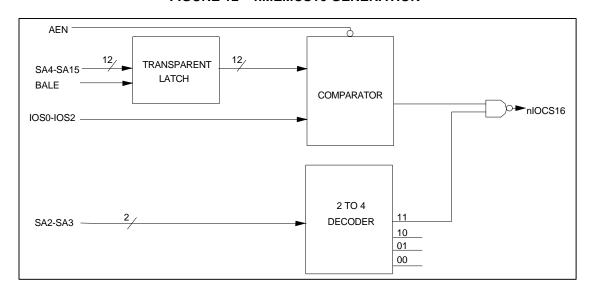

FIGURE 6 - I/O SELECTOR

16

FIGURE 9 - RAM BUFFER PACKET CONFIGURATION

Table 1 – User Configuration of Memory Map

|     |     |     |     |     | DE | CODED | BITS F | OUND | IN DAT | A REG | ISTER |    | RAM ADDRESS   | PROM ADDRESS  |

|-----|-----|-----|-----|-----|----|-------|--------|------|--------|-------|-------|----|---------------|---------------|

| MS4 | MS3 | MS2 | MS1 | MS0 | D7 | D6    | D5     | D4   | D3     | D2    | D1    | D0 | RANGE         | RANGE         |

| 0   | 0   | 0   | 0   | 0   | 1  | 1     | 0      | 0    | 0      | 0     | 0     | 0  | C:0000-C:07FF | C:2000-C:3FFF |

| 0   | 0   | 0   | 0   | 1   | 1  | 1     | 0      | 0    | 0      | 0     | 0     | 1  | C:0800-C:0FFF | C:2000-C:3FFF |

| 0   | 0   | 0   | 1   | 0   | 1  | 1     | 0      | 0    | 0      | 0     | 1     | 0  | C:1000-C:17FF | C:2000-C:3FFF |

| 0   | 0   | 0   | 1   | 1   | 1  | 1     | 0      | 0    | 0      | 0     | 1     | 1  | C:1800-C:1FFF | C:2000-C:3FFF |

| 0   | 0   | 1   | 0   | 0   | 1  | 1     | 0      | 0    | 0      | 1     | 0     | 0  | C:4000-C:47FF | C:6000-C:7FFF |

| 0   | 0   | 1   | 0   | 1   | 1  | 1     | 0      | 0    | 0      | 1     | 0     | 1  | C:4800-C:4FFF | C:6000-C:7FFF |

| 0   | 0   | 1   | 1   | 0   | 1  | 1     | 0      | 0    | 0      | 1     | 1     | 0  | C:5000-C:57FF | C:6000-C:7FFF |

| 0   | 0   | 1   | 1   | 1   | 1  | 1     | 0      | 0    | 0      | 1     | 1     | 1  | C:5800-C:5FFF | C:6000-C:7FFF |

| 0   | 1   | 0   | 0   | 0   | 1  | 1     | 0      | 0    | 1      | 1     | 0     | 0  | C:C000-C:C7FF | C:E000-C:FFFF |

| 0   | 1   | 0   | 0   | 1   | 1  | 1     | 0      | 0    | 1      | 1     | 0     | 1  | C:C800-C:CFFF | C:E000-C:FFFF |

| 0   | 1   | 0   | 1   | 0   | 1  | 1     | 0      | 0    | 1      | 1     | 1     | 0  | C:D000-C:D7FF | C:E000-C:FFFF |

| 0   | 1   | 0   | 1   | 1   | 1  | 1     | 0      | 0    | 1      | 1     | 1     | 1  | C:D800-C:DFFF | C:E000-C:FFFF |

| 0   | 1   | 1   | 0   | 0   | 1  | 1     | 0      | 1    | 0      | 0     | 0     | 0  | D:0000-D:07FF | D:2000-D:3FFF |

| 0   | 1   | 1   | 0   | 1   | 1  | 1     | 0      | 1    | 0      | 0     | 0     | 1  | D:0800-D:0FFF | D:2000-D:3FFF |

| 0   | 1   | 1   | 1   | 0   | 1  | 1     | 0      | 1    | 0      | 0     | 1     | 0  | D:1000-D:17FF | D:2000-D:3FFF |

| 0   | 1   | 1   | 1   | 1   | 1  | 1     | 0      | 1    | 0      | 0     | 1     | 1  | D:1800-D:1FFF | D:2000-D:3FFF |

| 1   | 0   | 0   | 0   | 0   | 1  | 1     | 0      | 1    | 0      | 1     | 0     | 0  | D:4000-D:47FF | D:6000-D:7FFF |

| 1   | 0   | 0   | 0   | 1   | 1  | 1     | 0      | 1    | 0      | 1     | 0     | 1  | D:4800-D:4FFF | D:6000-D:7FFF |

| 1   | 0   | 0   | 1   | 0   | 1  | 1     | 0      | 1    | 0      | 1     | 1     | 0  | D:5000-D:57FF | D:6000-D:7FFF |

| 1   | 0   | 0   | 1   | 1   | 1  | 1     | 0      | 1    | 0      | 1     | 1     | 1  | D:5800-D:5FFF | D:6000-D:7FFF |

| 1   | 0   | 1   | 0   | 0   | 1  | 1     | 0      | 1    | 1      | 0     | 0     | 0  | D:8000-D:87FF | D:A000-D:BFFF |

| 1   | 0   | 1   | 0   | 1   | 1  | 1     | 0      | 1    | 1      | 0     | 0     | 1  | D:8800-D:8FFF | D:A000-D:BFFF |

| 1   | 0   | 1   | 1   | 0   | 1  | 1     | 0      | 1    | 1      | 0     | 1     | 0  | D:9000-D:97FF | D:A000-D:BFFF |

| 1   | 0   | 1   | 1   | 1   | 1  | 1     | 0      | 1    | 1      | 0     | 1     | 1  | D:9800-D:9FFF | D:A000-D:BFFF |

| 1   | 1   | 0   | 0   | 0   | 1  | 1     | 0      | 1    | 1      | 1     | 0     | 0  | D:C000-D:C7FF | D:E000-D:FFFF |

| 1   | 1   | 0   | 0   | 1   | 1  | 1     | 0      | 1    | 1      | 1     | 0     | 1  | D:C800-D:CFFF | D:E000-D:FFFF |

| 1   | 1   | 0   | 1   | 0   | 1  | 1     | 0      | 1    | 1      | 1     | 1     | 0  | D:D000-D:D7FF | D:E000-D:FFFF |

| 1   | 1   | 0   | 1   | 1   | 1  | 1     | 0      | 1    | 1      | 1     | 1     | 1  | D:D800-D:DFFF | D:E000-D:FFFF |

| 1   | 1   | 1   | 0   | 0   | 1  | 1     | 1      | 0    | 0      | 0     | 0     | 0  | E:0000-E:07FF | E:2000-E:3FFF |

| 1   | 1   | 1   | 0   | 1   | 1  | 1     | 1      | 0    | 0      | 0     | 0     | 1  | E:0800-E:0FFF | E:2000-E:3FFF |

| 1   | 1   | 1   | 1   | 0   | 1  | 1     | 1      | 0    | 0      | 0     | 1     | 0  | E:1000-E:17FF | E:2000-E:3FFF |

| 1   | 1   | 1   | 1   | 1   | 1  | 1     | 1      | 0    | 0      | 0     | 1     | 1  | E:1800-E:1FFF | E:2000-E:3FFF |

#### ADDRESS DECODING

The COM90C66 includes address decoding circuitry that compares the value of the Address Bus to the address range selected by the Memory Select (MS0-MS4) and I/O Select (IOS0-IOS2) pins in order to determine

processor accesses to the on-board PROM, the on-chip RAM, and I/O locations. By placing switches on the MS0-MS4 and the IOS0-IOS2 pins, the user configures the Memory Map and I/O Map according to the possible address ranges shown in Tables 1 and 2.

Table 2 - User Configuration of I/O Map

| IOS2 | I0S1 | IOS0 | I/O ADDRESS RANGE |

|------|------|------|-------------------|

| 0    | 0    | 0    | 0260-026F         |

| 0    | 0    | 1    | 0290-029F         |

| 0    | 1    | 0    | 02E0-02EF         |

| 0    | 1    | 1    | 02F0-02FF         |

| 1    | 0    | 0    | 0300-030F         |

| 1    | 0    | 1    | 0350-035F         |

| 1    | 1    | 0    | 0380-038F         |

| 1    | 1    | 1    | 03E0-03EF         |

#### **Memory Address Decoding**

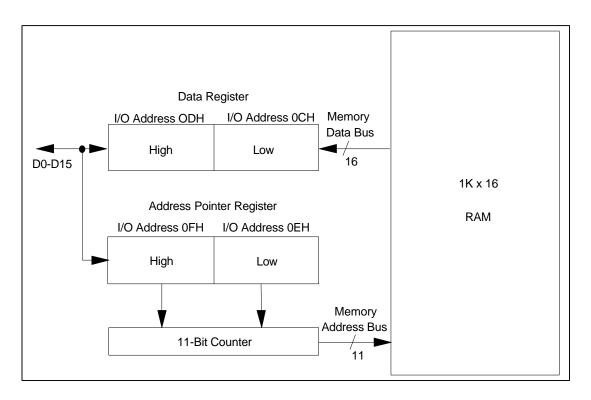

The Memory Address Decoding circuitry is used to select a block from the memory map of the processor for PROM and RAM accesses. Figure 4 illustrates how the memory selection works. The MS4-MS0 pins are decoded through a 5 to 9 Decoder to generate a 9-bit value. These nine bits are compared to the A19-A11 lines of the Address Bus in order to select a particular 16K memory segment. Figure 7 illustrates a 16K block of memory that has been selected by the MS4-MS0 pins. The PROM occupies the upper 8K area of the selected 16K segment and is accessed when A13 = 1. The RAM occupies one of four selectable 2K areas of the selected 16K segment and is accessed when A13 = 0. A11 and A12 are used to determine which 2K segment of the lower 8K area will be used for the RAM buffer.

Figure 5 illustrates how the external PROM selection works. The MS4-MS0 pins are

decoded through a 5 to 7 Decoder to generate a 7-bit value. These seven bits are compared to the A19-A13 lines of the Address Bus in order to select an 8K memory range. Figure 7 illustrates an 8K block of memory for the PROM. In I/O 16K x 8 Mode only a 16K memory range is selected for the PROM. Figure 8 illustrates a 16K block of memory for the PROM.

The nENROM pin is used to enable decoding for the on-board PROM. If nENROM is connected to a logic "1", the COM90C66 will not generate the nPROM signal, the nTOPL signal, or the IOCHRDY signal for accesses to the PROM. In this configuration, the COM90C66 will only occupy a 2K segment of memory.

# I/O Address Decoding

This section is used to select a block of 16 I/O locations from the I/O map of the processor. Figure 6 illustrates how the I/O selection

Table 3 – Read Register Summary

|                     | 1       |              |         |       |      |       |               |       |    |

|---------------------|---------|--------------|---------|-------|------|-------|---------------|-------|----|

| REGISTER            | MSB     |              | ADDRESS |       |      |       |               |       |    |

| STATUS              | RI      | Х            | х       | POR   | TEST | RECON | TMA           | TA    | 00 |

| DIAG.<br>STATUS     | MYRECON | х            | RCVACT  | TOKEN | Х    | Х     | Х             | Х     | 01 |

| CONFIG-<br>URATION  | 16EN    | CCHEN        | DECODE  | ET1   | ET2  | WAIT  | IO-<br>ACCESS | TXOFF | 02 |

| I/O SELECT          | 0       | 0            | I/O5    | I/O4  | I/O3 | I/O2  | I/O1          | I/O0  | 03 |

| MEMORY<br>SELECT    | MEM7    | МЕМ6         | MEM5    | MEM4  | МЕМ3 | MEM2  | MEM1          | МЕМО  | 04 |

| NODE<br>ID          | NID7    | NID6         | NID5    | NID4  | NID3 | NID2  | NID1          | NID0  | 05 |

| RESERVED            | Х       | х            | х       | Х     | Х    | X     | Х             | Х     | 06 |

| RESERVED            | х       | Х            | х       | Х     | Х    | х     | х             | Х     | 07 |

| RESET               | Х       | Х            | Х       | Х     | Х    | Х     | Х             | Х     | 08 |

| RESET               | X       | Х            | х       | Х     | Х    | Х     | х             | Х     | 09 |

| RESET               | x       | Х            | Х       | Х     | Х    | х     | Х             | Х     | 0A |

| RESET               | Х       | Х            | Х       | Х     | Х    | Х     | Х             | Х     | 0B |

| DATA<br>LOW         | D7      | D6           | D5      | D4    | D3   | D2    | D1            | D0    | 0C |

| DATA<br>HIGH        | D15     | D14          | D13     | D12   | D11  | D10   | D9            | D8    | 0D |

| ADDRESS<br>PTR LOW  | A7      | A6           | A5      | A4    | A3   | A2    | A1            | A0    | 0E |

| ADDRESS<br>PTR HIGH | Х       | AUTO-<br>INC | х       | Х     | Х    | A10   | A9            | A8    | 0F |

Table 4 – Write Register Summary

| ADDRESS | MSB  | WRITE        |        |      |      |       |               | LSB   | REGISTER             |

|---------|------|--------------|--------|------|------|-------|---------------|-------|----------------------|

| 00      | RI   | 0            | 0      | 0    | 0    | RECON | 0             | TA    | INTERRUPT<br>MASK    |

| 01      | D7   | D6           | D5     | D4   | D3   | D2    | D1            | D0    | COMMAND              |

| 02      | 16EN | CCHEN        | DECODE | ET1  | ET2  | WAIT  | IO-<br>ACCESS | TXOFF | CONFIG-<br>URATION   |

| 03      | 0    | 0            | 0      | 0    | 0    | 0     | 0             | 0     | RESERVED             |

| 04      | 0    | 0            | 0      | 0    | 0    | 0     | 0             | 0     | RESERVED             |

| 05      | NID7 | NID6         | NID5   | NID4 | NID3 | NID2  | NID1          | NID0  | NODE<br>ID           |

| 06      | 0    | 0            | 0      | 0    | 0    | 0     | 0             | 0     | RESERVED             |

| 07      | D7   | D6           | D5     | D4   | D3   | D2    | D1            | D0    | EXTERNAL<br>REGISTER |

| 08      | X    | х            | х      | Χ    | Х    | х     | х             | Х     | RESET                |

| 09      | х    | Х            | Х      | Х    | Х    | Х     | Х             | Х     | RESET                |

| 0A      | Х    | х            | х      | Х    | х    | Х     | х             | Х     | RESET                |

| 0B      | Х    | х            | х      | Х    | Х    | Х     | х             | х     | RESET                |

| 0C      | D7   | D6           | D5     | D4   | D3   | D2    | D1            | D0    | DATA<br>LOW          |

| 0D      | D15  | D14          | D13    | D12  | D11  | D10   | D9            | D8    | DATA<br>HIGH         |

| 0E      | A7   | A6           | A5     | A4   | А3   | A2    | A1            | A0    | ADDRESS<br>PTR LOW   |

| 0F      | 0    | AUTO-<br>INC | 0      | 0    | 0    | A10   | A9            | A8    | ADDRESS<br>PTR HIGH  |

process works. The IOS2-IOS0 pins are decoded through a 3 to 12 Decoder to generate a 12-bit value. These 12 bits are compared to the A15-A4 lines of the address bus in order to determine which block of 16 I/O locations will be used by the chip. A logic "0" on the AEN signal enables the I/O decoding process. Tables 3 and 4 illustrate the COM90C66 register map. Reserved locations should not be accessed.

#### **INTERNAL REGISTERS**

The COM90C66 contains internal registers which may be accessed by the microprocessor. All undefined bits are read as undefined and must be written as logic "0".

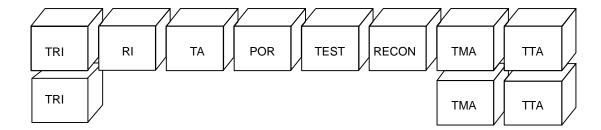

# Status Register

The COM90C66 Status Register is an 8-bit read-only register which can be accessed by the microprocessor. All of the bits in this register (except for bits 5 and 6) are software-compatible with previous SMSC ARCNET devices. The Extended Timeout bits are now in the Configuration Register. The Status Register contents are traditionally defined as in Table 5. The Status Register contents are defined differently during the Command Chaining Please refer to the "Command operation. Chaining" section of this document for these definitions. The Status Register defaults to the value 1XX1 0001 upon either hardware or software reset.

# Interrupt Mask Register (IMR)

The COM90C66 is capable of generating an interrupt signal when certain status bits become true. A write to the IMR specifies which status bits will be enabled to generate the interrupt. The bit positions in the IMR are in the same position as their corresponding status bits in the Status Register, and a logic "1" in a particular position enables the corresponding interrupt. While the Receiver Inhibited, Reconfiguration,

and Transmitter Available status bits are capable of generating an interrupt if enabled, the TMA status bit will never cause an interrupt. The IMR takes on the following bit definition:

| BIT | BIT | BIT | BIT | BIT | BIT 2 | BIT | BIT |

|-----|-----|-----|-----|-----|-------|-----|-----|

| 7   | 6   | 5   | 4   | 3   |       | 1   | 0   |

| RI  | Х   | Х   | Х   | Х   | RE-   | Х   | TA  |

|     |     |     |     |     | CON   |     |     |

The three maskable status bits are ANDed with their respective mask bits, and the results are ORed to produce the processor interrupt signal INTR. An RI or TA interrupt is masked when the corresponding mask bit is reset to logic "0", but will reappear when the corresponding mask bit is set to logic "1" again, unless the interrupt status condition has been cleared by this time. A RECON interrupt is cleared when the CLEAR FLAGS command is issued. The Interrupt Mask Register defaults to the value 0000 0000 upon either hardware or software reset.

#### **Diagnostic Status Register**

The Diagnostic Status Register contains three read-only bits which give the user the ability to troubleshoot network or node operation. The various combinations of these bits and the Transmitter Off bit of the Configuration Register represent different situations and can be used during troubleshooting. These bits are reset to logic "0" upon reading the Diagnostic Status Register or upon software or hardware reset. The register contents are as in Table 6. The Diagnostic Status Register defaults to the value 0X00 XXXX upon either hardware or software reset.

#### **Command Register**

Execution of commands are initiated by performing a processor I/O write with the written data defining the commands listed in Table 7. Any combinations of written data other than those listed in Table 7 are not permitted and may result in incorrect chip and/or network operation.

Table 5 - Status Register

|     | Table 5 - Status Register              |        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |  |  |  |

|-----|----------------------------------------|--------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| BIT | BIT NAME                               | SYMBOL | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |  |  |  |

| 7   | Receiver Inhibited                     | RI     | This bit, if high, indicates that a packet has been deposited into the RAM buffer page nn as specified by the last ENABLE RECEIVE TO PAGE nn command. No messages will be received until this command is issued, and once the message has been received, the RI bit gets set, thereby inhibiting the receiver. The RI bit is cleared by issuing an ENABLE RECEIVE TO PAGE nn command. This bit, when set, will cause an interrupt if the corresponding bit of the Interrupt Mask Register is also set. |  |  |  |

| 6   | (not used)                             |        | This bit is undefined.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |  |  |  |

| 5   | (not used)                             |        | This bit is undefined.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |  |  |  |

| 4   | Power On Reset                         | POR    | This bit, if high, indicates that the COM90C66 has been reset by either a software reset, a hardware reset, or setting the Node ID = 00H. The POR bit is cleared by the CLEAR FLAGS command.                                                                                                                                                                                                                                                                                                           |  |  |  |

| 3   | Test                                   | TEST   | This bit is intended for test and diagnostic purposes. It is a logic "0" under normal operating conditions.                                                                                                                                                                                                                                                                                                                                                                                            |  |  |  |

| 2   | Reconfiguration                        | RECON  | This bit, if high, indicates that the Line Idle Timer has timed out because the RXIN pin (pin 57) was idle for 82 S. The RECON bit is cleared during a CLEAR FLAGS command. This bit, when set, will cause an interrupt if the corresponding bit in the Interrupt Mask Register is also set. The interrupt service routine should consist of looking at the MYRECON bit of the Diagnostic Status Register to make sure that there are not consecutive reconfigurations caused by this node.            |  |  |  |

| 1   | Transmitter<br>Message<br>Acknowledged | ТМА    | This bit, if high, indicates that the packet transmitted as a result of an ENABLE TRANSMIT FROM PAGE nn command has been positively acknowledged. This bit should only be considered valid after the TA bit (bit 0) is set. Broadcast messages are never acknowledged. The TMA bit is cleared by issuing the ENABLE TRANSMIT FROM PAGE nn command.                                                                                                                                                     |  |  |  |

| 0   | Transmitter<br>Available               | ТА     | This bit, if high, indicates that the transmitter is available for transmitting. This bit is set at the conclusion of an ENABLE TRANSMIT FROM PAGE nn command or upon execution of a DISABLE TRANSMITTER command. The TA bit is cleared by issuing the ENABLE TRANSMIT FROM PAGE nn command after the node next receives the token. This bit, when set, will cause an interrupt if the corresponding bit in the Interrupt Mask Register is also set.                                                   |  |  |  |

Table 6 - Diagnostic Status Register

| BIT       | BIT NAME           | SYMBOL       | DESCRIPTION                                                                                                                                                                                                                                                                                                                               |

|-----------|--------------------|--------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| DII       | DII NAWE           | STWIBUL      | DESCRIPTION                                                                                                                                                                                                                                                                                                                               |

| 7         | My Reconfiguration | MY-<br>RECON | This bit, if high, indicates that the reconfiguration that has just occurred was caused by this node. This bit is set when the Token Reception Timer times out. This bit is typically read after the RECON bit of the Status Register is found to be set. Refer to the Improved Diagnostics section of this document for further details. |

| 5         | Receive Activity   | RCVACT       | This bit, if high, indicates that receive activity (data transition) is detected on the RXIN pin of the device. This bit may be used in diagnostic troubleshooting of the network or node. Refer to the Improved Diagnostics section of this document for further details.                                                                |

| 4         | Token Seen         | TOKEN        | This bit, if high, indicates that a token has been seen on the network, sent by a node other than this node. This bit may be used in diagnostic troubleshooting of the network or node. Refer to the Improved Diagnostics section of this document for further details.                                                                   |

| 6,<br>3-0 | (not used)         |              | These bits are undefined.                                                                                                                                                                                                                                                                                                                 |

# Table 7 - Command Register

| WRITTEN DATA | COMMAND NAME                | DESCRIPTION                                                                                                                                                                                                                                                                              |

|--------------|-----------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0000 0000    | CLEAR TRANSMIT<br>INTERRUPT | This command is only used in the Command Chaining operation. Please refer to the Command Chaining section of this document for definition of this command.                                                                                                                               |

| 0000 0001    | DISABLE<br>TRANSMITTER      | This command will cancel any pending transmit command (transmission that has not yet started) and will set the TA (Transmitter Available) status bit to logic "1" when the COM90C66 next receives the token.                                                                             |

| 0000 0010    | DISABLE<br>RECEIVER         | This command will cancel any pending receive command. If the COM90C66 is not yet receiving a packet, the RI (Receiver Inhibited) bit will be set to logic "1" the next time the token is received. If packet reception is already underway, reception will run to its normal conclusion. |

Table 7 - Command Register

| WRITTEN DATA | COMMAND NAME                    | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|--------------|---------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 000n n011    | ENABLE TRANSMIT<br>FROM PAGE nn | This command prepares the COM90C66 to begin a transmit sequence from RAM buffer page nn the next time it receives the token. When this command is loaded, the TA and TMA bits are reset to logic "0". The TA bit is set to logic "1" upon completion of the transmit sequence. The TMA bit will have been set by this time if the COM90C66 has received an acknowledgement from the destination node. This acknowledgement is strictly hardware level, which is sent by the receiving node before its controlling processor is even aware of message reception. It is also possible for this acknowledgement to get lost due to line errors. This implies that the TMA bit is not a guarantee of proper destination reception. Refer to Figure 1 for details of the transmit sequence and its relation to the TA and TMA status bits. |

| b00n n100    | ENABLE RECEIVE<br>TO PAGE nn    | This command allows the COM90C66 to receive data packets into RAM buffer page nn and resets the RI status bit to logic "0". If the value of "b" is a logic "1", the COM90C66 will also receive broadcast transmission. A broadcast transmission is a transmission to ID zero. The RI status bit is set to logic "1" upon successful reception of a message.                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| 0000 c101    | DEFINE<br>CONFIGURATION         | This command defines the maximum length of packets that may be handled by the device. If the value of "c" is a logic "1", the COM90C66 will handle long as well as short packets. If the value of "c" is a logic "0", the COM90C66 will only handle short packets (packets less than 254 bytes).                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| 000r p110    | CLEAR FLAGS                     | This command resets one or both flags of the COM90C66. If the value of "p" is a logic "1", the POR status flag is reset. If the value of "r" is a logic "1", the RECON status flag is reset.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| 0000 1000    | CLEAR RECEIVE<br>INTERRUPT      | This command is only used in the Command Chaining operation. Please refer to the Command Chaining section of this document for definition of this command.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

**Table 8 - Configuration Register**

| BIT  | BIT NAME                   | SYMBOL   | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|------|----------------------------|----------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7    | 16-Bit Enable              | 16EN     | This bit, if high, enables 16-bit operation of the device. A low level on this bit enables only 8-bit operation. This bit defaults to a logic "0" upon hardware reset.                                                                                                                                                                                                                                                                                                                                                                                            |

| 6    | Command<br>Chaining Enable | CCHEN    | This bit, if high, enables the Command Chaining operation of the device. Please refer to the Command Chaining section of this document for further details. A low level on this bit ensures software compatibility with previous SMSC ARCNET devices. This bit defaults to a logic "0" upon hardware reset.                                                                                                                                                                                                                                                       |

| 5    | Decode Mode                | DECODE   | In I/O Mapped applications, this bit is used to choose between an 8K or 16K block of ROM. In this case, a logic "0" defines 8K, while a logic "1" defines 16K. In Memory Mapped applications, this bit and the nENROM input are used to choose whether the nMEMCS16 signal will be generated by decoding a block of 128K or 2K. In this case, a logic "0" defines 128K, while a logic "1" defines 2K. For more details on the use of this bit, refer to the Memory vs. I/O Cycles section of this document. This bit defaults to a logic "0" upon hardware reset. |

| 4, 3 | Extended<br>Timeout 1, 2   | ET1, ET2 | These bits allow the network to operate over longer distances than the default four miles by controlling the Response Time, the Idle Time, and the Reconfiguration Time. For proper network operation, all nodes should be configured for the same timeout values. The bit combinations follow:    RESPONSE   IDLE   RECONFIGURATION                                                                                                                                                                                                                              |

Table 8 - Configuration Register

| BIT | BIT NAME        | SYMBOL        | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                              |

|-----|-----------------|---------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 2   | Wait State      | WAIT          | This bit is used to select the type of cycle. A logic "1" on this bit negates the IOCHRDY signal for approximately one or two XTAL1 clocks, creating one wait state. A logic "0" selects zero wait state arbitration to the buffer RAM and generates the Zero Wait State signal. Refer to the wait State Details section of this document for further information. This bit defaults to a logic "1" upon hardware reset. |

| 1   | I/O Access      | IO-<br>ACCESS | A logic "1" on this bit configures the buffer RAM for sequential I/O mapped accesses, while a logic "0" configures the buffer RAM for memory mapped accesses. This bit defaults to a logic "0" upon hardware reset.                                                                                                                                                                                                      |

| 0   | Transmitter Off | TXOFF         | A logic "1" on this bit disables the transmitter of the COM90C66, while the receiver remains functional. A logic "0" keeps the transmitter enabled. This bit may be used in diagnostic troubleshooting of the network or node. Refer to the Improved Diagnostics section of this document for further details. This bit defaults to a logic "0" upon hardware reset.                                                     |

Table 9 - Address Pointer Low Register

| BIT | BIT NAME    | SYMBOL | DESCRIPTION                                                                                  |

|-----|-------------|--------|----------------------------------------------------------------------------------------------|

| 7-0 | Address 7-0 | A7-A0  | These bits hold the lower eight address bits which provide the addresses to the on-chip RAM. |

Table 10 - Address Pointer High Register

| BIT       | BIT NAME       | SYMBOL       | DESCRIPTION                                                                                                                                                                                                                                                                                                                           |

|-----------|----------------|--------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7,<br>5-3 | (not used)     |              | These bits are undefined.                                                                                                                                                                                                                                                                                                             |

| 6         | Auto Increment | AUTO-<br>INC | This bit controls whether or not the address pointer will increment automatically when the device is in I/O Mapping Mode. A logic "1" on this bit will automatically increment the pointer after each access. A logic "0" will disable this function. Please refer to the Memory Vs. I/O section of this document for further detail. |

| 2-0       | Address 10-8   | A10-A8       | These bits hold the upper three address bits which provide the addresses to the on-chip RAM.                                                                                                                                                                                                                                          |

#### Configuration Register

The Configuration Register is a read/write register which can be accessed by the microprocessor to configure the different modes of the COM90C66. The register contents are as in Table 8. The Configuration Register defaults to the value 0001 1100 upon hardware reset only.

#### **Memory Select Register**

This register contains the decoded bits of the Memory Select 0-4 switch. For further details, refer to the Memory Address Decoding section of this document, as well as Figure 4 and Table 1.

# I/O Select Register

This register contains the decoded bits of the I/O Select 0-2 switch. For further details, refer to the I/O Address Decoding section of this document, as well as Figure 6 and Table 2.

# **Node ID Register**