# 4

# SINGLE CHIP DIGITAL DELAY IC

#### **■** GENERAL DESCRIPTION

NJU9702 is a single chip digital delay LSI designed for Dolby Prologic or other types surround processor.

It consists of 16k SRAM, input/output filter, A/D D/A converters and control logic.

The A/D and D/A converter is using a ADM (Adaptive Delta Modulation) method. Consequently, it is realized low noise and low distortion

The delay time can select from 64 mode of 0.5ms to 32.8ms in 0.5ms step, according to the application.

Furthermore, the NJU9702 has a sleep mode, mute function, and power on initialization function which perform low current consumption in the sleep mode, muting on/off control and power on initialization.

#### **■ FEATURES**

- ADM (Adaptive Delta Modulation) Method A/D and D/A Converter

- Low Noise and Low Distortion (No=95[dBV] TYP., THD=0.2[%] TYP.)

- 64 Delay Time Modes From 0.5ms To 32.8ms In 0.5ms step

- Low Current Consumption In Sleep Mode

- Input/Output Filter Built-in (Required External CR)

- A/D, D/A Converter Built-in (Required External CR)

- 16K SRAM (Internal)

- · Power on initialization

- Oscillation Circuit

- Package Outline

DIP24, SOP24

C-MOS Technology

#### **■ PACKAGE OUTLINE**

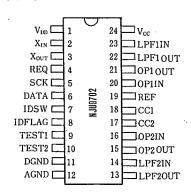

#### ■ PIN CONFIGURATION

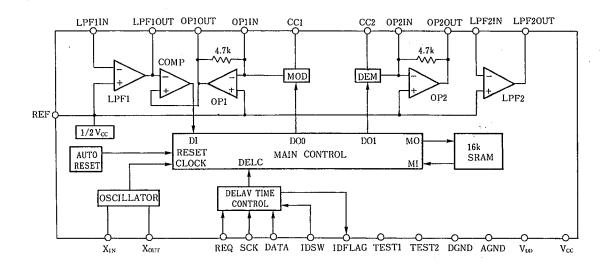

#### **■ BLOCK DIAGRAM**

# ■ TERMINAL DESCRIPTION

| NO.   | SYMBOL          | FUNCTIONS                                                |                                                       |                |                              |  |  |  |

|-------|-----------------|----------------------------------------------------------|-------------------------------------------------------|----------------|------------------------------|--|--|--|

| 1     | V <sub>DD</sub> | Voltage Supply for Digital Block V <sub>DD</sub> =5[V]   | oltage Supply for Digital Block V <sub>DD</sub> =5[V] |                |                              |  |  |  |

| 11    | DGND            | Digital GND DGND=0[V]                                    |                                                       |                |                              |  |  |  |

| 24    | Vcc             | Voltage Supply for Analog Block V <sub>CC</sub> =5[V]    |                                                       |                |                              |  |  |  |

| 12    | AGND            | Analog GND AGND=0[V]                                     |                                                       |                |                              |  |  |  |

| 19    | REF             | Analog Refernece Voltage REF=1/2 · V <sub>CC</sub>       |                                                       |                |                              |  |  |  |

| 2     | X <sub>IN</sub> | Oscillator Input Terminal                                |                                                       |                |                              |  |  |  |

| 3     | Xout            | Oscillator Output Terminal                               |                                                       | C              | 40 2MII O III                |  |  |  |

| 4     | REQ             | Data Request Input Terminal                              |                                                       | Connects       | to 2MHz ceramic Oscillator   |  |  |  |

| 5     | SCK             | Serial Data Shift Clock Input Terminal                   |                                                       |                |                              |  |  |  |

| 6     | DATA            | Serial Data Input Terminal                               |                                                       |                |                              |  |  |  |

| 7     | IDSW            | ID Switch (ID Code When Connect to the Common Bus)       |                                                       |                |                              |  |  |  |

| 8     | IDFLAG          | ID Flag (Data Input Confirmation and Serial Data Output) |                                                       |                |                              |  |  |  |

| 18    | CCI             | Current Control 1 Modulator                              |                                                       | ADM Controller |                              |  |  |  |

| 17    | CC2             | Current Control 2 Demodulator                            |                                                       | ADM CC         |                              |  |  |  |

| 9, 10 | TEST1, 2        | Test Terminal (Normally Connects to the GND)             |                                                       |                |                              |  |  |  |

| 23    | LPFIIN          | Lowpass Filter 1 Input                                   | 1,,,,                                                 | out Side       |                              |  |  |  |

| 22    | LPFIOUT         | Lowpass Filter 1 Output                                  | 1111                                                  | out side       | Constitute a Lowpass Filter  |  |  |  |

| 14    | LPF2IN          | Lowpass Filter 2 Input                                   | <u> </u>                                              | tput Side      | with external C and R.       |  |  |  |

| 13    | LPF2OUT         | Lowpass Filter 2 Output                                  | Ou                                                    | tput Side      |                              |  |  |  |

| 20    | OPIIN           | OP-AMP 1 Input                                           | 100                                                   | out Sida       |                              |  |  |  |

| 21    | OPIOUT          | OP-AMP 1 Output                                          | 111                                                   | out Side       | Constitute a Integrator with |  |  |  |

| 16    | OP2IN           | OP-AMP 2 Input                                           |                                                       | tput Side      | external C.                  |  |  |  |

| 15    | OP2OUT          | OP-AMP 2 Output                                          | Ou                                                    | tput side      |                              |  |  |  |

#### **■ FUNCTION DESCRIPTION**

The sampling frequency (fs) is 500KHz when master clock frequency is 2MHz.

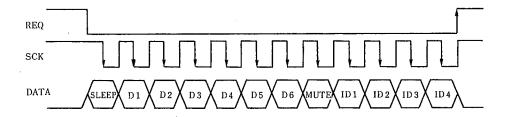

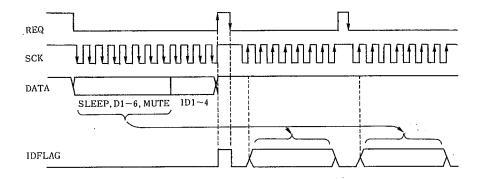

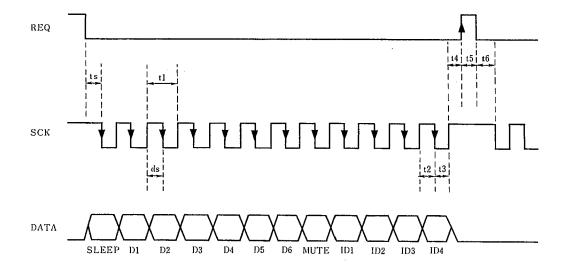

1)Data Format and Setting

The delay time is set by serial data.

The serial data is written into the NJU9702 sincronized by falling edge of shift clock (SCK) and the last 12 bit is effective before the data request (REQ) rising edge.

The time chart of serial data input is shown as fallows.

In order to avoid the shock noise output at the delay time setting, mute function using is recommended.

(note1)

When the corresponding DATA of ID code (refer 5) input to the NJU9702 during the REQ signal is "High", the DATA changed because of the NJU9702 always loading the latest 12-bit data.

Therefore following three operation methods are required when serial data input.

a)Fix the DATA terminal to "High" or "Low" except data setting period.

b)Fix the REQ terminal to "Low" except data setting period.

c)Fix the SCK terminal to "High" or "Low" after 12-bit data input.

(note2)

To use the mute after setting the delay time to avoided the shock noise.

### 2)Sleep Mode Setting

The sleep mode can be set by writing the code "1" (H level) to the Sleep bit of the serial data.

The sleep mode performs ① output muting, ② stop the internal clock, ③ stop the memory operation and put a low current consumption mode. Normally, this Sleep bit must be "0" (L level).

In order to avoid the shock noise output when the sleep mode released, mute function using is recommended.

| SLEEP | MODE   | FUNCTIONS                                                            |  |

|-------|--------|----------------------------------------------------------------------|--|

| . 0   | NORMAL | Normal operation .                                                   |  |

| 1     | SLEEP  | ①Output Muting ② Stop the Internal Clock ③ Stop the Memory Operation |  |

3)Delay Time Setting

64 kind of delay time from 0.5ms to 32.8ms in 0.5ms is set by D1 to D6 of the serial data.

| D6 | D5 | D4 | D3  | D2  | DI    | Delay T. |      |  |

|----|----|----|-----|-----|-------|----------|------|--|

|    |    |    |     | 0   | 0     | 0.5      |      |  |

|    |    |    | 0   | 1 [ | 1     | 1.0      |      |  |

|    |    |    |     | . 1 | 0     | 1.5      |      |  |

|    |    | 0  |     | ,   | 1     | 2.0      |      |  |

|    |    | U  |     |     | 0     | 2.6      |      |  |

|    |    |    | 1   | 0   | 1     | 3.1      |      |  |

|    |    |    | 1   | 1   | 0     | 3.6      |      |  |

|    |    |    | ]   | 1   | 1     | 4.1      |      |  |

|    | 0  |    |     |     | 0     | 4.6      |      |  |

|    |    |    |     | 0   | 5.1   |          |      |  |

|    |    |    | 0   | ı   | 0 5.6 |          |      |  |

|    |    |    |     | ١ ، | 1     | 6.1      |      |  |

|    |    | 1  |     |     | 0 6.7 |          |      |  |

|    | 1  |    |     | 0   | 1 7.2 |          |      |  |

|    |    |    | 1   | 1   | 0     | 7.7      |      |  |

|    |    |    |     | ,   | 1     | 8.2      |      |  |

| 0  |    |    | 0   | 0   | 0     | 8.7      |      |  |

|    |    |    |     |     | 1     | 9.2      |      |  |

|    |    |    |     | 1 - | 0     | 9.7      |      |  |

|    |    |    |     |     | 1     | 10.2     |      |  |

|    |    | 0  |     |     | 0     | 10.8     |      |  |

|    |    |    | . 0 | 1   | 11.3  |          |      |  |

|    |    |    | 1   |     | 0     | 11.8     |      |  |

|    | 1  |    |     | 1   | ı     | 12.3     |      |  |

|    |    |    |     |     | 0     | 12.8     |      |  |

|    |    |    |     | 0   | 1     | 13.3     |      |  |

|    |    |    | 0   |     | 0     | 13.8     |      |  |

|    |    |    |     | l   | 1     | 14.3     |      |  |

|    |    | 1. |     |     | 0     | 14.8     |      |  |

|    |    |    |     | 0   | 1     | 15.4     |      |  |

|    |    |    | 1   |     | 0     | 15.9     |      |  |

|    |    |    |     |     | 1     | 1        | 16.4 |  |

| $ \begin{array}{c ccccccccccccccccccccccccccccccccccc$ |                                              |

|--------------------------------------------------------|----------------------------------------------|

| $ \begin{array}{c ccccccccccccccccccccccccccccccccccc$ |                                              |

| 0 1 1 18.4<br>0 0 18.9<br>0 1 19.5                     |                                              |

| 0 1 18.4<br>0 0 18.9<br>1 19.5                         |                                              |

| 0 0 18.9                                               |                                              |

| 1 19.5                                                 |                                              |

| 0 200                                                  |                                              |

|                                                        |                                              |

| 20.5                                                   | 17.4<br>17.9<br>18.4<br>18.9<br>19.5<br>20.0 |

| 0 0 21.0                                               |                                              |

| 1   1   21.5                                           | _                                            |

| 0 22.0                                                 | _                                            |

| 1 22.5                                                 |                                              |

| 0 0 23.0                                               |                                              |

| 23.6                                                   |                                              |

| 1 0 24.1                                               | _                                            |

| 1 1 24.6                                               | _                                            |

| 0 0 25.1                                               |                                              |

| 0 1 25.6                                               |                                              |

| 1 0 26.1                                               |                                              |

| 0 1 26.6                                               |                                              |

| 0 0 27.1                                               |                                              |

| 1 27.6                                                 |                                              |

| 1 0 28.2                                               |                                              |

| 1 28.7                                                 |                                              |

| 0 0 29.2                                               |                                              |

| 0 1 29.7                                               |                                              |

| 1 0 30.2                                               |                                              |

| 1 30.7                                                 |                                              |

| 0 0 31.2                                               |                                              |

| 0 0 31.2                                               |                                              |

| 0 32.3                                                 |                                              |

| 1 32.8                                                 |                                              |

#### 4)Mute Setting

The mute mode can be set by writing the code "I" (H level) to the Mute bit of the serial data. Normally, this Mute bit must be "0" (L level).

| MUTE | MODE   | FUNCTIONS        |

|------|--------|------------------|

| 0    | NORMAL | Normal operation |

| 1    | SLEEP  | Output Muting    |

#### 5)ID Code Setting

The access froms the controller (CPU) is recognized the ID code input. It is useful when the NJU9702 connect the common bus togather with other LSI (s). The IDSW can select the prefixed ID code. If the other LSI using the ID code system and setting the same code already, please select other code by using this SW (IDSW).

| CONDITIONS | CODE SELECTION TERM. |     |     |     |     |

|------------|----------------------|-----|-----|-----|-----|

| CONDITIONS | IDSW                 | IDI | ID2 | ID3 | ID4 |

| 1          | 0                    | 0   | 0   | 1   | 0   |

| 2          | 1                    | 0   | 0   | 1   | 1   |

(note) ID code input except mentiond above, the NJU9702 can not be receive any data. In this case, the NJU9702 stil keeping the condition input before.

#### 6)IDFLAG

IDFLAG is terminal to check the setting of delay time and the setting conditions.

When the serial data is received by the NJU9702, the IDFLAG terminal output "H" level for controller (CPU)'s confermation.

After serial data writting, except the ID code (Sleep, D1 to D6, and Mute) can read out for checking. When the read out, ① set the "L" level of the request signal (REQ), ② input the clock signal are required. The data is output syncronized by the rising edge of the clock signal. The ID code can not read out even if over 8 clock input.

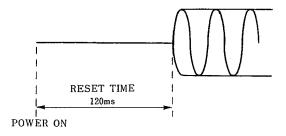

NJU9702 performs power-on-initialization when turn on the power. After 120ms pased the turn at the condition of  $V_{CC}=5V$ , Capacitor connecting to the REF terminal=4.7  $\mu$ F, it is released automatically. The 20.0ms delay time is set by the power-on-initialization.

The reset period of NJU9702 depends on an on-chip resistance "R" and a capacitor connected REF terminal. Next expression can compute the reset time.

Reset Time= $2.5 \times C (\mu F)$

Condition :  $V_{CC}=5V$ ,  $C=4.7 \mu F$  (REF terminal)

(REMARKS)

The NJU9702 needs to work a MUTE function for interruption that shock noise occurs when RESET is released.

The NJU9702 needs to supply a power to  $V_{DD}$  in adavance or at the mean time with other power source  $V_{CC}$ . If a power supplying sequence is not performed correctly, then power-on-initialization dose not work correctly.

4

### **■ ABSOLUTE MAXIMUM RATINGS**

(Ta=25°C)

| PARAMETER                   | SYMBOL           | RATINGS  | UNIT |

|-----------------------------|------------------|----------|------|

|                             | V <sub>DD</sub>  | 6.5      | V    |

| Supply Voltage              | Vcc              | 6.5      | V    |

| Operating Current           | lee              | 100      | mA   |

| Power Dissipation           | P <sub>D</sub>   | 500      | mV   |

| Operating Temperature Range | Topr             | -20~+75  | °C   |

| Storage Temperature Range   | T <sub>stg</sub> | -40~+125 | °C   |

(note)  $V_{DD}$  should be rise up before  $V_{CC}$  or same time. Otherwise power-on-initialization may not be operate corectly.

# **■ RECOMMENDED OPERATING CONDITIONS**

(V<sup>+</sup>=5V, Ta=25°C)

| PARAMETER         | SYMBOL           | CONDITIONS | MIN.               | TYP. | MAX.               | UNIT |

|-------------------|------------------|------------|--------------------|------|--------------------|------|

| Counties Valence  | V <sub>DD</sub>  |            | 4.5                | 5.0  | 5.5                | V    |

| Operating Voltage | V <sub>cc</sub>  |            | 4.5                | 5.0  | 5.5                | V    |

| Clock Frequency   | fek              |            |                    | 2.0  |                    | MHz  |

| Input Voltage "H" | VIII             |            | 0.7V <sub>DD</sub> |      | V <sub>DD</sub>    | V    |

| Input Voltage "L" | V <sub>IL</sub>  |            | 0                  | _    | 0.3V <sub>DD</sub> | V    |

| Sirial Clock      | f <sub>sek</sub> |            |                    | _    | 4.0                | MHz  |

## **■ ELECTRICAL CHARACTERISTICS**

$(V_{DD}=V_{CC}=5V, f=1 \text{kHz}, V_0=200 \text{mVrms}, Ta=25^{\circ}\text{C})$

| PARAMETER                  | SYMBOL            | TEST CONDITIONS                 | MIN. | TYP. | MAX. | UNIT |

|----------------------------|-------------------|---------------------------------|------|------|------|------|

| Operating Current          | Icc               | No Signal                       | _    | 16   | 35   | mA   |

| Voltage Gain               | Gv                | R <sub>L</sub> =47K Ω           | -3.5 | -0.5 | 2.5  | dB   |

| Max. Output Voltage        | Vo <sub>max</sub> | THD=10%                         | 0.7  | ì    | _    | Vrms |

| Output Distortion          | THD               | 30kHz LPF                       | _    | 0.2  | 1.0  | %    |

| Output Noise Voltage       | No                | DIN-AUDIO                       |      | -95  | -75  | dBV  |

| Supply Voltage Rejc. Ratio | SVRR              | V <sub>CC</sub> =20dBV, f=100Hz | _    | -40  | -25  | dB   |

| Frequency Characteristics  | f                 | -3dB, V <sub>0</sub> =100mVrms  | _    | 7    | -    | kHz  |

# ■ SERIAL DATA TIMING

| PARAMETER           | SYMBOL | MIN. | TYP. | MAX. | UNIT |

|---------------------|--------|------|------|------|------|

| SCK Clock Width     | tl     | 250  | _    |      | ns   |

| SCK Duty            | dş     | 40   | 50   | 60   | %    |

| Data Set-up Time    | 12     | 100  | t1/2 | _    | ns   |

| Data Hold Time      | 13     | 100  | t1/2 | -    | ns   |

| REQ Hold Time       | t4     | 100  |      | -    | ns   |

| REQ "H" Pulse Width | 15     | 100  | _    | _    | ns   |

| SCK Set-up Time     | t6     | 100  | -    | -    | ns   |

# ■ TIMING CHART

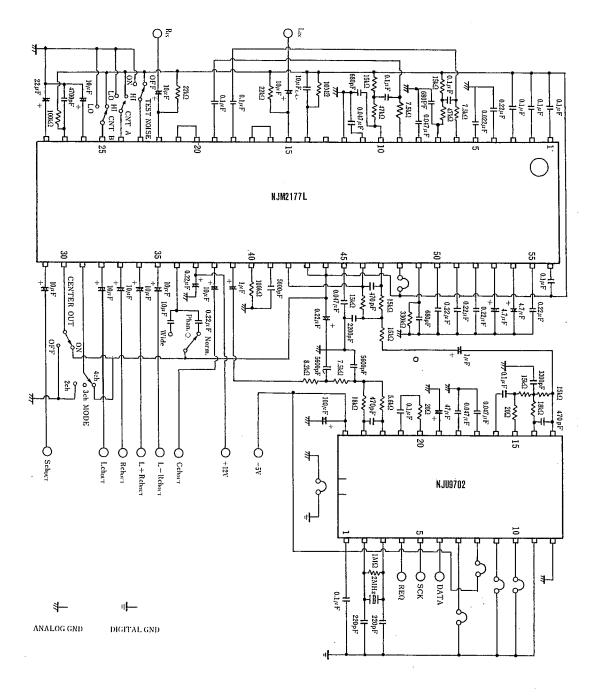

# ■ APLICATION CIRCUIT(1) (Combined with NJM2177)

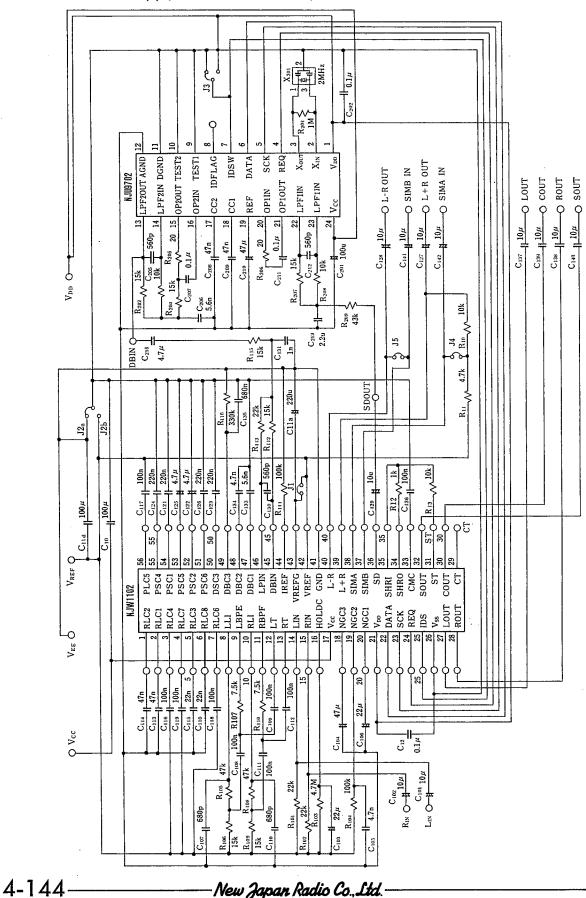

# ■ APLICATION CIRCUIT(2) (Combined with NJW1102)

| N |   |   | IQ | 7   | N | 2 |

|---|---|---|----|-----|---|---|

| 7 | U | L | IJ | , , | v | ~ |

# **MEMO**

[CAUTION]

The specifications on this databook are only given for information , without any guarantee as regards either mistakes or omissions. The application circuits in this databook are described only to show representative usages of the product and not intended for the guarantee or permission of any right including the industrial rights.