# **YGV627**

# **AVDP3E**

Advanced Video Display processor 3 Enhanced

#### **■ OUTLINE**

YGV627 is a VDP (Video Display Processor) that realizes higher resolution, multi-color and high speed drawing by adopting a synchronous DRAM as the video memory, while maintaining the register compatibility with YGV617B that is used for controlling the high minuteness On Screen Display (OSD).

Since the device is capable of displaying bitmap images with various resolutions ranging from NTSC to SVGA on the monitors with any size of screen including wide screen, it can be used for controlling OSD for various display units. Also, it is capable of representation of varied images in accordance with the application because numerous number of colors can be selected such as the one in the range from 16 to 65536 RGB color display, or natural image display using YCrCb.

In addition, the existing system can be up-graded easily thanks to the basic features from YGV617B such as a high speed drawing function, character drawing function, synchronization with external video signal, digital video input / output function, and hardware cursor display function.

# **■ FEATURES**

YGV627 is capable of selecting two modes by using the setting of ENH pin.

For convenience, the case of using  $\overline{ENH}$  pin with LOW level (enabled) is referred to as "expansion mode" in this document. In the expansion mode, all the functions can be used.

The case of using  $\overline{\text{ENH}}$  pin with HIGH level (disabled) is referred to as "compatibility mode". In the compatibility mode, the software compatibility with YGV617B is maintained, but the functions enhanced for YGV617B cannot be used. These modes should be used in accordance with the purpose of the application of this device.

#### [Display functions]

- Three screen configuration including bitmap screen, sprite cursor screen and external input video screen (or single color border screen)

- Monitor synchronization frequency, dot clock frequency, and display screen resolution can be specified optionally.

- Display dot clock up to 40 MHz (Example of resolution: NTSC, PAL, VGA, SVGA, NTSC wide, and VGA wide)

- Support with progressive scanning and interlaced scanning

- Resolution of sprite cursor screen is 32 X 32 dots. (The sprite cursor can also be used as cross-hair line cursor.)

- Smooth hardware scroll function

- Upper / lower two division display on the bitmap screen (The two sections can be scrolled independently).

- 256 words X 16 bits CLUT is built-in (The number of display colors of 32768 colors or 65536 colors can be selected.)

- Display colors: 16 palette color, 256 palette color, 32768 RGB color, 65536 RGB color, YCrCb422 (ITU601)

- YCrCb(ITU601) -to-8 bit RGB decoder is built-in.

- α blending function that mixes with external input screen or single color border screen. (64 intensity levels)

- Dot clock generation with built-in PLL circuit

- Generates dot clock that synchronizes with HSYNC of external video signal.

- Generates dot clock that synchronizes with external input clock. (such as sub-carrier clock)

YAMAHA CORPORATION:

YGV627 CATALOG CATALOG No.: LSI-4GV627A5

2002.12

# [Drawing functions]

Commands

Block transfer by word (CPU to VRAM, VRAM to CPU, VRAM to VRAM)

Font drawing, dot drawing and rectangular drawing.

• Drawing attribute Sets drawing clip area, drawing offset or drawing page, and designates bit mask, color mask,

logical operation (NOT, AND, OR, EOR etc.), or direction of transfer.

#### [Operational clock]

System clock (clock for drawing system): up to 33 MHz

Dot clock (clock for display system): up to 40 MHz

# [CPU interface]

• 16 bit or 8 bit asynchronous interface

• Provided with a video memory space up to 8M bytes and internal register space of 128 bytes.

• The video memory space and internal register space can be mapped indirectly with 16 byte registers.

• Built-in data buffer for memory space access and built-in data FIFO for drawing commands

• CPU interruption based on various conditions of display and drawing

• DMA transfer of drawing command data can be made when connected with external DMA controller

# [Video memory interface]

● Connected memory: 16M bits SDRAM (512k words X 16 bits X 2 banks) 1 piece

or 64M bits SDRAM (1M words X 16 bits X 4 banks) 1 piece

• SDRAM clock: up to 66 MHz (System clock multiplied by 2 or 4)

• Built-in FIFO for display data improves the drawing access efficiency and realizes high speed drawing.

# [Monitor interface]

• Analog RGB output with built-in DAC (8 bits for RGB individually)

• Digital video input / output (6 bits for RGB individually)

• Equipped with sub-carrier clock output, dot clock output, sync signal output, YS and attribute output pins.

# [Others]

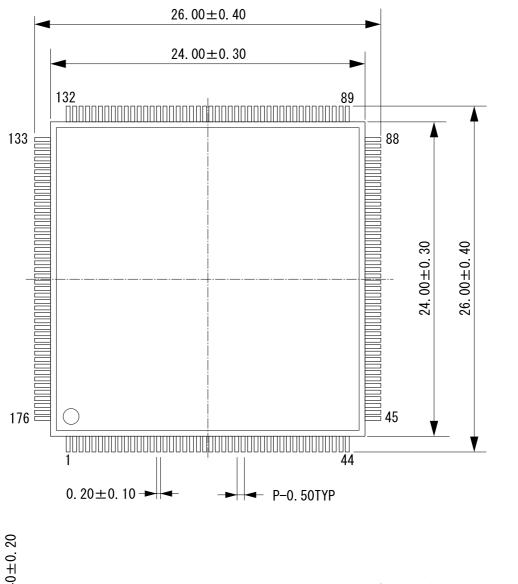

Package: 176LQFP (YGV627-V)CMOS, 3.3V single power supply

• Operating temperature range: -40 to +85 °C

#### Supplementary information:

For YGV627, Application Manual that details the specifications of the device and the evaluation board (MSY627DB01/02) are available in addition to this brochure.

The evaluation board is equipped with an SDRAM of 8 MB as a video memory. be realized when it is used with Hitachi's CPU board, Super H Solution Engine.

The device driver provided by Yamaha and attached to the evaluation board consists of the main body of the driver and API related layers, allowing the user to build it into the system easily according to the environment.

For the details of these products, inquire of the sales agents or our business

For CPU board, inquire of: Hitachi ULSI Systems Co., Ltd.

Tel:+81-42-351-6600

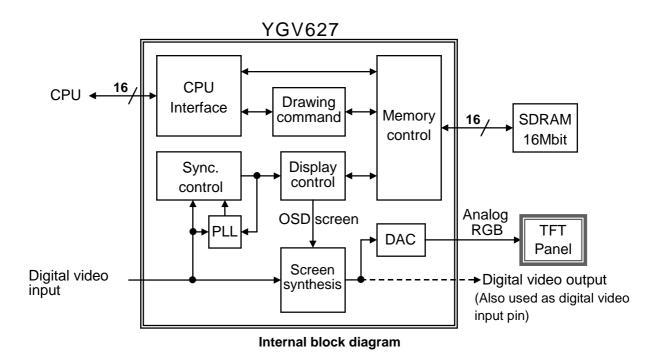

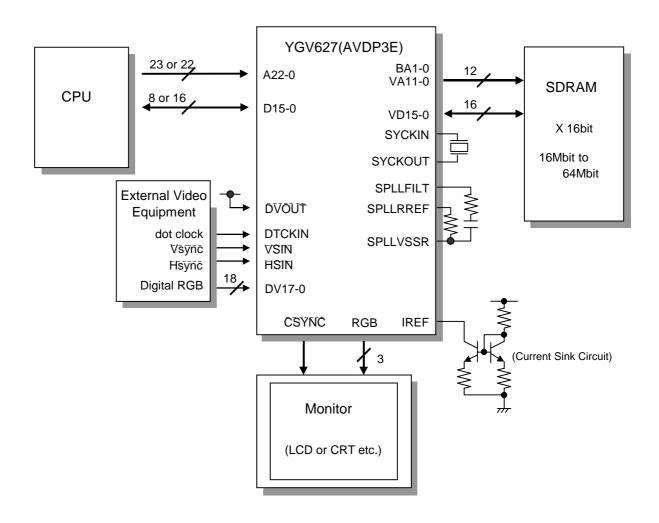

# **■ BLOCK DIAGRAM**

YGV627 is connected to the external memory bus of CPU as an external I/O device. As a video memory, SDRAM of up to 64M bits can be connected to local memory bus of YGV627 to send bitmap image data stored in the video memory into monitor as RGB signal in accordance with display scan timing.

YGV627 stores image data from CPU to the video memory by accessing video memory directly through CPU interface or by accessing the video memory using internal drawing command that transfers the data by block.

YGV627 has a function that synthesizes external images with bitmap image of YGV627 on the screen by synchronizing the scan timing of YGV627 with display timing of external video signals.

3

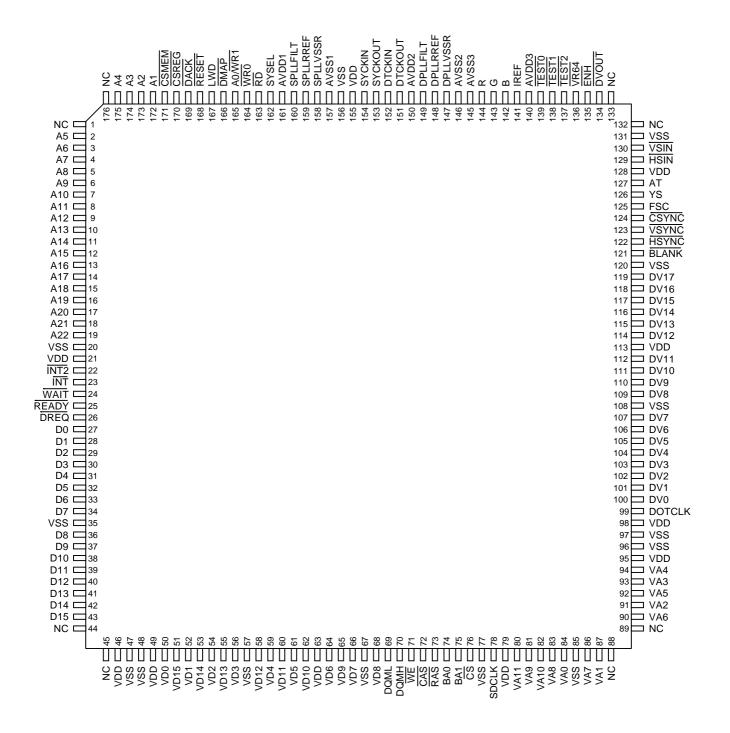

# **■ PIN ASSIGNMENT**

Top view

## **■ PIN FUNCTIONS**

# <CPU interface>

#### ● D15-0 (I/O: PULL UP)

This is a data bus for connecting with external processor. D15–D8 are not used when the CPU bus with 8 bit type (when low level is inputted to LWD). At this time, keep the D15–D8 open. These pins are provided with pull-up resistors respectively.

# ● A22-1 (I)

This is an address bus to be connected with external general purpose microcomputer. In the indirect access mode (high level inputted to  $\overline{DMAP}$  pin), input to A22-A4 pins are ignored when accessing  $\overline{CSREG}$  space. In the direct access mode (low level inputted to  $\overline{DMAP}$  pin), input to A22-A8 pins are ignored when accessing

YGV627 can be used as a YGV617B compatible device when A22 and A21 pins are fixed to low level. Unused pins must be set to low level or high level.

## ● CSREG (I)

It is a chip select signal input to register space (I/O). When this chip select signal is active, the read / write pulses inputted are made valid so that the registers in the YGV627 are accessed.

The function of this pin is the same as that of  $\overline{CSIO}$  pin of YGV617B.

# • CSMEM (I)

This is a chip select signal input pin for video memory port. The read / write pulse inputted while this signal is active can be used to directly access the video memory controlled by YGV627.

It is possible not to use  $CSMEM\_$  because the video memory can also be accessed from registers. In such case, it is necessary to input high level to  $\overline{CSMEM}$  pin.

# ● A0 / WR1, WR0 (I)

When chip select input is active, these pins control write access to YGV627.

D15–D8 are controlled by A0 /  $\overline{WR1}$ , and D7–D0 by  $\overline{WR0}$ .

When the CPU is 8 bit type, A0 /  $\overline{WR1}$  functions as CPU address bit 0.

#### • RD (1)

When chip select input is active,  $\overline{RD}$  controls read access from YGV627.

D15-D0 are in Output State in the period while both this signal and chip select signals are active.

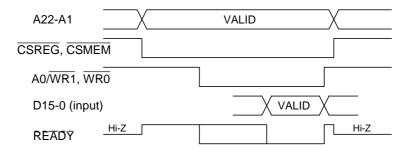

#### • READY (O: PULL UP, 3-state output)

This is data ready signal output to CPU. The  $\overline{READY}$  signal is made low when the internal state of YGV627 is accessible.  $\overline{READY}$  is a 3-state output. When  $\overline{CSREG}$  or  $\overline{CSMEM}$  is not active, it is high impedance state, and when  $\overline{CSREG}$  or  $\overline{CSMEM}$  is active and  $\overline{RD}$  or  $\overline{WR1}$ ,  $\overline{WR0}$  is not active, high level is outputted from  $\overline{READY}$

Some CPU must use WAIT signal instead of this signal.

**READY** signal at write access

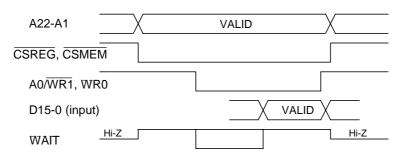

# • WAIT (O: PULL UP, 3-state output)

This is data wait signal output to CPU. When  $\overline{CSREG}$  or  $\overline{CSMEM}$  is active, the level of  $\overline{WAIT}$  signal is made low once with respect to  $\overline{RD}$  or  $\overline{WR1}$ ,  $\overline{WR0}$  in accordance with the internal state of YGV627, and in accessible state, it outputs high level.

When  $\overline{CSREG}$  or  $\overline{CSMEM}$  is not active, it is in high impedance state, and when  $\overline{CSREG}$  or  $\overline{CSMEM}$  is active and  $\overline{RD}$  or  $\overline{WR1}$ ,  $\overline{WR0}$  is not active, high level is outputted from this pin.

Some CPU must use READY signal instead of this signal.

WAIT signal at write access

# • INT (O: Open drain output)

This is interrupt request signal output to CPU.

This signal is made low when the internal state of YGV627 coincides with the setting conditions of registers.

This signal is reset with access to YGV627's internal register.

# • INT2 (O: High speed bus interrupt output)

This is an interrupt request signal output to CPU, and its output logical value is the same as that of  $\overline{\text{INT}}$ .

For high speed CPU bus, this output signal is used to avoid the influence of transit time caused by the pull-up resistor when the interrupt signal is negated.

Use INT or INT2 in accordance with the requirement of the system into which the YGV627 is built-in.

#### ● LWD (I: PULL UP)

This is used to select width of CPU data bus.

When this signal is high level input, the device is compatible with 16 bit system and when low level input, the device is compatible with 8 bit system respectively.

Since LWD is used for selection of a mode, always fix it to either level.

#### • RESET (I: PULL UP, with Schmitt)

Initial reset signal is inputted to  $\overline{RESET}$ . The reset signal input resets the internal state of the device and the internal registers are cleared to "0". (Some registers are loaded with initial value.)

Be sure to input the reset signal after power up.

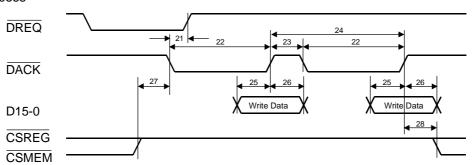

# ● DREQ (0)

DREQ outputs command data request signal to external DMA controller.

# ● DACK (I: PULL UP)

Command data transfer permission signal is inputted to  $\overline{DACK}$  in response to  $\overline{DREQ}$  signal to external DMA controller.

#### ● DMAP (I: PULL UP)

DMAP is used to select a register space mapping method.

When high level is inputted, 16 byte indirect mapping is selected. When low level is inputted, all the registers except CLUT are mapped directly in the 128 byte space. The input to  $\overline{DMAP}$  determines the valid address when  $\overline{CSREG}$  signal is active.

$\overline{DMAP}$  input signal is valid regardless of the state of  $\overline{ENH}$  input signal.

When using YGV627 in YGV617B compatibility mode, input high level to  $\overline{DMAP}$ .

Since  $\overline{DMAP}$  is for selection of a mode, always fix it to either level.

#### ● ENH (I: PULL UP)

This signal permits enhanced functions for YGV617B.

When high level is inputted, only the registers that are compatible with YGV617B are made valid, and the function of the enhanced registers are fixed to their default values. When low level is inputted, the function of the enhanced register is made valid.

This pin selects enable / disable of the enhanced functions and determines SDRAM access timing at the same time. In compatibility mode, the timing of access to SDRAM is equal to that of the performance of YGV617B, but in enhancement mode, the access performance is doubled.

Since ENH is for selection of a mode, always fix it to either level.

# < Video memory interface>

# ● BA1-0, VA11-VA0 (O)

These pins output address for SDRAM that is used as a video memory controlled by YGV627.

They <u>output</u> row address and column address on time sharing basis. BA1 and BA0 output bank address. However, when  $\overline{VR64}$  is a high level input (16M bits SDRAM is connected), VA11 becomes bank select.

When a read command or write command is sent to the SDRAM, VA10 functions as auto-precharge enable. Since these pins are always driven by YGV627, VRAM halt function of YGV617B cannot be used.

# ● VD15-VD0 ( I/O: PULL UP )

These pins constitute a data bus for SDRAM that is used as video memory controlled by YGV627. VRAM halt function of YGV617B cannot be used.

#### • RAS (0)

RAS outputs row address strobe signal for SDRAM that is used as a video memory controlled by YGV627. Since RAS is always driven by YGV627, VRAM halt function of YGV617B cannot be used.

#### • CAS (0)

CAS outputs column address strobe signal for SDRAM that is used as a video memory controlled by YGV627. Since CAS is always driven by YGV627, VRAM halt function of YGV617B cannot be used.

#### ● WE (0)

WE outputs write strobe signal for SDRAM that is used as a video memory controlled by YGV627. Since WE is always driven by YGV627, VRAM halt function of YGV617B cannot be used.

# ● DQMH, DQML (O)

These pins output data mask signal for SDRAM that is used as a video memory controlled by YGV627. DQMH is for VD15 – VD8, and DQML is for VD7–VD0.

# • <del>cs</del> (0)

This pin outputs chip select signal for SDRAM that is used as a video memory controlled by YGV627. YGV627 requires connection to SDRAM because the device uses  $\overline{\text{CS}}$  control for access to SDRAM for power saving purpose and against switching noise.

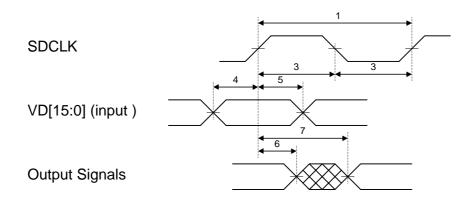

#### SDCLK (0)

This pin outputs clock for SDRAM that is used as a video memory controlled by YGV627.

Every output signal connected to SDRAM is outputted synchronizing with the rising edge of this clock. The read data from SDRAM is latched in the YGV627 at the rising edge of this clock. The clock enable pin of SDRAM should always be used in enable state.

# ▼R64 (I: PULL UP)

High level is inputted when the capacity of SDRAM that is used as a video memory controlled by YGV627 is 16M bits, or low level is inputted when the capacity is 64M bits. This signal determines the function of signal outputted from BA1, BA0, and VA11–VA0 pins. Connect with the SDRAM as specified below. Since this pin is for selection of a mode, always fix it to either level.

#### ★ $\overline{\text{VR64}}$ = "H" (when connected with 16M bits SDRAM)

| YGV627 pins | CS | RAS | CAS | WE                    | BA1 | BA0 | VA11 | VA10 | VA9 | VA8 | VA7-0 |

|-------------|----|-----|-----|-----------------------|-----|-----|------|------|-----|-----|-------|

| SDRAM pins  | CS | RAS | CAS | $\overline{	ext{WE}}$ |     |     | A11  | A10  | A9  | A8  | A7-0  |

# ★ $\overline{VR64}$ = "L" (when connected with 64M bits SDRAM)

| YGV627 pins | CS | RAS | CAS | WE | BA1 | BA0 | VA11 | VA10 | VA9 | VA8 | VA7-0 |

|-------------|----|-----|-----|----|-----|-----|------|------|-----|-----|-------|

| SDRAM pins  | CS | RAS | CAS | WE | A13 | A12 | A11  | A10  | A9  | A8  | A7-0  |

# < Display monitor interface>

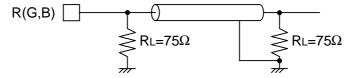

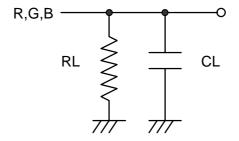

# • R, G, B (O: Analog output)

These pins output linear RGB signal. When a termination resistor of 37.5  $\Omega$  is connected, voltage amplitude with resolution of 8 bits (256 levels) is outputted. These pins can directly drive a monitor whose impedance is 75  $\Omega$  as shown below.

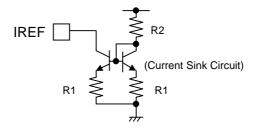

# ● IREF (I: Analog input)

Reference current for RGB DAC is inputted to this pin. The reference current of -9.38 mA provides amplitude of 0.7 Vp-p (typical value). When supplying the reference current, use a current sink circuit as shown below. For the following circuit, adjust the values of R1 and R2 so that the pin potential of IREF ( $V_{IREF}$ ) become approximately 1.37 V.

# • CSYNC (O)

This pin outputs a composite sync signal to external monitor. In interlace mode, it outputs equivalent pulse.

# • VSYNC (0)

This pin outputs vertical sync signal to external monitor.

# ● HSYNC (0)

This pin outputs horizontal sync signal to external monitor.

#### • BLANK (O)

This pin outputs a signal that indicates non-display period (blank period). Therefore, it can be used as a signal that indicates valid display period for LCD panel.

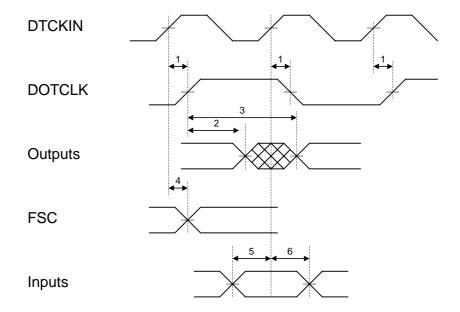

#### • FSC (0)

This pin outputs sub-carrier clock for video encoder.

This pin can output a clock inputted to DTCKIN pin divided by 1, 2, 4 or 8 which may be selected in accordance with the register setting. Inputting a clock of 14.318 MHz into DTCKIN pin provides sub-carrier clock of 3.58 MHz when divided by 4.

#### DOTCLK (O)

Output signal of display data (analog R, G, B, DV17-DV0, YS, AT) is outputted synchronizing with DOTCLK.

# ● DVOUT (I: PULL UP)

This pin selects input/output of external video data terminal.

The external video terminal becomes output when low level is inputted to this pin, or input when high level is inputted to this pin. The input/output of the external video data terminal can be changed with internal register EXIO(R#05). In such case, input high level to  $\overline{DVOUT}$  or keep it open.

#### ● DV17-0 (I/O: PULL UP)

These are input/output pins for digital external video data.

These pins become input when high level is inputted to  $\overline{DVOUT}$  and EXIO(R#05) ="0" is set, or becomes output when low level is inputted to  $\overline{DVOUT}$  pin or EXIO(R#05) ="1" is set.

For the external video data, a format with 6 bits for digital RGB individually, or a format with 6 bits for CrYCb individually can be selected.

The format of the input / output data is as shown below.

| DV17 16 15 14 13 12 | 11 10 9 8 7 6 | 5 4 3 2 1 0   |

|---------------------|---------------|---------------|

| R(Cr)5-0(I/O)       | G(Y)5-0(I/O)  | B(Cb)5-0(I/O) |

#### ● YS (O)

When performing superimposition, this pin outputs a signal that controls switching with external signal. When displaying bitmap plane, this pin outputs inversion signal for YSN bits that can be set by dot. In the border displaying period or blank period, this pin outputs inversion signal of border YS data.

#### • AT (O)

This pin outputs 1 bit attribute data that can be set by display dot. When ATE(R#05) signal of internal register is set to "0", the value set in the ATD bit of register is outputted regardless the display data.

When "1" is set for ATE signal, B0 (LSB of Blue) that is inputted to DAC for blue is outputted from AT pin. At this time, the same data of MSB is inputted to LSB of DAC for blue.

During the blank period, B0 of border is outputted when ATE signal is set to "1". When the signal is set to "1", the value set to ATD bit is outputted.

This signal can be used, for example, for specifying semi-transparency (YM) when externally mixing display data.

#### ● VSIN (I: PULL UP)

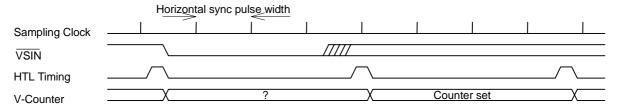

This signal resets the vertical timing of CRT controller block of YGV627. When this input signal is sampled with period equal to the pulse width of horizontal sync signal, and low level is detected three times consecutively, the internal V counter is set at the first HTL timing (horizontal sync signal start timing) immediately after the moment. In interlace mode, field identification is performed at the resetting of vertical timing by inputting composite sync signal of external video through this pin. This feature allows the superimposition synchronizing with frame period easily. If this signal is inputted during the display period, the display data of the next one field is not guaranteed. This pin can be kept open if this function is not used. The function of this pin is the same as that of VRESET pin of YGV617B.

# ● HSIN (I: PULL UP)

This signal resets the horizontal timing of CRT controller block of YGV627.

The horizontal timing is set to the horizontal sync starting position at the moment this signal falls from high level to low level, and at the same time, the phase of dot clock is reset.

When the built-in PLL is operated in the external sync mode, the input signal and output of HSYNC pin are locked.

If this signal is inputted during the display period, the display data of the next line is not guaranteed.

This pin can be kept open if this function is not used.

The function of this pin is the same as that of HRESET pin of YGV617B.

#### < Clocks>

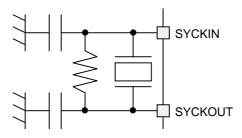

# • SYCKIN (I), SYCKOUT (O)

Crystal is connected to these pins to generate reference clock that is used in the system.

The built-in PLL produces SDRAM clock based on this clock. When supplying system clock and dot clock using the same clock through SYSEL pin (when low level is inputted to SYSEL), input the common clock through DTCKIN pin. At this time, input low level or high level signal into SYCKIN pin. SYCKOUT pin can be kept open.

When inputting externally generated clock, input it into SYCKIN pin.

SYCKIN and SYCKOUT pins are the same as VCKIN and VCKOUT pins of YGV617B.

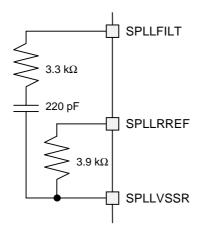

#### SPLLVSSR, SPLLRREF, SPLLFILT (Analog)

These pins are used to connect external resistors and capacitors for the built-in PLL that produces SDRAM clock.

#### Notes:

- 1. Arrange the components so that the parasitic capacitance among SPLLFILT, SPLLRREF and SPLLVSSR is minimized and the signals do not cross each other.

- 2. PLL may not lock if there is a time difference between the rising moment of AVDD (for PLL) and the rising moment of VDD (for Digital Logic).

#### ● SYSEL (I: PULL UP)

This signal selects the source of reference clock to be used in the system.

When low level is inputted to SYSEL, the system clock and dot clock use the same source of the clock. In this case, the common clock is inputted into DTCKIN. Therefore, there is no need to input clock into SYCKIN. When high level is inputted to SYSEL, SYCKIN pin input is used as the reference system clock independent from the dot clock.

When SYSEL is used with low level input, be sure to input stable clock into DTCKIN even if the clock produced by the built-in PLL is used as the dot clock. Since SYSEL is used for selection of a mode, always fix it to either level. This pin has a pull-up resistor.

The function of this pin is the same as that of VCKS pin of YGV617B.

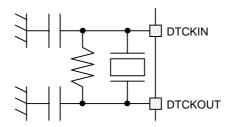

#### DTCKIN (I), DTCKOUT (O)

Crystal is connected to these pins to input dot clock.

When operating the built-in PLL in FSC sync mode, the reference clock is inputted to these pins. At this time, the clock with multiple of fsc is to be inputted. When PLL function is not used, this input clock is supplied directly to the CRTC block and displays data control block. When low level is inputted to SYSEL, it is also supplied as the reference system clock.

When inputted externally generated clock, input it into DTCKIN.

DTCKIN and DTCKOUT are the same as DCKIN and DCKOUT of YGV617B.

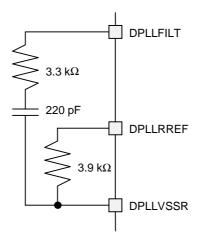

# • DPLLVSSR, DPLLRREF, DPLLFILT (Analog)

These pins are used to connect external resistors and capacitors for the built-in PLL that produces dot clock. When directly using DTCKIN input signal as dot clock without using the built-in PLL, keep DPLLFILT open and short-circuit between DPLLRREF and DPLLVSSR.

#### Notes:

- 1. Arrange the components so that the parasitic capacitance among DPLLFILT, DPLLRREF and DPLLVSSR is minimized and the signals do not cross each other.

- 2. PLL may not lock if there is a time difference between the rising moment of AVDD (for PLL) and the rising moment of VDD (for Digital Logic).

11

# <Other pins>

# ● TEST2-0 (I: Pull Up)

These pins are used for testing internal circuit of YGV627. Be sure to keep them open (without connecting any component) when using the device.

# ● AVDD1, AVSS1 (I)

These pins supply power to VCO analog circuit that generates SDRAM clock. Connect +3.3 V to AVDD1 and ground level to AVSS1.

# ● AVDD2, AVSS2 (I)

These pins supply power to VCO analog circuit that generates dot clock. Connect +3.3 V to AVDD2 and ground level to AVSS2.

#### ■ AVDD3, AVSS3 (1)

These pins supply power to analog circuit of RGB DAC section. Connect +3.3 V to AVDD3 and ground level to AVSS3.

#### • VDD, VSS (I)

These pins supply power to digital circuit of YGV627.

Connect +3.3 V to VDD and ground level to VSS. YGV627 has several VDD and VSS, all of which require power supply. Connect a bypass capacitor between VDD and VSS as a noise killer as close as possible to the pins. Power supplies, VDD, AVDD1, AVDD2 and AVDD3 are to be turned on at the same time, in principle. Turning on the power supplies at the same time means that they are to be turned on before the potential difference between them reaches and exceeds 0.6 V. Avoid making the potential difference 0.6 V or over continuously (over approximately one second), or the reliability of this LSI may be deteriorated. If the potential difference among the power supplies cannot be avoided, be sure to turn on/off VDD, AVDD1, AVDD2 and AVDD3 so that their voltages do not exceed VDD.

# **■ ELECTRICAL CHARACTERISTICS**

# • Absolute maximum ratings

| Items                                      | Symbol             | Ratings                      | Unit |

|--------------------------------------------|--------------------|------------------------------|------|

| Supply Voltage (VDD, AVDD)                 | V <sub>DD</sub> *1 | -0.5 to +4.6                 | V    |

| Input pin voltage (DTCKIN, SYCKIN, VD15-0) | Vı*1               | -0.5 to V <sub>DD</sub> +0.5 | V    |

| Input pin voltage (other than the above)   | Vı*1               | −0.5 to 5.5                  | V    |

| Output pin voltage                         | Vo <sup>*1</sup>   | -0.5 to VDD+0.5              | V    |

| Output pin current                         | lo                 | -20 to +20                   | mA   |

| Storage temperature                        | Tstg               | -50 to +125                  | °C   |

$<sup>^{*1}</sup>$ : Value with respect to VSS (GND) = 0V

# • Recommended operating conditions

| Items                                           | Symbol             | Min.               | Тур. | Max.     | Unit |

|-------------------------------------------------|--------------------|--------------------|------|----------|------|

| Supply Voltage (VDD, AVDD)                      | V <sub>DD</sub> *1 | 3.0                | 3.3  | 3.6      | V    |

| Supply Voltage                                  | Vss                |                    | 0    |          | V    |

| Low level input voltage (VD15-0)                | VIL*1              | -0.3               |      | 0.8      | V    |

| High level input voltage (VD15-0)               | V <sub>IH</sub> *1 | 2.2                |      | VDD +0.3 | V    |

| Low level input voltage (DTCKIN, SYCKIN)        | VIL*1              | -0.3               |      | 0.3Vpd   | V    |

| High level input voltage (DTCKIN, SYCKIN)       | V <sub>IH</sub> *1 | 0.7V <sub>DD</sub> |      | VDD +0.3 | V    |

| Low level input voltage (RESET pin )            | VIL*1              | -0.3               |      | 0.8      | ٧    |

| High level input voltage (RESET pin )           | V <sub>IH</sub> *1 | 2.4                |      | 5.3      | V    |

| Low level input voltage (other than the above)  | VIL*1              | -0.3               |      | 0.8      | V    |

| High level input voltage (other than the above) | V <sub>IH</sub> *1 | 2.2                |      | 5.3      | V    |

| Ambient operating temperature                   | Тор                | -40                |      | +85      | °C   |

<sup>\*1:</sup> Value with respect to Vss (GND) = 0V

# • Electrical characteristics under recommended operating conditions

# • DC characteristics

| Items                        | Symbol            | Min. | Тур. | Max. | Unit |

|------------------------------|-------------------|------|------|------|------|

| Low level output voltage     | Vol*1             |      |      | 0.4  | V    |

| High level output voltage *2 | Vон <sup>*3</sup> | 2.4  |      |      | V    |

| Input leakage current        | Iμ                |      |      | 10   | μΑ   |

| Output leakage current       | ILO               |      |      | 25   | μΑ   |

| Current consumption*4 *5     | IDD               |      | 180  | 220  | mA   |

<sup>\*1:</sup> Measurement condition IoL=1.6mA

# • Pin capacity

| Items                       | Symbol | Min. | Тур. | Max. | Unit |

|-----------------------------|--------|------|------|------|------|

| Input pin capacity          | Cı     |      |      | 8    | pF   |

| Output pin capacity         | Со     |      |      | 10   | pF   |

| Input / Output pin capacity | Сю     |      |      | 12   | pF   |

<sup>\*2:</sup> Except Open Drain pin

<sup>\*3:</sup> Measurement condition IoH= -1.0mA

<sup>\*4:</sup> Typical value means average value obtained when a general image is displayed.

<sup>\*5:</sup> Maximum value means instantaneous maximum value obtained when the internal circuit is fully operated.

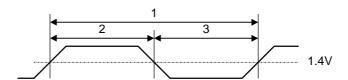

# AC characteristics

NOTE: When measuring timing, the input signal reference level is 1.4 V and transition time tT=1 ns. The transition time is measured at the time of  $V_{IH}$  and  $V_{IL}$ . When the transition time is over 1 ns, the input signal reference level is  $V_{IH}$  (minimum value) and  $V_{IL}$  (maximum value).

# Clock input

| No. | Items                                | Symbol         | Min.  | Тур.                | Max.             | Unit |

|-----|--------------------------------------|----------------|-------|---------------------|------------------|------|

| 1   | DTCKIN: Input Clock Frequency        | <b>f</b> DTCK  | 1     | 14.32 <sup>*1</sup> | 40 <sup>*2</sup> | MHz  |

| '   | DTCKIN: Clock Cycle Time             | <b>t</b> DCK   | 25    |                     | 1000             |      |

| 2   | DTCKIN: Clock High Level Pulse Width | twhdck         | 11.25 |                     |                  | ns   |

| 3   | DTCKIN: Clock Low Level Pulse Width  | twlock         | 11.25 |                     |                  |      |

|     | DTCKIN : Clock Duty                  | Dock           | 45    | 50                  | 55               | %    |

| 1   | SYCKIN: Input Clock Frequency        | fsck           | 1     | 16.6                | 33.3             | MHz  |

| ı   | SYCKIN : Clock Cycle Time            | tsck           | 30    |                     | 1000             |      |

| 2   | SYCKIN: Clock High Level Pulse Width | <b>twh</b> sck | 13.5  |                     |                  | ns   |

| 3   | SYCKIN: Clock Low Level Pulse Width  | twlsck         | 13.5  |                     |                  |      |

|     | SYCKIN : Clock Duty                  | Dsck           | 45    | 50                  | 55               | %    |

<sup>\*1:</sup> This is the case of NTSC. Use of other scanning mode allows optional selection of 13.5 MHz, 27 MHz, 28.6 MHz, 33 MHz or other frequency.

When oscillating clock directly with XTAL, the maximum frequency is 33.3 MHz. When inputting clock over 33.3 MHz, input clock signal oscillated externally with clock module or other means into DTCKIN pin.

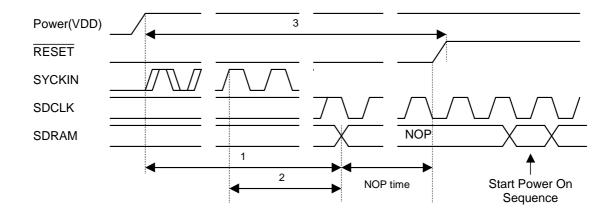

# Reset input

| No. | Items                                        | Symbol | Min. | Тур. | Max. | Unit             |

|-----|----------------------------------------------|--------|------|------|------|------------------|

| 1   | SDCLK stabilization time after VDD input*1   |        | 1    |      |      | ms               |

|     | SDCLK signal stabilization time after SYCKIN |        | 1    |      |      | ms               |

| 3   | RESET Input Pulse Width                      | twrs   | 1.5  |      |      | ms <sup>*2</sup> |

Since YGV627 produces SDRAM clock with PLL, it requires approximately 1ms after stabilization of power supply level and SYCKIN pin input clock for stabilization of clock. Moreover, in power on sequence of SDRAM, NOP state $^{*3}$  of 100  $\mu$ s to 500  $\mu$ s or over is needed after stabilization of the power supply level and clock frequency. Keep these times with assert time of  $\overline{RESET}$  pin (low level pulse width tWRS).

After negating RESET signal, power on sequence of SDRAM is started by issuing Precharge All command (PALL).

<sup>\*1:</sup> This rule applies from the moment all power supplies, VDD pin, AVDD1 pin, AVDD2 pin, and AVDD3 pin are turned on.

$<sup>^{*2}</sup>$ : The value when stabilization time of SDRAM is 500  $\mu s$

<sup>\*3:</sup> For the time needed for NOP state, confirm the specification of SDRAM to be adopted.

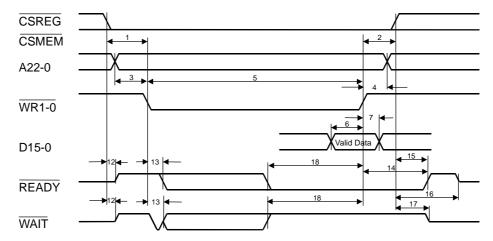

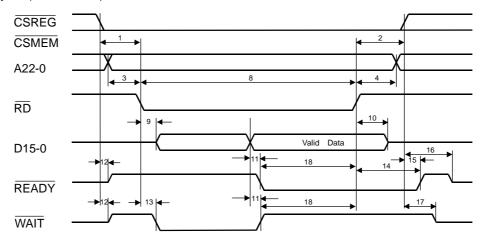

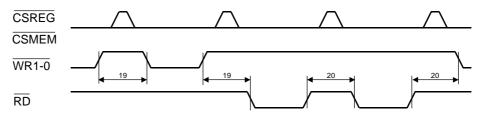

# • System interface (Measurement condition: C<sub>L</sub>=50 PF)

| No. | Items                                                   | Symbol         | Min.       | Тур. | Max. | Unit | Note |

|-----|---------------------------------------------------------|----------------|------------|------|------|------|------|

| 1   | CSREG, CSMEM setup time                                 | tscs           | 2          |      |      |      |      |

| 2   | CSREG, CSMEM hold time                                  | thcs           | 0          |      |      |      |      |

| 3   | A22-0 setup time                                        | tsa            | 5          |      |      |      |      |

| 4   | A22–0 hold time                                         | tha            | 0          |      |      |      |      |

| 5   | WR1-0 pulse width (@no wait access)                     | <b>tw</b> iwr  | 20         |      |      |      | 7    |

| 6   | D15–0 setup time (@write access)                        | tsd            | 10         |      |      |      |      |

| 7   | D15–0 hold time (@write access)                         | th□            | 3          |      |      |      |      |

| 8   | RD pulse width (@no wait access)                        | <b>tw</b> ird  | 2tsck+15   |      |      |      | 1    |

| 9   | D15-0 turn on time (@read access)                       | tond           | 0          |      | 15   |      |      |

| 10  | D15–0 turn off time (@read access)                      | toff□          | 5          |      | 15   |      |      |

| 11  | D15-0 valid data output delay time (@read access)       | td□            |            |      | 0    |      |      |

| 12  | READY, WAIT turn on time (Z to H)                       | tonrw          | 0          |      | 5    |      |      |

| 13  | READY, WAIT delay time from WR1-0 active (H to L)       | <b>td</b> RW   |            |      | 45   |      | 6    |

| 14  | READY hold time from WR1-0, RD inactive (L to H)        | threwr         | 3          |      | 18   |      |      |

| 15  | READY hold time from CSREG, CSMEM inactive              | threcs         | 3          |      | 18   | ns   |      |

| 16  | READY turn off time after CSREG, CSMEM inactive         | toffrc         | 7          |      | 18   | 113  |      |

| 17  | WAIT turn off time after CSREG, CSMEM inactive          | toffwc         |            |      | 5    |      |      |

| 18  | WR1-0, RD hold time after READY active or WAIT inactive | thwr           |            |      | 0    |      |      |

| 19  | WR1-0, RD "high" level width after write access         | twhwRW         | 10         |      |      |      | 2    |

| 19  | WR1-0, RD "high" level width after write access         | <b>twh</b> wrw | 2.5tsck+15 |      |      |      | 3    |

| 19  | WR1-0, RD "high" level width after write access         | <b>twh</b> wrw | 5.5tsck+15 |      |      |      | 4    |

| 20  | WR1-0, RD "high" level width after read access          | <b>twh</b> wrr | 10         |      |      |      |      |

| 21  | DREQ hold time                                          | <b>th</b> DRQ  | 0          |      |      |      |      |

| 22  | DACK pulse width                                        | <b>tw</b> idak | 20         |      |      |      |      |

| 23  | DACK high level width (@ 8bits system bus (LWD= "0"))   | <b>twh</b> dak | 10         |      |      |      | 5    |

| 24  | DACK cycle time (@ 8bits system bus (LWD= "0"))         | <b>tcy</b> dak | 2tsck      |      |      |      | 5    |

| 25  | D15–0 setup time (@DMA access)                          | <b>ts</b> DMA  | 10         |      |      |      |      |

| 26  | D15-0 hold time (@DMA access)                           | th             | 10         |      |      |      |      |

| 27  | DACK delay time after CS inactive                       | <b>td</b> DAK  | 5          |      |      |      |      |

| 28  | CSREG, CSMEMdelay time after DACK inactive              | thcak          | 5          |      |      |      |      |

Note 1 : Defined with time from the fall of  $\overline{RD}$  to the time settled read data is outputted. Actually, it is necessary to keep setup time for the rise of  $\overline{RD}$ .

Note 2: When hardware wait is permitted

Note 3: After write access to other than R#00-0E when hardware wait is prohibited (No Wait mode)

Note 4: After write access to R#00-0E when hardware wait is prohibited (No Wait mode)

Note 5: Valid only when system bus is 8 bits (low level is inputted to LWD pin)

Note 6: Value at the time when sufficient time elapses from write access immediately before

Note 7: Conditions of both twiwr  $\geq$  20ns and twiwr  $\geq$  tdrw must be met when  $\overline{WAIT}$  and  $\overline{READY}$  are used.

• Write cycle (WR1-0 control)

• Read cycle (RD control)

• WR1-0, RD input prohibited period

DMA access

# • SDRAM interface (Measurement condition C<sub>L</sub>=30 PF)

| No. | Items                          | Symbol  | Min. | Тур. | Max. | Unit | Note |

|-----|--------------------------------|---------|------|------|------|------|------|

| 1   | SDCLK:cycle time               | tcSDCLK | 15   |      |      |      | 1,2  |

| 2   | SDCLK:clock jitter             | -       |      |      | ±1   |      | 1    |

| 3   | SDCLK:clock width              | twSDCLK | 5    |      |      |      | 1    |

| 4   | VD[15:0]:input data setup time | tsVD    | 2    |      |      | ns   | 1    |

| 5   | VD[15:0]:input data hold time  | thVD    | 2    |      |      |      | 1    |

| 6   | Output signal:hold time        | thSDO   | 2    |      |      |      | 3    |

| 7   | Output signal:delay time       | tdSDO   |      |      | 12   |      | 3    |

Note 1: PLL must be in stabilized state.

Note 2: SDCLK is oscillated with built-in VCO. Oscillated frequency range of VCO ranges from 110 MHz to 134 MHz. Therefore, the frequency range of SDCLK must be set for 55 MHz through 66.6 MHz.

Note 3: Output signals are those outputted from the following pins. BA1-0, VA11-0, VD15-0, CS, RAS, CAS, WE, DQMH, or DQML

# • Monitor interface (Measurement condition C<sub>L</sub>=30 PF)

| No. | Items                                                | Symbol   | Min. | Тур. | Max. | Unit | Note |

|-----|------------------------------------------------------|----------|------|------|------|------|------|

| 1   | DOTCLK:delay time                                    | tdDOTCLK |      |      | 15   |      | 1    |

| 2   | CSYNC, VSYNC, HSYNC, DV17–0 (out) :output hold time  | thDISP   | 0    |      |      |      |      |

| 3   | CSYNC, VSYNC, HSYNC, DV17-0 (out) :output delay time | tdDISP   |      |      | 15   | ns   |      |

| 4   | FSC:delay time                                       | tdFSC    |      |      | 15   | 113  |      |

| 5   | HSIN, VSIN, DV17-0 (in): input setup time            | tsSIN    | 10   |      |      |      |      |

| 6   | HSIN, VSIN, DV17-0 (in): input hold time             | thSIN    | 5    |      |      |      |      |

Note 1: When PLL is not used (R#22:DCKS= "0")

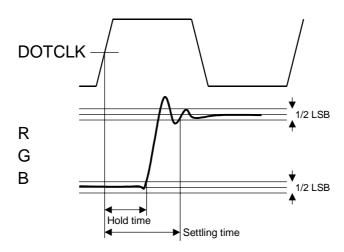

# • Characteristics of RGB output pins

| Items                           | Symbol       | Min. | Тур. | Max. | Unit |

|---------------------------------|--------------|------|------|------|------|

| Resolution                      |              |      |      | 8    | bit  |

| Settling time                   | R∟=37.5Ω     |      |      | 24   | ns   |

| Output hold time                | CL=30pF      | 5    |      |      | ns   |

| Amplitude of output voltage     | IREF=-9.38mA |      | 0.7  |      | V    |

| Deviation of Vp-p of R, G and B |              |      |      | 3    | %    |

Settling time is defined as the period from the rise of DOTCLK to the time when output level of DAC enters in the range of  $\pm 1/2$  LSB of the DOTCLK level after changing.

Output hold time is defined as the period from the rise of DOTCLK to the time when output level of DAC goes out of the range of  $\pm 1/2$  LSB of the DOTCLK level after changing.

# Measurement circuit

# **■** Example of System Configuration

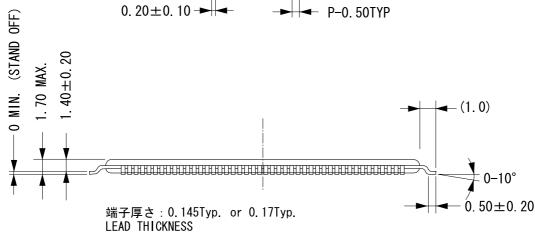

# **■** External Dimensions of Package

モールドコーナー形状は、この図面と若干異なるタイプのものもあります。

カッコ内の寸法値は参考値とする。モールド外形寸法はバリを含まない。

単位(UNIT): mm(millimeters)

The shape of the molded corner may slightly different from the shape in this diagram.

The figure in the parenthesis ( ) should be used as a reference. Plastic body dimensions do not include burr of resin.

UNIT: mm

注) 表面実装LSIは保管条件及び、半田付けについての特別な配慮が必要です。 詳しくはヤマハ代理店までお問い合わせ下さい。

Note: The LSIs for surface mount need special consideration on storage and soldering conditions. For detailed information, Please contact your nearest Yamaha agent.

# IMPORTANT NOTICE

- 1. Yamaha reserves the right to make changes to its Products and to this document without notice. The information contained in this document has been carefully checked and is believed to be reliable. However, Yamaha assumes no responsibilities for inaccuracies and makes no commitment to update or to keep current the information contained in this document.

- 2. These Yamaha Products are designed only for commercial and normal industrial applications, and are not suitable for other uses, such as medical life support equipment, nuclear facilities, critical care equipment or any other application the failure of which could lead to death, personal injury or environmental or property damage. Use of the Products in any such application is at the customer's sole risk and expense.

- 3. YAMAHA ASSUMES NO LIABILITY FOR INCIDENTAL, CONSEQUENTIAL, OR SPECIAL DAMAGES OR INJURY THAT MAY RESULT FROM MISAPPLICATION OR IMPROPER USE OR OPERATION OF THE PRODUCTS.

- 4. YAMAHA MAKES NO WARRANTY OR REPRESENTATION THAT THE PRODUCTS ARE SUBJECT TO INTELLECTUAL PROPERTY LICENSE FROM YAMAHA OR ANY THIRD PARTY, AND YAMAHA MAKES NO WARRANTY OR REPRESENTATION OF NON-INFRANGIMENT WITH RESPECT TO THE PRODUCTS. YAMAHA SPECIALLY EXCLUDES ANY LIABILITY TO THE CUSTOMER OR ANY THIRD PARTY ARISING FROM OR RELATED TO THE PRODUCTS' INFRINGEMENT OF ANY THIRD PARTY'S INTELLECTUAL PROPERTY RIGHTS, INCLUDING THE PATENT, COPYRIGHT, TRADEMARK OR TRADE SECRET RIGHTS OF ANY THIRD PARTY.

- 5. EXAMPLES OF USE DESCRIBED HEREIN ARE MERELY TO INDICATE THE CHARACTERISTICS AND PERFORMANCE OF YAMAHA PRODUCTS. YAMAHA ASSUMES NO RESPONSIBILITY FOR ANY INTELLECTUAL PROPERTY CLAIMS OR OTHER PROBLEMS THAT MAY RESULT FROM APPLICATIONS BASED ON THE EXAMPLES DESCRIBED HEREIN. YAMAHA MAKES NO WARRANTY WITH RESPECT TO THE PRODUCTS, EXPRESS OR IMPLIED, INCLUDING, BUT NOT LIMITED TO THE WARRANTIES OF MERCHANTABILITY, FITNESS FOR A PARTICULAR USE AND TITLE.

Notice

The specifications of this product are subject to improvement changes without prior notice.

AGENCY -

# YAMAHA CORPORATION

Address inquiries to:

Semiconductor Sales & Marketing Department

Head Office 203, Matsunokijima, Toyooka-mura

Iwata-gun, Shizuoka-ken, 438-0192, Japan Tel. +81-539-62-4918 Fax. +81-539-62-5054

■ Tokyo Office 2-17-11. Takanawa, Minato-ku,

Tokyo, 108-8568, Japan Tel. +81-3-5488-5431 Fax. +81-3-5488-5088

Osaka Office 3-12-12, Minami Senba, Chuo-ku,

Osaka City, Osaka, 542-0081, Japan Tel. +81-6-6252-6221 Fax. +81-6-6252-6229