# **OKI** Semiconductor

Preliminary. This version: Jan. 1998 Previous version: Dec. 1996

# MSM5416282

262,144-Word × 16-Bit Multiport DRAM

#### DESCRIPTION

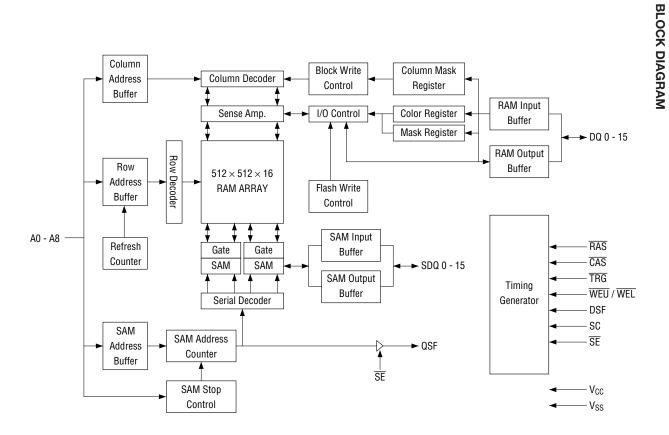

The MSM5416282 is a 4-Mbit CMOS multiport DRAM composed of a 262,144-word by 16-bit dynamic RAM, and a 512-word by 16-bit SAM. Its RAM and SAM operate independently and asynchronously.

It supports three types of operations: random access to RAM port, high speed serial access to SAM port, and bidirectional transfer of data between any selected row in the RAM port and the SAM port. In addition to the conventional multiport DRAM operating modes, the MSM5416282 features block write and flash write functions on the RAM port, and a split data transfer capability on the SAM port. The SAM port requires no refresh operation because it uses static CMOS flip-flops.

### **FEATURES**

- Single power supply: 5 V ±10%

- Full TTL compatibility

- Multiport organization

RAM: 256K word  $\times$  16 bits SAM:  $512 \text{ word} \times 16 \text{ bits}$

- Fast page mode

- Write per bit

- Byte write

- Masked flash write

- Masked block write (8 columns)

- Package:

64-pin 525 mil plastic SSOP (SSOP64-P-525-0.80-K)

- Hidden refresh

- Serial read/write

- 512 tap location

- Bidirectional data transfer

- Split transfer

- Masked write transfer

(Product: MSM5416282-xxGS-K) xx indicates speed rank.

#### PRODUCT FAMILY

| Familia       | Acces | Access Time |        | Time  | Power Dissipation |         |  |

|---------------|-------|-------------|--------|-------|-------------------|---------|--|

| Family        | RAM   | SAM         | RAM    | SAM   | Operating         | Standby |  |

| MSM5416282-50 | 50 ns | 17 ns       | 110 ns | 20 ns | 180 mA            | 8 mA    |  |

| MSM5416282-60 | 60 ns | 18 ns       | 120 ns | 22 ns | 170 mA            | 8 mA    |  |

| MSM5416282-70 | 70 ns | 20 ns       | 140 ns | 22 ns | 160 mA            | 8 mA    |  |

| • | CAS | before | RAS | refresh |

|---|-----|--------|-----|---------|

- Refresh: 512 cycles/8 ms

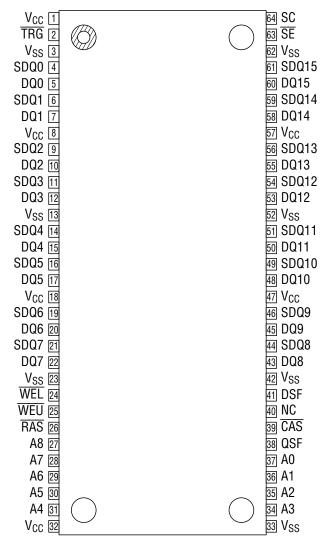

# **PIN CONFIGURATION (TOP VIEW)**

64-Pin Plastic SSOP

| Pin Name     | Function                        | Pin Name | Function                |

|--------------|---------------------------------|----------|-------------------------|

| A0 - A8      | Address Input                   | SC       | Serial Clock            |

| DQ0 - DQ15   | RAM Inputs/Outputs              | SE       | SAM Port Enable         |

| SDQ0 - SDQ15 | SDQ0 - SDQ15 SAM Inputs/Outputs |          | Special Function Input  |

| RAS          | Row Address Strobe              | QSF      | Special Function Output |

| CAS          | Column Address Strobe           | Vcc      | Power Supply (5 V)      |

| WEL          | Write Enable Lower              | Vss      | Ground (0 V)            |

| WEU          | Write Enable Upper              | NC       | No Connection           |

| TRG          | Transfer/Output Enable          |          |                         |

Note: The same power supply voltage must be provided to every  $V_{CC}$  pin, and the same GND voltage level must be provided to every  $V_{SS}$  pin.

3/37

### **ELECTRICAL CHARACTERISTICS**

# **Absolute Maximum Ratings**

(Note: 1)

| Parameter             | Symbol           | Condition   | Rating      | Unit |

|-----------------------|------------------|-------------|-------------|------|

| Input Output Voltage  | V <sub>T</sub>   | Ta = 25°C   | -1.0 to 7.0 | V    |

| Output Current        | I <sub>OS</sub>  | Ta = 25°C   | 50          | mA   |

| Power Dissipation     | P <sub>D</sub>   | Ta = 25°C   | 1           | W    |

| Operating Temperature | T <sub>opr</sub> | _           | 0 to 70     | °C   |

| Storage Temperature   | T <sub>stg</sub> | <del></del> | -55 to 150  | °C   |

## **Recommended Operating Conditions**

$(Ta = 0^{\circ}C \text{ to } 70^{\circ}C) \text{ (Note: 2)}$

| Parameter            | Symbol          | Min. | Тур. | Max. | Unit |

|----------------------|-----------------|------|------|------|------|

| Power Supply Voltage | V <sub>CC</sub> | 4.5  | 5.0  | 5.5  | V    |

| Input High Voltage   | V <sub>IH</sub> | 2.4  |      | 6.5  | V    |

| Input Low Voltage    | V <sub>IL</sub> | -1.0 |      | 0.8  | V    |

# Capacitance

$(V_{CC} = 5 V \pm 10\%, f = 1 MHz, Ta = 25^{\circ}C)$

| Parameter                | Symbol               | Min.         | Max. | Unit |

|--------------------------|----------------------|--------------|------|------|

| Input Capacitance        | Ci                   | _            | 6    | pF   |

| Input/Output Capacitance | C <sub>io</sub>      | _            | 7    | pF   |

| Output Capacitance       | C <sub>o</sub> (QSF) | <del>_</del> | 7    | pF   |

Note: This parameter is periodically sampled and is not 100% tested.

# **DC Characteristics 1**

| Parameter                | Symbol                    | Condition                                           | Min. | Max. | Unit |  |

|--------------------------|---------------------------|-----------------------------------------------------|------|------|------|--|

| Output "H" Level Voltage | V <sub>OH</sub>           | I <sub>OH</sub> = -2 mA                             | 2.4  | _    | V    |  |

| Output "L" Level Voltage | V <sub>OL</sub>           | I <sub>OL</sub> = 2 mA                              | _    | 0.4  | V    |  |

| Input Leakage Current    | $0 \le V_{IN} \le V_{CC}$ |                                                     |      |      | μА   |  |

| Output Leakage Current   | I <sub>LO</sub>           | $0 \le V_{OUT} \le 5.5 \text{ V}$<br>Output Disable | -10  | 10   |      |  |

### **DC Characteristics 2**

$(V_{CC} = 5 V \pm 10\%, Ta = 0^{\circ}C \text{ to } 70^{\circ}C)$

| H (DAM)                                                                                                         | 0414    | 0                  | -50  | -60  | -70  |      | NI - 4 - |

|-----------------------------------------------------------------------------------------------------------------|---------|--------------------|------|------|------|------|----------|

| Item (RAM)                                                                                                      | SAM     | Symbol             | Max. | Max. | Max. | Unit | Note     |

| Operating Current                                                                                               | Standby | I <sub>CC1</sub>   | 140  | 130  | 120  |      | 3, 4     |

| $(\overline{RAS}, \overline{CAS} \text{ Cycling}, t_{RC} = t_{RC} \text{ min.})$                                | Active  | I <sub>CC1</sub> A | 180  | 170  | 160  |      | 17       |

| Standby Current                                                                                                 | Standby | I <sub>CC2</sub>   | 8    | 8    | 8    |      |          |

| $(\overline{RAS}, \overline{CAS} = V_{IH})$                                                                     | Active  | I <sub>CC2</sub> A | 60   | 55   | 55   |      | 3, 4     |

| RAS Only Refresh Current                                                                                        | Standby | I <sub>CC3</sub>   | 140  | 130  | 120  |      | 3, 4     |

| $(\overline{RAS} \text{ Cycling}, \overline{CAS} = V_{IH}, t_{RC} = t_{RC} \text{ min.})$                       | Active  | I <sub>CC3</sub> A | 180  | 170  | 160  |      | 17       |

| Page Mode Current                                                                                               | Standby | I <sub>CC4</sub>   | 150  | 140  | 130  |      | 3, 4     |

| $(\overline{RAS} = V_{IL}, \overline{CAS} \text{ Cycling}, t_{PC} = t_{PC} \text{ min.})$                       | Active  | I <sub>CC4</sub> A | 200  | 190  | 180  | mΛ   | 18       |

| CAS before RAS Refresh Current                                                                                  | Standby | I <sub>CC5</sub>   | 120  | 110  | 100  | mA   | 3, 4     |

| $(\overline{RAS} \text{ Cycling}, \overline{CAS} \text{ before } \overline{RAS}, t_{RC} = t_{RC} \text{ min.})$ | Active  | I <sub>CC5</sub> A | 160  | 150  | 140  |      | 3, 4     |

| Data Transfer Current                                                                                           | Standby | I <sub>CC6</sub>   | 130  | 120  | 110  |      | 3, 4     |

| $(\overline{RAS}, \overline{CAS} \text{ Cycling}, t_{RC} = t_{RC} \text{ min.})$                                | Active  | I <sub>CC6</sub> A | 170  | 160  | 150  |      | 17       |

| Flash Write Current                                                                                             | Standby | I <sub>CC7</sub>   | 130  | 120  | 110  |      | 3, 4     |

| $(\overline{RAS}, \overline{CAS} \text{ Cycling}, t_{RC} = t_{RC} \text{ min.})$                                | Active  | I <sub>CC7</sub> A | 170  | 160  | 150  |      | 3, 4     |

| Block Write Current                                                                                             | Standby | I <sub>CC8</sub>   | 130  | 120  | 110  |      | 3, 4     |

| $(\overline{RAS}, \overline{CAS} \text{ Cycling}, t_{RC} = t_{RC} \text{ min.})$                                | Active  | I <sub>CC8</sub> A | 170  | 160  | 150  |      | 3, 4     |

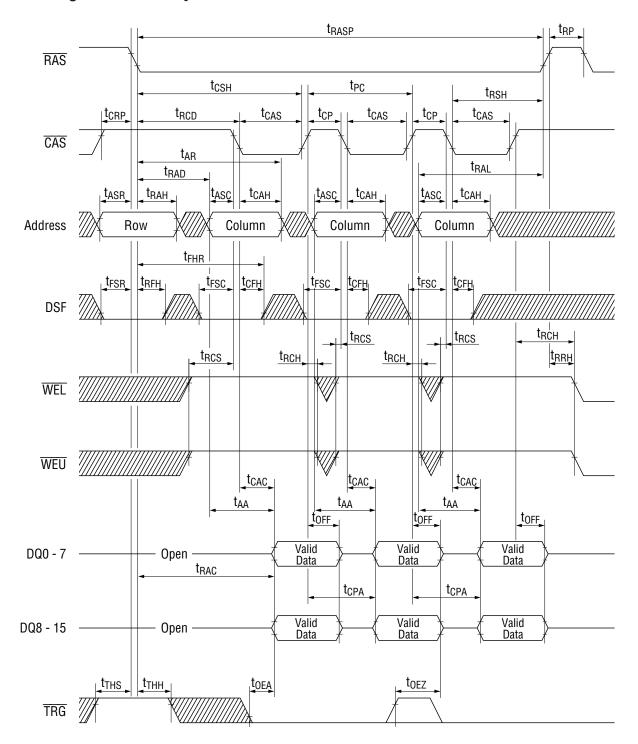

# AC Characteristics (1/3)

|                                                               |                   | -5   | 50   | -60  |      | -70  |      |      |       |

|---------------------------------------------------------------|-------------------|------|------|------|------|------|------|------|-------|

| Parameter                                                     | Symbol            | Min. | Мах. | Min. | Мах. | Min. | Max. | Unit | Note  |

| Random Read or Write Cycle Time                               | t <sub>RC</sub>   | 84   | _    | 104  | _    | 124  | _    | ns   |       |

| Read Modify Write Cycle                                       | t <sub>RWC</sub>  | 135  | _    | 140  | _    | 170  | _    | ns   |       |

| Fast Page Mode Cycle Time                                     | t <sub>PC</sub>   | 25   | _    | 30   | _    | 35   |      | ns   |       |

| Fast Page Mode Read Modify Write Cycle Time                   | t <sub>PRWC</sub> | 72   | _    | 76   | _    | 81   | _    | ns   |       |

| Access Time from RAS                                          | t <sub>RAC</sub>  | _    | 50   | _    | 60   | _    | 70   | ns   | 8, 14 |

| Access Time from Column Address                               | t <sub>AA</sub>   | _    | 25   | _    | 30   | _    | 35   | ns   | 8, 14 |

| Access Time from CAS                                          | t <sub>CAC</sub>  | _    | 15   | _    | 15   | _    | 20   | ns   | 8, 15 |

| Access Time from CAS Precharge                                | t <sub>CPA</sub>  | _    | 30   | _    | 35   | _    | 40   | ns   | 8, 15 |

| Output Buffer Turn-off Delay                                  | t <sub>OFF</sub>  | 0    | 12   | 0    | 15   | 0    | 17   | ns   | 10    |

| Transition Time (Rise and Fall)                               | t <sub>T</sub>    | 2    | 35   | 2    | 35   | 2    | 35   | ns   | 7     |

| RAS Precharge Time                                            | t <sub>RP</sub>   | 30   | —    | 40   | _    | 50   |      | ns   |       |

| RAS Pulse Width                                               | t <sub>RAS</sub>  | 50   | 10k  | 60   | 10k  | 70   | 10k  | ns   |       |

| RAS Pulse Width (Fast Page Mode Only)                         | t <sub>RASP</sub> | 50   | 100k | 60   | 100k | 70   | 100k | ns   |       |

| RAS Hold Time                                                 | t <sub>RSH</sub>  | 15   | —    | 15   | —    | 20   |      | ns   |       |

| CAS Hold Time                                                 | t <sub>CSH</sub>  | 45   | —    | 45   | —    | 55   |      | ns   |       |

| CAS Pulse Width                                               | t <sub>CAS</sub>  | 15   | 10k  | 15   | 10k  | 15   | 10k  | ns   |       |

| RAS to CAS Delay Time                                         | t <sub>RCD</sub>  | 15   | 35   | 15   | 42   | 15   | 50   | ns   | 14    |

| RAS to Column Address Delay Time                              | t <sub>RAD</sub>  | 12   | 25   | 12   | 30   | 12   | 35   | ns   | 14    |

| Column Address to RAS Lead Time                               | t <sub>RAL</sub>  | 25   | _    | 30   | _    | 35   | _    | ns   |       |

| CAS to RAS Precharge Time                                     | t <sub>CRP</sub>  | 5    | _    | 5    | _    | 10   | _    | ns   |       |

| CAS Precharge Time (Fast Page Mode)                           | t <sub>CP</sub>   | 6    | _    | 10   | _    | 10   | _    | ns   |       |

| Row Address Set-up Time                                       | t <sub>ASR</sub>  | 0    | _    | 0    | _    | 0    | _    | ns   |       |

| Row Address Hold Time                                         | t <sub>RAH</sub>  | 8    | _    | 10   | _    | 10   | _    | ns   |       |

| Column Address Set-up Time                                    | t <sub>ASC</sub>  | 0    | _    | 0    | _    | 0    |      | ns   |       |

| Column Address Hold Time                                      | t <sub>CAH</sub>  | 8    |      | 10   | _    | 10   | _    | ns   |       |

| Column Address Hold Time referenced to RAS                    | t <sub>AR</sub>   | 40   |      | 50   |      | 55   | _    | ns   |       |

| Read Command Set-up Time                                      | t <sub>RCS</sub>  | 0    |      | 0    |      | 0    |      | ns   |       |

| Read Command Hold Time                                        | t <sub>RCH</sub>  | 0    | _    | 0    | _    | 0    | _    | ns   | 11    |

| Read Command Hold Time referenced to $\overline{RAS}$         | t <sub>RRH</sub>  | 0    | _    | 0    | _    | 0    | _    | ns   | 11    |

| Write Command Set-up Time                                     | twcs              | 0    |      | 0    | _    | 0    | _    | ns   | 13    |

| Write Command Hold Time                                       | t <sub>WCH</sub>  | 8    | _    | 10   | _    | 10   | _    | ns   |       |

| Write Command Hold Time referenced to $\overline{\text{RAS}}$ | t <sub>WCR</sub>  | 40   | _    | 50   | _    | 55   | _    | ns   |       |

| Write Command Pulse Width                                     | t <sub>WP</sub>   | 8    |      | 10   |      | 10   |      | ns   |       |

| Write Command to RAS Lead Time                                | t <sub>RWL</sub>  | 12   | _    | 15   | _    | 15   |      | ns   |       |

| Write Command to CAS Lead Time                                | t <sub>CWL</sub>  | 12   |      | 15   | _    | 15   |      | ns   |       |

# AC Characteristics (2/3)

|                                                |                  | -5   | 50   | -(   | 60   |      | 70   |      |      |

|------------------------------------------------|------------------|------|------|------|------|------|------|------|------|

| Parameter                                      | Symbol           | Min. | Мах. | Min. | Мах. | Min. | Max. | Unit | Note |

| Data Set-up Time                               | t <sub>DS</sub>  | 0    | _    | 0    | _    | 0    | _    | ns   | 12   |

| Data Hold Time                                 | t <sub>DH</sub>  | 8    | _    | 10   | _    | 12   | _    | ns   | 12   |

| Data Hold Time referenced to RAS               | t <sub>DHR</sub> | 40   | _    | 50   | _    | 55   | _    | ns   |      |

| RAS to WE Delay Time                           | t <sub>RWD</sub> | 70   | _    | 80   | _    | 90   | _    | ns   | 13   |

| Column Address to WE Delay Time                | t <sub>AWD</sub> | 45   | _    | 50   | _    | 55   | _    | ns   | 13   |

| CAS to WE Delay Time                           | t <sub>CWD</sub> | 30   | _    | 35   | _    | 40   | _    | ns   | 13   |

| Data to CAS Delay Time                         | t <sub>DZC</sub> | 0    | _    | 0    | _    | 0    | _    | ns   |      |

| Data to TRG Delay Time                         | t <sub>DZO</sub> | 0    | _    | 0    | _    | 0    | _    | ns   |      |

| Access Time from TRG                           | t <sub>OEA</sub> | _    | 15   | _    | 15   | _    | 20   | ns   |      |

| Output Buffer Turn-off Delay from TRG          | t <sub>OEZ</sub> | 0    | 12   | 0    | 15   | 0    | 15   | ns   |      |

| TRG Command Hold Time                          | t <sub>OEH</sub> | 8    | _    | 10   | _    | 10   | _    | ns   |      |

| RAS Hold Time referenced to TRG                | t <sub>ROH</sub> | 10   | _    | 10   | _    | 15   | _    | ns   |      |

| CAS Set-up Time for CAS before RAS Cycle       | t <sub>CSR</sub> | 5    | _    | 5    | _    | 5    | _    | ns   |      |

| CAS Hold Time for CAS before RAS Cycle         | t <sub>CHR</sub> | 8    | _    | 10   | _    | 10   | _    | ns   |      |

| RAS Precharge to CAS Active Time               | t <sub>RPC</sub> | 0    | _    | 0    | _    | 0    | _    | ns   |      |

| Refresh Period                                 | t <sub>REF</sub> | _    | 8    | _    | 8    | _    | 8    | ms   |      |

| WE Set-up Time                                 | t <sub>WSR</sub> | 0    | _    | 0    | _    | 0    | _    | ns   |      |

| WE Hold Time                                   | t <sub>RWH</sub> | 8    | _    | 10   | _    | 10   | _    | ns   |      |

| DSF Set-up Time referenced to RAS              | t <sub>FSR</sub> | 0    | _    | 0    | _    | 0    | _    | ns   |      |

| DSF Hold Time referenced to RAS (1)            | t <sub>RFH</sub> | 8    | _    | 10   | _    | 10   | _    | ns   |      |

| DSF Hold Time referenced to RAS (2)            | t <sub>FHR</sub> | 40   | _    | 50   | _    | 55   | _    | ns   |      |

| DSF Set-up Time referenced to CAS              | t <sub>FSC</sub> | 0    | _    | 0    | _    | 0    | _    | ns   |      |

| DSF Hold Time referenced to CAS                | t <sub>CFH</sub> | 8    | _    | 10   | _    | 10   | _    | ns   |      |

| Write Per Bit Mask Data Set-up Time            | t <sub>MS</sub>  | 0    | _    | 0    | _    | 0    | _    | ns   |      |

| Write Per Bit Mask Data Hold Time              | t <sub>MH</sub>  | 8    | _    | 10   | _    | 10   | _    | ns   |      |

| TRG High Set-up Time                           | t <sub>THS</sub> | 0    | _    | 0    | _    | 0    | _    | ns   |      |

| TRG High Hold Time                             | t <sub>THH</sub> | 8    | —    | 10   | —    | 10   | _    | ns   |      |

| TRG Low Set-up Time                            | t <sub>TLS</sub> | 0    | _    | 0    | _    | 0    | _    | ns   |      |

| TRG Low Hold Time                              | t <sub>TLH</sub> | 8    | 10k  | 10   | 10k  | 10   | 10k  | ns   |      |

| TRG Low Hold Time referenced to RAS            | t <sub>RTH</sub> | 40   | 10k  | 50   | 10k  | 60   | 10k  | ns   |      |

| TRG Low Hold Time referenced to Column Address | t <sub>ATH</sub> | 20   | _    | 20   | _    | 25   | _    | ns   |      |

| TRG Low Hold Time referenced to CAS            | t <sub>CTH</sub> | 15   |      | 15   |      | 20   | _    | ns   |      |

# AC Characteristics (3/3)

| Parrie :                                     | 0                 | -4   | 50   | -6   | 60   | -7   | 70   | 11. 2 |      |

|----------------------------------------------|-------------------|------|------|------|------|------|------|-------|------|

| Parameter                                    | Symbol            | Min. | Max. | Min. | Max. | Min. | Мах. | Unit  | Note |

| TRG to RAS Precharge Time                    | t <sub>TRP</sub>  | 40   |      | 40   |      | 50   | _    | ns    |      |

| TRG Precharge Time                           | t <sub>TP</sub>   | 15   | _    | 20   |      | 20   | _    | ns    |      |

| RAS to First SC Delay Time (Read Transfer)   | t <sub>RSD</sub>  | 50   | _    | 60   | _    | 70   | _    | ns    |      |

| Column Address to First SC Delay Time        | t <sub>ASD</sub>  | 25   | _    | 30   | _    | 35   | _    | ns    |      |

| CAS to First SC Delay Time (Read Transfer)   | t <sub>CSD</sub>  | 20   | _    | 20   | _    | 20   | _    | ns    |      |

| Last SC to TRG Lead Time                     | t <sub>TSL</sub>  | 5    | _    | 5    | _    | 5    | _    | ns    |      |

| TRG to First SC Delay Time (Read Transfer)   | t <sub>TSD</sub>  | 10   | _    | 10   | _    | 10   | _    | ns    |      |

| Last SC to RAS Set-up Time (Serial Input)    | t <sub>SRS</sub>  | 20   | _    | 20   | _    | 25   | _    | ns    |      |

| Serial Output Buffer Turn-off Delay from RAS | t <sub>SDZ</sub>  | 10   | 30   | 10   | 30   | 10   | 40   | ns    | 10   |

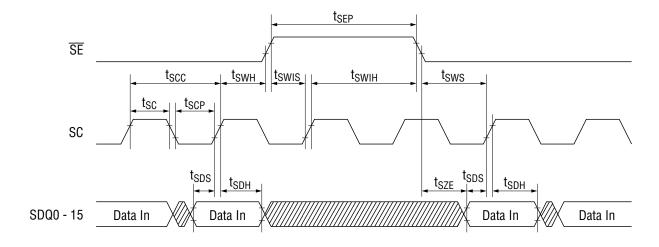

| SC Cycle Time                                | t <sub>SCC</sub>  | 18   | _    | 18   | _    | 20   | _    | ns    |      |

| SC Pulse Width (SC High Time)                | t <sub>SC</sub>   | 5    | _    | 5    | _    | 5    | _    | ns    |      |

| SC Precharge Time (SC Low Time)              | t <sub>SCP</sub>  | 5    | _    | 5    | _    | 5    | _    | ns    |      |

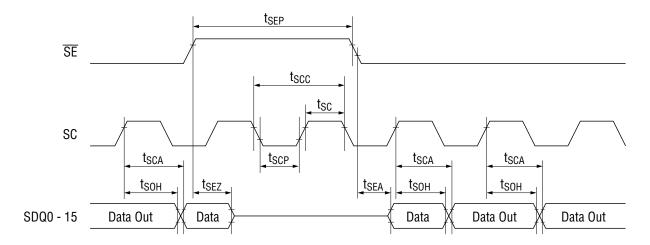

| Access Time from SC                          | t <sub>SCA</sub>  | _    | 15   | _    | 15   | _    | 17   | ns    | 9    |

| Serial Output Hold Time from SC              | t <sub>SOH</sub>  | 3    | _    | 3    | _    | 5    | _    | ns    | 19   |

| Access Time from SE                          | t <sub>SEA</sub>  | _    | 15   |      | 15   | _    | 17   | ns    | 9    |

| SE Pulse Width                               | t <sub>SE</sub>   | 10   | _    | 10   | _    | 10   | _    | ns    |      |

| SE Precharge Time                            | t <sub>SEP</sub>  | 10   | _    | 10   | _    | 10   | _    | ns    |      |

| Serial Output Buffer Turn-off Delay from SE  | t <sub>SEZ</sub>  | 0    | 14   | 0    | 15   | 0    | 17   | ns    | 10   |

| Split Transfer Set-up Time                   | t <sub>STS</sub>  | 20   | _    | 20   | _    | 25   | _    | ns    |      |

| Split Transfer Hold Time                     | t <sub>STH</sub>  | 20   | _    | 20   | _    | 25   | _    | ns    |      |

| SC-QSF Delay Time                            | t <sub>SQD</sub>  | _    | 20   | _    | 20   | _    | 25   | ns    |      |

| TRG-QSF Delay Time                           | t <sub>TQD</sub>  | _    | 20   | _    | 20   | _    | 25   | ns    |      |

| CAS-QSF Delay Time                           | t <sub>CQD</sub>  | _    | 30   | _    | 30   | _    | 35   | ns    |      |

| RAS-QSF Delay Time                           | t <sub>RQD</sub>  | _    | 65   | _    | 70   | _    | 75   | ns    |      |

| RAS to Serial Input Delay Time               | t <sub>SDD</sub>  | 30   | _    | 30   | _    | 40   | _    | ns    |      |

| Serial Input Set-up Time                     | t <sub>SDS</sub>  | 0    | _    | 0    | _    | 0    | _    | ns    |      |

| Serial Input Hold Time                       | t <sub>SDH</sub>  | 8    | _    | 10   | _    | 10   | _    | ns    |      |

| Serial Input to SE Delay Time                | t <sub>SZE</sub>  | 0    | _    | 0    | _    | 0    | _    | ns    |      |

| Serial Input to First SC Delay Time          | t <sub>SZS</sub>  | 0    | _    | 0    | _    | 0    | _    | ns    |      |

| Serial Write Enable Set-up Time              | t <sub>SWS</sub>  | 0    | _    | 0    | _    | 0    | _    | ns    |      |

| Serial Write Enable Hold Time                | t <sub>SWH</sub>  | 8    |      | 10   | _    | 10   | _    | ns    |      |

| Serial Write Disable Set-up Time             | t <sub>SWIS</sub> | 0    |      | 0    |      | 0    |      | ns    |      |

| Serial Write Disable Hold Time               | t <sub>SWIH</sub> | 8    |      | 10   |      | 10   | _    | ns    |      |

Notes:

- 1. Exposure beyond the "Absolute Maximum Ratings" may cause permanent damage to the device.

- 2. All voltages are referenced to  $V_{SS}$ .

- 3. These parameters depend on the cycle rate.

- 4. These parameters depend on output loading. Specified values are obtained with the output open.

- 5. An initial pause of 200  $\mu$ s is required after power up followed by any 8  $\overline{RAS}$  cycles ( $\overline{TRG}$  = "high") and any 8 SC cycles before proper device operation is achieved. In the case of using an internal refresh counter, a minimum of 8  $\overline{CAS}$  before  $\overline{RAS}$  cycles instead of 8  $\overline{RAS}$  cycles are required.

- 6. AC measurements assume  $t_T = 5$  ns.

- 7.  $V_{IH}$  (Min.) and  $V_{IL}$  (Max.) are reference levels for measuring timing of input signals. Also, transition times are measured between  $V_{IH}$  and  $V_{IL}$ .

- 8. RAM port outputs are measured with a load equivalent to 1 TTL load and 50 pF. DOUT reference levels :  $V_{OH}/V_{OL} = 2.0 \text{ V}/0.8 \text{ V}$ .

- 9. SAM port outputs are measured with a load equivalent to 1 TTL load and 30 pF. DOUT reference levels :  $V_{OH}/V_{OL} = 2.0 \text{ V}/0.8 \text{ V}$ .

- 10.  $t_{OFF}$  (Max.),  $t_{OEZ}$  (Max.),  $t_{SDZ}$  (Max.) and  $t_{SEZ}$  (Max.) define the time at which the outputs achieve the open circuit condition, and are not referenced to output voltage levels. This parameter is sampled and not 100% tested.

- 11. Either  $t_{RCH}$  or  $t_{RRH}$  must be satisfied for a read cycle.

- 12. These parameters are referenced to  $\overline{CAS}$  leading edge of early write cycles, and to  $\overline{WE}$  leading edge in  $\overline{TRG}$  controlled write cycles and read modify write cycles.

- 13.  $t_{WCS}$ ,  $t_{RWD}$ ,  $t_{CWD}$  and  $t_{AWD}$  are not restrictive operating parameters. They are included in the data sheet as electrical characteristics only. If  $t_{WCS} \ge t_{WCS}$  (Min.), the cycle is an early write cycle, and the data out pin will remain open circuit throughout the entire cycle; If  $t_{RWD} \ge t_{RWD}$  (Min.),  $t_{CWD} \ge t_{CWD}$  (Min.) and  $t_{AWD} \ge t_{AWD}$  (Min.), the cycle is a read modify write cycle, and the data out will contain data read from the selected cell; If neither of the above sets of conditions are satisfied, the condition of the data out is indeterminate.

- 14. Operation within the  $t_{RCD}$  (Max.) limit ensures that  $t_{RAC}$  (Max.) can be met.  $t_{RCD}$  (Max.) is specified as a reference point only: If  $t_{RCD}$  is greater than the specified  $t_{RCD}$  (Max.) limit, then access time is controlled by  $t_{CAC}$ .

- 15. Operation within the  $t_{RAD}$  (Max.) limit ensures that  $t_{RAC}$  (Max.) can be met.  $t_{RAD}$  (Max.) is specified as a reference point only: If  $t_{RAD}$  is greater than the specified  $t_{RAD}$  (Max.) limit, then access time is controlled by  $t_{AA}$ .

- 16. Input levels at the AC testing are 3.0 V/0 V.

- 17. Address (A0 A8) may be changed two times or less while  $\overline{RAS} = V_{II}$ .

- 18. Address (A0 A8) may be changed once or less while  $\overline{CAS} = V_{IH}$  and  $\overline{RAS} = V_{IL}$ .

- 19. This is guaranteed by design. ( $t_{SOH}/t_{COH} = t_{SCA}/t_{CAC}$  output transition time) This parameter is not 100% tested.

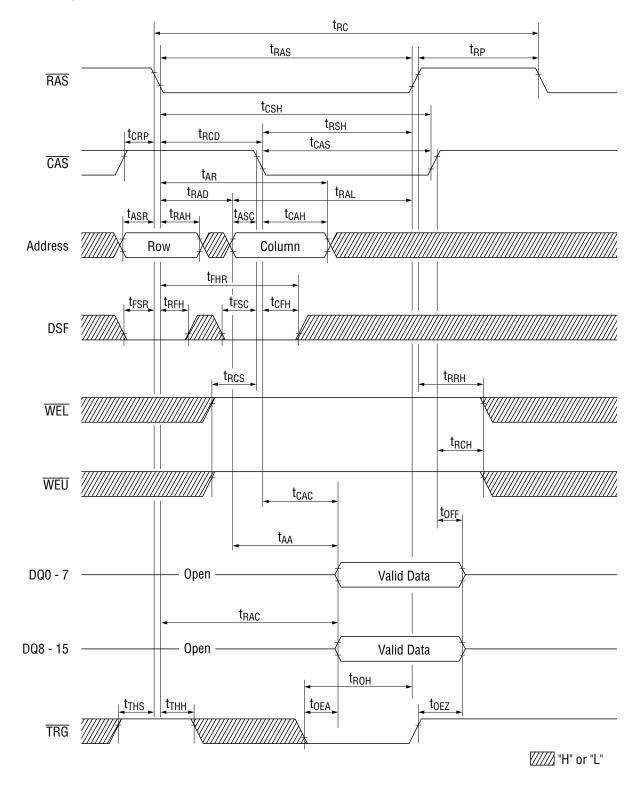

# **TIMING WAVEFORM**

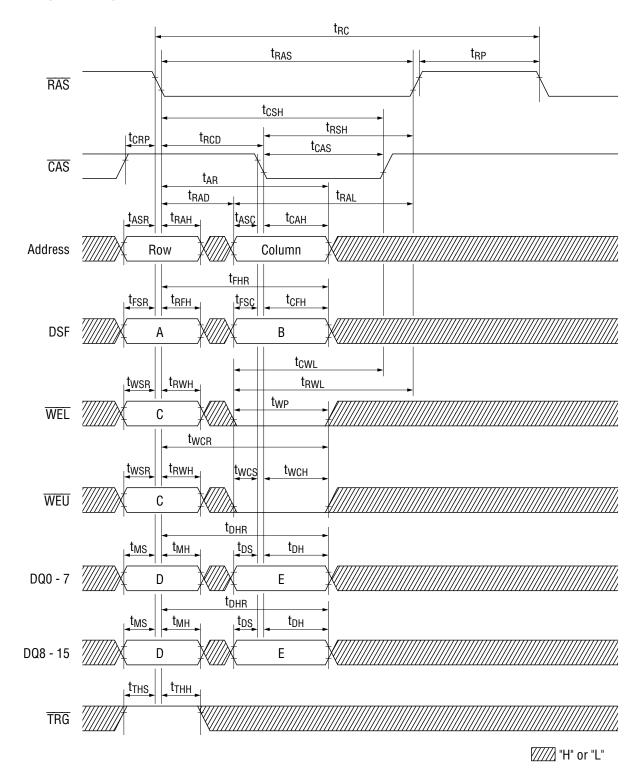

# **Read Cycle**

**OKI** Semiconductor MSM5416282

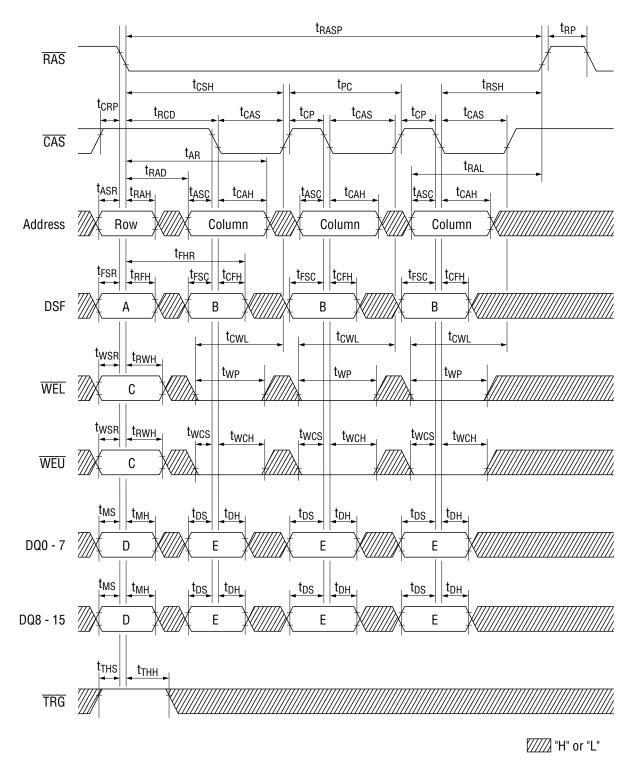

# **Fast Page Mode Read Cycle**

"H" or "L"

# **Write Cycle Function Table**

|      | Ī   | RAS Fall | ing Edge   | 7   | CAS Falling Edge |                     |

|------|-----|----------|------------|-----|------------------|---------------------|

| Code | Α   | С        | D          | В   | E                | Function            |

|      | DSF | WEL/U    | DQ         | DSF | DQ               |                     |

| RWM  | 0   | 0        | Write Mask | 0   | Valid Data       | Masked Write        |

| BWM  | 0   | 0        | Write Mask | 1   | Column Mask      | Masked Block Write  |

| FWM  | 1   | 0        | Write Mask | Х   | Χ                | Masked Flash Write  |

| RW   | 0   | 1        | Χ          | 0   | Valid Data       | Normal Write        |

| BW   | 0   | 1        | Χ          | 1   | Column Mask      | Block Write         |

| LCR  | 1   | 1        | Χ          | 1   | Color Data       | Load Color Register |

WRITE MASK DATA: "Low" = Mask, "High" = No Mask

# **Column Mask Data**

|            | DQ0 - 15 | Column Mask Data                  |                |

|------------|----------|-----------------------------------|----------------|

|            | DQ0      | Column 0 (A0 = 0, A1 = 0, A2 = 0) |                |

|            | DQ1      | Column 1 (A0 = 1, A1 = 0, A2 = 0) |                |

|            | DQ2      | Column 2 (A0 = 0, A1 = 1, A2 = 0) |                |

| Lower Byte | DQ3      | Column 3 (A0 = 1, A1 = 1, A2 = 0) | Low : Mask     |

| Lower byte | DQ4      | Column 4 (A0 = 0, A1 = 0, A2 = 1) | High : No Mask |

|            | DQ5      | Column 5 (A0 = 1, A1 = 0, A2 = 1) |                |

|            | DQ6      | Column 6 (A0 = 0, A1 = 1, A2 = 1) |                |

|            | DQ7      | Column 7 (A0 = 1, A1 = 1, A2 = 1) |                |

|            | DQ8      | Column 0 (A0 = 0, A1 = 0, A2 = 0) |                |

|            | DQ9      | Column 1 (A0 = 1, A1 = 0, A2 = 0) |                |

|            | DQ10     | Column 2 (A0 = 0, A1 = 1, A2 = 0) | ]              |

| Unnar Duta | DQ11     | Column 3 (A0 = 1, A1 = 1, A2 = 0) | Low : Mask     |

| Upper Byte | DQ12     | Column 4 (A0 = 0, A1 = 0, A2 = 1) | High : No Mask |

|            | DQ13     | Column 5 (A0 = 1, A1 = 0, A2 = 1) |                |

|            | DQ14     | Column 6 (A0 = 0, A1 = 1, A2 = 1) |                |

|            | DQ15     | Column 7 (A0 = 1, A1 = 1, A2 = 1) |                |

# **Early Write Cycle**

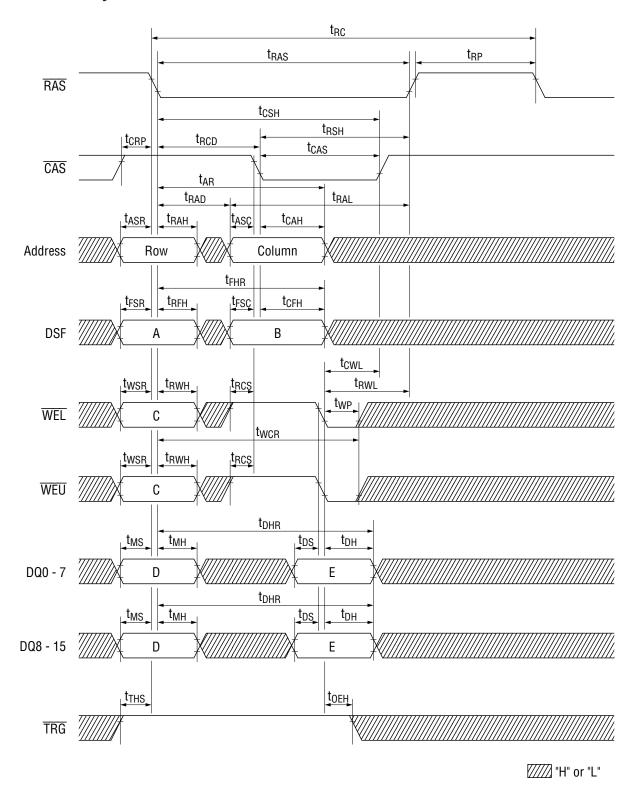

# **Late Write Cycle**

14/37

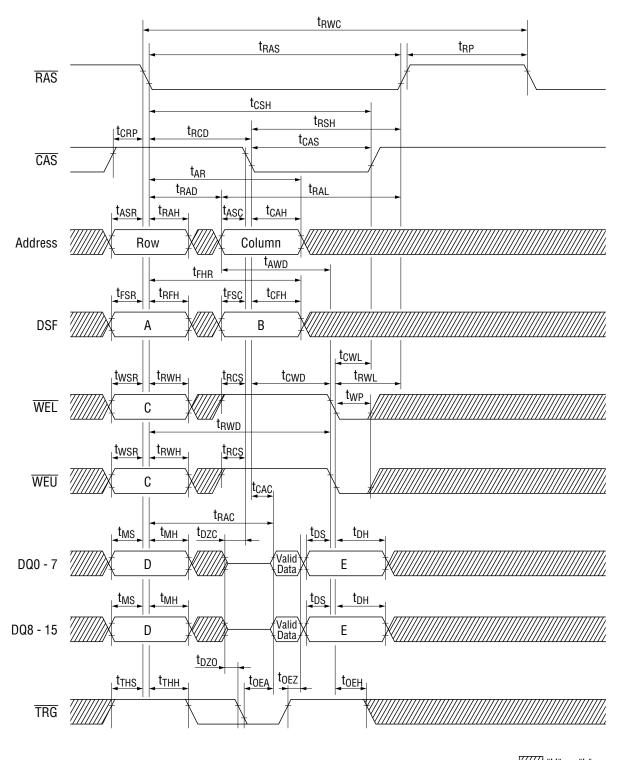

# **Read Modify Write Cycle**

"H" or "L"

**OKI** Semiconductor MSM5416282

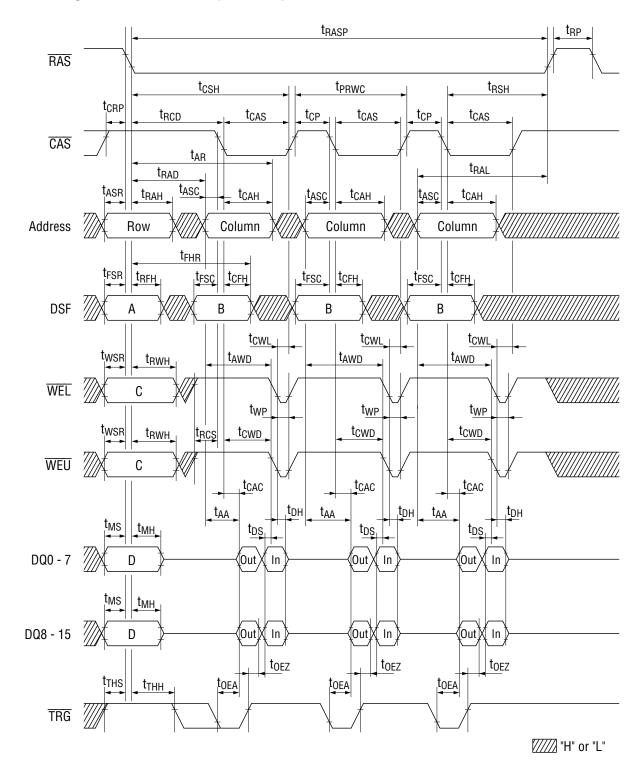

# **Fast Page Mode Early Write Cycle**

16/37

# **Fast Page Mode Read Modify Write Cycle**

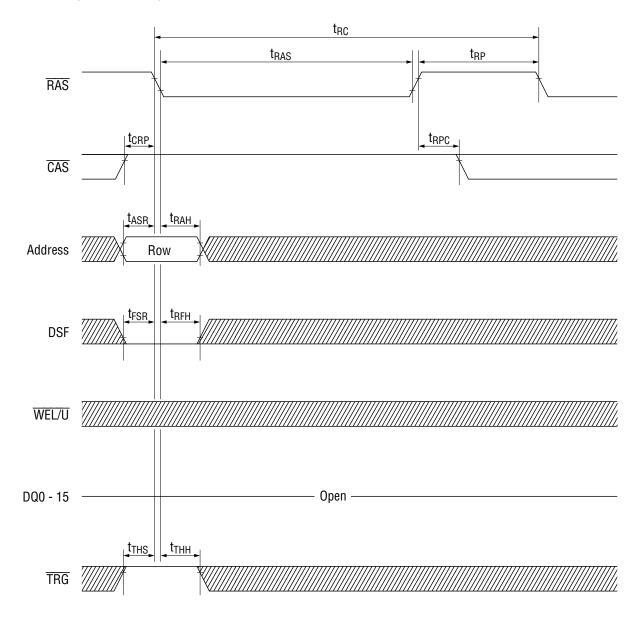

# **RAS** Only Refresh Cycle

"H" or "L"

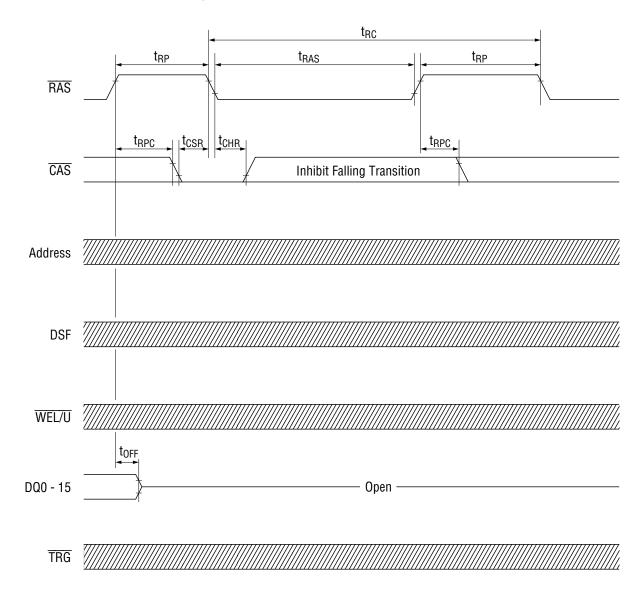

# **CAS** before **RAS** Refresh Cycle

"H" or "L"

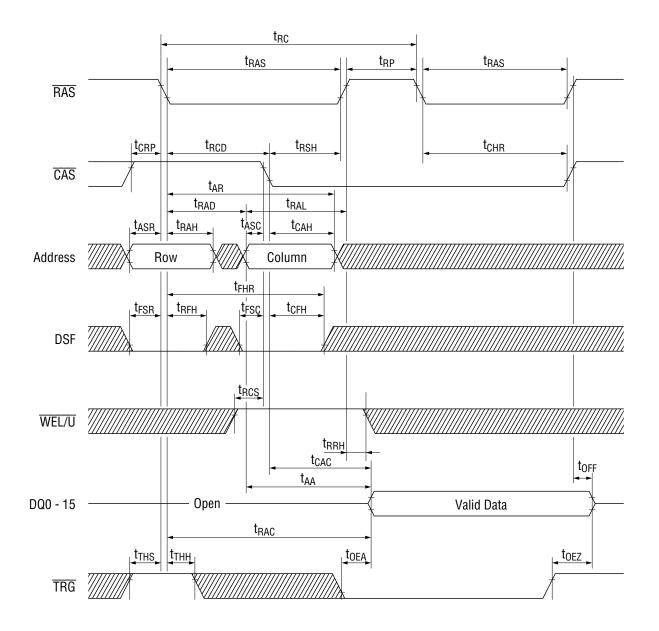

# **Hidden Refresh Cycle**

////// "H" or "L"

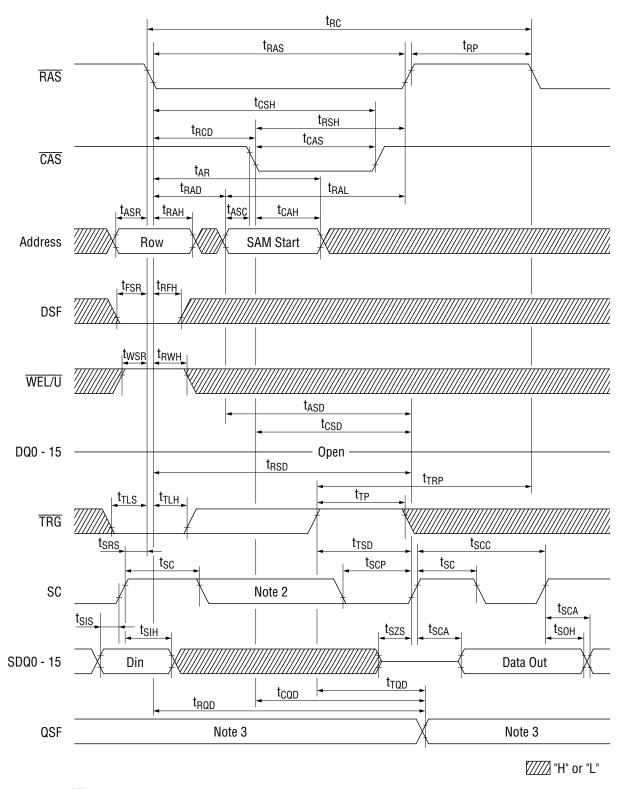

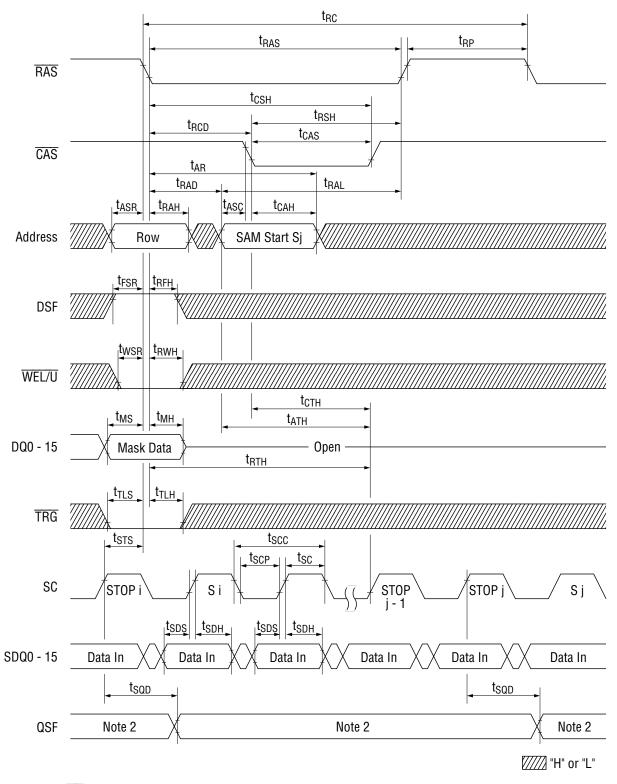

### **Read Transfer 1**

Note 1:  $\overline{SE} = "L"$

**Note 2:** There must be no rising transitions

**Note 3:** QSF = "L"-- Lower SAM (0 - 255) is active

QSF = "H"-- Upper SAM (256 - 511) is active

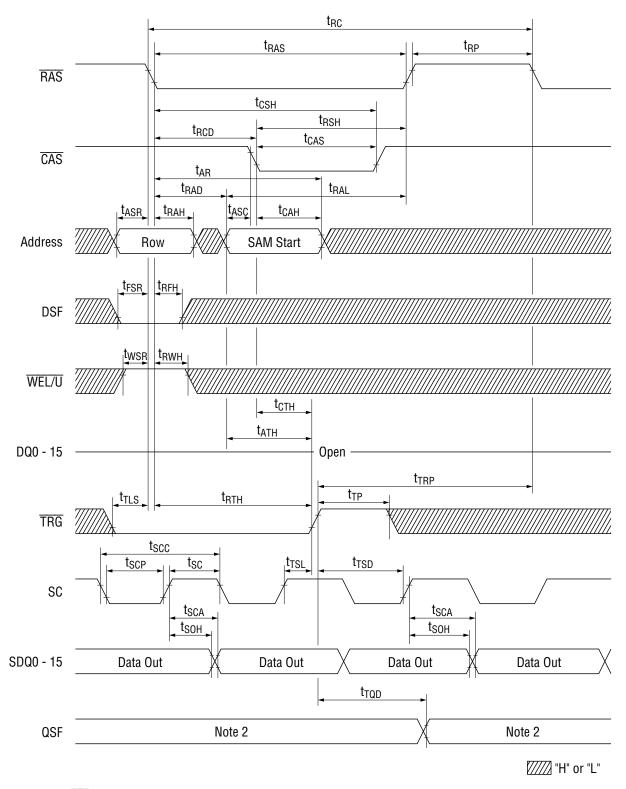

# Read Transfer 2 (Real Time Read Transfer)

Note 1:  $\overline{SE} = L^{*}$

**Note 2:** QSF = "L"-- Lower SAM (0 - 255) is active

QSF = "H"-- Upper SAM (256 - 511) is active

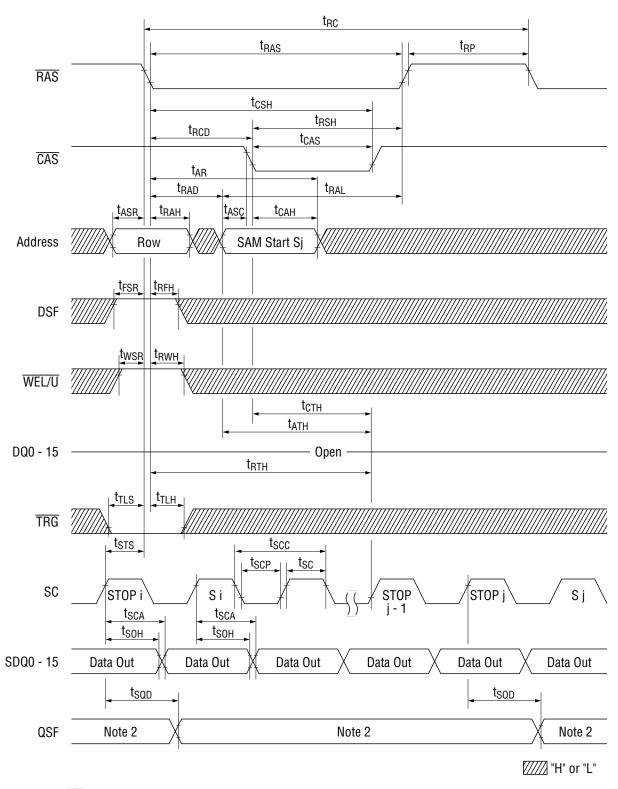

### **Split Read Transfer**

Note 1:  $\overline{SE} = L^{*}$

**Note 2:** QSF = "L"-- Lower SAM (0 - 255) is active

QSF = "H"-- Upper SAM (256 - 511) is active

Note 3: Si is the SAM start address in before SRT

**Note 4:** STOP i and STOP j are programmable stop addresses

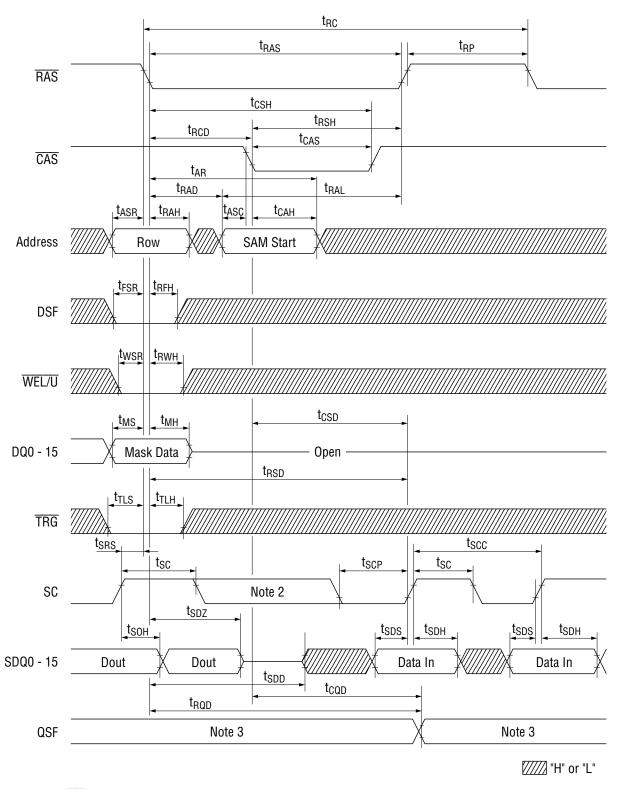

### **Masked Write Transfer**

Note 1:  $\overline{SE} = "L"$

**Note 2:** There must be no rising transitions

**Note 3:** QSF = "L"-- Lower SAM (0 - 255) is active

QSF = "H"-- Upper SAM (256 - 511) is active

#### **Masked Split Write Transfer**

Note 1:  $\overline{SE} = L^{*}$

**Note 2:** QSF = "L"-- Lower SAM (0 - 255) is active

QSF = "H"-- Upper SAM (256 - 511) is active

**Note 3:** Si is the SAM start address in before SWT

**Note 4:** STOP i and STOP j are programmable stop addresses

# **Serial Read Cycle**

# **Serial Write Cycle**

////// "H" or "L"

#### **PIN FUNCTIONS**

#### Address Input: A0 - A8

The 18 address bits decode 16 bits of the 4,194,304 locations in the MSM5416282 memory array. The address bits are multiplexed to 9 address input pins (A0 - A8) as standard DRAM. 9 row address bits are latched at the falling edge of  $\overline{RAS}$ . The following 9 column address bits are latched at the falling edge of  $\overline{CAS}$ .

#### Row Address Strobe: RAS

$\overline{RAS}$  is a basic RAM control signal. The RAM port is in standby mode when the  $\overline{RAS}$  level is "high". As the standard DRAM's  $\overline{RAS}$  signal function,  $\overline{RAS}$  is the control input that latches the row address bits, and a random access cycle begins at the falling edge of  $\overline{RAS}$ . In addition to the conventional  $\overline{RAS}$  signal function, the level of the input signals  $\overline{CAS}$ ,  $\overline{TRG}$ ,

WEL, WEU and DSF at the falling edge of RAS, determines the MSM5416282 operation mode.

#### Column Address Strobe: CAS

As the standard DRAM's  $\overline{\text{CAS}}$  signal function,  $\overline{\text{CAS}}$  is the control input signal that latches the column address input, and the state of the special function input DSF to select in conjunction with the  $\overline{\text{RAS}}$  control, either read/write operations or the special block write feature on the RAM port when the DSF is held "low" at the falling edge of  $\overline{\text{RAS}}$ .  $\overline{\text{CAS}}$  also acts as a RAM port output enable signal.

#### Data Transfer/Output Enable: TRG

$\overline{TRG}$  is also a control input signal having multiple functions. As the standard DRAM's  $\overline{OE}$  signal function,  $\overline{TRG}$  is used as an output enable control when  $\overline{TRG}$  is "high" at the falling edge of  $\overline{RAS}$ . In addition to the conventional  $\overline{OE}$  signal function, a data transfer operation is started between the RAM port and the SAM port when  $\overline{TRG}$  is "low" at the falling edge of  $\overline{RAS}$ .

#### Write Per Bit/Write Enable: WEL and WEU

$\overline{\text{WEL}}$  and  $\overline{\text{WEU}}$  are control input signals having multiple functions. As the standard DRAM's  $\overline{\text{WE}}$  signal function, these are used to write data into the memory on the RAM port when  $\overline{\text{WEL}}$  and  $\overline{\text{WEU}}$  are both "high" at the falling edge of  $\overline{\text{RAS}}$ .

In addition to the conventional  $\overline{WE}$  signal function, both  $\overline{WEL}$  and  $\overline{WEU}$  determine the write-perbit function, when either  $\overline{WEL}$  or  $\overline{WEU}$  is "low" at the falling edge of  $\overline{RAS}$  during RAM port operations.

The  $\overline{WEL}$  and  $\overline{WEU}$  also determine the direction of data transfer between the RAM and SAM. When both  $\overline{WEL}$  and  $\overline{WEU}$  are "high" at the falling edge of  $\overline{RAS}$ , the data is transferred from RAM to SAM (read transfer). When either  $\overline{WEL}$  or  $\overline{WEU}$  is "low" at the falling edge of  $\overline{RAS}$ , the data is transferred SAM to RAM (write transfer).

OKI Semiconductor MSM5416282

#### Write Mask Data/Data Input and Output: DQ0 - DQ15

In conventional write-per bit mode, the DQ pins function as mask data at the falling edge of  $\overline{RAS}$ . Data is written only to high DQ pins. Data on low DQ pins is masked and internal data is retained. After that, they function as input/output pins similar to a standard DRAM.

#### Serial Clock: SC

SC is a main serial cycle control input signal. All operations of the SAM port are synchronized with the serial clock SC. Data is shifted in or out of the SAM registers at the rising edge of SC. In a serial read cycle, the output data becomes valid on the SDQ pins after the maximum specified serial access time  $t_{SCA}$  from the rising edge of SC.

In a serial write cycle, data on SDQ pins at the rising edge of SC are fetched into the SAM register.

#### Serial Enable: SE

The  $\overline{SE}$  is a serial access enable control and serial read/write control signal. In a serial read cycle,  $\overline{SE}$  is used as an output control. In a serial write cycle,  $\overline{SE}$  is used as a write enable control. When  $\overline{SE}$  is "high", serial access is disabled. However, the serial address pointer location is still incremented when SC is clocked even when  $\overline{SE}$  is "high".

#### **Special Function Input: DSF**

The DSF is latched at the falling edge of  $\overline{RAS}$  and  $\overline{CAS}$ . It allows for the selection of several RAM ports and transfer operating modes. In addition to the conventional multiport DRAM, the special functions consisting of flash write, block write, load/read color register, and split read/write transfer can be invoked.

#### **Special Function Output: QSF**

QSF is an output signal, which during split register mode indicates which half of the split SAM is being accessed. QSF "low" indicates that the lower split SAM (0 - 255) is being accessed. QSF "high" indicates that the upper SAM (256 - 511) is being accessed.

QSF is enabled by  $\overline{SE}$ . When  $\overline{SE}$  is "high", QSF is in high impedance.

#### Serial Input/Output: SDQ0 - SDQ15

Serial input/output mode is determined by the most recent read or write transfer cycle. When a read transfer cycle is performed, the SAM port is in the output mode. When a write or pseudo write transfer cycle is performed, the SAM port is switched from output mode to input mode.

**OKI** Semiconductor MSM5416282

### **OPERATION MODES**

Table-1 shows the function truth table for a listing of all available RAM ports, and transfer operations of the MSM5416282.

The RAM port and data transfer operations are determined by the state of  $\overline{CAS}$ ,  $\overline{TRG}$ ,  $\overline{WEL}$ ,  $\overline{WEU}$  and DSF at the falling edge of  $\overline{RAS}$ , and by the level of DSF at the falling edge of  $\overline{CAS}$ .

**Table-1. Function Truth Table**

|      |     | RAS↓ |    |     | CAS↓ | Address |                    | W/IO |                  | \A/wita       | Oalan             |                                |  |  |

|------|-----|------|----|-----|------|---------|--------------------|------|------------------|---------------|-------------------|--------------------------------|--|--|

| Code | CAS | TRG  | WE | DSF | DSF  | RAS↓    | CAS↓               | RAS↓ | CAS<br>/WE↓      | Write<br>Mask | Color<br>Register | Function                       |  |  |

| CBR  | 0   | *    | *  | *   | _    | *       | *                  | *    | *                | _             | _                 | CBR Refresh                    |  |  |

| ROR  | 1   | 1    | *  | 0   | _    | Row     | _                  | *    | _                | _             | _                 | RAS Only Refresh               |  |  |

| MWT  | 1   | 0    | 0  | 0   | *    | Row     | TAP                | WM1  | *                | Yes           | _                 | Masked Write Transfer          |  |  |

| MSWT | 1   | 0    | 0  | 1   | *    | Row     | TAP                | WM1  | *                | Yes           | _                 | Masked Split<br>Write Transfer |  |  |

| RT   | 1   | 0    | 1  | 0   | *    | Row     | TAP                | *    | *                | _             | _                 | Read Transfer                  |  |  |

| SRT  | 1   | 0    | 1  | 1   | *    | Row     | TAP                | *    | *                | _             | _                 | Split Read Transfer            |  |  |

| RWM  | 1   | 1    | 0  | 0   | 0    | Row     | Column             | WM1  | Din,Dout         | Yes           | _                 | Read/Write<br>(Mask)           |  |  |

| BWM  | 1   | 1    | 0  | 0   | 1    | Row     | Column<br>A3c - 8c | WM1  | Column<br>Select | Yes           | Use               | Masked Block Write             |  |  |

| FWM  | 1   | 1    | 0  | 1   | *    | Row     | *                  | WM1  | _                | Yes           | Use               | Masked Flash Write             |  |  |

| RW   | 1   | 1    | 1  | 0   | 0    | Row     | Column             | *    | Din,Dout         | No            | _                 | Read/Write<br>(No Mask)        |  |  |

| BW   | 1   | 1    | 1  | 0   | 1    | Row     | Column<br>A3c - 8c | *    | Column<br>Select | No            | Use               | Block Write<br>(No Mask)       |  |  |

| LCR  | 1   | 1    | 1  | 1   | 1    | Row     | *                  | *    | Color<br>Data    |               | Load              | Load Color Register            |  |  |

If the DSF is "high" at the falling edge of  $\overline{RAS}$ , special functions such as split transfer, flash write, load color register can be invoked.

If the DSF is "low" at the falling edge of  $\overline{RAS}$  and "high" at the falling edge of  $\overline{CAS}$ , the block write feature can be invoked.

#### RAM PORT OPERATION

RAM Read Cycle: RAS falling edge --- TRG = CAS = "H", DSF = "L"

CAS falling edge --- DSF = "L"

Row address is entered at the falling edge of  $\overline{RAS}$  and column address at the falling edge of  $\overline{CAS}$  to the device as in conventional DRAM. When both  $\overline{WEL}$  and  $\overline{WEU}$  are "high" and  $\overline{TRG}$  is "low" while  $\overline{CAS}$  is "low", the data outputs through DQ pins.

RAM Write Cycle: RAS falling edge --- TRG = CAS = "H", DSF = "L"

CAS falling edge --- DSF = "L"

1) Write cycle with no mask:  $\overline{RAS}$  falling edge --  $\overline{WEL}$  =  $\overline{WEU}$  = "H"

If either  $\overline{\text{WEL}}$  or  $\overline{\text{WEU}}$  is set "low" at the falling edge of  $\overline{\text{CAS}}$  after  $\overline{\text{RAS}}$  goes "low", a write cycle is excuted. If either  $\overline{\text{WEL}}$  or  $\overline{\text{WEU}}$  is set "low" before the  $\overline{\text{CAS}}$  falling edge, this cycle becomes an early write cycle, and all DQ pins attain high impedance.

If either  $\overline{\text{WEL}}$  or  $\overline{\text{WEU}}$  is "low" when  $\overline{\text{CAS}}$  goes "low", the write affects only those corresponding 8 bits with the latched data.

If both  $\overline{\text{WEL}}$  and  $\overline{\text{WEU}}$  are set "low" after the  $\overline{\text{CAS}}$  falling edge, this cycle becomes a late write cycle, and all 16 data are latched on the falling edge of  $\overline{\text{WEL}}$  or  $\overline{\text{WEU}}$ .

Byte write occurs if either WEL or WEU falls during the cycle. DQ pins don't achieve high impedance in this cycle, so data should be entered with TRG in "high".

2) Write cycle with mask:  $\overline{RAS}$  falling edge --  $\overline{WEL}$  or  $\overline{WEU}$  = "L"

If either  $\overline{\text{WEL}}$  or  $\overline{\text{WEU}}$  is set "low" at the falling edge of  $\overline{\text{RAS}}$ , the mask write mode can be invoked. Mask data is loaded and used. The mask data on DQ0 - DQ15 is latched into the write mask register at the falling edge of  $\overline{\text{RAS}}$ . When the mask data is low, writing is inhibited into the RAM and the mask data is high, data is written into the RAM. This mask data is in effect during the  $\overline{\text{RAS}}$  cycle. In page mode cycle the mask data is retained during page access.

Load/Read Color Register: RAS falling edge --- CAS = TRG = WEL = WEU = DSF = "H"

CAS falling edge --- DSF = "H"

The MSM5416282 is provided with an on-chip 16-bit color register for use during the flash write or block write operation. Each bit of the color register corresponds to one of the DRAM I/O blocks.

The data presented on the DQi lines is subsequently latched into the color register at the falling edge of either  $\overline{CAS}$  or  $\overline{WE}$  whichever occurs later.

The read color register cycle is activated by holding both  $\overline{WEL}$  and  $\overline{WEU}$  "high" at the falling edge of  $\overline{CAS}$ , and throughout the remainder of the cycle. The data in the color register becomes valid on the DQi lines after the specified access times from  $\overline{RAS}$  and  $\overline{TRG}$  are satisfied.

During the load/read color register cycle, the memory cells on the row address latched at the falling edge of  $\overline{RAS}$  are refreshed.

Flash Write: RAS falling edge --- CAS = TRG = DSF = "H", WEL = WEU = "L"

Flash write allows for the data in the color register to be written into all the memory locations of a selected row.

Each bit of the color register corresponds to one of the DRAM I/O blocks. The flash write operation can be selectively controlled on an I/O basis in the same manner as the write per bit operation. The mask data is the same as that of a RAM write cycle.

**OKI** Semiconductor MSM5416282

Block Write: RAS falling edge --- CAS = TRG = "H", DSF = "L"

CAS falling edge --- DSF = "H"

Block write allows for the data in the color register to be written into 8 consecutive column address locations, starting from a selected column address in a selected row.

The block write operation can be selectively controlled on an I/O basis, and a column mask capability is also available. This function is implemented as lower byte and upper byte. During a block write cycle, the 3 least significant column address locations (A0C, A1C and A2C) are internally controlled, and only the 6 most significant column addresses (A3C - A8C) are latched at the falling edge of  $\overline{\text{CAS}}$ .

- 1) No mask block write: WEL and WEU "high" at the falling edge of RAS The data on 16 DQ pins is cleared by the data of the color register.

- 2) Masked block write: WEL or WEU "low" at the falling edge of RAS

The mask data is the same as that of a RAM write cycle. (new mask and persistent mask)

|                | Bit 0      | Bit 15     |  |  |  |

|----------------|------------|------------|--|--|--|

| Color Register | 11001110   | 01110011   |  |  |  |

| I/O Mask       | 11111010   | 01101011   |  |  |  |

| Column Mask    | 10010011   | 00111100   |  |  |  |

|                | Lower Byte | Upper Byte |  |  |  |

|          | 8 Column × 8 DQ (Lower Byte) |     |     |     |     |     |     |     |     | 8 Column × 8 DQ (Upper Byte) |      |      |      |      |      |      |

|----------|------------------------------|-----|-----|-----|-----|-----|-----|-----|-----|------------------------------|------|------|------|------|------|------|

| Column 7 | 1                            | 1   | 0   | 0   | 1   | *   | 1   | *   | *   | *                            | *    | *    | *    | *    | *    | *    |

| Column 6 | 1                            | 1   | 0   | 0   | 1   | *   | 1   | *   | *   | *                            | *    | *    | *    | *    | *    | *    |

| Column 5 | *                            | *   | *   | *   | *   | *   | *   | *   | *   | 1                            | 1    | *    | 0    | *    | 1    | 1    |

| Column 4 | *                            | *   | *   | *   | *   | *   | *   | *   | *   | 1                            | 1    | *    | 0    | *    | 1    | 1    |

| Column 3 | 1                            | 1   | 0   | 0   | 1   | *   | 1   | *   | *   | 1                            | 1    | *    | 0    | *    | 1    | 1    |

| Column 2 | *                            | *   | *   | *   | *   | *   | *   | *   | *   | 1                            | 1    | *    | 0    | *    | 1    | 1    |

| Column 1 | *                            | *   | *   | *   | *   | *   | *   | *   | *   | *                            | *    | *    | *    | *    | *    | *    |

| Column 0 | 1                            | 1   | 0   | 0   | 1   | *   | 1   | *   | *   | *                            | *    | *    | *    | *    | *    | *    |

|          | DOO                          | DQ1 | DQ2 | D03 | DQ4 | D05 | D06 | DQ7 | 008 | 000                          | DQ10 | DQ11 | DQ12 | DQ13 | DQ14 | DQ15 |

Note: Location "\*" can not be loaded.

#### **Example of Block Write**

#### SAM PORT OPERATION

#### Single Register Mode

High speed serial read or write operations can be performed through the SAM port independent of the RAM port operation, except during read/write transfer cycles.

The preceding transfer operation determines the direction of data flow through the SAM port. If the preceding transfer is a read transfer, the SAM port is in the output mode. If the preceding transfer is write transfer, the SAM port is in the input mode.

Serial data can be read out of the SAM after a read transfer has been performed. The data is shifted out of the SAM starting at any of the 512 bits locations.

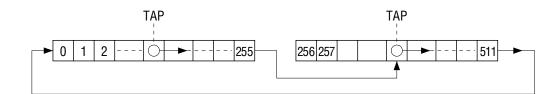

The TAP location corresponds to the column address selected at the falling edge of  $\overline{\text{CAS}}$  during the read or write transfer cycle. The SAM registers are configured as a circular data register. The data is shifted out sequentially. It starts from the selected TAP location at the most significant bit (511), then wraps around to the least significant bit (0).

#### Split Register Mode

In split register mode data can be shifted into or out of one half of the SAM, while a split read or split write transfer is being performed on the other half of the SAM.

Conventional (non split) read, or write transfer cycle must precede any split read or split write transfers. The split read and write transfers will not change the SAM port mode set by the preceding conventional transfer operation. In the split register mode, serial data can be shifted in or out of one of the split SAM registers, starting from any at the 256 TAP locations, excluding the last address of each split SAM the data is shifted in or out sequentially starting from the selected TAP location at the most significant bit (255 or 511) of the first split SAM, and then the SAM pointer moves to the TAP location selected for the second split SAM to shift data in or out sequentially, starts from this TAP location at the most significant bit (511 or 255), and finally wraps around to the least significant bit.

#### DATA TRANSFER OPERATIONS

The MSM5416282 features two types of bidirectional data transfer capability between RAM and SAM.

- 1) Conventional (non split) transfer: 512 words by 16 bits of data can be loaded from RAM to SAM (Read transfer), or from SAM to RAM (Write transfer).

- 2) Split transfer: 256 words by 16 bits of data can be loaded from the lower/upper half of the RAM to the lower/upper half of the SAM (Split read transfer), or from the lower/upper half of SAM to the lower/upper half of RAM (Split write transfer).

The conventional transfer and split transfer modes are controlled by the DSF input signal. Data transfer is invoked by holding the  $\overline{TRG}$  signal "low" at the falling edge of  $\overline{RAS}$ .

The MSM5416282 supports 4 types of transfer operations: Read transfer, Split read transfer, Write transfer and Split write transfer as shown in the truth table. The type of transfer operation is determined by the state of  $\overline{CAS}$ ,  $\overline{WEL}$ ,  $\overline{WEU}$  and DSF latched at the falling edge of  $\overline{RAS}$ . During conventional transfer operations, the SAM port is switched from input to output mode (Read transfer), or output to input mode (Write transfer). It remains unchanged during split transfer operation (Split read transfer or Split write transfer).

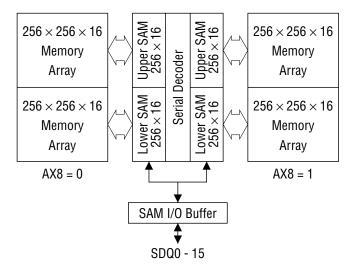

Both RAM and SAM are divided by the most significant row address (AX8), as shown in Figure 1. Therefore, no data transfer between AX8 = 0 side RAM and AX8 = 1 side RAM can be provided through the SAM. Care must be taken if the split read transfer on AX8 = 1 side (or AX8 = 0 side) is provided after the read transfer or the split read transfer, is provided on AX8 = 0 side (or AX8 = 1 side).

Figure 1. RAM and SAM Configuration

## Read Transfer: RAS falling edge --- CAS = WEL = WEU = "H", TRG = DSF = "L"

Read transfer consists of loading a selected row of data from the RAM into the SAM register. A read transfer is invoked by holding  $\overline{CAS}$  "high",  $\overline{TRG}$  "low",  $\overline{WEL}$  and  $\overline{WEU}$  "high", and DSF "low" at the falling edge of  $\overline{RAS}$ . The row address selected at the falling edge of  $\overline{RAS}$  determines the RAM row to be transferred into the SAM. The transfer cycle is completed at the rising edge of  $\overline{TRG}$ . When the transfer is completed, the SAM port is set into the output mode. In a read/real time read transfer cycle, the transfer of a new row of data is completed at the rising edge of  $\overline{TRG}$ , and this data becomes valid on the SDQ lines after the specified access time  $t_{SCA}$  from the rising edge of the subsequent SC cycles. The start address of the serial pointer of the SAM is determined by the column address selected at the falling edge of  $\overline{CAS}$ . In a read transfer cycle (which is preceded by a write transfer cycle), SC clock must be held at a constant  $V_{IL}$  or  $V_{IH}$  after the SC high time has been satisfied. A rising edge of the SC clock must not occur until after the specified delay  $t_{TSD}$  from the rising edge of  $\overline{TRG}$ .

In a real time read transfer cycle (which is preceded by another read transfer cycle), the previous row data appears on the SQD lines until the  $\overline{TRG}$  signal goes "high", and the serial access time  $t_{SCA}$  for the following serial clock is satisfied. This feature allows for the first bit of the new row of data to appear on the serial output as soon as the last bit of the previous row has been strobed without any timing loss. To make this continuous data flow possible, the rising edge of  $\overline{TRG}$  must be synchronized with  $\overline{RAS}$ ,  $\overline{CAS}$ , and the subsequent rising edge of SC ( $t_{RTH}$ ,  $t_{CTH}$  and  $t_{TSL}/t_{TSD}$  must be satisfied).

# Masked Write Transfer: RAS falling edge --- CAS = "H", TRG = DSF = "L" WEL or WEU = "L"

Write transfer cycle consists of loading the content of the SAM register into a selected row of the RAM. This write transfer operation, which is the same as a mask write operation in RAM, can be selectively controlled for 16 DQis by inputing the mask data from DQ0 - DQ15 at the falling edge of  $\overline{RAS}$ .

If the SAM data to be transferred must first be loaded through the SAM, a Masked write transfer operation (all DQ pins "low" at falling edge of  $\overline{RAS}$ ) must precede the write transfer cycles. A masked write transfer is invoked by holding  $\overline{CAS}$  "high",  $\overline{TRG}$  "low",  $\overline{WEL}$  or  $\overline{WEU}$  "low", and DSF "low" at the falling edge of  $\overline{RAS}$ . The row address selected at the falling edge of  $\overline{RAS}$  determines the RAM row address into which the data will be transferred. The column address selected at the falling edge of  $\overline{CAS}$  determines the start address of the serial pointer of the SAM. After the write transfer is completed, the SDQ lines are set in the input mode so that serial data synchronized with the SC clock can be loaded.

When consecutive write transfer operations are performed, new data must not be written into the serial register until the  $\overline{RAS}$  cycle of the preceding write transfer is completed. Consequently, the SC clock must be held at a constant  $V_{IL}$  or  $V_{IH}$  during the  $\overline{RAS}$  cycle. A rising edge of the SC clock is only allowed after the specified delay  $t_{CSD}$  from the falling edge of the  $\overline{CAS}$ , at which time a new row of data can be written in the serial register.

Data transferred to SAM by read transfer cycle or split read transfer cycle can be written to the other address of RAM by write transfer cycle. However, the address to write data must be the same as that of the read transfer cycle (row address AX8).

OKI Semiconductor MSM5416282

#### Split Data Transfer and QSF

The MSM5416282 features a bidirectional split data transfer capability between the RAM and SAM. During split data transfer operation, the serial register is split into two halves which can be controlled independently. Split read or split write transfer operation can be performed to or from one half of the serial register, while serial data can be shifted into or out of the other half of the serial register. The most significant column address location (A8C) is controlled internally to determine which half of the serial register will be reloaded from the RAM. QSF is an output which indicates which half of the serial register is in an active state. QSF changes state when the last SC clock is applied to active split SAM.

Split read transfer consists of loading 256 words by 16 bits of data from a selected row of the split RAM into the corresponding non-active split SAM register. Serial data can be shifted out from the other half of the split SAM register simultaneously. During split read transfer operation, the RAM port input clocks do not have to be synchronized with the serial clock SC, thus eliminating timing restrictions as in the case of real time read transfers. A split read transfer can be performed after a delay of  $t_{\rm STS}$  from the change of state of the QSF output is satisfied.

Conventional (non-split) read transfer operation must precede split read transfer cycles.

Split write transfer consists of loading 256 words by 16 bits of data from the non-active split SAM register into a selected row of the corresponding split RAM. Serial data can be shifted into the other half of the split SAM register simultaneously. During split write transfer operation, the RAM port input clocks do not have to be synchronized with the serial clock SC, thus allowing for real time transfer. This write transfer operation, which is the same as a mask write operation in RAM, can be selectively controlled for 16 DQis by inputing the mask data from DQ0 - DQ15 at the falling edge of  $\overline{RAS}$ .

A split write transfer can be performed after a delay of t<sub>STS</sub> from the change of state of the QSF output is satisfied.

A masked write transfer operation must precede split write transfer. The purpose is to switch the SAM port from output mode to input mode, and to set the initial TAP location prior to split write transfer operations.

#### **POWER UP**

Power must be applied to the  $\overline{RAS}$  and  $\overline{TRG}$  input signals to pull them "high" before, or at the same time as, the  $V_{CC}$  supply is turned on. After power-up, a pause of 200  $\mu$ s minimum is required with  $\overline{RAS}$  and  $\overline{TRG}$  held "high". After the pause, a minimum of  $8\,\overline{RAS}$  and  $8\,SC$  dummy cycles must be performed to stabilize the internal circuitry, before valid read, write or transfer operations can begin. During the initialization period, the  $\overline{TRG}$  signal must be held "high". If the internal refresh counter is used, a minimum  $8\,\overline{CAS}$  before  $\overline{RAS}$  cycles are required instead of  $8\,\overline{RAS}$  cycles.

#### (NOTE) INITIAL STATE AFTER POWER UP

The initial state can not be guaranteed for various power up conditions and input signal levels. Therefore, it is recommended that the initial state be set after the initialization of the device is performed and before valid operations begin.

OKI Semiconductor MSM5416282

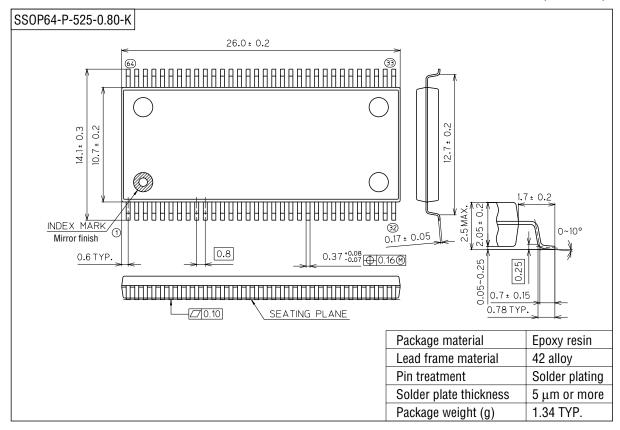

#### PACKAGE DIMENSIONS

(Unit: mm)

Notes for Mounting the Surface Mount Type Package

The SOP, QFP, TSOP, SOJ, QFJ (PLCC), SHP and BGA are surface mount type packages, which are very susceptible to heat in reflow mounting and humidity absorbed in storage. Therefore, before you perform reflow mounting, contact Oki's responsible sales person for the product name, package name, pin number, package code and desired mounting conditions (reflow method, temperature and times).