# **OKI** Semiconductor

This version: Jan. 1998 Previous version: Nov. 1996

# MSM80C154S/83C154S

**CMOS 8-bit Microcontroller**

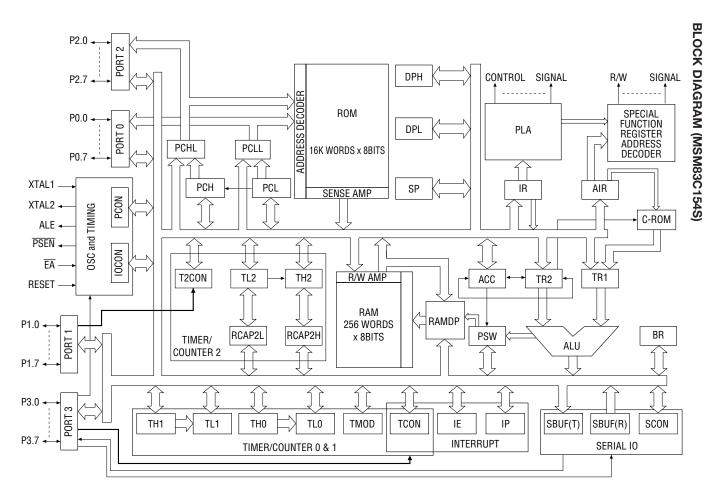

#### **GENERAL DESCRIPTION**

The MSM80C154S/MSM83C154S, designed for the high speed version of the existing MSM80C154/MSM83C154, is a higher performance 8-bit microcontroller providing low-power consumption.

The MSM80C154S/MSM83C154S covers the functions and operating range of the existing MSM80C154/83C154/80C51F/80C31F.

The MSM80C154S is identical to the MSM83C154S except it does not contain the internal program memory (ROM).

#### **FEATURES**

Operating range

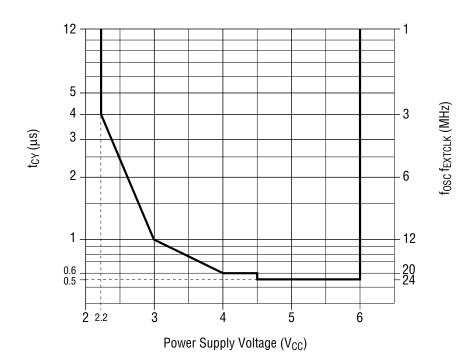

Operating frequency :  $0 \text{ to } 3 \text{ MHz} \text{ (V}_{cc}=2.2 \text{ to } 6.0 \text{ V)}$

0 to 12 MHz ( $V_{cc}$ =3.0 to 6.0 V) 0 to 24 MHz ( $V_{cc}$ =4.5 to 6.0 V)

Operating voltage : 2.2 to 6.0 V

Operating temperature : -40 to +85°C (Operation at +125°C conforms to

the other specification.)

• Fully static circuit

Upward compatible with the MSM80C51F/80C31F

• On-chip program memory : 16K words x 8 bits ROM (MSM83C154S only)

On-chip data memory

External program memory address space

64K bytes ROM (Max)

External data memory address space

64K bytes RAM

I/O ports

4 ports x 8 bits

(Port 1, 2, 3, impedance programmable) : 32 • 16-bit timer/counters : 3

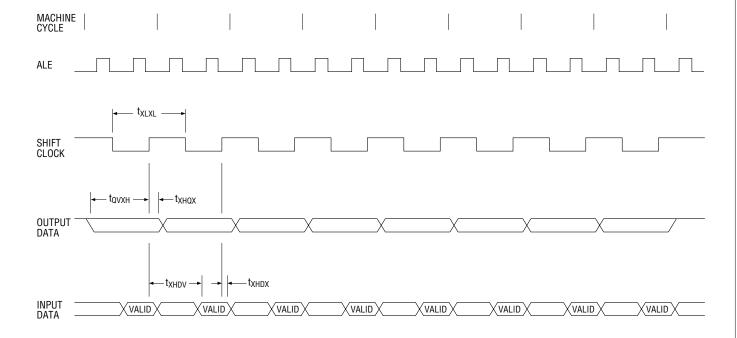

• Multifunctional serial port : I/O Expansion mode

: UART mode (featuring error detection)

• 6-source 2-priority level Interrupt and multi-level

Interrupt available by programming IP and IE registers

Memory-mapped special function registers

Bit addressable data memory and SFRs

Minimum instruction cycle : 500 ns @ 24 MHz operation

• Standby functions : Power-down mode (oscillator stop)

Activated by software or hardware; providing

ports with floating or active status

The software power-down stet mode is terminated by interrupt signal enabling execution from

the interrupted address.

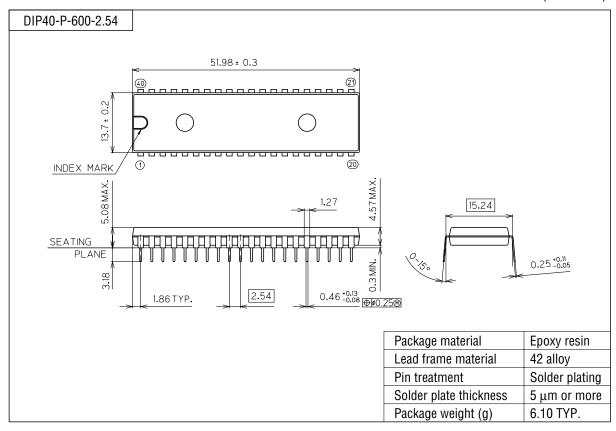

• Package options

40-pin plastic DIP (DIP40-P-600-2.54) : (Product name: MSM80C154SRS/

MSM83C154S-xxxRS)

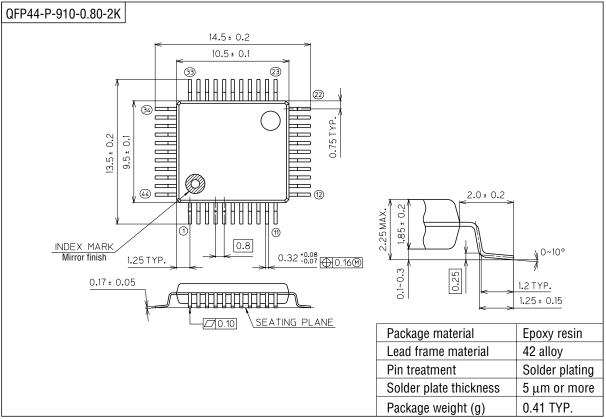

44-pin plastic QFP (QFP44-P-910-0.80-2K): (Product name: MSM80C154SGS-2K/

MSM83C154S-xxxGS-2K)

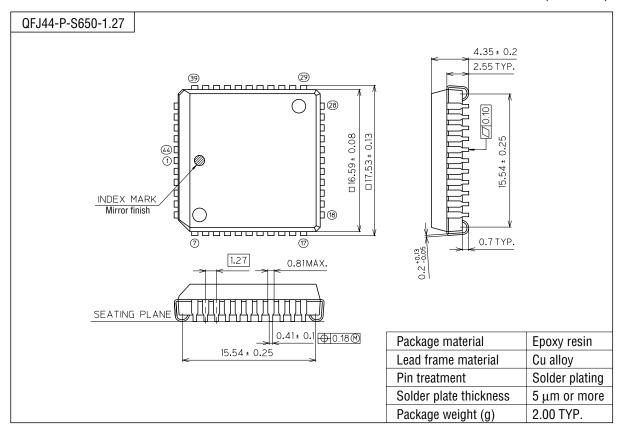

44-pin QFJ (QFJ44-P-S650-1.27) : (Product name: MSM80C154SJS/

MSM83C154S-xxxJS)

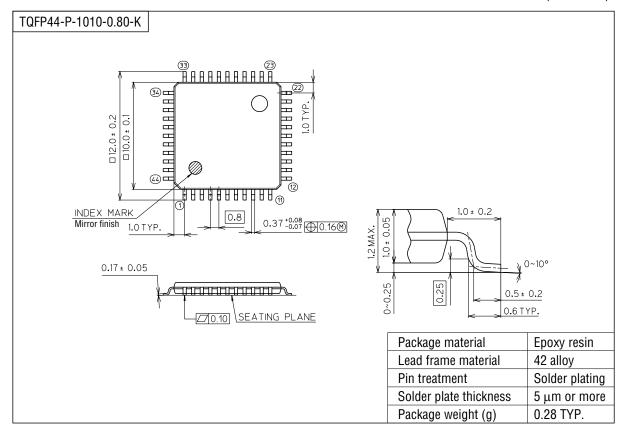

44-pin TQFP (TQFP44-P-1010-0.80-K) : (Product name: MSM80C154STS-K/

MSM83C154S-xxxTS-K)

xxx: indicates the code number

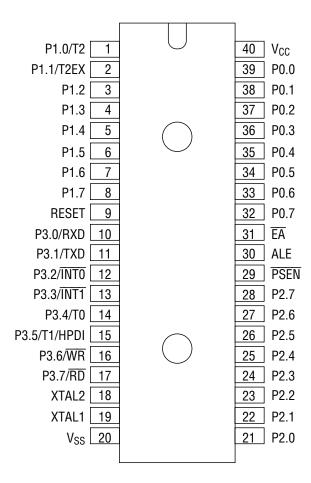

## **PIN CONFIGURATION (TOP VIEW)**

40-Pin Plastic DIP

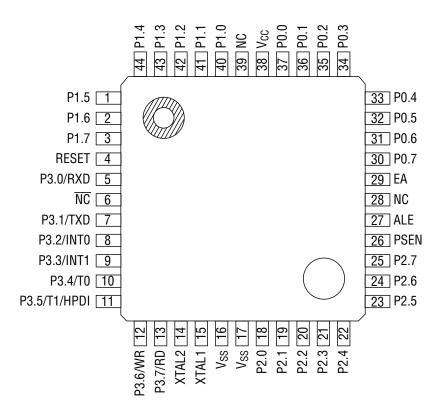

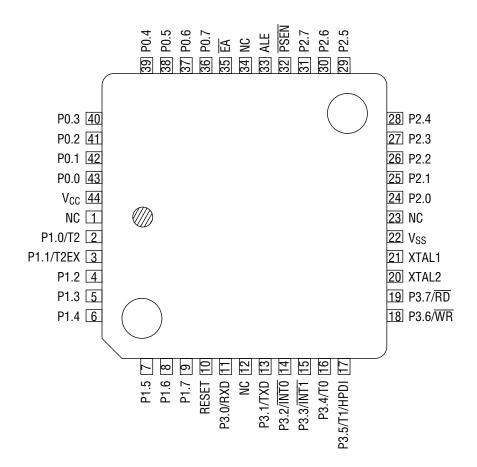

## **PIN CONFIGURATION (Continued)**

NC: No-connection pin

44-Pin Plastic QFP

NC: No-connection pin

44-Pin Plastic TQFP

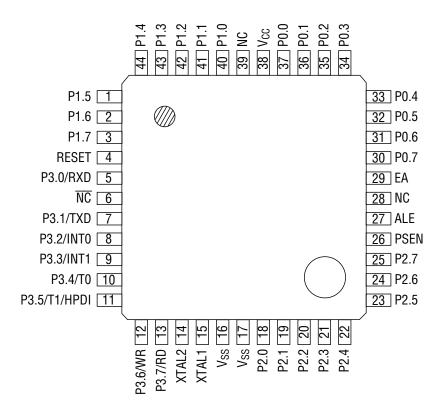

## **PIN CONFIGURATION (Continued)**

NC: No-connection pin

44-Pin Plastic QFJ

## **PIN DESCRIPTIONS**

| Symbol       | Descriptipn                                                                                                                                                                                                                                                                                                                                                           |

|--------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| P0.0 to P0.7 | Bidirectional I/O ports. They are also the data/address bus (input/output of data and output of lower 8-bit address when external memory is accessed). They are open-drain outputs when used as I/O ports, but 3-state outputs when used as data/address bus.                                                                                                         |

| P1.0 to P1.7 | P1.0 to P1.7 are quasi-bidirectional I/O ports. They are pulled up internally when used as input ports. Two of them have the following secondary functions:  •P1.0 (T2) : used as external clock input pins for the timer/counter 2.  •P1.1 (T2EX) : used as trigger input for the timer/counter 2 to be reloaded or captured; causing the timer/counter 2 interrupt. |

| P2.0 to P2.7 | P2.0 to P2.7 are quasi-bidirectional I/O ports. They also output the higher 8-bit address when an external memory is accessed. They are pulled up internally when used as input ports.                                                                                                                                                                                |

| P3.0 to P3.7 | P3.0 to P3.7 are quasi-bidirectional I/O ports. They are pulled up internally when used as input ports. They also have the following secondary functions:  •P3.0 (RXD)  Serial data input/output in the I/O expansion mode and serial data input in the UART mode when the serial port is used.                                                                       |

|              | <ul> <li>•3.1 (TXD)</li> <li>Synchronous clock output in the I/O expansion mode and serial data output in the UART mode when the serial port is used.</li> <li>•3.2 (INTO)</li> <li>Used as input pin for the external interrupt 0, and as count-up control pin for the timer/counter 0.</li> </ul>                                                                   |

|              | <ul> <li>•3.3 (INT1)</li> <li>Used as input pin for the external interrupt 1, and as count-up control pin for the timer/counter 1.</li> <li>•3.4 (T0)</li> <li>Used as external clock input pin for the timer/counter 0.</li> </ul>                                                                                                                                   |

|              | <ul> <li>•3.5 (T1) Used as external clock input pin for the timer/counter 1 and power-down-mode control input pin.</li> <li>•3.6 (WR) Output of the write-strobe signal when data is written into external data memory.</li> <li>•3.7 (RD) Output of the read-strobe signal when data is read from external data memory.</li> </ul>                                   |

| ALE          | Address latch enable output for latching the lower 8-bit address during external memory access.  Two ALE pulses are activated per machine cycle except during external data memory access at which time one ALE pulse is skipped.                                                                                                                                     |

| PSEN         | Program store enable output which enables the external memory output to the bus during external program memory access. Two PSEN pulses are activated per machine cycle except during external data memory access at which two PSEN pulses are skipped.                                                                                                                |

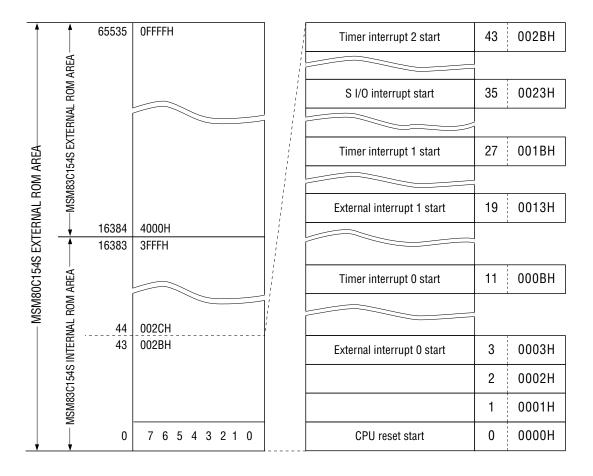

| ĒĀ           | When $\overline{EA}$ is held at "H" level, the MSM 83C154S executes instructions from internal program memory at address 0000H to 3FFFH, and executes instructions from external program memory above address 3FFFH.  When $\overline{EA}$ is held at "L" level, the MSM80C154S/MSM83C154S executes instructions from external program memory for all addresses.      |

# **PIN Descriptions (Continued)**

| Symbol          | Descriptipn                                                                                                                                                                                                                               |

|-----------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| RESET           | If this pin remains "H" for at least one machine cycle, the MSM80C154S/MSM83C154S is reset. Since this pin is pulled down internally, a power-on reset is achieved by simply connecting a capacitor between $V_{\text{CC}}$ and this pin. |

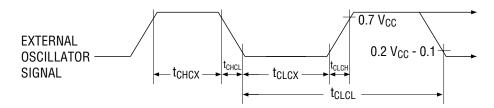

| XTAL1           | Oscillator inverter input pin. External clock is input through XTAL1 pin.                                                                                                                                                                 |

| XTAL2           | Oscillator inverter output pin.                                                                                                                                                                                                           |

| V <sub>CC</sub> | Power supply pin during both normal operation and standby operations.                                                                                                                                                                     |

| V <sub>SS</sub> | GND pin.                                                                                                                                                                                                                                  |

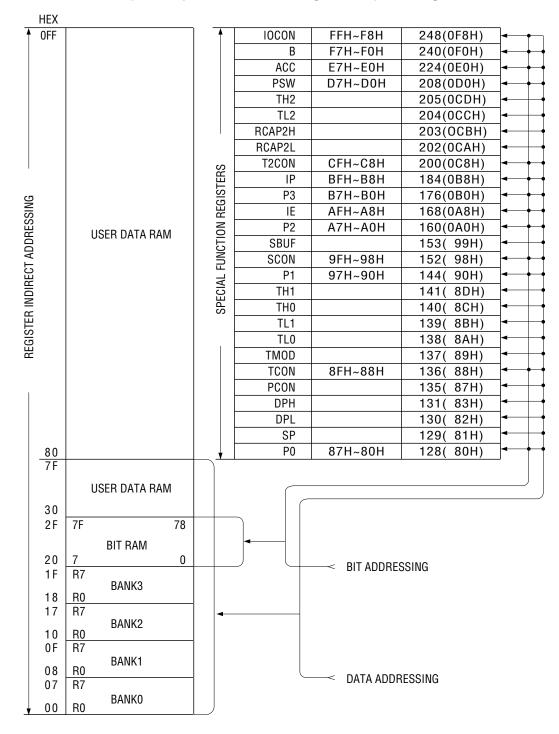

## **REGISTERS**

## **Diagram of Special Function Registers**

| REGISTER |    |    |    | BIT AD | DRESS |    |    |    | DIRECT     |

|----------|----|----|----|--------|-------|----|----|----|------------|

| NAME     | b7 | b6 | b5 | b4     | b3    | b2 | b1 | b0 | ADDRESS    |

| IOCON    | FF | FE | FD | FC     | FB    | FA | F9 | F8 | 0F8H (248) |

| В        | F7 | F6 | F5 | F4     | F3    | F2 | F1 | F0 | 0F0H (240) |

| ACC      | E7 | E6 | E5 | E4     | E3    | E2 | E1 | E0 | 0E0H (224) |

| PSW      | D7 | D6 | D5 | D4     | D3    | D2 | D1 | D0 | 0D0H (208) |

| TH2      |    |    |    |        |       |    |    |    | 0CDH (205) |

| TL2      |    |    |    |        |       |    |    |    | 0CCH (204) |

| RCAP2H   |    |    |    |        |       |    |    |    | 0CBH (203) |

| RCAP2L   |    |    |    |        |       |    |    |    | 0CAH (202) |

| T2CON    | CF | CE | CD | CC     | СВ    | CA | C9 | C8 | 0C8H (200) |

| IP       | BF | BE | BD | BC     | BB    | BA | В9 | B8 | 0B8H (184) |

| P3       | В7 | В6 | B5 | B4     | В3    | B2 | B1 | В0 | 0B0H (176) |

| IE       | AF | AE | AD | AC     | AB    | AA | A9 | A8 | 0A8H (168) |

| P2       | A7 | A6 | A5 | A4     | А3    | A2 | A1 | A0 | 0A0H (160) |

| SBUF     |    |    |    |        |       |    |    |    | 99H (153)  |

| SCON     | 9F | 9E | 9D | 9C     | 9B    | 9A | 99 | 98 | 98H (152)  |

| P1       | 97 | 96 | 95 | 94     | 93    | 92 | 91 | 90 | 90H (144)  |

| TH1      |    |    |    |        |       |    |    |    | 8DH (141)  |

| TH0      |    |    |    |        |       |    |    |    | 8CH (140)  |

| TL1      |    |    |    |        |       |    |    |    | 8BH (139)  |

| TL0      |    |    |    |        |       |    |    |    | 8AH (138)  |

| TMOD     |    |    |    |        |       |    |    |    | 89H (137)  |

| TCON     | 8F | 8E | 8D | 8C     | 8B    | 8A | 89 | 88 | 88H (136)  |

| PCON     |    |    |    |        |       |    |    |    | 87H (135)  |

| DPH      |    |    |    |        |       |    |    |    | 83H (131)  |

| DPL      |    |    |    |        |       |    |    |    | 82H (130)  |

| SP       |    |    |    |        |       |    |    |    | 81H (129)  |

| P0       | 87 | 86 | 85 | 84     | 83    | 82 | 81 | 80 | 80H (128)  |

# **Special Function Registers**

# Timer mode register (TMOD)

| NAME                | ADDDECC | MSB                   |                                           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                           |                           |                    |                  | LSB     |  |

|---------------------|---------|-----------------------|-------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------|---------------------------|--------------------|------------------|---------|--|

| NAME                | ADDRESS | 7                     | 6                                         | 5                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 4                                         | 3                         | 2                  | 1                | 0       |  |

| TMOD                | 89H     | GATE                  | C/T                                       | M1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | M0                                        | GATE                      | C/T                | M1               | M0      |  |

| <b>BIT LOCATION</b> | FLAG    |                       |                                           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | FUNC                                      | CTION                     |                    |                  |         |  |

| TMOD.0              | M0      | M1                    | M0                                        | Timer/co                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | unter 0 mc                                | de setting                |                    |                  |         |  |

|                     |         | 0                     | 0                                         | 8-bit tim                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | er/counter                                | with 5-bit                | prescalar.         |                  |         |  |

|                     |         | 0                     | 1                                         | 16-bit timer/counter.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                           |                           |                    |                  |         |  |

|                     |         | 1                     | 0                                         | 8-bit tim                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | er/counter                                | with 8-bit                | auto reload        | ding.            |         |  |

| TMOD.1              | M1      | 1                     | 1                                         | and TH0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | unter 0 sep<br>(8-bit) tim<br>t by TH0 ca | er/counter.               |                    |                  |         |  |

| TMOD.2              | C/T     | XTAL1•2<br>C/T = "0". | divided by                                | ount clock of the state of the | is the inpu                               | ıt applied t              | o timer/co         |                  |         |  |

| TMOD.3              | GATE    | control th            | ie start an<br>is "1", tim                | , the TR0 b<br>d stop of ti<br>er/counter<br>signal are                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | mer/count<br>0 starts co                  | er 0 counti<br>unting who | ng.<br>en both the | ·<br>e TR0 bit o | of TCON |  |

| TMOD.4              | M0      | M1                    | M0                                        | Timer/co                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | unter 1 mc                                | de setting                |                    |                  |         |  |

|                     |         | 0                     | 0                                         | 8-bit time                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | er/counter                                | with 5-bit                | prescalar.         |                  |         |  |

|                     |         | 0                     | 1                                         | 16-bit tin                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | ner/counte                                | r                         |                    |                  |         |  |

| TMOD.5              | M1      | 1                     | 0                                         | 8-bit time                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | er/counter                                | with 8-bit                | auto reload        | ding.            |         |  |

| G.UUIVI 1           | IVI I   | 1                     | 1                                         | Timer/co                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | unter 1 op                                | eration sto               | pped.              |                  |         |  |

| TMOD.6              | C/T     | XTAL1•2<br>C/T = "0". | divided by                                | ount clock of the state of the | is the inpu                               | ıt applied t              | o timer/co         |                  |         |  |

| TMOD.7              | GATE    | When this timer/cou   | s bit is "0"<br>inter 1 co<br>is "1", tim | , the TR1 b<br>unting.<br>er/counter<br>signal are                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 1 starts co                               | unting who                | en both the        | e TR1 bit o      | of TCON |  |

# Power control register (PCON)

| NAME         | ADDRESS | MSB                                                           |                                                                                |                                                                  |                                                                          |                                                       |                                          |                            | LSB                |

|--------------|---------|---------------------------------------------------------------|--------------------------------------------------------------------------------|------------------------------------------------------------------|--------------------------------------------------------------------------|-------------------------------------------------------|------------------------------------------|----------------------------|--------------------|

| IVAIVIE      | ADDRESS | 7                                                             | 6                                                                              | 5                                                                | 4                                                                        | 3                                                     | 2                                        | 1                          | 0                  |

| PCON         | 87H     | SMOD                                                          | HPD                                                                            | RPD                                                              |                                                                          | GF1                                                   | GF0                                      | PD                         | IDL                |

| BIT LOCATION | FLAG    |                                                               |                                                                                |                                                                  | FUNC                                                                     | TION                                                  |                                          |                            |                    |

| PCON.0       | IDL     | IDLE mod<br>and the s                                         | de is set, b<br>erial port r                                                   | hen this bi<br>ut XTAL1•<br>emain acti<br>it is genera           | 2, timer/co<br>ve.  IDLE n                                               | unters 0, 1                                           | and 2, the                               | e interrupt                | circuits,          |

| PCON.1       | PD      | stopped \                                                     | when PD n                                                                      | en this bit i<br>node is set<br>s generated                      | . PD mode                                                                |                                                       |                                          |                            |                    |

| PCON.2       | GF0     | General p                                                     | urpose bit                                                                     |                                                                  |                                                                          |                                                       |                                          |                            |                    |

| PCON.3       | GF1     | General p                                                     | urpose bit                                                                     |                                                                  |                                                                          |                                                       |                                          |                            |                    |

| PCON.4       | _       | Reserved                                                      | bit. The c                                                                     | output data                                                      | is "1", if th                                                            | e bit is rea                                          | ıd.                                      |                            |                    |

| PCON.5       | RPD     | interrupt Power-do enabled b If the inte "1" (even of the pow | signal.<br>own mode<br>oy IE (inter<br>rrupt flag<br>if interrupt<br>wer-down- |                                                                  | cancelled I<br>e register)<br>' by an inte<br>d), the pro<br>ing instruc | oy an inter<br>when this<br>errupt requ<br>gram is ex | rupt signal<br>bit is "0".<br>est signal | if the inte                |                    |

| PCON.6       | HPD     | If the leve<br>is change                                      | el of the po<br>ed from "1"<br>m is put in                                     | wn setting<br>ower failure<br>to "0" whe<br>to hard po           | detect sign this bit is                                                  | nal applied<br>s "1", XTAL                            | d to the HP<br>.1•2 oscilla              | DI pin (pir<br>tion is sto | n 3.5)<br>pped and |

| PCON.7       | SMOD    | the serial<br>The seria<br>processir                          | port, this<br>I port oper                                                      | inter 1 carr<br>bit has the<br>ation clock<br>he bit is "1<br>g. | following to is reduced                                                  | functions.<br>d by 1/2 w                              | hen the bit                              | is "0" for o               | delayed            |

# Timer control register (TCON)

| NAME         | ADDDECC | MSB        |                          |                                            |             |             |          |                | LSB        |

|--------------|---------|------------|--------------------------|--------------------------------------------|-------------|-------------|----------|----------------|------------|

| NAME         | ADDRESS | 7          | 6                        | 5                                          | 4           | 3           | 2        | 1              | 0          |

| TCON         | 88H     | TF1        | TR1                      | TF0                                        | TR0         | IE1         | IT1      | IE0            | IT0        |

| BIT LOCATION | FLAG    |            |                          |                                            | FUNC        | TION        | •        |                |            |

| TCON.0       | IT0     |            | nterrupt 0<br>etect mode | •                                          | sed in leve | l-detect m  | ode when | this bit is "  | 0" and in  |

| TCON.1       | IE0     | The bit is | reset auto               | ng for exter<br>matically v<br>nd reset by | vhen an int | errupt is s |          |                |            |

| TCON.2       | IT1     |            | nterrupt 1<br>etect mode |                                            | sed in leve | l detect m  | ode when | this bit is "( | O", and in |

| TCON.3       | IE1     | The bit is | reset auto               | ng for exter<br>matically v<br>nd reset by | vhen an int | errupt is s |          |                |            |

| TCON.4       | TR0     |            |                          | stop contro<br>rts countin                 |             |             |          | s counitng     | when "0".  |

| TCON.5       | TF0     | The bit is | reset auto               | ng for time<br>matically v<br>when a car   | vhen an int | errupt is s |          | er/counter     | 0.         |

| TCON.6       | TR1     | _          |                          | stop contro<br>starts cour                 |             |             |          | ps countin     | g when "0" |

| TCON.7       | TF1     | The bit is | reset auto               | ng for timen<br>matically v<br>when carry  | vhen interr | upt is serv |          | /counter 1     |            |

# Serial port control register (SCON)

| NAME         | ADDDECC | MSB                                              |                                                         |                                                           |                                                                                       |                                      |                                            |            | LSB     |

|--------------|---------|--------------------------------------------------|---------------------------------------------------------|-----------------------------------------------------------|---------------------------------------------------------------------------------------|--------------------------------------|--------------------------------------------|------------|---------|

| INAIVIE      | ADDRESS | 7                                                | 6                                                       | 5                                                         | 4                                                                                     | 3                                    | 2                                          | 1          | 0       |

| SCON         | 98H     | SM0                                              | SM1                                                     | SM2                                                       | REN                                                                                   | TB8                                  | RB8                                        | TI         | RI      |

| BIT LOCATION | FLAG    |                                                  |                                                         |                                                           | FUNC                                                                                  | TION                                 |                                            |            |         |

| SCON.0       | RI      | This flag<br>This flag<br>by the ST<br>In mode 2 | must be re<br>is set after<br>OP bit whe<br>2 or 3, how | eset by soft<br>the eighth<br>en in any o<br>vever, RI is | nterrupt rec<br>ware during<br>bit of data<br>ther mode<br>s not set if<br>is receive | ng interrup<br>has been<br>the RB8 d | t service ro<br>received w<br>ata is "0" w | /hen in mo | ,       |

| SCON.1       | TI      | by softwa<br>This flag                           | re during i<br>is set after                             | interrupt se<br>the eighth                                | on" interrup<br>ervice rout<br>bit of data<br>ent when in                             | ine.<br>ı has been                   | sent when                                  |            |         |

| SCON.2       | RB8     | The STOF                                         | bit is app                                              |                                                           | n mode 2<br>3 if SM2 =<br>0.                                                          |                                      |                                            | 3.         |         |

| SCON.3       | TB8     |                                                  |                                                         |                                                           | nth data bit<br>TB8 by so                                                             |                                      | node 2 or 3                                | 3.         |         |

| SCON.4       | REN     | No recept                                        | n enable co<br>tion when<br>n enabled v                 |                                                           | = "1".                                                                                |                                      |                                            |            |         |

| SCON.5       | SM2     | reception<br>The "end                            | " signal is                                             | not set in t<br>on" signal s                              | a is "0" with<br>the RI flag.<br>et in the R                                          |                                      |                                            |            |         |

| SCON.6       | SM1     | SM0                                              | SM1                                                     | MODE                                                      | <br>                                                                                  |                                      |                                            |            |         |

|              |         | 0                                                | 0                                                       | 0                                                         | 8-bit shif                                                                            | t register l                         | /0                                         |            |         |

|              |         | 0                                                | 1                                                       | 1                                                         | 8-bit UAF                                                                             | RT variable                          | baud rate                                  |            |         |

| SCON.7       | SM0     | 1                                                | 0                                                       | 2                                                         | 9-bit UAF                                                                             | RT 1/32 XT                           | AL1, 1/64                                  | XTAL1 ba   | ud rate |

|              |         | 1                                                | 1                                                       | 3                                                         | 9-bit UAF                                                                             | RT variable                          | baud rate                                  |            |         |

## Interrupt enable register (IE)

| NAME         | ADDRESS | MSB         |            |                                             |               |              |             |     | LSB |

|--------------|---------|-------------|------------|---------------------------------------------|---------------|--------------|-------------|-----|-----|

| NAME         | ADDRESS | 7           | 6          | 5                                           | 4             | 3            | 2           | 1   | 0   |

| IE           | 0A8H    | EA          | _          | ET2                                         | ES            | ET1          | EX1         | ET0 | EX0 |

| BIT LOCATION | FLAG    |             |            |                                             | FUNC          | TION         |             |     |     |

| IE.0         | EX0     | Interrupt . | disabled w | for extern<br>then bit is 'hen bit is '     | '0".          | t <b>0</b> . |             |     |     |

| IE.1         | ET0     | Interrupt   | disabled w | for timer i<br>hen bit is '<br>hen bit is " | '0".          |              |             |     |     |

| IE.2         | EX1     | Interrupt   | disabled w | for extern<br>hen bit is hen bit is "       | '0".          | 11.          |             |     |     |

| IE.3         | ET1     | Interrupt   | disabled w | for timer i<br>hen bit is 'hen bit is '     | '0".          |              |             |     |     |

| IE.4         | ES      | Interrupt . | disabled w | for serial  <br>hen bit is 'hen bit is '    | '0".          |              |             |     |     |

| IE.5         | ET2     | Interrupt   | disabled w | for timer i<br>hen bit is 'hen bit is '     | '0".          |              |             |     |     |

| IE.6         | _       | Reserved    | bit. The c | utput data                                  | is "1" if the | e bit is rea | d.          |     |     |

| IE.7         | EA      | All interru | •          | ntrol bit.<br>sabled whe<br>ntrolled by     |               |              | bit is "1". |     |     |

## Interrupt priority register (IP)

| NAME         | ADDRESS | MSB<br>7  | 6                          | 5                          | 4                       | 3                                            | 2            | 1           | LSB<br>0 |

|--------------|---------|-----------|----------------------------|----------------------------|-------------------------|----------------------------------------------|--------------|-------------|----------|

| IP           | 0B8H    | PCT       | _                          | PT2                        | PS                      | PT1                                          | PX1          | PT0         | PX0      |

| BIT LOCATION | FLAG    |           |                            |                            | FUN                     | CTION                                        |              |             |          |

| IP.0         | PX0     |           |                            | for extern<br>when bit is  |                         | ot 0.                                        |              |             |          |

| IP.1         | PT0     |           |                            | for timer i<br>when bit is |                         | ).                                           |              |             |          |

| IP.2         | PX1     |           |                            | for extern<br>when bit is  |                         | ot 1.                                        |              |             |          |

| IP.3         | PT1     |           |                            | for timer i                |                         |                                              |              |             |          |

| IP.4         | PS      |           |                            | for serial<br>when bit is  |                         |                                              |              |             |          |

| IP.5         | PT2     |           |                            | for timer i<br>when bit is |                         |                                              |              |             |          |

| IP.6         |         | Reserved  | bit. The o                 | utput data                 | is "1" if th            | e bit is rea                                 | d.           |             |          |

| IP.7         | PCT     | The prior | ity register<br>d when thi | s bit is "0".              | are valid a<br>When the | nd priority<br>e bit is "1",<br>trolled by t | the priority | / interrupt |          |

# Program status word register (PSW)

|              | 4000000 | MSB                   |                                                                                                                                               |                   |                                                       |                           |              |             | LSB                                    |  |

|--------------|---------|-----------------------|-----------------------------------------------------------------------------------------------------------------------------------------------|-------------------|-------------------------------------------------------|---------------------------|--------------|-------------|----------------------------------------|--|

| NAME         | ADDRESS | 7                     | 6                                                                                                                                             | 5                 | 4                                                     | 3                         | 2            | 1           | 0                                      |  |

| PSW          | 0D0H    | CY                    | AC                                                                                                                                            | F0                | RS1                                                   | RS0                       | OV           | F1          | Р                                      |  |

| BIT LOCATION | FLAG    |                       | FUNCTION                                                                                                                                      |                   |                                                       |                           |              |             |                                        |  |

| PSW.0        | Р       | This bit is           | Accumulator (ACC) parity indicator. This bit is "1" when the "1" bit number in the accumulator is an odd number, and "0" when an even number. |                   |                                                       |                           |              |             |                                        |  |

| PSW.1        | F1      | User flag             | which may                                                                                                                                     | y be set to       | "0" or "1" a                                          | s desired b               | y the user   | r.          |                                        |  |

| PSW.2        | OV      | result of a of execut | an arithme<br>ing multipl                                                                                                                     | tic operation ins |                                                       | g is also s<br>IUL AB) is | et to "1" if | the resulta | "1" as a<br>nt product<br>out is reset |  |

| PSW.3        | RS0     | RAM regi              | ster bank :                                                                                                                                   | switch            |                                                       |                           |              |             |                                        |  |

|              |         | RS1                   | RS0                                                                                                                                           | BANK              |                                                       | RA                        | M ADDRE      | SS          |                                        |  |

|              |         | 0                     | 0                                                                                                                                             | 0                 | 00H - 07H                                             | 1                         |              |             |                                        |  |

| PSW.4        | RS1     | 0                     | 1                                                                                                                                             | 1                 | 08H - 0FH                                             | 1                         |              |             |                                        |  |

|              |         | 1                     | 0                                                                                                                                             | 2                 | 10H - 17H                                             | 1                         |              |             |                                        |  |

|              |         | 1                     | 1                                                                                                                                             | 3                 | 18H - 1FI                                             | 1                         |              |             |                                        |  |

| PSW.5        | F0      | User flag             | which may                                                                                                                                     | y be set to       | "0" or "1" a                                          | s desired b               | y the user   | ſ.          |                                        |  |

| PSW.6        | AC      | This flag executing   | an arithm                                                                                                                                     |                   | C <sub>3</sub> is gene<br>tion instructes to "O".     |                           | bit 3 of th  | e ALU as a  | a result of                            |  |

| PSW.7        | CY      | executing             | is set to "1<br>an arithm                                                                                                                     | etic operat       | C <sub>7</sub> is gene<br>tion instruc<br>the flag is | tion.                     |              | ie ALU as i | result of                              |  |

# I/O control register (IOCON)

| NABAE        | ADDDECC | MSB                                                                                                                                                                                |               |                                         |            |              |             |                    | LSB    |

|--------------|---------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------|-----------------------------------------|------------|--------------|-------------|--------------------|--------|

| NAME         | ADDRESS | 7                                                                                                                                                                                  | 6             | 5                                       | 4          | 3            | 2           | 1                  | 0      |

| IOCON        | 0F8H    | _                                                                                                                                                                                  | T32           | SERR                                    | IZC        | P3HZ         | P2HZ        | P1HZ               | ALF    |

| BIT LOCATION | FLAG    |                                                                                                                                                                                    | •             |                                         | FUNC       | CTION        |             |                    |        |

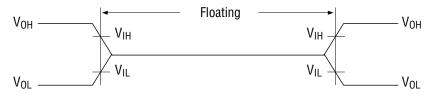

| IOCON.0      | ALF     | outputs f                                                                                                                                                                          | rom ports     | mode (PD<br>0, 1, 2, and<br>ports 0, 1, | d 3 are sw | itched to fl | oating stat | set to "1",<br>us. | the    |

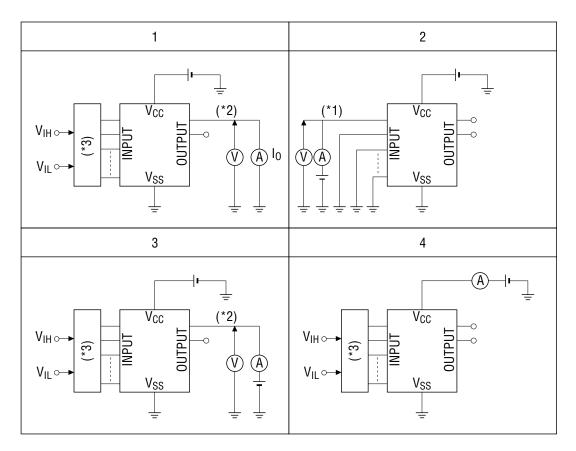

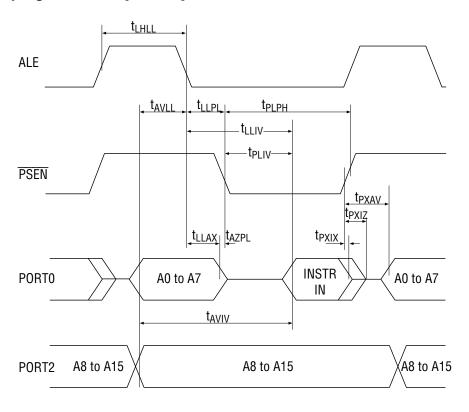

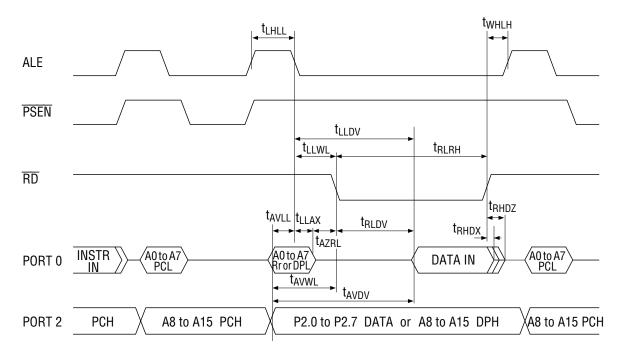

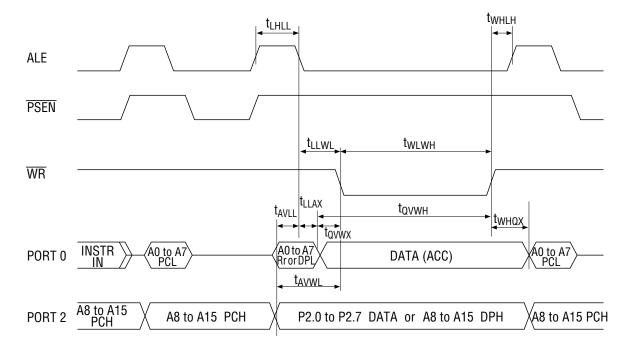

| IOCON.1      | P1HZ    | Port 1 be                                                                                                                                                                          | comes a h     | igh impeda                              | ınce input | port when    | this bit is | "1".               |        |