# YAMAHA L S I

# **YSS215**

# **AVSP**

## **Audio & Visual Surround Processor**

#### OUTLINE

YSS215 is digital sound field processor with Dolby Pro Logic decoder based on Digital Signal Processing technology.

The LSI has A/D & D/A Converter and uses digital signal processing for almost all functions needed in Pro Logic. This allows construction of highly reliable decoder with small quantity of components. It also has original sound field simulation circuit with 29 digital delay line (370 ms at max.), so you can design 2in-4out surround system easily.

#### FEATURES

- Highly accurate signal processing with internal operation word length of 32 bits.

- Adaptive matrix, noise generator, 7 kHz low pass filter, modified B-type N.R. decoder and A/D

& D/A converter are built-in.

- Auto Input Balance circuit is built-in. (ON/OFF)

- Capable of mixing 8 taps with delay time up to 370 ms at surround channel in Dolby Pro Logic mode.

- Capable of noise control.

- Original simulation surround using digital delay (maximum delay time: 370 ms, 29 taps (L+R, L−R), low pass filter (ON/OFF)).

- External 256k PSRAM interface for 16 bits linear digital delay.

- Serial interface with microprocessor for parameter control.

- Analog signal processing for the front three channels (L, R, C).

- Master clock frequency: 11.2896 MHz, sampling frequency: 44.1 kHz.

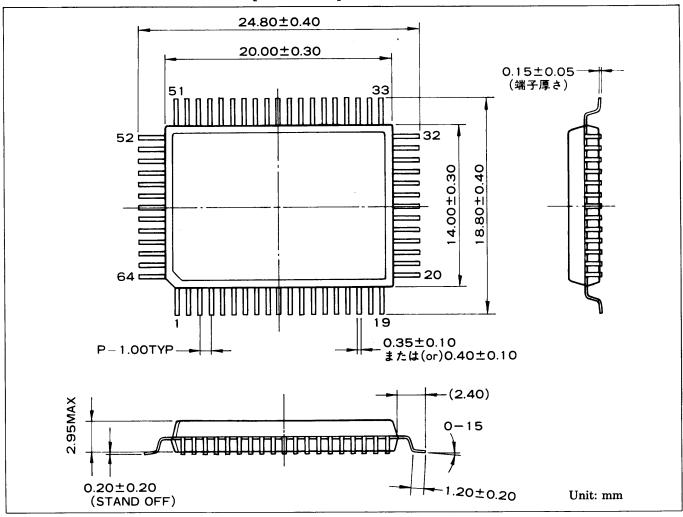

- 5V single power supply, silicon gate CMOS, 64 pin QFP package. (YSS215-F)

- Dolby reference operate level: 300 mVr.m.s.

#### (Note)

"Dolby Pro Logic" is a trademark of Dolby Laboratories Licensing Corporation. This LSI is available only to licensees of Dolby Laboratories Licensing Corp.

-YAMAHA CORPORATION

YSS215 CATALOG CATALOG No. : LSI-4SS2152

1995. 5

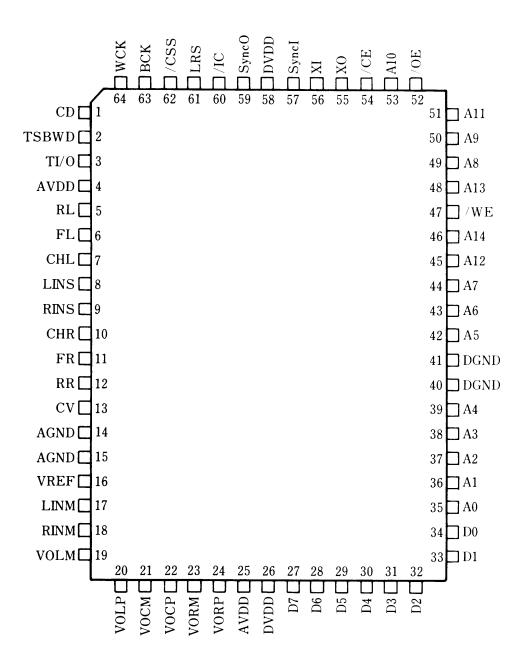

#### ■ PIN CONFIGURATION

64pin QFP TOP VIEW

#### ■ PIN DESCRIPTIONS

| Pin No. | I/O  | Pin name | Description                                               |

|---------|------|----------|-----------------------------------------------------------|

| 1       | Its  | CD       | Serial data for parameter data input                      |

| 2       | Ic   | TSBWD    | LSI test terminal, to be usually connected to DVDD        |

| 3       | Ic   | TI/O     | LSI test terminal, to be usually connected to DVDD        |

| 4       | A –  | AVDD     | +5V power supply (for D/A & A/D converter)                |

| 5       | AO   | RL       | RL channel, D/A output                                    |

| 6       | AO   | FL       | FL channel, D/A output                                    |

| 7       | A –  | CHL      | Sample/hold capacitor terminal for LINS input             |

| 8       | ΑI   | LINS     | L channel, A/D input                                      |

| 9       | ΑI   | RINS     | R channel, A/D input                                      |

| 10      | A –  | CHR      | Sample/hold capacitor terminal for RINS input             |

| 11      | AO   | FR       | FR channel, D/A output                                    |

| 12      | AO   | RR       | RR channel, D/A output                                    |

| 13      | AO   | CV       | Center voltage of A/D, multiplying DAC                    |

| 14      | A –  | AGND     | Ground (for D/A & A/D converter)                          |

| 15      | A –  | AGND     | Ground (for multiplying DAC)                              |

| 16      | AI   | VREF     | Reference voltage input of multiplying DAC                |

| 17      | AI   | LINM     | L channel, multiplying DAC input                          |

| 18      | AI   | RINM     | R channel, multiplying DAC input                          |

| 19      | AO   | VOLM     | Connected to L channel, operational amplifier, - terminal |

| 20      | AO   | VOLP     | Connected to L channel, operational amplifier, + terminal |

| 21      | AO   | VOCM     | Connected to C channel, operational amplifier, - terminal |

| 22      | AO   | VOCP     | Connected to C channel, operational amplifier, + terminal |

| 23      | AO   | VORM     | Connected to R channel, operational amplifier, - terminal |

| 24      | AO   | VORP     | Connected to R channel, operational amplifier, + terminal |

| 25      | A –  | AVDD     | +5V power supply (for multiplying DAC)                    |

| 26      | _    | DVDD     | +5V power supply (for digital circuit)                    |

| 27      | I/Ot | D7       | Data 7 for external delay RAM                             |

| 28      | I/Ot | D6       | Data 6 for external delay RAM                             |

| 29      | I/Ot | D5       | Data 5 for external delay RAM                             |

| 30      | I/Ot | D4       | Data 4 for external delay RAM                             |

| 31      | I/Ot | D3       | Data 3 for external delay RAM                             |

| 32      | I/Ot | D2       | Data 2 for external delay RAM                             |

| 33      | I/Ot | D1       | Data 1 for external delay RAM                             |

| 34      | I/Ot | D0       | Data 0 for external delay RAM                             |

| 35      | 0    | A0       | Address 0 for external delay RAM                          |

| 36      | 0    | A1       | Address 1 for external delay RAM                          |

| 37      | О    | A2       | Address 2 for external delay RAM                          |

| 38      | O    | A3       | Address 3 for external delay RAM                          |

| 39      | О    | A4       | Address 4 for external delay RAM                          |

| 40      | _    | DGND     | Ground (for digital circuit)                              |

| 41      |      | DGND     | Ground (for digital circuit)                              |

| 42      | О    | A5       | Address 5 for external delay RAM                          |

| Pin No. | I/O | Pin name | Description                                                                  |

|---------|-----|----------|------------------------------------------------------------------------------|

| 43      | 0   | A6       | Address 6 for external delay RAM                                             |

| 44      | 0   | A7       | Address 7 for external delay RAM                                             |

| 45      | О   | A12      | Address 12 for external delay RAM                                            |

| 46      | 0   | A14      | Address 14 for external delay RAM                                            |

| 47      | О   | /WE      | WE for external delay RAM, write enable terminal                             |

| 48      | 0   | A13      | Address 13 for external delay RAM                                            |

| 49      | О   | A8       | Address 8 for external delay RAM                                             |

| 50      | 0   | A9       | Address 9 for external delay RAM                                             |

| 51      | 0   | A11      | Address 11 for external delay RAM                                            |

| 52      | О   | /OE      | OE for external delay RAM, output enable terminal                            |

| 53      | 0   | A10      | Address 10 for external delay RAM                                            |

| 54      | О   | /CE      | CE for external delay RAM, chip enable terminal                              |

| 55      | О   | XO       | X'tal oscillator terminal                                                    |

| 56      | I   | XI       | X'tal oscillator terminal (11.2896 MHz)                                      |

| 57      | It  | SYNCI    | Test terminal, to be usually connected to DVDD                               |

| 58      | _   | DVDD     | +5V power supply (for digital circuit)                                       |

| 59      | О   | SYNCO    | Test terminal, usually without connection                                    |

| 60      | Ics | /IC      | Initial clear terminal (Power-on resetting is required.)                     |

| 61      | О   | LRS      | Terminal for external Auto Input Balance circuit, usually without connection |

| 62      | О   | /CSS     | Terminal for external Auto Input Balance circuit, usually without connection |

| 63      | Its | BCK      | Bit clock for parameter data input                                           |

| 64      | Its | WCK      | Word clock for parameter data input                                          |

Note) Meanings of the symbols at the column I/O:

I: Input terminal O

O: Output terminal

A: Analog terminal

t: TTL level

c: CMOS level

s: Schmidt input

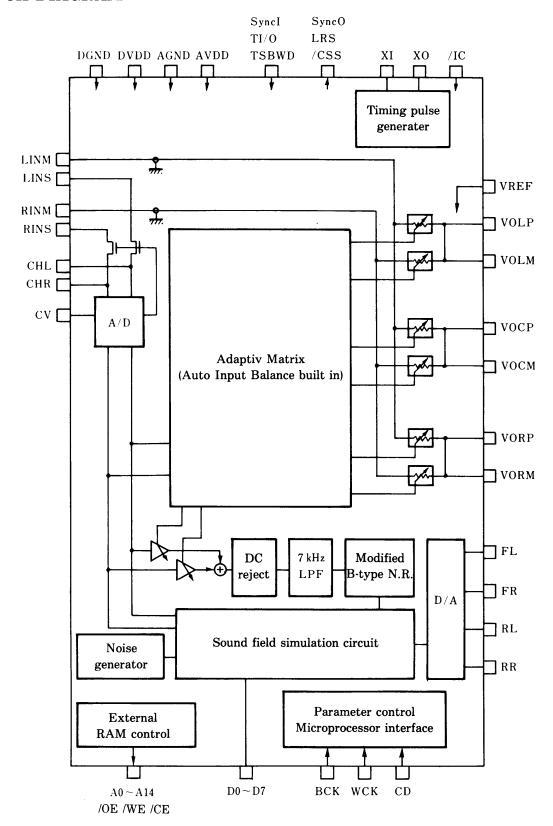

#### ■ BLOCK DIAGRAM

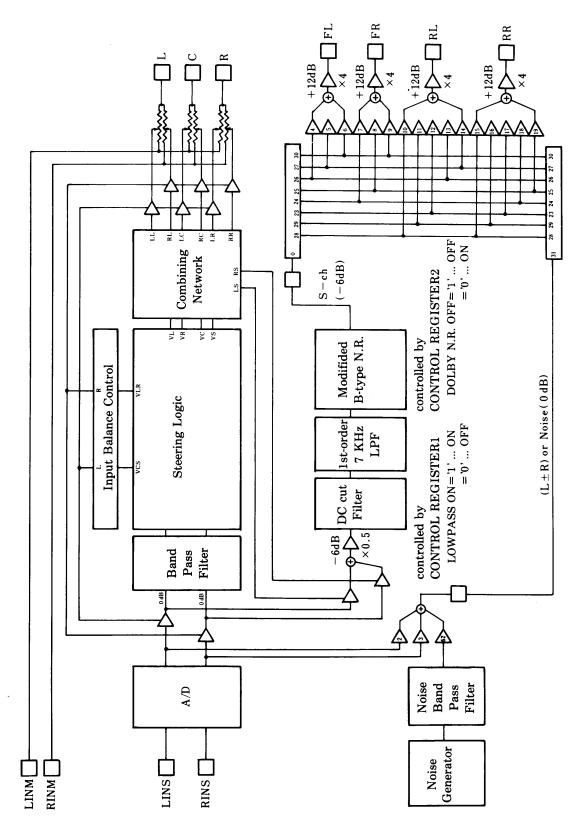

## ■ Dolby Pro Logic BLOCK DIAGRAM

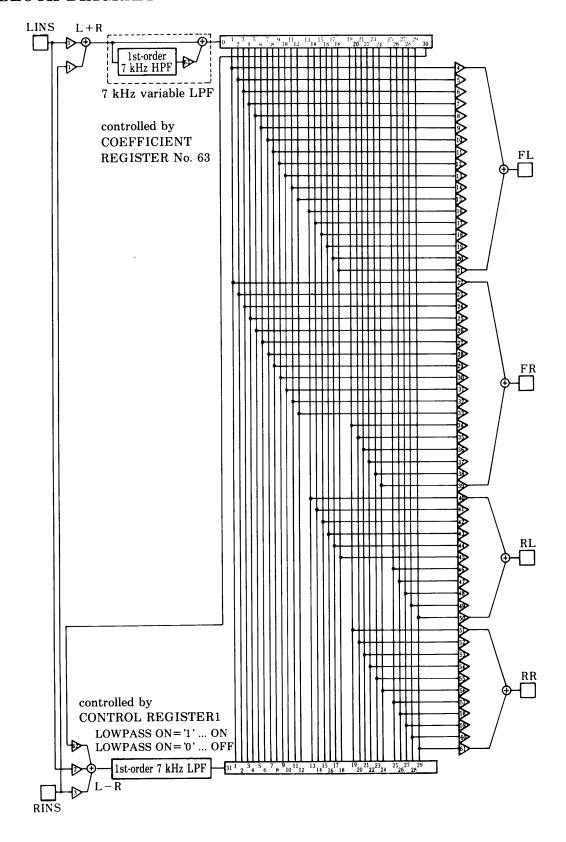

#### ■ DSP BLOCK DIAGRAM

#### ■ EXTERNAL DATA RAM INTERFACE

External RAM interface reads and writes a 256 Kbit Pseudo Static RAM. The LSI accesses eight-bit data from D0 to D7 twice to obtain 16 bit data.

Please use a PSRAM with access-time of 100nsec.

#### ■ MICROPROCESSOR INTERFACE

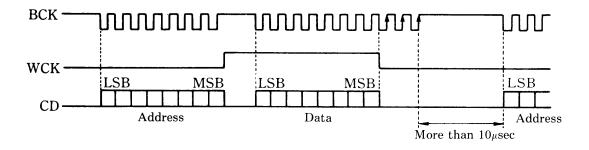

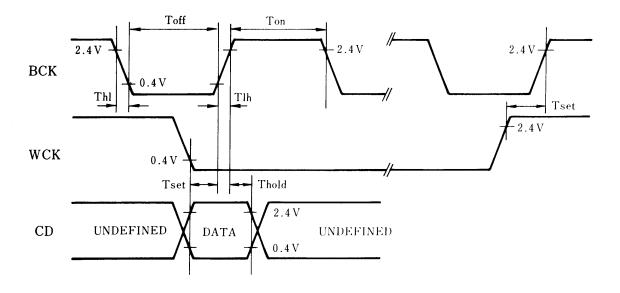

MICROPROCESSOR INTERFACE writes parameters to Control Registers using BCK, WCK and CD. The timing is shown below.

#### (1) TIMING CHART

Note 1) More than three BCK rises are required after the MSB of data is input and WCK falls. For writing to Coefficient Register (address: \$81 to \$BF) and Address Register (address: \$C0 to \$FF), at least 10µs is required between the third BCK rise and the next CD input.

Note 2) CD data without a WCK rise or fall, and data of addresses \$04, \$08 to \$0F, \$10 to \$3F, \$80 and \$C0 are ineffective.

#### (2) CONTROL REGISTER MAP

| ADDR | NANCO          |       |          |           | BIT ASSI    | GNMENT      | 1           | <del>,</del> |         |

|------|----------------|-------|----------|-----------|-------------|-------------|-------------|--------------|---------|

| HEX  | NAME           | LSB   | 1        | 2         | 3           | 4           | 5           | 6            | MSB     |

| 00   | MASTER CONTROL | IC    | CL       |           |             |             |             |              |         |

|      | REGISTER       |       | MUTE     | ×         | ×           | ×           | ×           | ×            | ×       |

| 01   | CONTROL        | DOLBY | CENTER   | STEERING  | SURROUND    | PHANTOM     | MMIX        | LOWPASS      | AUTO    |

|      | REGISTER 1     | ON    | OFF      | OFF       | STEERING    | ON          | ON          | ON           | BALANCE |

|      |                |       |          |           | OFF         |             |             |              | ON      |

| 02   | CONTROL        |       | EXTERNAL |           |             |             |             |              |         |

|      | REGISTER 2     | ON    | RAM      | N.R.      | ×           | ×           | ×           | ×            | ×       |

| -    |                |       | OFF      | OFF       |             |             |             |              |         |

| 03   | STEERING       |       |          |           |             |             |             |              |         |

|      | GAIN           |       |          |           |             |             |             |              |         |

| 05   | TESTT          |       |          | (Do not v | write, rese | t with Init | tial clear) |              |         |

| 06   | TEST1          |       |          |           |             |             |             |              |         |

| 07   | TEST2          |       |          |           |             |             |             |              |         |

| 40   | MAIN CHANNEL   |       |          |           |             |             |             |              |         |

| :    | MANUAL         |       |          |           |             |             |             |              |         |

| 7F   | MIX CONTROL    |       |          |           |             |             |             |              |         |

| 81   | COEFFICIENT    |       |          |           |             |             |             |              |         |

|      | REGISTER       |       |          |           |             |             |             |              |         |

| BF   | 100101010      |       |          |           |             |             |             |              |         |

| C1   | DELAY TIME     |       |          |           |             |             |             |              |         |

| FF   | REGISTER       |       |          |           |             |             |             |              |         |

- ×; Don't Care

- Don't write to the other Address

#### (3) DATA DESCRIPTION

#### • MASTER CONTROL REGISTER

| IC   | '1'=Initial clear (initializes internal circuit)                            |

|------|-----------------------------------------------------------------------------|

| CL   | '1'=Initial data clear                                                      |

| MUTE | (Sound data in external RAM and internal filter RAM can be cleared to '0'.) |

Note 1) Internal IC and external /IC have same functions, but MASTER CONTROL REGISTER is reset to '0' with external /IC.

Note 2) CL MUTE resets all processing sound data to '0'. Note that it needs 370 ms to clear all data in external PSRAM.

#### • CONTROL REGISTER 1

| DOLBY    | '1'=Dolby Pro Logic mode                                             |                      |

|----------|----------------------------------------------------------------------|----------------------|

| ON       | '0'=Simulation surround mode                                         | (set to '1' with IC) |

| CENTER   | '1'=Center channel off                                               |                      |

| OFF      | '0'=Center channel on                                                | (set to '0' with IC) |

| STEERING | '1'=Steering off for all channels                                    |                      |

| OFF      | '0'=Steering on for all channels                                     |                      |

|          | It must be set to '1' for Simulation surround mode or '0' for Dolb   | y Pro Logic mode.    |

|          |                                                                      | (set to '0' with IC) |

| SURROUND | '1'=Steering off for surround channel                                |                      |

| STEERING | '0'=Steering on for surround channel                                 |                      |

| OFF      | When this bit is set to '1', steering is not passed to surround char | inel.                |

| -        | This bit must be set to '1' for 3 channel logic.                     | (set to '0' with IC) |

| PHANTOM  | '1'=Phantom on, '0'=Phantom off                                      |                      |

| ON       | PHANTOM ON='1' must be used with CENTER OFF='1'.                     | (set to '0' with IC) |

| MMIX     | '1'=Data of multiplying DACs are set with the microprocessor.        |                      |

| ON       | '0'=Data of multiplying DACs are controlled by Steering circuit.     |                      |

|          | It must be set to '0' for Dolby Pro Logic mode.                      | (set to '0' with IC) |

| LOWPASS  | '1'=7kHz low pass filter on, '0'=7kHz low pass filter off            |                      |

| ON       | In simulation surround mode, data of L, R and tap NO. 30 are inp     | out to this LPF.     |

|          | (see DSP BLOCK DIAGRAM)                                              | (set to '0' with IC) |

| AUTO     | '1'=Auto Input Balance on                                            |                      |

| BALANCE  | '0'=Auto Input Balance off                                           |                      |

| ON       |                                                                      | (set to '0' with IC) |

Note 1) When DOLBY ON='1', the multiplying DAC's values of front 3 channels can be set with MMIX ON='1'. But the steering of surround channel is still controlled by Steering circuit.

Note 2) LOWPASS ON ('0' or '1') is effective when DOLBY ON='1' as well as when DOLBY ON='0'.

#### • CONTROL REGISTER 2

| NOISE    | '0'=Noise generator off          |                      |

|----------|----------------------------------|----------------------|

| ON       | '1'=Noise generator on           | (set to '0' with IC) |

| EXTERNAL | '0'=External PSRAM interface on  |                      |

| RAM OFF  | '1'=External PSRAM interface off | (set to '0' with IC) |

| DOLBY    | '0'=Dolby Noise Reduction on     |                      |

| N.R. OFF | '1'=Dolby Noise Reduction off    | (set to '0' with IC) |

Note 1) NOISE ON is a reset signal of M-sequence noise generator.

Noise output is '0' when it is set to '0'.

Note 2) When EXTERNAL RAM OFF='1', external PSRAM can be removed.

This bit should be set to '0' in normal use.

Note 3) When DOLBY N.R. OFF='1', sliding band filter in N.R. circuit can be stopped.

And then • TSBWD=1  $\rightarrow$  Noise Reduction off

• TSBWD=0 → Noise Reduction max.

Please connect TSBWD (pin No.2) to DVDD in normal use.

#### • MAIN CHANNEL MANUAL MIX CONTROL

It sets the mixing gains of main channels. D0 to D10 are the data for multiplying DACs.

|     | Address Data |    |            |    |   |   | Channel |     |    |    |    |    |    |    |     |                     |

|-----|--------------|----|------------|----|---|---|---------|-----|----|----|----|----|----|----|-----|---------------------|

| MSB | 6            | 5  | 4          | 3  | 2 | 1 | LSB     | MSB | 6  | 5  | 4  | 3  | 2  | 1  | LSB | Channei             |

| 0   | 1            | D2 | D1         | D0 | 0 | 0 | 0       | D10 | D9 | D8 | D7 | D6 | D5 | D4 | D3  | L input - L output  |

| 0   | 1            | D2 | D1         | D0 | 0 | 0 | 1       | D10 | D9 | D8 | D7 | D6 | D5 | D4 | D3  | R input -> L output |

| 0   | 1            | D2 | D1         | D0 | 0 | 1 | 0       | D10 | D9 | D8 | D7 | D6 | D5 | D4 | D3  | L input → R output  |

| 0   | 1            | D2 | D1         | D0 | 0 | 1 | 1       | D10 | D9 | D8 | D7 | D6 | D5 | D4 | D3  | R input → R output  |

| 0   | 1            | D2 | <b>D</b> 1 | D0 | 1 | 0 | 0       | D10 | D9 | D8 | D7 | D6 | D5 | D4 | D3  | L input → C output  |

| 0   | 1            | D2 | D1         | D0 | 1 | 0 | 1       | D10 | D9 | D8 | D7 | D6 | D5 | D4 | D3  | R input - C output  |

- Note 1) Data are 11 bits in sign-magnitude form. D10 represents sign and D9 to D0 represent magnitude (0 to 1023).

- Note 2) These registers are effective when MMIX ON='1'.

- Note 3) Two multiplying DACs connected to one output (for example, L input  $\rightarrow L$  output and R input  $\rightarrow L$  output) cannot have negative values at a time.

#### • COEFFICIENT REGISTER

|     | Address |   |   |          |   |   | Coefficient NO | Data            |     |                                        |   |   |   |   |   |     |

|-----|---------|---|---|----------|---|---|----------------|-----------------|-----|----------------------------------------|---|---|---|---|---|-----|

| MSB | 6       | 5 | 4 | 3        | 2 | 1 | LSB            | Coefficient NO. | MSB | 6                                      | 5 | 4 | 3 | 2 | 1 | LSB |

| 1   | 0       | 0 | 0 | 0        | 0 | 0 | 1              | 1               |     |                                        | • |   |   |   |   | •   |

|     |         |   |   | <b>}</b> |   |   |                | l               |     | Max. 127 to Min128 2's complement form |   |   |   |   |   |     |

| 1   | 0       | 1 | 1 | 1        | 1 | 1 | 1              | 63              |     |                                        |   |   |   |   |   |     |

- Note 1) Data are 8 bits in 2's complement form.

- Note 2) Coefficient numbers correspond to those in DOLBY PRO LOGIC BLOCK DIAGRAM and DSP BLOCK DIAGRAM.

#### • DELAY TIME REGISTER

|     | Address |   |   |   |   |   |     | m NO    |     | Data (Delay-time data) |      |             |               |     |   |     |  |

|-----|---------|---|---|---|---|---|-----|---------|-----|------------------------|------|-------------|---------------|-----|---|-----|--|

| MSB | 6       | 5 | 4 | 3 | 2 | 1 | LSB | Tap NO. | MSB | 6                      | 5    | 4           | 3             | 2   | 1 | LSB |  |

| 1   | 1       | × | 0 | 0 | 0 | 0 | 1   | 1       |     |                        |      |             |               |     |   |     |  |

|     |         |   | ł |   |   |   |     | l       |     |                        | 1.45 | 1 ~<br>125m | 255<br>sec/D. | АТА |   |     |  |

| 1   | 1       | × | 1 | 1 | 1 | 1 | 1   | 31      |     |                        |      |             |               |     |   |     |  |

Note 1) Tap numbers correspond to those in DOLBY PRO LOGIC BLOCK DIAGRAM and DSP BLOCK DIAGRAM.

Delay-time data of tap NO. 31 correspond to address in PSRAM to which sound data are written. (Tap NO. 31 is a output tap to PSRAM.) PSRAM can be divided into two blocks according to delay-time data of tap NO. 31. If delay-time data of a tap are bigger than those of tap NO. 31, the tap reads sound data of tap NO. 31 and sound data are delayed as much as the difference between delay-time data of these taps. If delay-time data of a tap are smaller than those of tap NO. 31, the tap reads sound data of tap NO. 0 and they are delayed as much as the delay-time data of the tap.

Maximum delay is 370 ms with increment of 1.45125 ms.

- Note 2) Delay-time data '0' and the same delay-time data as tap NO. 31 should not be used for tap NO. 1 ~ NO. 30. When delay isn't required, let analog signals go through by using MANUAL MIX CONTROL.

- Note 3) To be precise, delay of two samplings (about 44  $\mu$ s) will be added to the delay of FL, FR, RL and RR because of A/D & D/A conversion. And difference by 1 sampling (about  $22\mu$ s) may be caused due to timing adjustment for reading/writing to external RAM.

- Note 4) When DOLBY ON='1', data of only tap NO. 23 to 30 are effective. In order to output surround signals, delay-time data of 15 to 30 ms should be written to at least one of these taps.

#### ■ ELECTRICAL CHARACTERISTICS

#### • ABSOLUTE MAXIMUM PATINGS

| Parameter             | Symbol | Min. | Max.    | Unit                 |

|-----------------------|--------|------|---------|----------------------|

| Power supply voltage  | Vdd    | -0.3 | +7.0    | V                    |

| Input voltage         | VI     | -0.3 | VDD+0.5 | V                    |

| Input current         | Iı     |      | 10      | mA                   |

| Operating temperature | Тор    | - 20 | +75     | $^{\circ}\mathrm{C}$ |

| Storage temperature   | Tstg   | - 50 | +125    | °C                   |

#### • RECOMMENDED OPERATING CONDITIONS

| Parameter             | Symbol | Min. | Тур. | Max. | Unit                 |

|-----------------------|--------|------|------|------|----------------------|

| Power supply voltage  | Vdd    | 4.75 | 5.0  | 5.25 | V                    |

| Operating temperature | Top    | 0    | 25   | 70   | $^{\circ}\mathrm{C}$ |

## • DC CHARACTERISTICS (CONDITIONS: Ta=25 °C, $VDD=5.0\pm0.25V$ )

| Parameter              | Symbol | Condition         | Min. | Typ. | Max. | Unit         |

|------------------------|--------|-------------------|------|------|------|--------------|

| Power consumption      | W      | VDD=5.0V          |      | 250  | 400  | mW           |

| Input voltage H level  | VIH    |                   |      |      |      | v            |

| TTL level              |        |                   | 2.7  |      | VDD  |              |

| CMOS level             |        |                   | 3.5  |      | VDD  |              |

| Input voltage L level  | VIL    |                   |      |      |      | v            |

| TTL level              |        |                   | 0    |      | 0.4  |              |

| COMS level             |        |                   | 0    |      | 1.0  |              |

| Input leakage current  | IIL    |                   |      |      | 10   | $\mu A$      |

| Output voltage H level | Vон    | $IOH = 200 \mu A$ | 3.0  |      | VDD  | $\mathbf{v}$ |

| Output voltage L level | Vol    | Iol = -2mA        | 0    |      | 0.4  | v            |

#### • AC CHARACTERISTICS

| Parameter          | Symbol | Min. | Тур.    | Max. | Unit |

|--------------------|--------|------|---------|------|------|

| BCK max. frequency | Хвск   |      |         | 2.0  | MHz  |

| BCK rise time      | Thl    |      |         | 50   | nsec |

| BCK fall time      | Thl    |      |         | 50   | nsec |

| BCK on time        | Ton    | 200  |         |      | nsec |

| BCK off time       | Toff   | 200  |         |      | nsec |

| Data set-up time   | Tset   | 50   |         |      | nsec |

| Data hold time     | Thold  | 20   |         |      | nsec |

| XI frequency       | XIN    | 11.0 | 11.2896 | 12.0 | MHz  |

| XI clock duty      |        | 40   | 50      | 60   | %    |

#### • ANALOG CHARACTERISTICS (CONDITIONS: VDD=+5V, Ta=25°C, XIN=11.2896MHz)

| Parameter                              | Symbol | Condition         | Min. | Typ. | Max.  | Unit     |

|----------------------------------------|--------|-------------------|------|------|-------|----------|

| Multiplying DAC impedance              | RM     |                   | 8.0  | 9.6  | 11.5  | ΚΩ       |

| Output distortion                      |        | Output            |      |      |       |          |

| Main channel                           | Dmmax  | 300mVr.m.s.       |      | 0.03 | 0.1   | %        |

| Surround channel                       | Dsmax  |                   |      | 0.25 | 0.7   |          |

| Output S/N                             |        |                   |      |      |       |          |

| Main channel                           | S/N m  |                   | 85   |      |       |          |

| Surround channel                       |        | CCIR-ARM          |      |      |       |          |

| Dolby Pro Logic mode                   | S/Nsd  | (0dB=300mVr.m.s.) | 70   | 77   |       | dB       |

| Simulation Surround                    | S/Nss  |                   | 65   | 70   |       |          |

| mode *1                                |        |                   |      |      |       |          |

| Frequency response                     |        |                   |      |      |       |          |

| Main channel                           | Frm    | 50~20kHz          |      |      | ±0.2  | dB       |

| Surround channel                       | Frs    | 50~ 6kHz          |      |      | ±0.5  |          |

| Modified B-type N.R. decoding accuracy | N.R.a  | 0dB=300mVr.m.s.   |      |      | ± 1.0 | dB       |

| Noise generator output level           | Nout   | after Noise BPF   |      | 85   |       | mVr.m.s. |

| Dolby Pro Logic<br>steering separation | STsep  |                   |      | 30   |       | dB       |

| Max. input level                       | Smax   | 0dB=300mVr.m.s.   | 15   |      |       | dB       |

Note 1) Main Channel indicates L, R, and C channel.

Surround Channel indicates FL, FR, RL, and RR channel.

Note 2) \*1 Unity Gain.

#### ■ EXTERNAL DIMENSIONS [YSS215-F]

Note: The LSIs for surface mount need especial consideration on storage and soldering conditions. For detailed information, please contact your nearest agent of yamaha.

The specifications of this product are subject to improvement changes without prior notice.

#### IMPORTANT NOTICE

- 1. Yamaha reserves the right to make changes to its Products and to this document without notice. The information contained in this document has been carefully checked and is believed to be reliable. However, Yamaha assumes no responsibilities for inaccuracies and makes no commitment to update or to keep current the information contained in this document.

- 2. These Yamaha Products are designed only for commercial and normal industrial applications, and are not suitable for other uses, such as medical life support equipment, nuclear facilities, critical care equipment or any other application the failure of which could lead to death, personal injury or environmental or property damage. Use of the Products in any such application is at the customer's sole risk and expense.

- 3. YAMAHA ASSUMES NO LIABILITY FOR INCIDENTAL, CONSEQUENTIAL OR SPECIAL DAMAGES OR INJURY THAT MAY RESULT FROM MISAPPLICATION OR IMPROPER USE OR OPERATION OF THE PRODUCTS.

- 4. YAMAHA MAKES NO WARRANTY OR REPRESENTATION THAT THE PRODUCTS ARE SUBJECT TO INTELLECTUAL PROPERTY LICENSE FROM YAMAHA OR ANYTHIRD PARTY, AND YAMAHA MAKES NO WARRANTY OR REPRESENTATION OF NON-INFRINGEMENT WITH RESPECT TO THE PRODUCTS. YAMAHA SPECIFICALLY EXCLUDES ANY LIABILITY TO THE CUSTOMER OR ANY THIRD PARTY ARISING FROM OR RELATED TO THE PRODUCTS' INFRINGEMENT OF ANY THIRD PARTY'S INTELLECTUAL PROPERTY RIGHTS, INCLUDING THE PATENT. COPYRIGHT, TRADEMARK OR TRADE SECRET RIGHTS OF ANY THIRD PARTY.

- 5. EXAMPLES OF USE DESCRIBED HEREIN ARE MERELY TO INDICATE THE CHARACTERISTICS AND PERFORMANCE OF YAMAHA PRODUCTS. YAMAHA ASSUMES NO RESPONSIBILITY FOR ANY INTELLECTUAL PROPERTY CLAIMS OR OTHER PROBLEMS THAT MAY RESULT FROM APPLICATIONS BASED ON THE EXAMPLES DESCRIBED HEREIN. YAMAHA MAKES NO WARRANTY WITH RESPECT TO THE PRODUCTS, EXPRESS OR IMPLIED, INCLUDING, BUT NOT LIMITED TO THE WARRANTIES OF MERCHANTABILITY, FITNESS FOR A PARTICULAR USE AND TITLE.

# - AGENCY -

#### YAMAHA CORPORATION

Address inquiries to:

Semiconductor Sales & Marketing Department

■ Head Office 203, Matsunokijima, Toyooka-mura, Iwata-gun, Shizuoka-ken, 438-0192

Tel. +81-539-62-4918 Fax. +81-539-62-5054

2-17-11, Takanawa, Minato-ku, ■ Tokyo Office

Tokyo, 108-8568

Tel. +81-3-5488-5431 Fax. +81-3-5488-5088

■ Osaka Office Namba Tsujimoto Nissei Bldg. 4F

1-13-17, Namba Naka, Naniwa-ku, Osaka City, Osaka, 556-0011

Tel. +81-6-6633-3690 Fax. +81-6-6633-3691

■ U.S.A. Office YAMAHA Systems Technology

100 Century Center Court, San Jose, CA 95112

Tel. +1-408-467-2300 Fax. +1-408-437-8791