# **MSM5832RS**

#### REAL TIME CLOCK/CALENDAR

### GENERAL DESCRIPTION

The MSM5832RS is a metal-gate CMOS Real Time Clock/Calendar for use in bus-oriented microprocessor applications. The on-chip 32.768Hz crystal controlled oscillator time base is divided to provide addressable 4-bit I/O data of SECONDS, MINUTES, HOURS, DAY-OF-WEEK, DATE, MONTH, and YEAR. Data access is controlled by 4-bit address, chip select, read, write and hold inputs. Other functions include 12H/24H format selection, leap year identification and manual  $\pm 30$  second correction.

The MSM5832RS normally operates from a 5V ±5% supply. Battery backup operation down to 2.2V allows continuation of time keeping when main power is off. The MSM5832RS is offered in an 18-lead dual-in-line plastic (RS suffix) package.

#### **FEATURES**

- \*7 Function SECOND, MINUTE, HOUR, DAY, DAY-OF-WEEK, MONTH, YEAR

- Automatic leap year calendar

- 12 or 24 hour format

- \* ±30 second error correction

- 4-BIT DATA BUS

- 4-BIT ADDRESS

- \* READ, WRITE, HOLD, and CHIP SELECT inputs

- Reference signal outputs 1024, 1, 1/60, 1/3600Hz

- \* 32.768kHz crystal controlled operation

- Single 5V power supply

- Back-up battery operation to  $V_{DD}$  = 2.2V

- · Low power dissipation

90 μW Max. at V<sub>DD</sub> = 3V

2.5 mW Max. at  $V_{DD} = 5V$

· 18 pin plastic DIP (DIP18-P-300)

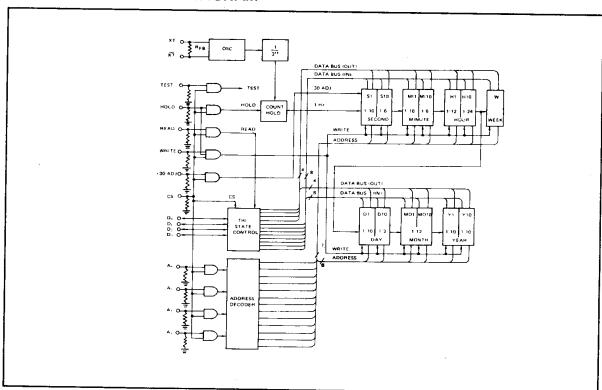

### FUNCTIONAL BLOCK DIAGRAM

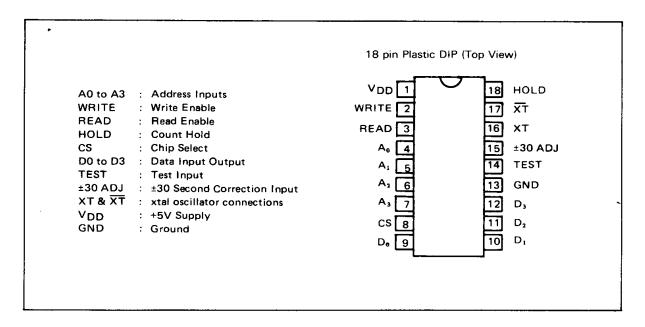

#### PIN CONFIGURATION

#### REGISTER TABLE

|                | Address<br>Input |                |                | Register | Data           | a Inp | ut/O           | utput | Data  | Remarks                                                                                          |  |

|----------------|------------------|----------------|----------------|----------|----------------|-------|----------------|-------|-------|--------------------------------------------------------------------------------------------------|--|

| A <sub>0</sub> | Aı               | A <sub>2</sub> | A <sub>3</sub> | Name     | D <sub>0</sub> | $D_1$ | D <sub>2</sub> | D₃    | Limit | Helilajks                                                                                        |  |

| 0              | 0                | 0              | 0              | S1       | *              | *     | *              | *     | 0 ~ 9 | S1 or S10 are reset to zero irrespective of input data D0-D3 when write                          |  |

| 1              | 0                | 0              | 0              | S10      | *              | *     | *              |       | 0 ~ 5 | instruction is executed with address selection.                                                  |  |

| 0              | 1                | 0              | o              | MI1      | *              | *     | *              | *     | 0 ~ 9 |                                                                                                  |  |

| 1              | 1                | 0              | 0              | MI10     | *              | *     | *              |       | 0 ~ 5 |                                                                                                  |  |

| 0              | 0                | 1              | 0              | H1       | *              | *     | *              | *     | 0~9   |                                                                                                  |  |

| 1              | О                | 1              | 0              | H10      | *              | *     | †              | †     | 0~1   | D2 = "1" for PM D3 = "1" for<br>24 hour format<br>D2 = "0" for AM D3 = "0" for<br>12 hour format |  |

| 0              | 1                | 1              | 0              | W        | *              | *     | *              |       | 0 ~ 6 |                                                                                                  |  |

| 1              | 1                | 1              | 0              | D1       | *              | *     | *              | *     | 0~9   |                                                                                                  |  |

| 0              | 0                | 0              | 1              | D10      | *              | *     | t              |       | 0 ~ 3 | D2 = "1" for 29 days in month 2<br>D2 = "0" for 28 days in month 2 (2)                           |  |

| 1              | 0                | 0              | 1              | MO1      | *              | *     | *              | *     | 0~9   |                                                                                                  |  |

| 0              | 1                | 0              | 1              | MO10     | *              |       |                |       | 0 ~ 1 |                                                                                                  |  |

| 1              | 1                | 0              | 1              | Y1       | *              | *     | *              | *     | 0~9   |                                                                                                  |  |

| 0              | 0                | 1              | 1              | Y10      | *              | *     | *              | *     | 0~9   |                                                                                                  |  |

(1) \*data valid as "0" or "1".

Blank does not exist (unrecognized during a write and held at "0" during a read) †data bits used for AM/PM, 12/24 HOUR and leap year.

(2) If D2 previously set to "1", upon completion of month 2 day 29, D2 will be internally reset to "0".

Table 1

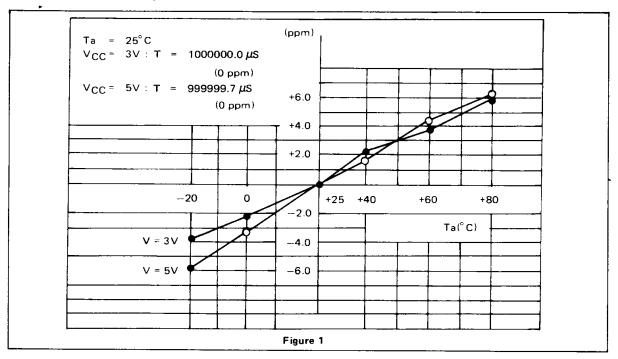

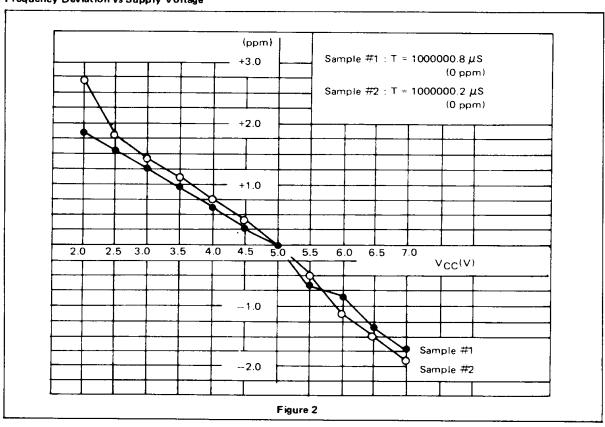

#### OSCILLATOR FREQUENCY DEVIATIONS

#### Frequency Deviation vs Temperature

#### Frequency Deviation vs Supply Voltage

#### **ABSOLUTE MAXIMUM RATINGS**

| Rating              | Symbol | Value                        | Unit |

|---------------------|--------|------------------------------|------|

| Supply voltage      | VDD    | <b>−0.3 ~ 7.0</b>            | V    |

| Input voltage       | VI     | -0.3 ~ V <sub>DD</sub> + 0.3 | V    |

| Data I/O voltage    | ٧٥     | -0.3 ∼ V <sub>DD</sub> + 0.3 | V    |

| Storage Temperature | Tstg   | -55 ~ 150                    | °c   |

#### **OPERATING CONDITIONS**

| Parameter                | Symbol          | Min. | Тур.   | Max. | Unit | Conditions                |

|--------------------------|-----------------|------|--------|------|------|---------------------------|

| Supply Voltage           | V <sub>DD</sub> | 4.5  | 5      | 7    | V    |                           |

| Standby Supply Voltage   | VDH             | 2.2  | _      | 7    | V    |                           |

|                          | VIH             | 3.6  | _      | VDD  | V    | V <sub>DD</sub> = 5V ± 5% |

| Input Signal Level       | VIL             | -0.3 | _      | 8.0  | ٧    | Respect to GND            |

| Crystal Oscillator Freq. | f(XT)           | _    | 32.768 | -    | kHz  |                           |

| Operating Temperature    | TOP             | -30  | -      | +85  | °C   |                           |

### DC CHARACTERISTICS

$(V_{CC} = 5V \pm 5\%; T_A = -30 \text{ to } +85^{\circ}C)$

| Parameter                   | Symbol | Min, | Тур. | Max. | Unit | Conditions                                       |

|-----------------------------|--------|------|------|------|------|--------------------------------------------------|

| (.)                         | lін    | 10   | 25   | 50   | μΑ   | V <sub>IN</sub> =5V, V <sub>DD</sub> =5V         |

| Input Current (1)           | †IL    | _    | _    | -1   | μΑ   | V <sub>IN</sub> = 0V                             |

| Data I/O Leakage<br>Current | ILD    | -10  | _    | 10   | μΑ   | V <sub>I/O</sub> = 0 to V <sub>DD</sub>          |

| Output Low Voltage          | VoL    | _    |      | 0.4  | V    | I <sub>O</sub> = 1.6 mA, CS = "1",<br>READ = "1" |

| Output Low Current          | lOL    | 1.6  | _    | _    | mA   | V <sub>O</sub> = 0.4V, CS = "1",<br>READ = "1"   |

|                             | IDDS   | _    | 15   | 30   | μΑ   | V <sub>CC</sub> = 3V, Ta = 25°C                  |

| Operating Supply Current    | ۵۵۱    | _    | 100  | 500  | μΑ   | V <sub>CC</sub> = 5V, Ta = 25°C                  |

(1) XT,  $\overline{XT}$  and  $D_0 \sim D_3$  excluded.

#### **SWITCHING CHARACTERISTICS**

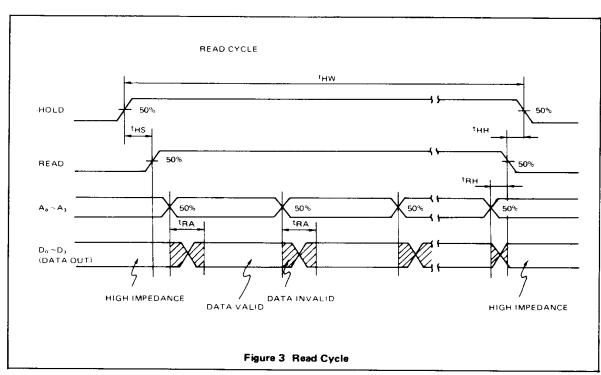

#### (1) READ mode

| (V <sub>DD</sub> | = | 5V | ±5%, | Ta | = | 25° | C) |

|------------------|---|----|------|----|---|-----|----|

|------------------|---|----|------|----|---|-----|----|

| Parameter             | Symbol          | Condition                                                        | MIN | TYP | MAX | Unit |

|-----------------------|-----------------|------------------------------------------------------------------|-----|-----|-----|------|

| HOLD Set-up Time      | tHS             |                                                                  | 150 | _   | _   | μs   |

| HOLD Hold Time        | thh             |                                                                  | 0   |     | _   | μs   |

| HOLD Pulse Width      | thw             |                                                                  | _   | _   | 990 | ms   |

| HOLD "L" Hold Time    | tHL             |                                                                  | 130 | _   |     | μs   |

| READ Hold Time        | tRH             |                                                                  | 0   | -   | _   | μs   |

| READ Set-up Time      | tRS             |                                                                  | 0   | _   | _   | μs   |

| READ Access Time      | <sup>t</sup> RA | R <sub>PULL</sub> . <sub>UP</sub> = 5KΩ<br>C <sub>L</sub> = 15pF | _   |     | 6   | μς   |

| ADDRESS Set-up Time   | †AS             |                                                                  | 3   |     | _   | μs   |

| ADDRESS Hold Time     | tAH             |                                                                  | 0.2 | _   | -   | μς   |

| READ Pulse Width      | †RW             | R <sub>PULL-UP</sub> = 5KΩ<br>C <sub>L</sub> = 15pF              | 2   | _   | _   | μs   |

| DARA Access Time      | †AC             | R <sub>PULL-UP</sub> = 5KΩ<br>C <sub>L</sub> = 15pF              | -   | -   | 0.6 | μς   |

| OUTPUT Disable Time   | toff            | RPULL-UP = $5K\Omega$<br>C <sub>L</sub> = $15 pF$                | _   | -   | 0.6 | μs   |

| CS Enable Delay Time  | tCS1            |                                                                  | _   | _   | 0.6 | μs   |

| CS Disable Delay Time | tCS2            |                                                                  | _   |     | 0.6 | μs   |

Notes: 1. A Read occurs during the overlap of a high CS and a high READ.

2. CS may be a permanent "1", or may be coincident with HOLD pulse.

#### **SWITCHING CHARACTERISTICS**

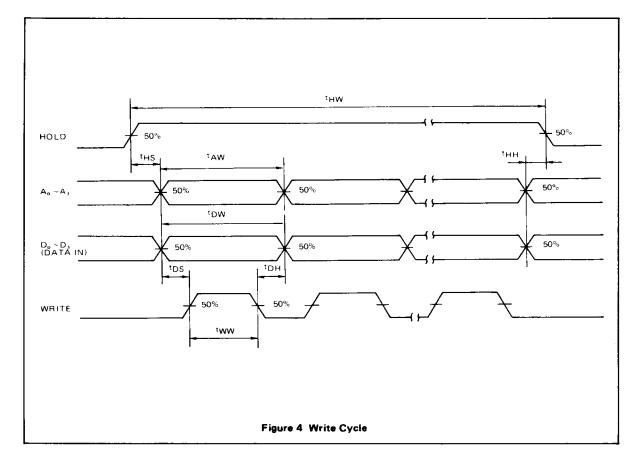

### (2) WRITE mode

$(V_{DD} = 5V \pm 5\%, Ta = 25^{\circ}C)$

| Parameter             | Symbol          | Condition | MIN | TYP | MAX | Unit |

|-----------------------|-----------------|-----------|-----|-----|-----|------|

| HOLD Set-up Time      | tHS             |           | 150 | _   | -   | μs   |

| HOLD Bold Time        | tнн             |           | 0   |     |     | μs   |

| HOLD Pulse Width      | thw             |           |     |     | 990 | ms   |

| HOLD "L" Hold Time    | tHL             |           | 130 | _   | _   | μs   |

| ADDRESS Pulse Width   | tAW             |           | 1.7 | _   | _   | μs   |

| Data Pulse Width      | tDW             |           | 1.7 | _   | _   | μs   |

| DATA Set-up Time      | t <sub>DS</sub> |           | 0.5 | -   | _   | μs   |

| DATA Hold Time        | toh             |           | 0.2 | _   | _   | μs   |

| WRITE Pulse Width     | tww             |           | 1.0 | _   | _   | μs   |

| CS Enable Delay Time  | tCS1            |           | -   | -   | 0.6 | μs   |

| CS Disoble Delay Time | tCS2            |           | _   | _   | 0.6 | μs   |

- Notes: 1. A WRITE occurs during the overlap of a high CS, a high HOLD and a high WRITE.

- 2. CS may be permanent "1", or may be coincident with HOLD pulse.

Powerec Downloaded from Elcodis.com Well of Conference Stributor

## PIN DESCRIPTION

| Name                            | Pin No. | Description                                                                                                                                                                                                                                                                                             |  |  |  |  |

|---------------------------------|---------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| V <sub>DD</sub>                 | 1       | Power supply pin. Application circuits for power supply are described in Figure 9.                                                                                                                                                                                                                      |  |  |  |  |

| WRITE                           | 2       | Data write pin. Data write cycle is described in Figure 4.                                                                                                                                                                                                                                              |  |  |  |  |

| READ                            | 3       | Data read pin. Data read cycle is described in Figure 3.                                                                                                                                                                                                                                                |  |  |  |  |

| A <sub>0</sub> ~ A <sub>3</sub> | 4 ~ 7   | Address input pins used to select internal counters for read/write operations.  The address is specified by 4-bit binary code as shown in Table 1.                                                                                                                                                      |  |  |  |  |

| c s                             | 8       | Chip slect pin which is required to interface with the external circuit. HOLD, WRITE, READ, $\pm 30$ ADJ, TEST, D <sub>0</sub> $\sim$ D <sub>3</sub> and A <sub>0</sub> $\sim$ A <sub>3</sub> pins are activated if CS is set at H level, while all of these pins are disabled if CS is set at L level. |  |  |  |  |

| $D_0 \sim D_3$                  | 9 ~ 12  | Data input/output pins (bidirectional bus). As shown in Figure 5, external pull-up registers of 4.7 k $\Omega\sim10$ k $\Omega$ are required by the open-drain NMOS output. D <sub>3</sub> is the MSB, while D <sub>0</sub> is the LSB                                                                  |  |  |  |  |

|                                 |         | +5V D <sub>0</sub> D <sub>10</sub>                                                                                                                                                                                                                                                                      |  |  |  |  |

|                                 |         | +5V Do,                                                                                                                                                                                                                                                                                                 |  |  |  |  |

|                                 |         | C S. READ  MSM5832RS                                                                                                                                                                                                                                                                                    |  |  |  |  |

|                                 |         | Figure 5                                                                                                                                                                                                                                                                                                |  |  |  |  |

| Name   | Pin No. | Description                                                                                                                                                                                                                                                                                                                                                                                                                                |  |  |  |  |

|--------|---------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| GND,   | 13      | Ground pin.                                                                                                                                                                                                                                                                                                                                                                                                                                |  |  |  |  |

| TEST   | 14      | Test pin. Normally this pin should be left open or should be set at ground level. With CS at $V_{DD}$ , pulses to $V_{DD}$ on the TEST input will directly clock the $S_1$ , $MI_{10}$ , $W$ , $D_1$ and $Y_1$ counters, depending on which counter is addressed ( $W$ and $D_1$ are selected by $D_1$ address in this mode only). Roll-over to next counter is enabled in this mode.                                                      |  |  |  |  |

| ±30ADJ | 15      | This pin is used to adjust the time within the extent of $\pm$ 30 seconds. If this pin is set at H level when the seconds digits are 0 $\sim$ 29, the seconds digits are cleared to 0. If this pin is set at H level when the seconds digits are 30 $\sim$ 59, the second digits will be cleared to 0 and the minutes digits will be increased by +1. To enable this function, 31.25 ms or more width's pulse should be input to this pin. |  |  |  |  |

| XT     | 16      | Oscillator pin. 32.768 kHz crystal, capacitor and trimmer condensor for f quency adjustment connected to these pins. See Figure 6. As for oscillat                                                                                                                                                                                                                                                                                         |  |  |  |  |

| хт     | 17      | frequency deviation, refer to Figure 1 and Figure 2.  If an external clock is to be used for the MSM5832RS's oscillation source, the external clock is to be input to XT, and XT should be left open.                                                                                                                                                                                                                                      |  |  |  |  |

|        |         | GND or VDD  C <sub>1</sub> XT  RFB  RS  MSM5832RS                                                                                                                                                                                                                                                                                                                                                                                          |  |  |  |  |

|        |         | Figure 6                                                                                                                                                                                                                                                                                                                                                                                                                                   |  |  |  |  |

| HOLD   | 18      | Switching this input to $V_{DD}$ inhibits the internal 1 Hz clock to the S1 counter. After the specified HOLD set-up time (150 $\mu$ s), all counters will be in a static state, thus allowing error-free read or write operations. So long as th HOLD pulse width is less than 990 ms, real time accuracy will be undisturbed. Pull-down to GND is provided by an internal resistor.                                                      |  |  |  |  |

# REFERENCE SIGNAL OUTPUT PIN

| <ul> <li>Condition</li> </ul> | Output             | Reference Frequency | Pulse Width |

|-------------------------------|--------------------|---------------------|-------------|

| HOLD = L                      | D <sub>0</sub> (1) | 1024 Hz             | duty 50%    |

| READ = H                      | D <sub>1</sub>     | 1 Hz                | 122.1 μS    |

| CS = H                        | D <sub>2</sub>     | 1/60 Hz             | 122.1 µS    |

| $A_0 \sim A_3 = H$            | D <sub>3</sub>     | 1/3600 Hz           | 122.1 µS    |

<sup>(1) 1024</sup> Hz signal at  $D_{\theta}$  not dependent on HOLD input level.

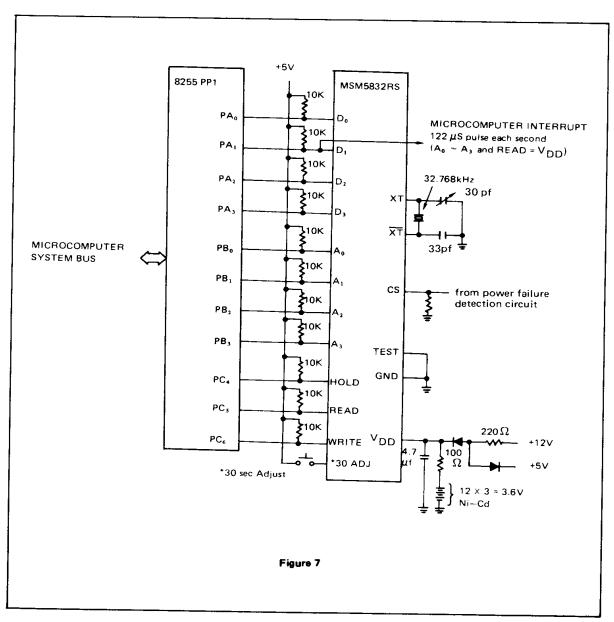

#### **APPLICATION EXAMPLE**

Open or ground unused pins (pins other than the XT, XT, D0-D3, and BUSY pins).

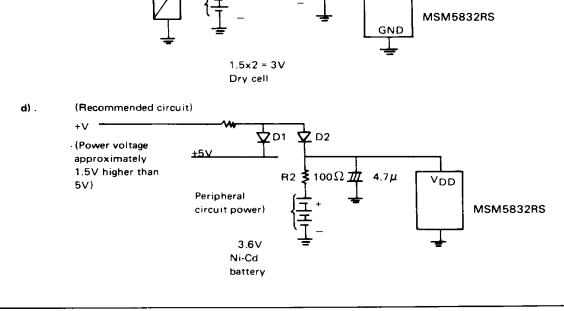

$V_F = 0.69V$ 1S1588 Ripple K +5.7V 100\$ 20 mV P-P Operating state  $\nabla_{DD}$ a) 0 mV Backup C372 GND MSM5832RS 1.2x3 = 3.6VF= 0.69 Ni-Cd battery VCE(Sat) = 0.1VRipple A495 20 mV P-P Operating state 51K 10K <del>√//</del>4.7µ  $100\Omega$ Backup 0 mV  $V_{DD}$ **b)** . 10K 4 GND MSM5832RS 1.2x3 = 3.6VNi-Cd battery RL 100 $\Omega$ +5V RLc) .  $v_{DD}$

Note: Use the same diodes for D1 and D2 to reduce the level difference between +5V and VDD of the MSM5832RS.