# LOW-COST I<sup>2</sup>C CONTROLLED DEFLECTION PROCESSOR FOR MULTISYNC MONITOR

# FEATURES

#### General

- ADVANCED I<sup>2</sup>C BUS CONTROLLED DEFLECTION PROCESSOR DEDICATED FOR HIGH-END CRT MONITORS

- SINGLE SUPPLY VOLTAGE 12V

- VERY LOW JITTER

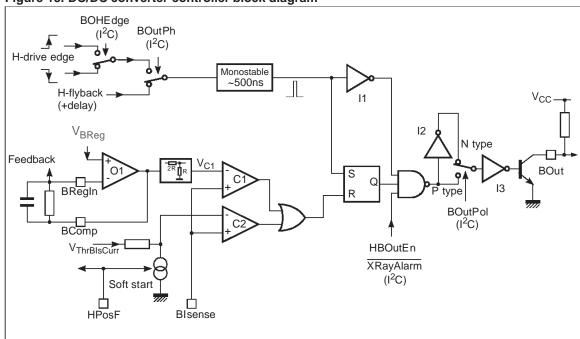

- DC/DC CONVERTER CONTROLLER

- ADVANCED EW DRIVE

- ADVANCED ASYMMETRY CORRECTIONS

- AUTOMATIC MULTISTANDARD SYNCHRONIZATION

- 2 DYNAMIC CORRECTION WAVEFORM OUTPUTS

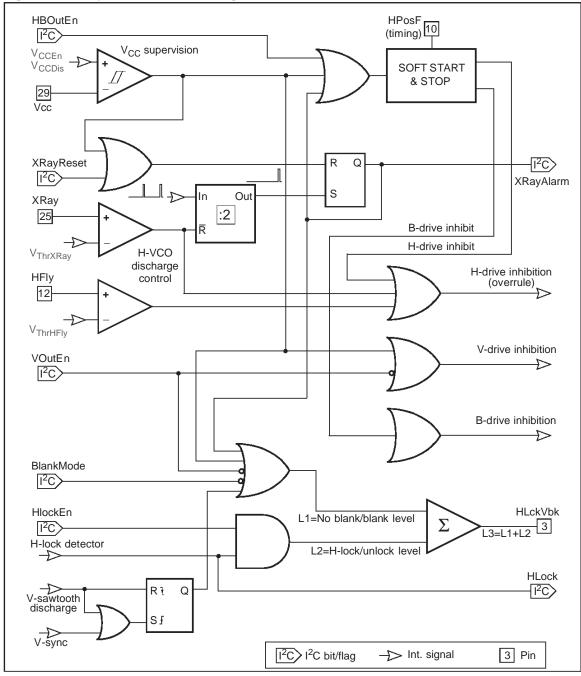

- X-RAY PROTECTION AND SOFT-START & STOP ON HORIZONTAL AND DC/DC DRIVE OUTPUTS

- I<sup>2</sup>C BUS STATUS REGISTER

#### Horizontal section

- 150 kHz maximum frequency

- Corrections of geometric asymmetry: Pin cushion asymmetry, Parallelogram

- Tracking of asymmetry corrections with vertical size and position

- Fully integrated horizontal moiré cancellation

#### Vertical section

- 200 Hz maximum frequency

- Vertical ramp for DC-coupled output stage with adjustments of: C-correction, S-correction for super-flat CRT, Vertical size, Vertical position

- Vertical moiré cancellation through vertical ramp waveform

- Compensation of vertical breathing with EHT variation

#### **EW** section

- Symmetrical geometry corrections: Pin cushion, Keystone, Top/Bottom corners separately

- Horizontal size adjustment

- Tracking of EW waveform with Vertical size and position and adaptation to frequency

- Compensation of horizontal breathing through EW waveform

### **Dynamic correction section**

- Generates waveforms for dynamic corrections like focus, brightness uniformity, ...

- 1 output with vertical dynamic correction waveform

- 1 output with horizontal dynamic correction waveform

- Fixed on screen by means of tracking system

#### **DC/DC controller section**

- Step-up and step-down conversion modes

- External sawtooth configuration

- Bus-controlled output voltage

- Synchronization on hor. frequency with phase selection

- Selectable polarity of drive signal

# DESCRIPTION

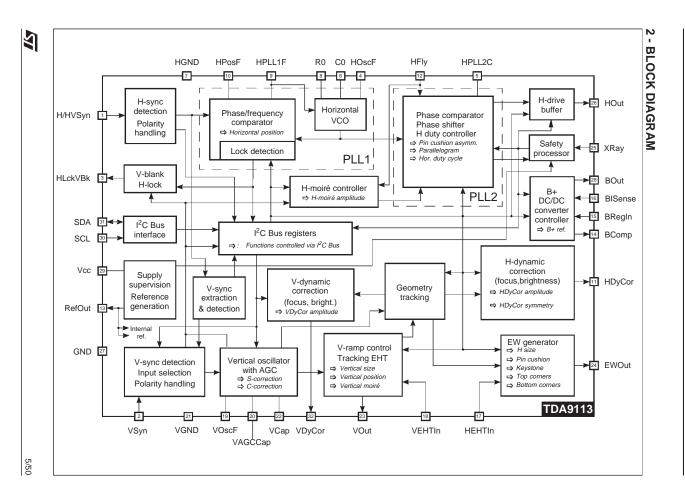

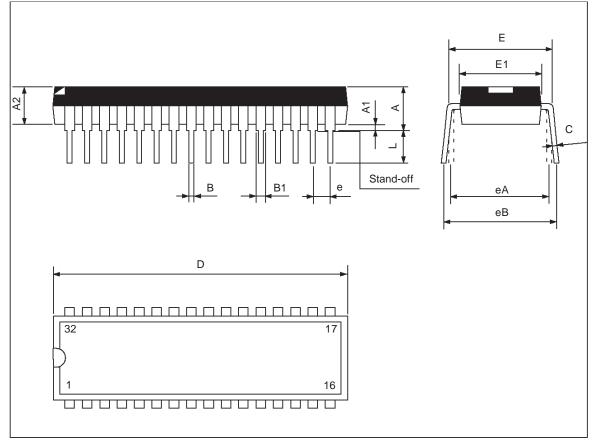

The TDA9113 is a monolithic integrated circuit assembled in a 32-pin shrink dual-in-line plastic package. This IC controls all the functions related to horizontal and vertical deflection in multimode or multi-frequency computer display monitors.

The internal sync processor, combined with the powerful geometry correction block, makes the TDA9113 suitable for very high performance monitors, using few external components.

Combined with other ST components dedicated for CRT monitors (microcontroller, video preamplifier, video amplifier, OSD controller) the TDA9113 allows fully I<sup>2</sup>C bus-controlled computer display monitors to be built with a reduced number of external components.

ORDER CODE: TDA9113

October 2001

1/50

# ------ TABLE OF CONTENTS -------

| 1 -PIN CONFIGURATION                               |     |

|----------------------------------------------------|-----|

| 2 -BLOCK DIAGRAM                                   | -   |

| 3 -PIN FUNCTION REFERENCE                          | . 6 |

| 4 -QUICK REFERENCE DATA                            | . 7 |

| 5 -ABSOLUTE MAXIMUM RATINGS                        | . 8 |

| 6 -ELECTRICAL PARAMETERS AND OPERATING CONDITIONS  |     |

| 6.1 - THERMAL DATA                                 |     |

| 6.2 - SUPPLY AND REFERENCE VOLTAGES                |     |

| 6.3 - SYNCHRONIZATION INPUTS                       |     |

| 6.4 - HORIZONTAL SECTION                           |     |

| 6.5 - VERTICAL SECTION                             | 12  |

| 6.6 - EW DRIVE SECTION                             |     |

| 6.7 - DYNAMIC CORRECTION OUTPUTS SECTION           |     |

| 6.8 -DC/DC CONTROLLER SECTION                      |     |

| 6.9 - MISCELLANEOUS                                |     |

| 7 -TYPICAL OUTPUT WAVEFORMS                        |     |

| 8 -I <sup>2</sup> C BUS CONTROL REGISTER MAP       |     |

| 9 -OPERATING DESCRIPTION                           | -   |

| 9.1 - SUPPLY AND CONTROL                           |     |

| 9.1.1 -Power supply and voltage references         |     |

| 9.1.2 - I <sup>2</sup> C Bus Control               |     |

| 9.2 - SYNC. PROCESSOR                              | -   |

| 9.2.1 -Synchronization signals                     |     |

| 9.2.2 -Sync. presence detection flags              |     |

| 9.2.3 -MCU controlled sync. selection mode         |     |

| 9.2.4 -Automatic sync. selection mode              |     |

| 9.3.1 -General                                     |     |

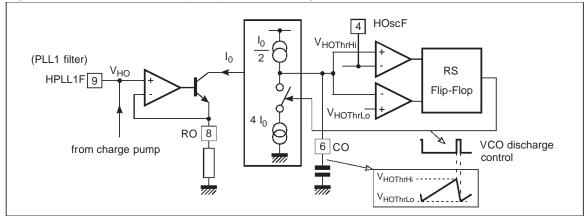

| 9.3.2 -PLL1                                        |     |

| 9.3.3 -Voltage controlled oscillator               |     |

| 9.3.4 -PLL2                                        |     |

| 9.3.5 -Dynamic PLL2 phase control                  |     |

| 9.3.6 -Output Section                              |     |

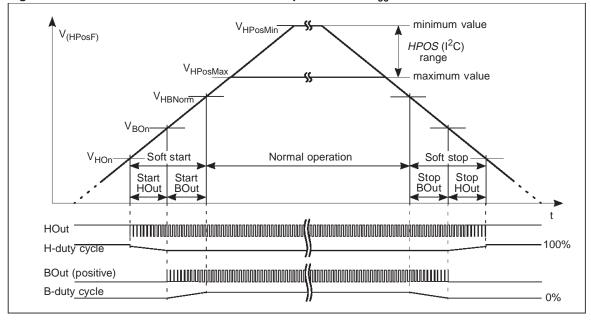

| 9.3.7 -Soft-start and soft-stop on H-drive         |     |

| 9.3.8 -Horizontal moiré cancellation               | 30  |

| 9.4 - VERTICAL SECTION                             |     |

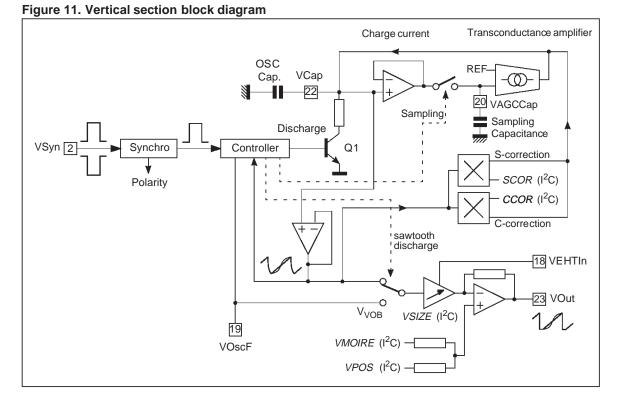

| 9.4.1 -General                                     |     |

| 9.4.2 -Vertical moiré                              |     |

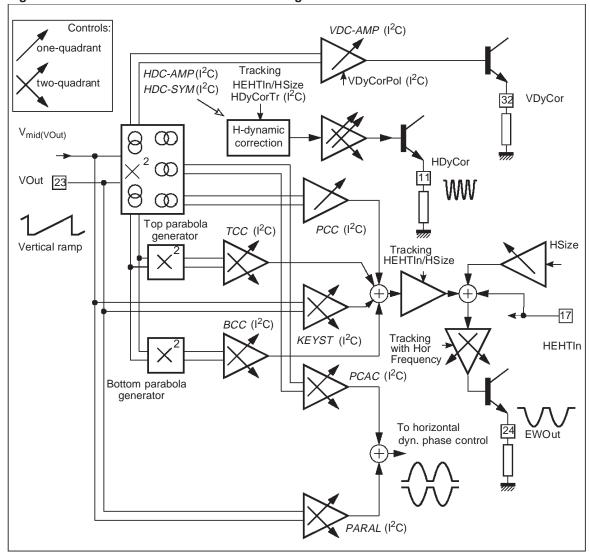

| 9.5 - EW DRIVE SECTION                             |     |

| 9.6 - DYNAMIC CORRECTION OUTPUTS SECTION           |     |

| 9.6.1 -Horizontal dynamic correction output HDyCor |     |

| 9.6.2 -Vertical dynamic correction output VDyCor   |     |

|                                                    |     |

| 9.8 - MISCELLANEOUS                                |     |

| 9.8.2 -Safety functions                            |     |

| 9.8.3 -X-ray protection                            |     |

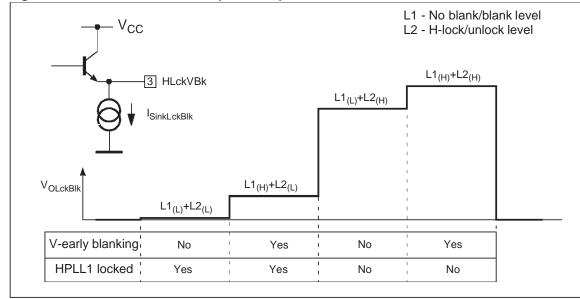

| 9.8.4 -Composite output HLckVBk                    |     |

|                                                    | -   |

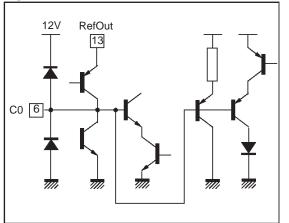

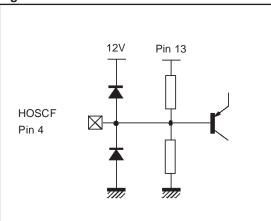

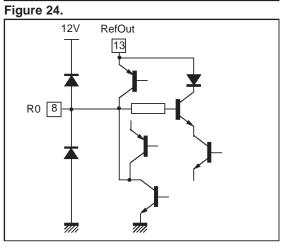

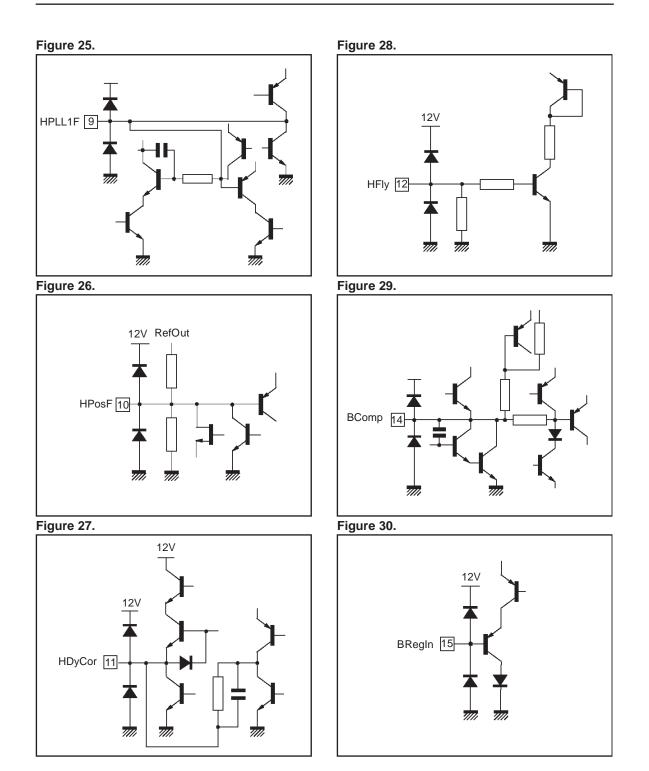

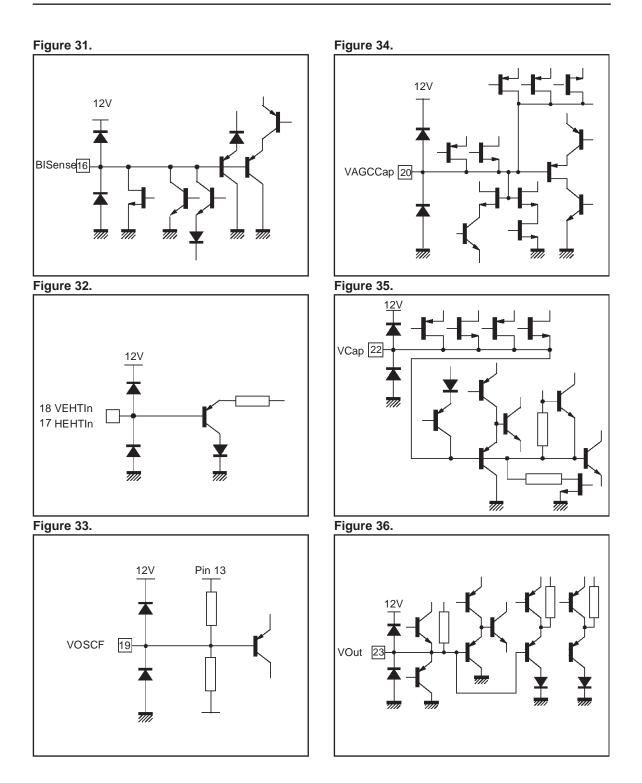

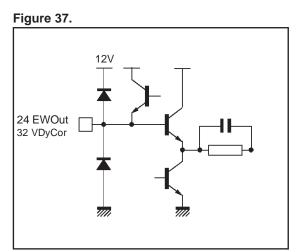

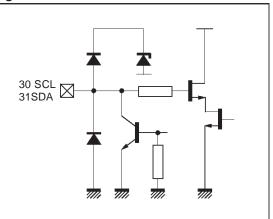

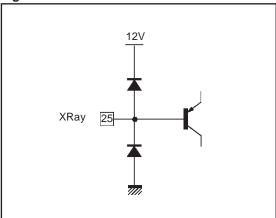

| 10 -INTERNAL SCHEMATICS     | 42 |

|-----------------------------|----|

| 11 -PACKAGE MECHANICAL DATA | 46 |

| 12 -GLOSSARY                | 47 |

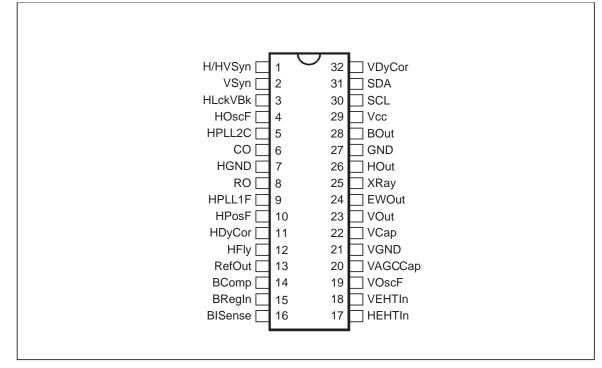

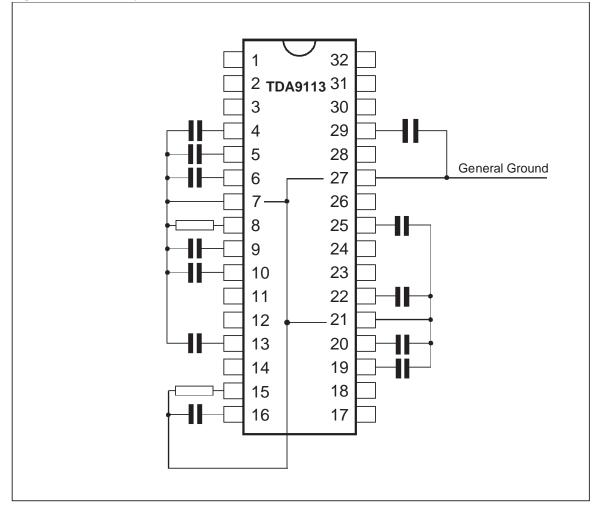

# **1 - PIN CONFIGURATION**

4/50

# **3 - PIN FUNCTION REFERENCE**

| Pin | Name    | Function                                                                              |

|-----|---------|---------------------------------------------------------------------------------------|

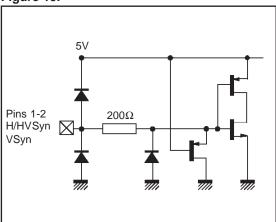

| 1   | H/HVSyn | TTL compatible Horizontal / Horizontal and Vertical Sync. input                       |

| 2   | VSyn    | TTL compatible Vertical Sync. input                                                   |

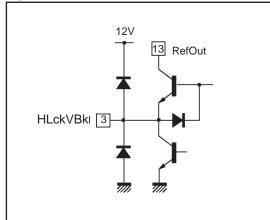

| 3   | HLckVBk | Horizontal PLL1 Lock detection and Vertical early Blanking composite output           |

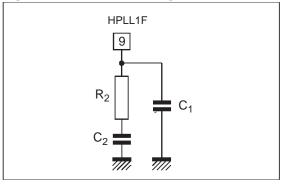

| 4   | HOscF   | High Horizontal Oscillator sawtooth threshold level Filter input                      |

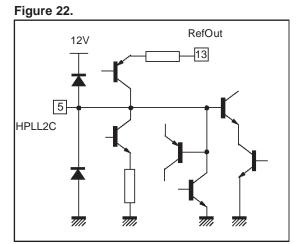

| 5   | HPLL2C  | Horizontal PLL2 loop Capacitive filter input                                          |

| 6   | СО      | Horizontal Oscillator Capacitor input                                                 |

| 7   | HGND    | Horizontal section GrouND                                                             |

| 8   | RO      | Horizontal Oscillator Resistor input                                                  |

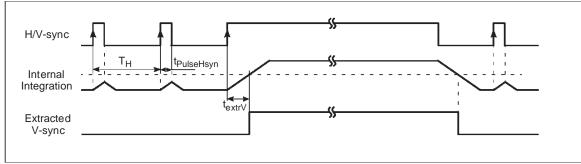

| 9   | HPLL1F  | Horizontal PLL1 loop Filter input                                                     |

| 10  | HPosF   | Horizontal Position Filter and soft-start time constant capacitor input               |

| 11  | HDyCor  | Horizontal Dynamic Correction output                                                  |

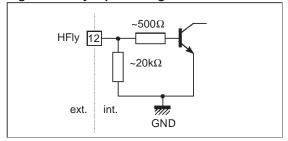

| 12  | HFly    | Horizontal Flyback input                                                              |

| 13  | RefOut  | Reference voltage Output                                                              |

| 14  | BComp   | B+ DC/DC error amplifier (Comparator) output                                          |

| 15  | BRegIn  | Regulation feedback Input of the B+ DC/DC converter controller                        |

| 16  | BISense | B+ DC/DC converter current (I) Sense input                                            |

| 17  | HEHTIn  | Input for compensation of Horizontal amplitude versus EHT variation                   |

| 18  | VEHTIn  | Input for compensation of Vertical amplitude versus EHT variation                     |

| 19  | VOscF   | Vertical Oscillator sawtooth low threshold Filter (capacitor to be connected to VGND) |

| 20  | VAGCCap | Input for storage Capacitor for Automatic Gain Control loop in Vertical oscillator    |

| 21  | VGND    | Vertical section GrouND                                                               |

| 22  | VCap    | Vertical sawtooth generator Capacitor                                                 |

| 23  | VOut    | Vertical deflection drive Output for a DC-coupled output stage                        |

| 24  | EWOut   | E/W Output                                                                            |

| 25  | XRay    | X-Ray protection input                                                                |

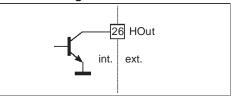

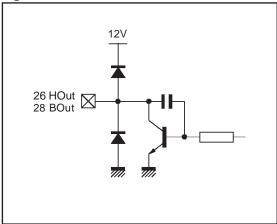

| 26  | HOut    | Horizontal drive Output                                                               |

| 27  | GND     | Main GrouND                                                                           |

| 28  | BOut    | B+ DC/DC converter controller Output                                                  |

| 29  | Vcc     | Supply voltage                                                                        |

| 30  | SCL     | I <sup>2</sup> C bus Serial CLock Input                                               |

| 31  | SDA     | I <sup>2</sup> C bus Serial DAta input/output                                         |

| 32  | VDyCor  | Vertical Dynamic Correction output                                                    |

# **4 - QUICK REFERENCE DATA**

| Characteristic                                                            | Value                    | Unit |

|---------------------------------------------------------------------------|--------------------------|------|

| General                                                                   |                          |      |

| Package                                                                   | SDIP 32                  |      |

| Supply voltage                                                            | 12                       | V    |

| Supply current                                                            | 65                       | mA   |

| Application category                                                      | Mid-range                |      |

| Means of control/Maximum clock frequency                                  | I <sup>2</sup> C Bus/400 | kHz  |

| EW drive                                                                  | Yes                      |      |

| DC/DC converter controller                                                | Yes                      |      |

| Horizontal section                                                        | - 1                      |      |

| Frequency range                                                           | 15 to 150                | kHz  |

| Autosync frequency ratio (can be enlarged in application)                 | 4.28                     |      |

| Positive/Negative polarity of horizontal sync signal/Automatic adaptation | Yes/Yes/Yes              |      |

| Duty cycle range of the drive signal                                      | 30 to 65                 | %    |

| Position adjustment range with respect to H period                        | ±10                      | %    |

| Soft start/Soft stop feature                                              | Yes/Yes                  | ,,,  |

| Hardware/Software PLL lock indication                                     | Yes/Yes                  |      |

| Parallelogram                                                             | Yes                      |      |

| Pin cushion asymmetry correction (also called Side pin balance)           | Yes                      |      |

| Top/Bottom/Common corner asymmetry correction                             | No/No/No                 |      |

| Tracking of asymmetry corrections with vertical size & position           | Yes                      |      |

| Horizontal moiré cancellation (int.) for Combined/Separated architecture  | Yes/Yes                  |      |

| Vertical section                                                          | 103/103                  |      |

| Frequency range                                                           | 35 to 200                | Hz   |

| Autosync frequency range (150nF at VCap and 470nF at VAGCCap)             | 50 to 180                | Hz   |

| Positive/Negative polarity of vertical sync signa/Automatic adaptation    | Yes/Yes/Yes              | п    |

| S-correction/C-correction/Super-flat tube characteristic                  | Yes/Yes/Yes              |      |

|                                                                           |                          |      |

| Vertical size/Vertical position adjustment                                | Yes/Yes                  |      |

| Vertical moiré cancellation (internal)                                    | Yes                      |      |

| Vertical breathing compensation                                           | Yes                      |      |

| EW section                                                                | -1 - <del>V</del>        |      |

| Pin cushion correction                                                    | Yes                      |      |

| Keystone correction                                                       | Yes                      |      |

| Top/Bottom/Common corner correction                                       | Yes/Yes/No               |      |

| Horizontal size adjustment                                                | Yes                      |      |

| Tracking of EW waveform with Frequency/Vertical size & position           | Yes/Yes                  |      |

| Breathing compensation on EW waveform                                     | Yes                      |      |

| Dynamic correction section (dyn. focus, dyn. brightness,)                 |                          |      |

| Vertical dynamic correction output VDyCor                                 | Yes                      |      |

| Horizontal dynamic correction output HDyCor                               | Yes                      |      |

| Composite HV dynamic correction output HVDyCor                            | No                       |      |

| Tracking of horizontal waveform component with Horizontal size/EHT        | Yes/Yes                  |      |

| Tracking of vertical waveforms (component) with V. size & position        | Yes                      |      |

| DC/DC controller section                                                  |                          |      |

| Step-up/Step-down conversion mode                                         | Yes/Yes                  |      |

|                                                                           | No/Yes                   |      |

| Internal/External sawtooth configuration                                  |                          |      |

| Internal/External sawtooth configuration Bus-controlled output voltage    | Yes                      |      |

|                                                                           | Yes<br>Yes/Yes           |      |

57

# **5 - ABSOLUTE MAXIMUM RATINGS**

All voltages are given with respect to ground.

Currents flowing from the device (sourced) are signed negative. Currents flowing to the device are signed positive.

| Symbol             | Parameter                                                                                                                                                                                                 |                                      | Value                                                                                    |                  |  |

|--------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------|------------------------------------------------------------------------------------------|------------------|--|

|                    | Falameter                                                                                                                                                                                                 | Min                                  | Max                                                                                      | Unit             |  |

| V <sub>CC</sub>    | Supply voltage (pin Vcc)                                                                                                                                                                                  | -0.4                                 | 13.5                                                                                     | V                |  |

| V <sub>(pin)</sub> | Pins HEHTIn, VEHTIn, XRay, HOut, BOut<br>Pins H/HVSyn, VSyn, SCL, SDA<br>Pins HLckVBk, CO, RO, HPLL1F, HPosF, HDyCor, BRegIn, BI-<br>Sense, VAGCCap, VCap, VDyCor, HOscF, VOscF<br>Pin HPLL2C<br>Pin HFly | -0.4<br>-0.4<br>-0.4<br>-0.4<br>-0.4 | V <sub>CC</sub><br>5.5<br>V <sub>RefO</sub><br>V <sub>RefO</sub> /2<br>V <sub>RefO</sub> | ><br>><br>><br>> |  |

| V <sub>ESD</sub>   | ESD susceptibility (human body model: discharge of 100pF through $1.5k\Omega$ )                                                                                                                           | -2000                                | 2000                                                                                     | V                |  |

| T <sub>stg</sub>   | Storage temperature                                                                                                                                                                                       | -40                                  | 150                                                                                      | °C               |  |

| Тj                 | Junction temperature                                                                                                                                                                                      |                                      | 150                                                                                      | °C               |  |

# **6 - ELECTRICAL PARAMETERS AND OPERATING CONDITIONS**

Medium (middle) value of an I<sup>2</sup>C Bus control or adjustment register composed of bits D0, D1,...,Dn is the one having Dn at "1" and all other bits at "0". Minimum value is the one with all bits at 0, maximum value is the one with all at "1".

Currents flowing from the device (sourced) are signed negative. Currents flowing to the device are signed positive.

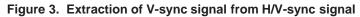

T<sub>H</sub> is period of horizontal deflection.

# 6.1 - THERMAL DATA

| Symbol |           | Parameter                            |      | Value |      |      |  |

|--------|-----------|--------------------------------------|------|-------|------|------|--|

| Symbol | Farameter | Min.                                 | Тур. | Max.  | Unit |      |  |

| Т      | amb       | Operating ambient temperature        | 0    |       | 70   | °C   |  |

| R      | th(j-a)   | Junction-ambience thermal resistance |      | 65    |      | °C/W |  |

# 6.2 - SUPPLY AND REFERENCE VOLTAGES

$T_{amb} = 25^{\circ}C$

| Symbol            | Parameter                              | Test Conditions                   | Value |      |      | Units |

|-------------------|----------------------------------------|-----------------------------------|-------|------|------|-------|

| eysoi             |                                        |                                   | Min.  | Тур. | Max. | onits |

| V <sub>CC</sub>   | Supply voltage at Vcc pin              |                                   | 10.8  | 12   | 13.2 | V     |

| I <sub>CC</sub>   | Supply current to Vcc pin              | $V_{\rm CC} = 12V$                |       | 65   |      | mA    |

| V <sub>RefO</sub> | Reference output voltage at RefOut pin | $V_{CC}$ = 12V, $I_{RefO}$ = -2mA | 7.65  | 8.0  | 8.2  | V     |

| I <sub>RefO</sub> | Current sourced by RefOut output       |                                   | -5    |      | 0    | mA    |

# **6.3 - SYNCHRONIZATION INPUTS**

Vcc = 12V,  $T_{amb} = 25^{\circ}C$

| Symbol                                 | Parameter                                                                       | Test Conditions                        | Value |      |      | Units |

|----------------------------------------|---------------------------------------------------------------------------------|----------------------------------------|-------|------|------|-------|

| Cyllisor                               | i alameter                                                                      |                                        | Min.  | Тур. | Max. |       |

| V <sub>LoH/HVSyn</sub>                 | LOW level voltage on H/HVSyn                                                    |                                        | 0     |      | 0.8  | V     |

| V <sub>HiH/HVSyn</sub>                 | HIGH level voltage on H/HVSyn                                                   |                                        | 2.2   |      | 5    | V     |

| V <sub>LoVSyn</sub>                    | LOW level voltage on VSyn                                                       |                                        | 0     |      | 0.8  | V     |

| V <sub>HiVSyn</sub>                    | HIGH level voltage on VSyn                                                      |                                        | 2.2   |      | 5    | V     |

| R <sub>PdSyn</sub>                     | Internal pull-down on H/HVSyn, VSyn                                             |                                        | 100   | 175  | 250  | kΩ    |

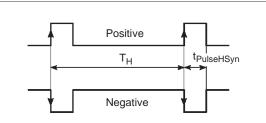

| t <sub>PulseHSyn</sub>                 | H sync. pulse duration on H/HVSyn pin                                           |                                        | 0.5   |      |      | μs    |

| t <sub>PulseHSyn</sub> /T <sub>H</sub> | Proportion of H sync pulse to H period                                          | Pin H/HVSyn                            |       |      | 0.2  |       |

| t <sub>PulseVSyn</sub>                 | V sync. pulse duration                                                          | Pins H/HVSyn, VSyn                     | 0.5   |      | 750  | μs    |

| t <sub>PulseVSyn</sub> /T <sub>V</sub> | Proportion of V sync pulse to V period                                          | Pins H/HVSyn, VSyn                     |       |      | 0.15 |       |

| t <sub>extrV</sub> /T <sub>H</sub>     | Proportion of sync pulse length to H peri-<br>od for extraction as V sync pulse | Pin H/HVSyn,<br>cap. on pin CO = 820pF | 0.21  | 0.3  |      |       |

| t <sub>HPolDet</sub>                   | Polarity detection time (after change)                                          | Pin H/HVSyn                            | 0.75  |      |      | ms    |

57

9/50

# 6.4 - HORIZONTAL SECTION

Vcc = 12V,  $T_{amb} = 25^{\circ}C$

| Symbol                                            | Parameter                                                                              | Test Conditions                                                      |                   | Units             |                   |             |

|---------------------------------------------------|----------------------------------------------------------------------------------------|----------------------------------------------------------------------|-------------------|-------------------|-------------------|-------------|

| Symbol                                            |                                                                                        |                                                                      | Min.              | Тур.              | Max.              |             |

| PLL1                                              | -                                                                                      |                                                                      |                   |                   |                   |             |

| I <sub>RO</sub>                                   | Current load on RO pin                                                                 |                                                                      |                   |                   | 1.5               | mA          |

| C <sub>CO</sub>                                   | Capacitance on CO pin                                                                  |                                                                      | 390               |                   |                   | pF          |

| f <sub>HO</sub>                                   | Frequency of hor. oscillator                                                           |                                                                      |                   |                   | 150               | kHz         |

| f <sub>HO(0)</sub>                                | Free-running frequency of hor. oscill. <sup>(1)</sup>                                  | R <sub>RO</sub> =5.23kΩ, C <sub>CO</sub> =820pF                      | 27                | 28.5              | 29.9              | kHz         |

| f <sub>HOCapt</sub>                               | Hor. PLL1 capture frequency <sup>(4)</sup>                                             | f <sub>HO(0)</sub> = 28.5kHz                                         | 29                |                   | 122               | kHz         |

| $\frac{\Delta f_{HO(0)}}{f_{HO(0)}\cdot\Delta T}$ | Temperature drift of free-running freq. <sup>(3)</sup>                                 |                                                                      |                   | -150              |                   | ppm/°C      |

| $\Delta f_{HO} / \Delta V_{HO}$                   | Average horizontal oscillator sensitivity                                              | f <sub>HO(0)</sub> = 28.5kHz                                         |                   | 19.6              |                   | kHz/V       |

| V <sub>HO</sub>                                   | H. oscill. control voltage on pin HPLL1F                                               | V <sub>RefO</sub> =8V                                                | 1.4               |                   | 6.0               | V           |

| V <sub>HOThrfr</sub>                              | Threshold on H. oscill. control voltage on<br>HPLL1F pin for tracking of EW with freq. | V <sub>RefO</sub> =8V                                                |                   | 5.0               |                   | V           |

| V <sub>HPosF</sub>                                | Control voltage on HPosF pin                                                           | HPOS (Sad01):<br>1111111b<br>1000000b<br>0000000b                    | 2.6<br>3.2<br>3.8 | 2.8<br>3.4<br>4.0 | 3.0<br>3.6<br>4.2 | V<br>V<br>V |

| V <sub>HOThrLo</sub>                              | Bottom of hor. oscillator sawtooth <sup>(6)</sup>                                      |                                                                      |                   | 1.6               |                   | V           |

| V <sub>HOThrHi</sub>                              | Top of hor. oscillator sawtooth <sup>(6)</sup>                                         |                                                                      |                   | 6.4               |                   | V           |

| PLL2                                              |                                                                                        | L                                                                    |                   | 1                 | 1                 | 1           |

| R <sub>In(HFly)</sub>                             | Input impedance on HFly input                                                          | $V_{(HFly)} > V_{ThrHFly}$ <sup>(2)</sup>                            | 300               | 500               | 700               | Ω           |

| I <sub>InHFly</sub>                               | Current into HFly input                                                                | At top of H flyback pulse                                            |                   |                   | 5                 | mA          |

| V <sub>ThrHFly</sub>                              | Voltage threshold on HFly input                                                        |                                                                      | 0.6               | 0.7               |                   | V           |

| V <sub>S(0)</sub>                                 | H flyback lock middle point <sup>(6)</sup>                                             | No PLL2 phase modula-<br>tion                                        |                   | 4.0               |                   | V           |

| V <sub>BotHPLL2C</sub>                            | Low clamping voltage on HPLL2C pin <sup>(5)</sup>                                      |                                                                      |                   | 1.6               |                   | V           |

| V <sub>TopHPLL2C</sub>                            | High clamping voltage on HPLL2C pin <sup>(5)</sup>                                     |                                                                      | 3.9               | 4.05              | 4.2               | V           |

| t <sub>ph</sub> (min)/T <sub>H</sub>              | Min. advance of H-drive OFF before middle of H flyback <sup>(7)</sup>                  | Null asym. correction                                                |                   | 0                 |                   | %           |

| t <sub>ph</sub> (max)/T <sub>H</sub>              | Max. advance of H-drive OFF before middle of H flyback <sup>(8)</sup>                  | Null asym. correction                                                |                   | 44                |                   | %           |

| H-drive outpu                                     | t on pin HOut                                                                          |                                                                      |                   |                   |                   |             |

| I <sub>HOut</sub>                                 | Current into HOut output                                                               | Output driven LOW                                                    |                   | Ι                 | 30                | mA          |

| t <sub>Hoff</sub> /T <sub>H</sub>                 | Duty cycle of H-drive signal                                                           | HDUTY (Sad00):<br>x111111b<br>x000000b<br>Soft-start/Soft-stop value |                   | 27<br>65<br>85    |                   | %<br>%<br>% |

| Picture geom                                      | etry corrections through PLL1 & PLL2                                                   | · · · ·                                                              |                   | ı                 |                   |             |

| t <sub>Hph</sub> /T <sub>H</sub>                  | H-flyback (center) static phase vs. sync<br>signal (via PLL1), see Figure 7            | <i>HPOS</i> (Sad01):<br>11111111b<br>00000000b                       |                   | +11<br>-11        |                   | %           |

| Symbol                              | Parameter                                                                                                                   | Test Conditions                                                                                                                                          | Value |                                |      | Units       |

|-------------------------------------|-----------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------|-------|--------------------------------|------|-------------|

|                                     | i arameter                                                                                                                  |                                                                                                                                                          | Min.  | Тур.                           | Max. |             |

| t <sub>PCAC</sub> /T <sub>H</sub>   | Contribution of pin cushion asymmetry<br>correction to phase of H-drive vs. static<br>phase (via PLL2), measured in corners | PCAC (Sad11h) full span<br>(9)<br>VPOS at medium<br>VSIZE at minimum<br>VSIZE at medium<br>VSIZE at maximum                                              |       | ±1.0<br>±1.8<br>±2.8           |      | %<br>%<br>% |

| t <sub>ParalC</sub> /T <sub>H</sub> | Contribution of parallelogram correction<br>to phase of H-drive vs. static phase (via<br>PLL2), measured in corners         | PARAL (Sad12h) full span<br>(9)<br>VPOS at medium<br>VSIZE at minimum<br>VSIZE at medium<br>VSIZE at maximum<br>VPOS at max. or min.<br>VSIZE at minimum |       | ±1.75<br>±2.2<br>±2.8<br>±1.75 |      | %<br>%<br>% |

**Note 1:** Frequency at no sync signal condition. For correct operation, the frequency of the sync signal applied must always be higher than the free-running frequency. The application must consider the spread of values of real electrical components in  $R_{RO}$  and  $C_{CO}$  positions so as to always meet this condition. The formula to calculate the free-running frequency is  $f_{HO(0)}=0.12125/(R_{RO}C_{CO})$

- **Note 2:** Base of NPN transistor with emitter to ground is internally connected on pin HFly through a series resistance of about  $500\Omega$  and a resistance to ground of about  $20k\Omega$ .

- Note 3: Evaluated and figured out during the device qualification phase. Informative. Not tested on every single unit.

- Note 4: This capture range can be enlarged by external circuitry.

- **Note 5:** The voltage on HPLL2C pin corresponds to immediate phase of leading edge of H-drive signal on HOut pin with respect to internal horizontal oscillator sawtooth. It must be between the two clamping levels given. Voltage equal to one of the clamping values indicates a marginal operation of PLL2 or non-locked state.

- Note 6: Internal threshold. See Figure 10.

- **Note 7:** The t<sub>ph</sub>(min)/T<sub>H</sub> parameter is fixed by the application. For correct operation of asymmetry corrections through dynamic phase modulation, this minimum must be increased by maximum of the total dynamic phase required in the direction leading to bending of corners to the left. Marginal situation is indicated by reach of V<sub>TopHPLL2C</sub> high clamping level by waveform on pin HPLL2C. Also refer to Note 5 and Figure 10.

- **Note 8:** The  $t_{ph}(max)/T_H$  parameter is fixed by the application. For correct operation of asymmetry corrections through dynamic phase modulation, this maximum must be reduced by maximum of the total dynamic phase required in the direction leading to bending of corners to the right. Marginal situation is indicated by reach of V<sub>BotHPLL2C</sub> low clamping level by waveform on pin HPLL2C. Also refer to Note 5 and Figure 10.

- Note 9: All other dynamic phase corrections of picture asymmetry set to their neutral (medium) positions.

# 6.5 - VERTICAL SECTION

# $V_{CC}$ = 12V, $T_{amb}$ = 25°C

| Symbol                                                   | Parameter                                                 | Test Conditions                                                                                                                                                                                                 | Value |                     |       | Units       |

|----------------------------------------------------------|-----------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|---------------------|-------|-------------|

| Symbol                                                   |                                                           | Test conditions                                                                                                                                                                                                 | Min.  | Тур.                | Max.  | Units       |

| GC-controlled ver                                        | tical oscillator sawtooth; ∀ <sub>RefO</sub> =            | 8V                                                                                                                                                                                                              |       |                     |       |             |

| R <sub>L(VAGCCap)</sub>                                  | Ext. load resistance on VAGCCap pin <sup>(10)</sup>       | $\Delta V_{amp} / V_{amp} (R=\infty) \le 1\%$                                                                                                                                                                   | 65    |                     |       | MΩ          |

| V <sub>VOB</sub>                                         | Sawtooth bottom voltage on VCap pin <sup>(11)</sup>       | No load on VOscF pin <sup>(11)</sup>                                                                                                                                                                            | 1.85  | 1.95                | 2.1   | V           |

| V <sub>VOT</sub>                                         | Sawtooth top voltage on VCap pin                          | AGC loop stabilized<br>V sync present<br>No V sync                                                                                                                                                              |       | 5<br>4.9            |       | V<br>V      |

| t <sub>VODis</sub>                                       | Sawtooth Discharge time                                   | C <sub>VCap</sub> =150nF                                                                                                                                                                                        |       | 80                  |       | μs          |

| f <sub>VO(0)</sub>                                       | Free-running frequency                                    | C <sub>VCap</sub> =150nF                                                                                                                                                                                        |       | 100                 |       | Hz          |

| f <sub>VOCapt</sub>                                      | AGC loop capture frequency                                | C <sub>VCap</sub> =150nF                                                                                                                                                                                        | 50    |                     | 185   | Hz          |

| $\frac{\Delta V_{VOdev}}{V_{VOamp}(16)}$                 | Sawtooth non-linearity <sup>(12)</sup>                    | AGC loop stabilized, <sup>(12)</sup>                                                                                                                                                                            |       | 0.5                 |       | %           |

| $\frac{\Delta V_{VOS-cor}}{V_{VOamp}}$                   | S-correction range                                        | AGC loop stabilized, $^{(13)}$<br>t <sub>VR</sub> =1/4 T <sub>VR</sub> $^{(15)}$<br>t <sub>VR</sub> =3/4 T <sub>VR</sub>                                                                                        |       | -5<br>+5            |       | %<br>%      |

| $\frac{\Delta V_{VOC-cor}}{V_{VOamp}}$                   | C-correction range                                        | $\begin{array}{l} \mbox{AGC loop stabilized,} & \mbox{(14)} \\ \mbox{t}_{VR} = 1/2 \ \mbox{T}_{VR} & \mbox{(15)} \\ \mbox{CCOR} (Sad0A): \\ \mbox{x000000b} \\ \mbox{x100000b} \\ \mbox{x1111111b} \end{array}$ |       | -3<br>0<br>+3       |       | %<br>%      |

| $\frac{\Delta V_{VOamp}}{V_{VOamp} \cdot \Delta f_{VO}}$ | Frequency drift of sawtooth amplitude <sup>(17)(18)</sup> | AGC loop stabilized<br>f <sub>VOCapt</sub> (min)≤f <sub>VOCapt</sub> (max)                                                                                                                                      |       | 200                 |       | ppm/H:      |

| ertical output driv                                      | e signal (on pin VOut); V <sub>RefO</sub> = 81            | 1                                                                                                                                                                                                               |       | ı                   |       |             |

| V <sub>mid(VOut)</sub>                                   | Middle point on VOut sawtooth                             | VPOS (Sad08):<br>x0000000b<br>x1000000b<br>x1111111b                                                                                                                                                            | 3.65  | 3.2<br>3.5<br>3.8   | 3.3   | V<br>V<br>V |

| V <sub>amp</sub>                                         | Amplitude of VOut sawtooth<br>(peak-to-peak voltage)      | <i>VSIZE</i> (Sad07):<br>x0000000b<br>x1000000b<br>x1111111b                                                                                                                                                    | 3.5   | 2.25<br>3.0<br>3.75 | 2.5   | V<br>V<br>V |

| VoffVOut                                                 | Level on VOut pin at V-drive "off"                        | I <sup>2</sup> Cbit VOutEn at 0                                                                                                                                                                                 |       | 3.8                 |       | V           |

| I <sub>VOut</sub>                                        | Current delivered by VOut out-<br>put                     |                                                                                                                                                                                                                 | -5    |                     | 5     | mA          |

| V <sub>VEHT</sub>                                        | Control input voltage range on VEHTIn pin                 |                                                                                                                                                                                                                 | 1     |                     | VRefO | V           |

| $\frac{\Delta V_{amp}}{V_{amp} \cdot \Delta V_{VEHT}}$   | Breathing compensation                                    | V <sub>VEHT</sub> >VRefO<br>V <sub>VEHT</sub> (min)≤V <sub>VEHT</sub> ≤V <sub>RefO</sub>                                                                                                                        |       | 0<br>2.5            |       | %/V<br>%/V  |

Note 10: Value of acceptable cumulated parasitic load resistance due to humidity, AGC storage capacitor leakage, etc., for less than 1% of  $V_{amp}$  change.

- Note 11: The threshold for  $V_{VOB}$  is generated internally and routed to VOscF pin. Any DC current on this pin will influence the value of  $V_{VOB}$ .

- Note 12: Maximum of deviation from an ideally linear sawtooth ramp at null *SCOR* (Sad09 at x000000b) and null *CCOR* (Sad0A at x100000b). The same rate applies to V-drive signal on VOut pin.

- Note 13: Maximum SCOR (Sad09 at x111111b), null CCOR (Sad0A at x100000b).

- Note 14: Null SCOR (Sad09 at x000000b).

- **Note 15:** "t<sub>VR</sub>" is time from the beginning of vertical ramp of V-drive signal on VOut pin. "T<sub>VR</sub>" is duration of this ramp, see chapter TYPICAL OUTPUT WAVEFORMS and Figure 20.

Note 16:  $V_{VOamp} = V_{VOT} - V_{VOB}$

Note 17: The same rate applies to V-drive signal on VOut pin.

Note 18: Informative, not tested on each unit.

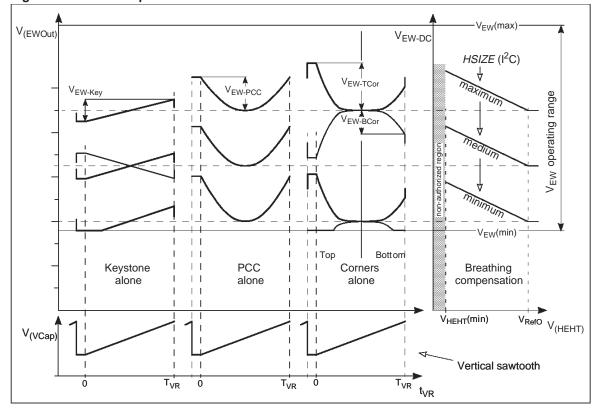

## 6.6 - EW DRIVE SECTION

$V_{CC} = 12V, T_{amb} = 25^{\circ}C$

| Symbol                                                                        | Parameter                                                                                | Test Conditions                                                                                                                                                                                                                 | Value |                                |                   | Units       |

|-------------------------------------------------------------------------------|------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|--------------------------------|-------------------|-------------|

| C y liber                                                                     |                                                                                          |                                                                                                                                                                                                                                 | Min.  | Тур.                           | Max.              |             |

| V <sub>EW</sub>                                                               | Output voltage on EWOut pin                                                              |                                                                                                                                                                                                                                 | 1.8   |                                | 6.5               | V           |

| I <sub>EWOut</sub>                                                            | Current sourced by EWOut out-<br>put                                                     |                                                                                                                                                                                                                                 | -1.5  |                                | 0                 | mA          |

| V <sub>HEHT</sub>                                                             | Control voltage range on HEH-<br>TIn pin                                                 |                                                                                                                                                                                                                                 | 1     |                                | V <sub>RefO</sub> | V           |

| V <sub>EW-DC</sub>                                                            | DC component of the EW-drive signal on EWOut pin                                         | (19)(22)(23)(30)<br>t <sub>VR</sub> =1/2 T <sub>VR</sub> <sup>(15)</sup><br><i>HSIZE</i> (Sad10h):<br>00000000b<br>10000000b<br>11111111b                                                                                       |       | 2<br>3.25<br>4.5               |                   | V<br>V<br>V |

| $\frac{\Delta V_{EW-DC}}{\Delta V_{HEHT}}$                                    | Breathing compensation on V <sub>EW-DC</sub>                                             | (19)(20)(21)(22)<br>t <sub>VR</sub> =1/2 T <sub>VR</sub> <sup>(15)</sup><br>V <sub>HEHT</sub> >V <sub>RefO</sub><br>V <sub>HEHT</sub> (min)≤V <sub>HEHT</sub> ≤VRefO                                                            |       | 0<br>-0.125                    |                   | V/V<br>V/V  |

| $\frac{\Delta V_{\text{EW}-\text{DC}}}{V_{\text{EW}-\text{DC}}\cdot\Delta T}$ | Temperature drift of DC compo-<br>nent of the EW-drive signal on<br>EWOut pin            | (18)(19)(21)(23)(30)<br>t <sub>VR</sub> =1/2 T <sub>VR</sub> <sup>(15)</sup>                                                                                                                                                    |       | 100                            |                   | ppm/°C      |

| V <sub>EW-PCC</sub>                                                           | Pin cushion correction compo-<br>nent of the EW-drive signal on<br>EWOut pin             | (19)(20)(21)(23)(24)(25)(26)(30)<br>VSIZE at maximum<br>PCC (Sad0C):<br>x000000b<br>x1100000b<br>x111111b<br>Tracking with VSIZE :<br>PCC at x100000b<br>VSIZE (Sad07):<br>x000000b<br>x100000b<br>(19)(20)(21)(24)(27)(29)(30) |       | 0<br>0.7<br>1.5<br>0.25<br>0.5 |                   |             |

| $\frac{V_{EW-PCC}[t_{vr}=0]}{EW-PCC}[t_{vr}=T_{VR}]$                          | Tracking of PCC component of<br>the EW-drive signal with vertical<br>position adjustment | PCC at x1111111b<br>VPOS (Sad08):<br>x0000000b<br>x1111111b                                                                                                                                                                     |       | 0.52<br>1.92                   |                   |             |

13/50

| Symbol                                                                                        | Parameter                                                                      | Test Conditions                                                                                | Value |                     |      | Units       |

|-----------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------|-------|---------------------|------|-------------|

| Cymbol                                                                                        | i urumeter                                                                     |                                                                                                | Min.  | Тур.                | Max. |             |

| V <sub>EW-Key</sub>                                                                           | Keystone correction component<br>of the EW-drive signal on<br>EWOut pin        | (20)(21)(22)(23)(24)(27)(28)(30)<br><i>KEYST</i> (Sad0D):<br>x0000000b<br>x1111111b            |       | 0.4<br>-0.4         |      | V<br>V      |

| V <sub>EW-TCor</sub>                                                                          | Top corner correction compo-<br>nent of the EW-drive signal on<br>EWOut pin    | (19)(21)(22)(23)(24)(25)(27)(30)<br><i>TCC</i> (Sad0E):<br>x0000000b<br>x1000000b<br>x1111111b |       | -1.25<br>0<br>+1.25 |      | V<br>V<br>V |

| V <sub>EW-BCor</sub>                                                                          | Bottom corner correction compo-<br>nent of the EW-drive signal on<br>EWOut pin | (19)(20)(22)(23)(24)(26)(27)(30)<br>BCC (Sad0F):<br>x0000000b<br>x1000000b<br>x1111111b        |       | -1.25<br>0<br>+1.25 |      | V<br>V<br>V |

| $\frac{{}^{\Delta V}_{EW}}{{}^{V}_{EW}{}^{[f}_{max}{}^{]}\cdot {}^{\Delta V}_{HO}}}$          | Tracking of EW-drive signal with horizontal frequency <sup>(32)</sup>          | V <sub>HO</sub> >VHOThrfr<br>V <sub>HO</sub> (min)≤V <sub>HO</sub> ≤V <sub>HOThrfr</sub>       |       | 0<br>20             |      | %/V<br>%/V  |

| $\frac{\Delta V_{\text{EW}-\text{AC}}}{V_{\text{EW}-\text{AC}} \cdot \Delta V_{\text{HEHT}}}$ | Breathing compensation on $V_{EW-AC}^{(31)}$                                   | (25)(26)<br>VHEHT>VRefO<br>V <sub>HEHT</sub> (min)≤V <sub>HEHT</sub> ≤VRefO                    |       | 0<br>1.75           |      | %/V<br>%/V  |

Note 19: KEYST at medium (neutral) value.

Note 20: TCC at medium (neutral) value.

**Note 21:** *BCC* at medium (neutral) value.

Note 22: PCC at minimum value.

Note 23: VPOS at medium (neutral) value.

**Note 24:** *HSIZE* at minimum value.

Note 25: Defined as difference of (voltage at  $t_{VR}$ =0) minus (voltage at  $t_{VR}$ =1/2  $T_{VR}$ ).

Note 26: Defined as difference of (voltage at  $t_{VR}=T_{VR}$ ) minus (voltage at  $t_{VR}=1/2$   $T_{VR}$ ).

**Note 27:** *VSIZE* at maximum value.

Note 28: Difference (voltage at  $t_{VR}$ =0) minus (voltage at  $t_{VR}$ =T<sub>VR</sub>).

Note 29: Ratio "A/B" of parabola component voltage at  $t_{VR}$ =0 versus parabola component voltage at  $t_{VR}$ =T<sub>VR</sub>.

Note 30: V<sub>HEHT</sub>>VRefO, V<sub>VEHT</sub>>VRefO

Note 31: V<sub>EW-AC</sub> is sum of all components other than V<sub>EW-DC</sub> (contribution of PCC, keystone correction and corner corrections).

**Note 32:** More precisely tracking with voltage on HPLL1F pin which itself depends on frequency at a rate given by external components on PLL1 pins. V<sub>EW</sub>[fmax] is the value at condition V<sub>HO</sub>>V<sub>HOThrfr</sub>.

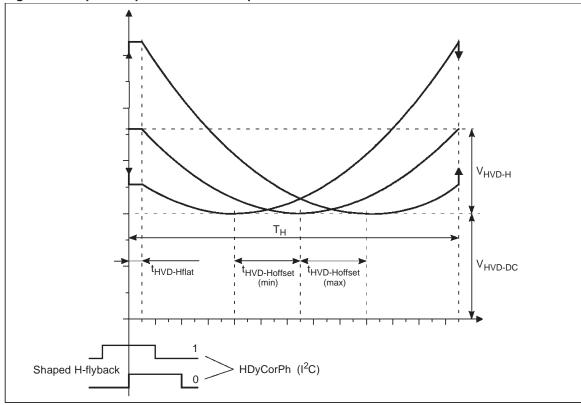

# 6.7 - DYNAMIC CORRECTION OUTPUTS SECTION

$V_{CC}$  = 12V,  $T_{amb}$  = 25°C

| Symbol                                                      | Parameter                                                                                  | Test Conditions                                                                                                                                                                   |      | Units                       |   |             |  |

|-------------------------------------------------------------|--------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|-----------------------------|---|-------------|--|

| Symbol                                                      | i didificter                                                                               | Test conditions                                                                                                                                                                   | Min. | Min. Typ. Max.              |   |             |  |

| Horizontal Dynamic                                          | Correction output HDyCor                                                                   |                                                                                                                                                                                   |      |                             |   |             |  |

| I <sub>HDyCor</sub>                                         | Current delivered by HDyCor<br>output                                                      |                                                                                                                                                                                   | -2   |                             | 0 | mA          |  |

| V <sub>HD-DC</sub>                                          | DC component of the drive signal<br>on HDyCor output                                       | R <sub>L(HDyCor)</sub> =10kΩ                                                                                                                                                      |      | 2.1                         |   | V           |  |

| $\frac{\Delta V_{HD-DC}}{V_{HD-DC} \cdot \Delta T}$         | Temperature drift of DC component<br>of the drive signal on HDyCor                         | (18)                                                                                                                                                                              |      | 200                         |   | ppm/°C      |  |

| V <sub>HD-H</sub>                                           | Amplitude of H-parabola compo-<br>nent of the drive signal on HDyCor<br>output             | (33)(34)<br>HDyCorTr Off<br><i>HDC-AMP</i> (Sad04):<br>x0000000b<br>x1000000b<br>x1111111b                                                                                        |      | 3.7<br>1.5<br>0.9           |   | V<br>V<br>V |  |

| V <sub>HD-H</sub> [TrHSOn]<br>V <sub>HD-H</sub> [TrHSOff]   | Impact of horizontal size adjust-<br>ment on HDyCor parabola<br>(tracking) <sup>(35)</sup> | V <sub>HEHT</sub> constant<br><i>HSIZE</i> (Sad10h):<br>00000000b<br>11111111b                                                                                                    |      | (1.34) <sup>2</sup><br>1    |   |             |  |

| V <sub>HD-H</sub> [TrEHTOn]<br>V <sub>HD-H</sub> [TrEHTOff] | Impact of voltage on HEHTIn input<br>on HDyCor parabola <sup>(36)</sup>                    | <i>HSIZE</i> constant<br>V <sub>HEHT</sub> >VRefO<br>V <sub>HEHT</sub> =VRefO-4V                                                                                                  |      | 1<br>(1.07) <sup>2</sup>    |   |             |  |

| $t_{HD-Hoffset}/T_H$                                        | Offset (phase) of parabola on HDy-<br>Cor output <sup>(38)</sup>                           | HDC-SYM (Sad05):<br>x0000000b<br>x1000000b <sup>(39)</sup><br>x1111111b                                                                                                           |      | +24.5<br>0<br>-24.5         |   | %<br>%<br>% |  |

| <sup>t</sup> HD-Hflat                                       | Duration of the flat part at the start of parabola on HDyCor output <sup>(38)</sup>        | f <sub>HO</sub> =31kHz                                                                                                                                                            |      | 500                         |   | ns          |  |

| Vertical Dynamic Co                                         | rrection output VDyCor                                                                     |                                                                                                                                                                                   |      |                             |   |             |  |

| I <sub>VDyCor</sub>                                         | Current delivered by VDyCor out-<br>put                                                    |                                                                                                                                                                                   | -1.5 |                             | 0 | mA          |  |

| V <sub>VD-DC</sub>                                          | DC component of the drive signal<br>on VDyCor output                                       | $R_{L(VDyCor)}=10k\Omega$                                                                                                                                                         |      | 4                           |   | V           |  |

| V <sub>VD-V</sub>                                           | Amplitude of V-parabola on VDy-<br>Cor output <sup>(40)</sup>                              | (23)<br><i>VSIZE</i> at medium<br><i>VDC-AMP</i> (Sad15h):<br>x0000000b<br>x1000000b<br>x1111111b<br><i>VDC-AMP</i> at maximum<br><i>VSIZE</i> (Sad07):<br>x0000000b<br>x1111111b |      | 0<br>0.5<br>1<br>0.6<br>1.6 |   |             |  |

| $\frac{V_{VD-V}[t_{vr}=0]}{V_{VD-V}[t_{vr}=T_{VR}]}$        | Tracking of V-parabola on VDyCor<br>output with vertical position <sup>(37)</sup>          | VDC-AMP at maximum<br>VPOS (Sad08):<br>x0000000b<br>x1111111b                                                                                                                     |      | 0.52<br>1.92                |   |             |  |

Note 33: HDC-AMP at minimum.

Note 34: HDC-SYM at medium.

- Note 35: Ratio of the amplitude at HDyCorTr=1 to the amplitude at HDyCorTr=0 (refer to chapter "I<sup>2</sup>C Bus control register map") as a quadratic function of horizontal size adjustment.

- Note 36: Ratio of the amplitude at HDyCorTr=1 to the amplitude at HDyCorTr=0 (refer to chapter "I<sup>2</sup>C Bus control register map") as a quadratic function of V<sub>HEHT</sub>.

- Note 37: Ratio of parabola voltage at  $t_{VR}$ =0 versus parabola voltage at  $t_{VR}$ =T<sub>VR</sub>.

Note 38: Refer to Figure 14.

Note 39: Taken for reference at given position of HDyCorPh flag.

Note 40: Unsigned value. Polarity selection by VDyCorPol I<sup>2</sup>C Bus bit. Refer to section I<sup>2</sup>C Bus control register map.

# 6.8 - DC/DC CONTROLLER SECTION

$V_{CC}$  = 12V,  $T_{amb}$  = 25°C

| Symbol                                 | Parameter                                                                               | Test Conditions                                                                      | Value                |                    |                                 | Units       |  |

|----------------------------------------|-----------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------|----------------------|--------------------|---------------------------------|-------------|--|

|                                        |                                                                                         |                                                                                      | Min. Typ. Max.       |                    | Max.                            |             |  |

| R <sub>B+FB</sub>                      | Ext. resistance applied between<br>BComp output and BRegIn input                        |                                                                                      | 5                    |                    |                                 | kΩ          |  |

| A <sub>OLG</sub>                       | Open loop gain of error amplifier<br>on BRegln input                                    | Low frequency <sup>(18)</sup>                                                        |                      | 100                |                                 | dB          |  |

| fugbw                                  | Unity gain bandwidth of error am-<br>plifier on BRegIn input                            | (18)                                                                                 |                      | 6                  |                                 | MHz         |  |

| I <sub>RI</sub>                        | Bias current delivered by regula-<br>tion input BRegIn                                  |                                                                                      |                      | -0.2               |                                 | μΑ          |  |

| I <sub>BComp</sub>                     | Output current capability of BComp output.                                              | HBOutEn = "Enable"<br>HBOutEn = "Disable" <sup>(41)</sup>                            | -0.5                 | 0.5                | 2.0                             | mA<br>mA    |  |

| A <sub>BISense</sub>                   | Voltage gain on BISense input                                                           |                                                                                      |                      | 3                  |                                 |             |  |

| V <sub>ThrBlsCurr</sub>                | Threshold voltage on BISense input<br>corresponding to current limitation               |                                                                                      | 1.98                 | 2.1                | 2.22                            | V           |  |

| I <sub>BISense</sub>                   | Input current sourced by BISense input                                                  |                                                                                      |                      | -1                 |                                 | μA          |  |

| t <sub>BOn</sub>                       | Conduction time of the power transistor                                                 |                                                                                      |                      |                    | T <sub>H</sub> - t <sub>h</sub> | HD-Hflat    |  |

| I <sub>BOut</sub>                      | Output current capability of BOut out-<br>put                                           |                                                                                      | 0                    |                    | 10                              | mA          |  |

| V <sub>BOSat</sub>                     | Saturation voltage of the internal output transistor on BOut                            | I <sub>BOut</sub> =10mA                                                              |                      | 0.25               | 0.4                             | V           |  |

| V <sub>BReg</sub>                      | Regulation reference for BRegIn volt-<br>age <sup>(42)</sup>                            | V <sub>RefO</sub> =8V<br><i>BREF</i> (Sad03):<br>x0000000b<br>x1000000b<br>x1111111b | 3.65<br>4.65<br>5.65 | 3.85<br>4.9<br>5.9 | 4.05<br>5.15<br>6.15            | ><br>><br>> |  |

| t <sub>BTrigDel</sub> / T <sub>H</sub> | Delay of BOut "Off-to-On" edge after middle of flyback pulse, as part of $T_{H}^{(43)}$ | BOutPh = "0"                                                                         |                      | 16                 |                                 | %           |  |

Note 41: A current sink is provided by the BComp output while BOut is disabled:

Note 42: Internal reference related to  $V_{RefO}$ . The same values to be found on pin BRegIn, while regulation loop is stabilized.

Note 43: Only applies to configuration specified in "Test conditions" column, i.e. synchronization of BOut "Off-to-On" edge with horizontal flyback signal. Refer to chapter "DC/DC controller" for more details.

# 6.9 - MISCELLANEOUS

$V_{CC}$  = 12V,  $T_{amb}$  = 25°C

| Symbol                  | Parameter                                                                   | Test Con                                                      |         | Units      |                 |            |        |

|-------------------------|-----------------------------------------------------------------------------|---------------------------------------------------------------|---------|------------|-----------------|------------|--------|

| Symbol                  | i arameter                                                                  | 1631 0011                                                     |         |            |                 | Max.       |        |

| Vertical blankir        | ng and horizontal lock indication comp                                      |                                                               | ILckVBk |            |                 |            |        |

| I <sub>SinkLckBk</sub>  | Sink current to HLckVBk pin                                                 | Note (44)                                                     |         |            | 100             |            | μΑ     |

|                         |                                                                             | V.blank                                                       | H.lock  |            |                 |            |        |

|                         |                                                                             | No                                                            | Yes     |            | 0.1             |            | V      |

| V <sub>OLckBk</sub>     | Output voltage on HLckVBk output                                            | Yes                                                           | Yes     |            | 1.1             |            | V      |

|                         |                                                                             | No                                                            | No      |            | 5               |            | V      |

|                         |                                                                             | Yes                                                           | No      |            | 6               |            | V      |

| Horizontal moi          | ré canceller                                                                |                                                               |         |            | 1               | 1          | I      |

| $\Delta T_{H(H-moire)}$ |                                                                             | HMOIRE (Sac                                                   | 102):   |            |                 |            |        |

| T <sub>H</sub>          | Modulation of T <sub>H</sub> by H. moiré function                           | x0000000b<br>x1111111b                                        |         |            | 0.02            |            | %<br>% |

| Vertical moiré d        | <br>canceller                                                               |                                                               |         |            | 0.02            |            |        |

|                         | Amplitude of modulation of V-drive sig-                                     | VMOIRE (Sad                                                   | 10Bh):  | 1          |                 |            |        |

| V <sub>V-moiré</sub>    | nal on VOut pin by vertical moiré.                                          | x000000b                                                      |         |            | 0               |            | mV     |

| Protection fund         |                                                                             | x1111111b                                                     |         | <u> </u>   | 3               |            | mV     |

|                         | Input threshold on XRay input <sup>(45)</sup>                               | [                                                             |         | 7.65       | 7.9             | 8.2        | l v    |

| V <sub>ThrXRay</sub>    | Delay time between XRay detection                                           |                                                               |         | 7.05       | 7.9             | 0.2        | V      |

| t <sub>XRayDelay</sub>  | event and protection action                                                 |                                                               |         |            | 2T <sub>H</sub> |            |        |

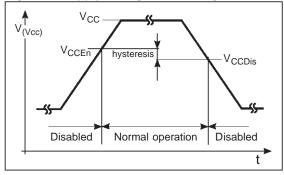

| V <sub>CCEn</sub>       | $V_{CC}$ value for start of operation at $V_{CC}$ ramp-up $^{(46)}$         |                                                               |         |            | 8.5             |            | V      |

| V <sub>CCDis</sub>      | $V_{CC}$ value for stop of operation at $V_{CC}$ ramp-down^{(46)}           |                                                               |         |            | 6.5             |            | V      |

| Control voltage         | es on HPosF pin for Soft start/stop ope                                     | ration <sup>(18)(47)</sup>                                    |         |            |                 |            |        |

| V <sub>HOn</sub>        | Threshold for start/stop of H-drive sig-<br>nal                             |                                                               |         |            | 1               |            | V      |

| V <sub>BOn</sub>        | Threshold for start/stop of B-drive sig-<br>nal                             |                                                               |         |            | 1.7             |            | V      |

| V <sub>HBNorm f</sub>   | Threshold for full operational duty cycle of H-drive and B-drive signals    |                                                               |         |            | 2.4             |            |        |

| V <sub>HPosF</sub>      | Voltage on HPosF pin as function of ad-<br>justment of <i>HPOS</i> register | Normal operat<br><i>HPOS</i> (Sad01<br>00000000b<br>11111111b |         | 3.8<br>2.6 | 4.0<br>2.8      | 4.2<br>3.0 | V<br>V |

Note 44: Current sunk by the pin if the external voltage is higher than one the circuit tries to force.

Note 45: The threshold is equal to actual  $V_{\text{RefO}}.$

Note 46: In the regions of  $V_{CC}$  where the device's operation is disabled, the H-drive, V-drive and B+-drive signals on

HOut, VOut and BOut pins, resp., are inhibited, the I<sup>2</sup>C Bus does not accept any data and the XRayAlarm flag is reset. Also see Figure 16

Note 47: See Figure 10

# 7 - TYPICAL OUTPUT WAVEFORMS Note (<sup>48</sup>)

| Function             | Sad | Pin     | Byte               | Waveform                                                                                           | Effect on Screen                                                                  |  |

|----------------------|-----|---------|--------------------|----------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------|--|

| Vertical Size        | 07  | VOut    | ×0000000           | V <sub>amp(min)</sub><br>★                                                                         |                                                                                   |  |

| Venical Size         | 07  | vOut    | x1111111           | Vamp(max)<br>Vmid(VOut)                                                                            |                                                                                   |  |

|                      |     |         | x0000000           |                                                                                                    |                                                                                   |  |

| Vertical<br>Position | 08  | VOut    | x1000000           | V <sub>mid(VOut)</sub> -3.5V                                                                       |                                                                                   |  |

|                      |     |         | x1111111           | V <sub>mid(VOut)</sub> 3.5V                                                                        |                                                                                   |  |

|                      |     |         | x0000000:<br>Null  | V <sub>VOamp</sub>                                                                                 |                                                                                   |  |

| S-correction         | 09  | 09 VOut | x11 <sup>-</sup>   | x1111111:<br>Max.                                                                                  | V <sub>VOS-cor</sub><br>V <sub>VOamp</sub><br>0 1/4 VR 3/4 VR TVR t <sub>VR</sub> |  |

|                      |     |         | x0000000           | V <sub>VOamp</sub><br>0 1/2 <sub>VR</sub> T <sub>VR</sub> t <sub>VR</sub>                          |                                                                                   |  |

| C-correction         | 0A  | 0A VOut | x1000000 :<br>Null | V <sub>VOamp</sub>                                                                                 |                                                                                   |  |

|                      |     |         | x1111111           | V <sub>VOamp</sub><br>V <sub>VOC-cor</sub><br>0 1/2T <sub>VR</sub> T <sub>VR</sub> t <sub>VR</sub> |                                                                                   |  |