# **OKI** Semiconductor

# MSM7702-01/02/03

Single Rail CODEC

#### **GENERAL DESCRIPTION**

The MSM7702 is a single-channel CODEC CMOS IC for voice signals ranging from 300 to 3400 Hz with filters for A/D and D/A conversion.

Designed especially for a single-power supply and low-power applications, the device is optimized for telephone terminals in digital wireless systems or ISDN systems.

The MSM7702 utilizes low-voltage operational amplifiers (Op-amps) to provide low-power consumption.

The device uses the same transmission clocks as those used in the MSM7508B and MSM7509B. The analog output signal can directly drive a piezoelectric type handset receiver.

#### **FEATURES**

- Single power supply: +2.7 V to +3.8 V

- Low power consumption

Operating mode: 15 mW Typ.  $V_{DD} = 3 V$ Power save mode: 3.6 mW Typ.  $V_{DD} = 3 V$ Power down mode: 0.05 mW Typ.  $V_{DD} = 3 V$

• ITU-T Companding law

MSM7702-01:  $\mu$ /A-law pin selectable

MSM7702-02: μ-law MSM7702-03: A-law

- Built-in PLL eliminates a master clock

- Serial data rate: 64/128/256/512/1024/2048 kHz

96/192/384/768/1536/1544/200 kHz

- Adjustable transmit gain

- Built-in reference voltage supply

- Analog output can directly drive a load equivalent to 1.2 k $\Omega$

- Pin-for-pin compatible with the MSM7578 and MSM7579

- Package options:

24-pin plastic SOP (SOP24-P-430-1.27-K) (Product name: MSM7702-01GS-K)

(Product name : MSM7702-02GS-K) (Product name : MSM7702-03GS-K)

This version: Aug. 1998

Previous version: Nov. 1996

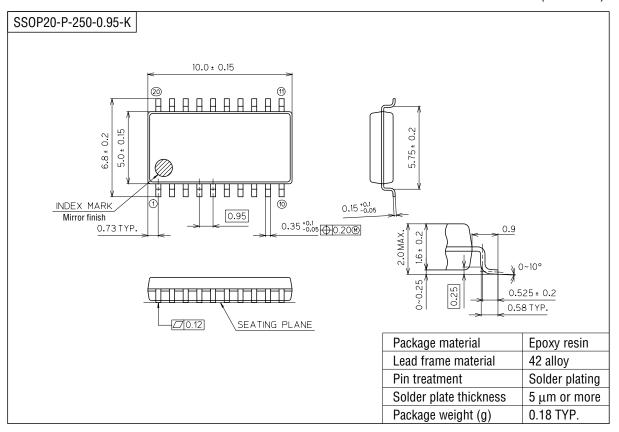

20-pin plastic SSOP (SSOP20-P-250-0.95-K) (Product name: MSM7702-01MS-K)

(Product name : MSM7702-02MS-K) (Product name : MSM7702-03MS-K)

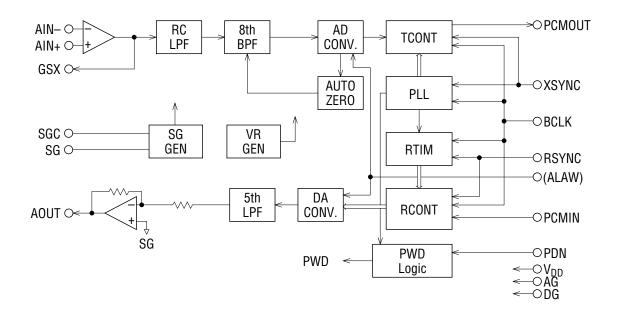

# **BLOCK DIAGRAM**

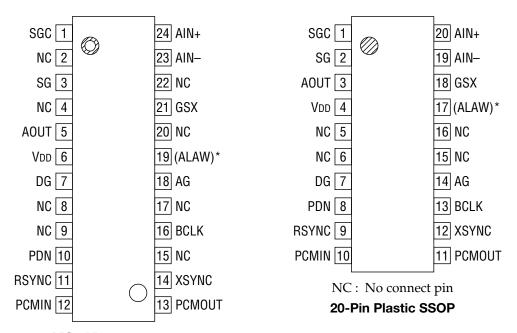

# **PIN CONFIGURATION (TOP VIEW)**

NC : No connect pin **24-Pin Plastic SOP**

<sup>\*</sup> The ALAW pin is only applied to the MSM7702-01GS-K/MSM7702-01MS-K.

#### PIN AND FUNCTIONAL DESCRIPTIONS

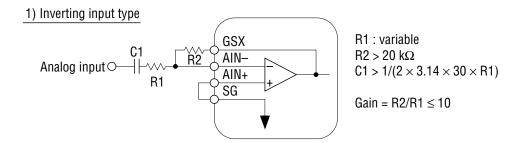

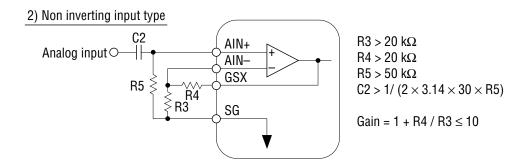

#### AIN+, AIN-, GSX

Transmit analog input and transmit level adjustment.

AIN+ is a non-inverting input to the op-amp; AIN- is an inverting input to the op-amp; GSX is connected to the output of the op-amp and is used to adjust the level, as shown below. When not using AIN- and AIN+, connect AIN- to GSX and AIN+ to SG. During power saving and power down modes, the GSX output is at AG voltage.

#### AG

Analog signal ground.

#### **AOUT**

Analog output.

The output signal has a maximum amplitude of 2.0  $V_{PP}$  above and below the signal ground voltage ( $V_{DD}/2$ ).

The output load resistance is a minimum of 1.2 k $\Omega$ .

During power saving or power down mode, the output of AOUT is at the voltage level of the signal ground.

#### $V_{DD}$

Power supply for +2.7 V to +3.8 V. (Typically 3.0 V)

#### **PCMIN**

PCM signal input.

A serial PCM signal input to this pin is converted to an analog signal in synchronization with the RSYNC signal and BCLK signal.

The data rate of the PCM signal is equal to the frequency of the BCLK signal.

The PCM signal is shifted at a falling edge of the BCLK signal and latched into the internal register when shifted by eight bits.

The start of the PCM data (MSD) is identified at the rising edge of RSYNC.

#### **BCLK**

Shift clock signal input for the PCMIN and PCMOUT signal.

The frequency, equal to the data rate, is 64, 96, 128, 192, 256, 384, 512, 768, 1024, 1536, 1544, 2048, or 200 kHz. Setting this signal to logic "1" or "0" drives both transmit and receive circuits to the power saving state.

#### **RSYNC**

Receive synchronizing signal input.

Eight required bits are selected from serial PCM signals on the PCMIN pin by the receive synchronizing signal.

Signals in the receive section are synchronized by this synchronizing signal. This signal must be synchronized in phase with the BCLK. The frequency should be 8 kHz ±50 ppm to guarantee the AC characteristics which are mainly the frequency characteristics of the receive section.

However, if the frequency characteristic of an applied system is not specified exactly, this device can operate in the range of  $8\,\mathrm{kHz}\pm2\,\mathrm{kHz}$ , but the electrical characteristics in this specification are not guaranteed.

#### **XSYNC**

Transmit synchronizing signal input.

The PCM output signal from the PCMOUT pin is output in synchronization with this transmit synchronizing signal. This synchronizing signal triggers the PLL and synchronizes all timing signals of the transmit section.

This synchronizing signal must be synchronized in phase with BCLK.

The frequency should be 8 kHz ±50 ppm to guarantee the AC characteristics which are mainly the frequency characteristics of the transmit section.

However, if the frequency characteristic of an applied system is not specified exactly, this device can operate in the range of 8 kHz ±2 kHz, but the electrical characteristics in this specification are not guaranteed.

Setting this signal to logic "1" or "0" drives both transmit and receive circuits to the power saving state.

#### DG

Ground for the digital signal circuits.

This ground is separate from the analog signal ground. The DG pin must be connected to the AG pin on the printed circuit board to make a common analog ground.

#### **PDN**

Power down control signal.

A logic "0" level drives both transmit and receive circuits to a power down state.

#### **PCMOUT**

PCM signal output.

The PCM output signal is output from MSD in a sequential order, synchronizing with the rising edge of the BCLK signal.

MSD may be output at the rising edge of the XSYNC signal, based on the timing between BCLK and XSYNC.

This pin is in a high impedance state except during 8-bit PCM output. It is also in a high impedance state during power saving or power down.

A pull-up resistor must be connected to this pin because its output is configured as an open drain. This device is compatible with the ITU-T recommendation on coding law and output coding format.

The MSM7702-03 (A-law) outputs the character signal, inverting the even bits.

| Innut/Outnut Lavel | PCMIN/PCMOUT       |                    |  |  |  |  |  |  |  |

|--------------------|--------------------|--------------------|--|--|--|--|--|--|--|

| Input/Output Level | MSM7702-02 (μ-law) | MSM7702-03 (A-law) |  |  |  |  |  |  |  |

|                    | MSD                | MSD                |  |  |  |  |  |  |  |

| +Full scale        | 1 0 0 0 0 0 0 0    | 1 0 1 0 1 0 1 0    |  |  |  |  |  |  |  |

| +0                 | 1 1 1 1 1 1 1 1    | 1 1 0 1 0 1 0 1    |  |  |  |  |  |  |  |

| -0                 | 0 1 1 1 1 1 1 1    | 0 1 0 1 0 1 0 1    |  |  |  |  |  |  |  |

| –Full scale        | 0 0 0 0 0 0 0 0    | 0 0 1 0 1 0 1 0    |  |  |  |  |  |  |  |

#### SG

Signal ground voltage output.

The output voltage is 1/2 of the power supply voltage.

The output drive current capability is  $\pm 200 \,\mu\text{A}$ .

This pin provides the SG level for CODEC peripherals.

This output voltage level is undefined during power saving or power down mode.

## **SGC**

Used to generate the signal ground voltage level by connecting a bypass capacitor. Connect a  $0.1\,\mu F$  capacitor with excellent high frequency characteristics between the AG pin and the SGC pin.

#### **ALAW**

Control signal input for the companding law selection.

Provides only for the MSM7702-01GS-K/7702-01MS-K. The CODEC will operate in the  $\mu$ -law when this pin is at a logic "0" level and the CODEC will operate in the A-law when this pin is at a logic "1" level. The CODEC operates in the  $\mu$ -law if the pin is left open, since this pin is internally pulled down.

# **ABSOLUTE MAXIMUM RATINGS**

| Parameter             | Symbol           | Condition    | Rating                        | Unit |

|-----------------------|------------------|--------------|-------------------------------|------|

| Power Supply Voltage  | V <sub>DD</sub>  | <del>_</del> | 0 to 7                        | V    |

| Analog Input Voltage  | V <sub>AIN</sub> | _            | -0.3 to V <sub>DD</sub> + 0.3 | V    |

| Digital Input Voltage | V <sub>DIN</sub> | _            | -0.3 to V <sub>DD</sub> + 0.3 | V    |

| Storage Temperature   | T <sub>STG</sub> | <del>_</del> | -55 to +150                   | °C   |

## RECOMMENDED OPERATING CONDITIONS

| Parameter                        | Symbol                                | Condition                                                                 | Min.                 | Тур.        | Max.                 | Unit      |

|----------------------------------|---------------------------------------|---------------------------------------------------------------------------|----------------------|-------------|----------------------|-----------|

| Power Supply Voltage             | $V_{DD}$                              | Voltage must be fixed                                                     | 2.7                  | 3.0         | 3.8                  | V         |

| Operating Temperature            | Ta                                    | _                                                                         | -30                  | +25         | +85                  | °C        |

| Analog Input Voltage             | V <sub>AIN</sub>                      | Connect AIN- and GSX                                                      |                      | _           | 1.4                  | $V_{PP}$  |

| Input High Voltage               | V <sub>IH</sub>                       | XSYNC, RSYNC, BCLK,                                                       | $0.45 \times V_{DD}$ | -           | V <sub>DD</sub>      | V         |

| Input Low Voltage                | V <sub>IL</sub>                       | PCMIN, PDN, ALAW                                                          | 0                    | _           | $0.16 \times V_{DD}$ | V         |

|                                  |                                       |                                                                           | 64, 128, 2           | 256, 512, 1 | 024,                 |           |

| Clock Frequency                  | F <sub>C</sub>                        | BCLK                                                                      | 2048, 96,            | 192, 384,   | 768,                 | kHz       |

|                                  |                                       |                                                                           | 1536, 154            |             |                      |           |

| Sync Pulse Frequency             | F <sub>S</sub>                        | XSYNC, RSYNC                                                              | 6.0                  | 8.0         | 10.0                 | kHz       |

| Clock Duty Ratio                 | D <sub>C</sub>                        | BCLK                                                                      | 40                   | 50          | 60                   | %         |

| Digital Input Rise Time          | t <sub>lr</sub>                       | XSYNC, RSYNC, BCLK,                                                       | _                    | _           | 50                   | ns        |

| Digital Input Fall Time          | t <sub>lf</sub>                       | PCMIN, PDN, ALAW                                                          | _                    | _           | 50                   | ns        |

| Transmit Cune Dules Catting Time | t <sub>XS</sub>                       | BCLK→XSYNC, See Timing Diagram                                            | 100                  |             | _                    | ns        |

| Transmit Sync Pulse Setting Time | t <sub>SX</sub>                       | $\textbf{XSYNC} {\rightarrow} \textbf{BCLK}, \textbf{See Timing Diagram}$ | 100                  |             | _                    | ns        |

| Receive Sync Pulse Setting Time  | t <sub>RS</sub>                       | BCLK→RSYNC, See Timing Diagram                                            | 100                  |             | _                    | ns        |

| neceive Sylic Pulse Setting Time | t <sub>SR</sub>                       | RSYNC→BCLK, See Timing Diagram                                            | 100                  | _           | _                    | ns        |

| Sync Pulse Width                 | tws                                   | XSYNC, RSYNC                                                              | 1 BCLK               |             | 100                  | μS        |

| PCMIN Set-up Time                | t <sub>DS</sub>                       | _                                                                         | 100                  |             | _                    | ns        |

| PCMIN Hold Time                  | t <sub>DH</sub>                       | _                                                                         | 100                  | _           | _                    | ns        |

| Digital Output Load              | R <sub>DL</sub>                       | Pull-up resistor                                                          | 0.5                  | _           | _                    | $k\Omega$ |

| Digital Output Load              | C <sub>DL</sub>                       | <u> </u>                                                                  |                      |             | 100                  | pF        |

| Analog Input Allowable DC Offset | \ \ \ \ \ \ \ \ \ \ \ \ \ \ \ \ \ \ \ | Transmit gain stage, Gain = 1                                             | -100                 |             | +100                 | mV        |

| Analog Input Allowable DC Offset | V <sub>off</sub>                      | Transmit gain stage, Gain = 10                                            | -10                  |             | +10                  | mV        |

| Allowable Jitter Width           | _                                     | XSYNC, RSYNC, BCLK                                                        |                      | _           | 1                    | μS        |

## **ELECTRICAL CHARACTERISTICS**

## **DC** and Digital Interface Characteristics

$(V_{DD} = 2.7 \text{ V to } 3.8 \text{ V}, \text{ Ta} = -30^{\circ}\text{C to } +85^{\circ}\text{C})$

|                                  | 1.               | (- 55                             |          | , , , , , , , , , , , , , , , , , , , |                 | <del></del> |

|----------------------------------|------------------|-----------------------------------|----------|---------------------------------------|-----------------|-------------|

| Parameter                        | Symbol           | Condition                         | Min.     | Тур.                                  | Max.            | Unit        |

|                                  | I <sub>DD1</sub> | Operating mode, No signal         |          | 5                                     | 9               | mA          |

| Power Supply Current             | I <sub>DD2</sub> | Power-down mode, PDN = 0          |          | 0.01                                  | 0.05            | mA          |

| Fower Supply Current             | 1                | Power-save mode, PDN = 1,         |          | 1.0                                   | 2.0             | m A         |

|                                  | I <sub>DD3</sub> | $XSYNC \to OFF$                   |          | 1.2                                   | 3.0             | mA          |

| Input High Voltage               |                  |                                   | 0.45×    |                                       | V <sub>DD</sub> | V           |

| Input High Voltage               | V <sub>IH</sub>  | _                                 | $V_{DD}$ | _                                     |                 | V           |

|                                  | V <sub>IL</sub>  |                                   | 0.0      | _                                     | 0.16×           | V           |

| Input Low Voltage                |                  | _                                 |          |                                       | $V_{DD}$        | V           |

| High Level Input Leakage Current | I <sub>IH</sub>  | _                                 | _        | _                                     | 2.0             | μΑ          |

| Low Level Input Leakage Current  | I <sub>IL</sub>  | _                                 |          | _                                     | 0.5             | μΑ          |

| Digital Output Low Voltage       | V <sub>OL</sub>  | Pull-up resistance $> 500 \Omega$ | 0.0      | 0.2                                   | 0.4             | V           |

| Digital Output Leakage Current   | I <sub>0</sub>   | PCMOUT                            | _        | _                                     | 10              | μΑ          |

| Input Capacitance                | C <sub>IN</sub>  | _                                 |          | 5                                     |                 | pF          |

| Analog Input Resistance          | R <sub>IN</sub>  | AIN+, AIN-                        | _        | 10                                    | _               | MΩ          |

## **Transmit Analog Interface Characteristics**

$(V_{DD} = 2.7 \text{ V to } 3.8 \text{ V}, \text{ Ta} = -30^{\circ}\text{C to } +85^{\circ}\text{C})$

| Parameter               | Symbol            | Condition              | Min. | Тур. | Max. | Unit |

|-------------------------|-------------------|------------------------|------|------|------|------|

| Input Resistance        | R <sub>INX</sub>  | AIN+, AIN-             | 10   | _    |      | MΩ   |

| Output Load Resistance  | R <sub>LGX</sub>  | GSX with respect to SG | 20   | _    | _    | kΩ   |

| Output Load Capacitance | C <sub>LGX</sub>  |                        | _    | _    | 30   | pF   |

| Output Amplitude        | V <sub>OGX</sub>  |                        | -0.7 | _    | +0.7 | ٧    |

| Offset Voltage          | V <sub>OSGX</sub> | Gain = 1               | -20  | _    | +20  | mV   |

## **Receive Analog Interface Characteristics**

$(V_{DD} = 2.7 \text{ V to } 3.8 \text{ V}, Ta = -30^{\circ}\text{C to } +85^{\circ}\text{C})$

| Parameter               | Symbol           | Condition               | Min. | Тур. | Max. | Unit |

|-------------------------|------------------|-------------------------|------|------|------|------|

| Output Load Resistance  | R <sub>LAO</sub> | AOUT with respect to SG | 1.2  | _    | _    | kΩ   |

| Output Load Capacitance | C <sub>LAO</sub> | AOUT with respect to SG | _    | _    | 50   | pF   |

| Output Amplitude        | V <sub>OAO</sub> | AOUT with respect to SG | -1.0 | _    | +1.0 | V    |

| Offset Voltage          | Vosao            | AOUT with respect to SG | -100 | _    | +100 | mV   |

## **AC Characteristics**

$(V_{DD} = 2.7 \text{ V to } 3.8 \text{ V}, Ta = -30^{\circ}\text{C to } +85^{\circ}\text{C})$

| Parameter                           | Symbol  | Freq.<br>(Hz) | Level<br>(dBm0) | Conditio | Min.  | Тур.      | Max.  | Unit |

|-------------------------------------|---------|---------------|-----------------|----------|-------|-----------|-------|------|

|                                     | Loss T1 | 60            |                 |          | 20    | 26        | _     | dB   |

|                                     | Loss T2 | 300           |                 |          | -0.15 | +0.1      | +0.20 | dB   |

| Transmit Francisco Decreases        | Loss T3 | 1020          |                 |          |       | Reference |       | dB   |

| Transmit Frequency Response         | Loss T4 | 2020          | 0               |          | -0.15 | -0.04     | +0.20 | dB   |

|                                     | Loss T5 | 3000          |                 |          | -0.15 | +0.13     | +0.20 | dB   |

|                                     | Loss T6 | 3400          |                 |          | 0     | 0.5       | 0.80  | dB   |

|                                     | Loss R1 | 300           |                 |          | -0.15 | -0.04     | +0.20 | dB   |

|                                     | Loss R2 | 1020          |                 |          |       | Reference |       | dB   |

| Receive Frequency Response          | Loss R3 | 2020          | 0               |          | -0.15 | +0.02     | +0.20 | dB   |

|                                     | Loss R4 | 3000          |                 |          | -0.15 | +0.10     | +0.20 | dB   |

|                                     | Loss R5 | 3400          |                 |          | 0.0   | 0.47      | 0.80  | dB   |

|                                     | SD T1   |               | 3               |          | 35    | 43        | _     |      |

|                                     | SD T2   |               | 0               |          | 35    | 41        | _     |      |

|                                     | SD T3   |               | -30             | *1       | 35    | 37        | _     |      |

| Transmit Signal to Distortion Ratio | SD T4   | 1020          | -40             | *2       | 00    | 29.5      |       | dB   |

|                                     |         |               |                 |          | 28    | 29        | _     |      |

|                                     | SD T5   |               | -45             | *2       | 00    | 25        |       |      |

|                                     |         |               |                 |          | 23    | 24        |       |      |

|                                     | SD R1   |               | 3               |          | 36    | 43        | _     |      |

|                                     | SD R2   |               | 0               |          | 36    | 41        | _     |      |

|                                     | SD R3   |               | -30             | *1       | 36    | 40        | _     |      |

| Receive Signal to Distortion Ratio  | CD D4   | 1020          | -40             | *2       | 30    | 33.5      |       | dB   |

|                                     | SD R4   |               |                 |          | 29    | 32        |       |      |

|                                     | CD DE   |               | 45              | *2       | 25    | 30        |       |      |

|                                     | SD R5   |               | <del>-45</del>  |          | 24    | 27        |       |      |

|                                     | GT T1   |               | 3               |          | -0.3  | 0         | +0.3  |      |

|                                     | GT T2   |               | -10             |          |       | Reference |       |      |

| Transmit Gain Tracking              | GT T3   | 1020          | -40             |          | -0.3  | +0.1      | +0.3  | dB   |

|                                     | GT T4   |               | -50             |          | -0.5  | -0.03     | +0.6  | 1    |

|                                     | GT T5   |               | -55             |          | -1.2  | 0         | +1.2  |      |

|                                     | GT R1   |               | 3               |          | -0.3  | 0.0       | +0.3  |      |

|                                     | GT R2   |               | -10             |          |       | Reference |       | dB   |

| Receive Gain Tracking               | GT R3   | 1020          | -40             |          | -0.3  | +0.11     | +0.3  |      |

|                                     | GT R4   |               | -50             |          | -0.6  | +0.22     | +0.6  |      |

|                                     | GT R5   |               | -55             |          | -1.2  | +0.15     | +1.2  |      |

<sup>\*1</sup> Psophometric filter is used

<sup>\*2</sup> Upper is specified for the  $\mu$ -law, lower for the A-law

# **AC Characteristics (Continued)**

$(V_{DD} = 2.7 \text{ V to } 3.8 \text{ V}, Ta = -30^{\circ}\text{C to } +85^{\circ}\text{C})$

| _                                                      |         | Frog          | Lovel           | 1                                     |       | _     |       |        |

|--------------------------------------------------------|---------|---------------|-----------------|---------------------------------------|-------|-------|-------|--------|

| Parameter                                              | Symbol  | Freq.<br>(Hz) | Level<br>(dBm0) | Condition                             | Min.  | Тур.  | Max.  | Unit   |

| Idle Channel Noise                                     | Nidle T | <u> </u>      | _               | AIN = SG<br>*1                        | _     | -70.5 | -68   | dBmOp  |

|                                                        | NidleR  | _             | _               | *1 *3                                 | _     | -78   | -74   |        |

| Absolute Level (Initial Difference)                    | AV T    |               |                 | $V_{DD} = 3.0 \text{ V}$<br>Ta = 25°C | 0.338 | 0.35  | 0.362 | Vrms   |

| Absolute Level (IIIItial Dillelellee)                  | AV R    |               |                 | 1α – 23 0                             | 0.483 | 0.50  | 0.518 | VIIIIS |

| Absolute Level<br>(Deviation of Temperature and Power) | AV Tt   | 1020          | 0               | V <sub>DD</sub> = +2.7<br>to 3.8 V    | -0.2  | _     | +0.2  | dB     |

|                                                        | AV Rt   |               |                 | Ta = -30<br>to 85°C                   | -0.2  | _     | +0.2  | dB     |

| Absolute Delay                                         | Td      | 1020          | 0               | A to A BCLK = 64 kHz                  | _     | _     | 0.60  | ms     |

|                                                        | tgd T1  | 500           |                 | *4                                    | _     | 0.19  | 0.75  |        |

|                                                        | tgd T2  | 600           |                 |                                       | _     | 0.11  | 0.35  |        |

| Transmit Group Delay                                   | tgd T3  | 1000          | 0               |                                       | _     | 0.02  | 0.125 | ms     |

|                                                        | tgd T4  | 2600          |                 |                                       | _     | 0.05  | 0.125 |        |

|                                                        | tgd T5  | 2800          |                 |                                       | _     | 0.07  | 0.75  |        |

|                                                        | tgd R1  | 500           |                 | *4                                    | _     | 0.00  | 0.75  |        |

|                                                        | tgd R2  | 600           |                 |                                       | _     | 0.00  | 0.35  |        |

| Receive Group Delay                                    | tgd R3  | 1000          | 0               |                                       | _     | 0.00  | 0.125 | ms     |

|                                                        | tgd R4  | 2600          |                 |                                       | _     | 0.09  | 0.125 |        |

|                                                        | tgd R5  | 2800          |                 |                                       |       | 0.12  | 0.75  |        |

| Crosstalk Attenuation                                  | CR T    | 1020          | 0               | $TRANS \to RECV$                      | 75    | 85    | _     | dB     |

| UI USSIAIK AILEITUALIUTI                               | CR R    | 1020          | U               | $RECV \to TRANS$                      | 70    | 80    | _     | ub     |

<sup>\*1</sup> Psophometric filter is used

<sup>\*2</sup> Upper is specified for the  $\mu$ -law, lower for the A-law

<sup>\*3</sup> μ-law: All "1", A-law: "11010101"

<sup>\*4</sup> Minimum value of the group delay distortion

# **AC Characteristics (Continued)**

$(V_{DD} = 2.7 \text{ V to } 3.8 \text{ V}, \text{ Ta} = -30^{\circ}\text{C to } +85^{\circ}\text{C})$

| Parameter                          | Symbol           | Freq.<br>(Hz)        | Level<br>(dBm0)        | Condition             | Min. | Тур.  | Max. | Unit |

|------------------------------------|------------------|----------------------|------------------------|-----------------------|------|-------|------|------|

| Discrimination                     | DIS              | 4.6 kHz to<br>72 kHz | 0                      | 0 to<br>4000 Hz       | 30   | 32    |      | dB   |

| Out-of-band Spurious               | S                | 300 to<br>3400       | 0                      | 4.6 kHz to<br>100 kHz | _    | -37.5 | -35  | dBm0 |

| Intermodulation Distortion         | IMD              | fa = 470<br>fb = 320 | -4                     | 2fa – fb              | _    | -52   | -35  | dBm0 |

| Power Supply Noise Rejection Ratio | PSR T<br>PSR R   | 0 to<br>50 kHz       | 50 mV <sub>PP</sub>    | *5                    | _    | 30    |      | dB   |

|                                    | t <sub>SD</sub>  |                      |                        |                       | 20   | _     | 200  |      |

| Digital Output Delay Time          | t <sub>XD1</sub> | C. 100 r             | \E                     |                       | 20   | _     | 200  | 200  |

|                                    | t <sub>XD2</sub> | OL = 100             | $C_L = 100 \text{ pF}$ |                       |      |       | 200  | ns   |

|                                    | t <sub>XD3</sub> |                      |                        |                       | 20   |       | 200  |      |

<sup>\*5</sup> The measurement under idle channel noise

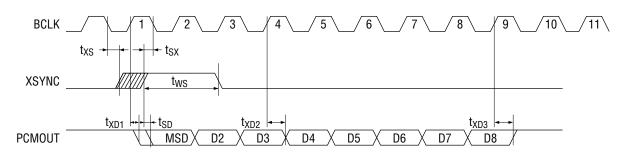

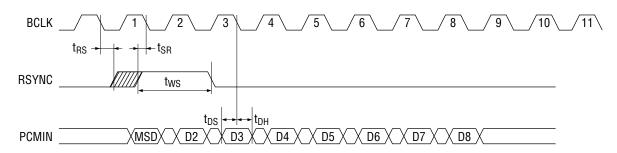

## **TIMING DIAGRAM**

## **PCM Data Input/Output Timing**

## Transmit Timing

When  $t_{XS} \le 1/2 \bullet Fc$ , the Delay of the MSD bit is defined as  $t_{XD1}$ . When  $t_{SX} \le 1/2 \bullet Fc$ , the Delay of the MSD bit is defined as  $t_{SD}$ .

#### Receive Timing

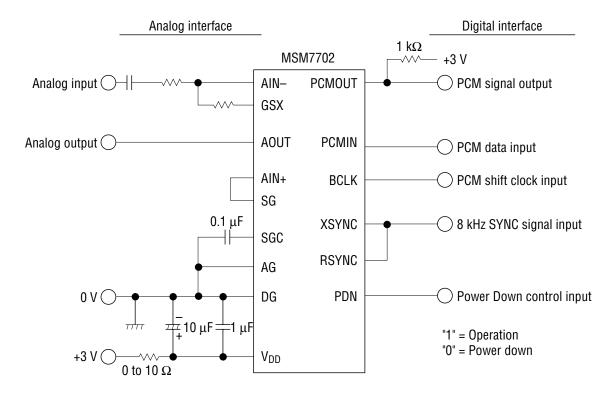

## **APPLICATION CIRCUIT**

The analog output signal has a maximum amplitude of  $\pm 1.0$  V above and below the offset voltage level of  $V_{DD}/2$ .

#### RECOMMENDATIONS FOR ACTUAL DESIGN

• To assure proper electrical characteristics, use bypass capacitors with excellent high frequency characteristics for the power supply and keep them as close as possible to the device pins.

- Connect the AG pin and the DG pin each other as close as possible. Connect to the system ground with low impedance.

- Mount the device directly on the board when mounted on PCBs. Do not use IC sockets. If an IC socket is unavoidable, use the short lead type socket.

- When mounted on a frame, use electro-magnetic shielding, if any electro-magnetic wave source such as power supply transformers surround the device.

- Keep the voltage on the V<sub>DD</sub> pin not lower than –0.3 V even instantaneously to avoid latchup phenomenon when turning the power on.

- Use a low noise (particularly, low level type of high frequency spike noise or pulse noise) power supply to avoid erroneous operation and the degradation of the characteristics of these devices.

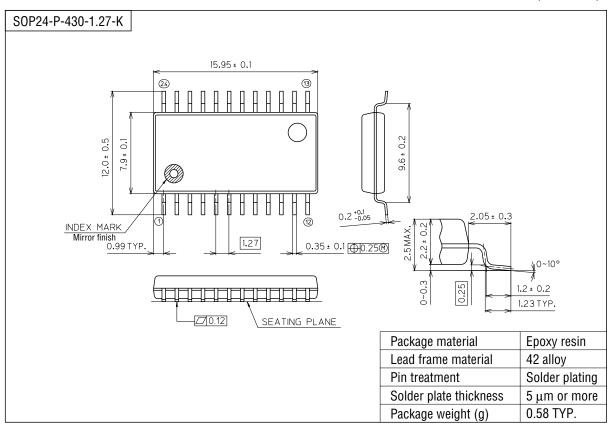

#### PACKAGE DIMENSIONS

(Unit: mm)

Notes for Mounting the Surface Mount Type Package

The SOP, QFP, TSOP, SOJ, QFJ (PLCC), SHP and BGA are surface mount type packages, which are very susceptible to heat in reflow mounting and humidity absorbed in storage. Therefore, before you perform reflow mounting, contact Oki's responsible sales person for the product name, package name, pin number, package code and desired mounting conditions (reflow method, temperature and times).

(Unit: mm)

Notes for Mounting the Surface Mount Type Package

The SOP, QFP, TSOP, SOJ, QFJ (PLCC), SHP and BGA are surface mount type packages, which are very susceptible to heat in reflow mounting and humidity absorbed in storage. Therefore, before you perform reflow mounting, contact Oki's responsible sales person for the product name, package name, pin number, package code and desired mounting conditions (reflow method, temperature and times).