## Intel<sup>®</sup> LXT3108 Octal T1/E1/J1 Long Haul/Short Haul Line Interface Unit

#### Datasheet

The Intel<sup>®</sup> LXT3108 is an octal 3.3 V Long Haul/Short Haul (LH/SH) T1/E1/J1 Line interface unit (LIU). This flexible LIU allows the design of T1/E1/J1 LH/SH multi-service cards with a single design and one bill of materials. The Intel<sup>®</sup> LXT3108 can be configured on a per-port basis through software. Intel's proven design makes the Intel<sup>®</sup> LXT3108 the perfect device for high-density T1/E1/J1 applications. To increase network reliability, the Intel<sup>®</sup> LXT3108 incorporates a DSP-based architecture with features such as Intel<sup>®</sup> Hitless Protection Switching (Intel<sup>®</sup> HPS) and Intel<sup>®</sup> Pulse Template Matching (Intel<sup>®</sup> PTM). The DSP-based architecture is less sensitive to power supply and temperature variations and allows the LIU to adapt to varying line conditions. Intel<sup>®</sup> HPS allows the design of 1+1 redundant cards without the use of relays as well as the ability to switch from one card to another without a loss of frame synchronization. Intel<sup>®</sup> PTM software allows the transmitter to shape the output pulse to meet various board conditions, without the need to change any external components.

### **Applications**

- Voice over packet gateways

- Integrated Multi-service Access Platforms (IMAPs)

- Integrated Access Devices (IADs)

- Inverse multiplexing for ATM (IMA)

### **Product Features**

- Intel<sup>®</sup> HPS for 1+1 protection without relays

- Intel<sup>®</sup> PTM software for pulse output adjustment through software without component or board change

- Interfaces with the Intel<sup>®</sup> IXF3208, Octal T1/E1/J1 Framer with Intel<sup>®</sup> On-Chip Performance Report Messaging (Intel<sup>®</sup> On-Chip PRM)

- T1 (100 Ohm), E1 (75 and 120 Ohm), J1 (110 Ohm) termination and LH/SH selectable per port through software without component change

- Receiver sensitivity exceeds 36 dB @ 772 KHz and 43 dB @ 1024 KHz of cable attenuation providing margin for board and cable variations

- 3.3 V power supply with 5 V tolerant inputs

- Wireless base stations

- Routers

- Frame relay access devices

- CSU/DSU equipment

- On chip Clock Adaptor (CLAD) that allows one master clock for T1/E1/J1 applications (1X, 2X, 4X or 8X T1 or E1 clock)

- 16-bit BPV/Excess Zero counters per port

- B8ZS/HDB3 encoders and decoders, and unipolar/bipolar I/O modes selectable per port

- Digital Jitter Attenuator (DJA) in either receive or transmit path

- Meets or exceeds specifications in ANSI T1.102, T1.403 and T1.408; ITU I.431, CTR12/13, G.703, G.736, G.775 and G.823; ETSI 300-166 and 300-233; and AT&T Pub 62411

- Available in a 17 x 17 mm 256 PBGA (LXT3108 BE) or 28 x 28 mm 208 QFP (LXT3108 HE) package

Information in this document is provided in connection with Intel<sup>®</sup> products. No license, express or implied, by estoppel or otherwise, to any intellectual property rights is granted by this document. Except as provided in Intel's Terms and Conditions of Sale for such products, Intel assumes no liability whatsoever, and Intel disclaims any express or implied warranty, relating to sale and/or use of Intel products including liability or warranties relating to fitness for a particular purpose, merchantability, or infringement of any patent, copyright or other intellectual property right. Intel products are not intended for use in medical, life saving, or life sustaining applications.

Intel may make changes to specifications and product descriptions at any time, without notice.

Designers must not rely on the absence or characteristics of any features or instructions marked "reserved" or "undefined." Intel reserves these for future definition and shall have no responsibility whatsoever for conflicts or incompatibilities arising from future changes to them.

The Intel<sup>®</sup> LXT3108 may contain design defects or errors known as errata which may cause the product to deviate from published specifications. Current characterized errata are available on request.

Contact your local Intel sales office or your distributor to obtain the latest specifications and before placing your product order.

Copies of documents which have an ordering number and are referenced in this document, or other Intel literature may be obtained by calling 1-800-548-4725 or by visiting Intel's website at http://www.intel.com.

#### Copyright © Intel Corporation, 2002

AlertVIEW, i960, AnyPoint, AppChoice, BoardWatch, BunnyPeople, CablePort, Celeron, Chips, Commerce Cart, CT Connect, CT Media, Dialogic, DM3, EtherExpress, ETOX, FlashFile, GatherRound, i386, i486, iCat, iCOMP, Insight960, InstantIP, Intel, Intel Iogo, Intel386, Intel486, Intel740, IntelDX2, IntelDX4, IntelSX2, Intel ChatPad, Intel Create&Share, Intel Dot.Station, Intel GigaBlade, Intel InBusiness, Intel Inside, Intel Inside logo, Intel NetBurst, Intel NetStructure, Intel Play, Intel Play logo, Intel Pocket Concert, Intel SingleDriver, Intel SpeedStep, Intel StrataFlash, Intel TeamStation, Intel WebOutfitter, Intel Xcon, Intel Xscale, Itanium, JobAnalyst, LANDesk, LanRover, MCS, MMX, MMX logo, NetPort, NetportExpress, Optimizer logo, OverDrive, Paragon, PC Dads, PC Parents, Pentium, Pentium II Xeon, Pentium III Xeon, Performance at Your Command, ProShare, RemoteExpress, Screamline, Shiva, SmartDie, Solutions960, Sound Mark, StorageExpress, The Computer Inside, The Journey Inside, This Way In, TokenExpress, Trillium, Vivonic, and VTune are trademarks or registered trademarks of Intel Corporation or its subsidiaries in the United States and other countries.

\*Other names and brands may be claimed as the property of others.

| 1.0  | Pin A      | Assignments                                                                  | 11 |

|------|------------|------------------------------------------------------------------------------|----|

| 2.0  | Signa      | al Descriptions                                                              | 13 |

| 3.0  | T1/E1      | 1/J1 Nomenclature                                                            | 27 |

| 4.0  | Intel®     | <sup>®</sup> LXT3108 LIU Nomenclature                                        |    |

| 5.0  | Func       | tional Description                                                           |    |

| 6.0  |            | Descriptions                                                                 |    |

| 7.0  |            | vare Support                                                                 |    |

| -    |            |                                                                              |    |

| 8.0  |            | lization                                                                     |    |

|      | 8.1<br>8.2 | CLAD Initialization                                                          |    |

|      | -          | Reset Operation                                                              |    |

| 9.0  | Powe       | er Supply Requirements                                                       | 41 |

|      | 9.1        | 5 V Tolerant I/O Pins                                                        |    |

|      | 9.2        | Layout Considerations                                                        |    |

|      |            | 9.2.1 Ground Plane                                                           |    |

|      |            | 9.2.2 Analog Power Supply                                                    |    |

|      |            | 9.2.3 Digital Power Supply                                                   |    |

| 10.0 | Trans      | smitter                                                                      | 43 |

|      | 10.1       | Transmit Line Interface                                                      |    |

|      |            | 10.1.1 Transmit Impedance Termination                                        |    |

|      |            | 10.1.2 Transmit Return Loss Performance                                      |    |

|      |            | 10.1.2.1 Intel <sup>®</sup> Pulse Template Matching (Intel <sup>®</sup> PTM) |    |

|      | 10.2       | 0                                                                            |    |

|      |            | 10.2.1 Transmit Idle Operation and Tri-stating Drivers                       |    |

| 11.0 | Rece       | iver                                                                         |    |

|      | 11.1       | Master Reference Clock                                                       |    |

|      | 11.2       | Receiver Digital Interface                                                   |    |

|      |            | 11.2.1 Receiver Idle Conditions                                              |    |

|      | 11.3       | Receiver Line Interface                                                      |    |

|      |            | 11.3.1 Receive Termination Impedance                                         |    |

|      |            | 11.3.2 Receiver Sensitivity Programming<br>11.3.2.1 Receiver Monitor Mode    |    |

|      | 11.4       | Receiver Status Information                                                  |    |

| 12.0 |            | r Attenuation (JA)                                                           |    |

| 12.0 | 12.1       | Digital Jitter Attenuator (DJA) Status                                       |    |

| 12.0 |            | vork Control and Maintenance Functions                                       |    |

| 13.0 |            |                                                                              |    |

|      | 13.1       | Diagnostic Modes                                                             |    |

|      |            | 13.1.1 In-Band Network Loop Up or Down Code Generator/Detector               |    |

|      |       | 13.1.2 Analog Loopback                                                        | 55  |

|------|-------|-------------------------------------------------------------------------------|-----|

|      |       | 13.1.3 Digital Loopback                                                       | 56  |

|      |       | 13.1.4 Remote Loopback                                                        | 56  |

|      |       | 13.1.5 Transmit All Ones (TAOS)                                               | 57  |

|      | 13.2  | Line Coding                                                                   |     |

|      |       | 13.2.1 Alternate Mark Inversion (AMI)                                         | 58  |

|      |       | 13.2.1.1 Bipolar with Eight Zero Substitution (B8ZS)                          | 59  |

|      |       | 13.2.1.2 High Density Bipolar Three (HDB3)                                    | 59  |

|      | 13.3  | Network Maintenance Functions                                                 | 60  |

|      |       | 13.3.1 Loss Of Signal (LOS)                                                   | 60  |

|      |       | 13.3.1.1 Operation of USER LOS with Amplitude Detection                       | 62  |

|      |       | 13.3.1.2 Operation of USER LOS with Marks Density Detection                   |     |

|      |       | 13.3.2 Alarm Indication Signal (AIS)                                          | 62  |

|      |       | 13.3.3 NLOOP Status                                                           |     |

|      |       | 13.3.3.1 T1 AMI/B8ZS BPVs                                                     | 63  |

|      |       | 13.3.3.2 E1 AMI/HDB3 BPVs                                                     |     |

|      |       | 13.3.3.3 Excess Zeroes (EXZ)                                                  |     |

|      |       | 13.3.4 Monitoring BPV and EXZ Line Coding Violations                          | 64  |

| 14.0 | Host  | Interface                                                                     | 65  |

|      |       |                                                                               |     |

|      | 14.1  | Supported Processors and Connections                                          | 65  |

|      |       | 14.1.1 MPC680<br>14.1.2 M68302                                                |     |

|      |       | 14.1.2 $M08302$<br>14.1.3 $Intel^{\text{@}} i960^{\text{@}}/i486^{\text{TM}}$ | 00  |

|      | 14.2  |                                                                               |     |

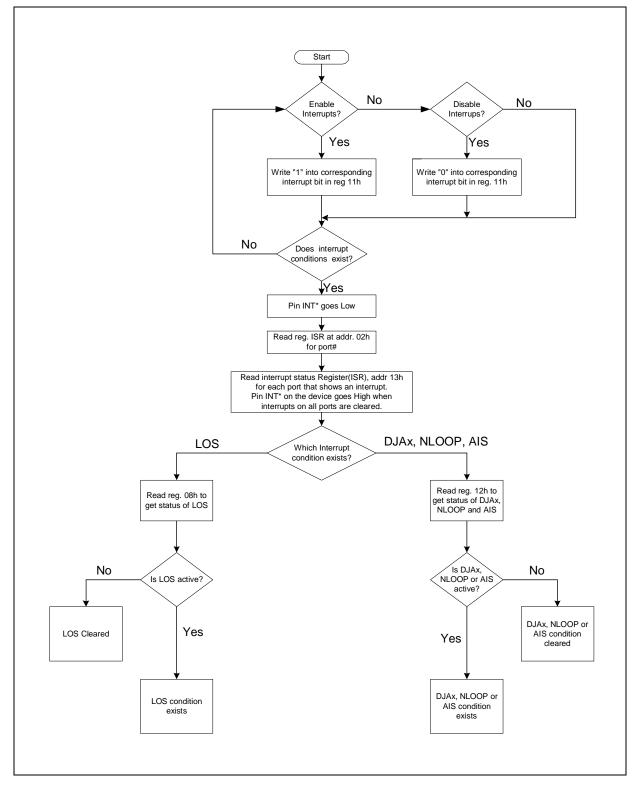

|      | 14.2  | Interrupts<br>14.2.1 Interrupt Enabling                                       |     |

|      |       | 14.2.1 Interrupt Erlability                                                   |     |

|      |       |                                                                               |     |

| 15.0 | Regis | ter Definitions                                                               | 69  |

|      | 15.1  | Global Registers                                                              | 69  |

|      | 15.2  | Port Page Register Bank (PPRB)                                                |     |

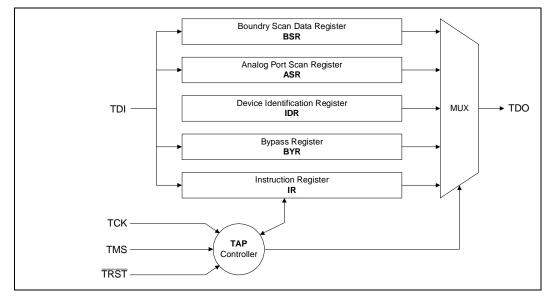

| 16.0 |       | Boundary Scan                                                                 | Q1  |

| 10.0 |       | -                                                                             |     |

|      | 16.1  | Architecture                                                                  |     |

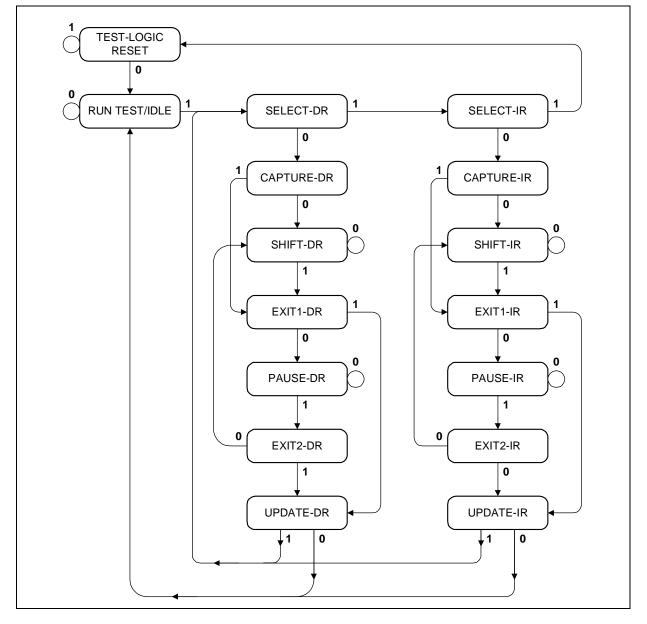

|      | 16.2  | TAP Controller                                                                |     |

|      | 16.3  | JTAG Register Description                                                     |     |

|      |       | 16.3.1 Boundary Scan Register (BSR)                                           |     |

|      |       | 16.3.2 Device Identification Register (IDR)                                   |     |

|      |       | 16.3.3 Bypass Register (BYR)                                                  |     |

|      |       | 16.3.4 Instruction Register (IR)                                              | 84  |

| 17.0 | Test  | Specifications                                                                | 87  |

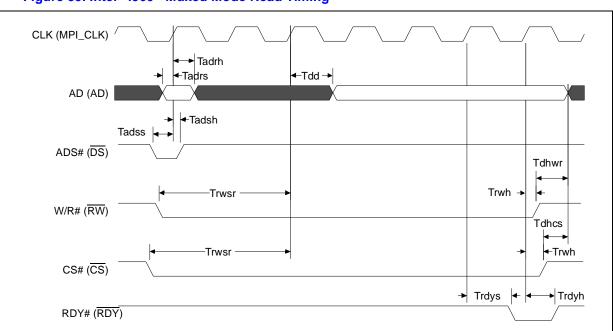

|      | 17.1  | Microprocessor Interface Timing Diagrams                                      |     |

|      | 17.2  | Referenced Standards                                                          | 105 |

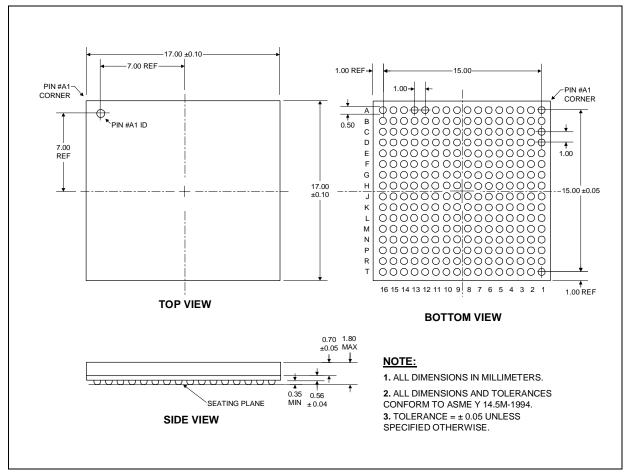

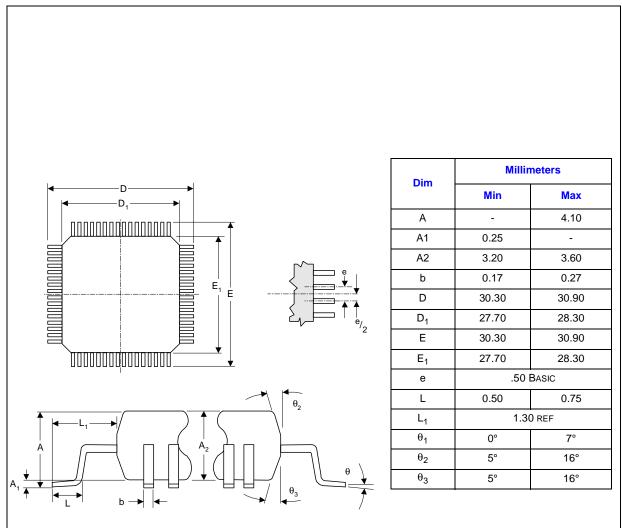

| 18.0 | Mech  | anical Specification                                                          | 107 |

| 19.0 | Gloss | sary                                                                          | 109 |

|      |       |                                                                               |     |

## Figures

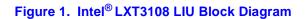

| 1  | Intel <sup>®</sup> LXT3108 LIU Block Diagram                                         |     |

|----|--------------------------------------------------------------------------------------|-----|

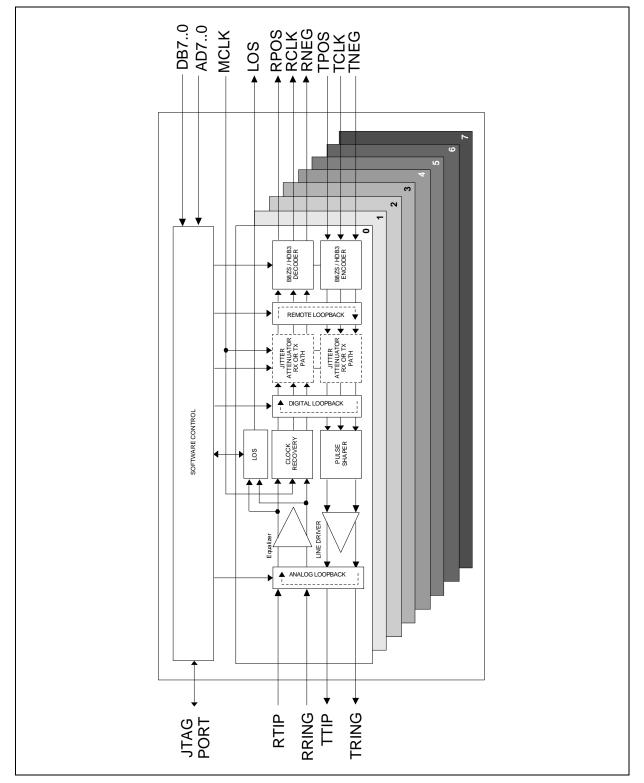

| 2  | Intel <sup>®</sup> LXT3108 HE 208 Pin Assignment                                     | 11  |

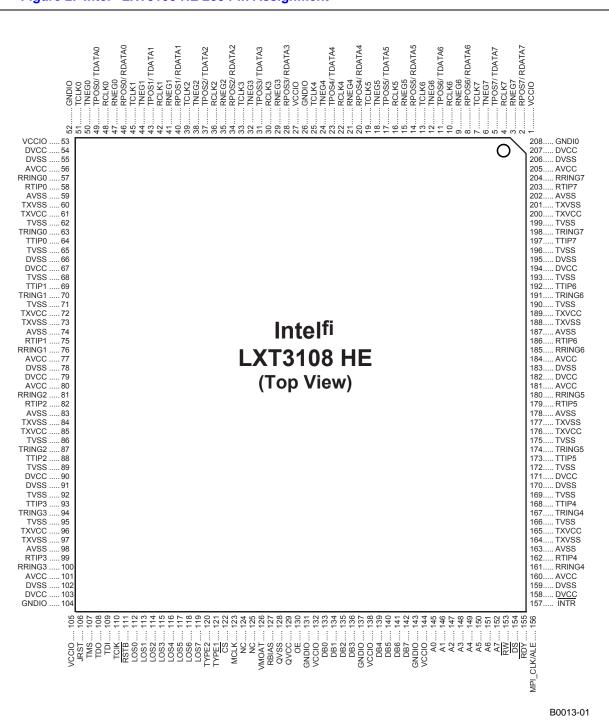

| 3  | Intel <sup>®</sup> LXT3108 BE 256 Plastic Ball Grid Array (PBGA) Assignments         |     |

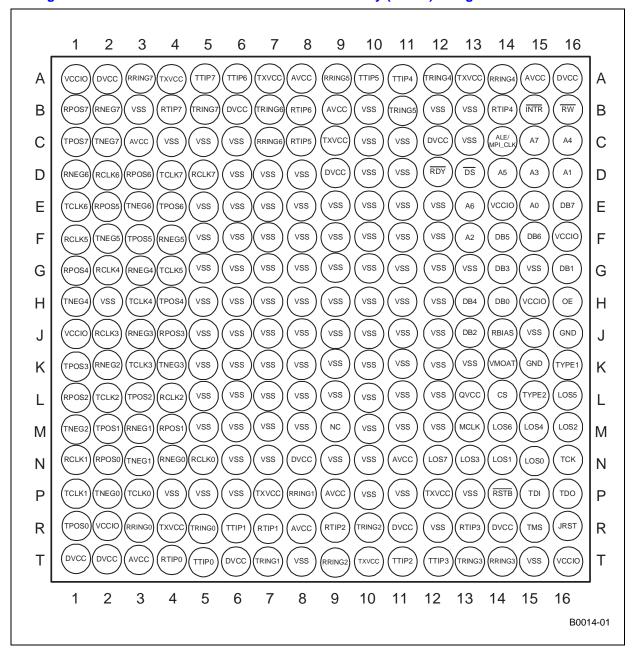

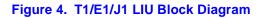

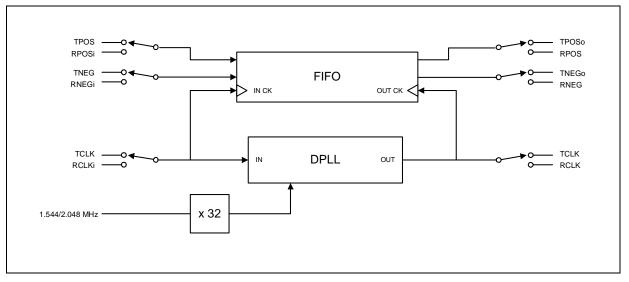

| 4  | T1/E1/J1 LIU Block Diagram                                                           | 31  |

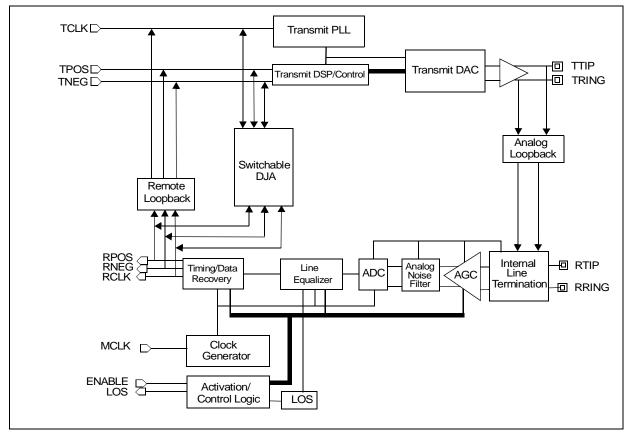

| 5  | Intel <sup>®</sup> LXT3108 LIU Port Block Diagram                                    |     |

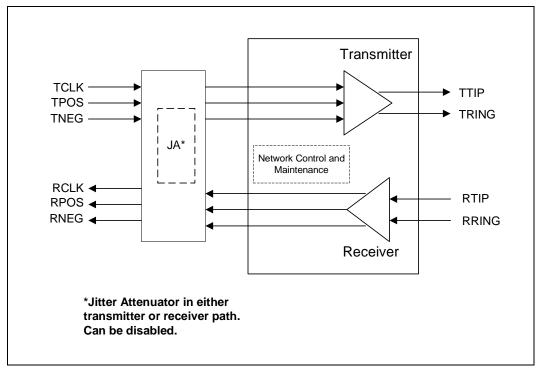

| 6  | Intel <sup>®</sup> LXT3108 LIU Port Circuit                                          | 34  |

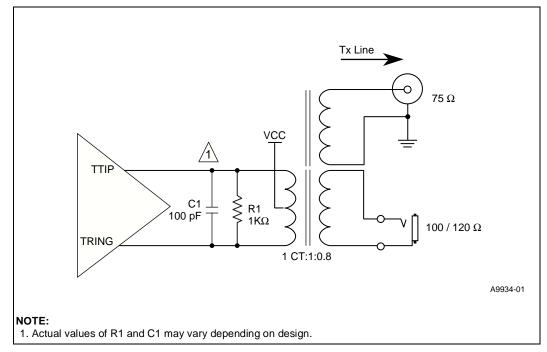

| 7  | Transmitter Circuit for Twisted Pair and Coaxial Cable                               | 35  |

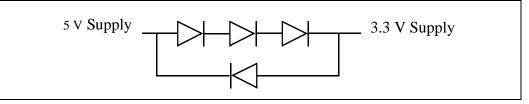

| 8  | Diode Protection Network When Inputs Power Up Before Supplies                        | 41  |

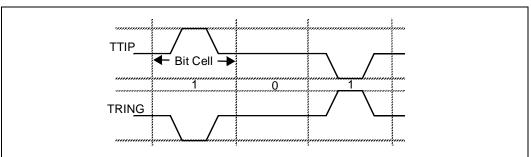

| 9  | 50% AMI Encoding                                                                     | 43  |

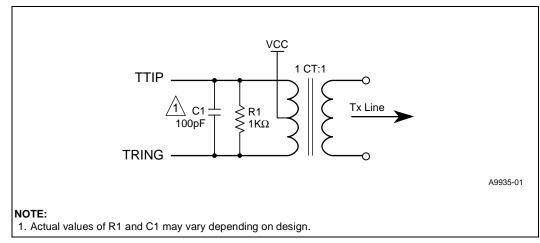

| 10 | Typical Transmitter Interface Connections                                            | 44  |

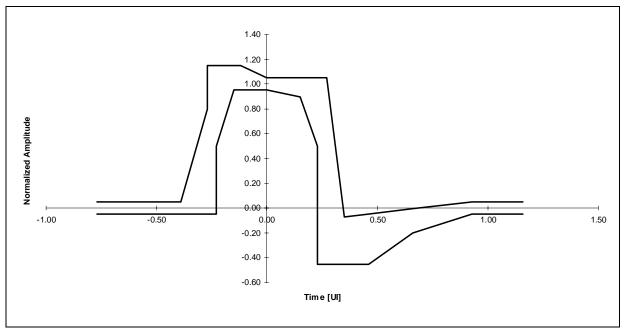

| 11 | T1, T1.102 Mask Templates                                                            | 46  |

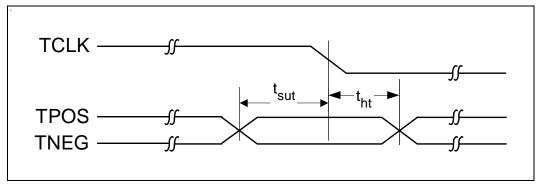

| 12 | Transmit Interface Timing                                                            | 47  |

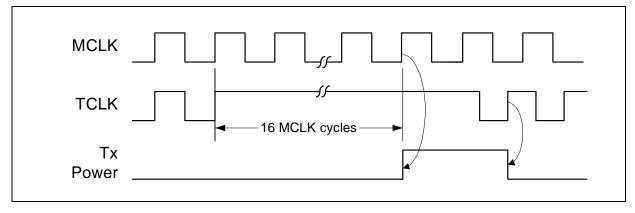

| 13 | TCLK Power Down Timing                                                               | 48  |

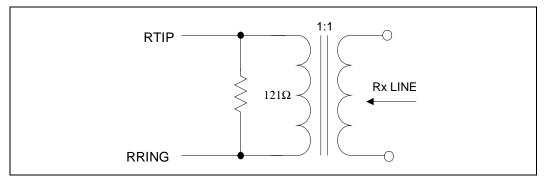

| 14 | Typical Receiver Interface                                                           | 50  |

| 15 | Jitter Attenuation Loop                                                              | 53  |

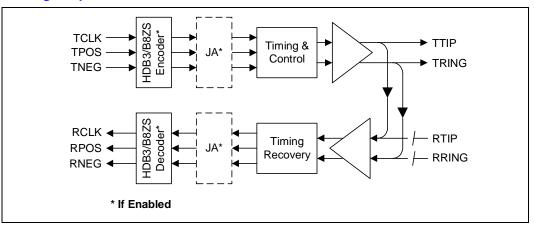

| 16 | Analog Loopback                                                                      | 56  |

| 17 | Digital Loopback                                                                     | 56  |

| 18 | Remote Loopback                                                                      | 57  |

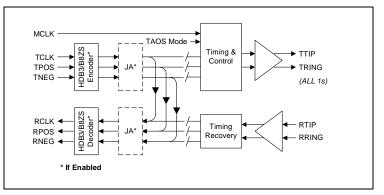

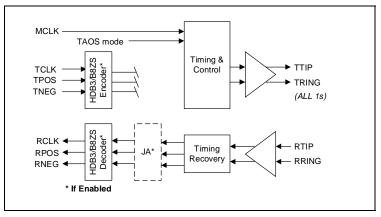

| 19 | TAOS Data Path                                                                       | 57  |

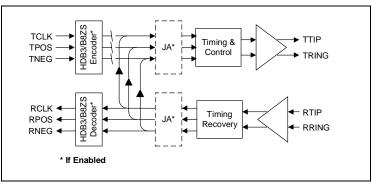

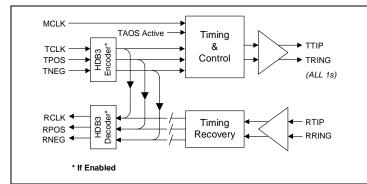

| 20 | TAOS with Digital Loopback                                                           | 58  |

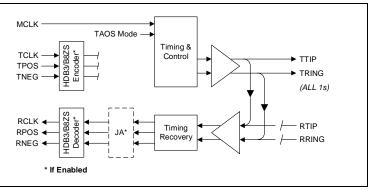

| 21 | TAOS with Analog Loopback                                                            |     |

| 22 | Interrupt Processing FlowChart                                                       | 68  |

| 23 | Intel <sup>®</sup> LXT3108 LIU JTAG Architecture                                     | 81  |

| 24 | JTAG State Diagram                                                                   | 83  |

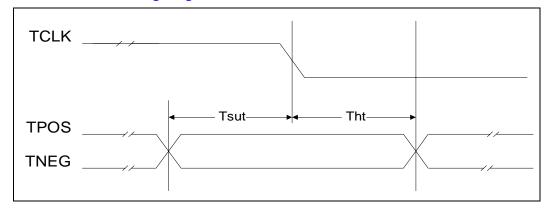

| 25 | Transmit Clock Timing Diagram                                                        | 91  |

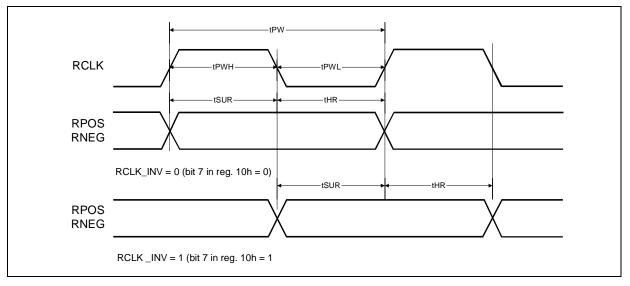

| 26 | Receive Clock Timing Diagram                                                         |     |

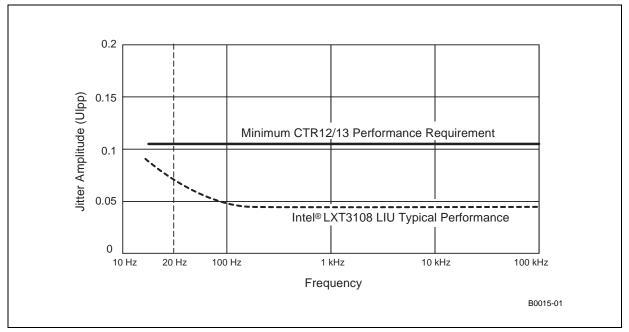

| 27 | Intel <sup>®</sup> LXT3108 LIU Output Jitter for CTR12/13 Applications               | 94  |

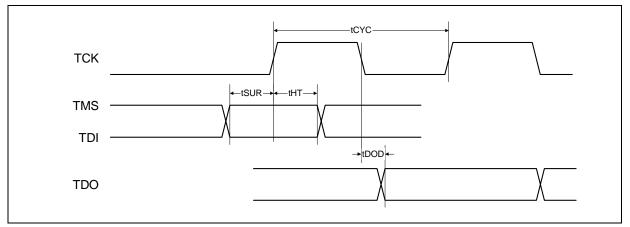

| 28 | JTAG Timing                                                                          | 94  |

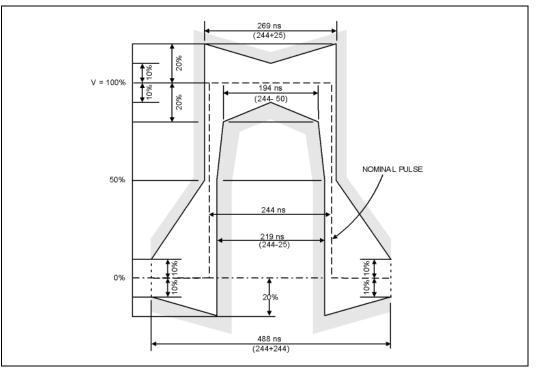

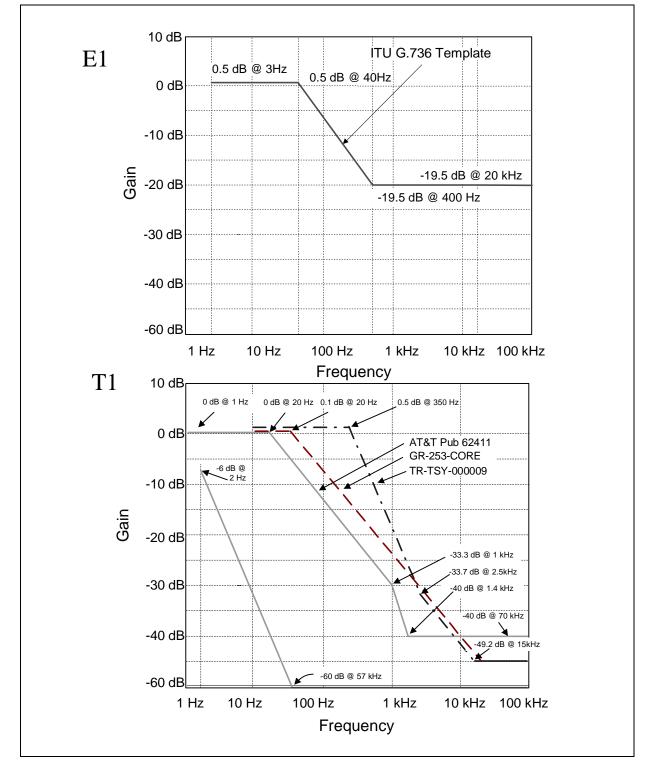

| 29 | E1, G.703 Mask Templates                                                             | 95  |

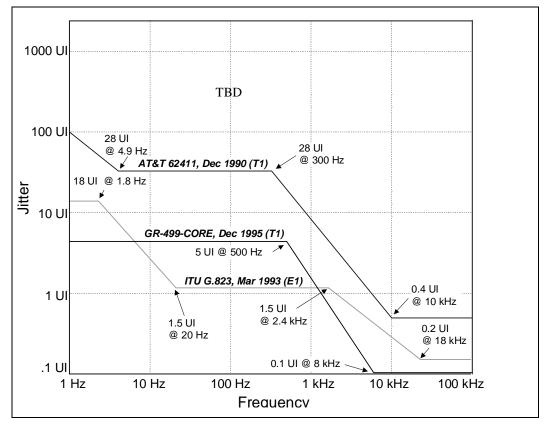

| 30 | Intel <sup>®</sup> LXT3108 LIU Jitter Tolerance Performance                          |     |

| 31 | Intel <sup>®</sup> LXT3108 LIU Jitter Transfer Performance                           | 97  |

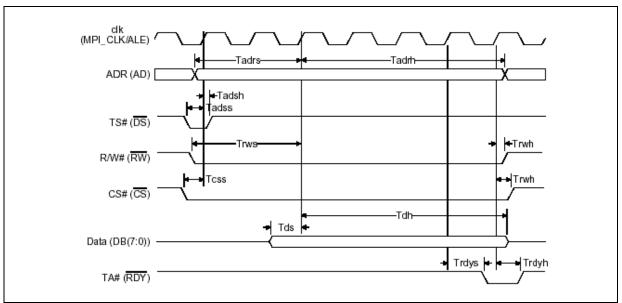

| 32 | MPC860 Write Timing                                                                  | 98  |

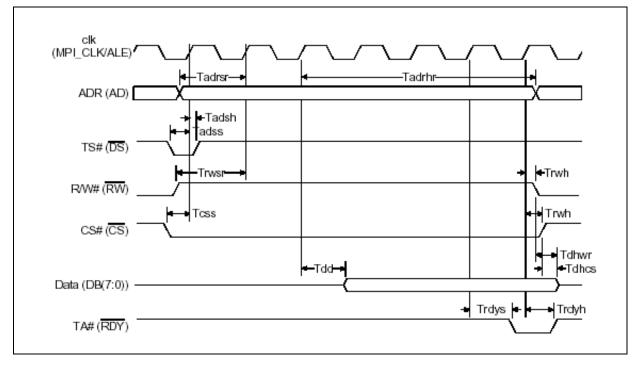

| 33 | MPC860 Read Timing                                                                   | 99  |

| 34 | M68302 Write Timing                                                                  | 100 |

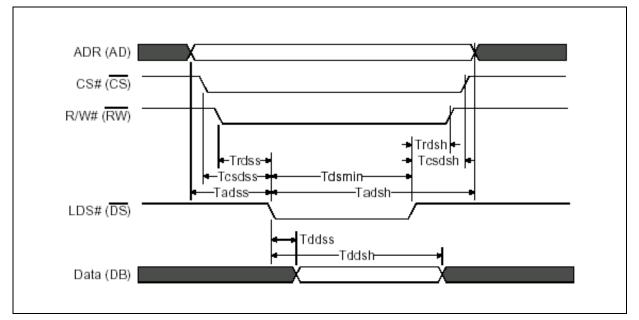

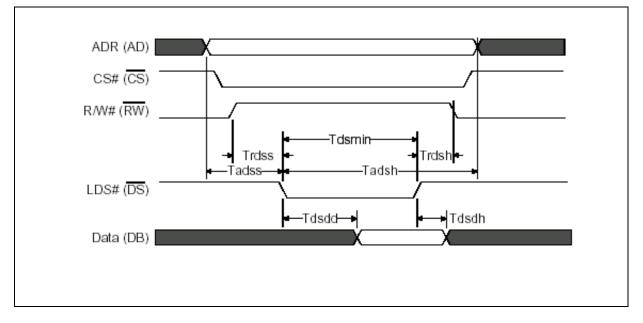

| 35 | M68302 Read Timing                                                                   |     |

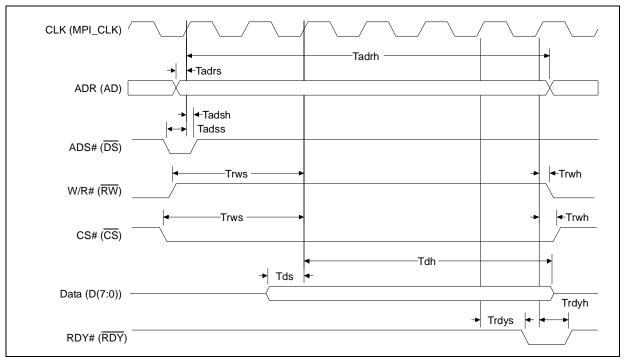

| 36 | Intel <sup>®</sup> i486 <sup>TM</sup> /i960 <sup>®</sup> Non-muxed Mode Write Timing | 102 |

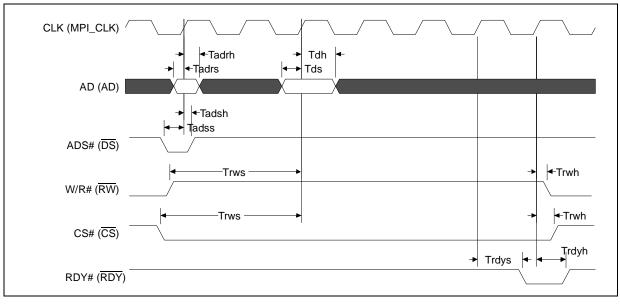

| 37 | Intel <sup>®</sup> i960 <sup>®</sup> Muxed Mode Write Timing                         | 102 |

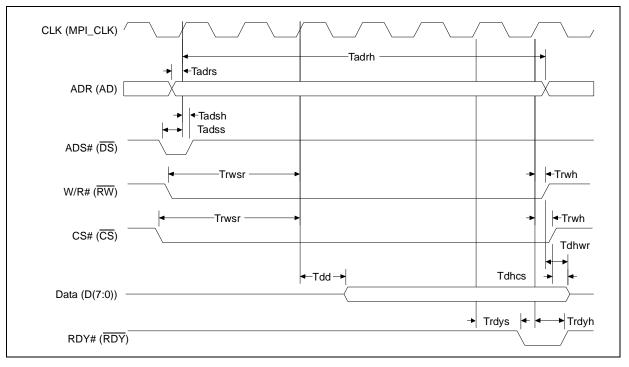

| 38 | Intel <sup>®</sup> i486 <sup>TM</sup> /i960 <sup>®</sup> Non-muxed Mode Read Timing  | 103 |

| 39 | Intel <sup>®</sup> i960 <sup>®</sup> Muxed Mode Read Timing                          | 104 |

| 40 | Intel <sup>®</sup> LXT3108 LIU 256 PBGA Mechanical Specification                     | 107 |

| 41 | Intel <sup>®</sup> LXT3108 LIU 208 Pin QFP Mechanical Specifications                 | 108 |

#### Contents

### **Tables**

| 1  | LXT3108 Pin Description                                                | 13   |

|----|------------------------------------------------------------------------|------|

| 2  | CLAD Initialization Options                                            |      |

| 3  | Transformer Specifications for the Intel <sup>®</sup> LXT3108 LIU      | .44  |

| 4  | Preset Pulse Shaping Settings and Conditions                           | . 45 |

| 5  | Transmit Return Loss Specifications for Frequency Range and Magnitude  | 46   |

| 6  | Powering Down the Transmitter with Static TCLK                         |      |

| 7  | Programming Receiver Sensitivity                                       |      |

| 8  | Jitter Attenuation Specifications                                      |      |

| 9  | LOS Criteria for Intel <sup>®</sup> LXT3108 LIU                        |      |

| 10 | LOS Register Configurations                                            |      |

| 11 | LOS Selection Defaults                                                 |      |

| 12 | AIS Service Condition Variations                                       |      |

| 13 | Excess Zero (EXZ) Definitions                                          |      |

| 14 | Interfacing the Intel <sup>®</sup> LXT3108 LIU to the MPC860 Processor |      |

| 15 | Interfacing the Intel <sup>®</sup> LXT3108 LIU to the M68302 Processor | .66  |

| 16 | Intel <sup>®</sup> i960 <sup>®</sup> /i486 <sup>TM</sup> Mode          |      |

| 17 | Global Register Addresses                                              |      |

| 18 | Port Page Select Register, CPS, 00h                                    |      |

| 19 | ID Register, ID, 01h                                                   |      |

| 20 | Interrupt Port Register, ICR, 02h                                      |      |

| 21 | CLAD Configuration Register1, 11h                                      |      |

| 22 | Port Page Register Bank Addresses                                      |      |

| 23 | Port Master Control Page Register, 01h                                 |      |

| 24 | Port Receiver Enable Page Register, 02h                                |      |

| 25 | Transmit Control Page Register, 03h                                    |      |

| 26 | Receive Control Page Register, 04h                                     |      |

| 27 | Termination Control Page Register, 05h                                 |      |

| 28 | Receiver Equalizer Status Zero Page Register, 06h                      |      |

| 29 | Receiver Equalizer Status One Page Register, 07h                       |      |

| 30 | Receiver Equalizer Status Two Page Register, 08h                       |      |

| 31 | LOS Window Page Register, 0Bh                                          |      |

| 32 | LOS Set Threshold One Page Register, 0Ch                               |      |

| 33 | LOS Reset Threshold Two Page Register, 0Dh                             |      |

| 34 | Loopback Enable Page Register, 10h                                     |      |

| 35 | Interrupt Enable Page Register, 11h                                    |      |

| 36 | Alarm Status One Page Register, 12h                                    |      |

| 37 | Interrupt Status Two Page Register, 13h                                |      |

| 38 | Line Coding Control One Page Register, 1Ch                             |      |

| 39 | JA Control Two Page Register, 1Dh                                      | .79  |

| 40 | DJA Corner Frequency Selection                                         |      |

| 41 | BPV Counter High Byte Page Register, 1Eh                               | .79  |

| 42 | BPV Counter Low Byte Page Register, 1Fh                                |      |

| 43 | Receiver Control Page Register, 3Ch                                    |      |

| 44 | Transmit Coefficient Page Register Range, 40h-6Fh                      |      |

| 45 | TAP State Description                                                  |      |

| 46 | Device Identification Register (IDR)                                   |      |

| 47 | Instruction Register (IR)                                              |      |

| 48 | Absolute Maximum Ratings                                               |      |

| 49 | Recommended Operating Conditions                                       |      |

|    |                                                                        |      |

| 50 | Electrical Characteristics (Over Recommended Operating Conditions)                    |     |

|----|---------------------------------------------------------------------------------------|-----|

| 51 | E1 Transmitter Analog Characteristics                                                 |     |

| 52 | E1 Receiver Analog Characteristics                                                    |     |

| 53 | T1 Transmitter Analog Characteristics                                                 |     |

| 54 | T1 Receiver Analog Characteristics                                                    | 90  |

| 55 | Master and Transmit Clock Timing Characteristics                                      | 91  |

| 56 | Jitter Attenuator Characteristics                                                     | 92  |

| 57 | Receive Timing Characteristics for T1 Operation                                       | 93  |

| 58 | Receive Timing Characteristics for E1 Operation                                       | 93  |

| 59 | JTAG Timing Characteristics                                                           | 94  |

| 60 | G.703 2.048 Mbps Pulse Mask Specifications                                            | 95  |

| 61 | T1.102 1.544 Mbps Pulse Mask Specifications                                           | 95  |

| 62 | MPC860 Write Timing Characteristics                                                   | 98  |

| 63 | MPC860 Read Timing Characteristics                                                    |     |

| 64 | M68302 Write Timing Characteristics                                                   |     |

| 65 | M68302 Read Timing Characteristics                                                    |     |

| 66 | Intel <sup>®</sup> i486 <sup>TM</sup> /i960 <sup>®</sup> Write Timing Characteristics |     |

| 67 | Intel <sup>®</sup> i486 <sup>TM</sup> /i960 <sup>®</sup> Read Timing Characteristics  | 104 |

### **Revision History**

| Date         | Revision | Description                                                                                                                                                        |

|--------------|----------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Ma. 2000     | 224      | Modified Figure: 2, 3, 5, 6, 7, 10, 32, 33, 34, 35<br>Modified Tables: 1, 4, 6, 8, 11, 12, 13, 14, 15, 18, 23, 24, 25, 26, 30, 44, 52, 63, 64, 66                  |

| May 2002     | -004     | Modified Section: 3.0, 4.0, 5.0, 6.0, 8.0, 9.0, 9.2, 10.1.2.1, 11.3.1, 11.3.2.1, 14.1.1, 14.1.2,                                                                   |

|              |          | Added Table: 43                                                                                                                                                    |

|              |          | Modified Figures: 1 - 3, 5 - 7, 10, 14, 15, 32 - 36, and 38.                                                                                                       |

|              | -003     | Modified Tables: 1, 5, 9 - 11, 14 - 18, 20, 22, 23, 26, 29 - 31, 33<br>- 36, 39, 40, 45, 47, 48, 50 - 55, 61 - 63, 65, and 66.                                     |

| Janyary 2002 |          | Modified Sections: 8.1, 8.2, 9.0, 9.2.1, 10.1, 10.2, 10.2.1, 10.3.1, 10.3.2, 11.0, 12.1.5, 12.3.2, 12.3.3.1, 12.3.3.2, 12.3.4, 13.0, 13.1, 13.2, 13.2.1, and 16.2. |

|              |          | Deleted Section: 16.1 and 16.1.1 - 4.                                                                                                                              |

|              |          | Deleted Tables: 58 - 61.                                                                                                                                           |

|              |          | Modified Pages: 1, 22 - 28, and 30.                                                                                                                                |

|              |          | Modified Tables: 1, 2, 44 - 53.                                                                                                                                    |

| July 2001    | -002     | Modified Figures:1-3, 5-7, 10, 11, 15, 26, 38 & 39.                                                                                                                |

|              |          | Modified: TOC, LOF and LOT.                                                                                                                                        |

|              |          | Added glossary.                                                                                                                                                    |

Intel<sup>®</sup> LXT3108 LIU

## intel®

intel®

### This page intentionally left blank.

### 1.0 Pin Assignments

Figure 2. Intel<sup>®</sup> LXT3108 HE 208 Pin Assignment

#### Figure 3. Intel<sup>®</sup> LXT3108 BE 256 Plastic Ball Grid Array (PBGA) Assignments

### 2.0 Signal Descriptions

| QFP | PBGA | Symbol           | I/O | Desci                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | ription                                                                                                                                                                                                                                                                                                                                                                 |

|-----|------|------------------|-----|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| WFF | PBGA | Symbol           | 1/0 | Bipolar Mode                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | Unipolar Mode                                                                                                                                                                                                                                                                                                                                                           |

| 1   | A1   | VCCIO            | S   | Power (I/O).                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | I                                                                                                                                                                                                                                                                                                                                                                       |

|     |      |                  |     | Receive Positive Data/Receive Data                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | Output (Port. 7).                                                                                                                                                                                                                                                                                                                                                       |

| 2   | B1   | RPOS7/<br>RDATA7 | DO  | Acts as the positive side of the bipolar<br>data output pair, RPOS7 and<br>RNEG7, recovered from the line<br>interface.<br>RPOS7 acts as an active high NRZ<br>receive data output. A High signal on<br>RPOS7 corresponds to receipt of a<br>positive pulse on RTIP/RRING. A<br>High signal on RNEG7 corresponds<br>to receipt of a negative pulse on<br>RTIP/RRING. As default this signal<br>along with RNEG7 is valid on the<br>falling edge of RCLK7. The LXT3108<br>can be programmed to validate the<br>RPOS7 and RNEG7data on the rising<br>edge of the RCLK7. This rule applies | RDATA7 digital framer interface pin<br>acts as a single Non-Return-to-Zero<br>(NRZ) output of the data recovered<br>from the line interface.                                                                                                                                                                                                                            |

|     |      |                  |     | to all ports (0 through 7).<br>Receive Negative Data (Port. 7).                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                                                                                                                                                                                                                                                                                                                                         |

| 3   | B2   | RNEG7/<br>RBPV7  | DO  | This digital framer interface pin acts<br>as the negative side of the bipolar<br>data output pair, RPOS7 and<br>RNEG7, recovered from the line<br>interface.<br>RNEG7 acts as an active high NRZ<br>receive signal output. A High signal<br>on RNEG7 corresponds to receipt of<br>a negative pulse on RTIP/RRING.<br>This signal along with RPOS7 is valid<br>on the falling edge of RCLK7.                                                                                                                                                                                             | RBPV7 indicates a receive BiPolar<br>Violation (BPV). It goes High on<br>receipt of a bipolar violation at the<br>receiver. This is a NRZ output, valid<br>by default on the falling edge of the<br>RCLK. The clock edge validating this<br>signal can be changed from falling<br>edge to rising edge by software. This<br>description applies to ports 0 through<br>7. |

| 4   | D5   | RCLK7            | DO  | <b>Receive Clock Output (Port. 7).</b> This digital framer interface pin provides the recovered clock from the signal received at RTIP7 and RRING7. Under LOS conditions there is a transition from the RCLK7 signal (derived from the recovered data) to an internal clock (synthesized from the MCLK signal by CLAD circuitry) at the RCLK7 output.                                                                                                                                                                                                                                   |                                                                                                                                                                                                                                                                                                                                                                         |

#### Table 1. LXT3108 Pin Description (Sheet 1 of 13)

#### Table 1. LXT3108 Pin Description (Sheet 2 of 13)

| QFP   | PBGA  | Symbol           | 1/0 | Description                                                                                                                                                                                                                                                                               |                                                                                                                  |                                            |                                                                |                                                                                         |

|-------|-------|------------------|-----|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------|--------------------------------------------|----------------------------------------------------------------|-----------------------------------------------------------------------------------------|

| Ser 1 | 1 DOA | Cymbol           |     | Bipolar Mode                                                                                                                                                                                                                                                                              |                                                                                                                  |                                            | Unipolar Mode                                                  |                                                                                         |

|       |       |                  |     | Transmit Positive Data/Transmit Data Input (Port. 7)                                                                                                                                                                                                                                      |                                                                                                                  |                                            |                                                                |                                                                                         |

| 5     | C1    | TPOS7/<br>TDATA7 | DI  | Digital framer interface<br>positive side of the b<br>pair, TPOS7 and TN<br>controls the signal tra-<br>line interface.<br>TPOS7 is an active h<br>that operates togethe<br>TPOS7 starts the tra<br>positive pulse on TTI<br>whereas TNEG7 star<br>transmission of a neg<br>TTIP7/TRING7. | ipolar data i<br>EG7, which<br>ansmitted to<br>high NRZ in<br>er with TNE<br>nsmission o<br>P7/TRING7<br>rts the | input<br>o the<br>put<br>G7.<br>of a<br>7, | TDATA7 acts as a<br>input controlling th<br>transmitted to the | e signal                                                                                |

|       |       |                  |     | TPOS7 TNEG7                                                                                                                                                                                                                                                                               | Selection                                                                                                        |                                            |                                                                | e signal<br>line interface.<br>und in unipolar<br>nich is 1.544 MHz<br>S7 and TNEG7, or |

|       |       |                  |     | 0 0                                                                                                                                                                                                                                                                                       | Space                                                                                                            |                                            |                                                                |                                                                                         |

|       |       |                  |     | 1 0                                                                                                                                                                                                                                                                                       | Positive N                                                                                                       | 1ark                                       |                                                                |                                                                                         |

|       |       |                  |     | 0 1                                                                                                                                                                                                                                                                                       | Negative<br>Mark                                                                                                 |                                            |                                                                |                                                                                         |

|       |       |                  |     | 1 1                                                                                                                                                                                                                                                                                       | Space                                                                                                            |                                            |                                                                |                                                                                         |

|       |       |                  |     | Transmit Negative                                                                                                                                                                                                                                                                         | Data (Port 7                                                                                                     | 7).                                        |                                                                |                                                                                         |

| 6     | C2    | TNEG7            | DI  | This digital framer int<br>as the negative side<br>data input pair, TPOS<br>which controls the sin<br>to the line interface.                                                                                                                                                              | of the bipola<br>S7 and TNE                                                                                      | ar<br>EG7,                                 | Tie TNEG7 to grou<br>mode.                                     | und in unipolar                                                                         |

|       |       |                  |     | Transmit Clock Inp                                                                                                                                                                                                                                                                        | ut (Port 7).                                                                                                     |                                            |                                                                |                                                                                         |

|       |       |                  |     | During normal opera<br>for T1/J1 operation, a<br>TDATA7, are sample                                                                                                                                                                                                                       | and 2.048 N                                                                                                      | /Hz fo                                     | r E1 operation. TPO                                            |                                                                                         |

|       |       |                  |     |                                                                                                                                                                                                                                                                                           | TCLK                                                                                                             | 0                                          | perating Mode                                                  |                                                                                         |

|       |       |                  |     |                                                                                                                                                                                                                                                                                           | Clocked                                                                                                          | Norm                                       | al operation                                                   |                                                                                         |

| 7     | D4    | TCLK7            | DI  |                                                                                                                                                                                                                                                                                           | L                                                                                                                | state                                      | r outputs three<br>d, but powered on<br>dundancy.              |                                                                                         |

|       |       |                  |     |                                                                                                                                                                                                                                                                                           | н                                                                                                                | state<br>down                              | r outputs three<br>d and powered<br>for reduced<br>r draw.     |                                                                                         |

|       |       |                  |     | <b>NOTE:</b> The Transmit All Ones (TAOS) generator uses MCLK as a timing reference. In order to assure that the output frequency is within specification limits, MCLK must have the applicable stability.                                                                                |                                                                                                                  |                                            |                                                                |                                                                                         |

|       |       |                  |     | Receive Positive Da                                                                                                                                                                                                                                                                       | ata/Receive                                                                                                      | Data                                       | Output (Port 6).                                               |                                                                                         |

| 8     | D3    | RPOS6/<br>RDATA6 | DO  | RPOS6 acts as the p<br>the bipolar data outp<br>and RNEG6, recover<br>interface.                                                                                                                                                                                                          | ut pair, RPC                                                                                                     | DS6                                        | RDATA6 acts as a of the data recove interface.                 | single NRZ output<br>red from the line                                                  |

#### Table 1. LXT3108 Pin Description (Sheet 3 of 13)

| 050 | DDCA | Symbol           |     | Description                                                                                                                                                                                                        |                                                                                                  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |                                 |  |

|-----|------|------------------|-----|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------|--|--|--|--|--|--|--|--|--|--|--|--|--|--|--|---------------------------------|--|

| QFP | PBGA | Symbol           | I/O | Bipolar Mode                                                                                                                                                                                                       | Unipolar Mode                                                                                    |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |                                 |  |

| -   |      |                  |     | Receive Negative Data (Port 6).                                                                                                                                                                                    |                                                                                                  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |                                 |  |

| 9   | D1   | RNEG6/<br>RBPV6  | DO  | RNEG6 acts as the negative side of<br>the bipolar data output pair, RPOS6<br>and RNEG6, recovered from the line<br>interface.                                                                                      | RBPV6 indicates receive BPV for port<br>6.                                                       |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |                                 |  |

| 10  | D2   | RCLK6            | DO  | Receive Clock Output (Port 6). This of<br>recovered clock from the signal receive<br>conditions there is a transition from the<br>recovered data) to an internal clock (sy<br>CLAD circuitry) at the RCLK6 output. | e RCLK6 signal (derived from the                                                                 |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |                                 |  |

|     |      |                  |     | Transmit Positive Data/Transmit Dat                                                                                                                                                                                | a Input (Port 6).                                                                                |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |                                 |  |

| 11  | E4   | TPOS6/<br>TDATA6 | DI  | TPOS6 acts as the positive side of<br>the bipolar data input pair, TPOS6<br>and TNEG6, which controls the signal<br>transmitted to the line interface.                                                             | TDATA6 acts as a single NRZ input data controlling the signal transmitted to the line interface. |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |                                 |  |

|     |      |                  |     | Transmit Negative Data (Port 6).                                                                                                                                                                                   | •                                                                                                |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |                                 |  |

| 12  | E3   | TNEG6            | DI  | TNEG6 acts as the negative side of<br>the bipolar data input pair, TPOS6<br>and TNEG6, which controls the signal<br>transmitted to the line interface.                                                             | Tie TNEG6 to ground in unipolar mode.                                                            |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |                                 |  |

| 13  | E1   | TCLK6            | DI  | Transmit Clock Input (Port 6).                                                                                                                                                                                     |                                                                                                  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |                                 |  |

| -   |      |                  |     | Receive Positive Data/Receive Data                                                                                                                                                                                 | Output (Port 5).                                                                                 |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |                                 |  |

| 14  | E2   | RPOS5/<br>RDATA5 | DO  | RPOS5 acts as the positive side of<br>the bipolar data output pair, RPOS5<br>and RNEG5, recovered from the line<br>interface.                                                                                      | RDATA5 acts as a single NRZ output<br>of the data recovered from the line<br>interface.          |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |                                 |  |

| -   |      |                  |     |                                                                                                                                                                                                                    |                                                                                                  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  | Receive Negative Data (Port 5). |  |

| 15  | F4   | RNEG5/<br>RBPV5  | DO  | RNEG5 acts as the negative side of<br>the bipolar data output pair, RPOS5<br>and RNEG5, recovered from the line<br>interface.                                                                                      | RBPV5 indicates Receive BPV for port 5.                                                          |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |                                 |  |

| 16  | F1   | RCLK5            | DO  | Receive Clock Output (Port 5).                                                                                                                                                                                     | •                                                                                                |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |                                 |  |

|     |      |                  |     | Transmit Positive Data/Transmit Dat                                                                                                                                                                                | a Input (Port 5).                                                                                |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |                                 |  |

| 17  | F3   | TPOS5/<br>TDATA5 | DI  | TPOS5 acts as the positive side of<br>the bipolar data input pair, TPOS5<br>and TNEG5, which controls the signal<br>transmitted to the line interface.                                                             | TDATA5 acts as a single NRZ input data controlling the signal transmitted to the line interface. |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |                                 |  |

|     |      |                  |     | Transmit Negative Data (Port 5).                                                                                                                                                                                   |                                                                                                  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |                                 |  |

| 18  | F2   | TNEG5            | DI  | TNEG5 acts as the negative side of<br>the bipolar data input pair, TPOS5<br>and TNEG5, which controls the signal<br>transmitted to the line interface.                                                             | Tie TNEG5 to ground in unipolar mode.                                                            |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |                                 |  |

| 19  | G4   | TCLK5            | DI  | Transmit Clock Input (Port 5).                                                                                                                                                                                     | ·                                                                                                |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |                                 |  |

|     |      |                  |     | Receive Positive Data/Receive Data                                                                                                                                                                                 | Output (Port 4).                                                                                 |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |                                 |  |

| 20  | G1   | RPOS4/<br>RDATA4 | DO  | RPOS4 acts as the positive side of<br>the bipolar data output pair, RPOS4<br>and RNEG4, recovered from the line<br>interface.                                                                                      | RDATA4 acts as a single NRZ output<br>of the data recovered from the line<br>interface.          |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |                                 |  |

#### Table 1. LXT3108 Pin Description (Sheet 4 of 13)

| QFP | BRCA | Symbol           | I/O | Description                                                                                                                                            |                                                                                                  |  |

|-----|------|------------------|-----|--------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------|--|

| QFF | PBGA | Symbol           | 1/0 | Bipolar Mode                                                                                                                                           | Unipolar Mode                                                                                    |  |

|     |      |                  |     | Receive Negative Data (Port 4).                                                                                                                        |                                                                                                  |  |

| 21  | G3   | RNEG4/<br>RBPV4  | DO  | RNEG4 acts as the negative side of<br>the bipolar data output pair, RPOS4<br>and RNEG4, recovered from the line<br>interface.                          | RBPV4 indicates Receive BPV for port 4.                                                          |  |

| 22  | G2   | RCLK4            | DO  | Receive Clock Output (Port 4).                                                                                                                         |                                                                                                  |  |

|     |      |                  |     | Transmit Positive Data/Transmit Dat                                                                                                                    | a Input (Port 4).                                                                                |  |

| 23  | H4   | TPOS4/<br>TDATA4 | DI  | TPOS4 acts as the positive side of<br>the bipolar data input pair, TPOS4<br>and TNEG4, which controls the signal<br>transmitted to the line interface. | TDATA4 acts as a single NRZ input data controlling the signal transmitted to the line interface. |  |

|     |      |                  |     | Transmit Negative Data (Port 4).                                                                                                                       |                                                                                                  |  |

| 24  | H1   | TNEG4            | DI  | TNEG4 acts as the negative side of<br>the bipolar data input pair, TPOS4<br>and TNEG4, which controls the signal<br>transmitted to the line interface. | Tie TNEG4 to ground in unipolar mode.                                                            |  |

| 25  | H3   | TCLK4            | DI  | Transmit Clock Input (Port 4).                                                                                                                         |                                                                                                  |  |

| 26  | H2   | GNDIO            | S   | Ground (I/O).                                                                                                                                          |                                                                                                  |  |

| 27  | J1   | VCCIO            | S   | Power (I/O).                                                                                                                                           |                                                                                                  |  |

|     |      |                  |     | Receive Positive Data/Receive Data Output (Port 3).                                                                                                    |                                                                                                  |  |

| 28  | J4   | RPOS3/<br>RDATA3 | DO  | RPOS3 acts as the positive side of<br>the bipolar data output pair, RPOS3<br>and RNEG3, recovered from the line<br>interface.                          | RDATA3 acts as a single NRZ output<br>of the data recovered from the line<br>interface.          |  |

|     |      |                  |     | Receive Negative Data (Port 3).                                                                                                                        |                                                                                                  |  |

| 29  | J3   | RNEG3/<br>RBPV3  | DO  | RNEG3 acts as the negative side of<br>the bipolar data output pair, RPOS3<br>and RNEG3, recovered from the line<br>interface.                          | This output indicates Receive BPV for port 3.                                                    |  |

| 30  | J2   | RCLK3            | DO  | Receive Clock Output (Port 3).                                                                                                                         |                                                                                                  |  |

|     |      |                  |     | Transmit Positive Data/Transmit Dat                                                                                                                    | a Input (Port 3).                                                                                |  |

| 31  | K1   | TPOS3/<br>TDATA3 | DI  | TPOS3 acts as the positive side of<br>the bipolar data input pair, TPOS3<br>and TNEG3, which controls the signal<br>transmitted to the line interface. | TDATA3 acts as a single NRZ input data controlling the signal transmitted to the line interface. |  |

|     |      |                  |     | Transmit Negative Data (Port 3).                                                                                                                       | •                                                                                                |  |

| 32  | K4   | TNEG3            | DI  | TNEG3 acts as the negative side of<br>the bipolar data input pair, TPOS3<br>and TNEG3, which controls the signal<br>transmitted to the line interface. | Tie TNEG3 to ground in unipolar mode.                                                            |  |

| 33  | K3   | TCLK3            | DI  | Transmit Clock Input (Port 3).                                                                                                                         |                                                                                                  |  |

|     |      |                  |     | Receive Positive Data/Receive Data Output (Port 2).                                                                                                    |                                                                                                  |  |

| 34  | L1   | RPOS2/<br>RDATA2 | DO  | RPOS2 acts as the positive side of<br>the bipolar data output pair, RPOS2<br>and RNEG2, recovered from the line<br>interface.                          | RDATA2 acts as a single NRZ output<br>of the data recovered from the line<br>interface.          |  |

#### Table 1. LXT3108 Pin Description (Sheet 5 of 13)

| QFP | PBGA | Symbol           | I/O | Desci                                                                                                                                                                                                              | ription                                                                                          |  |

|-----|------|------------------|-----|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------|--|

| WFF | PBGA | Symbol           | 1/0 | Bipolar Mode                                                                                                                                                                                                       | Unipolar Mode                                                                                    |  |

|     |      |                  |     | Receive Negative Data (Port 2).                                                                                                                                                                                    |                                                                                                  |  |

| 35  | К2   | RNEG2/<br>RBPV2  | DO  | RNEG2 acts as the negative side of<br>the bipolar data output pair, RPOS2<br>and RNEG2, recovered from the line<br>interface.                                                                                      | This output indicates Receive BPV for port 2.                                                    |  |

| 36  | L4   | RCLK2            | DO  | Receive Clock Output (Port 2).                                                                                                                                                                                     |                                                                                                  |  |

|     |      |                  |     | Transmit Positive Data/Transmit Dat                                                                                                                                                                                | a Input (Port 2).                                                                                |  |

| 37  | L3   | TPOS2/<br>TDATA2 | DI  | TPOS2 acts as the positive side of<br>the bipolar data input pair, TPOS2<br>and TNEG2, which controls the signal<br>transmitted to the line interface.                                                             | TDATA2 acts as a single NRZ input data controlling the signal transmitted to the line interface. |  |

|     |      |                  |     | Transmit Negative Data (Port 2).                                                                                                                                                                                   |                                                                                                  |  |

| 38  | M1   | TNEG2            | DI  | TNEG2 acts as the negative side of<br>the bipolar data input pair, TPOS2<br>and TNEG2, which controls the signal<br>transmitted to the line interface.                                                             | Tie TNEG2 to ground in unipolar mode.                                                            |  |

| 39  | L2   | TCLK2            | DI  | Transmit Clock Input (port 2).                                                                                                                                                                                     |                                                                                                  |  |

|     |      |                  |     | Receive Positive Data/Receive Data                                                                                                                                                                                 | Output (Port 1).                                                                                 |  |

| 40  | M4   | RPOS1/<br>RDATA1 | DO  | RPOS1 acts as the positive side of<br>the bipolar data output pair, RPOS1<br>and RNEG1, recovered from the line<br>interface.                                                                                      | RDATA1 acts as a single NRZ output<br>of the data recovered from the line<br>interface.          |  |

|     |      |                  |     | Receive Negative Data (Port 1).                                                                                                                                                                                    |                                                                                                  |  |

| 41  | МЗ   | RNEG1/<br>RBPV1  | DO  | RNEG1 acts as the negative side of<br>the bipolar data output pair, RPOS1<br>and RNEG1, recovered from the line<br>interface.                                                                                      | This output indicates Receive BPV for port 0.                                                    |  |

| 42  | N1   | RCLK1            | DO  | Receive Clock Output (Port 1). This of<br>recovered clock from the signal receive<br>conditions there is a transition from the<br>recovered data) to an internal clock (sy<br>CLAD circuitry) at the RCLK1 output. | ed at RTIP1 and RRING1. Under LOS<br>RCLK1 signal (derived from the                              |  |

|     |      |                  |     | Transmit Positive Data/Transmit Dat                                                                                                                                                                                | a Input (Port 1).                                                                                |  |

| 43  | M2   | TPOS1/<br>TDATA1 | DI  | TPOS1 acts as the positive side of<br>the bipolar data input pair, TPOS1<br>and TNEG1, which controls the signal<br>transmitted to the line interface.                                                             | TDATA1 acts as a single NRZ input data controlling the signal transmitted to the line interface. |  |

|     |      |                  |     | Transmit Negative Data (Port 1).                                                                                                                                                                                   |                                                                                                  |  |

| 44  | N3   | TNEG1            | DI  | TNEG1 acts as the negative side of<br>the bipolar data input pair, TPOS1<br>and TNEG1, which controls the signal<br>transmitted to the line interface.                                                             | Tie TNEG1 to ground in unipolar mode.                                                            |  |

| 45  | P1   | TCLK1            | DI  | Transmit Clock Input (Port 1).                                                                                                                                                                                     |                                                                                                  |  |

|     |      |                  |     | Receive Positive Data/Receive Data                                                                                                                                                                                 | Output (Port 0).                                                                                 |  |

| 46  | N2   | RPOS0/<br>RDATA0 | DO  | RPOS0 acts as the positive side of<br>the bipolar data output pair, RPOS0<br>and RNEG0, recovered from the line<br>interface.                                                                                      | RDATA0 acts as a single NRZ output<br>of the data recovered from the line<br>interface.          |  |

\_

#### Table 1. LXT3108 Pin Description (Sheet 6 of 13)

| QFP | PBGA | Symbol           | 1/0 | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                                                                  |  |

|-----|------|------------------|-----|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------|--|