# int<sub>el</sub> SK70720 and SK70721 Multi-Rate DSL Data Pump Chip Set

### Datasheet

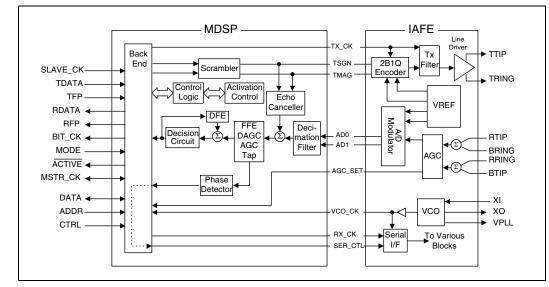

The Multi-Rate DSL Data Pump is a complete, variable-rate transceiver that provides full duplex communication on two wires using echo-canceller-with-hybrid and 2B1Q line coding technology. It provides symmetrical line rates from 272 to 784 kbps. Performance specifications are defined at the 272, 400, 528, and 784 kbps data rates which provide a payload of 4, 6, 8, or 12 64 kbps channels with a 16 kbps overhead channel. The MDSL Data Pump also supports applications where the payload is unchannellized.

The MDSL Data Pump chip set consists of two devices:

- SK70720 MDSL Digital Signal Processor (MDSP)

- SK70721 Integrated Analog Front-End (IAFE)

The IAFE is a fully integrated CMOS analog front-end IC which includes transmitter line drivers, filters, and 2B1Q encoding functions along with the receiver hybrid, AGC, A-to-D converter modulator and VCXO functions. The MDSP incorporates all digital signal processing required for A/D conversion, echo-cancellation, data scrambling and adaptive equalization as well as transceiver activation state machine control.

# **Applications**

- High speed residential Internet access

- Extended Range fractional T1/E1 transport WAN access for LAN routers

- 4 to 12-channel digital pair-gain

- Wireless base station to switch access

- Video Conferencing

# intel

Information in this document is provided in connection with Intel<sup>®</sup> products. No license, express or implied, by estoppel or otherwise, to any intellectual property rights is granted by this document. Except as provided in Intel's Terms and Conditions of Sale for such products, Intel assumes no liability whatsoever, and Intel disclaims any express or implied warranty, relating to sale and/or use of Intel products including liability or warranties relating to fitness for a particular purpose, merchantability, or infringement of any patent, copyright or other intellectual property right. Intel products are not intended for use in medical, life saving, or life sustaining applications.

Intel may make changes to specifications and product descriptions at any time, without notice.

Designers must not rely on the absence or characteristics of any features or instructions marked "reserved" or "undefined." Intel reserves these for future definition and shall have no responsibility whatsoever for conflicts or incompatibilities arising from future changes to them.

The SK70720 and SK70721 may contain design defects or errors known as errata which may cause the product to deviate from published specifications. Current characterized errata are available on request.

Contact your local Intel sales office or your distributor to obtain the latest specifications and before placing your product order.

Copies of documents which have an ordering number and are referenced in this document, or other Intel literature may be obtained by calling 1-800-548-4725 or by visiting Intel's website at http://www.intel.com.

Copyright © Intel Corporation, 2001

\*Third-party brands and names are the property of their respective owners.

| 1.0 | Feat                   | Features                                                                                           |    |  |  |  |  |

|-----|------------------------|----------------------------------------------------------------------------------------------------|----|--|--|--|--|

| 2.0 | Pin /                  | Assignment and Signal Descriptions                                                                 | 9  |  |  |  |  |

| 3.0 | Functional Description |                                                                                                    |    |  |  |  |  |

|     | 3.1                    | Framing                                                                                            |    |  |  |  |  |

|     |                        | 3.1.1 Fixed Data Rate Mode                                                                         | 17 |  |  |  |  |

|     |                        | 3.1.2 Variable Data Rate Mode                                                                      |    |  |  |  |  |

|     | 3.2                    | Component Description                                                                              |    |  |  |  |  |

|     |                        | 3.2.1 Integrated Analog Front End (IAFE)                                                           |    |  |  |  |  |

|     |                        | 3.2.2 MDSL Digital Signal Processor (MDSP)                                                         |    |  |  |  |  |

|     |                        | 3.2.3 MDSP/IAFE Interface                                                                          |    |  |  |  |  |

|     | 3.3                    | Line Interface                                                                                     |    |  |  |  |  |

|     | 3.4                    | MDSL Data Interface                                                                                |    |  |  |  |  |

|     |                        | 3.4.1 Clock Distribution                                                                           |    |  |  |  |  |

|     |                        | 3.4.2 Fixed Data Rate Operation                                                                    |    |  |  |  |  |

|     |                        | 3.4.3 Variable Data Rate Operation                                                                 |    |  |  |  |  |

|     |                        | 3.4.4 Data Interface Timing                                                                        |    |  |  |  |  |

|     | - <b>-</b>             | 3.4.5 Loopbacks                                                                                    |    |  |  |  |  |

|     | 3.5                    | Microprocessor Interface (MDSP)                                                                    |    |  |  |  |  |

|     |                        | 3.5.1 Control Pins                                                                                 |    |  |  |  |  |

|     |                        | 3.5.2 Register Definitions                                                                         |    |  |  |  |  |

|     | 0.0                    | 3.5.3 Register Access                                                                              |    |  |  |  |  |

|     | 3.6                    | Activation                                                                                         |    |  |  |  |  |

|     |                        | 3.6.1 Master Mode Activation Sequence                                                              |    |  |  |  |  |

|     |                        | <ul><li>3.6.2 Slave Mode Activation Sequence</li><li>3.6.3 Synchronization State Machine</li></ul> |    |  |  |  |  |

| 4.0 | Ann                    | -                                                                                                  |    |  |  |  |  |

| 4.0 | ••                     | lication Information                                                                               |    |  |  |  |  |

|     | 4.1                    | PCB Layout                                                                                         |    |  |  |  |  |

|     |                        | 4.1.1 Digital Section                                                                              |    |  |  |  |  |

|     |                        | 4.1.2 Analog Section                                                                               |    |  |  |  |  |

| 5.0 | Test                   | Specifications                                                                                     | 40 |  |  |  |  |

| 6.0 | Regi                   | ister Definitions                                                                                  | 52 |  |  |  |  |

|     |                        | 6.0.1 WR0—Main Control Register                                                                    |    |  |  |  |  |

|     |                        | 6.0.2 WR2—Interrupt Mask Register                                                                  |    |  |  |  |  |

|     |                        | 6.0.3 WR3—Read Coefficient Select Register                                                         |    |  |  |  |  |

|     |                        | 6.0.4 RD0—Main Status Register                                                                     |    |  |  |  |  |

|     |                        | 6.0.5 RD1—Receiver Gain Word Register                                                              |    |  |  |  |  |

|     |                        | 6.0.6 RD2—Noise Margin Register                                                                    |    |  |  |  |  |

|     |                        | 6.0.7 RD3 (LSB), RD4 (MSB)—Coefficient Read Register                                               |    |  |  |  |  |

|     |                        | 6.0.8 RD5—Activation Status Register                                                               |    |  |  |  |  |

|     |                        | 6.0.9 RD6—Receive Step Gain Register                                                               | 57 |  |  |  |  |

# intel®

| 7.0 | Mechanical Specifications | 59 |

|-----|---------------------------|----|

|-----|---------------------------|----|

# **Figures**

| 1                                                  | SK70720 and SK70721 Block Diagram                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 8                                                                  |

|----------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------|

| 2                                                  | SK70721 IAFE Pin Locations                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 9                                                                  |

| 3                                                  | SK70720 MDSP Pin Assignments                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 11                                                                 |

| 4                                                  | MDSL System Data Transport                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 17                                                                 |

| 5                                                  | MDSL Frame                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 17                                                                 |

| 6                                                  | Variable Data Rate Mode Framing                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 18                                                                 |

| 7                                                  | MDSP/IAFE Interface – Relative Timing                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 22                                                                 |

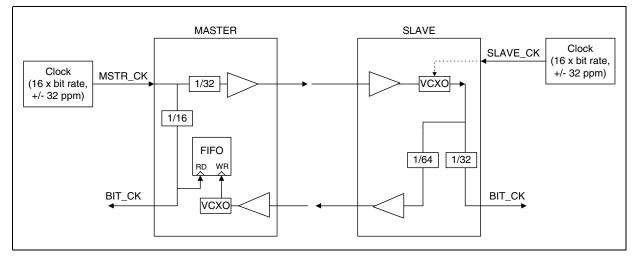

| 8                                                  | MDSL Clock Distribution In Master and Slave Modes                                                                                                                                                                                                                                                                                                                                                                                                                                        | 23                                                                 |

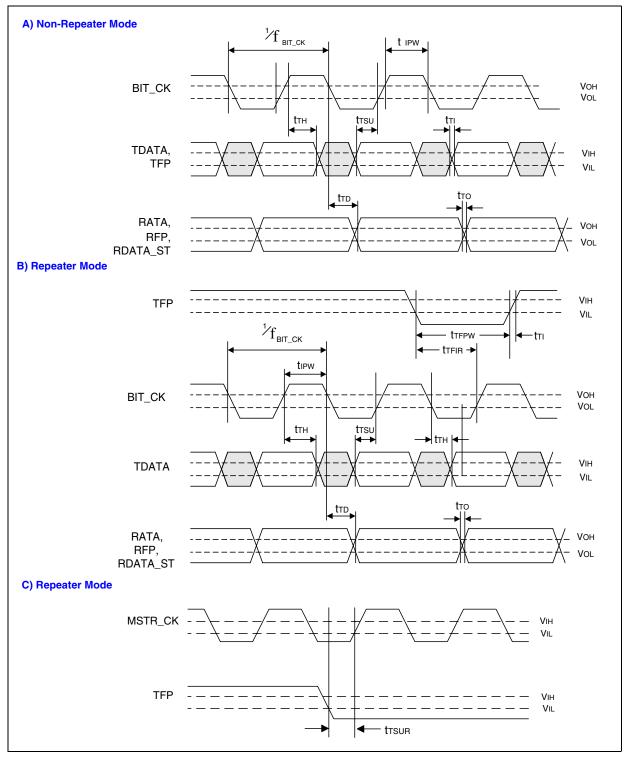

| 9                                                  | MDSP Digital Data Interface Timing                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 25                                                                 |

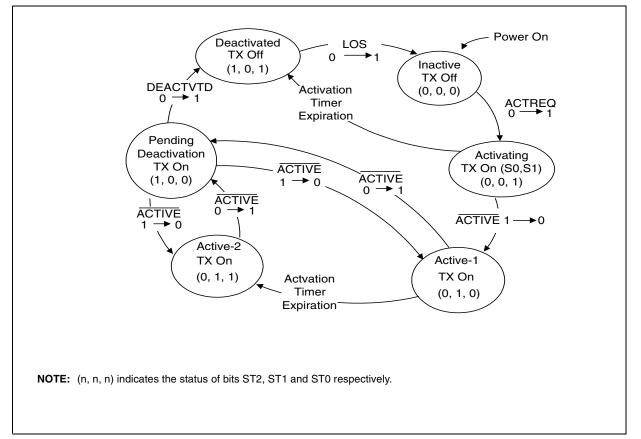

| 10                                                 | Master Mode Activation State Machine                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 29                                                                 |

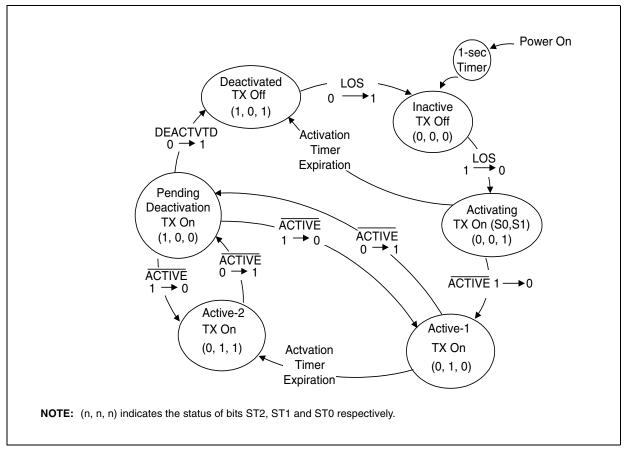

| 11                                                 | Slave Mode Activation State Machine                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                                    |

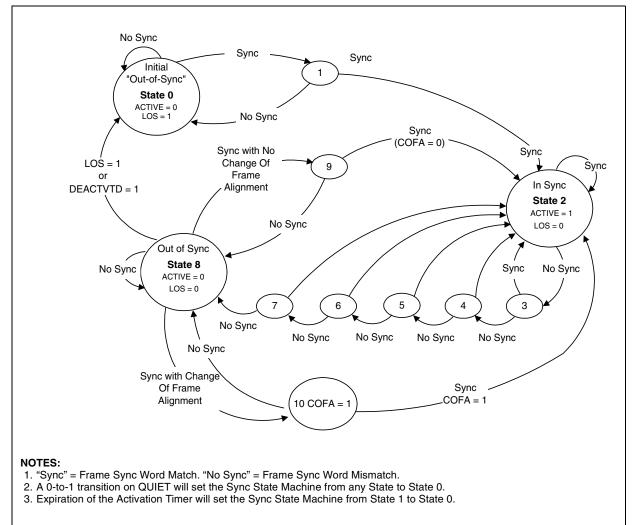

| 12                                                 | MDSL Synchronization State Machine                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 32                                                                 |

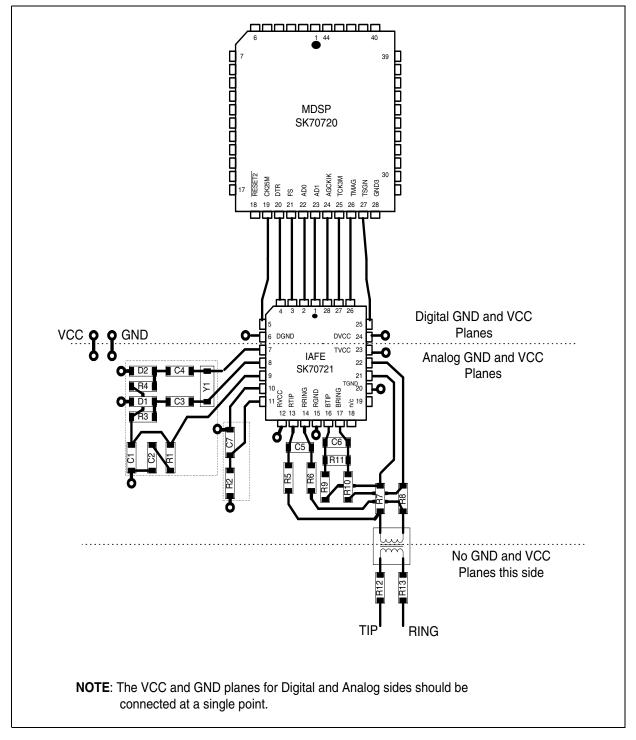

| 13                                                 | PCB Layout Guidelines                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                                    |

|                                                    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                    |

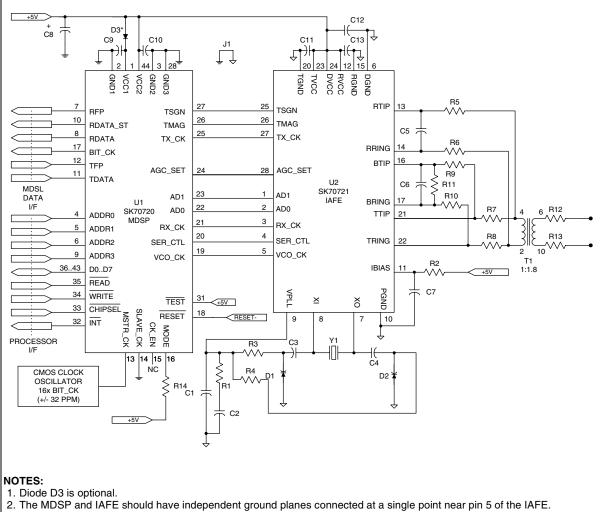

| 14                                                 | Typical Application for Master Mode Operation (Microprocessor Interface Mo<br>36                                                                                                                                                                                                                                                                                                                                                                                                         |                                                                    |

|                                                    | Typical Application for Master Mode Operation (Microprocessor Interface Mo                                                                                                                                                                                                                                                                                                                                                                                                               | ode).                                                              |

| 14                                                 | Typical Application for Master Mode Operation (Microprocessor Interface Mo<br>36                                                                                                                                                                                                                                                                                                                                                                                                         | ode) .<br>37                                                       |

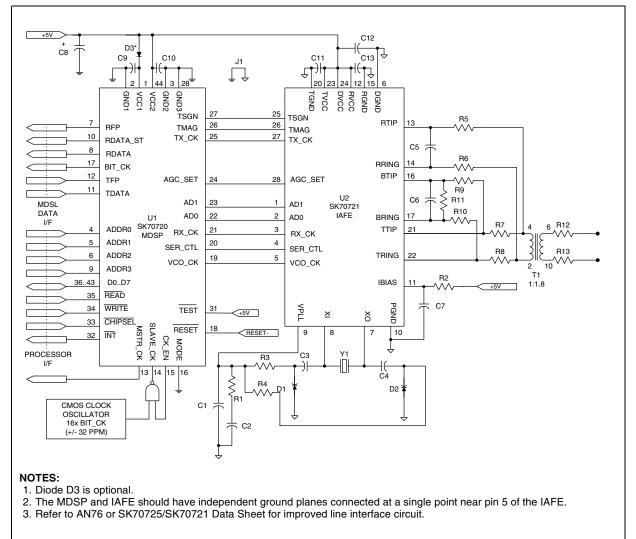

| 14<br>15                                           | Typical Application for Master Mode Operation (Microprocessor Interface Mo<br>36<br>Typical Application for Slave Mode Operation                                                                                                                                                                                                                                                                                                                                                         | ode) .<br>37<br>39                                                 |

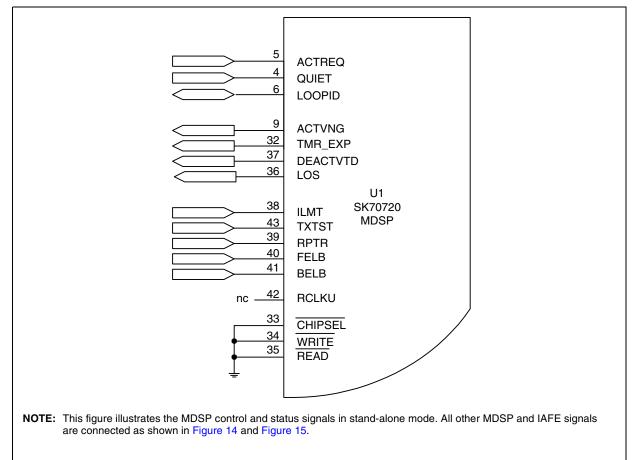

| 14<br>15<br>16                                     | Typical Application for Master Mode Operation (Microprocessor Interface Mo<br>36<br>Typical Application for Slave Mode Operation<br>MDSP Control and Status Signals (Stand-alone Mode)                                                                                                                                                                                                                                                                                                   | ode) .<br>37<br>39<br>41                                           |

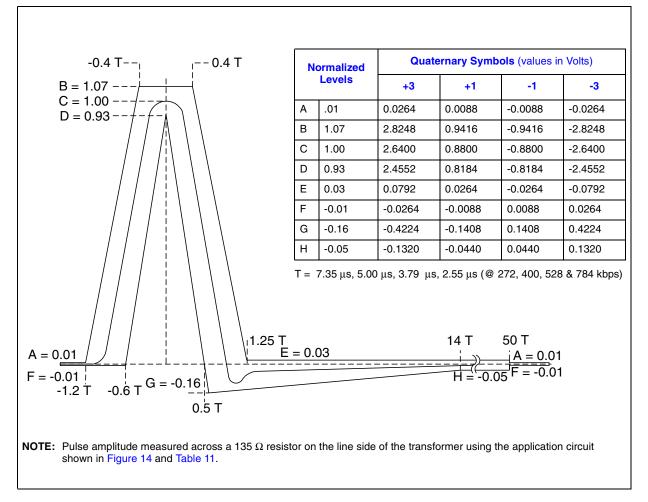

| 14<br>15<br>16<br>17                               | Typical Application for Master Mode Operation (Microprocessor Interface Mo<br>36<br>Typical Application for Slave Mode Operation<br>MDSP Control and Status Signals (Stand-alone Mode)<br>IAFE Normalized Pulse Amplitude Transmit Template                                                                                                                                                                                                                                              | ode) .<br>37<br>39<br>41<br>42                                     |

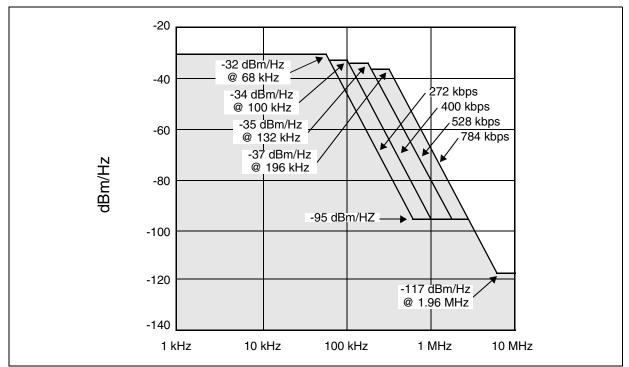

| 14<br>15<br>16<br>17<br>18                         | Typical Application for Master Mode Operation (Microprocessor Interface Mo<br>36<br>Typical Application for Slave Mode Operation<br>MDSP Control and Status Signals (Stand-alone Mode)<br>IAFE Normalized Pulse Amplitude Transmit Template<br>Transmit Power Spectral Density—Upper Bound                                                                                                                                                                                               | ode) .<br>37<br>39<br>41<br>42<br>43                               |

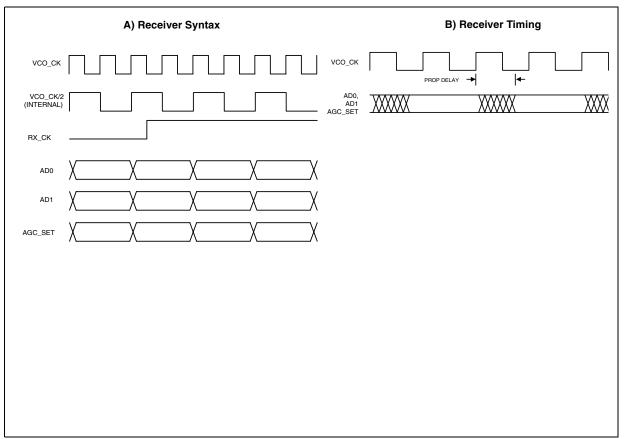

| 14<br>15<br>16<br>17<br>18<br>19                   | Typical Application for Master Mode Operation (Microprocessor Interface Mo<br>36<br>Typical Application for Slave Mode Operation<br>MDSP Control and Status Signals (Stand-alone Mode)<br>IAFE Normalized Pulse Amplitude Transmit Template<br>Transmit Power Spectral Density—Upper Bound<br>IAFE Receiver Syntax and Timing                                                                                                                                                            | ode) .<br>37<br>39<br>41<br>42<br>43<br>44                         |

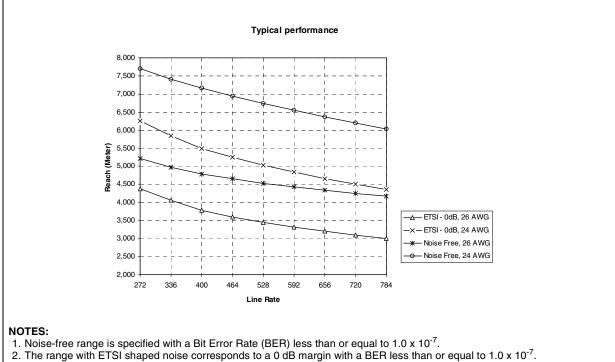

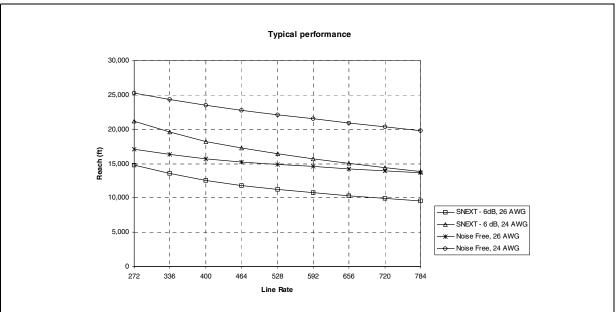

| 14<br>15<br>16<br>17<br>18<br>19<br>20             | Typical Application for Master Mode Operation (Microprocessor Interface Mo<br>36<br>Typical Application for Slave Mode Operation<br>MDSP Control and Status Signals (Stand-alone Mode)<br>IAFE Normalized Pulse Amplitude Transmit Template<br>Transmit Power Spectral Density—Upper Bound<br>IAFE Receiver Syntax and Timing<br>Typical Performance vs. Line Rate and Cable Gauge (Metric)<br>Typical Performance vs. Line Rate and Cable Gauge (English)<br>MDSL Data Interface Timing | ode) .<br>37<br>39<br>41<br>42<br>43<br>43<br>45<br>48             |

| 14<br>15<br>16<br>17<br>18<br>19<br>20<br>21       | Typical Application for Master Mode Operation (Microprocessor Interface Mo<br>36<br>Typical Application for Slave Mode Operation<br>MDSP Control and Status Signals (Stand-alone Mode)<br>IAFE Normalized Pulse Amplitude Transmit Template<br>Transmit Power Spectral Density—Upper Bound<br>IAFE Receiver Syntax and Timing<br>Typical Performance vs. Line Rate and Cable Gauge (Metric)<br>Typical Performance vs. Line Rate and Cable Gauge (English)                               | ode) .<br>37<br>39<br>41<br>42<br>43<br>43<br>45<br>48             |

| 14<br>15<br>16<br>17<br>18<br>19<br>20<br>21<br>22 | Typical Application for Master Mode Operation (Microprocessor Interface Mo<br>36<br>Typical Application for Slave Mode Operation<br>MDSP Control and Status Signals (Stand-alone Mode)<br>IAFE Normalized Pulse Amplitude Transmit Template<br>Transmit Power Spectral Density—Upper Bound<br>IAFE Receiver Syntax and Timing<br>Typical Performance vs. Line Rate and Cable Gauge (Metric)<br>Typical Performance vs. Line Rate and Cable Gauge (English)<br>MDSL Data Interface Timing | ode) .<br>37<br>39<br>41<br>42<br>43<br>43<br>44<br>45<br>48<br>50 |

# **Tables**

| 1  | SK70721 IAFE Pin Assignments/Signal Descriptions             |    |

|----|--------------------------------------------------------------|----|

| 2  | SK70720 MDSP Pin Assignments/Signal Descriptions             | 12 |

| 3  | Data Rate and Frame Length Examples                          |    |

| 4  | Minimum and Maximum Data Rate/Frame Time Examples            |    |

| 5  | IAFE Transmit Control                                        |    |

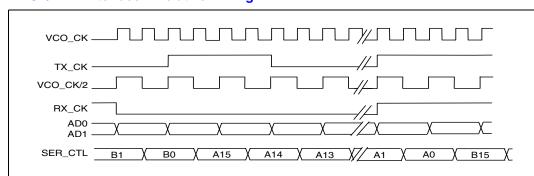

| 6  | MDSP/IAFE Serial Port Word Bit Definitions (Figure 7)        | 21 |

| 7  | State Machine Timer Durations (Figure 10 and Figure 11)      |    |

| 8  | Data Pump Activation States                                  |    |

| 9  | Activation and Synchronization States                        |    |

| 10 | Components for Suggested Circuitry (Figure 14 and Figure 15) |    |

| 11 | Transformer Specifications                                   |    |

|    | (Figure 14 and Figure 15, Reference T1)38                    |    |

| 12 | Crystal Specifications                                       |    |

|    | (Figure 14 and Figure 15, Reference Y1)38                    |    |

| 13 | IAFE Absolute Maximum Ratings                                |    |

| 14 | IAFE Recommended Operating Conditions                        |    |

|    |                                                              |    |

# intel®

| 15 | IAFE DC Electrical Characteristics (Over Recommended Range)               | 40                 |

|----|---------------------------------------------------------------------------|--------------------|

| 16 | IAFE Transmitter Electrical Parameters (Over Recommended Range)           | 41                 |

| 17 | IAFE Receiver Electrical Parameters (Over Recommended Range)              | 42                 |

| 18 | MDSP Absolute Maximum Ratings                                             | 45                 |

| 19 | MDSP Recommended Operating Conditions                                     | 45                 |

| 20 | MDSP DC Electrical Characteristics (Over Recommended Range)               | 46                 |

| 21 | MDSL Data Interface Timing Specifications (Figure 22)                     | 46                 |

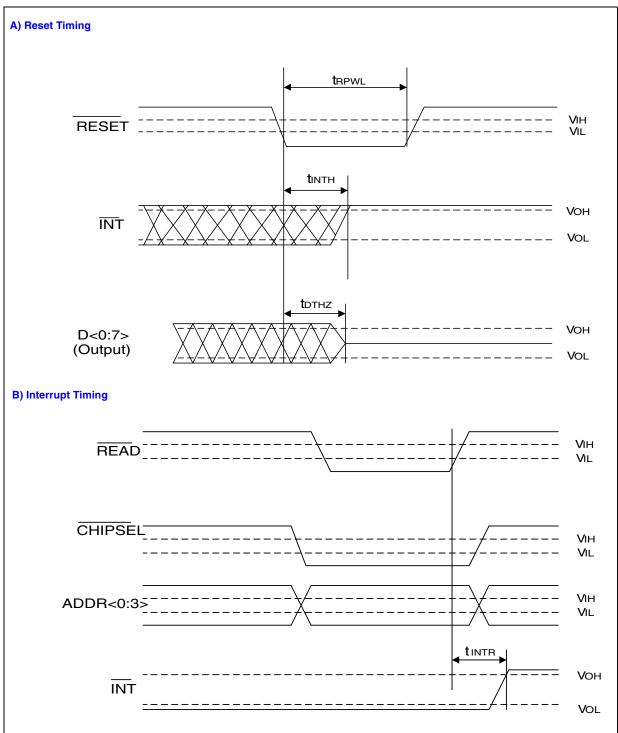

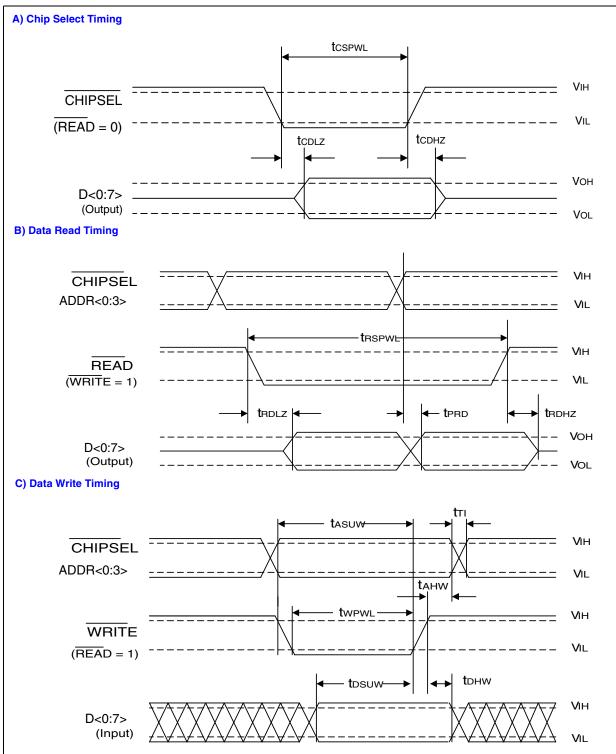

| 22 | MDSP/Microprocessor Interface Timing Specifications (Figure 19 & Figure 2 | <mark>0) 49</mark> |

| 23 | General System and Hardware Mode Timing                                   | 49                 |

| 24 | Register Summary                                                          | 52                 |

| 25 | Main Control Register WR0                                                 | 52                 |

| 26 | Interrupt Mask Register WR2                                               | 53                 |

| 27 | Read Coefficient Select Register WR3                                      | 54                 |

| 28 | Main Status Register RD0                                                  | 54                 |

| 29 | Receiver Gain Word Register                                               | 55                 |

| 30 | Noise Margin Register RD2                                                 |                    |

|    | (Noise Margin Coding)55                                                   |                    |

| 31 | Coefficient Read Register                                                 |                    |

| 32 | Activation Status Register RD5                                            |                    |

| 33 | Receiver AGC and FFE Step Gain Register RD6                               | 58                 |

|    |                                                                           |                    |

# **Revision History**

| Revision | Date | Description |

|----------|------|-------------|

|          |      |             |

|          |      |             |

|          |      |             |

# intel®

# **1.0 Features**

- Fully integrated, 2-chip transceiver

- Compliant with the following standards:

- ITU G.991.1

- ANSI Committee T1E1 .4-TR28 (T1E1.4/96-006)

- ETSI ETR -152

- Integrated line drivers, filters and hybrid circuits reduce the number of external components required

- Self-contained activation/start-up control eliminates an external microprocessor in many applications

- Parallel interface for processor control or monitoring

- Single +5V supply

- Typical power dissipation less than 500 mW—good for applications with remote power feeding

- Supports transparent repeater applications without an external processor or glue-logic

- Supports processor directed rate selection driven by receive signal level and noise margin

- Continuously adaptive echo canceller and equalizers maintain excellent transmission performance with changing noise and line characteristics

- Typical noise-free transmission range\*:

272 kbps 25.3 kft (7.7 km) on #24 AWG (0.5 mm) cable 17.1 kft (5.2 km) on #26 AWG (0.4 mm) cable <u>784 kbps</u> 19.8 kft (6.0 km) on #24 AWG (0.5 mm) cable 13.7 kft (4.2 km) on #26 AWG (0.4 mm) cable \* Refer to AN76 or SK70725/21 data sheet for details.

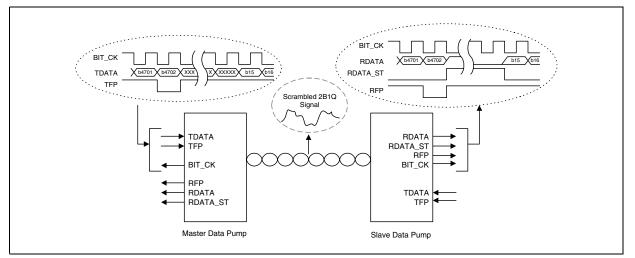

#### Figure 1. SK70720 and SK70721 Block Diagram

# 2.0 Pin Assignment and Signal Descriptions

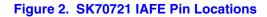

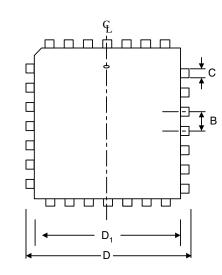

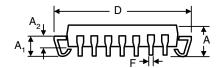

The IAFE is packaged in a 28-pin PLCC. Figure 2 shows the IAFE pin locations and Table 1 lists signal descriptions.

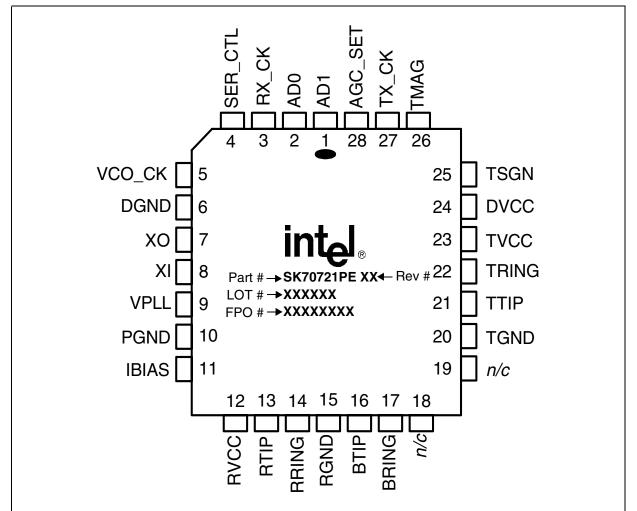

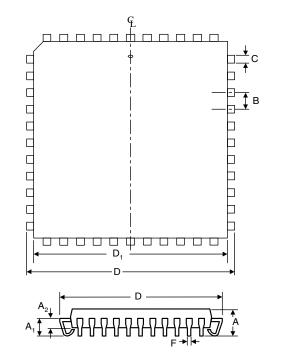

The MDSP device is packaged in a 44-pin PLCC. Figure 3 shows MDSP pin designations and Table 2 lists signal descriptions.

| Package Topside Markings |                                                                                                                       |  |  |  |  |  |

|--------------------------|-----------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| Marking                  | Definition                                                                                                            |  |  |  |  |  |

| Part #                   | Unique identifier for this product family.                                                                            |  |  |  |  |  |

| Rev #                    | Identifies the particular silicon "stepping" — refer to the specification update for additional stepping information. |  |  |  |  |  |

| Lot #                    | Identifies the batch.                                                                                                 |  |  |  |  |  |

FPO # Identifies the Finish Process Order.

#### Table 1. SK70721 IAFE Pin Assignments/Signal Descriptions

| Group           | Pin #    | Symbol  | I/O <sup>1</sup> | Description                                                                                                              |  |

|-----------------|----------|---------|------------------|--------------------------------------------------------------------------------------------------------------------------|--|

|                 | 13       | RTIP    | AI               | Peacity Tin and Ding. Dessiver differential inputs                                                                       |  |

|                 | 14       | RRING   | AI               | Receive Tip and Ring. Receiver differential inputs.                                                                      |  |

| Line            | 16       | BTIP    | AI               | Passive Palance Tin and Ping. Dessiver hybrid belance inputs                                                             |  |

| LINE            | 17       | BRING   | AI               | Receive Balance Tip and Ring. Receiver hybrid balance inputs.                                                            |  |

|                 | 21       | TTIP    | AO               | Transmit Tip and Ring. Line driver outputs.                                                                              |  |

| Γ               | 22       | TRING   | AO               |                                                                                                                          |  |

|                 | 7        | ХО      | AO               | Crystal Oscillator Input and Output. Connect a pullable crystal whose                                                    |  |

| PLL             | 8        | XI      | AI               | frequency is 32 times the bit rate between these two pins. Refer to the Applications Section for crystal specifications. |  |

|                 | 9        | VPLL    | AO               | PLL Control Voltage. Control signal for the VCXO.                                                                        |  |

| Power           | 10       | PGND    | S                | PLL Ground. 0 V.                                                                                                         |  |

|                 | 12       | RVCC    | S                | Receive Power Supply. +5 VDC (± 5%).                                                                                     |  |

|                 | 23       | TVCC    | S                | Transmit Power Supply. +5 VDC (± 5%).                                                                                    |  |

|                 | 24       | DVCC    | S                | Digital Power Supply. +5 VDC (± 5%).                                                                                     |  |

|                 | 6        | DGND    | S                | DVCC Ground. 0 V.                                                                                                        |  |

|                 | 15       | RGND    | S                | RVCC Ground. 0 V.                                                                                                        |  |

|                 | 20       | TGND    | S                | TVCC Ground. 0 V.                                                                                                        |  |

|                 | 3        | RX_CK   | DI               | Receive Baud Rate Clock Input.                                                                                           |  |

| Clock and       | 4        | SER_CTL | DI               | Serial Control Input.                                                                                                    |  |

| Control         | 5        | VCO_CK  | DO               | <b>MDSL Reference Clock Output.</b> Used as the receive timing reference for the MDSP.                                   |  |

|                 | 27       | TX_CK   | DI               | Transmit Symbol Clock Input. 16 times the transmit symbol rate.                                                          |  |

|                 | 28       | AGC_SET | DO               | AGC Adjust Output.                                                                                                       |  |

| Data Input      | 1        | AD1     | DO               | A-to-D Converter Data Line 1.                                                                                            |  |

| and             | 2        | AD0     | DO               | A-to-D Converter Data Line 0.                                                                                            |  |

| Output          | 25       | TSGN    | DI               | Transmit Quat Sign Input.                                                                                                |  |

|                 | 26       | TMAG    | DI               | Transmit Quat Magnitude.                                                                                                 |  |

| Analog<br>Input | 11       | IBIAS   | AI               | Input Bias. This input sets internal bias currents.                                                                      |  |

| No<br>Connects  | 18<br>19 | n/c     | -                | Not Connected. No internal connection                                                                                    |  |

| Package Topside Markings |                                                                                                                       |  |  |  |  |  |

|--------------------------|-----------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| Marking                  | Definition                                                                                                            |  |  |  |  |  |

| Part #                   | Unique identifier for this product family.                                                                            |  |  |  |  |  |

| Rev #                    | Identifies the particular silicon "stepping" — refer to the specification update for additional stepping information. |  |  |  |  |  |

| Lot #                    | Identifies the batch.                                                                                                 |  |  |  |  |  |

| FPO #                    | Identifies the Finish Process Order.                                                                                  |  |  |  |  |  |

| Group                  | Pin # | Symbol   | I/O <sup>4</sup> | Description                                                                                                                                                                                                                                                                                                                       |  |

|------------------------|-------|----------|------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

|                        | 1     | VCC1     | S                | Logic Power Supply. (Refer to Table 17).                                                                                                                                                                                                                                                                                          |  |

|                        | 44    | VCC2     | S                | <b>I/O Power Supply.</b> +5 VDC (± 5%).                                                                                                                                                                                                                                                                                           |  |

| Power                  | 2     | GND1     | S                | Ground 1. 0 V.                                                                                                                                                                                                                                                                                                                    |  |

|                        | 3     | GND2     | S                | Ground 2. 0 V.                                                                                                                                                                                                                                                                                                                    |  |

|                        | 28    | GND3     | S                | Ground 3. 0 V.                                                                                                                                                                                                                                                                                                                    |  |

|                        | 29    | n/c      | -                | No internal connection.                                                                                                                                                                                                                                                                                                           |  |

| Misc                   | 31    | TEST     | DI <sup>1</sup>  | Test. Reserved for factory testing. Tie High for normal operation.                                                                                                                                                                                                                                                                |  |

|                        | 18    | RESET    | DI <sup>1</sup>  | Reset. Pulse Low to initialize internal circuits.                                                                                                                                                                                                                                                                                 |  |

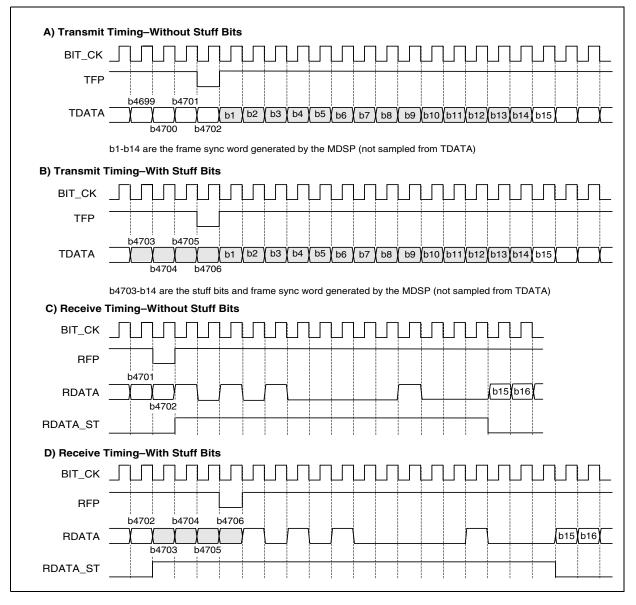

|                        | 10    | RDATA_ST | DO               | <b>Receive Data Strobe.</b> RDATA_ST goes High for 18 consecutive BIT_CK periods to indicate four stuffing bits (b4703 - 4706) and 14 frame bits (b1-14) on RDATA.                                                                                                                                                                |  |

|                        | 16    | MODE     | DI               | <b>Mode Select.</b> When MODE is High, the Data Pump operates in Master mode so that it is the link timing source and initiates activation. When MODE is Low, the Data Pump operates in Slave mode. Tied to internal pullup device. <i>The MDSP must be reset after the MODE is changed.</i>                                      |  |

|                        | 17    | BIT_CK   | DO               | <b>Bit Rate Clock.</b> This clock transfers data into and out of the MDSL data interface at the bit rate. MSTR_CK is the source of BIT_CK in Master Mode. VCO_CK is the source of BIT_CK in Slave Mode.                                                                                                                           |  |

| User Port <sup>2</sup> | 30    | ACTIVE   | DO               | <b>Link Active Indicator.</b> ACTIVE goes Low upon the receipt of two consecutive frame sync words. ACTIVE goes High when the frame sync word is not detected in six consecutive frames.                                                                                                                                          |  |

| Oser Port              | 8     | RDATA    | DO               | <b>MDSL Receive Data Output.</b> When $\overline{\text{ACTIVE}}$ is Low, the receive data including frame sync and stuff bits are output on RDATA. RDATA is High when $\overline{\text{ACTIVE}}$ is High.                                                                                                                         |  |

|                        | 7     | RFP      | DO               | <b>Receive Frame Pulse.</b> Low for one BIT_CK cycle during the last bit of the current MDSL receive frame on RDATA, either b4702 or b4706. RFP is valid when ACTIVE is Low.                                                                                                                                                      |  |

|                        | 11    | TDATA    | DI <sup>1</sup>  | <b>MDSL Transmit Data Stream.</b> When ACTIVE is Low, the Data Pump samples data on TDATA except during frame sync and stuff bits.                                                                                                                                                                                                |  |

|                        | 12    | TFP      | DI <sup>1</sup>  | <b>Transmit Frame Pulse.</b> TFP should be Low for one BIT_CK cycle the during last bit of the current MDSL frame on TDATA. <i>If TFP is pulled Low and is Low again three BIT_CK cycles later, RDATA, RFP, RDATA_ST, BIT_CK, CK_EN, and ACTIVE will tri-state until the device is reset.</i> Tied to an internal pull-up device. |  |

#### Table 2. SK70720 MDSP Pin Assignments/Signal Descriptions

The frame period is 2351 or 2353 baud times. See "Framing" on page 16.

This input is a Schmidt Triggered circuit and includes an internal pull-down device.

4. I/O column entries: DI = Digital Input; DO = Digital Output; DI/O = Digital Input/Output; AI = Analog Input; AO = Analog Output;

AI/O = Analog Input/Output; S = Supply.

| Group                                                  | Pin # | Symbol                | I/O <sup>4</sup>   | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                                                                                                                                                                                                                                                                               |  |  |

|--------------------------------------------------------|-------|-----------------------|--------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

|                                                        | 4     | QUIET                 | DI <sup>3</sup>    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | <b>Quiet Mode Enable.</b> Set High to force the MDSP into the Deactivated State. Set Low to enable activation requests (see ACTREQ).                                                                                                                                                          |  |  |

|                                                        | 5     | ACTREQ                | DI <sup>3</sup>    | Activation Request (Master mode) (no function in Slave mode). The this pin Low in Slave mode. When QUIET is Low, a rising edge on this pin initiates activation. The signal is ignored after activation (see QUIET).                                                                                                                                                                                                                                                                                                   |                                                                                                                                                                                                                                                                                               |  |  |

|                                                        | 6     | LOOPID                | DI <sup>3</sup> /O | mode). This inc<br>can be used for                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | Loop Number Input (Master mode) or Loop Number Indicator (Slave mode). This indicator is transmitted from the link Master to the slave and can be used for loop identification in systems that multiplex data onto multiple MDSL lines. In Slave mode LOOPID is valid only when ACTIVE i Low. |  |  |

| Hardware<br>Interface<br>(Hardware<br>Control<br>Mode) | 9     | ACTVNG                | DO                 | Activating State                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | te Indication. ACTVNG goes High when the MDSP is in the<br>a.                                                                                                                                                                                                                                 |  |  |

|                                                        | 32    | TMR_EXP               | DO                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | on Indicator. TMR_EXP goes High to indicate the<br>e activation timer.                                                                                                                                                                                                                        |  |  |

|                                                        | 33    | CHIPSEL               | DI <sup>3</sup>    | Chip Select                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | Assert these three pins Low to activate Hardware Control                                                                                                                                                                                                                                      |  |  |

|                                                        | 34    | WRITE                 | DI <sup>3</sup>    | Write Pulse                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | Mode. When any of them is High, the MDSP reverts                                                                                                                                                                                                                                              |  |  |

|                                                        | 35    | READ                  | DI <sup>3</sup>    | Read Pulse                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | immediately to Software Control Mode.                                                                                                                                                                                                                                                         |  |  |

|                                                        | 36    | LOS<br>(Master)       | DO                 | Loss of Signal Indicator. In Master mode, LOS goes High when<br>Pump enters the Inactive State. When the Data Pump reaches the<br>Deactivated State from Active-1 or Active-2, it starts the Loss of Si<br>(LOS) timer after Slave transmission stops. When the LOS timer e<br>the Data Pump goes to the Inactive State. When the Data Pump tr<br>from the Activating State directly to the Deactivated State, it may<br>immediately enter the Inactive State without waiting for Slave trans<br>to cease (Figure 10). |                                                                                                                                                                                                                                                                                               |  |  |

|                                                        |       | LOS<br><i>(Slave)</i> | DO                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | I <b>Indicator.</b> In Slave mode, LOS goes High immediately gnal energy is detected and the data pump enters the Figure 11).                                                                                                                                                                 |  |  |

|                                                        | 37    | DEACTVTD              | DO                 | <b>Deactivation Indicator.</b> DEACTVTD goes High when the Deactiva timer expires and the data pump goes from the Pending Deactivatio to the Deactivated state.                                                                                                                                                                                                                                                                                                                                                        |                                                                                                                                                                                                                                                                                               |  |  |

|                                                        | 38    | ILMT                  | DI <sup>1</sup>    | scrambled, "all valid sync word                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | Measurement Test. Set High to transmit a framed & 1s", 2B1Q pulse sequence. Pulse sequence will have a I. In the Slave configuration, when the ILMT mode is ata Pump may begin activation.                                                                                                    |  |  |

|                                                        | 39    | RPTR                  | DI <sup>1</sup>    | configures the adjacent device                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | e Enable. When in Master mode, setting RPTR High<br>data pump to derive timing from the MSTR_CK output of an<br>e for transparent repeater applications. The BIT_CK output<br>d to the TFP input pulse width. RPTR is ignored in Slave                                                        |  |  |

#### Table 2. SK70720 MDSP Pin Assignments/Signal Descriptions (Continued)

The frame period is 2351 or 2353 baud times. See "Framing" on page 16.

This input is a Schmidt Triggered circuit and includes an internal pull-down device.

4. I/O column entries: DI = Digital Input; DO = Digital Output; DI/O = Digital Input/Output; AI = Analog Input; AO = Analog Output;

AI/O = Analog Input/Output; S = Supply.

#### Table 2. SK70720 MDSP Pin Assignments/Signal Descriptions (Continued)

| Group                                   | Pin #                                                                                 | Symbol  | <b>I/O</b> <sup>4</sup> | Description                                                                                                                                                                                                                                                                                                           |  |  |

|-----------------------------------------|---------------------------------------------------------------------------------------|---------|-------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

|                                         | 40                                                                                    | FELB    | DI <sup>1</sup>         | <b>Front-End Loopback (Master only).</b> In the Inactive State, set High to cause the IAFE to loopback. The returned signal activates the MDSP which receives its own transmitted data. The chip set ignores incoming data from the Slave during loopback.                                                            |  |  |

| Hardware<br>Interface                   | 41                                                                                    | BELB    | DI <sup>1</sup>         | <b>Back-End Loopback.</b> In the Active-1 or Active-2 states, setting BELB High forces an internal, transparent loopback with RDATA connected to TDATA and RFP connected to TFP.                                                                                                                                      |  |  |

| (Hardware<br>Control<br>Mode)<br>-conťd | 42                                                                                    | RCLKU   | DO                      | <b>Receive Baud Rate Clock.</b> Aligned with BIT_CK in Slave mode, phase synchronous with receive pulse stream, However, during Activating State, the clocks may not be aligned. In the Master mode RCLKU has a constant, arbitrary, phase relationship with BIT_CK in Active State.                                  |  |  |

| contu                                   | 43                                                                                    | TXTST   | DI <sup>1</sup>         | <b>Transmit Test.</b> Set high to enable isolated transmit pulse generation.<br>TDATA controls the sign and TFP controls the magnitude of the transmitted<br>quat pulses according to the 2B1Q encoding rules. In the Slave<br>configuration, when the TXTST mode is selected, the Data Pump may<br>begin activation. |  |  |

|                                         | 36                                                                                    | D0      | DI <sup>1</sup> /O      | Data bit 0. Eight-bit, parallel data bus.                                                                                                                                                                                                                                                                             |  |  |

|                                         | 37                                                                                    | D1      | DI <sup>1</sup> /O      | Data bit 1                                                                                                                                                                                                                                                                                                            |  |  |

|                                         | 38                                                                                    | D2      | DI <sup>1</sup> /O      | Data bit 2                                                                                                                                                                                                                                                                                                            |  |  |

|                                         | 39                                                                                    | D3      | DI <sup>1</sup> /O      | Data bit 3                                                                                                                                                                                                                                                                                                            |  |  |

|                                         | 40                                                                                    | D4      | DI <sup>1</sup> /O      | Data bit 4                                                                                                                                                                                                                                                                                                            |  |  |

|                                         | 41                                                                                    | D5      | DI <sup>1</sup> /O      | Data bit 5                                                                                                                                                                                                                                                                                                            |  |  |

| Processor                               | 42                                                                                    | D6      | DI <sup>1</sup> /O      | Data bit 6                                                                                                                                                                                                                                                                                                            |  |  |

| Interface                               | 43                                                                                    | D7      | DI <sup>1</sup> /O      | Data bit 7                                                                                                                                                                                                                                                                                                            |  |  |

|                                         | 4                                                                                     | ADDR0   | DI <sup>3</sup>         | Address bit 0. Four-bit address, selects read or write register.                                                                                                                                                                                                                                                      |  |  |

| (Software                               | 5                                                                                     | ADDR1   | DI <sup>3</sup>         | Address bit 1                                                                                                                                                                                                                                                                                                         |  |  |

| Control<br>Mode)                        | 6                                                                                     | ADDR2   | DI <sup>3</sup>         | Address bit 2                                                                                                                                                                                                                                                                                                         |  |  |

| Mode)                                   | 9                                                                                     | ADDR3   | DI <sup>3</sup>         | Address bit 3                                                                                                                                                                                                                                                                                                         |  |  |

|                                         | 32                                                                                    | INT     | DO                      | Interrupt Output. Open drain output. Requires an external 10 k $\Omega$ pull up resistor. Goes Low on interrupt.                                                                                                                                                                                                      |  |  |

|                                         | 33                                                                                    | CHIPSEL | DI <sup>3</sup>         | Chip Select. Pull Low to read or write to registers.                                                                                                                                                                                                                                                                  |  |  |

|                                         | 34                                                                                    | WRITE   | DI <sup>3</sup>         | Write Pulse. Pull Low to write to registers.                                                                                                                                                                                                                                                                          |  |  |

|                                         | 35                                                                                    | READ    | DI <sup>3</sup>         | Read Pulse. Pull Low to read from registers.                                                                                                                                                                                                                                                                          |  |  |

| 1. This input                           | 1. This input is a Schmidt Triggered circuit and includes an internal pull-up device. |         |                         |                                                                                                                                                                                                                                                                                                                       |  |  |

This input is a Schmidt Triggered circuit and includes an internal pull-up device. 2. The frame period is 2351 or 2353 baud times. See "Framing" on page 16.

3. This input is a Schmidt Triggered circuit and includes an internal pull-down device.

4. I/O column entries: DI = Digital Input; DO = Digital Output; DI/O = Digital Input/Output; AI = Analog Input; AO = Analog

Output; Al/O = Analog Input/Output; S = Supply.

| Group     | Pin # | Symbol   | <b>I/O</b> <sup>4</sup> | Description                                                                                                                                                                                                                                                                                                              |

|-----------|-------|----------|-------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|           | 14    | SLAVE_CK | DI <sup>3</sup>         | Slave Mode Reference Clock. Mandatory in Slave mode. Tie High or Low in Master Mode. Clock input requires ± 32 ppm accuracy.                                                                                                                                                                                             |

|           | 15    | CK_EN    | DO                      | Slave Mode Reference Clock Enable. Active High enable for the SLAVE_CK clock. In slave mode, this pin goes Low to indicate the PLL is tracking the input signal from the master. Not used in master mode.                                                                                                                |

|           | 13    | MSTR_CK  | DI <sup>1</sup><br>DO   | <b>16x MDSL Reference Clock.</b> In Master Mode, this clock generates transmit and receive timing and must have ±32 ppm accuracy. In Slave Mode, this output is derived by dividing VCO_CK by two so that it may drive the MSTR_CK input of another data pump configured for Master mode as a repeater (with RPTR High). |

| Clock and | 19    | VCO_CK   | DI                      | 32x Receive Clock Input.                                                                                                                                                                                                                                                                                                 |

| Control   | 20    | SER_CTL  | DO                      | Serial Control Output.                                                                                                                                                                                                                                                                                                   |

|           | 21    | RX_CK    | DO                      | Receive Baud Rate Clock. Derived from VCO_CK.                                                                                                                                                                                                                                                                            |

|           | 22    | AD0      | DI                      | Analog to Digital Converter Data Line 0.                                                                                                                                                                                                                                                                                 |

|           | 23    | AD1      | DI                      | Analog to Digital Converter Data Line 1.                                                                                                                                                                                                                                                                                 |

|           | 24    | AGC_SET  | DI                      | AGC Adjust Input.                                                                                                                                                                                                                                                                                                        |

|           | 25    | TX_CK    | DO                      | Transmit Symbol Clock Output.                                                                                                                                                                                                                                                                                            |

|           | 26    | TMAG     | DO                      | Transmit Quat Magnitude Bit.                                                                                                                                                                                                                                                                                             |

|           | 27    | TSGN     | DO                      | Transmit Quat Sign Bit.                                                                                                                                                                                                                                                                                                  |

#### Table 2. SK70720 MDSP Pin Assignments/Signal Descriptions (Continued)

1. This input is a Schmidt Triggered circuit and includes an internal pull-up device.

2. The frame period is 2351 or 2353 baud times. See "Framing" on page 16.

3. This input is a Schmidt Triggered circuit and includes an internal pull-down device.

4. I/O column entries: DI = Digital Input; DO = Digital Output; DI/O = Digital Input/Output; AI = Analog Input; AO = Analog

Output;

Al/O = Analog Input/Output; S = Supply.

# 3.0 Functional Description

The MDSL Data Pump (MDP) provides synchronous, full duplex transmission on a single pair of wires using 2B1Q line coding and echo cancellation. The Data Pump supports symmetrical line rates from 272 to 784 kbps and provides complete start up and operation without an external processor. The MDP may be used to transport framed or unframed data which is synchronous, asynchronous, or near-synchronous to the clock rate of the data pump. This section provides an overview of how the MDP data interface functions to support these applications. For a detailed explanation on the how to configure the MDP for a specific application refer to the section entitled "MDSL Data Interface."

Figure 4 illustrates data transport using the MDSL system. Data is clocked into a transmitter, sent over the line, and clocked out of the receiver of the far-end transceiver. Data is transmitted simultaneously in both directions.

### 3.1 Framing

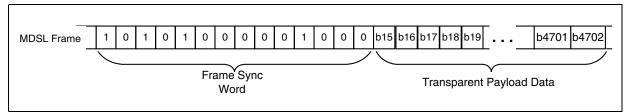

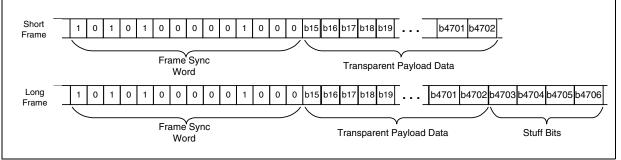

The MDP embeds a 14-bit frame synchronization word (FSW) in the data stream that divides the data into 4702-bit MDSL frames as shown in Figure 5. The framing signal serves three purposes:

- 1. It allows automatic activation and deactivation based on receiver frame sync word detection.