# SED1351

# **GRAPHICS LCD CONTROLLER**

### ■ DESCRIPTION

The SED1351F is a graphics LCD controller capable of controlling medium to large resolution displays. It transfers data from MPU to external frame buffer RAM and converts this data to display signals for LCD drivers. The SED1351F can display images with 4 gray shades and support display duty cycle as high as 1/1024.

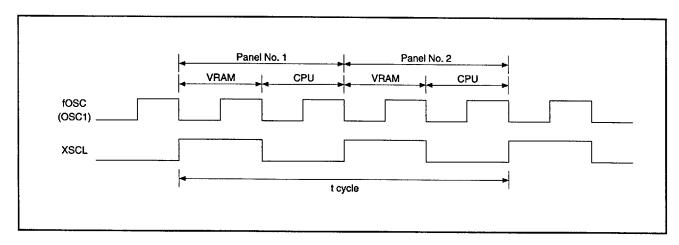

The SED1351F is designed to achieve high efficiency and data throughput to the LCD. It has a cycle steal mode which allows MPU to access frame buffer RAM without interfering with the display operation. The SED1351F can directly interface with up to eight 64K-bit SRAMs or two 256K-bit SRAMs.

The SED1351F can operate with either 5V or 3V power supply. The 5V version chip is the SED1351F0A and the 3V version chip is the SED1351FLB.

### **■ FEATURES**

- Low-power CMOS technology

- 8-bit or 16-bit MPU data interface

- Direct interface with 80xx, Z80 and 68xxx MPU

- 4- or 8-bit panel data bus for single panel and 4-bit bus for dual panel

- Support logical OR of layers and panel division

- Smooth vertical scrolling

- Virtual screen display up to 1024

- Binary mode (on/off only) generates black & white images

- Gray mode (on/off and two gray steps) generates images with 4 gray shades

### Maximum number of rows

| Binary mod | e | 2048 |

|------------|---|------|

| Gray mode  |   | 1024 |

Maximum number of rows:

Single panel ..... 1024 Dual panel ..... 2048

Maximumdisplaysizes when 64K-byteSRAMs are used:

Binary mode .............  $2048 \times 256 / 1024 \times 512$ Gray mode ...............  $1024 \times 256 / 512 \times 512$

Available models:

SED1351F<sub>0A</sub> ......5V, QFP5-100 pin SED1351F<sub>LB</sub> ......3V,QFP15-100 pin

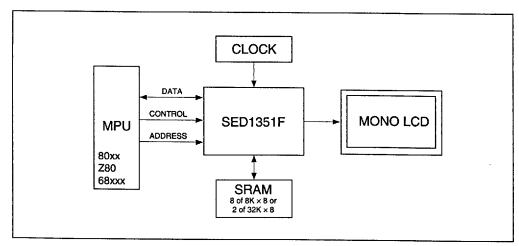

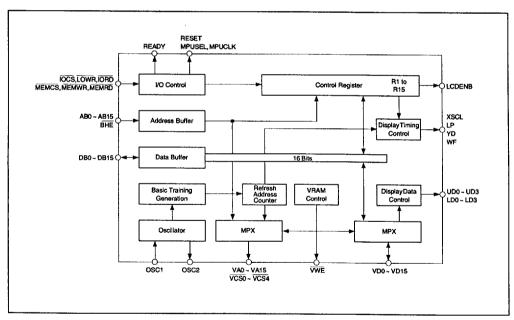

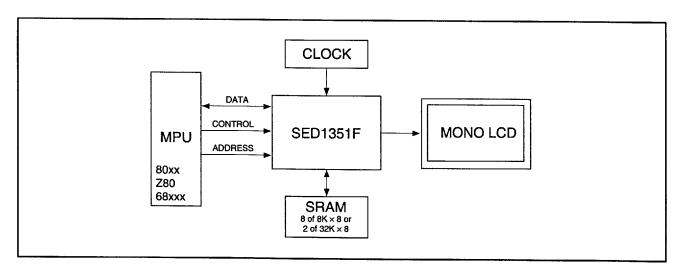

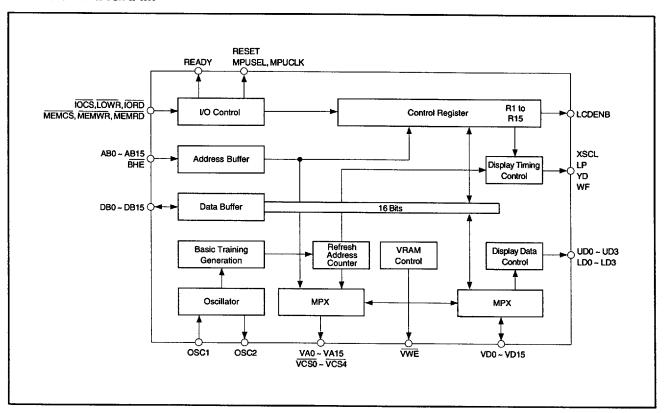

### ■ SYSTEM BLOCK DIAGRAM

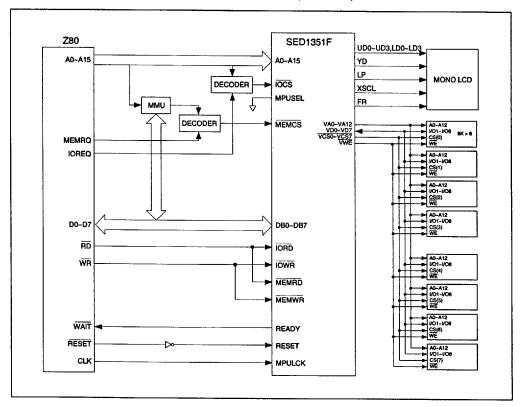

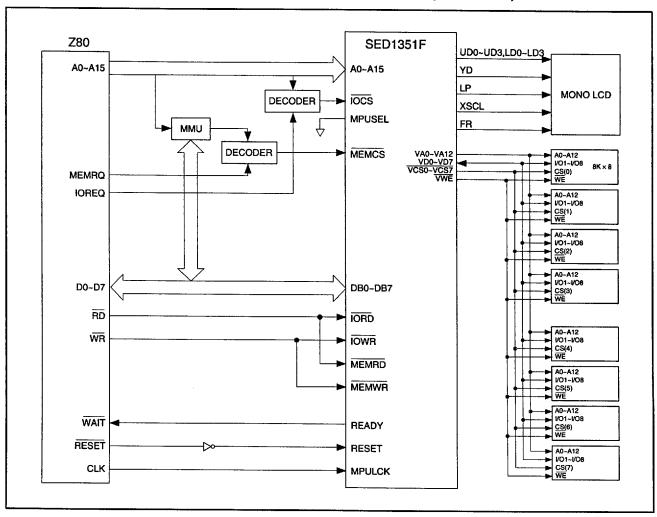

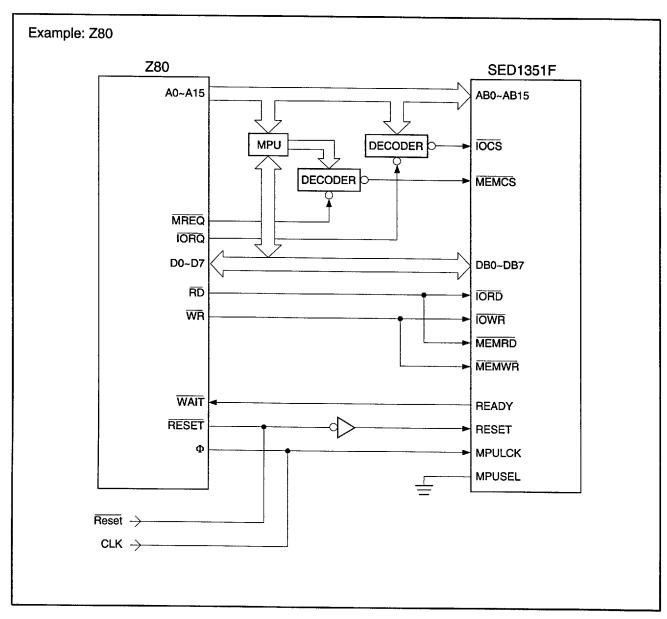

# ■ INTERFACE WITH 8-BIT MPU (Z-80) AND 64K-BIT SRAM (8 of 8K x 8)

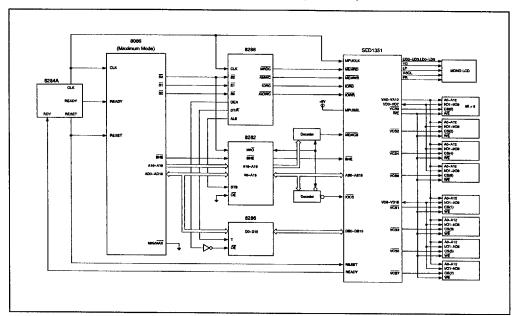

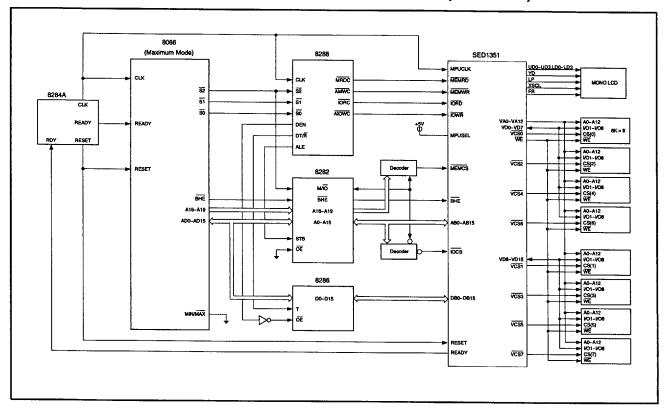

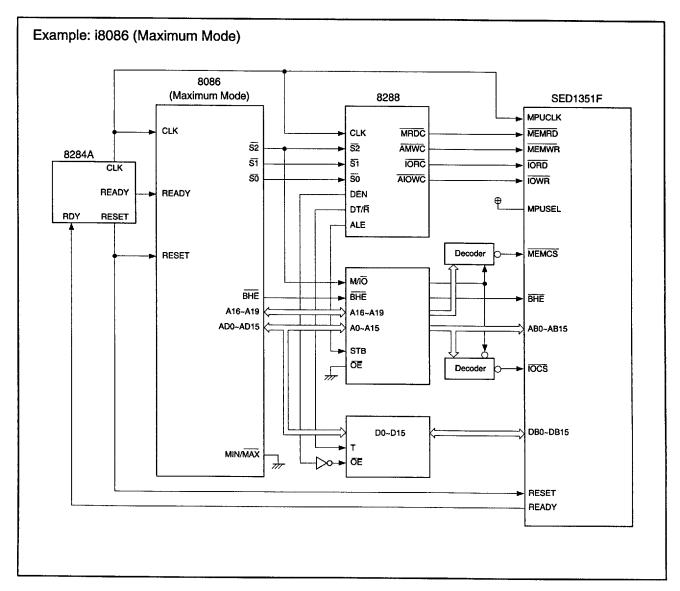

# ■ INTERFACE WITH 16-BIT MPU (8086) AND 64K-BIT SRAM (8 of 8K x 8)

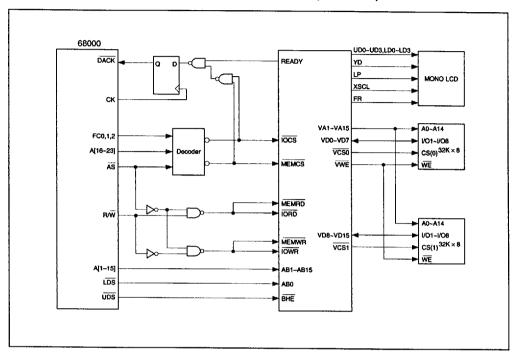

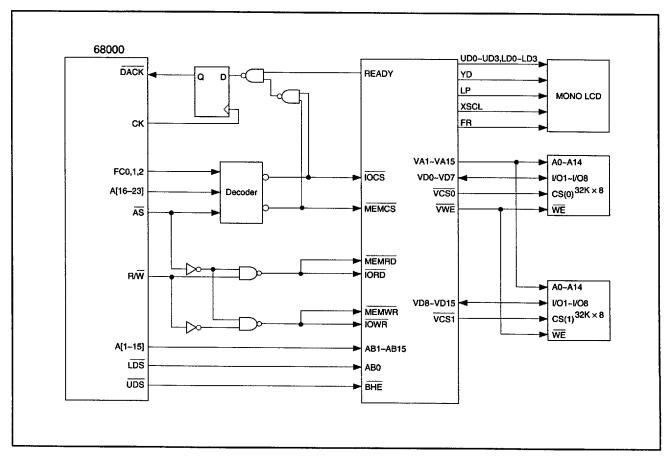

# ■ INTERFACE WITH 16-BIT MPU (68000) AND 256K-BIT SRAM (2 of 32K x 8)

## **■ SUPPORTED RESOLUTIONS**

| Diamlau        |      | Max  | cimum E | Display S | Size        |     | ODAN         | 00              |                 |

|----------------|------|------|---------|-----------|-------------|-----|--------------|-----------------|-----------------|

| Display<br>RAM | Mon  | ochr | ome     | 4 G       | 4 Grayscale |     | SRAM         | CPU             | SRAM            |

| I IZZIVI       | Х    |      | Υ       | ·x        |             | Υ   | Type         | Interface       | Interface       |

| 8K             | 256  | ×    | 256     | 256       | ×           | 128 | 1 of 8K × 8  | 8 bit           | 8 bit           |

| 16K            | 512  | ×    | 256     | 256       | ×           | 256 | 2 of 8K × 8  | 8 bit<br>16 bit | 8 bit<br>16 bit |

| 24K            | 512  | ×    | 384     | 384       | ×           | 256 | 3 of 8K × 8  | 8 bit           | 8 bit           |

| 32K            | 512  | ×    | 512     | 512       | ×           | 256 | 4 of 8K × 8  | 8 bit<br>16 bit | 8 bit<br>16 bit |

|                |      |      |         |           |             | Ī   | 1 of 32K × 8 | 8 bit           | 8 bit           |

| 48K            | 768  | ×    | 512     | 512       | ×           | 384 | 6 of 8K × 8  | 8 bit<br>16 bit | 8 bit<br>16 bit |

| 56K            | 896  | ×    | 512     | 512       | ×           | 448 | 7 of 8K × 8  | 8 bit           | 8 bit           |

| 64K            | 1024 | ×    | 512     | 512       | ×           | 512 | 8 of 8K × 8  | 8 bit<br>16 bit | 8 bit<br>16 bit |

|                |      |      |         |           |             |     | 2 of 32K × 8 | 8 bit<br>16 bit | 8 bit<br>16 bit |

### **■ BLOCK DIAGRAM**

# **■ ELECTRICAL CHARACTERISTICS**

# SED1351F0AAbsolute Maximum Ratings

(Vss = 0V)

| Parameter                      | Symbol  | Ratings              | Unit |

|--------------------------------|---------|----------------------|------|

| Supply voltage                 | VDD     | Vss-0.3 to 7.0       | V    |

| Input voltage                  | Vı      | Vss-0.3 to Vpp+0.3   | v    |

| Output voltage                 | Vo      | Vss-0.3 to Vpp+0.3   | V    |

| Output current/pin             | to      | ±10                  | mA   |

| Power dissipation              | Po      | 200                  | mW   |

| Supply current                 | loo/Iss | ±40                  | mA   |

| Storage temperature            | Tstg    | -65 to 150           | -€   |

| Soldering temperature and time | Tsol    | 260°C, 10s (at lead) |      |

# Recommended Operating Conditions

(Vss = 0V)

| Parameter             | Symbol | Condition | Min | Тур | Max | Unit |

|-----------------------|--------|-----------|-----|-----|-----|------|

| Supply voltage        | VDD    |           | 4.5 | 5.0 | 5.5 | V    |

| Input voltage         | Vı     |           | Vss | _   | VDD | V    |

| Operating temperature | Topr   |           | -20 | _   | 75  | °C   |

# o DC Characteristics (F0A)

$(Ta = -20 \text{ to } 75^{\circ}\text{C})$

| Parameter                            | Symbol           | Condition                                                                                           | Min                      | Тур | Max          | Unit |

|--------------------------------------|------------------|-----------------------------------------------------------------------------------------------------|--------------------------|-----|--------------|------|

| Static current                       | loos             | VIN = VDD, VDD = Max,<br>Vss, IOH = IOL = 0                                                         | _                        | -   | 100          | μА   |

| Input leakage current (Type 1)       | lu               | V <sub>DD</sub> = 5.5V,<br>V <sub>IH</sub> = V <sub>DD</sub> ,<br>V <sub>IL</sub> = V <sub>SS</sub> | -10                      | 1   | 10           | μА   |

| High level input voltage 1 (OSC1)    | Vim              | Voo = 5.5V                                                                                          | 3.5                      |     | _            | ٧    |

| Low level input voltage 1 (OSC1)     | VILI             | Voo = 4.5V                                                                                          | T —                      |     | 1.0          | ٧    |

| High level input voltage 2 (Type 2)  | V <sub>IH2</sub> | Voo = 5.5V                                                                                          | 2.0                      | _   | _            | ٧    |

| Low level input voltage 2 (Type 2)   | VIL2             | Voo = 4.5V                                                                                          | —                        | _   | 0.8          | ٧    |

| High level input voltage 3 (Type 3)  | V <sub>T+</sub>  | V00 = 5.5V                                                                                          | 4.0                      | _   |              | V    |

| Low level input voltage 3 (Type 3)   | V <sub>T-</sub>  | Voo = 4.5V                                                                                          | _                        |     | 0.8          | ٧    |

| Hysteresis voltage (Type 3)          | Vн               | Voo = 5V                                                                                            | 0.3                      | _   | _            | V    |

| High level output voltage 1 (Type 4) | Vон              | V <sub>DO</sub> = 4.5V<br>Іон = -2mA                                                                | V <sub>DD</sub><br>- 0.4 | -   |              | ٧    |

| Low level output voltage 1 (Type 4)  | Voli             | lo∟= 6mA                                                                                            | _                        | _   | Vss<br>+ 0.4 | ٧    |

| High level output voltage 2 (OSC2)   | Vonz             | V <sub>DD</sub> = 4.5V<br>Iон = −50µA                                                               | V <sub>DD</sub> - 0.4    |     | _            | ٧    |

| Low level output voltage 2 (OSC2)    | Vol2             | lo∟ = 50μA                                                                                          |                          | -   | Vss<br>+ 0.4 | ٧    |

### Note:

- Type 1. MEMCS, MEMWR, MEMRD, IOCS, IOWR, IORD, MPUCLK, ABO ~ AB15, BHE, MPUSEL, RESET, OSC

- Type 2. MEMCS, MEMWR, MEMRD, IOCS, IOWR, IORD, MPUCLK, ABO ~ AB15, BHE, DB0 ~ DB15, VD0 ~ VD15

- Type 3. MPUSEL, RESET

- Type 4. DB0 ~ DB15, READY, VA0 ~ VA15, VCS0 ~ VCS4, VD0 ~ VD15, VWE, XSCL, LP, WF, YD, UD0 ~ UD3, LD0 ~ LD3, LCDENB

# • SED1351FLA

# Absolute Maximum Ratings

(Vss = 0V)

|                     |         |                    | (    |

|---------------------|---------|--------------------|------|

| Parameter           | Symbol  | Ratings            | Unit |

| Supply voltage      | VDD     | Vss-0.3 to 7.0     | V    |

| Input voltage       | VI      | Vss-0.3 to VDD+0.5 | V    |

| Output voltage      | Vo      | Vss-0.3 to Vpp+0.5 | V    |

| Output current/pin  | lo      | ±24                | mA   |

| Power dissipation   | Po      | 200                | mW   |

| Supply current      | IDD/ISS | ±40                | mA   |

| Storage temperature | Tstg    | -65 to 150         | ∞    |

# Recommended Operating Conditions

(Vss = 0V)

| Parameter             | Symbol | Condition | Min | Тур | Max | Unit |

|-----------------------|--------|-----------|-----|-----|-----|------|

| Supply voltage        | VDD    |           | 2.7 | _   | 3.6 | ٧    |

| Input voltage         | Vı     |           | Vss | _   | DaV | V    |

| Operating temperature | Topr   |           | -20 | _   | 75  | °C   |

# o DC Characteristics (FLB)

$(Ta = -20 \text{ to } 75^{\circ}\text{C})$

| Parameter                            | Symbol           | Condition                                     | Min                      | Тур | Max                | Unit |

|--------------------------------------|------------------|-----------------------------------------------|--------------------------|-----|--------------------|------|

| Static current                       | loos             | VIN = VDD OF VSS,<br>VDD = MAX, IOH = IOL = 0 | _                        |     | 30                 | μА   |

| Input leakage current (Type 1)       | lı.              | VDD = MAX,<br>VIH = VDD,<br>VIL = VSS         | -1                       | _   | 1                  | μА   |

| High level input voltage 1 (OSC1)    | Viiii            | Voo = MAX                                     | 0.7V <sub>DD</sub>       | _   | _                  | V    |

| Low level input voltage 1 (OSC1)     | V <sub>IL1</sub> | V <sub>DD</sub> = MIN                         | _                        | _   | 0.2V <sub>DD</sub> | ٧    |

| High level input voltage 2 (Type 2)  | VIH2             | VDD = MAX                                     | 0.7V <sub>DD</sub>       | _   |                    | ٧    |

| Low level input voltage 2 (Type 2)   | VIL2             | Voo = MIN                                     | _                        | _   | 0.2V <sub>DD</sub> | V    |

| High level input voltage 3 (Type 3)  | V <sub>T+</sub>  | Voo = MAX                                     | 0.8Vpp                   |     |                    | ٧    |

| Low level input voltage 3 (Type 3)   | V <sub>T</sub> - | Voo = MIN                                     | _                        |     | 0.2V <sub>DD</sub> | ٧    |

| Hysteresis voltage (Type 3)          | VH               | Voo = TYP                                     | 0.3                      |     | _                  | ٧    |

| High level output voltage 1 (Type 4) | Vонт             | V <sub>DD</sub> = MIN<br>Іон = -1.5mA         | V <sub>DO</sub><br>- 0.3 | _   | _                  | ٧    |

| Low level output voltage 1 (Type 4)  | V <sub>OL1</sub> | lot = 3mA                                     | -                        |     | Vss<br>+ 0.3       | ٧    |

| High level output voltage 2 (OSC2)   | Vон2             | V <sub>DD</sub> = MIN<br>Iон = -50µA          | V <sub>DO</sub><br>- 0.4 | _   | _                  | ٧    |

| Low level output voltage 2 (OSC2)    | Vol2             | lo <sub>L</sub> = 50μA                        | _                        | _   | Vss<br>+ 0.4       | ٧    |

### Note:

- Type 1. MEMCS, MEMWR, MEMRD, IOCS, IOWR, IORD, MPUCLK, ABO ~ AB15, BHE, MPUSEL, RESET, OSC

- Type 2. MEMCS, MEMWR, MEMRD, IOCS, IOWR, IORD, MPUCLK, ABO ~ AB15, BHE, DB0 ~ DB15, VD0 ~ VD15

- Type 3. MPUSEL, RESET

- Type 4. DB0 ~ DB15, READY, VA0 ~ VA15, VCS0 ~ VCS4, VD0 ~ VD15, VWE, XSCL, LP, WF, YD, UD0 ~ UD3, LD0 ~ LD3, LCDENB

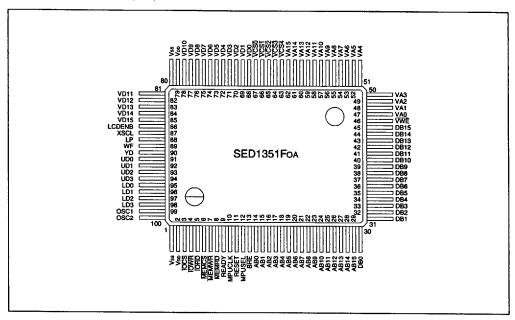

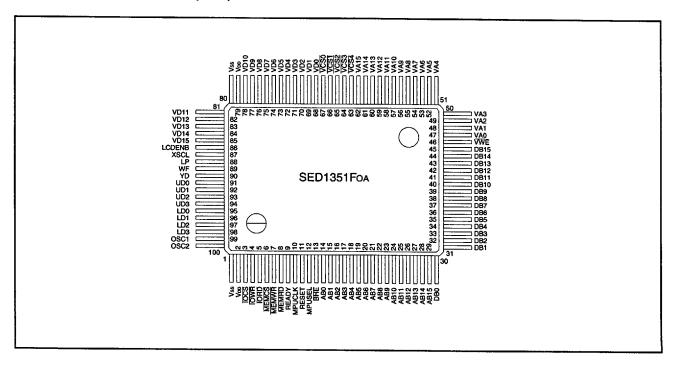

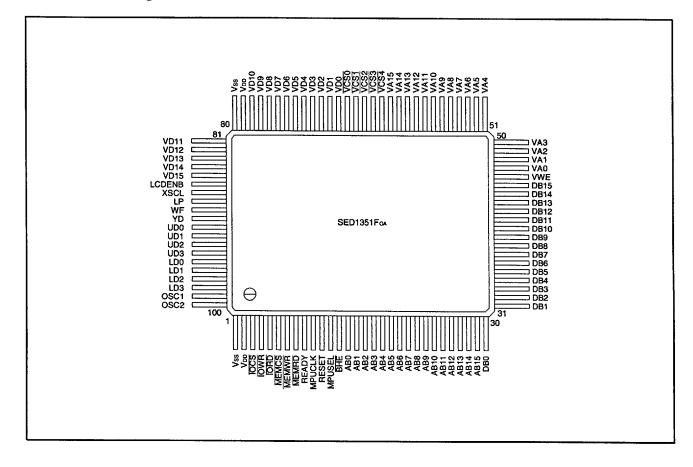

# ■ PIN CONFIGURATION (F0A)

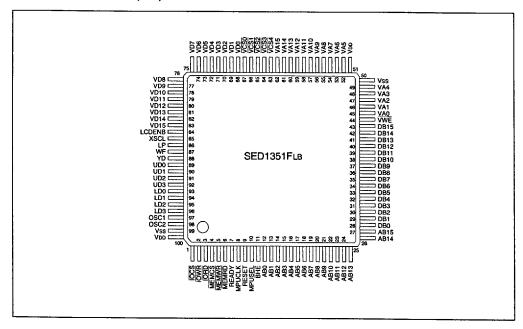

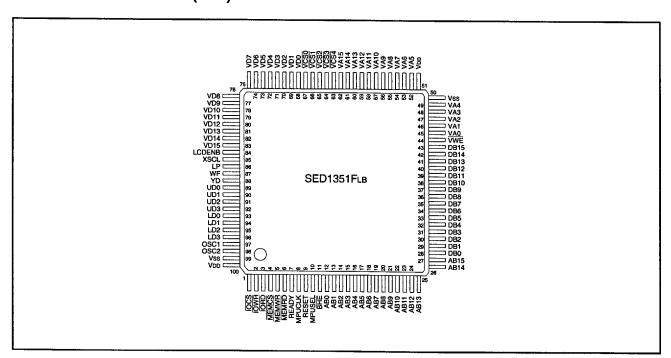

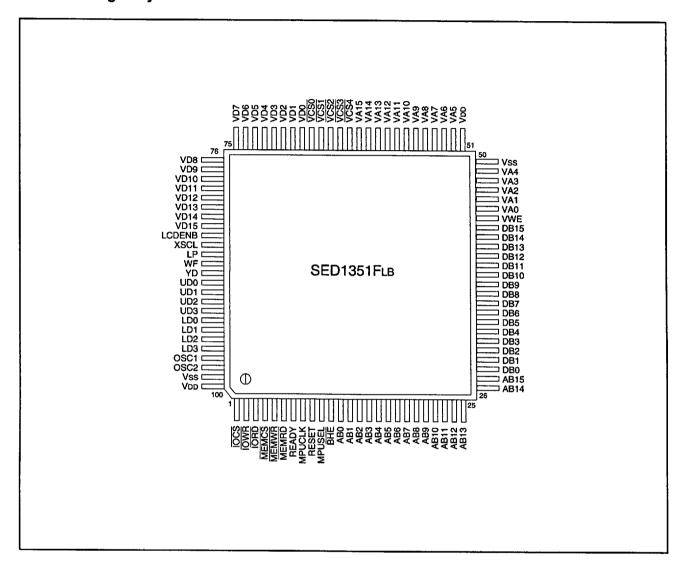

# **■ PIN CONFIGURATION (FLB)**

## ■ PIN DESCRIPTION

# 1. System Connector Terminals (at MPU)

| Pin Name    | Туре     | F0A<br>Pin No. | FLB<br>Pin No. | Drv | Description                                                                                                                                                                                                                                                                                                                  |

|-------------|----------|----------------|----------------|-----|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| DB0 to DB15 | 1/0      | 30 to 45       | 28 to 43       |     | These pins are interfaced with the MPU data bus. When using an 8-bit MPU, connect DB8 to DB15 to VDD.                                                                                                                                                                                                                        |

| AB0 to AB15 | l        | 14 to 29       | 12 to 27       |     | These pins are interfaced with the MPU address bus. If multiplexed address signals are used, connect them via latch circuits. A control register is selected by ABO to AB3. Correspondence of the MPU address bus to the VRAM address bus is such that ABi = VAi (where i is a pin number).                                  |

| ВНЕ         | I        | 13             | 11             |     | This signal is a bus high enable signal where a 16-bit MPU is used. It goes "L" (low) when an odd address is encountered. When using an 8-bit MPU configuration, connect the BHE pin to VDD.                                                                                                                                 |

| IOCS        | 1        | 3              | 1              |     | This pin selects a control register contained in the SED1351. It is "L" active, and must be assigned to MPU I/O space.                                                                                                                                                                                                       |

| IOWR        | 1        | 4              | 2              |     | This signal is used for writing data into a control register contained in the SED1351. It is "L" active, and must go "L" when it encounters an OUT instruction from the MPU.                                                                                                                                                 |

| IORD        | 1        | 5              | 3              |     | This signal is used for reading data from a control register contained in the SED1351. It is "L" active, and must go "L" when it encounters an IN instruction from the MPU.                                                                                                                                                  |

| MEMCS       | 1        | 6              | 4              |     | This signal is used for selecting VRAM. It is "L" active, and must be assigned to MPU memory space.                                                                                                                                                                                                                          |

| MEMWR       | I        | 7              | 5              |     | This signal is used for writing data to the VRAM. It is "L" active, and must go "L" when it encounters a memory write instruction from the MPU.                                                                                                                                                                              |

| MEMRD       | t        | 8              | 6              |     | This signal is used for reading data from the VRAM. It is "L" active, and must go "L" when it encounters a memory read instruction from the MPU.                                                                                                                                                                             |

| READY       | 0        | 9              | 7              |     | This signal requests the MPU to wait. It goes "L" by the falling edge of IOCS or MEMCS. It goes "H" by the rising edge of MPUCLK after completion of the SED1351 internal processing. Since READY is not a tri-state pin, it needed not be pulled up and must be connected directly to the READY (WAIT) terminal of the MPU. |

| MPUCLK      | 1        | 10             | 8              |     | This pin accepts an MPU clock. The MPU wait state is cleared by the rising edge of MPUCLK.                                                                                                                                                                                                                                   |

| MPUSEL      | l        | 12             | 10             |     | This signal is connected to either VDD or VSS for selection of an MPU.  MPUSEL = Vss 8-bitMPU(e.g., Z80, V20, i8088)                                                                                                                                                                                                         |

| RESET       |          | 11             | 9              |     | MPUSEL = V <sub>DD</sub> 16-bit MPU (e.g., V30, i8086)  The MPU reset signal comes to this pin. It is "H" active.                                                                                                                                                                                                            |

|             | <u> </u> | L              |                |     | and initializes a control register.                                                                                                                                                                                                                                                                                          |

### **Combinations of Control Pins**

| IOCS | IOWR | IORD | MEMCS | MEMWR | MEMRD | Operation                  |

|------|------|------|-------|-------|-------|----------------------------|

| 1    | *    | *    | 1     | *     | *     | Invalid                    |

| 0    | 0    | 1    | 1     | 1     | 1     | Write to control register  |

| 0    | 1    | 0    | 1     | 1     | 1     | Read from control register |

| 1    | 1    | 1    | 0     | 0     | 1     | Write to VRAM              |

| 1    | 1    | 1    | 0     | 1     | 0     | Read from VRAM             |

Note: Any combination other than those listed above will cause a system error.

1 = "H" (high)

0 = "L" (low)

\* = Don't care

### 2. VRAM Connector Terminals

| Pin Name                  | Туре | F0A<br>Pin No.        | FLB<br>Pin No.        | Drv | Description                                                                                                                                                                                                                           |

|---------------------------|------|-----------------------|-----------------------|-----|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| VD0 to VD15               | 1/0  | 68 to 78,<br>81 to 85 | 68 to 83              |     | These pins are interfaced with the VRAM data bus. For a 16-bit MPU configuration, VD0 to VD7 must be connected to even addresses, and VD8 to VD15 to odd addresses. For an 8-bit configuration, VD8 to VD15 must be connected to VDD. |

| VA0 to VA12               | 0    | 47 to 59              | 45 to 49,<br>52 to 59 |     | These pins are interfaced with the VRAM address bus and chip select pins.                                                                                                                                                             |

| VA13/VCS7 to<br>VA15/VCS5 | 0    | 60 to 62              | 60 to 62              |     | The SED1351 has chip select pins that can directly control eight 64K SRAMs (8K bytes each) or two                                                                                                                                     |

| VCS0 to VCS4              | 0    | 67 to 63              | 67 to 63              |     | 256K SRAMs (32K bytes) in the 64K VRAM space.<br>See Technical Manual for details.                                                                                                                                                    |

| VWE                       | 0    | 46                    | 44                    |     | This signal is used for writing data to the VRAM. It is "L" active, and must be connected to the WE pin of the VRAM.                                                                                                                  |

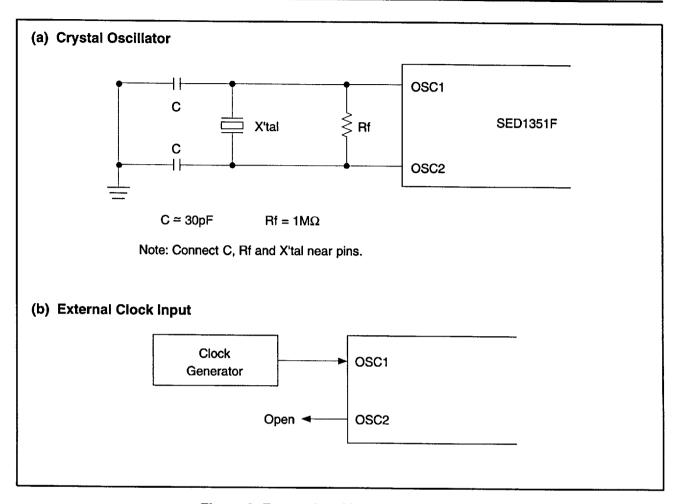

## 3. Oscillator Terminals

| Pin Name | Туре | F0A<br>Pin No. | FLB<br>Pin No. | Drv | Description                                                                                 |

|----------|------|----------------|----------------|-----|---------------------------------------------------------------------------------------------|

| OSC1     | 1    | 99             | 97             |     | The OSC1 (input) and OSC2 (output) pins gener-                                              |

| OSC2     | 0    | 100            | 98             |     | ate clocks for internal operation. They allow crystal oscillation and external clock input. |

### 4. Power Terminals

| Pin Name        | Туре | F0A<br>Pin No. | FLB<br>Pin No. | Drv | Description                                                                                                                                          |

|-----------------|------|----------------|----------------|-----|------------------------------------------------------------------------------------------------------------------------------------------------------|

| V <sub>DD</sub> |      | 2, 79          | 51, 100        |     | The power supply pins include two VDDs and two                                                                                                       |

| Vss             | _    | 1, 80          | 50, 99         |     | Vsss. Apply +5V or +3V to V <sub>DD</sub> and 0V to Vss. A capacitor (4.7 μF or more) must be connected near each pair of V <sub>DD</sub> /Vss pins. |

# 5. LCD Connector Terminals

| Pin Name              | Туре | F0A<br>Pin No. | FLB<br>Pin No. | Drv | Description                                                                                                                                                                                                                                                |

|-----------------------|------|----------------|----------------|-----|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| UD0 to UD3            | 1/0  | 91 to 94       | 89 to 92       |     | LCD display data. UD0 to UD3 are the upper panel                                                                                                                                                                                                           |

| LD0/UD4 to<br>LD3/UD7 | 0    | 95 to 98       | 93 to 96       |     | display data in the signal panel or double panel drive panel mode. LD0/UD4 to LD3/UD7 are the lower panel display data in the double panel drive mode. UD0 to UD3, and LD0/UD4 to LD3/UD7 are used for 8-bit data transfer in the single panel drive mode. |

| XSCL                  | 0    | 87             | 85             |     | This single is a shift clock for display data transfer. Take the UD0 to UD3, LD0/UD4 to LD3/UD7 display data into LCDs by the falling edge of XSCL.                                                                                                        |

| LP                    | 0    | 88             | 86             |     | This pin provides both a display data latch pulse and a scan signal transfer clock. Upon completion of transferring the LCD data on one line, display data can be latched or a scan signal transferred by the falling edge of LP.                          |

| WF                    | 0    | 89             | 87             |     | This pin provides a frame signal used for LCD AC driving.                                                                                                                                                                                                  |

| YD                    | 0    | 90             | 88             |     | This pin provides a scanning line start pulse. The signal is "H" active. Allow the scanning line drive IC to take in YD by the falling edge of LP.                                                                                                         |

|                       |      |                |                |     | The SED1351 has two lines of retracing; if two scanning line drive ICs are cascade-connected for the upper and lower panels in the double panel drive mode, two lines must be provided between the upper and lower scanning line drive outputs.            |

| LCDENB                | 0    | 86             | 84             |     | This pin provides the data which is set in bit 1 (D1) of the mode register (R1). LCDENB goes "L" when the system is reset; it can be effectively used for LCD power control.                                                                               |

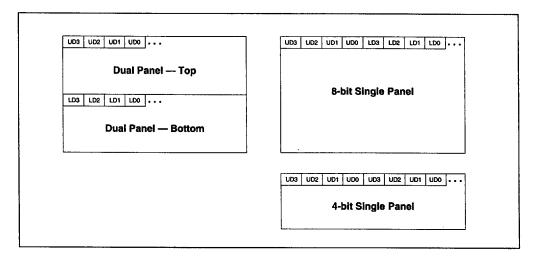

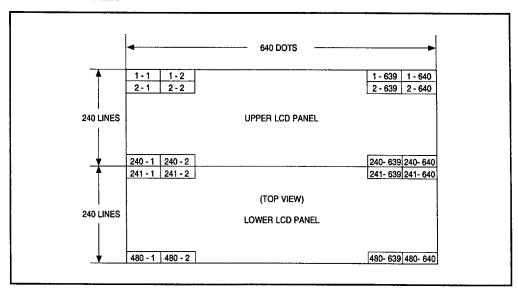

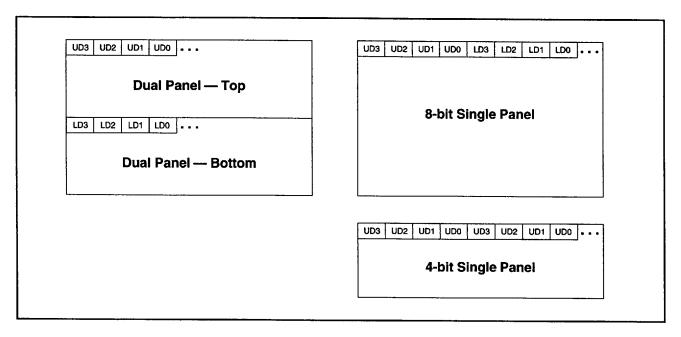

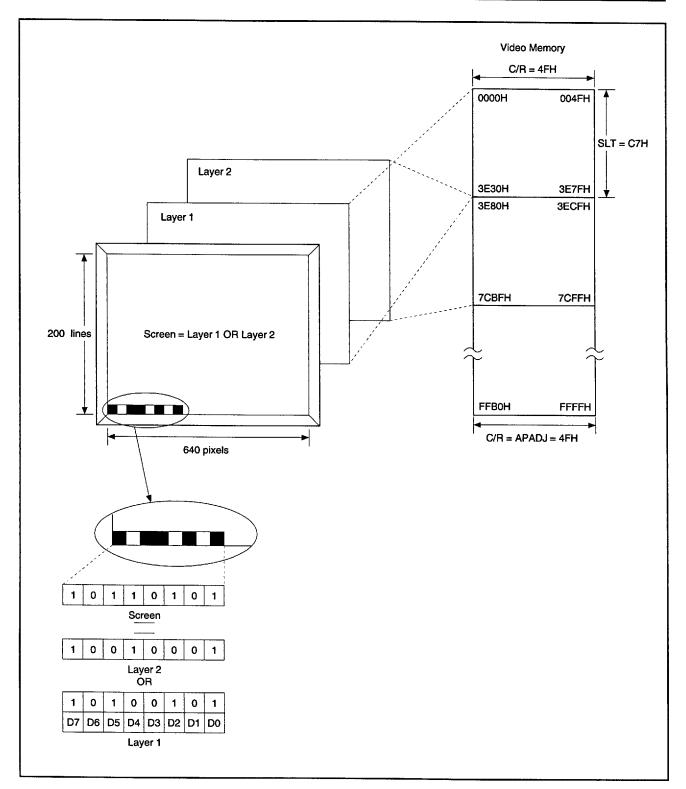

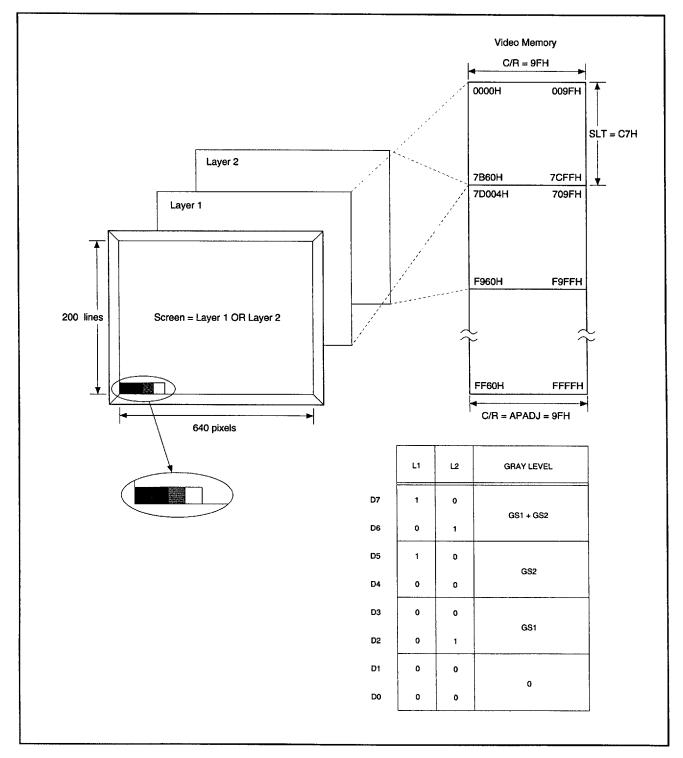

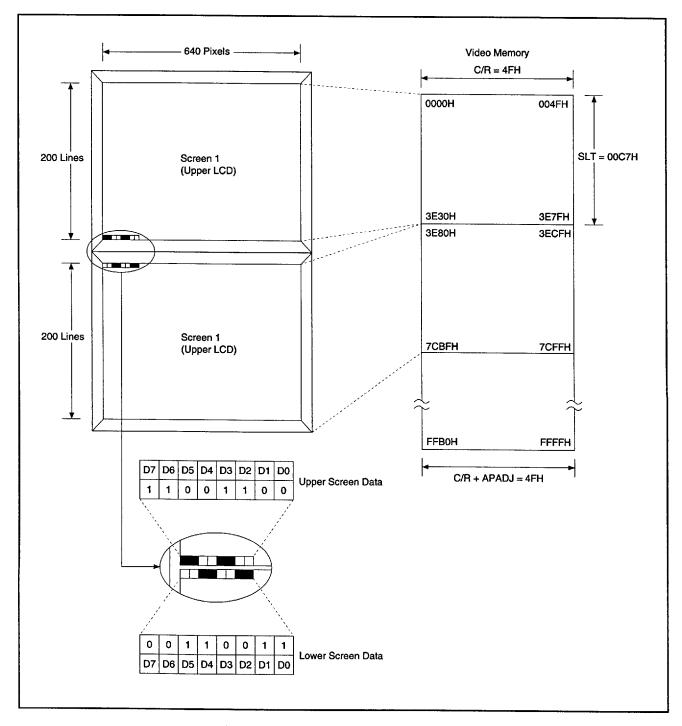

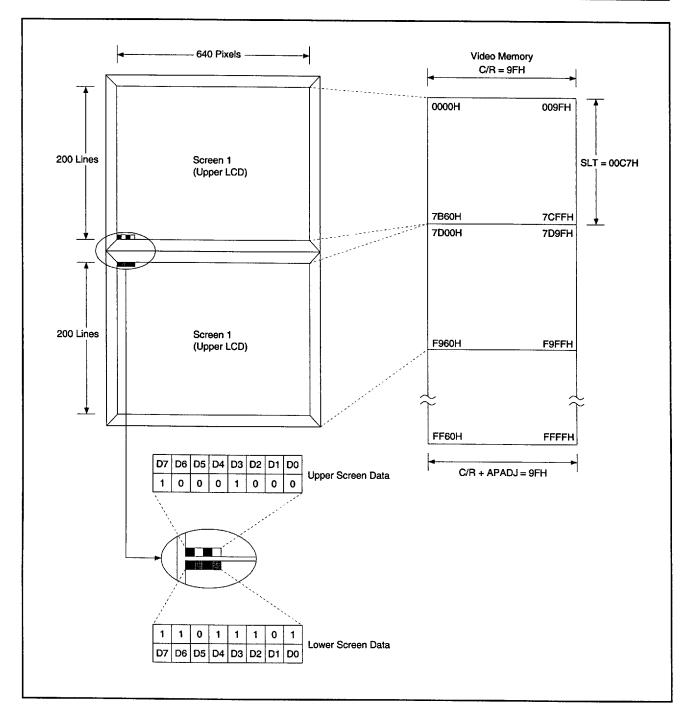

Illustrated below are the display data which are output from the UD0 to UD3, LD0/UD4 to LD3/UD7 and the display on the panel:

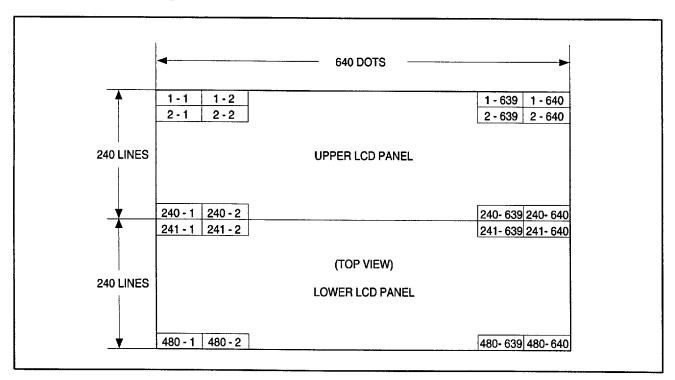

## ■ LCD PANEL PIXELS

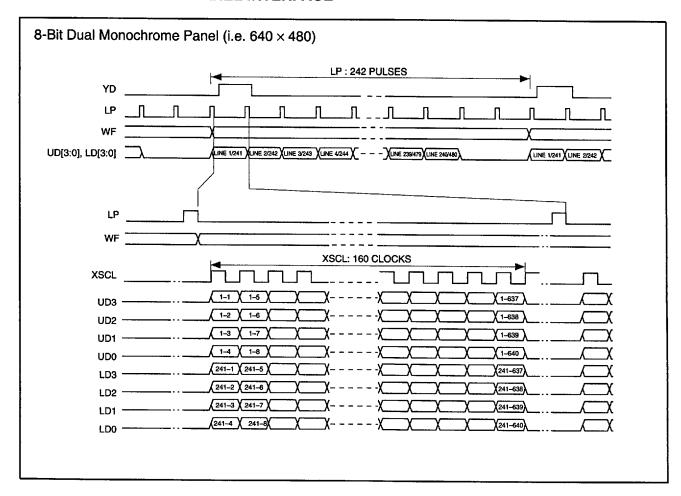

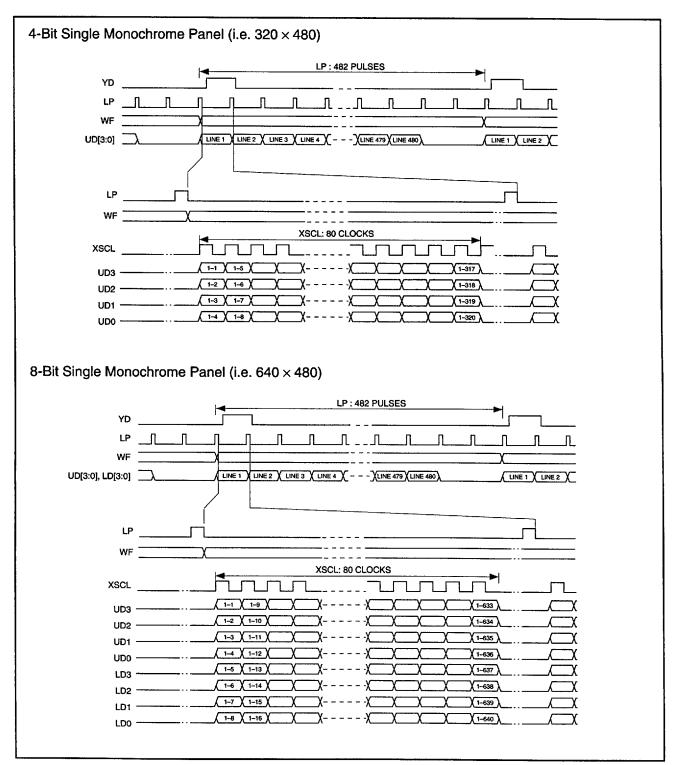

### **■ MONOCHROME LCD PANEL INTERFACE**

### **■ MONOCHROME LCD PANEL INTERFACE**

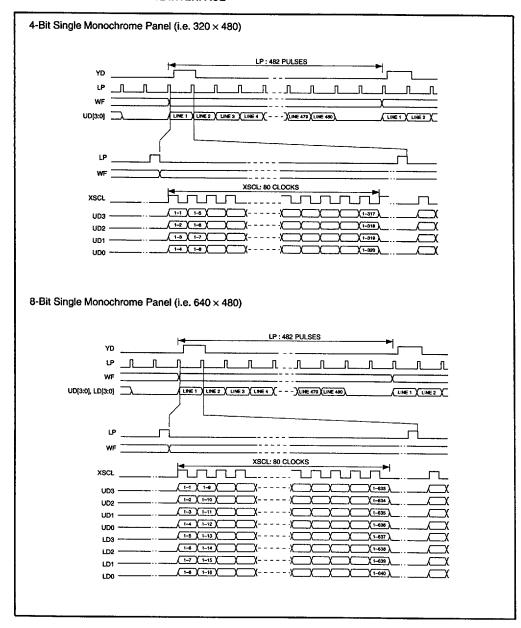

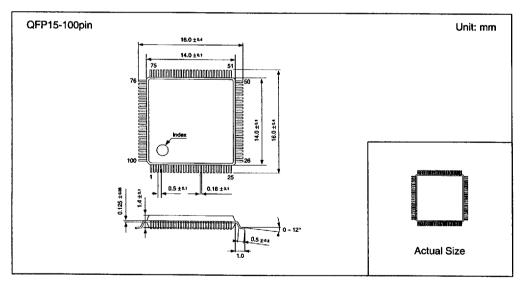

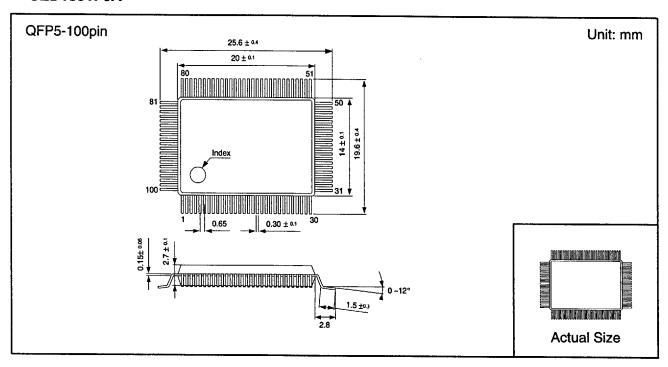

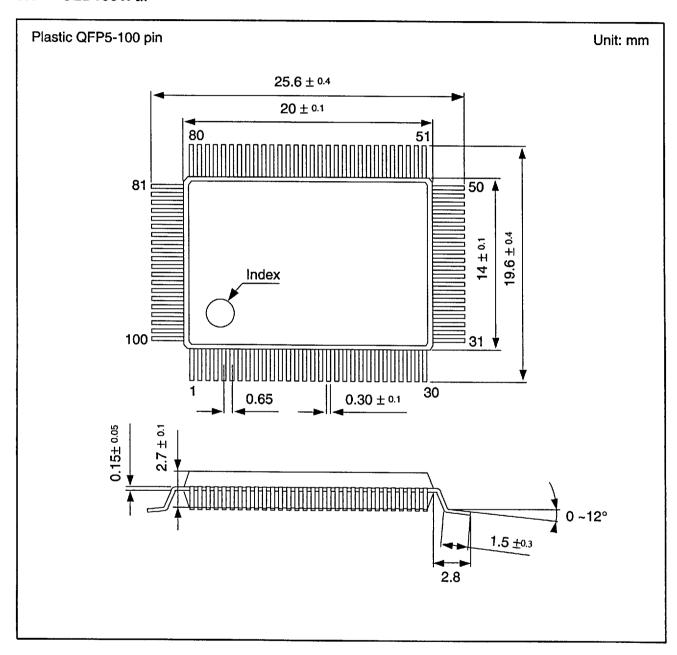

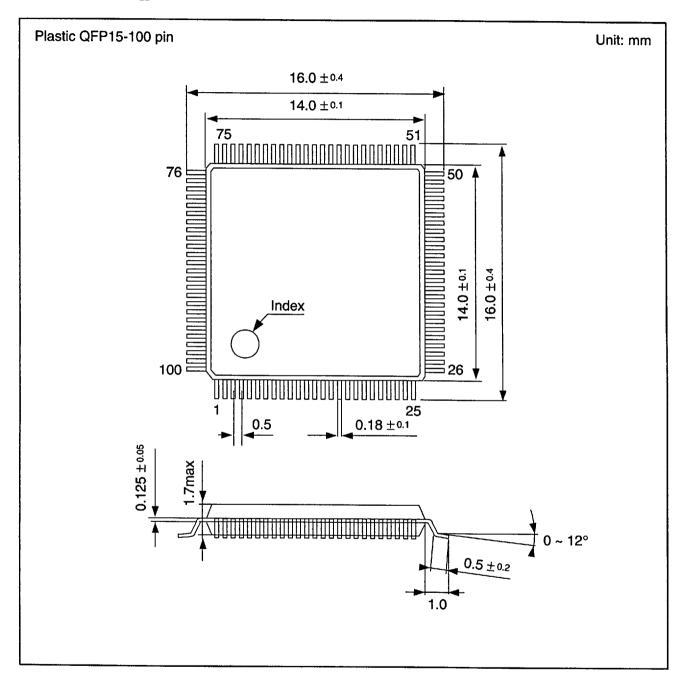

# ■ PACKAGE DIMENSIONS

### ● SED1351F0A

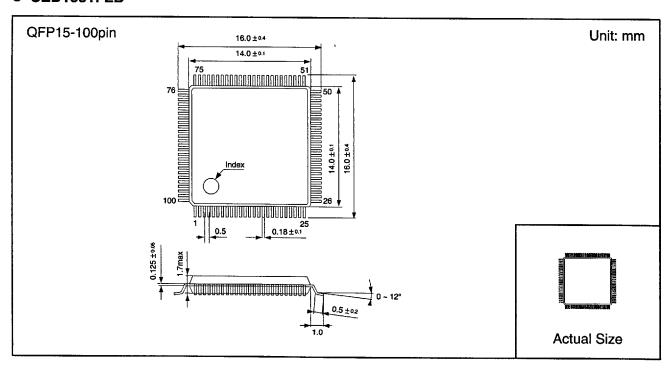

## SED1351FLB

# SED1351F<sub>0A/LB</sub> Graphics LCD Controller (GLC) Technical Manual

S-MOS Systems, Inc. September, 1995 Version 0.2

S-MOS Systems, Inc. • 2460 North First Street • San Jose, CA 95131 • Tel: (408) 922-0200 • Fax: (408) 922-0238

7932909 0003386 778 🖿

THIS PAGE INTENTIONALLY BLANK

# **CONTENTS**

| 1.0 | SED135  | 1F GRAPHIC             | S LCD C | ONTROLL                 | ER DATA SHEET                            | 7  |

|-----|---------|------------------------|---------|-------------------------|------------------------------------------|----|

| 2.0 | PIN DES | SCRIPTION              | •••••   | •••••                   |                                          | 31 |

|     | 2.1     |                        |         |                         |                                          |    |

|     |         | 2.1.1                  |         |                         |                                          |    |

|     |         | 2.1.2                  |         | _                       | cription Table                           |    |

|     | 2.2     | SED1351FLB             |         |                         |                                          |    |

|     |         | 2.2.1                  |         |                         |                                          |    |

|     |         | 2.2.2                  |         |                         | cription Table                           |    |

|     | 2.3     |                        |         |                         |                                          |    |

|     | 2.4     |                        |         |                         |                                          |    |

|     | 2.5     |                        |         |                         |                                          |    |

|     | 2.6     |                        |         |                         |                                          |    |

|     |         |                        |         |                         |                                          |    |

| 3.0 | ELECTI  | RICAL CHAR             | ACTERIS | STICS                   |                                          | 41 |

|     | 3.1     | SED1351F <sub>0A</sub> | •••••   | •••••                   |                                          | 41 |

|     |         | 3.1.1                  | SED135  | 1Foa Absolute           | Maximum Ratings                          | 41 |

|     |         | 3.1.2                  | Recomm  | ended Opera             | ating Conditions                         | 41 |

|     |         | 3.1.3                  | SED135  | 1F <sub>0A</sub> DC Cha | racteristics                             | 42 |

|     |         | 3.1.4                  | SED135  | 1Foa AC Cha             | racteristics                             | 43 |

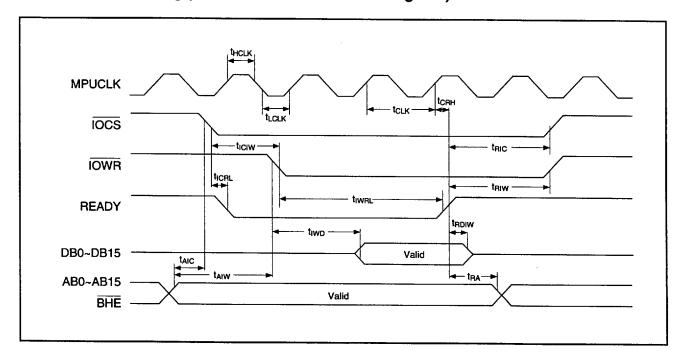

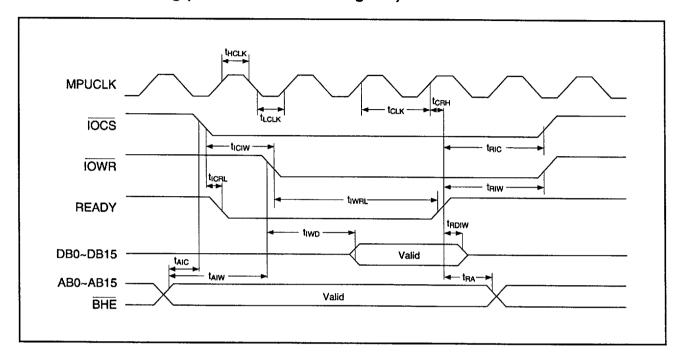

|     |         |                        | 3.1.4.1 | IOWR Timi               | ng (MPU Write Data to Control Register)  | 43 |

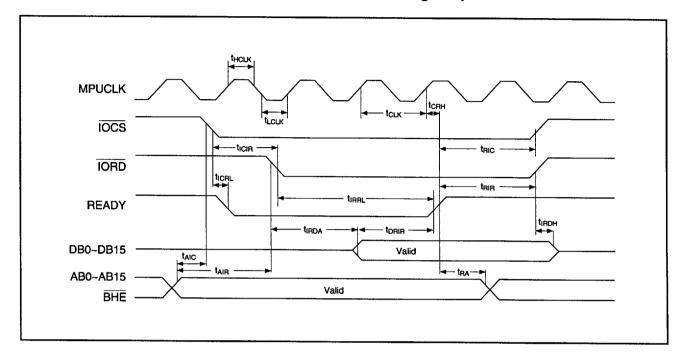

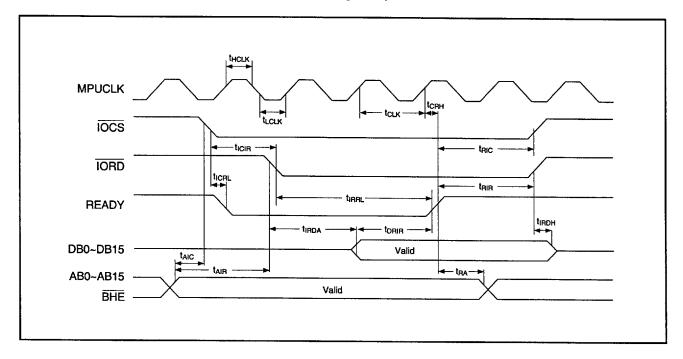

|     |         |                        | 3.1.4.2 | IORD Timir              | ng (MPU Read Data from Control Register) | 44 |

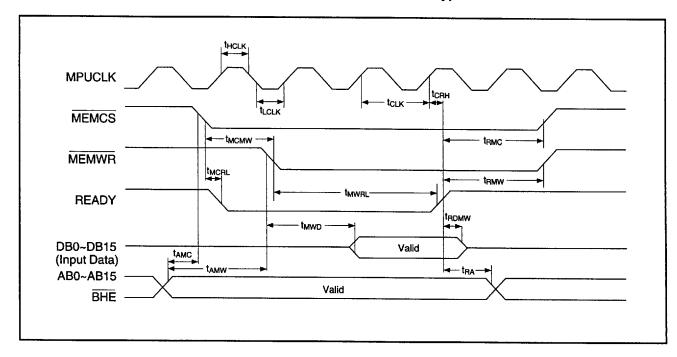

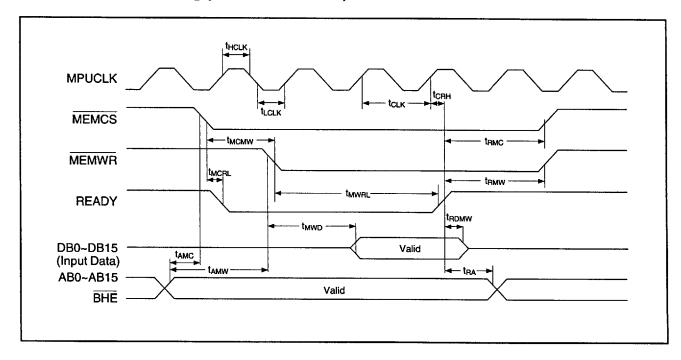

|     |         |                        | 3.1.4.3 | MEMWR T                 | iming (MPU Write Data to Video Memory)   | 45 |

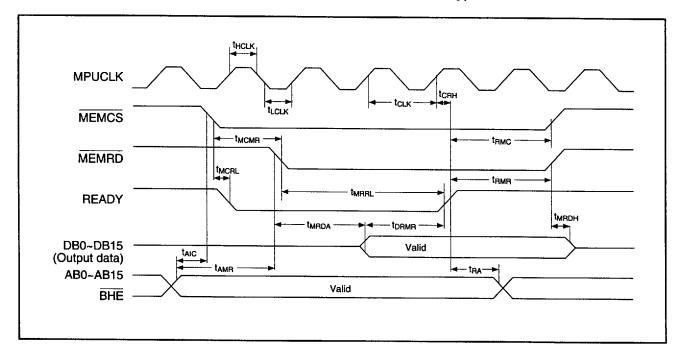

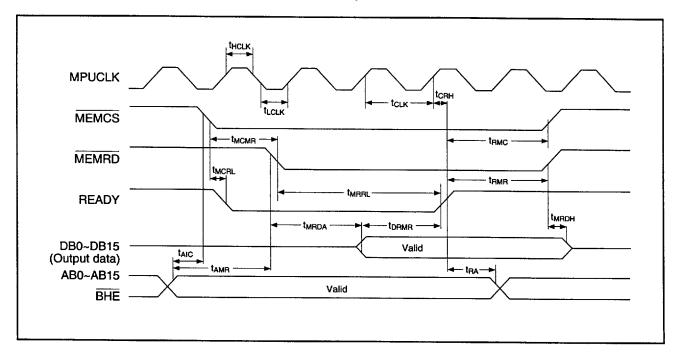

|     |         |                        | 3.1.4.4 | MEMRD Ti                | ming (MPU Read Data from Video Memory)   | 46 |

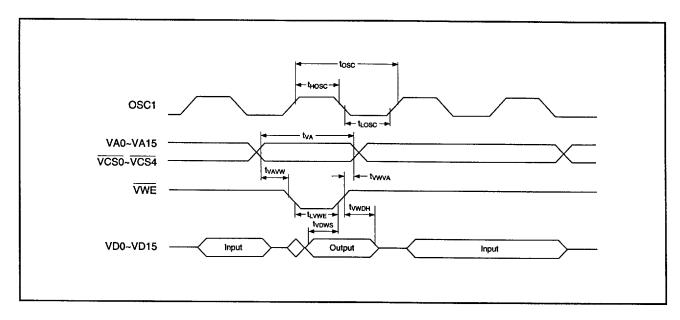

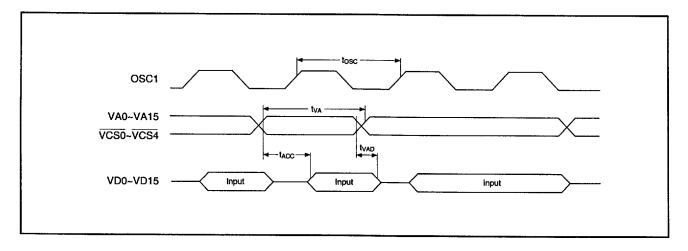

|     |         |                        | 3.1.4.5 | VRAM Inte               | rface Timing                             | 47 |

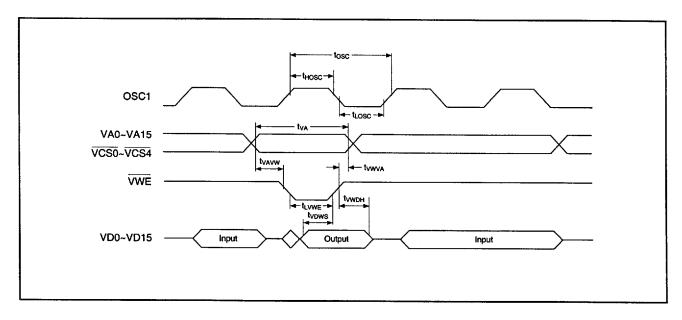

|     |         |                        |         | 3.1.4.5.1               | Write Data to VRAM                       | 47 |

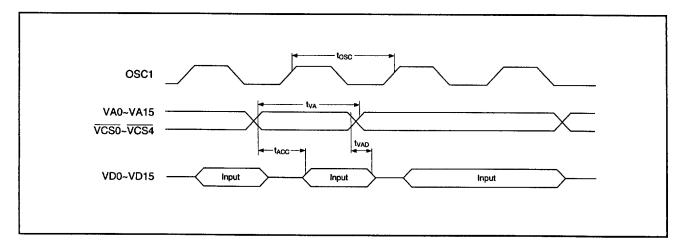

|     |         |                        |         | 3.1.4.5.2               | Read Data From VRAM                      | 47 |

|     |         |                        |         | 3.1.4.5.3               | Timing                                   | 48 |

| Tab | le | of  | Co           | nte | nte   |

|-----|----|-----|--------------|-----|-------|

| IUD | ıc | VI. | $\mathbf{v}$ |     | :1113 |

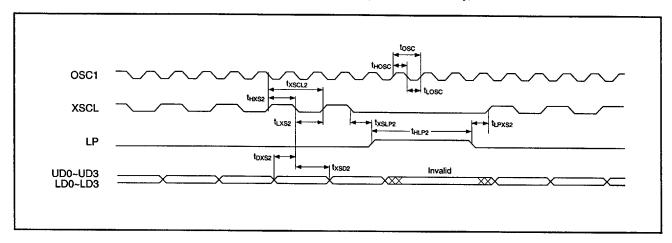

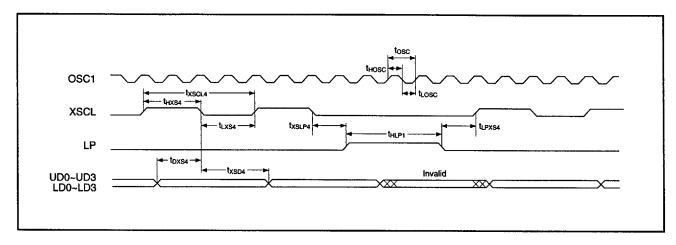

|       |       |                        | 3.1.4.6  | LCD Interfa               | ace Timing                                                       | 49 |

|-------|-------|------------------------|----------|---------------------------|------------------------------------------------------------------|----|

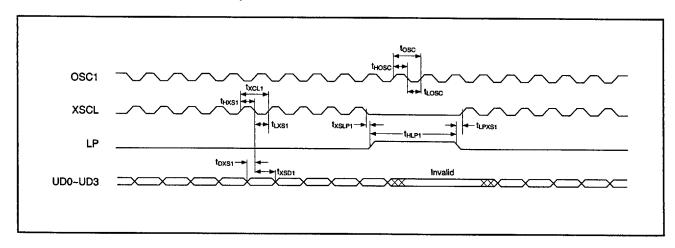

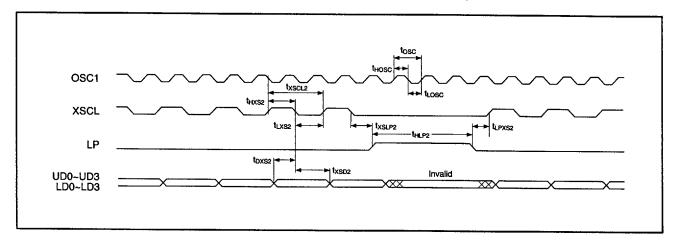

|       |       |                        |          | 3.1.4.6.1                 | Mode 1 (4-Bit transfer)                                          | 49 |

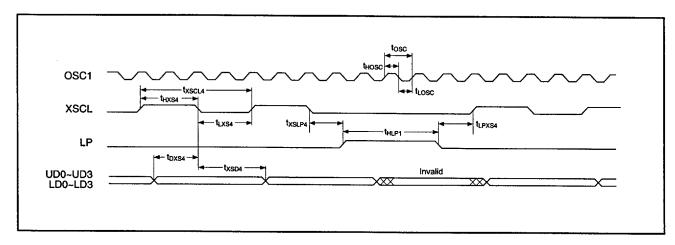

|       |       |                        |          | 3.1.4.6.2                 | Mode 1 (8-bit transfer), Mode 2, Mode 3 (4-bit                   |    |

|       |       |                        |          |                           | transfer), Mode 5                                                | 50 |

|       |       |                        |          | 3.1.4.6.3                 | Mode 3 (8-bit transfer, Mode 4, Mode 6                           | 51 |

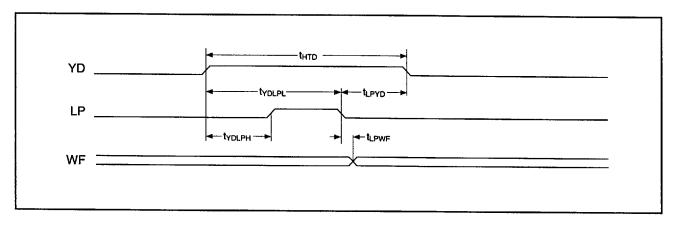

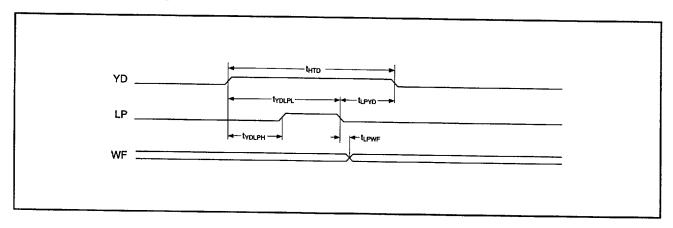

|       |       |                        |          | 3.1.4.6.4                 | Sync Timing                                                      |    |

|       | 3.2   | SED1351F <sub>LB</sub> |          |                           |                                                                  |    |

|       |       | 3.2.1                  | SED135   | 1F <sub>LB</sub> Absolute | e Maximum Ratings                                                | 53 |

|       |       | 3.2.2                  |          |                           | ating Conditions                                                 |    |

|       |       | 3.2.3                  |          |                           | racteristics                                                     |    |

|       |       | 3.2.4                  | SED135   | 1Flв AC Cha               | racteristics                                                     | 55 |

|       |       |                        | 3.2.4.1  | IOWR Timi                 | ng (Write to the Control Register)                               | 55 |

|       |       |                        | 3.2.4.2  | IORD Timi                 | ng (Read from Control Register)                                  | 56 |

|       |       |                        | 3.2.4.3  | MEMWR T                   | iming (Write to the VRAM)                                        | 57 |

|       |       |                        | 3.2.4.4  | MEMRD T                   | iming (Read from the VRAM)                                       | 58 |

|       |       |                        | 3.2.4.5  | Timing of I               | nterface with VRAM                                               | 59 |

|       |       |                        |          | 3.2.4.5.1                 | Write to the VRAM                                                | 59 |

|       |       |                        |          | 3.2.4.5.2                 | Read from the VRAM                                               | 59 |

|       |       |                        |          | 3.2.4.5.3                 | Timing                                                           | 60 |

|       |       |                        | 3.2.4.6  | LCD Interfa               | ace Timing                                                       | 61 |

|       |       |                        |          | 3.2.4.6.1                 | Mode 1 (4-Bit transfer)                                          | 61 |

|       |       |                        |          | 3.2.4.6.2                 | Mode 1 (8-bit transfer), Mode 2, Mode 3 (4-bit transfer), Mode 5 | 62 |

|       |       |                        |          | 3.2.4.6.3                 | Mode 3 (6-bit transfer), Mode 4, Mode 6                          | 63 |

|       |       |                        |          | 3.2.4.6.4                 | Sync Timing                                                      | 64 |

|       |       |                        |          |                           |                                                                  |    |

| 4.0 I | NTERN | IAL REGISTE            | RS       |                           |                                                                  | 67 |

|       | 4.1   | Summary                | ••••••   | •••••                     |                                                                  | 67 |

|       | 4.2   | Register Desc          | cription | ******************        |                                                                  | 68 |

|       |       | 4.2.1                  | R1 Mode  | e Register                |                                                                  | 68 |

|       |       | 4.2.2                  | R2 Line  | Byte Count F              | Register                                                         | 70 |

|       |       | 4.2.3                  |          |                           | Pulse Width Register                                             |    |

|       |       | 4.2.4                  |          |                           | Line Count Registers                                             |    |

|       |       | 4.2.5                  |          |                           | olay Start Address Registers                                     |    |

|       |       | 4.2.6                  |          |                           | play Start Address Registers                                     |    |

|       |       |                        |          | •                         | -<br>-                                                           |    |

|     |        | 4.2.7 R10, R11 Screen 1 Display Line Count Registers |     |

|-----|--------|------------------------------------------------------|-----|

|     |        | 4.2.8 R13 Address Pitch Adjustment Register          | 72  |

|     |        | 4.2.9 R14, R15 Gray-Scale Conversion Registers       | 73  |

| 5.0 | DISPLA | AY MODES                                             | 77  |

|     | 5.1    | Mode 1                                               | 77  |

|     | 5.2    | Mode 2                                               | 80  |

|     | 5.3    | Mode 3                                               | 82  |

|     | 5.4    | Mode 4                                               | 85  |

|     | 5.5    | Mode 5                                               | 87  |

| 6.0 | MPU IN | NTERFACE                                             | 95  |

|     | 6.1    | 8-bit MPU Interface                                  | 95  |

|     | 6.2    | 16-bit MPU Interface                                 | 96  |

| 7.0 | VIDEO  | MEMORY INTERFACE                                     | 99  |

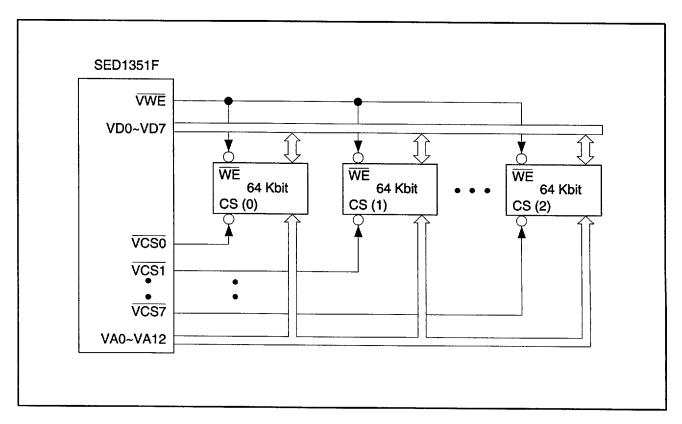

|     | 7.1    | 64 Kbit SRAM/8-bit MPU                               | 99  |

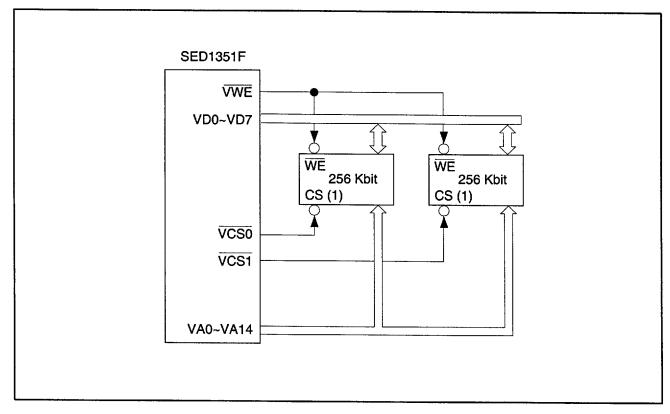

|     | 7.2    | 256 Kbit SRAM/8-bit MPU                              | 101 |

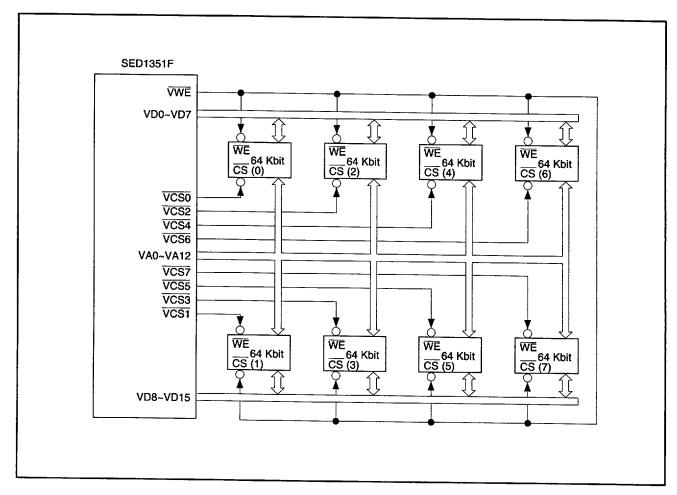

|     | 7.3    | 64 Kbit SRAM/16-bit MPU                              |     |

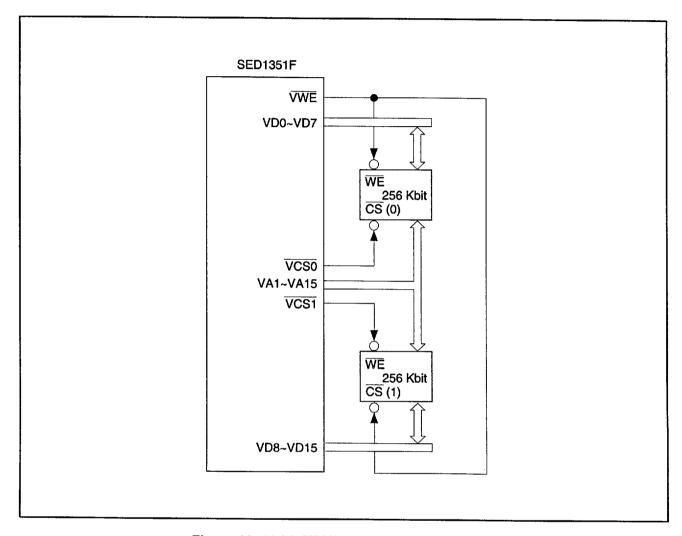

|     | 7.4    | 256 Kbit SRAM/16-bit MPU                             | 105 |

| 8.0 | LCD IN | ITERFACE                                             | 109 |

|     | 8.1    | DC Protection                                        | 109 |

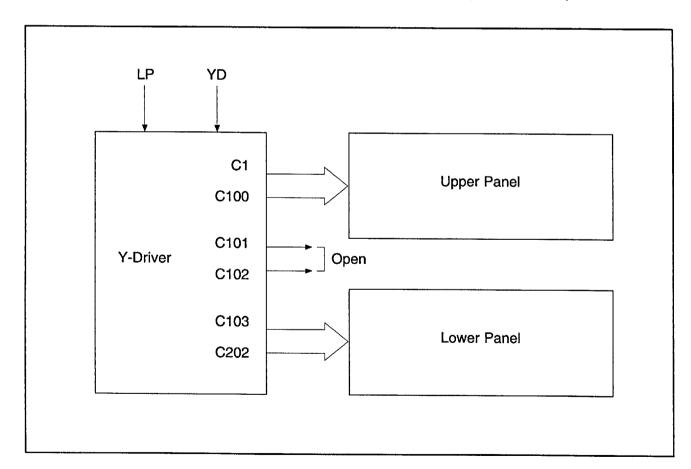

|     | 8.2    | Y-Drivers in Dual-LCD Panel Mode                     | 109 |

|     | 8.3    | Output Data Format                                   | 110 |

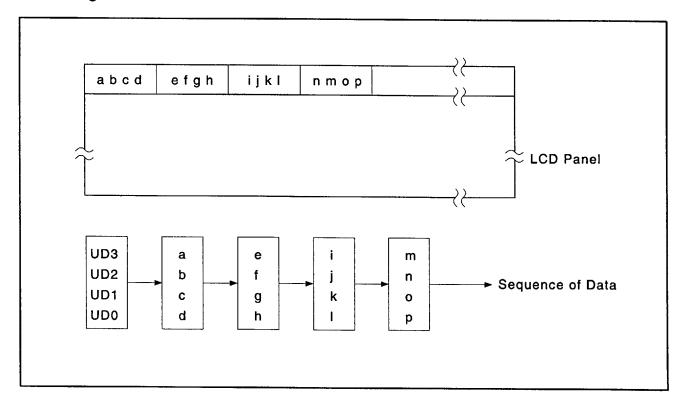

|     |        | 8.3.1 Single LCD/4-bit data                          | 110 |

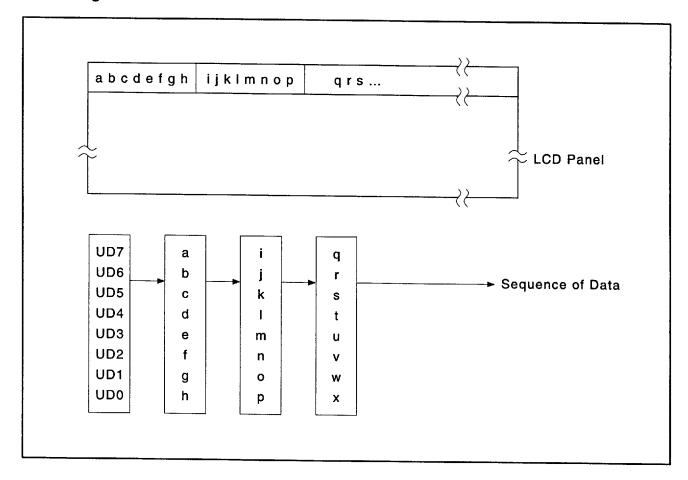

|     |        | 8.3.2 Single LCD/8-bit data                          | 111 |

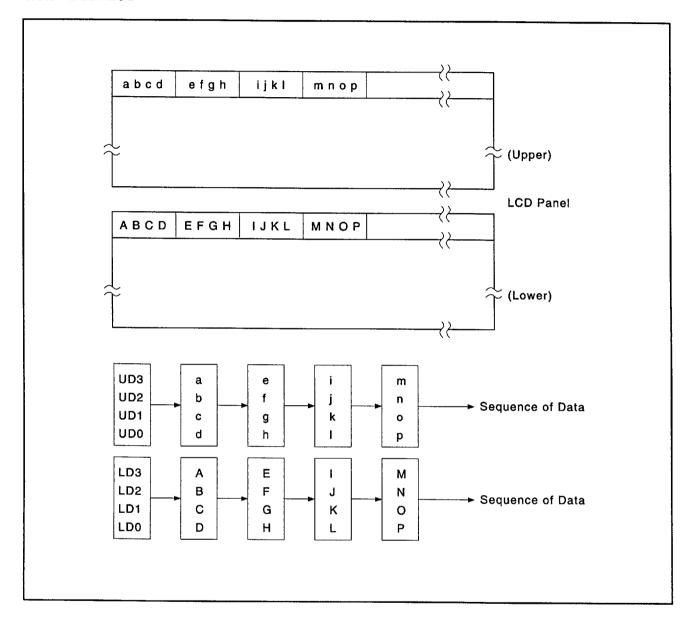

|     |        | 8.3.3 Dual LCD                                       | 112 |

| 9.0 | PACKA  | AGE DIMENSIONS                                       | 115 |

|     | 9.1    | SED1351F <sub>0A</sub>                               | 115 |

|     | 9.2    | SED1351F <sub>LB</sub>                               | 116 |

|     |        |                                                      |     |

THIS PAGE INTENTIONALLY BLANK

# *1.0* Data Sheet

THIS PAGE INTENTIONALLY BLANK

# 1.0 DATA SHEET

# **■ DESCRIPTION**

The SED1351F is a graphics LCD controller capable of controlling medium to large resolution displays. It transfers data from MPU to external frame buffer RAM and converts this data to display signals for LCD drivers. The SED1351F can display images with 4 gray shades and support display duty cycle as high as 1/1024.

The SED1351F is designed to achieve high efficiency and data throughput to the LCD. It has a cycle steal mode which allows MPU to access frame buffer RAM without interfering with the display operation. The SED1351F can directly interface with up to eight 64K-bit SRAMs or two 256K-bit SRAMs.

The SED1351F can operate with either 5V or 3V power supply. The 5V version chip is the SED1351F0A and the 3V version chip is the SED1351FLB.

### **■ FEATURES**

- Low-power CMOS technology

- 8-bit or 16-bit MPU data interface

- Direct interface with 80xx, Z80 and 68xxx MPU

- 4- or 8-bit panel data bus for single panel and 4-bit bus for dual panel

- Support logical OR of layers and panel division

- Smooth vertical scrolling

- Virtual screen display up to 1024

- Binary mode (on/off only) generates black & white images

- Gray mode (on/off and two gray steps) generates images with 4 gray shades

Maximum number of rows

Binary mode ..... 2048 Gray mode ..... 1024

Maximum number of rows:

Single panel ..... 1024 Dual panel ..... 2048

Maximum displaysizes when 64K-byte SRAMs are used:

> Binary mode .....  $2048 \times 256 / 1024 \times 512$ Gray mode .......  $1024 \times 256 / 512 \times 512$

Available models:

SED1351F0A ...... 5V, QFP5-100 pin SED1351FLB .......... 3V,QFP15-100 pin

# SYSTEM BLOCK DIAGRAM

# ■ INTERFACE WITH 8-BIT MPU (Z-80) AND 64K-BIT SRAM (8 of 8K x 8)

# ■ INTERFACE WITH 16-BIT MPU (8086) AND 64K-BIT SRAM (8 of 8K x 8)

# ■ INTERFACE WITH 16-BIT MPU (68000) AND 256K-BIT SRAM (2 of 32K x 8)

# 1.0 SED1351F Data Sheet

1.0

# **■ SUPPORTED RESOLUTIONS**

|         | Maximum Display Size |            |     | 0744 |      |              |           |           |

|---------|----------------------|------------|-----|------|------|--------------|-----------|-----------|

| Display | Mon                  | Monochrome |     | rays | cale | SRAM         | CPU       | SRAM      |

| RAM     | X                    | Y          | Х Ү |      | Υ    | Туре         | Interface | Interface |

| 8K      | 256                  | × 256      | 256 | ×    | 128  | 1 of 8K×8    | 8 bit     | 8 bit     |

| 16K     | 512                  | × 256      | 256 | ×    | 256  | 2 of 8K×8    | 8 bit     | 8 bit     |

|         |                      |            |     |      |      |              | 16 bit    | 16 bit    |

| 24K     | 512                  | × 384      | 384 | ×    | 256  | 3 of 8K×8    | 8 bit     | 8 bit     |

| 32K     | 512                  | × 512      | 512 | ×    | 256  | 4 of 8K × 8  | 8 bit     | 8 bit     |

|         |                      |            |     |      |      |              | 16 bit    | 16 bit    |

|         |                      |            |     |      |      | 1 of 32K × 8 | 8 bit     | 8 bit     |

| 48K     | 768                  | × 512      | 512 | ×    | 384  | 6 of 8K × 8  | 8 bit     | 8 bit     |

|         |                      |            |     |      |      |              | 16 bit    | 16 bit    |

| 56K     | 896                  | × 512      | 512 | ×    | 448  | 7 of 8K × 8  | 8 bit     | 8 bit     |

| 64K     | 1024                 | × 512      | 512 | ×    | 512  | 8 of 8K × 8  | 8 bit     | 8 bit     |

|         |                      |            |     |      |      |              | 16 bit    | 16 bit    |

|         |                      |            |     |      |      | 2 of 32K × 8 | 8 bit     | 8 bit     |

|         |                      |            |     |      |      |              | 16 bit    | 16 bit    |

# **■ BLOCK DIAGRAM**

# 1.0 SED1351F Data Sheet

1.0

# ■ ELECTRICAL CHARACTERISTICS

# SED1351F0A

# Absolute Maximum Ratings (F0A)

(Vss = 0V)

| Parameter                      | Symbol  | Ratings                | Unit |

|--------------------------------|---------|------------------------|------|

| Supply voltage                 | VDD     | Vss – 0.3 to 7.0       |      |

| Input voltage                  | Vı      | Vss - 0.3 to Vpp + 0.3 | V    |

| Output voltage                 | Vo      | Vss - 0.3 to Vpp + 0.3 | V    |

| Output current/pin             | lo      | ±10                    | mA   |

| Power dissipation              | PD      | 200                    | mW   |

| Supply current                 | IDD/ISS | ±40                    | mA   |

| Storage temperature            | Tstg    | -65 to 150             | °C   |

| Soldering temperature and time | Tsol    | 260°C, 10s (at lead)   |      |

# Recommended Operating Conditions (F0A)

(Vss = 0V)

| Parameter             | Symbol | Condition | Min | Тур | Max | Unit |

|-----------------------|--------|-----------|-----|-----|-----|------|

| Supply voltage        | VDD    |           | 4.5 | 5.0 | 5.5 | V    |

| Input voltage         | Vı     |           | Vss | _   | VDD | V    |

| Operating temperature | Topr   |           | -20 | _   | 75  | °C   |

# DC Characteristics (F0A)

$(Ta = -20 \text{ to } 75^{\circ}C)$

| Parameter                            | Symbol           | Condition                                   | Min                      | Тур | Max          | Unit |

|--------------------------------------|------------------|---------------------------------------------|--------------------------|-----|--------------|------|

| Static current                       | loos             | VIN = VDD, VDD = Max,<br>Vss, IOH = IOL = 0 |                          |     | 100          | μА   |

| Input leakage current (Type 1)       | lu               | VDD = 5.5V,<br>VIH = VDD,<br>VIL = VSS      | -10                      |     | 10           | μА   |

| High level input voltage 1 (OSC1)    | VIH1             | VDD = 5.5V                                  | 3.5                      | _   | _            | ٧    |

| Low level input voltage 1 (OSC1)     | VIL1             | VDD = 4.5V                                  | _                        |     | 1.0          | ٧    |

| High level input voltage 2 (Type 2)  | VIH2             | VDD = 5.5V                                  | 2.0                      |     |              | ٧    |

| Low level input voltage 2 (Type 2)   | VIL2             | VDD = 4.5V                                  | _                        |     | 0.8          | ٧    |

| High level input voltage 3 (Type 3)  | V <sub>T+</sub>  | VDD = 5.5V                                  | 4.0                      |     | _            | ٧    |

| Low level input voltage 3 (Type 3)   | VT-              | VDD = 4.5V                                  | _                        | _   | 0.8          | V    |

| Hysteresis voltage (Type 3)          | Vн               | VDD = 5V                                    | 0.3                      | _   | _            | V    |

| High level output voltage 1 (Type 4) | Vон1             | V <sub>DD</sub> = 4.5V<br>loн = -2mA        | V <sub>DD</sub><br>- 0.4 | _   |              | ٧    |

| Low level output voltage 1 (Type 4)  | Vol1             | loL = 6mA                                   |                          |     | Vss<br>+ 0.4 | ٧    |

| High level output voltage 2 (OSC2)   | VoH2             | VDD = 4.5V<br>IOH = -50μA                   | V <sub>DD</sub><br>- 0.4 | _   |              | ٧    |

| Low level output voltage 2 (OSC2)    | V <sub>OL2</sub> | loL = 50μA                                  |                          |     | Vss<br>+ 0.4 | ٧    |

# Note:

Type 1. MEMCS, MEMWR, MEMRD, IOCS, IOWR, IORD, MPUCLK, AB0 ~ AB15, BHE, MPUSEL, RESET, OSC

Type 2.  $\overline{\text{MEMCS}}$ ,  $\overline{\text{MEMRD}}$ ,  $\overline{\text{IOCS}}$ ,  $\overline{\text{IOWR}}$ ,  $\overline{\text{IORD}}$ , MPUCLK, AB0 ~ AB15,  $\overline{\text{BHE}}$ , DB0 ~ DB15, VD0 ~ VD15

Type 3. MPUSEL, RESET

Type 4. DB0 ~ DB15, READY, VA0 ~ VA15, VCS0 ~ VCS4, VD0 ~ VD15, VWE, XSCL, LP, WF, YD, UD0 ~ UD3, LD0 ~ LD3, **LCDENB**

# 1.0 SED1351F Data Sheet

1.0

# ■ ELECTRICAL CHARACTERISTICS

# • SED1351FLB

# Absolute Maximum Ratings (FLB)

(Vss = 0V)

| Parameter           | Symbol  | Ratings                     | Unit |

|---------------------|---------|-----------------------------|------|

| Supply voltage      | VDD     | Vss – 0.3 to 7.0            |      |

| Input voltage       | Vin     | Vss - 0.3 to Vpp + 0.5      | V    |

| Output voltage      | Vоит    | Vout Vss - 0.3 to Vpp + 0.5 |      |

| Output current/pin  | Іоит    | ±24                         | mA   |

| Power dissipation   | PD      | 200                         | mW   |

| Supply current      | IDD/Iss | ±40                         | mA   |

| Storage temperature | Tstg    | -65 to 150                  | °C   |

# Recommended Operating Conditions (FLB)

(Vss = 0V)

| Parameter             | Symbol | Condition | Min | Тур | Max | Unit |

|-----------------------|--------|-----------|-----|-----|-----|------|

| Supply voltage        | VDD    |           | 2.7 |     | 3.6 | V    |

| Input voltage         | Vin    |           | Vss |     | VDD | V    |

| Operating temperature | Topr   |           | -20 |     | 75  | °C   |

# DC Characteristics (FLB)

$(Ta = -20 \text{ to } 75^{\circ}\text{C})$

| Parameter                                                                                     | Symbol                                               | Condition                                      | Min                 | Тур | Max                     | Unit |

|-----------------------------------------------------------------------------------------------|------------------------------------------------------|------------------------------------------------|---------------------|-----|-------------------------|------|

| Static current                                                                                | IDDS                                                 | VIN = VDD or VSS<br>VDD = MAX<br>IOH = IOL = 0 |                     | _   | 30                      | μА   |

| Input leakage current (Type 1)                                                                | İL                                                   | VDD = MAX<br>VIH = VDD<br>VIL = VSS            | -1                  |     | 1                       | μА   |

| "H" level input voltage (OSC1) "L" level input voltage (OSC1)                                 | VIH1<br>VIL1                                         | VDD = MAX<br>VDD = MIN                         | 0.7 VDD             |     | <br>0.2 V <sub>DD</sub> | V    |

| "H" level input voltage (Type 2) "L" level input voltage (Type 2)                             | VIH2<br>VIL2                                         | VDD = MAX<br>VDD = MIN                         | 0.7 VDD             |     | 0.2Vpp                  | V    |

| "H" level input voltage (Type 3) "L" level input voltage (Type 3) Hysteresis voltage (Type 3) | V <sub>T+</sub><br>V <sub>T-</sub><br>V <sub>H</sub> | VDD = MAX<br>VDD = MIN<br>VDD = TYP            | 0.8 VDD<br>—<br>0.3 |     | 0.2 VDD                 | V    |

| "H" level output voltage (Type 4)                                                             | Vон1                                                 | VDD = MIN                                      | VDD - 0.3           | _   | _                       | ٧    |

| "L" level output voltage (Type 4)                                                             | V <sub>OL1</sub>                                     | Iон = −1.5mA<br>Io∟ = 3mA                      | _                   |     | V <sub>SS</sub> + 0.3   | ٧    |

| "H" level output voltage (OSC2)                                                               | VOH2                                                 | VDD = MIN                                      | VDD - 0.4           | _   | _                       | ٧    |

| "L" level output voltage (OSC2)                                                               | V <sub>OL2</sub>                                     | Iон = −50μA<br>Io∟ = 50μA                      |                     | _   | V <sub>SS</sub> + 0.4   | ٧    |

### Note:

Type 1. MEMCS, MEMWR, MEMRD, IOCS, IOWR, IORD, MPUCLK, AB0 ~ AB15, BHE, MPUSEL, RESET, OSC

Type 2. MEMCS, MEMWR, MEMRD, IOCS, IOWR, IORD, MPUCLK, ABO ~ AB15, BHE, DB0 ~ DB15, VD0 ~ VD15

Type 3. MPUSEL, RESET

Type 4. DB0 ~ DB15, READY, VA0 ~ VA15, VCS0 ~ VCS4, VD0 ~ VD15, VWE, XSCL, LP, WF, YD, UD0 ~ UD3, LD0 ~ LD3,

# 1.0 SED1351F Data Sheet

1.0

# **■ PIN CONFIGURATION (F0A)**

# **■ PIN CONFIGURATION (FLB)**

# ■ PIN DESCRIPTION

# 1. System Connector Terminals (at MPU)

| Pin Name    | Туре | F0A<br>Pin No. | FLB<br>Pin No. | Drv | Description                                                                                                                                                                                                                                                                                 |

|-------------|------|----------------|----------------|-----|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| DB0 to DB15 | 1/0  | 30 to 45       | 28 to 43       |     | These pins are interfaced with the MPU data bus. When using an 8-bit MPU, connect DB8 to DB15 to VDD.                                                                                                                                                                                       |

| AB0 to AB15 | I    | 14 to 29       | 12 to 27       |     | These pins are interfaced with the MPU address bus. If multiplexed address signals are used, connect them via latch circuits. A control register is selected by AB0 to AB3. Correspondence of the MPU address bus to the VRAM address bus is such that ABi = VAi (where i is a pin number). |

| BHE         | 1    | 13             | 11             |     | This signal is a bus high enable signal where a 16-bit MPU is used. It goes "L" (low) when an odd address is encountered. When using an 8-bit MPU configuration, connect the BHE pin to VDD.                                                                                                |

| IOCS        | l    | 3              | 1              |     | This pin selects a control register contained in the SED1351. It is "L" active, and must be assigned to MPU I/O space.                                                                                                                                                                      |

| IOWR        | I    | 4              | 2              |     | This signal is used for writing data into a control register contained in the SED1351. It is "L" active, and must go "L" when it encounters an OUT instruction from the MPU.                                                                                                                |

| IORD        | ı    | 5              | 3              |     | This signal is used for reading data from a control register contained in the SED1351. It is "L" active, and must go "L" when it encounters an IN instruction from the MPU.                                                                                                                 |

| MEMCS       | 1    | 6              | 4              |     | This signal is used for selecting VRAM. It is "L" active, and must be assigned to MPU memory space.                                                                                                                                                                                         |

| MEMWR       | l    | 7              | 5              |     | This signal is used for writing data to the VRAM. It is "L" active, and must go "L" when it encounters a memory write instruction from the MPU.                                                                                                                                             |

| MEMRD       | l    | 8              | 6              |     | This signal is used for reading data from the VRAM. It is "L" active, and must go "L" when it encounters a memory read instruction from the MPU.                                                                                                                                            |

# 1. System Connector Terminals (at MPU) (continued)

| Pin Name | Туре | F0A<br>Pin No. | FLB<br>Pin No. | Drv | Description                                                                                                                                                                                                                                                                                                                  |

|----------|------|----------------|----------------|-----|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| READY    | 0    | 9              | 7              |     | This signal requests the MPU to wait. It goes "L" by the falling edge of IOCS or MEMCS. It goes "H" by the rising edge of MPUCLK after completion of the SED1351 internal processing. Since READY is not a tri-state pin, it needed not be pulled up and must be connected directly to the READY (WAIT) terminal of the MPU. |

| MPUCLK   | 1    | 10             | 8              |     | This pin accepts an MPU clock. The MPU wait state is cleared by the rising edge of MPUCLK.                                                                                                                                                                                                                                   |

| MPUSEL   | 1    | 12             | 10             |     | This signal is connected to either VDD or VSS for selection of an MPU.  MPUSEL = VSS 8-bit MPU (e.g., Z80, V20, i8088)  MPUSEL = VDD 16-bit MPU (e.g., V30, i8086)                                                                                                                                                           |

| RESET    | l    | 11             | 9              |     | The MPU reset signal comes to this pin. It is "H" active, and initializes a control register.                                                                                                                                                                                                                                |

#### **Combinations of Control Pins**

| iocs | IOWR | IORD | MEMCS | MEMWR | MEMRD | Operation                  |

|------|------|------|-------|-------|-------|----------------------------|

| 1    | *    | *    | 1     | *     | *     | Invalid                    |

| 0    | 0    | 1    | 1     | 1     | 1     | Write to control register  |

| 0    | 1    | 0    | 1     | 1     | 1     | Read from control register |

| 1    | 1    | 1    | 0     | 0     | 1     | Write to VRAM              |

| 1    | 1    | 1    | 0     | 1     | 0     | Read from VRAM             |

Note: Any combination other than those listed above will cause a system error.

1 = "H" (high)

0 = L''(low)

\* = Don't care

## 2. VRAM Connector Terminals

| Pin Name               | Туре | F0A<br>Pin No.        | FLB<br>Pin No.        | Drv | Description                                                                                                                                                                                                                           |  |

|------------------------|------|-----------------------|-----------------------|-----|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| VD0 to VD15            | I/O  | 68 to 78,<br>81 to 85 | 68 to 83              |     | These pins are interfaced with the VRAM data bus. For a 16-bit MPU configuration, VD0 to VD7 must be connected to even addresses, and VD8 to VD15 to odd addresses. For an 8-bit configuration, VD8 to VD15 must be connected to VDD. |  |

| VA0 to VA12            | 0    | 47 to 59              | 45 to 49,<br>52 to 59 |     | These pins are interfaced with the VRAM address bus and chip select pins.                                                                                                                                                             |  |

| VA13/VCS7 to VA15/VCS5 | 0    | 60 to 62              | 60 to 62              |     | The SED1351 has chip select pins that can directly control eight 64K SRAMs (8K bytes each) or two                                                                                                                                     |  |

| VCS0 to VCS4           | 0    | 67 to 63              | 67 to 63              |     | 256K SRAMs (32K bytes) in the 64K VRAM space.<br>See Technical Manual for details.                                                                                                                                                    |  |

| VWE                    | 0    | 46                    | 44                    |     | This signal is used for writing data to the VRAM. It is "L" active, and must be connected to the WE pin of the VRAM.                                                                                                                  |  |

## 3. Oscillator Terminals

| Pin Name | Туре | F0A<br>Pin No. | FLB<br>Pin No. | Drv | Description                                                                                 |

|----------|------|----------------|----------------|-----|---------------------------------------------------------------------------------------------|

| OSC1     | 1    | 99             | 97             |     | The OSC1 (input) and OSC2 (output) pins gener-                                              |

| OSC2     | 0    | 100            | 98             |     | ate clocks for internal operation. They allow crystal oscillation and external clock input. |

## 4. Power Terminals

| Pin Name | Туре | F0A<br>Pin No. | FLB<br>Pin No. | Drv | Description                                                                                                                 |

|----------|------|----------------|----------------|-----|-----------------------------------------------------------------------------------------------------------------------------|

| VDD      | _    | 2, 79          | 51, 100        |     | The power supply pins include two VDDs and two                                                                              |

| Vss      | _    | 1, 80          | 50, 99         |     | Vsss. Apply +5V or +3V to VDD and 0V to Vss. A capacitor (4.7 µF or more) must be connected near each pair of VDD/Vss pins. |

# 5. LCD Connector Terminals

| Pin Name              | Туре | F0A<br>Pin No. | FLB<br>Pin No. | Drv | Description                                                                                                                                                                                                                                                |

|-----------------------|------|----------------|----------------|-----|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| UD0 to UD3            | I/O  | 91 to 94       | 89 to 92       |     | LCD display data. UD0 to UD3 are the upper panel                                                                                                                                                                                                           |

| LD0/UD4 to<br>LD3/UD7 | О    | 95 to 98       | 93 to 96       |     | display data in the signal panel or double panel drive panel mode. LD0/UD4 to LD3/UD7 are the lower panel display data in the double panel drive mode. UD0 to UD3, and LD0/UD4 to LD3/UD7 are used for 8-bit data transfer in the single panel drive mode. |

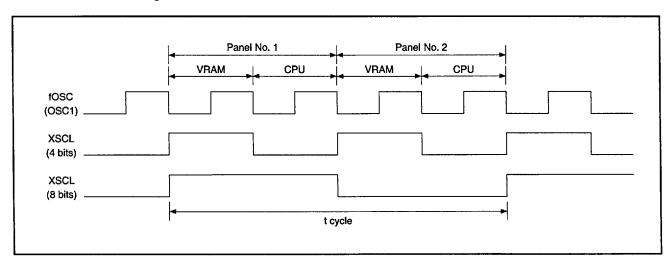

| XSCL                  | 0    | 87             | 85             |     | This single is a shift clock for display data transfer. Take the UD0 to UD3, LD0/UD4 to LD3/UD7 display data into LCDs by the falling edge of XSCL.                                                                                                        |

| LP                    | 0    | 88             | 86             |     | This pin provides both a display data latch pulse and a scan signal transfer clock. Upon completion of transferring the LCD data on one line, display data can be latched or a scan signal transferred by the falling edge of LP.                          |

| WF                    | 0    | 89             | 87             |     | This pin provides a frame signal used for LCD AC driving.                                                                                                                                                                                                  |

| YD                    | 0    | 90             | 88             |     | This pin provides a scanning line start pulse. The signal is "H" active. Allow the scanning line drive IC to take in YD by the falling edge of LP.                                                                                                         |

|                       |      |                |                |     | The SED1351 has two lines of retracing; if two scanning line drive ICs are cascade-connected for the upper and lower panels in the double panel drive mode, two lines must be provided between the upper and lower scanning line drive outputs.            |

| LCDENB                | 0    | 86             | 84             |     | This pin provides the data which is set in bit 1 (D1) of the mode register (R1). LCDENB goes "L" when the system is reset; it can be effectively used for LCD power control.                                                                               |

Illustrated below are the display data which are output from the UD0 to UD3, LD0/UD4 to LD3/UD7 and the display on the panel:

#### **■ LCD PANEL PIXELS**

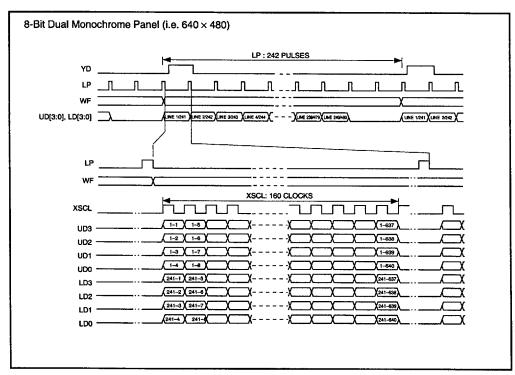

## ■ MONOCHROME LCD PANEL INTERFACE

#### ■ MONOCHROME LCD PANEL INTERFACE

## ■ PACKAGE DIMENSIONS

## SED1351F0A

## SED1351FLB

271-0.2 S-MOS Systems, Inc. • 2460 North First Street • San Jose, CA 95131 • Tel: (408) 922-0200 • Fax: (408) 922-0238 27

THIS PAGE INTENTIONALLY BLANK

# 2.0 Pin Description

# THIS PAGE INTENTIONALLY BLANK

# 2.0 PIN DESCRIPTION

#### 2.1 SED1351FOA

## 2.1.1 Pinout Diagram

# 2.1.2 SED1351F<sub>0A</sub> Pin Description Table

| Pin | Pin Name        | I/O |

|-----|-----------------|-----|

| 1   | Vss (GND)       | -   |

| 2   | V <sub>DD</sub> | _   |

| 3   | IOCS            | 1   |

| 4   | IOWR            |     |

| 5   | IORD            | 1   |

| 6   | MEMCS           | ı   |

| 7   | MEMWR           | 1   |

| 8   | MEMRD           | ı   |

| 9   | READY           | 0   |

| 10  | MPUCLK          | 1   |

| 11  | RESET           | 1   |

| 12  | MPUSEL          | 1   |

| 13  | BHE             | ı   |

| 14  | AB0             | 1   |

| 15  | AB1             | ı   |

| 16  | AB2             | ı   |

| 17  | AB3             | -   |

| 18  | AB4             | ı   |

| 19  | AB5             | ı   |

| 20  | AB6             |     |

| 21  | AB7             | ı   |

| 22  | AB8             | 1   |

| 23  | AB9             |     |

| 24  | AB10            |     |

| 25  | AB11            |     |

| 26  | AB12            | 1   |

| 27  | AB13            | ı   |

| 28  | AB14            | ı   |

| 29  | AB15            | 1   |

| 30  | DB0             | I/O |

| 31  | DB1             | I/O |

| 32  | DB2             | I/O |

| 33  | DB3             | I/O |

| 34  | DB4             | I/O |

| Pin | Pin Name | I/O          |

|-----|----------|--------------|

| 35  | DB5      | 1/0          |

| 36  | DB6      | 1/0          |

| 37  | DB7      | <del> </del> |

| 38  | DB8      | 1/0          |

|     |          | 1/0          |

| 39  | DB9      | 1/0          |

| 40  | DB10     | 1/0          |

| 41  | DB11     | 1/0          |

| 42  | DB12     | 1/0          |

| 43  | DB13     | 1/0          |

| 44  | DB14     | 1/0          |

| 45  | DB15     | 1/0          |

| 46  | VWE      | 0            |

| 47  | VA0      | 0            |

| 48  | VA1      | 0            |

| 49  | VA2      | 0            |

| 50  | VA3      | 0            |

| 51  | VA4      | 0            |

| 52  | VA5      | 0            |

| 53  | VA6      | 0            |

| 54  | VA7      | 0            |

| 55  | VA8      | 0            |

| 56  | VA9      | 0            |

| 57  | VA10     | 0            |

| 58  | VA11     | 0            |

| 59  | VA12     | 0            |

| 60  | VA13     | 0            |

| 61  | VA14     | 0            |

| 62  | VA15     | 0            |

| 63  | VCS4     | 0            |

| 64  | VCS3     | 0            |

| 65  | VCS2     | 0            |

| 66  | VCS1     | 0            |

| 67  | VCSO     | 0            |

| 68  | VD0      | 1/0          |

|     | 1 100    | "0           |

| Pin | Pin Name        | 1/0 |

|-----|-----------------|-----|

| 69  | VD1             | I/O |

| 70  | VD2             | I/O |

| 71  | VD3             | 1/0 |

| 72  | VD4             | 1/0 |

| 73  | VD5             | 1/0 |

| 74  | VD6             | 1/0 |

| 75  | VD7             | I/O |

| 76  | VD8             | 1/0 |

| 77  | VD9             | 1/0 |

| 78  | VD10            | 1/0 |

| 79  | V <sub>DD</sub> | _   |

| 80  | Vss (GND)       | _   |

| 81  | VD11            | 1/0 |

| 82  | VD12            | 1/0 |

| 83  | VD13            | I/O |

| 84  | VD14            | I/O |

| 85  | VD15            | 1/0 |

| 86  | LCDENB          | 0   |

| 87  | XSCL            | 0   |

| 88  | LP              | 0   |

| 89  | WF              | 0   |

| 90  | YD              | 0   |

| 91  | UD0             | 0   |

| 92  | UD1             | 0   |

| 93  | UD2             | 0   |

| 94  | UD3             | 0   |

| 95  | LD0             | 0   |

| 96  | LD1             | 0   |

| 97  | LD2             | 0   |

| 98  | LD3             | 0   |

| 99  | OSC1            | ı   |

| 100 | OSC2            | 0   |

# 2.0 Pin Description

2.2 - 2.2.1

#### 2.2 SED1351FLB

# 2.2.1 Package Layout

# 2.2.2 SED1351FLB Pin Description Table

| Pin | Pin Name | I/O |

|-----|----------|-----|

| 1   | IOCS     | 1   |

| 2   | IOWR     | l   |

| 3   | IORD     | 1   |

| 4   | MEMCS    | 1   |

| 5   | MEMWR    | ı   |

| 6   | MEMRD    | I   |

| 7   | READY    | 0   |

| 8   | MPUCLK   | Ī   |

| 9   | RESET    | I   |

| 10  | MPUSEL   | ı   |

| 11  | BHE      |     |

| 12  | AB0      | I   |

| 13  | AB1      | 1   |

| 14  | AB2      | ı   |

| 15  | AB3      | 1   |

| 16  | AB4      | ı   |

| 17  | AB5      | ı   |

| 18  | AB6      | 1   |

| 19  | AB7      | I   |

| 20  | AB8      | 1   |

| 21  | AB9      | 1   |

| 22  | AB10     | I   |

| 23  | AB11     | 1   |

| 24  | AB12     | I   |

| 25  | AB13     | 1   |

| 26  | AB14     | 1   |

| 27  | AB15     | 1   |

| 28  | DB0      | I/O |

| 29  | DB1      | I/O |

| 30  | DB2      | 1/0 |

| 31  | DB3      | I/O |

| 32  | DB4      | 1/0 |

| 33  | DB5      | 1/0 |

| 34  | DB6      | I/O |

| Pin | Pin Name  | I/O          |

|-----|-----------|--------------|

| 35  | DB7       | 1/0          |

| 36  | DB8       | I/O          |

| 37  | DB9       | 1/0          |

| 38  | DB10      | 1/0          |

| 39  | DB11      | 1/0          |

| 40  | DB12      | 1/0          |

| 41  | DB13      | 1/0          |

| 42  | DB14      | 1/0          |

| 43  | DB15      | 1/0          |

| 44  | VWE       | 0            |

| 45  | VA0       | 0            |

| 46  | VA1       | 0            |

| 47  | VA2       | 0            |

| 48  | VA3       | 0            |

| 49  | VA4       | 0            |

| 50  | Vss (GND) |              |

| 51  | VDD       | <del>-</del> |

| 52  | VA5       | 0            |

| 53  | VA6       | 0            |

| 54  | VA7       | 0            |

| 55  | VA8       | 0            |

| 56  | VA9       | 0            |

| 57  | VA10      | 0            |

| 58  | VA11      | 0            |

| 59  | VA12      | 0            |

| 60  | VA13      | 0            |

| 61  | VA14      | 0            |

| 62  | VA15      | 0            |

| 63  | VCS4      | 0            |

| 64  | VCS3      | 0            |

| 65  | VCS2      | 0            |

| 66  | VCS1      | 0            |

| 67  | VCS0      | 0            |

| 68  | VD0       | 1/0          |

| Pin | Pin Name        | 1/0 |

|-----|-----------------|-----|

| 69  | VD1             | 1/0 |

| 70  | VD2             | 1/0 |

| 71  | VD3             | I/O |

| 72  | VD4             | 1/0 |

| 73  | VD5             | 1/0 |

| 74  | VD6             | 1/0 |

| 75  | VD7             | 1/0 |

| 76  | VD8             | 1/0 |

| 77  | VD9             | 1/0 |

| 78  | VD10            | 1/0 |

| 79  | VD11            | I/O |

| 80  | VD12            | 1/0 |

| 81  | VD13            | 1/0 |

| 82  | VD14            | I/O |

| 83  | VD15            | I/O |

| 84  | LCDENB          | 0   |

| 85  | XSCL            | 0   |

| 86  | LP              | 0   |

| 87  | WF              | 0   |

| 88  | YD              | 0   |

| 89  | UD0             | 0   |

| 90  | UD1             | 0   |

| 91  | UD2             | 0   |

| 92  | UD3             | 0   |

| 93  | LD0             | 0   |

| 94  | LD1             | 0   |

| 95  | LD2             | 0   |

| 96  | LD3             | 0   |

| 97  | OSC1            | I   |

| 98  | OSC2            | 0   |

| 99  | Vss (GND)       |     |

| 100 | V <sub>DD</sub> |     |

#### 2.3 SYSTEM INTERFACE

**Table 1. MPU Interface Control Signal Functions**

| IOCS | IOWR | IORD | MEMCS | MEMWR | MEMRD | Operation                  |

|------|------|------|-------|-------|-------|----------------------------|

| 1    | *    | *    | 1     | *     | *     | Invalid                    |

| 0    | 0    | 1    | 1     | 1     | 1     | Write to control register  |

| 0    | 1    | 0    | 1     | 1     | 1     | Read from control register |

| 1    | 1    | 1    | 0     | 0     | 1     | Write to VRAM              |

| 1    | 1    | 1    | 0     | 1     | 0     | Read from VRAM             |

#### READY

MPU "wait" request output. It goes "L" on the falling edge of IOCS or MEMCS. It goes "H" the on the rising edge of the first MPUCLK after completion of SED1351F internal processing. READY is connected directly to the READY (or WAIT) terminal of the MPU.

#### MPUCLK

MPU clock input

#### MPUSEL

This input selects an 8- or 16-bit MPU interface.

- MPUSEL=0: 8-bit MPU interface (Z80, V20,i8088)

- MPUSEL=1: 16-bit MPU interface (V30,i8086)

#### RESET

MPU reset imput. This active high signal initializes R1, the system Mode Register.

#### **VRAM INTERFACE** 2.4

#### VD0-VD15

These pins are connected to the VRAM data bus. For 16-bit MPUs VD0-VD7 are connected to the data bus of even byte addresses and VD8-VD15 to the data bus of odd byte addresses. For 8-bit MPUs, VD8-VD15 must be tied to VDD.

## VA0-VA12,VA13/VCS7-VA15/VCS5,VCS0-VCS4

These pins are connected to the VRAM address bus and chip select lines.

The SED1351F provides select signals that can directly control eight 64 Kbit SRAMs (8 Kbytes each) or two 256 Kbit SRAMs (32 Kbytes) in the 64 Kbytes VRAM space.

#### VWE

This output is used for writing data to the VRAM. It is active low and is connected to the  $\overline{WE}$  input of the SRAMS.

#### 2.5 **LCD INTERFACE**

### UD0-UD3,LD0/UD4-LD3/UD7

LCD display data output lines. UD0-UD3 provide the upper panel display data in single- or dualpanel LCD modes. LD0/UD4-LD3/UD7 provide the lower panel display data in dual-panel, dualdrive LCD mode. UD0-UD3, LD0/UD4-LD3/UD7 are used for 8-bit data transfer in single-panel, single-drive LCD mode.

#### • XSCL

Display data shift clock output. Data is shifted into the LCD X-drivers on the falling edge of this signal.

#### • LP

Display data latch clock output. One line of data is latched into the LCD X-drivers on the falling edge of this signal. LP can also be used to shift the Y-drive active line down by one.

#### WF

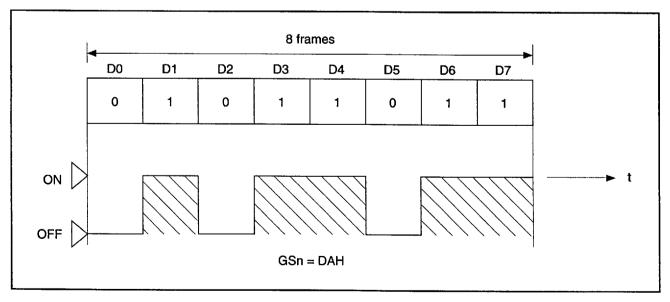

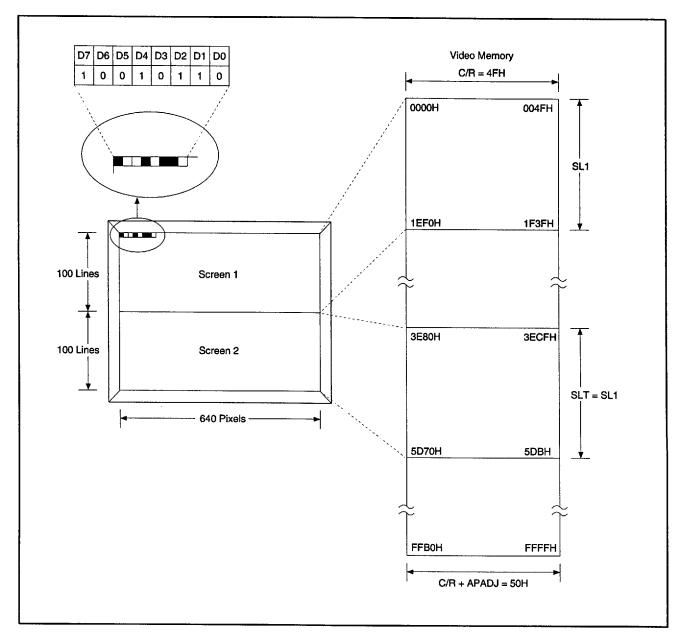

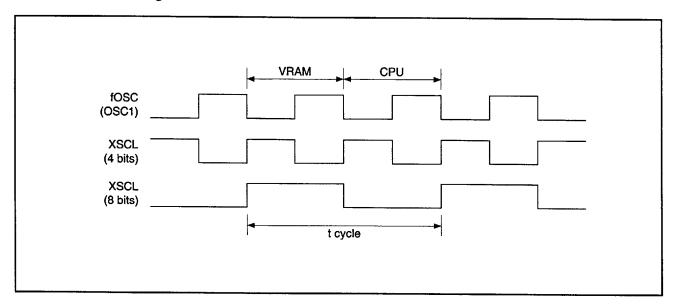

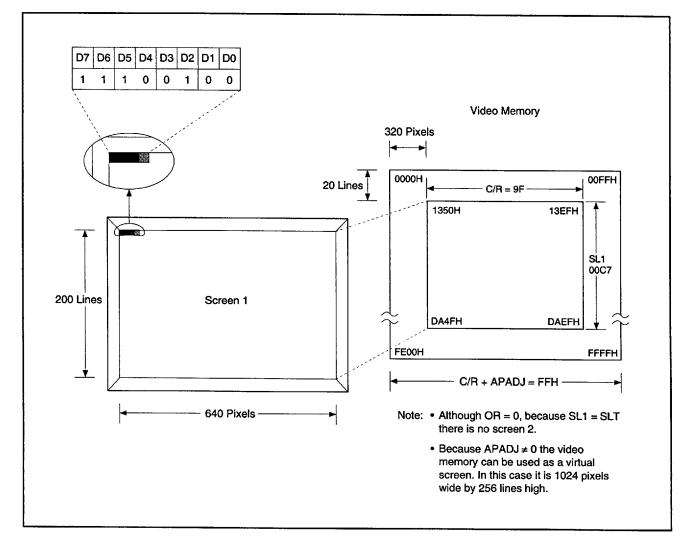

LCD AC-drive signal output.