# 256M-S DDR SDRAM HY5DU56422B(L)F HY5DU56822B(L)F

# **Revision History**

- 1. Revision 0.1 (July 2003)

- 1) Define Preliminary Specification

**PRELIMINARY**

#### **DESCRIPTION**

The Hynix HY5DU56422 and HY5DU56822 are a 268,435,456-bit CMOS Double Data Rate(DDR) Synchronous DRAM, ideally suited for the main memory applications which requires large memory density and high bandwidth.

The Hynix 256Mb DDR SDRAMs offer fully synchronous operations referenced to both rising and falling edges of the clock. While all addresses and control inputs are latched on the rising edges of the CK (falling edges of the /CK), Data, Data strobes and Write data masks inputs are sampled on both rising and falling edges of it. The data paths are internally pipelined and 2-bit prefetched to achieve very high bandwidth. All input and output voltage levels are compatible with SSTL 2.

#### **FEATURES**

- VDD, VDDQ = 2.5V +/- 0.2V

- All inputs and outputs are compatible with SSTL\_2 interface

- Fully differential clock inputs (CK, /CK) operation

- Double data rate interface

- Source synchronous data transaction aligned to bidirectional data strobe (DOS)

- x16 device has two bytewide data strobes (UDQS, LDQS) per each x8 I/O

- Data outputs on DQS edges when read (edged DQ)

Data inputs on DQS centers when write (centered DQ)

- On chip DLL align DQ and DQS transition with CK transition

- DM mask write data-in at the both rising and falling edges of the data strobe

- All addresses and control inputs except data, data strobes and data masks latched on the rising edges of the clock

- Programmable CAS latency 1.5, 2, 2.5 and 3 supported

- Programmable burst length 2 / 4 / 8 with both sequential and interleave mode

- Internal four bank operations with single pulsed /RAS

- tRAS Lock-out function supported

- Auto refresh and Self refresh supported

- 8192 refresh cycles / 64ms

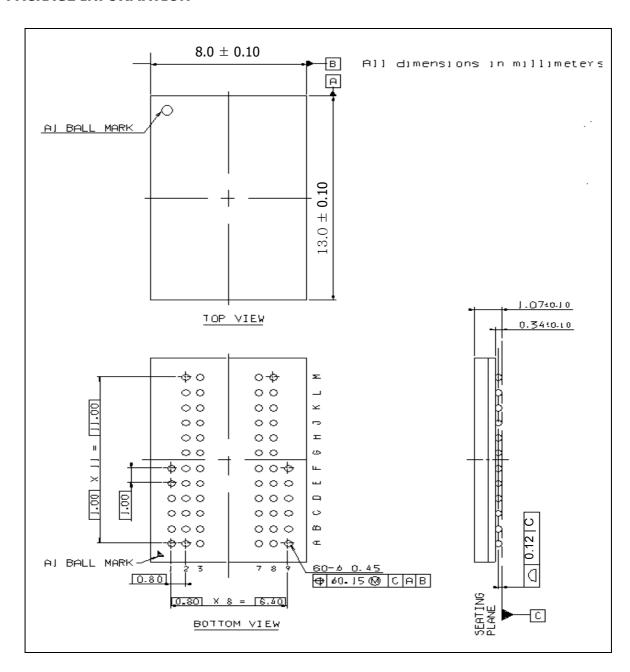

- 60 Ball FBGA Package Type

- Full and Half strength driver option controlled by EMRS

#### **ORDERING INFORMATION**

| Part No.           | Configuration | Package |

|--------------------|---------------|---------|

| HY5DU56422B(L)F-X* | 64Mx4         | 60 Ball |

| HY5DU56822B(L)F-X* | 32Mx8         | FBGA    |

<sup>\*</sup> X means speed grade

#### **OPERATING FREQUENCY**

| Grade | CL2    | CL2.5  | Remark<br>(CL-tRCD-tRP) |  |  |

|-------|--------|--------|-------------------------|--|--|

| - J   | 133MHz | 166MHz | DDR333 (2.5-3-3)        |  |  |

| - M   | 133MHz | 133MHz | DDR266 (2-2-2)          |  |  |

| - K   | 133MHz | 133MHz | DDR266A (2-3-3)         |  |  |

| - H   | 100MHz | 133MHz | DDR266B (2.5-3-3)       |  |  |

| - L   | 100MHz | 125MHz | DDR200 (2-2-2)          |  |  |

<sup>\*</sup> CL1.5 @ DDR200 supported

Rev. 0.1 / Apr. 02

<sup>\*</sup> CL3 supported

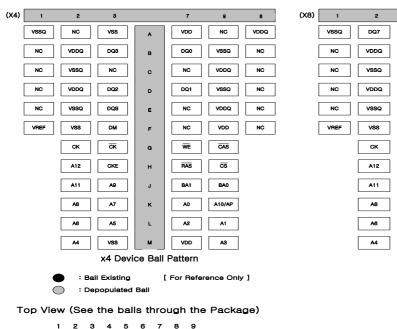

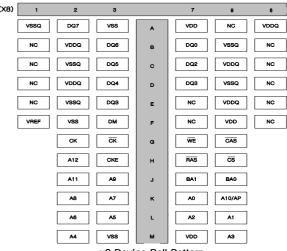

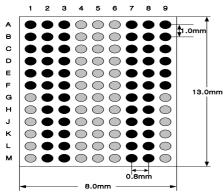

#### **PIN CONFIGURATION**

x8 Device Ball Pattern

BGA Package Ball Pattern Top View

#### **ROW AND COLUMN ADDRESS TABLE**

| ITEMS               | 64Mx4            | 32Mx8           |  |

|---------------------|------------------|-----------------|--|

| Organization        | 16M x 4 x 4banks | 8M x 8 x 4banks |  |

| Row Address         | A0 - A12         | A0 - A12        |  |

| Column Address      | A0-A9, A11       | A0-A9           |  |

| Bank Address        | BA0, BA1         | BA0, BA1        |  |

| Auto Precharge Flag | A10              | A10             |  |

| Refresh             | 8K               | 8K              |  |

# **PIN DESCRIPTION**

| PIN                 | TYPE   | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|---------------------|--------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| CK, /CK             | Input  | Clock: CK and /CK are differential clock inputs. All address and control input signals are sampled on the crossing of the positive edge of CK and negative edge of /CK. Output (read) data is referenced to the crossings of CK and /CK (both directions of crossing).                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| CKE                 | Input  | Clock Enable: CKE HIGH activates, and CKE LOW deactivates internal clock signals, and device input buffers and output drivers. Taking CKE LOW provides PRECHARGE POWER DOWN and SELF REFRESH operation (all banks idle), or ACTIVE POWER DOWN (row ACTIVE in any bank). CKE is synchronous for POWER DOWN entry and exit, and for SELF REFRESH entry. CKE is asynchronous for SELF REFRESH exit, and for output disable. CKE must be maintained high throughout READ and WRITE accesses. Input buffers, excluding CK, /CK and CKE are disabled during POWER DOWN. Input buffers, excluding CKE are disabled during SELF REFRESH. CKE is an SSTL_2 input, but will detect an LVCMOS LOW level after Vdd is applied. |

| /CS                 | Input  | Chip Select: Enables or disables all inputs except CK, /CK, CKE, DQS and DM. All commands are masked when CS is registered high. CS provides for external bank selection on systems with multiple banks. CS is considered part of the command code.                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| BA0, BA1            | Input  | Bank Address Inputs: BA0 and BA1 define to which bank an ACTIVE, Read, Write or PRE-CHARGE command is being applied.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| A0 ~ A12            | Input  | Address Inputs: Provide the row address for ACTIVE commands, and the column address and AUTO PRECHARGE bit for READ/WRITE commands, to select one location out of the memory array in the respective bank. A10 is sampled during a precharge command to determine whether the PRECHARGE applies to one bank (A10 LOW) or all banks (A10 HIGH). If only one bank is to be precharged, the bank is selected by BA0, BA1. The address inputs also provide the op code during a MODE REGISTER SET command. BA0 and BA1 define which mode register is loaded during the MODE REGISTER SET command (MRS or EMRS).                                                                                                        |

| /RAS, /CAS, /WE     | Input  | Command Inputs: /RAS, /CAS and /WE (along with /CS) define the command being entered.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| DM<br>(LDM, UDM)    | Input  | Input Data Mask: DM is an input mask signal for write data. Input data is masked when DM is sampled HIGH along with that input data during a WRITE access. DM is sampled on both edges of DQS. Although DM pins are input only, the DM loading matches the DQ and DQS loading. For the x16, LDM corresponds to the data on DQ0-Q7; UDM corresponds to the data on DQ8-Q15.                                                                                                                                                                                                                                                                                                                                         |

| DQS<br>(LDQS, UDQS) | I/O    | Data Strobe: Output with read data, input with write data. Edge aligned with read data, centered in write data. Used to capture write data. For the x16, LDQS corresponds to the data on DQ0-Q7; UDQS corresponds to the data on DQ8-Q15.                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| DQ                  | I/O    | Data input / output pin : Data bus                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| VDD/VSS             | Supply | Power supply for internal circuits and input buffers.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| VDDQ/VSSQ           | Supply | Power supply for output buffers for noise immunity.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| VREF                | Supply | Reference voltage for inputs for SSTL interface.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| NC                  | NC     | No connection.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

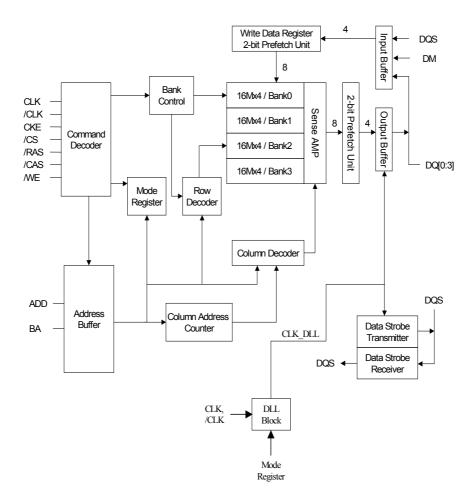

# **FUNCTIONAL BLOCK DIAGRAM (64Mx4)**

4Banks x 16Mbit x 4 I/O Double Data Rate Synchronous DRAM

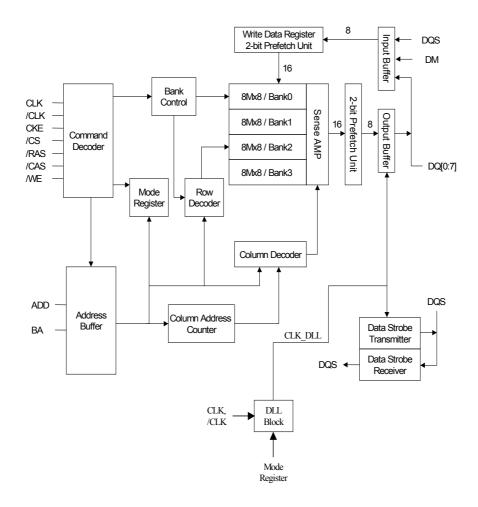

# **FUNCTIONAL BLOCK DIAGRAM (32Mx8)**

4Banks x 8Mbit x 8 I/O Double Data Rate Synchronous DRAM

#### SIMPLIFIED COMMAND TRUTH TABLE

| Comman                    | d                   | CKEn-1 | CKEn | cs | RAS | CAS | WE | ADDR | A10/<br>AP | ВА | Note |

|---------------------------|---------------------|--------|------|----|-----|-----|----|------|------------|----|------|

| Extended Mode Re          | egister Set         | Н      | Х    | L  | L   | L   | L  | С    | P code     |    | 1,2  |

| Mode Registe              | er Set              | Н      | Х    | L  | L   | L   | L  | О    | P code     |    | 1,2  |

| Device Dese               | elect               | Н      | Х    | Н  | Х   | Х   | Х  |      | Х          |    | 1    |

| No Operati                | on                  | "      | ^    | L  | Н   | Н   | Н  |      | Х          |    |      |

| Bank Activ                | /e                  | Н      | Х    | L  | L   | Н   | Н  | R/   | 4          | V  | 1    |

| Read                      |                     | Н      | Х    | L  | Н   | L   | Н  | CA   | L          | V  | 1    |

| Read with Autop           | recharge            | 11     | ^    | _  | ''  |     | "  | CA   | Н          | •  | 1,3  |

| Write                     |                     | Н      | Х    | L  | Н   | L   | L  | CA   | L          | V  | 1    |

| Write with Autop          | recharge            | 11     | ^    | L  | "   | L   | L  | CA   | Н          |    | 1,4  |

| Precharge All             | Precharge All Banks |        | Х    | L  | L   | Н   | L  | Х    | Н          | Х  | 1,5  |

| Precharge select          | ed Bank             | Н      | ^    | _  | _   |     | _  | ^    | L          | ٧  | 1    |

| Read Burst S              | Stop                | Н      | Х    | L  | Н   | Н   | L  | Х    |            | 1  |      |

| Auto Refre                | sh                  | Н      | Н    | L  | L   | L   | Н  | Х    |            | 1  |      |

|                           | Entry               | Н      | L    | L  | L   | L   | Н  |      |            |    | 1    |

| Self Refresh              | Exit                | L      | Н    | Н  | Х   | Х   | Х  |      | Χ          |    | 1    |

|                           | LAIC                | _      |      | L  | Н   | Н   | Н  |      |            |    |      |

|                           | Entry               | Н      | L    | Н  | Х   | Х   | Х  |      |            |    | 1    |

| Precharge Power           | Litay               |        | _    | L  | Н   | Н   | Н  |      | X          |    | 1    |

| Down Mode                 | Down Mode Exit      | L      | Н    | Н  | Х   | Х   | Х  |      | Λ          |    | 1    |

| EXIL                      |                     | _      |      | L  | Н   | Н   | Н  |      |            |    | 1    |

|                           | Entry               | Н      | L    | Н  | Х   | Х   | Х  |      |            |    | 1    |

| Active Power<br>Down Mode | Lift                | ''     | _    | L  | V   | V   | V  | x    |            |    | 1    |

|                           | Exit                | L      | Н    |    | )   | X   |    |      |            |    | 1    |

( H=Logic High Level, L=Logic Low Level, X=Don't Care, V=Valid Data Input, OP Code=Operand Code, NOP=No Operation )

#### Note:

- 1. LDM/UDM states are Don't Care. Refer to below Write Mask Truth Table.

- 2. OP Code(Operand Code) consists of A0~A11 and BA0~BA1 used for Mode Register setting duing Extended MRS or MRS. Before entering Mode Register Set mode, all banks must be in a precharge state and MRS command can be issued after tRP period from Prechagre command.

- 3. If a Read with Autoprecharge command is detected by memory component in CK(n), then there will be no command presented to activated bank until CK(n+BL/2+tRP).

- 4. If a Write with Autoprecharge command is detected by memory component in CK(n), then there will be no command presented to activated bank until CK(n+BL/2+1+tDPL+tRP). Last Data-In to Prechage delay(tDPL) which is also called Write Recovery Time (tWR) is needed to guarantee that the last data has been completely written.

- 5. If A10/AP is High when Precharge command being issued, BA0/BA1 are ignored and all banks are selected to be precharged.

### **WRITE MASK TRUTH TABLE**

| Function     | CKEn-1 | CKEn | /CS, /RAS, /CAS, /WE | DM | ADD<br>R | A10/<br>AP | ВА | Note |

|--------------|--------|------|----------------------|----|----------|------------|----|------|

| Data Write   | Н      | Х    | Х                    | L  |          | Х          |    | 1    |

| Data-In Mask | Н      | Х    | Х                    | Н  |          | Х          |    | 1    |

#### Note:

1. Write Mask command masks burst write data with reference to LDQS/UDQS(Data Strobes) and it is not related with read data. In case of x16 data I/O, LDM and UDM control lower byte(DQ0~7) and Upper byte(DQ8~15) respectively.

# **OPERATION COMMAND TRUTH TABLE-I**

| Current<br>State | /cs | /RAS | /CAS | /WE | Address    | Command       | Action                                        |

|------------------|-----|------|------|-----|------------|---------------|-----------------------------------------------|

|                  | Н   | Х    | Х    | Х   | Х          | DSEL          | NOP or power down <sup>3</sup>                |

|                  | L   | Н    | Н    | Н   | Х          | NOP           | NOP or power down <sup>3</sup>                |

|                  | L   | Н    | Н    | L   | Х          | BST           | ILLEGAL <sup>4</sup>                          |

|                  | L   | Н    | L    | Н   | BA, CA, AP | READ/READAP   | ILLEGAL <sup>4</sup>                          |

| IDLE             | L   | Н    | L    | L   | BA, CA, AP | WRITE/WRITEAP | ILLEGAL <sup>4</sup>                          |

|                  | L   | L    | Н    | Н   | BA, RA     | ACT           | Row Activation                                |

|                  | L   | L    | Н    | L   | BA, AP     | PRE/PALL      | NOP                                           |

|                  | L   | L    | L    | Н   | Х          | AREF/SREF     | Auto Refresh or Self Refresh <sup>5</sup>     |

|                  | L   | L    | L    | L   | OPCODE     | MRS           | Mode Register Set                             |

|                  | Н   | Х    | Х    | Х   | Х          | DSEL          | NOP                                           |

|                  | L   | Н    | Н    | Н   | Х          | NOP           | NOP                                           |

|                  | L   | Н    | Н    | L   | Х          | BST           | ILLEGAL <sup>4</sup>                          |

|                  | L   | Н    | L    | Н   | BA, CA, AP | READ/READAP   | Begin read : optional AP <sup>6</sup>         |

| ROW              | L   | Н    | L    | L   | BA, CA, AP | WRITE/WRITEAP | Begin write : optional AP <sup>6</sup>        |

| ACTIVE           | L   | L    | Н    | Н   | BA, RA     | ACT           | ILLEGAL <sup>4</sup>                          |

|                  | L   | L    | Н    | L   | BA, AP     | PRE/PALL      | Precharge <sup>7</sup>                        |

|                  | L   | L    | L    | Н   | Х          | AREF/SREF     | ILLEGAL <sup>11</sup>                         |

|                  | L   | L    | L    | L   | OPCODE     | MRS           | ILLEGAL <sup>11</sup>                         |

|                  | Н   | Х    | Х    | Х   | Х          | DSEL          | Continue burst to end                         |

|                  | L   | Н    | Н    | Н   | Х          | NOP           | Continue burst to end                         |

|                  | L   | Н    | Н    | L   | Х          | BST           | Terminate burst                               |

|                  | L   | Н    | L    | Н   | BA, CA, AP | READ/READAP   | Term burst, new read:optional AP <sup>8</sup> |

| READ             | L   | Н    | L    | L   | BA, CA, AP | WRITE/WRITEAP | ILLEGAL                                       |

|                  | L   | L    | Н    | Н   | BA, RA     | ACT           | ILLEGAL <sup>4</sup>                          |

|                  | L   | L    | Н    | L   | BA, AP     | PRE/PALL      | Term burst, precharge                         |

|                  | L   | L    | L    | Н   | Х          | AREF/SREF     | ILLEGAL <sup>11</sup>                         |

|                  | L   | L    | L    | L   | OPCODE     | MRS           | ILLEGAL <sup>11</sup>                         |

|                  | Н   | Х    | Х    | Х   | Х          | DSEL          | Continue burst to end                         |

|                  | L   | Н    | Н    | Н   | Х          | NOP           | Continue burst to end                         |

| WRITE            | L   | Н    | Н    | L   | X          | BST           | ILLEGAL <sup>4</sup>                          |

|                  | L   | Н    | L    | Н   | BA, CA, AP | READ/READAP   | Term burst, new read:optional AP <sup>8</sup> |

|                  | L   | Н    | L    | L   | BA, CA, AP | WRITE/WRITEAP | Term burst, new write:optional AP             |

# **OPERATION COMMAND TRUTH TABLE-II**

| Current<br>State   | /cs | /RAS | /CAS | /WE | Address    | Command       | Action                   |

|--------------------|-----|------|------|-----|------------|---------------|--------------------------|

|                    | L   | L    | Н    | Н   | BA, RA     | ACT           | ILLEGAL <sup>4</sup>     |

| WOITE              | L   | L    | Н    | L   | BA, AP     | PRE/PALL      | Term burst, precharge    |

| WRITE              | L   | L    | L    | Н   | Х          | AREF/SREF     | ILLEGAL <sup>11</sup>    |

|                    | L   | L    | L    | L   | OPCODE     | MRS           | ILLEGAL <sup>11</sup>    |

|                    | Н   | Х    | Х    | Х   | Х          | DSEL          | Continue burst to end    |

|                    | L   | Н    | Н    | Н   | Х          | NOP           | Continue burst to end    |

|                    | L   | Н    | Н    | L   | Х          | BST           | ILLEGAL                  |

| READ               | L   | Н    | L    | Н   | BA, CA, AP | READ/READAP   | ILLEGAL <sup>10</sup>    |

| WITH<br>AUTOPRE-   | L   | Н    | L    | L   | BA, CA, AP | WRITE/WRITEAP | ILLEGAL <sup>10</sup>    |

| CHARGE             | L   | L    | Н    | Н   | BA, RA     | ACT           | ILLEGAL <sup>4,10</sup>  |

|                    | L   | L    | Н    | L   | BA, AP     | PRE/PALL      | ILLEGAL <sup>4,10</sup>  |

|                    | L   | L    | L    | Н   | Х          | AREF/SREF     | ILLEGAL <sup>11</sup>    |

|                    | L   | L    | L    | L   | OPCODE     | MRS           | ILLEGAL <sup>11</sup>    |

|                    | Н   | Х    | Х    | Х   | Х          | DSEL          | Continue burst to end    |

|                    | L   | Н    | Н    | Н   | Х          | NOP           | Continue burst to end    |

|                    | L   | Н    | Н    | L   | Х          | BST           | ILLEGAL                  |

| WRITE              | L   | Н    | L    | Н   | BA, CA, AP | READ/READAP   | ILLEGAL <sup>10</sup>    |

| AUTOPRE-<br>CHARGE | L   | Н    | L    | L   | BA, CA, AP | WRITE/WRITEAP | ILLEGAL <sup>10</sup>    |

| CHARGE             | L   | L    | Н    | Н   | BA, RA     | ACT           | ILLEGAL <sup>4,10</sup>  |

|                    | L   | L    | Н    | L   | BA, AP     | PRE/PALL      | ILLEGAL <sup>4,10</sup>  |

|                    | L   | L    | L    | Н   | Х          | AREF/SREF     | ILLEGAL <sup>11</sup>    |

|                    | L   | L    | L    | L   | OPCODE     | MRS           | ILLEGAL <sup>11</sup>    |

|                    | Н   | Х    | Х    | Х   | Х          | DSEL          | NOP-Enter IDLE after tRP |

|                    | L   | Н    | Н    | Н   | Х          | NOP           | NOP-Enter IDLE after tRP |

|                    | L   | Н    | Н    | L   | X          | BST           | ILLEGAL <sup>4</sup>     |

|                    | L   | Н    | L    | Н   | BA, CA, AP | READ/READAP   | ILLEGAL <sup>4,10</sup>  |

| PRE-<br>CHARGE     | L   | Н    | L    | L   | BA, CA, AP | WRITE/WRITEAP | ILLEGAL <sup>4,10</sup>  |

| S. J. 410L         | L   | L    | Н    | Н   | BA, RA     | ACT           | ILLEGAL <sup>4,10</sup>  |

|                    | L   | L    | Н    | L   | BA, AP     | PRE/PALL      | NOP-Enter IDLE after tRP |

|                    | L   | L    | L    | Н   | Х          | AREF/SREF     | ILLEGAL <sup>11</sup>    |

|                    | L   | L    | L    | L   | OPCODE     | MRS           | ILLEGAL <sup>11</sup>    |

# **OPERATION COMMAND TRUTH TABLE-III**

| Current<br>State   | /CS | /RAS | /CAS | /WE | Address    | Command       | Action                           |

|--------------------|-----|------|------|-----|------------|---------------|----------------------------------|

|                    | Н   | Х    | Х    | Х   | Х          | DSEL          | NOP - Enter ROW ACT after tRCD   |

|                    | L   | Н    | Н    | Н   | Х          | NOP           | NOP - Enter ROW ACT after tRCD   |

|                    | L   | Н    | Н    | L   | Х          | BST           | ILLEGAL <sup>4</sup>             |

|                    | L   | Н    | L    | Н   | BA, CA, AP | READ/READAP   | ILLEGAL <sup>4,10</sup>          |

| ROW<br>ACTIVATING  | L   | Н    | L    | L   | BA, CA, AP | WRITE/WRITEAP | ILLEGAL <sup>4,10</sup>          |

| ACTIVATING         | L   | L    | Н    | Н   | BA, RA     | ACT           | ILLEGAL <sup>4,9,10</sup>        |

|                    | L   | L    | Н    | L   | BA, AP     | PRE/PALL      | ILLEGAL <sup>4,10</sup>          |

|                    | L   | L    | L    | Н   | Х          | AREF/SREF     | ILLEGAL <sup>11</sup>            |

|                    | L   | L    | L    | L   | OPCODE     | MRS           | ILLEGAL <sup>11</sup>            |

|                    | Н   | Х    | X    | X   | Х          | DSEL          | NOP - Enter ROW ACT after tWR    |

|                    | L   | Н    | Н    | Н   | Х          | NOP           | NOP - Enter ROW ACT after tWR    |

|                    | L   | Н    | Н    | L   | Х          | BST           | ILLEGAL <sup>4</sup>             |

|                    | L   | Н    | L    | Н   | BA, CA, AP | READ/READAP   | ILLEGAL                          |

| WRITE              | L   | Н    | L    | L   | BA, CA, AP | WRITE/WRITEAP | ILLEGAL                          |

| RECOVERING         | L   | L    | Н    | Н   | BA, RA     | ACT           | ILLEGAL <sup>4,10</sup>          |

|                    | L   | L    | Н    | L   | BA, AP     | PRE/PALL      | ILLEGAL <sup>4,11</sup>          |

|                    | L   | L    | L    | Н   | Х          | AREF/SREF     | ILLEGAL <sup>11</sup>            |

|                    | L   | L    | L    | L   | OPCODE     | MRS           | ILLEGAL <sup>11</sup>            |

|                    | Н   | Х    | Х    | Х   | Х          | DSEL          | NOP - Enter precharge after tDPL |

|                    | L   | Н    | Н    | Н   | Х          | NOP           | NOP - Enter precharge after tDPL |

|                    | L   | Н    | Н    | L   | Х          | BST           | ILLEGAL <sup>4</sup>             |

| WRITE              | L   | Н    | L    | Н   | BA, CA, AP | READ/READAP   | ILLEGAL <sup>4,8,10</sup>        |

| RECOVERING<br>WITH | L   | Н    | L    | L   | BA, CA, AP | WRITE/WRITEAP | ILLEGAL <sup>4,10</sup>          |

| AUTOPRE-<br>CHARGE | L   | L    | Н    | Н   | BA, RA     | ACT           | ILLEGAL <sup>4,10</sup>          |

|                    | L   | L    | Н    | L   | BA, AP     | PRE/PALL      | ILLEGAL <sup>4,11</sup>          |

|                    | L   | L    | L    | Н   | Х          | AREF/SREF     | ILLEGAL <sup>11</sup>            |

|                    | L   | L    | L    | L   | OPCODE     | MRS           | ILLEGAL <sup>11</sup>            |

|                    | Н   | Х    | Х    | Х   | Х          | DSEL          | NOP - Enter IDLE after tRC       |

|                    | L   | Н    | Н    | Н   | Х          | NOP           | NOP - Enter IDLE after tRC       |

| REFRESHING         | L   | Н    | Н    | L   | Х          | BST           | ILLEGAL <sup>11</sup>            |

|                    | L   | Н    | L    | Н   | BA, CA, AP | READ/READAP   | ILLEGAL <sup>11</sup>            |

### **OPERATION COMMAND TRUTH TABLE-IV**

| Current<br>State | /CS | /RAS | /CAS | /WE | Address    | Command       | Action                      |

|------------------|-----|------|------|-----|------------|---------------|-----------------------------|

|                  | L   | Н    | L    | L   | BA, CA, AP | WRITE/WRITEAP | ILLEGAL <sup>11</sup>       |

|                  | L   | L    | Н    | Н   | BA, RA     | ACT           | ILLEGAL <sup>11</sup>       |

| WRITE            | L   | L    | Н    | L   | BA, AP     | PRE/PALL      | ILLEGAL <sup>11</sup>       |

|                  | L   | L    | L    | Н   | Х          | AREF/SREF     | ILLEGAL <sup>11</sup>       |

|                  | L   | L    | L    | L   | OPCODE     | MRS           | ILLEGAL <sup>11</sup>       |

|                  | Н   | Х    | Х    | Х   | Х          | DSEL          | NOP - Enter IDLE after tMRD |

|                  | L   | Н    | Н    | Н   | Х          | NOP           | NOP - Enter IDLE after tMRD |

|                  | L   | Н    | Н    | L   | Х          | BST           | ILLEGAL <sup>11</sup>       |

| MODE             | L   | Н    | L    | Н   | BA, CA, AP | READ/READAP   | ILLEGAL <sup>11</sup>       |

| REGISTER         | L   | Н    | L    | L   | BA, CA, AP | WRITE/WRITEAP | ILLEGAL <sup>11</sup>       |

| ACCESSING        | L   | L    | Н    | Н   | BA, RA     | ACT           | ILLEGAL <sup>11</sup>       |

|                  | L   | L    | Н    | L   | BA, AP     | PRE/PALL      | ILLEGAL <sup>11</sup>       |

|                  | L   | L    | L    | Н   | Х          | AREF/SREF     | ILLEGAL <sup>11</sup>       |

|                  | L   | L    | L    | L   | OPCODE     | MRS           | ILLEGAL <sup>11</sup>       |

### Note:

- 1. H Logic High Level, L Logic Low Level, X Don't Care, V Valid Data Input, BA - Bank Address, AP - AutoPrecharge Address, CA - Column Address, RA - Row Address, NOP - NO Operation.

- 2. All entries assume that CKE was active(high level) during the preceding clock cycle.

- 3. If both banks are idle and CKE is inactive(low level), then in power down mode.

- 4. Illegal to bank in specified state. Function may be legal in the bank indicated by Bank Address(BA) depending on the state of that bank.

- 5. If both banks are idle and CKE is inactive(low level), then self refresh mode.

- 6. Illegal if tRCD is not met.

- 7. Illegal if tRAS is not met.

- 8. Must satisfy bus contention, bus turn around, and/or write recovery requirements.

- 9. Illegal if tRRD is not met.

- 10. Illegal for single bank, but legal for other banks in multi-bank devices.

- 11. Illegal for all banks.

# **CKE FUNCTION TRUTH TABLE**

| Current<br>State               | CKEn-<br>1 | CKEn | /CS | /RAS | /CAS | /WE | /ADD | Action                                    |

|--------------------------------|------------|------|-----|------|------|-----|------|-------------------------------------------|

|                                | Н          | Х    | Х   | Х    | Х    | Х   | Х    | INVALID                                   |

|                                | L          | Н    | Н   | Х    | Х    | Х   | Х    | Exit self refresh, enter idle after tSREX |

| CELE                           | L          | Н    | L   | Н    | Н    | Н   | Х    | Exit self refresh, enter idle after tSREX |

| SELF<br>REFRESH <sup>1</sup>   | L          | Н    | L   | Н    | Н    | L   | Х    | ILLEGAL                                   |

|                                | L          | Н    | L   | Н    | L    | Х   | Х    | ILLEGAL                                   |

|                                | L          | Н    | L   | L    | Х    | Х   | Х    | ILLEGAL                                   |

|                                | L          | L    | Х   | Х    | Х    | Х   | Х    | NOP, continue self refresh                |

|                                | Н          | Х    | Х   | Х    | Х    | Х   | Х    | INVALID                                   |

|                                | L          | Н    | Н   | Х    | Х    | Х   | Х    | Exit power down, enter idle               |

| DOWED                          | L          | Н    | L   | Н    | Н    | Н   | Х    | Exit power down, enter idle               |

| POWER<br>DOWN <sup>2</sup>     | L          | Н    | L   | Н    | Н    | L   | Х    | ILLEGAL                                   |

| 20                             | L          | Н    | L   | Н    | L    | Х   | Х    | ILLEGAL                                   |

|                                | L          | Н    | L   | L    | Х    | Х   | Х    | ILLEGAL                                   |

|                                | L          | L    | Х   | Х    | Х    | Х   | Х    | NOP, continue power down mode             |

|                                | Н          | Н    | Х   | Х    | Х    | Х   | Х    | See operation command truth table         |

|                                | Н          | L    | L   | L    | L    | Н   | Х    | Enter self refresh                        |

|                                | Н          | L    | Н   | Х    | Х    | Х   | Х    | Exit power down                           |

| ALL DANKS                      | Н          | L    | L   | Н    | Н    | Н   | Х    | Exit power down                           |

| all banks<br>Idle <sup>4</sup> | Н          | L    | L   | Н    | Н    | L   | Х    | ILLEGAL                                   |

|                                | Н          | L    | L   | Н    | L    | Х   | Х    | ILLEGAL                                   |

|                                | Н          | L    | L   | L    | Н    | Х   | Х    | ILLEGAL                                   |

|                                | Н          | L    | L   | L    | L    | L   | Х    | ILLEGAL                                   |

|                                | L          | L    | Х   | Х    | Х    | Х   | Х    | NOP                                       |

| ANIV CTATE                     | Н          | Н    | Х   | Х    | Х    | Х   | Х    | See operation command truth table         |

| ANY STATE<br>OTHER             | Н          | L    | Х   | Х    | Х    | Х   | Х    | ILLEGAL <sup>5</sup>                      |

| THAN<br>ABOVE                  | L          | Н    | Х   | Х    | Х    | Х   | Х    | INVALID                                   |

| ADOVE                          | L          | L    | Х   | Х    | Х    | Х   | Х    | INVALID                                   |

|                                |            |      |     |      |      |     |      | ı                                         |

#### Note:

When CKE=L, all DQ and DQS must be in Hi-Z state.

- 1. CKE and /CS must be kept high for a minimum of 200 stable input clocks before issuing any command.

- 2. All command can be stored after 2 clocks from low to high transition of CKE.

- 3. Illegal if CLK is suspended or stopped during the power down mode.

- 4. Self refresh can be entered only from the all banks idle state.

- 5. Disabling CLK may cause malfunction of any bank which is in active state.

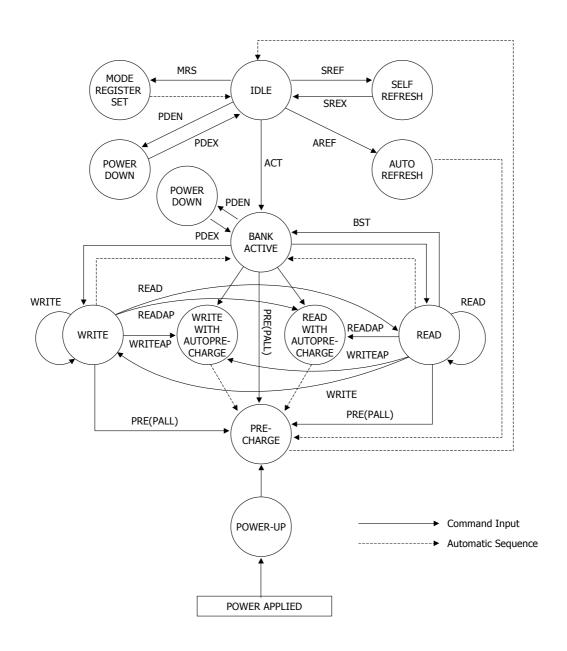

### **SIMPLIFIED STATE DIAGRAM**

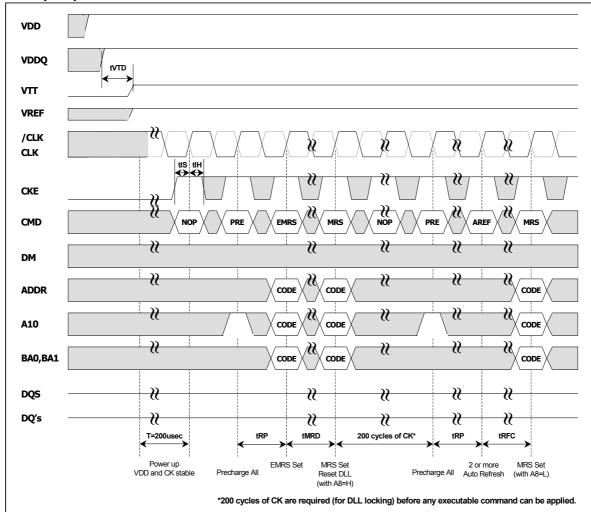

### POWER-UP SEQUENCE AND DEVICE INITIALIZATION

DDR SDRAMs must be powered up and initialized in a predefined manner. Operational procedures other than those specified may result in undefined operation. Except for CKE, inputs are not recognized as valid until after VREF is applied. CKE is an SSTL\_2 input, but will detect an LVCMOS LOW level after VDD is applied. Maintaining an LVCMOS LOW level on CKE during power-up is required to guarantee that the DQ and DQS outputs will be in the High-Z state, where they will remain until driven in normal operation (by a read access). After all power supply and reference voltages are stable, and the clock is stable, the DDR SDRAM requires a 200us delay prior to applying an executable command.

Once the 200us delay has been satisfied, a DESELECT or NOP command should be applied, and CKE should be brought HIGH. Following the NOP command, a PRECHARGE ALL command should be applied. Next a EXTENDED MODE REGISTER SET command should be issued for the Extended Mode Register, to enable the DLL, then a MODE REGISTER SET command should be issued for the Mode Register, to reset the DLL, and to program the operating parameters. 200 clock cycles are required between the DLL reset and any command. During the 200 cycles of CK, for DLL locking, executable commands are disallowed (a DESELECT or NOP command must be applied). After the 200 clock cycles, a PRECHARGE ALL command should be applied, placing the device in the all banks idle state.

Once in the idle state, two AUTO REFRESH cycles must be performed. Additionally, a MODE REGISTER SET command for the Mode Register, with the reset DLL bit deactivated (i.e. to program operating parameters without resetting the DLL) must be performed. Following these cycles, the DDR SDRAM is ready for normal operation.

1. Apply power - VDD, VDDQ, VTT, VREF in the following power up sequencing and attempt to maintain CKE at LVC-MOS low state. (All the other input pins may be undefined.

No power sequencing is specified during power up or power down given the following cirteria:

- VDD and VDDQ are driven from a single power converter output.

- VTT is limited to 1.44V (reflecting VDDQ(max)/2 + 50mV VREF variation + 40mV VTT variation).

- VREF tracks VDDQ/2.

- A minimum resistance of 42 ohms (22 ohm series resistor + 22 ohm parallel resistor 5% tolerance) limits the input current from the VTT supply into any pin.

If the above criteria cannot be met by the system design, then the following sequencing and voltage relationship must be adhered to during power up:

| Voltage description | Sequencing Voltage relationship to avoid latch- |               |  |  |  |

|---------------------|-------------------------------------------------|---------------|--|--|--|

| VDDQ                | After or with VDD                               | < VDD + 0.3V  |  |  |  |

| VTT                 | After or with VDDQ                              | < VDDQ + 0.3V |  |  |  |

| VREF                | After or with VDDQ                              | < VDDQ + 0.3V |  |  |  |

- 2. Start clock and maintain stable clock for a minimum of 200usec.

- 3. After stable power and clock, apply NOP condition and take CKE high.

- Issue Extended Mode Register Set (EMRS) to enable DLL.

- Issue Mode Register Set (MRS) to reset DLL and set device to idle state with bit A8=high. (An additional 200 cycles of clock are required for locking DLL)

- 6. Issue Precharge commands for all banks of the device.

- 7. Issue 2 or more Auto Refresh commands.

- 8. Issue a Mode Register Set command to initialize the mode register with bit A8 = Low.

### **Power-Up Sequence**

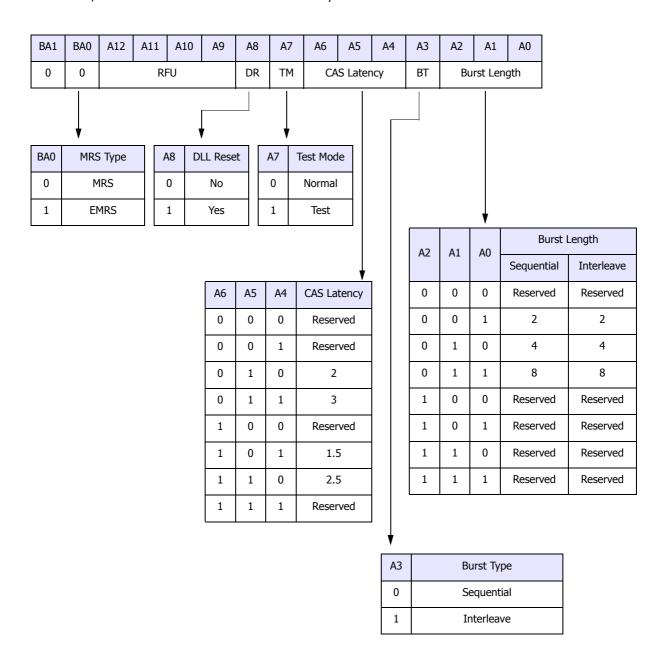

### **MODE REGISTER SET (MRS)**

The mode register is used to store the various operating modes such as /CAS latency, addressing mode, burst length, burst type, test mode, DLL reset. The mode register is programed via MRS command. This command is issued by the low signals of /RAS, /CAS, /CS, /WE and BAO. This command can be issued only when all banks are in idle state and CKE must be high at least one cycle before the Mode Register Set Command can be issued. Two cycles are required to write the data in mode register. During the MRS cycle, any command cannot be issued. Once mode register field is determined, the information will be held until resetted by another MRS command.

#### **BURST DEFINITION**

| Burst Length | Starting Address (A2,A1,A0) | Sequential             | Interleave             |

|--------------|-----------------------------|------------------------|------------------------|

| 2            | XX0                         | 0, 1                   | 0, 1                   |

| 2            | XX1                         | 1, 0                   | 1, 0                   |

|              | X00                         | 0, 1, 2, 3             | 0, 1, 2, 3             |

| 4            | X01                         | 1, 2, 3, 0             | 1, 0, 3, 2             |

| 7            | X10                         | 2, 3, 0, 1             | 2, 3, 0, 1             |

|              | X11                         | 3, 0, 1, 2             | 3, 2, 1, 0             |

|              | 000                         | 0, 1, 2, 3, 4, 5, 6, 7 | 0, 1, 2, 3, 4, 5, 6, 7 |

|              | 001                         | 1, 2, 3, 4, 5, 6, 7, 0 | 1, 0, 3, 2, 5, 4, 7, 6 |

|              | 010                         | 2, 3, 4, 5, 6, 7, 0, 1 | 2, 3, 0, 1, 6, 7, 4, 5 |

| 8            | 011                         | 3, 4, 5, 6, 7, 0, 1, 2 | 3, 2, 1, 0, 7, 6, 5, 4 |

| 0            | 100                         | 4, 5, 6, 7, 0, 1, 2, 3 | 4, 5, 6, 7, 0, 1, 2, 3 |

|              | 101                         | 5, 6, 7, 0, 1, 2, 3, 4 | 5, 4, 7, 6, 1, 0, 3, 2 |

|              | 110                         | 6, 7, 0, 1, 2, 3, 4, 5 | 6, 7, 4, 5, 2, 3, 0, 1 |

|              | 111                         | 0, 1, 2, 3, 4, 5, 6, 7 | 7, 6, 5, 4, 3, 2, 1, 0 |

#### **BURST LENGTH & TYPE**

Read and write accesses to the DDR SDRAM are burst oriented, with the burst length being programmable. The burst length determines the maximum number of column locations that can be accessed for a given Read or Write command. Burst lengths of 2, 4, or 8 locations are available for both the sequential and the interleaved burst types. Reserved states should not be used, as unknown operation or incompatibility with future versions may result.

When a Read or Write command is issued, a block of columns equal to the burst length is effectively selected. All accesses for that burst take place within this block, meaning that the burst wraps within the block if a boundary is reached. The block is uniquely selected by A1-Ai when the burst length is set to two, by A 2 -Ai when the burst length is set to four and by A 3 -Ai when the burst length is set to eight (where Ai is the most significant column address bit for a given configuration). The remaining (least significant) address bit(s) is (are) used to select the starting location within the block. The programmed burst length applies to both Read and Write bursts.

Accesses within a given burst may be programmed to be either sequential or interleaved; this is referred to as the burst type and is selected via bit A3. The ordering of accesses within a burst is determined by the burst length, the burst type and the starting column address, as shown in Burst Definitionon Table

#### **CAS LATENCY**

The Read latency, or CAS latency, is the delay, in clock cycles, between the registration of a Read command and the availability of the first burst of output data. The latency can be programmed 1.5, 2, 2.5 or 3 clocks.

If a Read command is registered at clock edge n, and the latency is m clocks, the data is available nominally coincident with clock edge n + m.

Reserved states should not be used as unknown operation or incompatibility with future versions may result.

#### **DLL RESET**

The DLL must be enabled for normal operation. DLL enable is required during power up initialization, and upon returning to normal operation after having disabled the DLL for the purpose of debug or evaluation. The DLL is automatically disabled when entering self refresh operation and is automatically re-enabled upon exit of self refresh operation. Any time the DLL is enabled, 200 clock cycles must occur to allow time for the internal clock to lock to the externally applied clock before an any command can be issued.

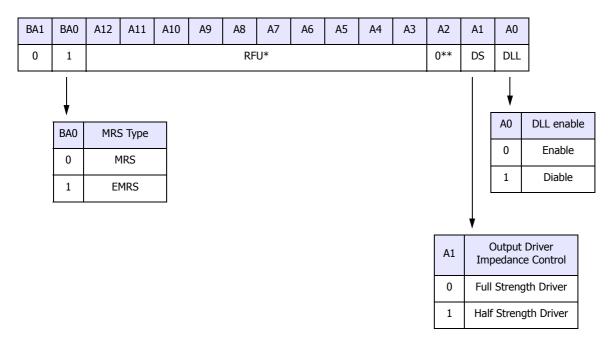

#### **OUTPUT DRIVER IMPEDANCE CONTROL**

The normal drive strength for all outputs is specified to be SSTL\_2, Class II. Hynix also supports a half strength driver option, intended for lighter load and/or point-to-point environments. Selection of the half strength driver option will reduce the output drive strength by 50% of that of the full strength driver. I-V curves for both the full strength driver and the half strength driver are included in this document.

### **EXTENDED MODE REGISTER SET (EMRS)**

The Extended Mode Register controls functions beyond those controlled by the Mode Register; these additional functions include DLL enable/disable, output driver strength selection(optional). These functions are controlled via the bits shown below. The Extended Mode Register is programmed via the Mode Register Set command (BA0=1 and BA1=0) and will retain the stored information until it is programmed again or the device loses power.

The Extended Mode Register must be loaded when all banks are idle and no bursts are in progress, and the controller must wait the specified time before initiating any subsequent operation. Violating either of these requirements will result in unspecified operation.

st All bits in RFU address fields must be programmed to Zero, all other states are reserved for future usage

<sup>\*\*</sup> This part do not support /QFC function, A2 must be programmed to Zero.

### **ABSOLUTE MAXIMUM RATINGS**

| Parameter                          | Symbol    | Rating     | Unit     |

|------------------------------------|-----------|------------|----------|

| Ambient Temperature                | TA        | 0 ~ 70     | °C       |

| Storage Temperature                | TSTG      | -55 ~ 125  | °C       |

| Voltage on Any Pin relative to VSS | VIN, VOUT | -0.5 ~ 3.6 | V        |

| Voltage on VDD relative to VSS     | VDD       | -0.5 ~ 3.6 | V        |

| Voltage on VDDQ relative to VSS    | VDDQ      | -0.5 ~ 3.6 | V        |

| Output Short Circuit Current       | IOS       | 50         | mA       |

| Power Dissipation                  | PD        | 1          | W        |

| Soldering Temperature · Time       | TSOLDER   | 260 · 10   | °C · sec |

Note: Operation at above absolute maximum rating can adversely affect device reliability

### **DC OPERATING CONDITIONS** (TA=0 to 70 °C, Voltage referenced to VSS = 0V)

| Parameter            | Symbol | Min              | Тур.   | Max              | Unit | Note |

|----------------------|--------|------------------|--------|------------------|------|------|

| Power Supply Voltage | VDD    | 2.3              | 2.5    | 2.7              | V    |      |

| Power Supply Voltage | VDDQ   | 2.3              | 2.5    | 2.7              | V    | 1    |

| Input High Voltage   | VIH    | VREF + 0.15      | -      | VDDQ + 0.3       | V    |      |

| Input Low Voltage    | VIL    | -0.3             | -      | VREF - 0.15      | V    | 2    |

| Termination Voltage  | VTT    | VREF - 0.04      | VREF   | VREF + 0.04      | V    |      |

| Reference Voltage    | VREF   | VDDQ/2 -<br>50mV | VDDQ/2 | VDDQ/2 +<br>50mV | V    | 3    |

#### Note:

- 1. VDDQ must not exceed the level of VDD.

- 2. VIL (min) is acceptable -1.5V AC pulse width with  $\leq$  5ns of duration.

- 3. VREF is expected to be equal to 0.5\*VDDQ of the transmitting device, and to track variations in the dc level of the same. Peak to peak noise on VREF may not exceed +/- 2% of the dc value.

### **DC CHARACTERISTICS I** (TA=0 to 70°C, Voltage referenced to VSS = 0V)

| Parameter              | Symbol | Min.       | Max        | Unit | Note          |

|------------------------|--------|------------|------------|------|---------------|

| Input Leakage Current  | ILI    | -2         | 2          | uA   | 1             |

| Output Leakage Current | ILO    | -5         | 5          | uA   | 2             |

| Output High Voltage    | Voh    | VTT + 0.76 | -          | V    | IOH = -15.2mA |

| Output Low Voltage     | VOL    | -          | VTT - 0.76 | V    | IOL = +15.2mA |

Note: 1. VIN=0 to VDD, All other pins are not tested under VIN =0V. 2. DOUT is disabled, VOUT=0 to VDDQ

# **DC CHARACTERISTICS II** (TA=0 to 70 °C, Voltage referenced to Vss = 0V)

# 64Mx4

| Davametev                                  | Cymbal | Took Condition                                                                                                                                        |                                                                                                                       |         |     | Speed       | l   |     | Unit | Noto |

|--------------------------------------------|--------|-------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------|---------|-----|-------------|-----|-----|------|------|

| Parameter                                  | Symbol | Test Condition                                                                                                                                        |                                                                                                                       | -J      | -M  | -К          | -Н  | -L  | Unit | Note |

| Operating Current                          | IDD0   | One bank; Active - Precharge;<br>tRC=tRC(min); tCK=tCK(min); I<br>DQS inputs changing twice per<br>address and control inputs chan<br>per clock cycle | =tCK(min); DQ,DM and ng twice per clock cycle;                                                                        |         | 20  | 1           | 10  | 100 | mA   |      |

| Operating Current                          | IDD1   | One bank; Active - Read - Prech<br>Burst=2; tRC=tRC(min); tCK=t0<br>address and control inputs chan<br>per clock cycle; IOUT=0mA                      | CK(min);                                                                                                              | 120 110 |     | 10          | 100 | mA  |      |      |

| Precharge Power<br>Down Standby<br>Current | IDD2P  | All banks idle; Power down mod<br>tCK=tCK(min)                                                                                                        | e; CKE=Low,                                                                                                           | 10      |     |             |     |     | mA   |      |

| Idle Standby Current                       | IDD2F  | /CS=High, All banks idle; tCK=t<br>CKE=High; address and control<br>changing once per clock cycle.<br>VIN=VREF for DQ, DQS and DM                     | inputs                                                                                                                | 50 45   |     |             | 40  | mA  |      |      |

| Active Power Down<br>Standby Current       | IDD3P  | One bank active; Power down n<br>CKE=Low, tCK=tCK(min)                                                                                                | node ;                                                                                                                |         |     | 15          |     | J   | mA   |      |

| Active Standby<br>Current                  | IDD3N  | Precharge; tRC=tRAS(max); tCl<br>DQ, DM and DQS inputs changii                                                                                        | ock cycle; Address and other control inputs                                                                           |         |     |             | 50  | mA  |      |      |

| Operating Current                          | IDD4R  | Burst=2; Reads; Continuous burst; One bank active; Address and control inputs changing once per clock cycle; tCK=tCK(min); IOUT=0mA                   |                                                                                                                       | 1       | 70  | 1!          | 50  | 140 | mA   |      |

| Operating Current                          | IDD4W  | bank active; Address and contro<br>changing once per clock cycle;                                                                                     | 2; Writes; Continuous burst; One tive; Address and control inputs once per clock cycle; K(min); DQ, DM and DQS inputs |         |     | 1           | 70  | 160 | mA   |      |

| Auto Refresh Current                       | IDD5   | tRC=tRFC(min); All banks active                                                                                                                       | =tRFC(min); All banks active                                                                                          |         |     | 180 170 160 |     |     | mA   |      |

| Self Refresh Current                       | IDD6   | CKE=<0.2V; External clock on;                                                                                                                         |                                                                                                                       |         | 3   |             |     |     | mA   |      |

| Co. Norcon Current                         | 1550   | tCK=tCK(min)                                                                                                                                          | Low Power                                                                                                             |         |     | 1.5         |     |     | mA   |      |

| Operating Current -<br>Four Bank Operation | IDD7   | Four bank interleaving with BL=<br>the following page for detailed t                                                                                  | ,                                                                                                                     | 2       | .70 | 20          | 60  | 250 | mA   |      |

# **DC CHARACTERISTICS II** (TA=0 to 70 °C, Voltage referenced to Vss = 0V)

# 32Mx8

| Barrary at an                              | Complete L | Took Condition                                                                                                                                                       |                                                                                                                                                                                           |       |         | Speed | l   |     | Unit | Nata |

|--------------------------------------------|------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|---------|-------|-----|-----|------|------|

| Parameter                                  | Symbol     | Test Condition                                                                                                                                                       |                                                                                                                                                                                           | -J    | -M      | -K    | -H  | -L  | Unit | Note |

| Operating Current                          | IDD0       | One bank; Active - Precharge;<br>tRC=tRC(min); tCK=tCK(min); I<br>DQS inputs changing twice per<br>address and control inputs char<br>per clock cycle                | clock cycle;                                                                                                                                                                              | 1     | 20      | 1     | 10  | 100 | mA   |      |

| Operating Current                          | IDD1       | One bank; Active - Read - Prech<br>Burst=2; tRC=tRC(min); tCK=to<br>address and control inputs char<br>per clock cycle; IOUT=0mA                                     | CK(min);                                                                                                                                                                                  | 1     | 20      | 1     | 10  | 100 | mA   |      |

| Precharge Power<br>Down Standby<br>Current | IDD2P      | All banks idle; Power down mod<br>tCK=tCK(min)                                                                                                                       | e; CKE=Low,                                                                                                                                                                               |       |         | 10    |     |     | mA   |      |

| Idle Standby Current                       | IDD2F      | /CS=High, All banks idle; tCK=t<br>CKE=High; address and control<br>changing once per clock cycle.<br>VIN=VREF for DQ, DQS and DM                                    | inputs                                                                                                                                                                                    | 50 45 |         |       | 40  | mA  |      |      |

| Active Power Down<br>Standby Current       | IDD3P      | One bank active; Power down n<br>CKE=Low, tCK=tCK(min)                                                                                                               |                                                                                                                                                                                           |       | 15      |       | 1   | mA  |      |      |

| Active Standby<br>Current                  | IDD3N      | Precharge; tRC=tRAS(max); tCl<br>DQ, DM and DQS inputs changi                                                                                                        | S=HIGH; CKE=HIGH; One bank; Active-echarge; tRC=tRAS(max); tCK=tCK(min); Q, DM and DQS inputs changing twice per ock cycle; Address and other control inputs langing once per clock cycle |       |         | 5     | 55  | 50  | mA   |      |

| Operating Current                          | IDD4R      | Burst=2; Reads; Continuous bur<br>active; Address and control inpu<br>once per clock cycle; tCK=tCK(r<br>IOUT=0mA                                                    | uts changing                                                                                                                                                                              |       | 70      | 1     | 50  | 140 | mA   |      |

| Operating Current                          | IDD4W      | Burst=2; Writes; Continuous bu<br>bank active; Address and contro<br>changing once per clock cycle;<br>tCK=tCK(min); DQ, DM and DQ<br>changing twice per clock cycle | ol inputs                                                                                                                                                                                 | 1     | 80      | 1     | 70  | 160 | mA   |      |

| Auto Refresh Current                       | IDD5       | tRC=tRFC(min); All banks active                                                                                                                                      | tive 180 170                                                                                                                                                                              |       | 70      | 160   | mA  |     |      |      |

| Self Refresh Current                       | IDD6       | CKE=<0.2V; External clock on;                                                                                                                                        | Normal                                                                                                                                                                                    |       |         | 3     |     |     | mA   |      |

| Sen Remedia current                        | 1000       | tCK=tCK(min)                                                                                                                                                         | Low Power                                                                                                                                                                                 | 1.5   |         |       | mA  |     |      |      |

| Operating Current -<br>Four Bank Operation | IDD7       | 5                                                                                                                                                                    | our bank interleaving with BL=4, Refer to he following page for detailed test condition                                                                                                   |       | 270 260 |       | 250 | mA  |      |      |

#### **DETAILED TEST CONDITIONS FOR DDR SDRAM IDD1 & IDD7**

#### IDD1: Operating current: One bank operation

- 1. Only one bank is accessed with tRC(min), Burst Mode, Address and Control inputs on NOP edge are changing once per clock cycle. lout = 0mA

- 2. Timing patterns

- DDR200(100Mhz, CL=2): tCK = 10ns, CL2, BL=2, tRCD = 2\*tCK, tRC = 10\*tCK, tRAS = 5\*tCK Read: A0 N R0 N N P0 N A0 N repeat the same timing with random address changing 50% of data changing at every burst

- DDR266B(133Mhz, CL=2.5) : tCK = 7.5ns, CL=2.5, BL=2, tRCD = 3\*tCK, tRC = 9\*tCK, tRAS = 6\*tCK Read : A0 N N R0 N N P0 N N A0 N repeat the same timing with random address changing 50% of data changing at every burst

- DDR266A(133Mhz, CL=2) : tCK = 7.5ns, CL=2, BL=2, tRCD = 3\*tCK, tRC = 9\*tCK, tRAS = 6\*tCK Read : A0 N N R0 N N P0 N N A0 N repeat the same timing with random address changing 50% of data changing at every burst

- DDR266(133Mhz, CL=2): tCK = 7.5ns, CL=2, BL=2, tRCD = 2\*tCK, tRC = 8\*tCK, tRAS = 6\*tCK Read: A0 N R0 N N P0 N A0 N repeat the same timing with random address changing 50% of data changing at every burst

- DDR333(166Mhz, CL=2.5): tCK = 6ns, CL=2, BL=2, tRCD = 3\*tCK, tRC = 10\*tCK, tRAS = 7\*tCK Read: A0 N N R0 N N N P0 N N A0 N repeat the same timing with random address changing 50% of data changing at every burst

Legend: A=Activate, R=Read, W=Write, P=Precharge, N=NOP

### **IDD7**: Operating current: Four bank operation

- 1. Four banks are being interleaved with tRC(min), Burst Mode, Address and Control inputs on NOP edge are not changing. lout = 0mA

- 2. Timing patterns

- DDR200(100Mhz, CL=2): tCK = 10ns, CL2, BL=4, tRRD = 2\*tCK, tRCD= 3\*tCK, Read with autoprecharge Read: A0 N A1 R0 A2 R1 A3 R2 A0 R3 A1 R0 repeat the same timing with random address changing 50% of data changing at every burst

- DDR266B(133Mhz, CL=2.5): tCK = 7.5ns, CL=2.5, BL=4, tRRD = 2\*tCK, tRCD = 3\*tCK, Read with autoprecharge Read: A0 N A1 R0 A2 R1 A3 R2 N R3 A0 N A1 R0 repeat the same timing with random address changing 50% of data changing at every burst

- DDR266A(133Mhz, CL=2): tCK = 7.5ns, CL2=2, BL=4, tRRD = 2\*tCK, tRCD = 3\*tCK, Read with autoprecharge Read: A0 N A1 R0 A2 R1 A3 R2 N R3 A0 N A1 R0 repeat the same timing with random address changing 50% of data changing at every burst

- DDR333(166Mhz, CL=2.5): tCK = 6ns, CL=2.5, BL=4, tRRD = 2\*tCK, tRCD = 3\*tCK, Read with autoprecharge Read: A0 N A1 R0 A2 R1 A3 R2 N R3 A0 N A1 R0 repeat the same timing with random address changing 50% of data changing at every burst

Legend: A=Activate, R=Read, W=Write, P=Precharge, N=NOP

# **AC OPERATING CONDITIONS** (TA=0 to 70 °C, Voltage referenced to Vss = 0V)

| Parameter                                            | Symbol  | Min          | Max          | Unit | Note |

|------------------------------------------------------|---------|--------------|--------------|------|------|

| Input High (Logic 1) Voltage, DQ, DQS and DM signals | VIH(AC) | VREF + 0.31  |              | V    |      |

| Input Low (Logic 0) Voltage, DQ, DQS and DM signals  | VIL(AC) |              | VREF - 0.31  | V    |      |

| Input Differential Voltage, CK and /CK inputs        | VID(AC) | 0.7          | VDDQ + 0.6   | V    | 1    |

| Input Crossing Point Voltage, CK and /CK inputs      | VIX(AC) | 0.5*VDDQ-0.2 | 0.5*VDDQ+0.2 | V    | 2    |

#### Note:

- 1. VID is the magnitude of the difference between the input level on CK and the input on /CK.

- 2. The value of VIX is expected to equal 0.5\*V DDQ of the transmitting device and must track variations in the DC level of the same.

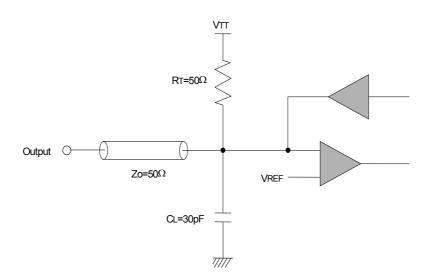

# **AC OPERATING TEST CONDITIONS** (TA=0 to 70°C, Voltage referenced to VSS = 0V)

| Parameter                                                | Value       | Unit |

|----------------------------------------------------------|-------------|------|

| Reference Voltage                                        | VDDQ x 0.5  | V    |

| Termination Voltage                                      | VDDQ x 0.5  | V    |

| AC Input High Level Voltage (VIH, min)                   | VREF + 0.31 | V    |

| AC Input Low Level Voltage (VIL, max)                    | VREF - 0.31 | V    |

| Input Timing Measurement Reference Level Voltage         | VREF        | V    |

| Output Timing Measurement Reference Level Voltage        | Vπ          | V    |

| Input Signal maximum peak swing                          | 1.5         | V    |

| Input minimum Signal Slew Rate                           | 1           | V/ns |

| Termination Resistor (RT)                                | 50          | Ω    |

| Series Resistor (Rs)                                     | 25          | Ω    |

| Output Load Capacitance for Access Time Measurement (CL) | 30          | pF   |

# AC CHARACTERISTICS I (AC operating conditions unless otherwise noted)

| Dawawakaw                                      |            | Compleal | DDR                         | 333  | DDR                         | 266  | 11-14 | Note    |

|------------------------------------------------|------------|----------|-----------------------------|------|-----------------------------|------|-------|---------|

| Parameter                                      |            | Symbol   | Min                         | Max  | Min                         | Max  | Unit  | Note    |

| Row Cycle Time                                 |            | tRC      | 60                          | -    | 60                          | ı    | ns    |         |

| Auto Refresh Row Cycle Time                    |            | tRFC     | 72                          | -    | 75                          | -    | ns    |         |

| Row Active Time                                |            | tRAS     | 42                          | 70K  | 45                          | 120K | ns    |         |

| Active to Read with Auto Precharge             | e Delay    | tRAP     | tRCD or tRPmin              | -    | tRCD or tRPmin              | -    | ns    | 16      |

| Row Address to Column Address Do               | elay       | tRCD     | 18                          | -    | 15                          | -    | ns    |         |

| Row Active to Row Active Delay                 |            | tRRD     | 12                          | -    | 15                          | -    | ns    |         |

| Column Address to Column Address               | s Delay    | tCCD     | 1                           | -    | 1                           | -    | CK    |         |

| Row Precharge Time                             |            | tRP      | 18                          | -    | 15                          | -    | ns    |         |

| rite Recovery Time                             |            | tWR      | 15                          | -    | 15                          | -    | ns    |         |

| Write to Read Command Delay                    |            | tWTR     | 1                           | -    | 1                           | -    | CK    |         |

| Auto Precharge Write Recovery + Precharge Time |            | tDAL     | (tWR/tCK)<br>+<br>(tRP/tCK) | -    | (tWR/tCK)<br>+<br>(tRP/tCK) | -    | CK    | 15      |

| System Clock Cycle Time                        | CL = 2.5   | 101/     | 6                           | 12   | 7.5                         | 12   | ns    |         |

|                                                | CL = 2     | - tCK    | 7.5                         | 12   | 7.5                         | 12   | ns    |         |

| Clock High Level Width                         |            | tCH      | 0.45                        | 0.55 | 0.45                        | 0.55 | CK    |         |

| Clock Low Level Width                          |            | tCL      | 0.45                        | 0.55 | 0.45                        | 0.55 | CK    |         |

| Data-Out edge to Clock edge Skew               |            | tAC      | -0.7                        | 0.7  | -0.75                       | 0.75 | ns    |         |

| DQS-Out edge to Clock edge Skew                |            | tDQSCK   | -0.6                        | 0.6  | -0.75                       | 0.75 | ns    |         |

| DQS-Out edge to Data-Out edge SI               | kew        | tDQSQ    | -                           | 0.4  | -                           | 0.5  | ns    |         |

| Data-Out hold time from DQS                    |            | tQH      | tHP<br>-tQHS                | 1    | tHP<br>-tQHS                | 1    | ns    | 1,10    |

| Clock Half Period                              |            | tHP      | min<br>(tCL,tCH)            | -    | min<br>(tCL,tCH)            | -    | ns    | 1,9     |

| Data Hold Skew Factor                          |            | tQHS     | -                           | 0.6  | -                           | 0.75 | ns    | 10      |

| Valid Data Output Window                       |            | tDV      | tQH-t                       | DQSQ | tQH-t                       | DQSQ | ns    |         |

| Data-out high-impedance window f               | rom CK,/CK | tHZ      | -0.7                        | 0.7  | -0.75                       | 0.75 | ns    | 17      |

| Data-out low-impedance window fr               | om CK, /CK | tLZ      | -0.7                        | 0.7  | -0.75                       | 0.75 | ns    | 17      |

| Input Setup Time (fast slew rate)              |            | tIS      | 0.75                        | -    | 0.9                         | -    | ns    | 2256    |

| Input Hold Time (fast slew rate)               |            | tIH      | 0.75                        | -    | 0.9                         | -    | ns    | 2,3,5,6 |

| Parameter                                | Symbol   | DDR  | R333 | DDF  | R266 | Unit | Note    |

|------------------------------------------|----------|------|------|------|------|------|---------|

| Parameter                                | Syllibol | Min  | Max  | Min  | Max  | Unit | Note    |

| Input Setup Time (slow slew rate)        | tɪs      | 0.8  | -    | 1.0  | -    | ns   | 2,4,5,6 |

| Input Hold Time (slow slew rate)         | tɪH      | 0.8  | -    | 1.0  | -    | ns   | 2,4,3,0 |

| Input Pulse Width                        | tIPW     | 2.2  | -    | 2.2  | -    | ns   | 6       |

| Write DQS High Level Width               | tDQSH    | 0.35 | -    | 0.35 | -    | CK   |         |

| Write DQS Low Level Width                | tDQSL    | 0.35 | -    | 0.35 | -    | CK   |         |

| Clock to First Rising edge of DQS-In     | tDQSS    | 0.75 | 1.25 | 0.72 | 1.28 | CK   |         |

| Data-In Setup Time to DQS-In (DQ & DM)   | tDS      | 0.45 | -    | 0.5  | -    | ns   | 6,7,11, |

| Data-in Hold Time to DQS-In (DQ & DM)    | tDH      | 0.45 | -    | 0.5  | -    | ns   | 12,13   |

| DQ & DM Input Pulse Width                | tDIPW    | 1.75 | -    | 1.75 | -    | ns   |         |

| Read DQS Preamble Time                   | trpre    | 0.9  | 1.1  | 0.9  | 1.1  | CK   |         |

| Read DQS Postamble Time                  | trpst    | 0.4  | 0.6  | 0.4  | 0.6  | CK   |         |

| Write DQS Preamble Setup Time            | twpres   | 0    | -    | 0    | -    | CK   |         |

| Write DQS Preamble Hold Time             | twpreh   | 0.25 | -    | 0.25 | -    | CK   |         |

| Write DQS Postamble Time                 | twpst    | 0.4  | 0.6  | 0.4  | 0.6  | CK   |         |

| Mode Register Set Delay                  | tMRD     | 2    | -    | 2    | -    | CK   |         |

| Exit Self Refresh to Any Execute Command | txsc     | 200  | -    | 200  | -    | CK   | 8       |

| Average Periodic Refresh Interval        | trefi    | -    | 7.8  | -    | 7.8  | us   |         |

# **AC CHARACTERISTICS II** (AC operating conditions unless otherwise noted)

| Davamatan                                         |               | Complete | DDR                         | 266A | DDR                         | 266B | DDR                         | 200  | 1112 | Nata |

|---------------------------------------------------|---------------|----------|-----------------------------|------|-----------------------------|------|-----------------------------|------|------|------|

| Parameter                                         |               | Symbol   | Min                         | Max  | Min                         | Max  | Min                         | Max  | Unit | Note |

| Row Cycle Time                                    |               | tRC      | 65                          | -    | 65                          | -    | 70                          | -    | ns   |      |

| Auto Refresh Row Cycle Tim                        | ne            | tRFC     | 75                          | -    | 75                          | -    | 80                          | -    | ns   |      |

| Row Active Time                                   |               | tRAS     | 45                          | 120K | 45                          | 120K | 50                          | 120K | ns   |      |

| Active to Read with Auto Pr                       | echarge Delay | tRAP     | tRCD or<br>tRPmin           | -    | tRCD or tRPmin              | -    | tRCD or<br>tRPmin           | -    | ns   | 16   |

| Row Address to Column Address Delay               |               | tRCD     | 20                          | -    | 20                          | -    | 20                          | -    | ns   |      |