DATASHEET PMC-1991437

PM8316 TEMUX-84

ISSUE 4

HIGH DENSITY T1/E1 FRAMER WITH INTEGRATED VT/TU MAPPER AND M13 MUX

# **PM8316**

# **TEMUX-84**

# HIGH DENSITY T1/E1 FRAMER WITH INTEGRATED VT/TU MAPPER AND M13 MULTIPLEXER

# DATASHEET

# PROPRIETARY AND CONFIDENTIAL PRELIMINARY ISSUE 4: MAY 2001

DATASHEET PMC-1991437

ISSUE 4

HIGH DENSITY T1/E1 FRAMER WITH INTEGRATED VT/TU MAPPER AND M13 MUX

# **CONTENTS**

| 1 | FEAT  | URES                                 | 1  |

|---|-------|--------------------------------------|----|

| 2 | APPL  | ICATIONS                             | 16 |

| 3 | REFE  | ERENCES                              | 17 |

| 4 | APPL  | ICATION EXAMPLES                     | 21 |

| 5 | BLOC  | CK DIAGRAM                           | 24 |

|   | 5.1   | TOP LEVEL BLOCK DIAGRAM              | 24 |

|   | 5.2   | M13 MULTIPLEXER MODE BLOCK DIAGRAM   | 25 |

|   | 5.3   | VT/TU MAPPER ONLY MODE BLOCK DIAGRAM | 26 |

|   | 5.4   | DS3/E3 FRAMER ONLY BLOCK DIAGRAM     | 27 |

| 6 | DESC  | CRIPTION                             | 28 |

| 7 | PIN C | DIAGRAM                              | 33 |

| 8 | PIN C | DESCRIPTION                          | 34 |

| 9 | FUNC  | CTIONAL DESCRIPTION                  | 72 |

|   | 9.1   | TRANSPARENT VIRTUAL TRIBUTARIES      | 72 |

|   | 9.2   | THE TRIBUTARY INDEXING               | 73 |

|   | 9.3   | T1 FRAMING                           | 75 |

|   | 9.4   | E1 FRAMING                           | 78 |

|   | 9.5   | T1/E1 PERFORMANCE MONITORING         | 84 |

|   | 9.6   | T1/E1 HDLC RECEIVER                  | 85 |

|   | 9.7   | T1/E1 ELASTIC STORE (ELST)           | 86 |

|   | 9.8   | T1/E1 SIGNALING EXTRACTION           | 86 |

|   | 9.9   | T1/E1 RECEIVE PER-CHANNEL CONTROL    | 87 |

DATASHEET PMC-1991437

ISSUE 4

| 9.10 | T1 TRANSMITTER                                                         |

|------|------------------------------------------------------------------------|

| 9.11 | E1 TRANSMITTER                                                         |

| 9.12 | T1/E1 HDLC TRANSMITTERS 89                                             |

| 9.13 | T1/E1 RECEIVE AND TRANSMIT DIGITAL JITTER<br>ATTENUATORS               |

| 9.14 | T1/E1 PSEUDO RANDOM BINARY SEQUENCE GENERATION<br>AND DETECTION (PRBS) |

| 9.15 | DS3 FRAMER (DS3-FRMR) 96                                               |

| 9.16 | DS3 BIT ORIENTED CODE DETECTION                                        |

| 9.17 | DS3/E3 HDLC RECEIVER (RDLC)                                            |

| 9.18 | DS3/E3 PERFORMANCE MONITOR ACCUMULATOR<br>(DS3/E3-PMON)                |

| 9.19 | DS3 TRANSMITTER (DS3-TRAN) 101                                         |

| 9.20 | DS3/E3 HDLC TRANSMITTERS 102                                           |

| 9.21 | DS3 PSEUDO RANDOM PATTERN GENERATION AND<br>DETECTION (PRGD)           |

| 9.22 | M23 MULTIPLEXER (MX23) 104                                             |

| 9.23 | DS2 FRAMER (DS2 FRMR) 105                                              |

| 9.24 | M12 MULTIPLEXER (MX12) 106                                             |

| 9.25 | E3 FRAMER 107                                                          |

| 9.26 | E3 TRANSMITTER 109                                                     |

| 9.27 | E3 TRAIL TRACE BUFFER111                                               |

| 9.28 | TRIBUTARY PAYLOAD PROCESSOR (VTPP)112                                  |

| 9.29 | RECEIVE TRIBUTARY PATH OVERHEAD PROCESSOR<br>(RTOP)114                 |

| 9.30 | RECEIVE TRIBUTARY TRACE BUFFER (RTTB)116                               |

DATASHEET PMC-1991437

ISSUE 4

|    | 9.31 | RECEIVE TRIBUTARY BIT ASYNCHRONOUS DEMAPPER (RTDM)  | . 116 |

|----|------|-----------------------------------------------------|-------|

|    | 9.32 | RECEIVE TRIBUTARY BYTE SYNCHRONOUS DEMAPPER         | .119  |

|    | 9.33 | DS3 MAPPER DROP SIDE (D3MD)                         | 120   |

|    | 9.34 | TRANSMIT TRIBUTARY PATH OVERHEAD PROCESSOR (TTOP)   | 123   |

|    | 9.35 | TRANSMIT REMOTE ALARM PROCESSOR (TRAP)              | 124   |

|    | 9.36 | TRANSMIT TRIBUTARY BIT ASYNCHRONOUS MAPPER (TTMP)   | 125   |

|    | 9.37 | TRANSMIT TRIBUTARY BYTE SYNCHRONOUS MAPPER          | 126   |

|    | 9.38 | DS3 MAPPER ADD SIDE (D3MA)                          | 126   |

|    | 9.39 | EGRESS H-MVIP SYSTEM INTERFACE                      | 128   |

|    | 9.40 | INGRESS SYSTEM H-MVIP INTERFACE                     | 130   |

|    | 9.41 | EXTRACT SCALEABLE BANDWIDTH INTERCONNECT<br>(EXSBI) | 132   |

|    | 9.42 | INSERT SCALEABLE BANDWIDTH INTERCONNECT<br>(INSBI)  | 133   |

|    | 9.43 | FLEXIBLE BANDWIDTH PORTS                            | 134   |

|    | 9.44 | JTAG TEST ACCESS PORT                               | 134   |

|    | 9.45 | MICROPROCESSOR INTERFACE                            | 135   |

| 10 | NORM | AL MODE REGISTER DESCRIPTION                        | 161   |

| 11 | TEST | FEATURES DESCRIPTION                                | 162   |

|    | 11.1 | JTAG TEST PORT                                      | 165   |

| 12 | OPER | ATION                                               | 172   |

|    | 12.1 | TRIBUTARY INDEXING                                  | 172   |

|    | 12.2 | CLOCK AND FRAME SYNCHRONIZATION CONSTRAINTS         | 174   |

DATASHEET PMC-1991437

ISSUE 4

|    | 12.3  | SLC®96 177                                          |

|----|-------|-----------------------------------------------------|

|    | 12.4  | DS3 FRAME FORMAT 179                                |

|    | 12.5  | SERVICING INTERRUPTS 180                            |

|    | 12.6  | USING THE PERFORMANCE MONITORING FEATURES 181       |

|    | 12.7  | USING THE INTERNAL DS3 OR E3 HDLC TRANSMITTER 185   |

|    | 12.8  | USING THE INTERNAL DS3 OR E3 DATA LINK RECEIVER 189 |

|    | 12.9  | USING THE INTERNAL T1/E1 DATA LINK RECEIVER         |

|    | 12.10 | USING THE INTERNAL T1/E1 DATA LINK TRANSMITTER 195  |

|    | 12.11 | USING THE TIME-SLICED T1/E1 TRANSCEIVERS 197        |

|    | 12.12 | T1 AUTOMATIC PERFORMANCE REPORT FORMAT 198          |

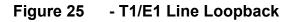

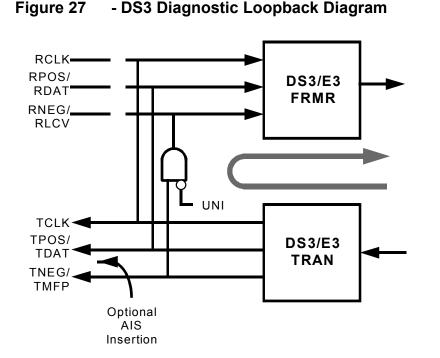

|    | 12.13 | T1/E1 FRAMER LOOPBACK MODES 200                     |

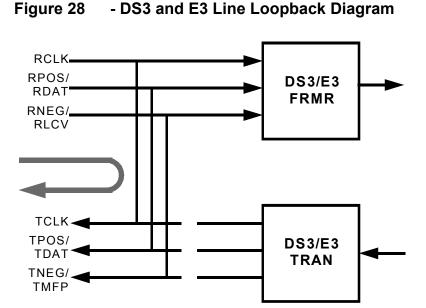

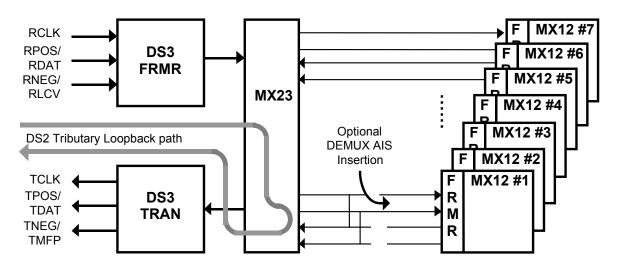

|    | 12.14 | DS3 AND E3 LOOPBACK MODES 202                       |

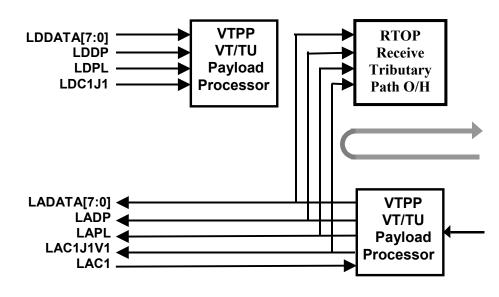

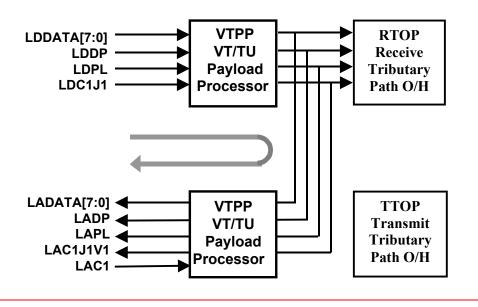

|    | 12.15 | TELECOM BUS MAPPER/DEMAPPER LOOPBACK MODES. 205     |

|    | 12.16 | SBI BUS DATA FORMATS 206                            |

|    | 12.17 | H-MVIP DATA FORMAT 227                              |

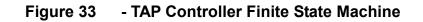

|    | 12.18 | JTAG SUPPORT 233                                    |

| 13 | FUNC  | TIONAL TIMING 241                                   |

|    | 13.1  | DS3 LINE SIDE INTERFACE TIMING 241                  |

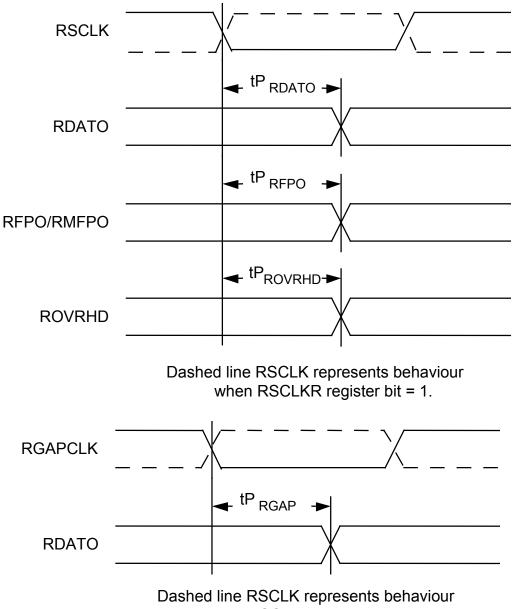

|    | 13.2  | DS3 AND E3 SYSTEM SIDE INTERFACE TIMING 245         |

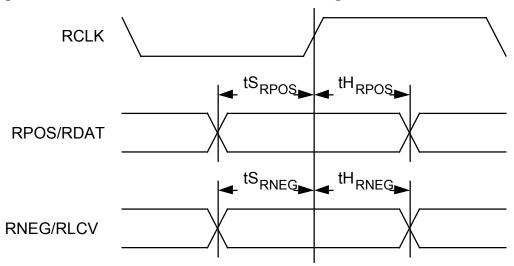

|    | 13.3  | TELECOM DROP BUS INTERFACE TIMING 249               |

|    | 13.4  | TELECOM ADD BUS INTERFACE TIMING 252                |

|    | 13.5  | SONET/SDH SERIAL ALARM PORT TIMING 255              |

|    | 13.6  | SBI DROP BUS INTERFACE TIMING                       |

DATASHEET PMC-1991437

ISSUE 4

HIGH DENSITY T1/E1 FRAMER WITH INTEGRATED VT/TU MAPPER AND M13 MUX

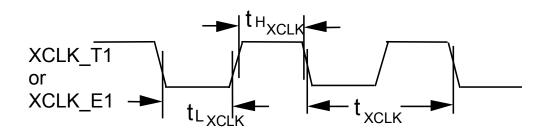

|    | 13.7 | SBI ADD BUS INTERFACE TIMING                | 257 |

|----|------|---------------------------------------------|-----|

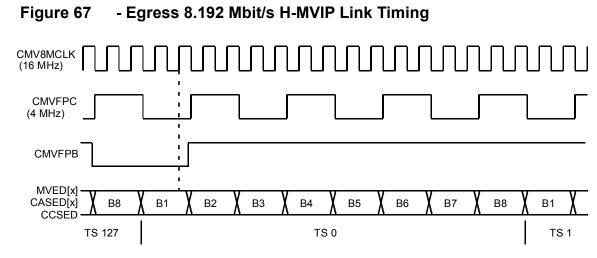

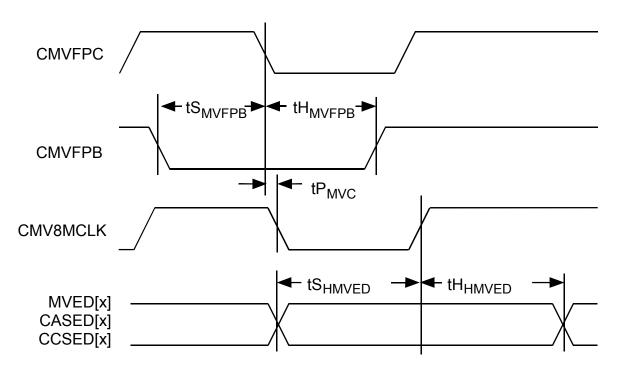

|    | 13.8 | EGRESS H-MVIP LINK TIMING                   | 258 |

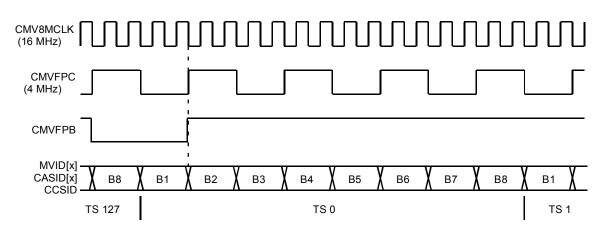

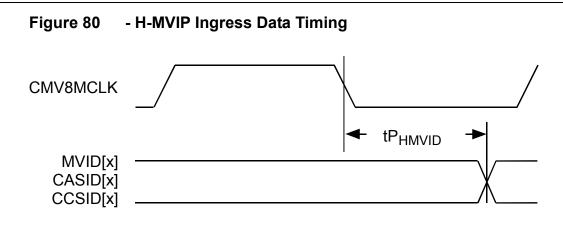

|    | 13.9 | INGRESS H-MVIP LINK TIMING                  | 259 |

| 14 | ABSC | OLUTE MAXIMUM RATINGS                       | 260 |

| 15 | D.C. | CHARACTERISTICS                             | 261 |

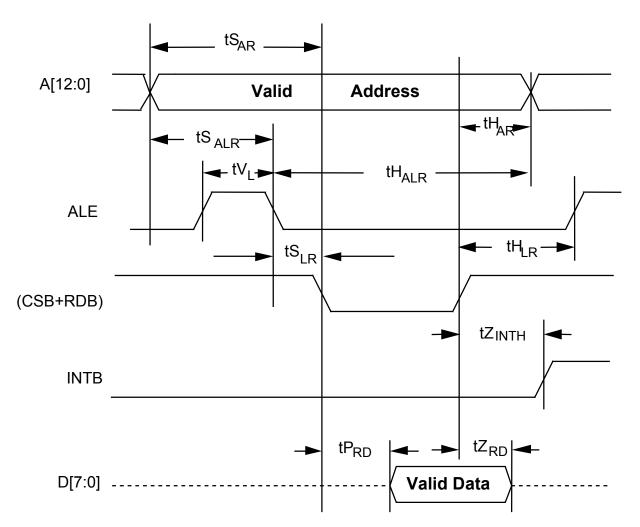

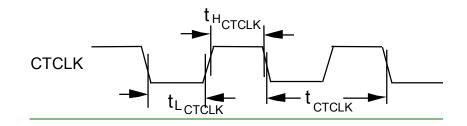

| 16 | MICR | OPROCESSOR INTERFACE TIMING CHARACTERISTICS | 264 |

| 17 | ΤΕΜΙ | JX-84 TIMING CHARACTERISTICS                | 268 |

| 18 | ORDI | ERING AND THERMAL INFORMATION               | 293 |

| 19 | MECI | HANICAL INFORMATION                         | 294 |

# LIST OF FIGURES

| FIGURE 1 - ANY-SERVICE-ANY-PORT APPLICATION      | . 21 |

|--------------------------------------------------|------|

| FIGURE 2 - HIGH DENSITY FRAME RELAY APPLICATION  | . 22 |

| FIGURE 3 - FRACTIONAL DS3 APPLICATION            | . 22 |

| FIGURE 4 - TEMUX-84 BLOCK DIAGRAM                | . 24 |

| FIGURE 5 - M13 MULTIPLEXER BLOCK DIAGRAM         | . 25 |

| FIGURE 6 - VT/TU MAPPER BLOCK DIAGRAM            | . 26 |

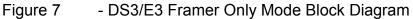

| FIGURE 7 - DS3/E3 FRAMER ONLY MODE BLOCK DIAGRAM | . 27 |

| FIGURE 8 - PIN DIAGRAM                           | . 33 |

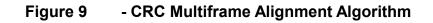

| FIGURE 9 - CRC MULTIFRAME ALIGNMENT ALGORITHM    | . 81 |

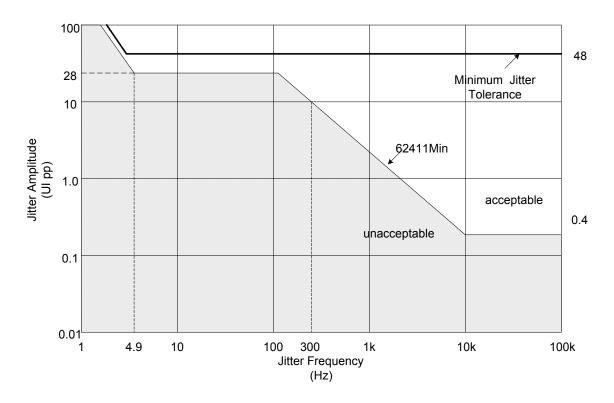

| FIGURE 10- JITTER TOLERANCE T1 MODES             | . 92 |

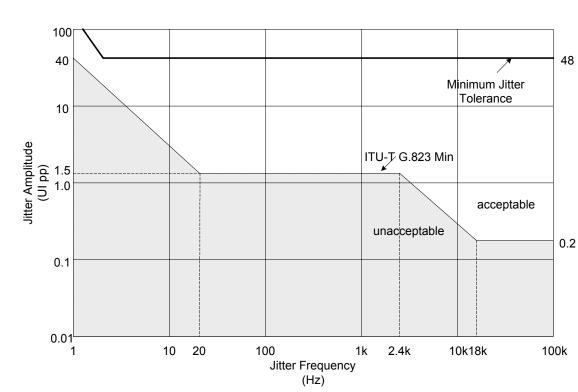

| FIGURE 11 - JITTER TOLERANCE E1 MODES            | . 93 |

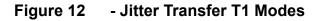

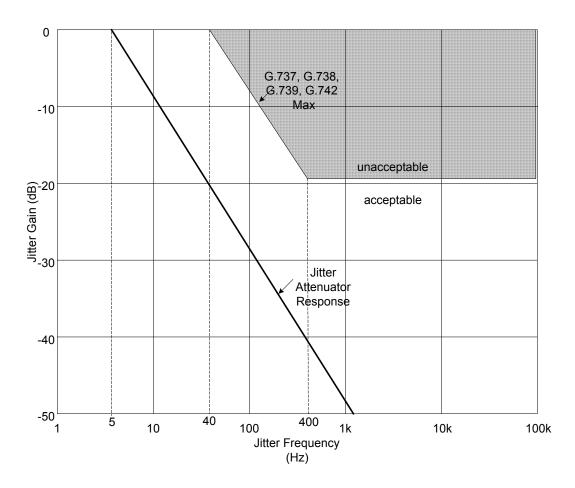

| FIGURE 12- JITTER TRANSFER T1 MODES              | . 94 |

DATASHEET PMC-1991437

ISSUE 4

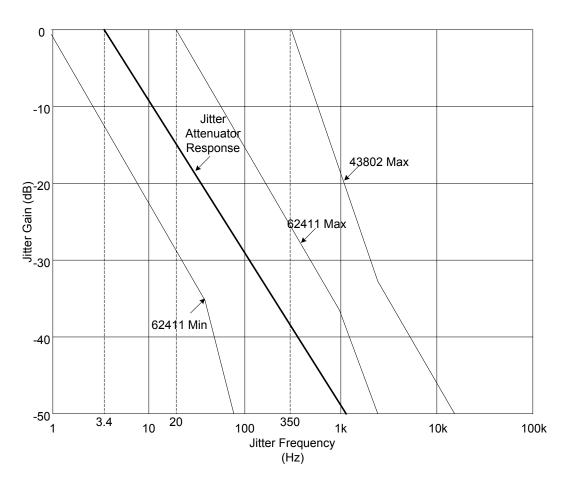

| FIGURE 13-JITTER TRANSFER E1 MODES                       | ; |

|----------------------------------------------------------|---|

| FIGURE 14- EGRESS CLOCK SLAVE: H-MVIP 129                | ) |

| FIGURE 15- INGRESS CLOCK SLAVE: H-MVIP 130               | ) |

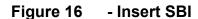

| FIGURE 16 - INSERT SBI 133                               | ; |

| FIGURE 17- DS3 FRAME STRUCTURE 179                       | ) |

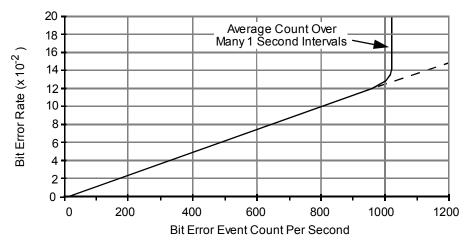

| FIGURE 18- FER COUNT VS. BER (E1 MODE) 182               | ) |

| FIGURE 19- CRCE COUNT VS. BER (E1 MODE) 183              | } |

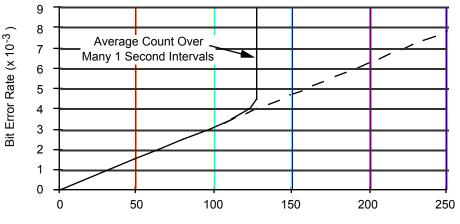

| FIGURE 20- FER COUNT VS. BER (T1 ESF MODE) 184           | ŀ |

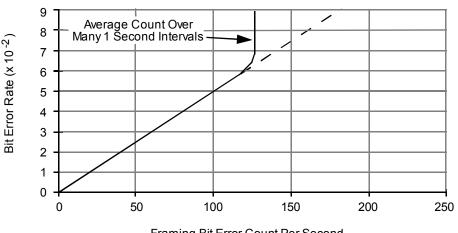

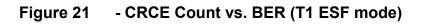

| FIGURE 21- CRCE COUNT VS. BER (T1 ESF MODE) 185          | , |

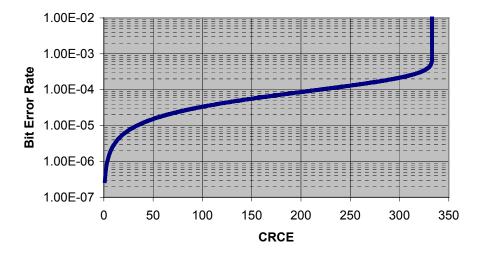

| FIGURE 22- CRCE COUNT VS. BER (T1 SF MODE) 185           | , |

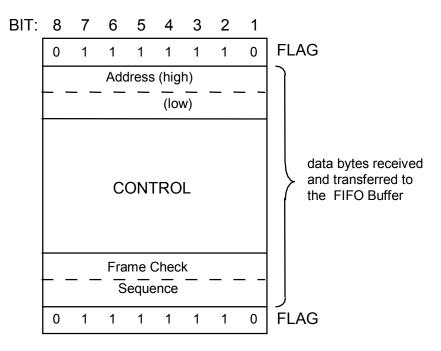

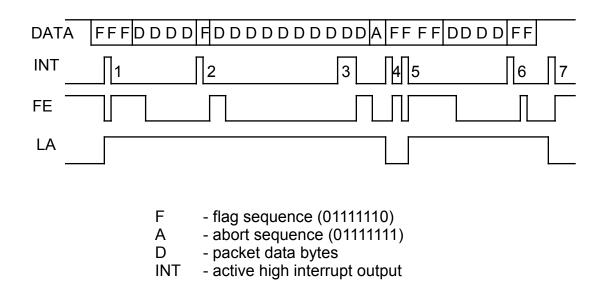

| FIGURE 23- TYPICAL DATA FRAME                            | ) |

| FIGURE 24- EXAMPLE MULTI-PACKET OPERATIONAL SEQUENCE 192 | ) |

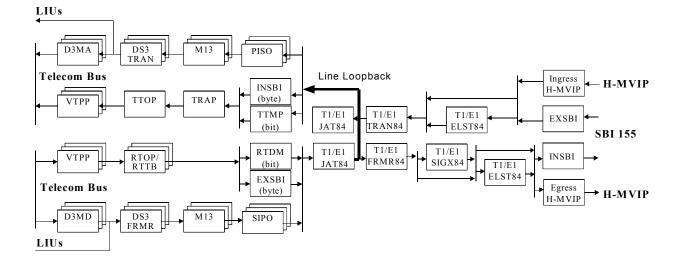

| FIGURE 25- T1/E1 LINE LOOPBACK 201                       |   |

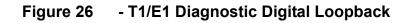

| FIGURE 26-T1/E1 DIAGNOSTIC DIGITAL LOOPBACK              | ) |

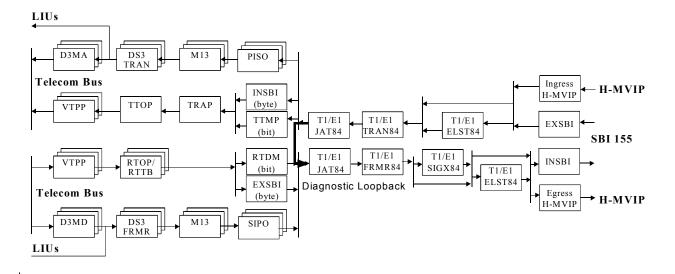

| FIGURE 27 - DS3 DIAGNOSTIC LOOPBACK DIAGRAM              | ; |

| FIGURE 28- DS3 AND E3 LINE LOOPBACK DIAGRAM              | • |

| FIGURE 29- DS2 LOOPBACK DIAGRAM                          | • |

| FIGURE 30- TELECOM DIAGNOSTIC LOOPBACK DIAGRAM           | ; |

| FIGURE 31- TELECOM LINE LOOPBACK DIAGRAM 206             | ) |

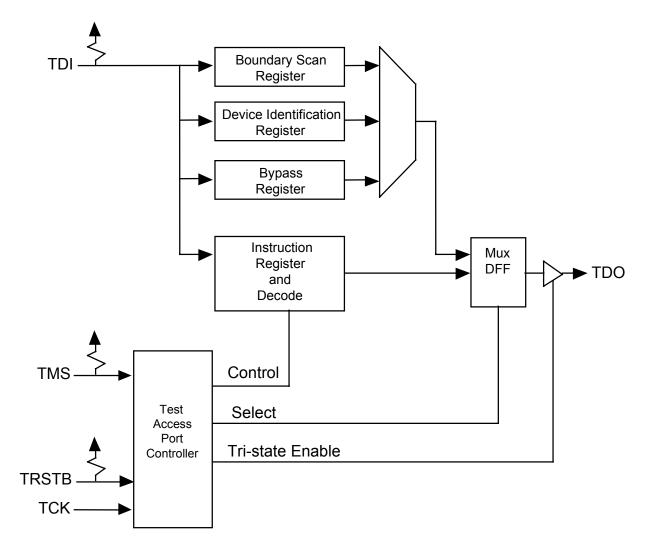

| FIGURE 32- BOUNDARY SCAN ARCHITECTURE                    | • |

| FIGURE 33- TAP CONTROLLER FINITE STATE MACHINE           | , |

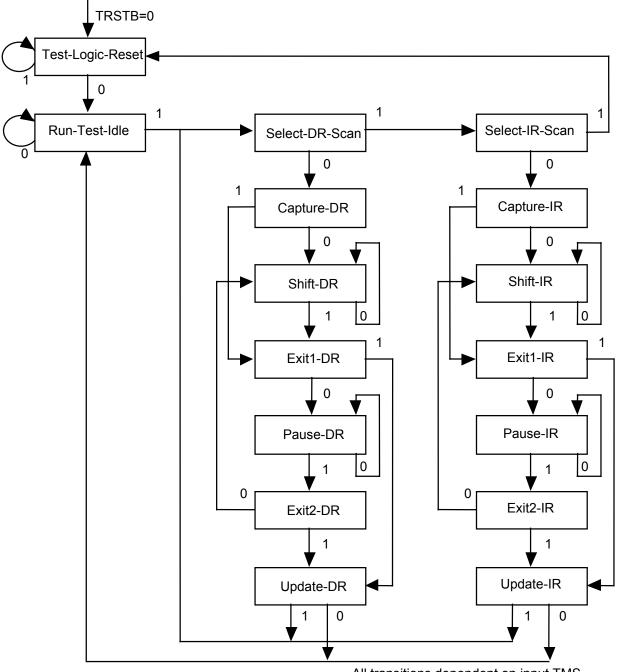

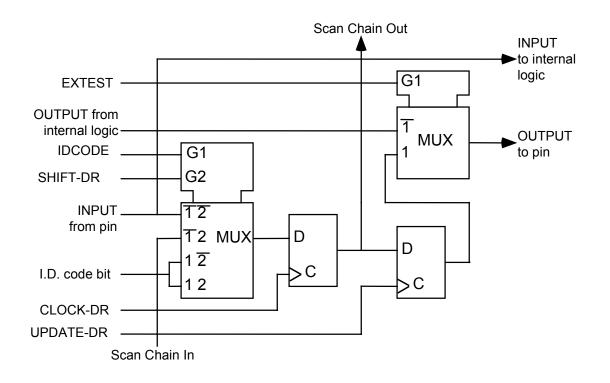

| FIGURE 34- INPUT OBSERVATION CELL (IN_CELL)              | ; |

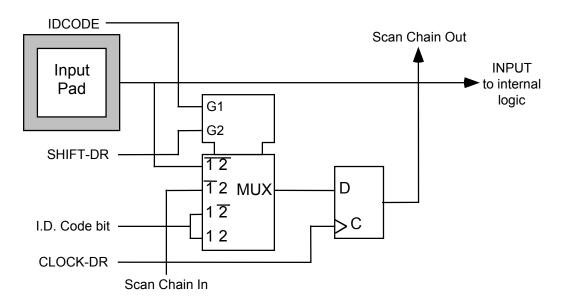

| FIGURE 35- OUTPUT CELL (OUT_CELL)                        | ) |

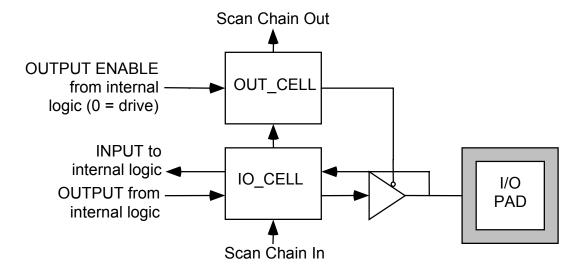

| FIGURE 36- BIDIRECTIONAL CELL (IO_CELL)                  | ) |

PRELIMINARY DATASHEET

PMC-1991437

PM8316 TEMUX-84

ISSUE 4

| FIGURE 37- LAYOUT OF OUTPUT ENABLE AND BIDIRECTIONAL<br>CELLS                                                                                                                                                      |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

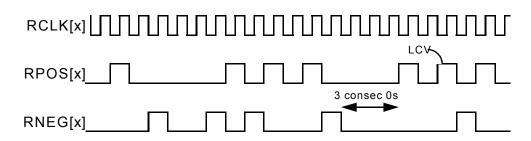

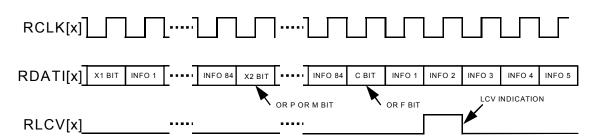

| FIGURE 38- RECEIVE BIPOLAR DS3 STREAM                                                                                                                                                                              |

| FIGURE 39- RECEIVE UNIPOLAR DS3 STREAM 241                                                                                                                                                                         |

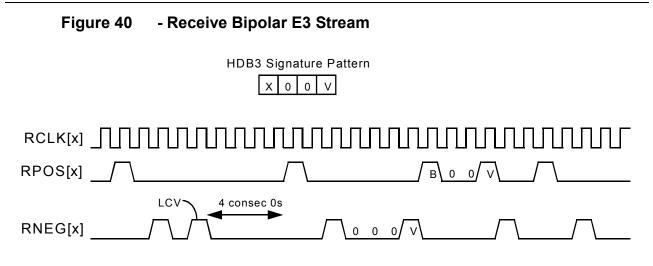

| FIGURE 40- RECEIVE BIPOLAR E3 STREAM 242                                                                                                                                                                           |

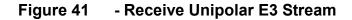

| FIGURE 41- RECEIVE UNIPOLAR E3 STREAM 242                                                                                                                                                                          |

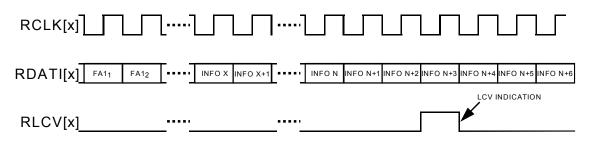

| FIGURE 42- TRANSMIT BIPOLAR DS3 STREAM                                                                                                                                                                             |

| FIGURE 43- TRANSMIT UNIPOLAR DS3 STREAM 243                                                                                                                                                                        |

| FIGURE 44- TRANSMIT BIPOLAR E3 STREAM                                                                                                                                                                              |

| FIGURE 45- TRANSMIT UNIPOLAR E3 STREAM                                                                                                                                                                             |

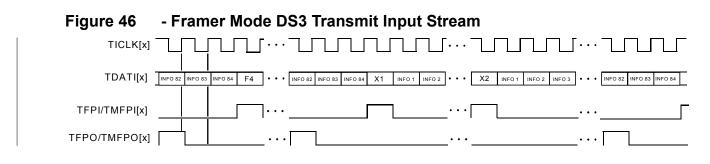

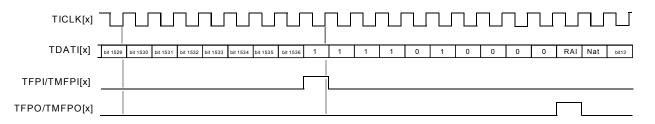

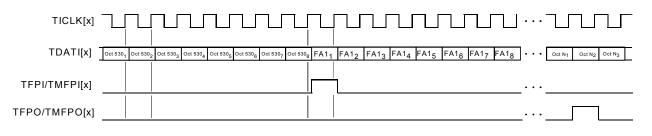

| FIGURE 46- FRAMER MODE DS3 TRANSMIT INPUT STREAM 245                                                                                                                                                               |

| FIGURE 47- FRAMER MODE DS3 TRANSMIT INPUT STREAM WITH<br>TGAPCLK                                                                                                                                                   |

| FIGURE 48- FRAMER MODE DS3 RECEIVE OUTPUT STREAM                                                                                                                                                                   |

|                                                                                                                                                                                                                    |

| FIGURE 49- FRAMER MODE DS3 RECEIVE OUTPUT STREAM WITH<br>RGAPCLK 246                                                                                                                                               |

|                                                                                                                                                                                                                    |

| RGAPCLK                                                                                                                                                                                                            |

| RGAPCLK                                                                                                                                                                                                            |

| RGAPCLK                                                                                                                                                                                                            |

| RGAPCLK                                                                                                                                                                                                            |

| RGAPCLK246FIGURE 50- FRAMER MODE G.751 E3 TRANSMIT INPUT STREAM246FIGURE 51- FRAMER MODE G.751 E3 TRANSMIT INPUT STREAM<br>WITH TGAPCLK247FIGURE 52- FRAMER MODE G.751 E3 RECEIVE OUTPUT STREAM<br>WITH RGAPCLK247 |

PM8316 TEMUX-84

DATASHEET PMC-1991437

ISSUE 4

| FIGURE 57- FRAMER MODE G.832 E3 RECEIVE OUTPUT STREAM<br>WITH RGAPCLK | 9 |

|-----------------------------------------------------------------------|---|

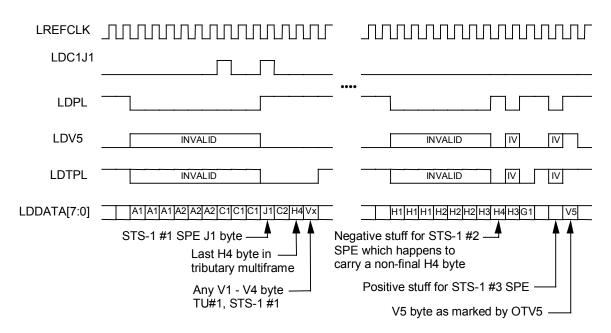

| FIGURE 58- TELECOM DROP BUS TIMING - STS-1 SPES / AU3 VCS 250         | 0 |

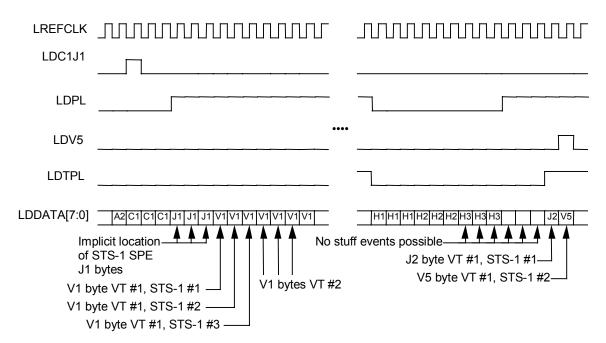

| FIGURE 59- TELECOM DROP BUS TIMING - LOCKED STS-1 SPES /<br>AU3 VCS   | 1 |

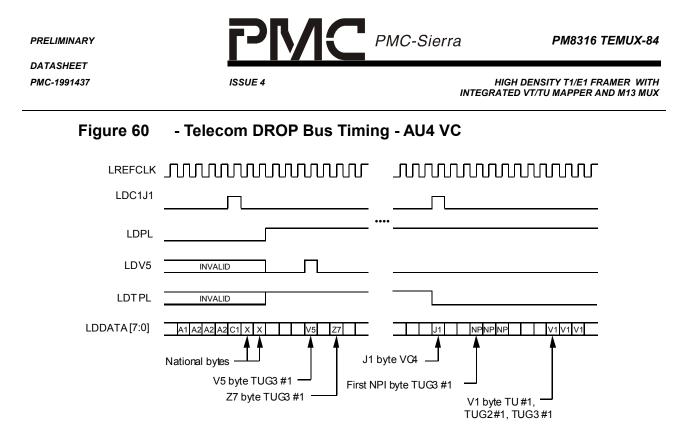

| FIGURE 60- TELECOM DROP BUS TIMING - AU4 VC 252                       | 2 |

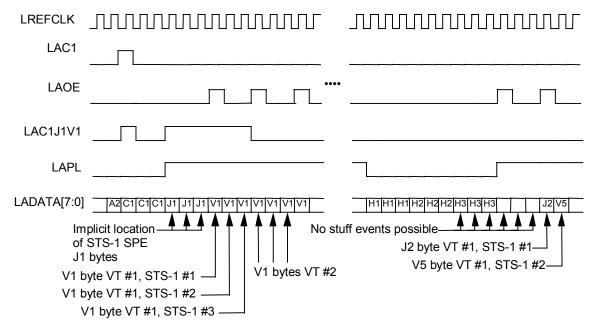

| FIGURE 61- TELECOM ADD BUS TIMING - LOCKED STS-1 SPES /<br>AU3 VCS    | 3 |

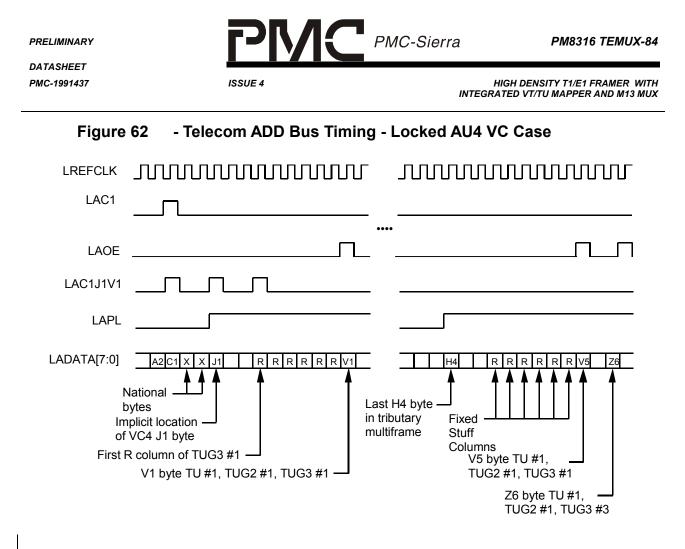

| FIGURE 62- TELECOM ADD BUS TIMING - LOCKED AU4 VC CASE                | 4 |

| FIGURE 63- REMOTE SERIAL ALARM PORT TIMING 256                        | 6 |

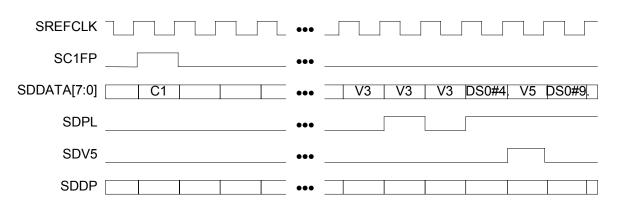

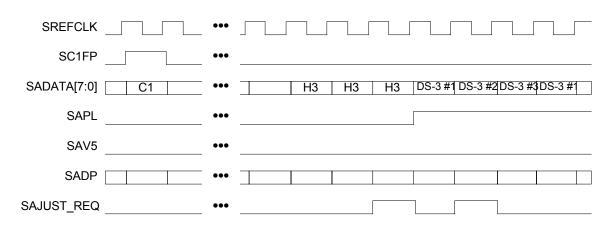

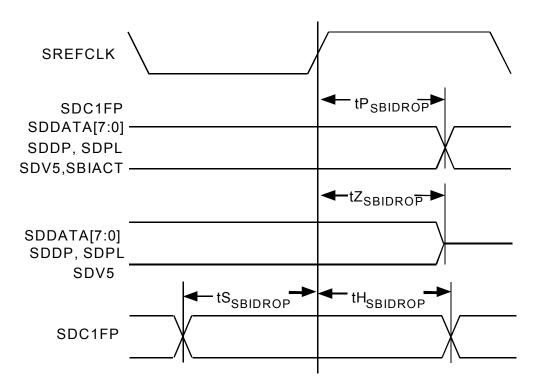

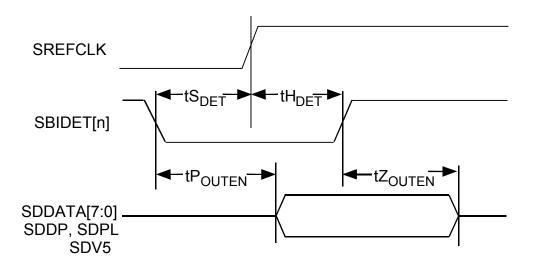

| FIGURE 64- SBI DROP BUS T1/E1 FUNCTIONAL TIMING 256                   | 6 |

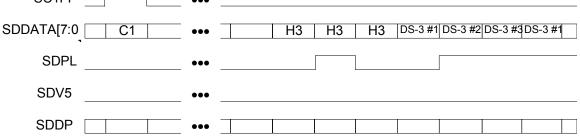

| FIGURE 65- SBI DROP BUS DS3/E3 FUNCTIONAL TIMING 257                  | 7 |

| FIGURE 66- SBI ADD BUS JUSTIFICATION REQUEST FUNCTIONAL<br>TIMING     | 7 |

| FIGURE 67- EGRESS 8.192 MBIT/S H-MVIP LINK TIMING 259                 | 9 |

| FIGURE 68- INGRESS 8.192 MBIT/S H-MVIP LINK TIMING 259                | 9 |

| FIGURE 69- DS3/E3 TRANSMIT INTERFACE TIMING                           | 9 |

| FIGURE 70- DS3/E3 RECEIVE INTERFACE TIMING 272                        | 2 |

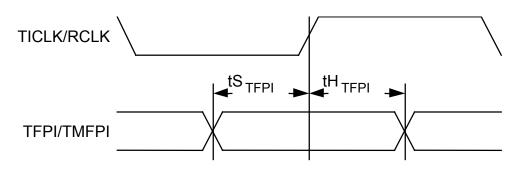

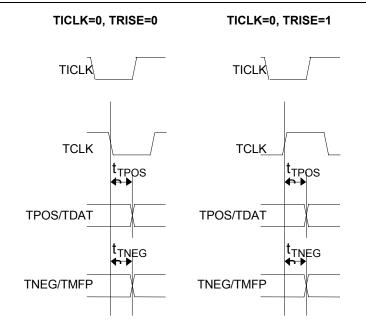

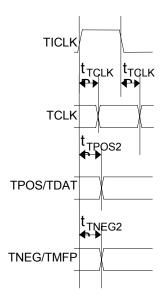

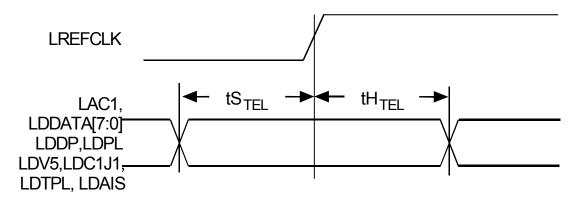

| FIGURE 71- LINE SIDE TELECOM BUS INPUT TIMING 275                     | 5 |

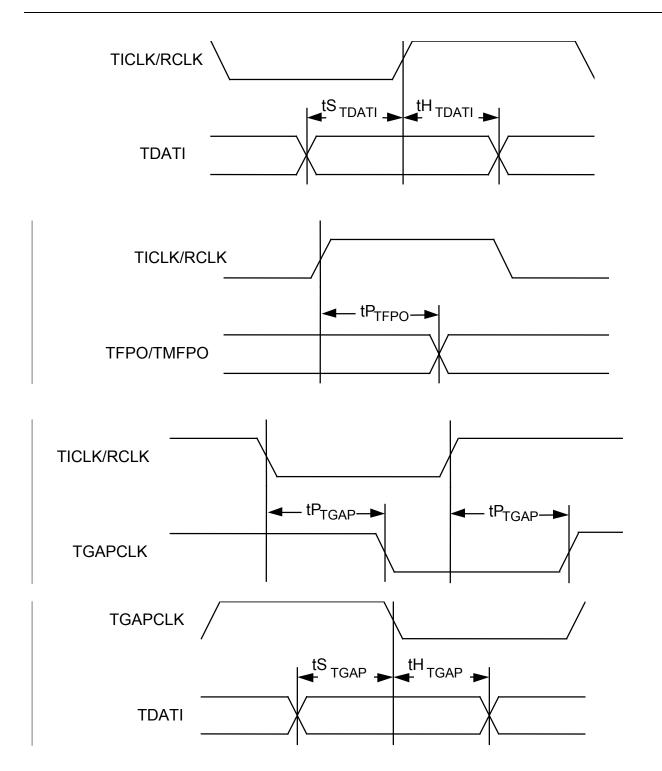

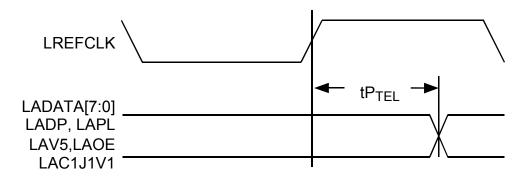

| FIGURE 72- TELECOM BUS OUTPUT TIMING 277                              | 7 |

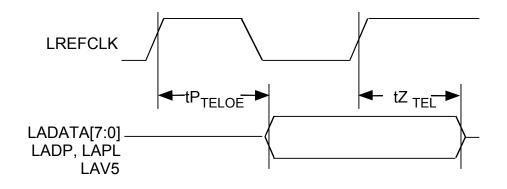

| FIGURE 73- TELECOM BUS TRISTATE OUTPUT TIMING 277                     | 7 |

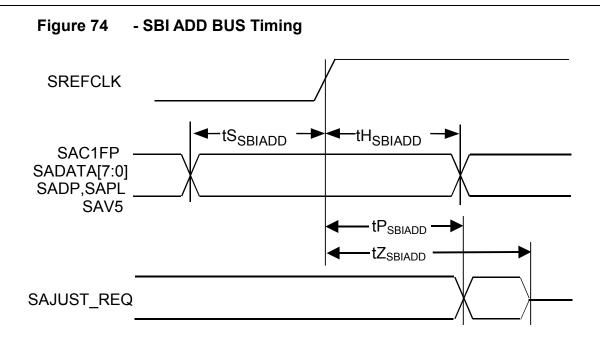

| FIGURE 74- SBI ADD BUS TIMING                                         | 0 |

| FIGURE 75- SBI DROP BUS TIMING 282                                    | 2 |

| FIGURE 76- SBI DROP BUS COLLISION AVOIDANCE TIMING                    | 2 |

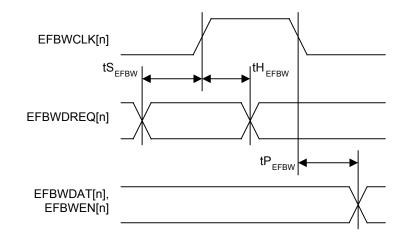

| FIGURE 77- EGRESS FLEXIBLE BANDWIDTH PORT TIMING                      | 3 |

DATASHEET PMC-1991437

ISSUE 4

HIGH DENSITY T1/E1 FRAMER WITH INTEGRATED VT/TU MAPPER AND M13 MUX

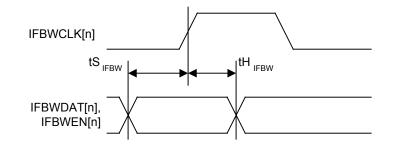

| FIGURE 78- INGRESS FLEXIBLE BANDWIDTH PORT TIMING  | 284 |

|----------------------------------------------------|-----|

| FIGURE 79- H-MVIP EGRESS DATA & FRAME PULSE TIMING | 286 |

| FIGURE 80- H-MVIP INGRESS DATA TIMING              | 287 |

| FIGURE 81- XCLK INPUT TIMING                       | 288 |

| FIGURE 82- TRANSMIT LINE INTERFACE TIMING          | 289 |

| FIGURE 83- REMOTE SERIAL ALARM PORT TIMING         | 290 |

| FIGURE 84- JTAG PORT INTERFACE TIMING              | 292 |

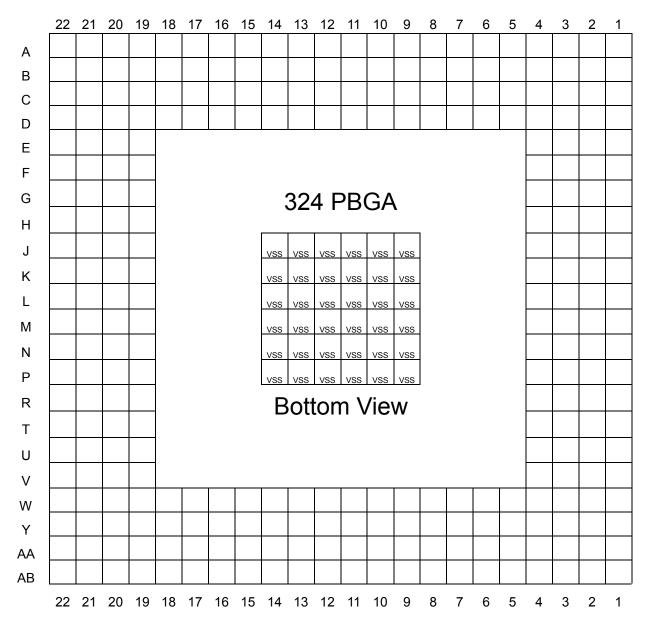

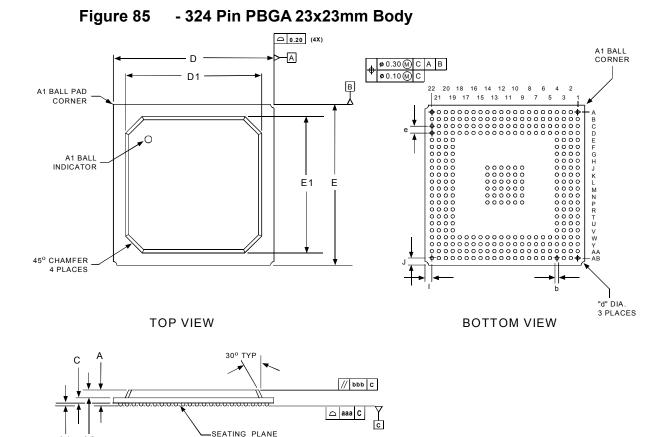

| FIGURE 85- 324 PIN PBGA 23X23MM BODY               | 294 |

# LIST OF TABLES

| TABLE 1  | - E1 FRAMER FRAMING STATES                        | 82  |

|----------|---------------------------------------------------|-----|

| TABLE 2  | - PATH SIGNAL LABEL MISMATCH STATE                | 115 |

| TABLE 3  | - ASYNCHRONOUS T1 TRIBUTARY MAPPING               | 117 |

| TABLE 4  | - ASYNCHRONOUS E1 TRIBUTARY MAPPING               | 118 |

| TABLE 5  | - ASYNCHRONOUS DS3 MAPPING TO STS-1 (STM-0/AU3) 1 | 120 |

| TABLE 6  | - DS3 AIS FORMAT 1                                | 121 |

| TABLE 7  | - DS3 DESYNCHRONIZER CLOCK GAPPING ALGORITHM 1    | 123 |

| TABLE 8  | - DS3 SYNCHRONIZER BIT STUFFING ALGORITHM 1       | 128 |

| TABLE 9  | - REGISTER MEMORY MAP 1                           | 135 |

| TABLE 10 | - INSTRUCTION REGISTER 1                          | 165 |

| TABLE 11 | - IDENTIFICATION REGISTER 1                       | 165 |

| TABLE 12 | - BOUNDARY SCAN REGISTER 1                        | 166 |

| TABLE 13 | - INDEXING FOR 1.544 MBIT/S TRIBUTARIES 1         | 173 |

PRELIMINARY DATASHEET

PMC-1991437

PM8316 TEMUX-84

ISSUE 4

| TABLE 14       - INDEXING FOR 2.048 MBIT/S TRIBUTARIES                               |

|--------------------------------------------------------------------------------------|

| TABLE 15 - 77.76 SBI AND TELECOM BUS ALIGNMENT OPTIONS 175                           |

| TABLE 16- 19.44 MHZ SBI TO 77.76 MHZ TELECOM TO BUS ALIGNMENT<br>OPTIONS176          |

| TABLE 17-77.76 MHZ SBI TO 19.44 MHZ TELECOM TO BUS ALIGNMENT<br>OPTIONS0PTIONS176    |

| TABLE 18 - PMON COUNTER SATURATION LIMITS (E1 MODE) 181                              |

| TABLE 19 - PMON COUNTER SATURATION LIMITS (T1 MODE) 182                              |

| TABLE 20       - PERFORMANCE REPORT MESSAGE STRUCTURE AND         CONTENTS       198 |

| TABLE 21 - PERFORMANCE REPORT MESSAGE STRUCTURE NOTES 199                            |

| TABLE 22 - PERFORMANCE REPORT MESSAGE CONTENTS                                       |

| TABLE 23 - STRUCTURE FOR CARRYING MULTIPLEXED LINKS                                  |

| TABLE 24       - T1/TVT1.5 TRIBUTARY COLUMN NUMBERING                                |

| TABLE 25       - E1/TVT2 TRIBUTARY COLUMN NUMBERING                                  |

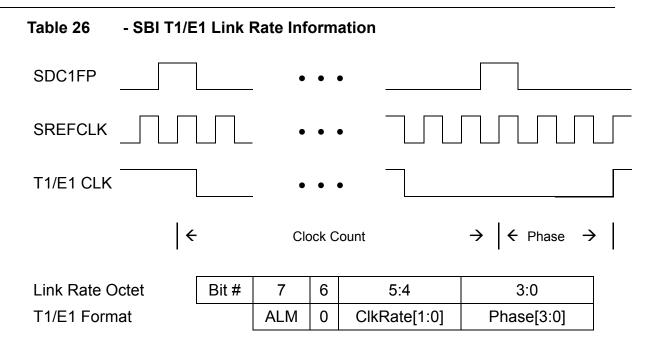

| TABLE 26 - SBI T1/E1 LINK RATE INFORMATION 212                                       |

| TABLE 27 - SBI T1/E1 CLOCK RATE ENCODING                                             |

| TABLE 28 - DS3 LINK RATE INFORMATION                                                 |

| TABLE 29 - DS3 CLOCK RATE ENCODING                                                   |

| TABLE 30 - T1 FRAMING FORMAT 214                                                     |

| TABLE 31 - T1 CHANNEL ASSOCIATED SIGNALING BITS 215                                  |

| TABLE 32    - E1 FRAMING FORMAT    217                                               |

| TABLE 33 - E1 CHANNEL ASSOCIATED SIGNALING BITS 218                                  |

| TABLE 34 - DS3 FRAMING FORMAT 219                                                    |

| TABLE 35    - DS3 BLOCK FORMAT                                                       |

ISSUE 4

| TABLE 36 - DS3 MULTI-FRAME STUFFING FORMAT                                                |

|-------------------------------------------------------------------------------------------|

| TABLE 37 - E3 FRAMING FORMAT    221                                                       |

| TABLE 38    - E3 FRAME STUFFING FORMAT    222                                             |

| TABLE 39 - TRANSPARENT VT1.5/TU11 FORMAT                                                  |

| TABLE 40 - TRANSPARENT VT2/TU12 FORMAT                                                    |

| TABLE 41       - DATA AND CAS T1 H-MVIP FORMAT                                            |

| TABLE 42       - DATA AND CAS E1 H-MVIP FORMAT                                            |

| TABLE 43       - CCS AND TS0 H-MVIP FORMAT                                                |

| TABLE 44 - ABSOLUTE MAXIMUM RATINGS       260                                             |

| TABLE 45    - D.C. CHARACTERISTICS    261                                                 |

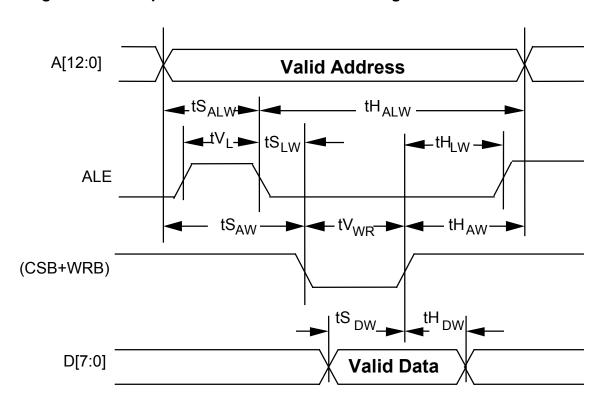

| TABLE 46       - MICROPROCESSOR INTERFACE READ ACCESS       264                           |

| TABLE 47       - MICROPROCESSOR INTERFACE WRITE ACCESS                                    |

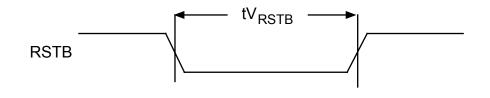

| TABLE 48 - RSTB TIMING                                                                    |

| TABLE 49 - DS3/E3 TRANSMIT INTERFACE TIMING                                               |

| TABLE 50       - DS3/E3 RECEIVE INTERFACE TIMING                                          |

| TABLE 51- LINE SIDE TELECOM BUS INPUT TIMING – 19.44 MHZ (FIGURE<br>74)                   |

| TABLE 52- TELECOM BUS OUTPUT TIMING - 19.44 MHZ (FIGURE 72 AND<br>FIGURE 73)              |

| TABLE 53- TELECOM BUS OUTPUT TIMING – 77.76 MHZ (FIGURE 72 AND<br>FIGURE 73)FIGURE 73)276 |

| TABLE 54 - SBI ADD BUS TIMING – 19.44 MHZ (FIGURE 74) 278                                 |

| TABLE 55 - SBI ADD BUS TIMING – 77.76 MHZ (FIGURE 74) 279                                 |

| TABLE 56 - SBI DROP BUS TIMING - 19.44 MHZ (FIGURE 72 FIGURE 75<br>AND )                  |

DATASHEET PMC-1991437

ISSUE 4

| TABLE 57 - SBI DROP BUS TIMING - 77.76 MHZ (FIGURE 75 TO FIGURE 76)281 |

|------------------------------------------------------------------------|

| TABLE 58 - EGRESS FLEXIBLE BANDWIDTH PORT TIMING (FIGURE 77)283        |

| TABLE 59       - INGRESS FLEXIBLE BANDWIDTH PORT TIMING (FIGURE 78)    |

| TABLE 60 - H-MVIP EGRESS TIMING (FIGURE 79) 285                        |

| TABLE 61 - H-MVIP INGRESS TIMING (FIGURE 80) 286                       |

| TABLE 62 - XCLK INPUT (FIGURE 81)                                      |

| TABLE 63 - TRANSMIT LINE INTERFACE TIMING (FIGURE 82) 289              |

| TABLE 64 - REMOTE SERIAL ALARM PORT TIMING                             |

| TABLE 65 - JTAG PORT INTERFACE    291                                  |

| TABLE 66 - ORDERING INFORMATION                                        |

| TABLE 67 - THERMAL INFORMATION – THETA JA VS. AIRFLOW                  |

DATASHEET PMC-1991437

ISSUE 4

HIGH DENSITY T1/E1 FRAMER WITH INTEGRATED VT/TU MAPPER AND M13 MUX

#### 1 FEATURES

- Integrates 84 T1/E1 framers, three SONET/SDH VT1.5/VT2/TU11/TU12 bit asynchronous or byte synchronous mappers, three full featured M13 multiplexers with DS3 framers, three E3 framers, and three SONET/SDH DS3 mappers in a single monolithic device for terminating DS3 multiplexed T1 streams, SONET/SDH mapped T1 streams or SONET/SDH mapped E1 streams.

- Each SPE/DS3 independently programmable to allow the following modes of operation:

- Eight T1 modes of operation:

- Up to 84 T1 streams mapped as bit asynchronous VT1.5 virtual tributaries into three STS-1 SPEs or TU-11 tributary units into three STM-1/VC3 or TUG3 from a STM-1/VC4.

- Up to 84 T1 streams mapped as byte synchronous VT1.5 virtual tributaries into three STS-1 SPEs or TU-11 tributary units into three STM-1/VC3 or TUG3 from a STM-1/VC4.

- Three STS-1, AU3 or TUG3 Bit Asynchronous VT1.5 or TU-11 Mappers with ingress or egress per tributary link monitoring.

- Up to 84 T1 streams M13 multiplexed into three serial DS3 streams.

- Up to 84 T1 streams M13 multiplexed into three DS3s, the DS3s are asynchronously mapped into three STS-1/STM-0 SPEs.

- DS3 M13 Multiplexer with ingress or egress per link monitoring.

- Up to 84 DS3 multiplexed T1 streams are mapped as bit asynchronous VT1.5 virtual tributaries or TU-11 tributary units, providing a transmultiplexing function between DS3 and SONET/SDH.

- Up to 63 T1 streams mapped as bit asynchronous TU-12 tributary units into three STM-1/VC3 or TUG3 from a STM-1/VC4.

DATASHEET PMC-1991437

ISSUE 4

- Four E1 modes of operation:

- Up to 63 E1 streams mapped as bit asynchronous VT2 virtual tributaries into three STS-1 SPE or TU-12 tributary units into a STM-1/VC3 or TUG3 from a STM-1/VC4.

- Up to 63 E1 streams mapped as byte synchronous VT2 virtual tributaries into three STS-1 SPE or TU-12 tributary units into a STM-1/VC3 or TUG3 from a STM-1/VC4.

- Three STS-1, AU3 or TUG3 Bit Asynchronous VT2 or TU-12 Mappers with ingress or egress per tributary link monitoring.

- Up to 63 E1 streams multiplexed into three DS3s following the ITU-T G.747 recommendation.

- Two unchannelized DS3 modes of operation:

- Standalone unchannelized DS3 framer mode for access to the entire DS3 payload.

- Up to three DS3 streams are mapped bit asynchronously into VC-3s.

- Standalone unchannelized E3 framer mode (ITU-T Rec. G.751 or G.832) for access to the entire E3 payload.

- Up to 84 VT1.5/TU11 or 63 VT2/TU12 tributaries can be passed between the line SONET/SDH bus and the SBI bus as transparent virtual tributaries with pointer processing.

- Supports 8 Mbit/s H-MVIP on the system interface for all T1 or E1 links, a separate 8 Mbit/s H-MVIP system interface for all T1 or E1 CAS channels and a separate 8 Mbit/s H-MVIP system interface for all T1 or E1 CCS and V5.1/V5.2 channels.

- Supports a byte serial Scaleable Bandwidth Interconnect (SBI) bus interface for high density system side device interconnection of up to 84 T1 streams, 63 E1 streams, 3 DS3 streams or 3 E3 streams. This interface also supports transparent virtual tributaries when used with the SONET/SDH mapper.

- Supports insertion and extraction of arbitrary rate (eg. fractional DS3) data streams to and from the SBI bus interface.

- Provides jitter attenuation in the T1 or E1 receive and transmit directions.

DATASHEET PMC-1991437

HIGH DENSITY T1/E1 FRAMER WITH INTEGRATED VT/TU MAPPER AND M13 MUX

- Provides three independent de-jittered T1 or E1 recovered clocks for system timing and redundancy.

- Provides per link diagnostic and line loopbacks.

**ISSUE 4**

- Provides an on-board programmable binary sequence generator and detector for error testing at DS3 and E3 rates. Includes support for patterns recommended in ITU-T 0.151.

- Also provides PRBS generators and detectors on each tributary for error testing at DS1, E1 and NxDS0 rates as recommended in ITU-T 0.151 and 0.152.

- Supports the M23 and C-bit parity DS3 formats.

- When configured to operate as a DS3 or E3 Framer, gapped transmit and receive clocks can be optionally generated for interface to link layer devices which only need access to payload data bits.

- DS3 or E3 Transmit clock source can be selected from either an external oscillator or from the receive side clock (loop-timed).

- Provides a SONET/SDH Add/Drop bus interface with integrated VT1.5, TU-11, VT2 and TU-12 mapper for T1and E1 streams. Also provides a DS3 mapper.

- Provides a generic 8-bit microprocessor bus interface for configuration, control and status monitoring. Provides a standard 5 signal P1149.1 JTAG test port for boundary scan board test purposes.

- Low power 1.8V/3.3V CMOS technology. All pins are 5V tolerant.

- 324-pin fine pitch PBGA package (23mm x 23mm). Supports industrial temperature range (-40°C to 85°C) operation.

# Each one of 84 T1 receiver sections:

- Frames to DS-1 signals in SF, SLC®96 and ESF formats.

- Frames to TTC JT-G.704 multiframe formatted J1 signals. Supports the alternate CRC-6 calculation for Japanese applications.

- Provides Red, Yellow, and AIS alarm integration.

- Supports RAI-CI and AIS-CI alarm detection and generation.

PM8316 TEMUX-84

DATASHEET PMC-1991437

ISSUE 4

- Provides ESF bit-oriented code detection and an HDLC/LAPD interface for terminating the ESF facility data link.

- Provides Inband Loopback Code generation and detection.

- Indicates signaling state change, and two superframes of signaling debounce on a per-DS0 basis.

- Provides an HDLC interface with 128 bytes of buffering for terminating the facility data link.

- Provides performance monitoring counters sufficiently large as to allow performance monitor counter polling at a minimum rate of once per second. Optionally, updates the performance monitoring counters and interrupts the microprocessor once per second, timed to the receive line.

- Provides an optional elastic store which may be used to time the ingress streams to a common clock and frame alignment in support of a H-MVIP interface.

- Provides DS-1 robbed bit signaling extraction and insertion, with optional data inversion, programmable idle code substitution, digital milliwatt code substitution, bit fixing, and two superframes of signaling debounce on a per-channel basis.

- A pseudo-random sequence user selectable from 2<sup>7</sup> –1, 2<sup>11</sup> –1, 2<sup>15</sup> –1 or 2<sup>20</sup> –1, may be detected in the T1 stream in either the ingress or egress directions. The detector counts pattern errors using a 16-bit non-saturating PRBS error counter. The pseudo-random sequence can be the entire T1 or any combination of DS0s within a framed T1.

- Line side interface is either from the DS3 interface via the M13 multiplex or from the SONET/SDH Drop bus via the VT1.5, TU-11, VT2 or TU-12 demapper.

- System side interface is either H-MVIP or SBI bus.

- Frames in the presence of and detects the "Japanese Yellow" alarm.

- Supports the alternate CRC-6 calculation for Japanese applications.

- Provides external access for up to three de-jittered recovered T1 clocks.

DATASHEET PMC-1991437

HIGH DENSITY T1/E1 FRAMER WITH INTEGRATED VT/TU MAPPER AND M13 MUX

#### Each one of 63 E1 receiver sections:

**ISSUE 4**

- Frames to ITU-T G.704 basic and CRC-4 multiframe formatted E1 signals. The framing procedures are consistent ITU-T G.706 specifications.

- Provides an HDLC interface with 128 bytes of buffering for terminating the national use bit data link.

- Extracts 4-bit codewords from the E1 national use bits as specified in ETS 300 233.

- V5.2 link indication signal detection.

- Provides performance monitoring counters sufficiently large as to allow performance monitor counter polling at a minimum rate of once per second. Optionally, updates the performance monitoring counters and interrupts the microprocessor once per second, timed to the receive line.

- Provides a two-frame elastic store buffer for backplane rate adaptation that performs controlled slips and indicates slip occurrence and direction.

- Frames to the E1 signaling multiframe alignment when enabled and extracts channel associated signaling. Alternatively, a common channel signaling data link may be extracted from timeslot 16.

- Can be programmed to generate an interrupt on change of signaling state.

- Provides trunk conditioning which forces programmable trouble code substitution and signaling conditioning on all channels or on selected channels.

- A pseudo-random sequence user selectable from 2<sup>7</sup> –1, 2<sup>11</sup> –1, 2<sup>15</sup> –1 or 2<sup>20</sup> –1, may be detected in the E1 stream in either the ingress or egress directions. The detector counts pattern errors using a 16-bit non-saturating PRBS error counter. The pseudo-random sequence can be the entire E1 or any combination of timeslots within the framed E1.

- Line side interface is from the SONET/SDH Drop bus via the VT2 or TU-12 demapper.

- System side interface is either H-MVIP or SBI bus.

- Provides external access for up to three de-jittered recovered E1 clocks.

DATASHEET PMC-1991437

HIGH DENSITY T1/E1 FRAMER WITH INTEGRATED VT/TU MAPPER AND M13 MUX

#### Each one of 84 T1 transmitter sections:

**ISSUE 4**

- May be timed to its associated receive clock (loop timing) or may derive its timing from a common egress clock or a common transmit clock; the transmit line clock may be synthesized from an N\*8 kHz reference.

- Provides minimum ones density through Bell (bit 7), GTE or "jammed bit 8" zero code suppression on a per-DS0 basis. Provides a 128 byte buffer to allow insertion of the facility data link using the host interface.

- Supports transmission of the alarm indication signal (AIS) or the Yellow alarm signal in SF, SLC®96 and ESF formats.

- Provides transparency for the F-bit to support SLC®96 data link insertion.

- Autonomously transmits an ESF Performance Report Message each second.

- Provides a digital phase locked loop for generation of a low jitter transmit clock.

- Provides a FIFO buffer for jitter attenuation and rate conversion in the transmitter.

- Supports the alternate ESF CRC-6 calculation for Japanese applications.

- A pseudo-random sequence user selectable from 2<sup>7</sup> –1, 2<sup>11</sup> –1, 2<sup>15</sup> –1 or 2<sup>20</sup> –1, may be inserted into the T1 stream in either the ingress or egress directions. The pseudo-random sequence can be inserted into the entire T1 or any combination of DS0s within the framed T1.

- Line side interface is through either DS3 Interface via the M13 multiplex or the SONET/SDH Add bus via the VT1.5, TU-11, VT2 or TU-12 mapper.

- System side interface is either H-MVIP or SBI bus.

#### Each one of 63 E1 transmitter sections:

- Provides a FIFO buffer for jitter attenuation and rate conversion in the transmit path.

- Transmits G.704 basic and CRC-4 multiframe formatted E1.

- Supports unframed mode and framing bit, CRC, or data link by-pass.

- Provides signaling insertion, programmable idle code substitution, digital milliwatt code substitution, and data inversion on a per channel basis.

DATASHEET PMC-1991437

**ISSUE 4**

PM8316 TEMUX-84

HIGH DENSITY T1/E1 FRAMER WITH INTEGRATED VT/TU MAPPER AND M13 MUX

- Provides trunk conditioning which forces programmable trouble code substitution and signaling conditioning on all channels or on selected channels.

- Provides a digital phase locked loop for generation of a low jitter transmit clock.

- A pseudo-random sequence user selectable from 2<sup>7</sup> –1, 2<sup>11</sup> –1, 2<sup>15</sup> –1 or 2<sup>20</sup> –1, may be inserted into the E1 stream in either the ingress or egress directions. The pseudo-random sequence can be inserted into the entire E1 or any combination of timeslots within the framed E1.

- Optionally inserts a datalink in the E1 national use bits.

- Supports 4-bit codeword insertion in the E1 national use bits as specified in ETS 300 233

- Supports transmission of the alarm indication signal (AIS) and the remote alarm indication (RAI) signal.

- Line side interface is through the SONET/SDH Add bus via the VT2 or TU-12 mapper.

- System side interface is either H-MVIP or SBI bus.

# Six full featured T1/E1 Pattern Generators and Detectors:

- Each generator and detector pair may be associated with any one of the 84 T1s or 63 E1s.

- Any sub-set of DS0s within a tributary may be selected.

- Provides programmable pseudo-random test sequence generation (up to 2<sup>32</sup>-1 bit length sequences conforming to ITU-T O.151 standards) or any repeating pattern up to 32 bits. Diagnostic abilities include single bit error insertion or error insertion at bit error rates ranging from 10<sup>-1</sup> to 10<sup>-7</sup>.

# Each one of three SONET/SDH Tributary Path Processing Sections:

- Interfaces with a byte wide Telecom Add/Drop bus, interfacing directly with the PM5362 TUPP-PLUS and PM5342 SPECTRA-155 at 19.44 MHz.

- Seamlessly interfaces with a 77.76 MHz Drop bus. Interfaces to a 77.76 MHz Add bus with minimal external logic.

DATASHEET PMC-1991437

**ISSUE 4**

PM8316 TEMUX-84

- Compensates for pleisiochronous relationships between incoming and outgoing higher level (STS-1, AU4, AU3) synchronous payload envelope frame rates through processing of the lower level tributary pointers.

- Optionally frames to the H4 byte in the path overhead to determine tributary multi-frame boundaries and generates change of loss-of-frame status interrupts.

- Detects loss of pointer (LOP) and re-acquisition for each tributary and optionally generates interrupts.

- Detects tributary path alarm indication signal (AIS) and return to normal state for each tributary and optionally generates interrupts

- Detects tributary elastic store underflow and overflow and optionally generates interrupts.

- Provides individual tributary path signal label register that hold the expected label and detects tributary path signal label mismatch alarms (PSLM) and return to matched state for each tributary and optionally generates interrupts.

- Detects tributary path signal label unstable alarms (PSLU) and return to stable state for each tributary and optionally generates interrupts.

- Detects assertion and removal of tributary extended remote defect indications (RDI) for each tributary and optionally generates interrupts.

- Calculates and compares the tributary path BIP-2 error detection code for each tributary and configurable to accumulate the BIP-2 errors on block or bit basis in internal registers.

- Allows insertion of all-zeros or all-ones tributary idle code with unequipped indication and valid pointer into any tributary under software control.

- Allows software to force the AIS insertion on a per tributary basis.

- Inserts valid H4 byte and all-zeros fixed stuff bytes. Remaining path overhead bytes (J1, B3, C2,G1, F2, Z3, Z4, Z5) are set to all-zeros.

- Inserts valid pointers and all-zeros transport overhead bytes on the outgoing Telecom Add bus, with valid control signals.

- Support in-band error reporting by updating the FEBE, RDI and auxiliary RDI bits in the V5 byte with the status of the incoming stream and remote alarm pins.

DATASHEET PMC-1991437

ISSUE 4

HIGH DENSITY T1/E1 FRAMER WITH INTEGRATED VT/TU MAPPER AND M13 MUX

Calculates and inserts the tributary path BIP-2 error detection code for each tributary.

### Each one of three SONET/SDH VT/TU Mapper Sections:

- Inserts up to 28 bit asynchronous mapped VT1.5 virtual tributaries into an STS-1 SPE from T1 streams.

- Inserts up to 28 bit asynchronous mapped TU-11 tributary units into a STM-1/VC4 TUG3 or STM-1/VC3 from T1 streams.

- Inserts up to 28 byte synchronous mapped VT1.5 virtual tributaries into an STS-1 SPE or TU-11 tributary units into an STM-1/VC3 or TUG3 from a STM-1/VC4.

- Inserts up to 21 bit asynchronous mapped VT2 virtual tributaries into an STS-1 SPE from E1 streams.

- Inserts up to 21 bit asynchronous mapped TU-12 tributary units into an STM-1/VC4 TUG3 or STM-1/VC3 from E1 or T1 streams.

- Processes the tributary trace message (J2) of the tributaries carried in each STS-1/TUG-3 synchronous payload envelope.

- Bit asynchronous mapping assigns stuff control bits for all streams independently using an all digital control loop. Stuff control bits are dithered to produce fractional mapping jitter at the receiving desynchronizer.

- Sets all fixed stuff bits for asynchronous mappings to zeros or ones per microprocessor control

- Extracts up to 28 bit asynchronous mapped VT1.5 virtual tributaries from an STS-1 SPE into T1 streams via an optional elastic store.

- Extracts up to 28 bit asynchronous mapped TU-11 tributary units from an STM-1/VC4 TUG3 or STM-1/VC3 into T1 streams via an optional elastic store.

- Extracts up to 21 bit asynchronous mapped VT2 virtual tributaries from an STS-1 SPE into E1 streams via an optional elastic store.

- Extracts up to 21 bit asynchronous mapped TU-12 tributary units from an STM-1/VC4 TUG3 or STM-1/VC3 into E1 or T1 streams via an optional elastic store.

DATASHEET PMC-1991437

ISSUE 4

- Demapper ignores all transport overhead bytes, path overhead bytes and stuff (R) bits

- Performs majority vote C-bit decoding to detect stuff requests.

# Each one of three SONET/SDH DS3 Mapper Sections:

- Maps a DS3 stream into an STS-1 SPE (AU3).

- Sets all fixed stuff (R) bits to zeros or ones per microprocessor control

- Extracts a DS3 stream from an STS-1 SPE (AU3).

- Demapper ignores all transport overhead bytes, path overhead bytes and stuff (R) bits

- Performs majority vote C-bit decoding to detect stuff requests

- Complies with DS3 to STS-1 asynchronous mapping standards

### Each one of three DS3 Receiver Sections:

- Frames to a DS3 signal with a maximum average reframe time of less than 1.5 ms (as required by TR-TSY-000009 Section 4.1.2 and TR-TSY-000191 Section 5.2).

- Decodes a B3ZS-encoded signal and indicates line code violations. The definition of line code violation is software selectable.

- Provides indication of M-frame boundaries from which M-subframe boundaries and overhead bit positions in the DS3 stream can be determined by external processing.

- Detects the DS3 alarm indication signal (AIS) and idle signal. Detection algorithms operate correctly in the presence of a 10<sup>-3</sup> bit error rate.Extracts valid X-bits and indicates far end receive failure (FERF).

- Accumulates up to 65,535 line code violation (LCV) events per second, 65,535 P-bit parity error events per second, 1023 F-bit or M-bit (framing bit) events per second, 65,535 excessive zero (EXZ) events per second, and when enabled for C-bit parity mode operation, up to 16,383 C-bit parity error events per second, and 16,383 far end block error (FEBE) events per second.

DATASHEET PMC-1991437

PM8316 TEMUX-84

HIGH DENSITY T1/E1 FRAMER WITH INTEGRATED VT/TU MAPPER AND M13 MUX

- Detects and validates bit-oriented codes in the C-bit parity far end alarm and control channel.

- Terminates the C-bit parity path maintenance data link with an integral HDLC receiver having a 128-byte deep FIFO buffer with programmable interrupt threshold. Supports polled or interrupt-driven operation. Selectable none, one or two address match detection on first byte of received packet.

- Programmable pseudo-random test-sequence detection–(up to 2<sup>32</sup> -1 bit length patterns conforming to ITU-T O.151 standards) and analysis features.

# Each one of three DS3 Transmit Sections:

**ISSUE 4**

- Provides the overhead bit insertion for a DS3 stream.

- Provides a bit serial clock and data interface, and allows the M-frame boundary and/or the overhead bit positions to be located via an external interface.

- Provides B3ZS encoding.

- Generates an B3ZS encoded 100... repeating pattern to aid in pulse mask testing.

- Inserts far end receive failure (FERF), the DS3 alarm indication signal (AIS) and the idle signal when enabled by internal register bits.

- Provides optional automatic insertion of far end receive failure (FERF) on detection of loss of signal (LOS), out of frame (OOF), alarm indication signal (AIS) or red alarm condition.

- Provides diagnostic features to allow the generation of line code violation error events, parity error events, framing bit error events, and when enabled for the C-bit parity application, C-bit parity error events, and far end block error (FEBE) events.

- Supports insertion of bit-oriented codes in the C-bit parity far end alarm and control channel.

- Optionally inserts the C-bit parity path maintenance data link with an integral HDLC transmitter. Supports polled and interrupt-driven operation.

- Provides programmable pseudo-random test sequence generation (up to 2<sup>32</sup>-1 bit length sequences conforming to ITU-T O.151 standards) or any

DATASHEET PMC-1991437

PM8316 TEMUX-84

ISSUE 4

repeating pattern up to 32 bits. The test pattern can be framed or unframed. Diagnostic abilities include single bit error insertion or error insertion at bit error rates ranging from  $10^{-1}$  to  $10^{-7}$ .

#### M23 Multiplexer Section:

- Multiplexes 7 DS2 bit streams into a single M23 format DS3 bit stream.

- Performs required bit stuffing/destuffing including generation and interpretation of C-bits.

- Includes required FIFO buffers for rate adaptation in the multiplex path.

- Allows insertion and detection of per DS2 payload loopback requests encoded in the C-bits to be activated under microprocessor control.

- Internally generates a DS2 clock for use in integrated M13 or C-bit parity multiplex applications. Alternatively accepts external DS2 clock reference.

- Allows per DS2 alarm indication signal (AIS) to be activated or cleared for either direction under microprocessor control.

- Allows DS2 alarm indication signal (AIS) to be activated or cleared in the demultiplex direction automatically upon loss of DS3 frame alignment or signal.

- Supports C-bit parity DS3 format.

# DS2 Framer Section:

- Frames to a DS2 (ANSI T1.107 section 8) signal with a maximum average reframe time of less than 7 ms (as required by TR-TSY-000009 Section 4.1.2 and TR-TSY-000191 Section 5.2).

- Detects the DS2 alarm indication signal (AIS) in 9.9 ms in the presence of a 10<sup>-3</sup> bit error rate.

- Extracts the DS2 X-bit remote alarm indication (RAI) bit and indicates far end receive failure (FERF).

- Accumulates up to 255 DS2 M-bit or F-bit error events per second.

DATASHEET PMC-1991437

HIGH DENSITY T1/E1 FRAMER WITH INTEGRATED VT/TU MAPPER AND M13 MUX

#### **DS2 Transmitter Section:**

**ISSUE 4**

- Generates the required X, F, and M bits into the transmitted DS2 bit stream. Allows inversion of inserted F or M bits for diagnostic purposes.

- Provides for transmission of far end receive failure (FERF) and alarm indication signal (AIS) under microprocessor control.

- Provides optional automatic insertion of far end receive failure (FERF) on detection of out of frame (OOF), alarm indication signal (AIS) or red alarm condition.

#### M12 Multiplexer Section:

- Multiplexes four DS1 or three 2048 kbit/s (according to ITU-T Rec. G.747) bit streams into a single M12 format DS2 bit stream.

- Performs required bit stuffing including generation and interpretation of Cbits.

- Includes required FIFO buffers for rate adaptation in the multiplex path.

- Performs required inversion of second and fourth multiplexed DS1 streams as required by ANSI T1.107 Section 7.2.

- Allows insertion and detection of per DS1 payload loopback requests encoded in the C-bits to be activated under microprocessor control.

- Allows per tributary alarm indication signal (AIS) to be activated or cleared for either direction under microprocessor control.

- Allows automatic tributary AIS to be activated upon DS2 out of frame.

#### Each one of three E3 Framer Sections:

- Frames to G.751 and G.832 E3 unchannelized data streams.

- For G.832, terminates the Trail Trace and either the Network Requirement or the General Purpose data link.

DATASHEET PMC-1991437

ISSUE 4

HIGH DENSITY T1/E1 FRAMER WITH INTEGRATED VT/TU MAPPER AND M13 MUX

#### Each one of three E3 Transmit Sections:

- Provides frame insertion for the G.751 or G.832 E3 applications, alarm insertion, and diagnostic features.

- for G.832, the Trail Trace is inserted, and an integral HDLC transmitter is provided to insert either the Network Requirement or the General Purpose data link.

#### Synchronous System Interfaces:

- Provides twenty one 8 Mbit/s H-MVIP data interfaces for synchronous access to all the DS0s of all 84 T1 links or all timeslots of all 63 E1s. T1 DS0s are bundled from four T1 links in sequential order, 1-4, 5-8, 9-12, ..., 81-84. E1 timeslots are bundled from 4 E1 links in sequential order, 1-4, 5-8, 9-12, ..., 57-60 and 61-63.

- Provides twenty one 8 Mbit/s H-MVIP interfaces for synchronous access to all channel associated signaling (CAS) bits for all T1 DS0s or E1 timeslots. The CAS bits occupy one nibble of every byte on the H-MVIP interfaces and are repeated over the entire T1 or E1 multi-frame.

- Provides three 8 Mbit/s H-MVIP interfaces for common channel signaling (CCS) channels as well as V5.1 and V5.2 channels. In T1 mode DS0 24 is available through this interface. In E1 mode timeslots 15, 16 and 31 are available through this interface. Optionally, timeslot 0 may be presented instead of timeslot 15.

- All links accessed via the H-MVIP interface will be synchronously timed to the common H-MVIP clock and frame alignment signals, CMV8MCLK, CMVFP, CMVFPC.

- H-MVIP access for Channel Associated Signaling is available with the Scaleable Bandwidth Interconnect bus as an optional replacement for CAS access over the SBI bus as well as with the H-MVIP data interface. Common Channel Signaling H-MVIP access is available with the SBI bus, serial PCM and H-MVIP data interfaces.

- Alarm status, T1 F-bit and inband signaling control is available using otherwise unused bit positions.

- Compatible with H-MVIP PCM backplanes supporting 8.192 Mbit/s.

DATASHEET PMC-1991437

HIGH DENSITY T1/E1 FRAMER WITH INTEGRATED VT/TU MAPPER AND M13 MUX

#### Scaleable Bandwidth Interconnect (SBI) Bus:

**ISSUE 4**

- Provides a high density byte serial interconnect for all framed and unframed TEMUX-84 links. Utilizes an Add/Drop configuration to asynchronously mutliplex up to 84 T1s, 63 E1s or 3 DS3s, with multiple payload or link layer processors.

- Operates at either 19.44 MHz or 77.76 MHz.

- External devices can access unframed DS3, framed unchannelized DS3, unframed E3, framed unchannelized E3, unframed (clear channel) T1s, framed T1s, unframed (clear channel) E1s, framed E1s, arbitrary rate clear channel data stream (eg. fractional DS3), transparent virtual tributaries or transparent tributary units over this interface.

- Framed and unframed T1 access can be selected on a per T1 basis. Framed and unframed E1 access can be selected on a per E1 basis.

- Up to three arbitrary rate data streams inserted into and extracted from the SBI via bit serial ports.

- Synchronous access for T1 DS0 channels or E1 timeslots is supported in a locked format mode. Selectable on a per tributary basis.

- Transparent VT/TU access can be selected only when tributaries are mapped into SONET/SDH.

- Transparent VT1.5s and TU-11s can be selected on a per tributary basis in combination with framed and unframed T1s. Transparent VT2s and TU-12s can be selected on a per tributary basis in combination with framed and unframed E1s.

- Channel associated signaling bits for channelized T1 and E1 are explicitly identified across the bus.

- Transmit timing is mastered either by the TEMUX-84 or a layer 2 device connecting to the SBI bus. Timing mastership is selectable on a per tributary basis, where a tributary is either an individual T1, E1, E3 or a DS3.

DATASHEET PMC-1991437

ISSUE 4

HIGH DENSITY T1/E1 FRAMER WITH INTEGRATED VT/TU MAPPER AND M13 MUX

#### 2 APPLICATIONS

- High density T1 interfaces for multiplexers, multi-service switches, routers and digital modems.

- High density E1 interfaces for multiplexers, multi-service switches, routers and digital modems.

- Frame Relay switches and access devices (FRADS)

- SONET/SDH Add Drop Multiplexers

- SONET/SDH Terminal Multiplexers

- M23 Based M13 Multiplexer

- C-Bit Parity Based M13 Multiplexer

- Channelized and Unchannelized DS3 Frame Relay Interfaces

- Optical Access Equipment

- Digital Access Cross-Connect Systems

DATASHEET PMC-1991437

PM8316 TEMUX-84

ISSUE 4

HIGH DENSITY T1/E1 FRAMER WITH INTEGRATED VT/TU MAPPER AND M13 MUX

#### 3 REFERENCES

- American National Standard for Telecommunications Digital Hierarchy -Synchronous DS3 Format Specifications, ANSI T1.103-1993

- American National Standard for Telecommunications ANSI T1.105 "Synchronous Optical Network (SONET) – Basic Description Including Multiplex Structure, Rates, and Formats," October 27, 1995.

- American National Standard for Telecommunications ANSI T1.105.02 "Synchronous Optical Network (SONET) – Payload Mappings," October 27, 1995.

- American National Standard for Telecommunications Digital Hierarchy -Formats Specification, ANSI T1.107-1995

- American National Standard for Telecommunications Digital Hierarchy Layer 1 In-Service Digital Transmission Performance Monitoring, ANSI T1.231-1997

- American National Standard for Telecommunications Carrier to Customer Installation - DS-1 Metallic Interface Specification, ANSI T1.403-1995

- American National Standard for Telecommunications Customer Installation-to-Network - DS3 Metallic Interface Specification, ANSI T1.404-1994

- American National Standard for Telecommunications Integrated Services Digital Network (ISDN) Primary Rate- Customer Installation Metallic Interfaces Layer 1 Specification, ANSI T1.408-1990

- Bell Communications Research, TR–TSY-000009 Asynchronous Digital Multiplexes Requirements and Objectives, Issue 1, May 1986

- Bell Communications Research DS-1 Rate Digital Service Monitoring Unit Functional Specification, TA-TSY-000147, Issue 1, October, 1987

- Bell Communications Research Alarm Indication Signal Requirements and Objectives, TR-TSY-000191 Issue 1, May 1986

- Bell Communications Research Wideband and Broadband Digital Cross-Connect Systems Generic Criteria, TR-NWT-000233, Issue 3, November 1993

PMC-1991437

PMC PMC-Sierra

**ISSUE 4**

PM8316 TEMUX-84

- Bell Communications Research Digital Interface Between The SLC®96 Digital Loop Carrier System And A Local Digital Switch, TR-TSY-000008, Issue 2, August 1987

- Bellcore GR-253-CORE "SONET Transport Systems: Common Criteria," Issue 2, Revision 1, December 1997.

- Bell Communications Research Integrated Digital Loop Carrier Generic Requirements, Objectives, and Interface, TR-NWT-000303, Issue 2, December, 1992

- Bell Communications Research Transport Systems Generic Requirements (TSGR): Common Requirement, TR-TSY-000499, Issue 5, December, 1993

- Bell Communications Research OTGR: Network Maintenance Transport Surveillance - Generic Digital Transmission Surveillance, TR-TSY-000820, Section 5.1, Issue 1, June 1990

- AT&T Requirements For Interfacing Digital Terminal Equipment To Services Employing The Extended Superframe Format, TR 54016, September, 1989.

- AT&T Accunet T1.5 Service Description and Interface Specification, TR 62411, December, 1990

- ITU Study Group XVIII Report R 105, Geneva, 9-19 June 1992

- ETSI ETS 300 011 ISDN Primary Rate User-Network Interface Specification and Test Principles, 1992.

- ETSI ETS 300 233 Access Digital Section for ISDN Primary Rates, May 1994

- ETSI ETS 300 324-1 Signaling Protocols and Switching (SPS); V interfaces at the Digital Local Exchange (LE) V5.1 Interface for the Support of Access Network (AN) Part 1: V5.1 Interface Specification, February, 1994.

- ETSI ETS 300 347-1 Signaling Protocols and Switching (SPS); V Interfaces at the Digital Local Exchange (LE) V5.2 Interface for the Support of Access Network (AN) Part 1: V5.2 Interface Specification, September 1994.

- ETSI ETS 300 417-1-1 "Transmission and Multiplexing (TM); Generic Functional Requirements for Synchronous Digital Hierarchy (SDH) equipment; Part 1-1: Generic processes and performance," January, 1996.

- ETSI, Generic Functional Requirements for Synchronous Digital Hierarchy (SDH) Equipment, Jan 1996

DATASHEET PMC-1991437

PM8316 TEMUX-84

HIGH DENSITY T1/E1 FRAMER WITH INTEGRATED VT/TU MAPPER AND M13 MUX

• ITU-T - Recommendation G.704 - Synchronous Frame Structures Used at Primary Hierarchical Levels, July 1995.

**ISSUE 4**

- ITU-T Recommendation G.706 Frame Alignment and CRC Procedures Relating to G.704 Frame Structures, 1991.

- ITU-T Recommendation G.732 Characteristics of Primary PCM Multiplex Equipment Operating at 2048 kbit/s, 1993.

- ITU-T Recommendation G.707 Network Node Interface for the Synchronous Digital Hierarchy, 1996

- ITU-T Recommendation G.747 Second Order Digital Multiplex Equipment Operating at 6312 kbit/s and Multiplexing Three Tributaries at 2048 kbit/s, 1988

- ITU-T Recommendation G.751, CCITT Blue Book Fasc. III.4, "Digital Multiplex Equipments Operating at the Third Order Bit Rate of 34,368 kbit/s and the Fourth Order Bit Rate of 139,264 kbit/s and Using Positive Justification", 1988.

- ITU-T Recommendation G.775, Loss of Signal (LOS) and Alarm Indication Signal (AIS) Defect Detection and Clearance Criteria, 11/94

- ITU-T Recommendation G.783 Characteristics of Synchronous Digital Hierarchy (SDH) Equipment Functional Blocks, April, 1997.

- ITU-T Recommendation G.823, The Control of Jitter and Wander within Digital Networks which are Based on the 2048 kbit/s Hierarchy, 03/94ITU-T Recommendation G.832 - "Transport of SDH Elements on PDH Networks: Frame and Multiplexing Structures", 1993.

- ITU-T Recommendation G.964, V-Interfaces at the Digital Local Ex–hange (LE)

V5.1 Interface (Based on 2048 kbit/s) for the Support of Access Network (AN), June 1994.

- ITU-T Recommendation G.965, V-Interfaces at the Digital Local Ex–hange (LE)

V5.2 Interface (Based on 2048 kbit/s) for the Support of Access Network (AN), March –995.

- ITU-T Recommendation I.431 Primary Rate User-Network Interface Layer 1 Specification, 1993.

- ITU-T Recommendation O.151 Error Performance Measuring Equipment Operating at the Primary Rate and Above, October 1992

DATASHEET PMC-1991437

**ISSUE 4**

PM8316 TEMUX-84

- ITU-T Recommendation O.152 Error Performance Measuring Equipment for Bit Rates of 64 kbit/s and N x 64 kbit/s, October 1992

- ITU-T Recommendation O.153 Basic Parameters for the Measurement of Error Performance at Bit Rates below the Primary Rate, October 1992.

- ITU-T Recommendation Q.921 ISDN User-Network Interface Data Link Layer Specification, March 1993

- International Organization for Standardization, ISO 3309:1984 High-Level Data Link Control procedures - Frame Structure

- PMC-Sierra Inc., PMC-980577 Saturn Compatible Scaleable Bandwidth Interface (SBI) Specification, Issue 3, 1998

- TTC Standard JT-G704 Frame Structures on Primary and Secondary Hierarchical Digital Interfaces, 1995.

- TTC Standard JT-G706 Frame Synchronization and CRC Procedure

- TTC Standard JT-I431 ISDN Primary Rate User-Network Interface Layer 1 Specification, 1995.

- Nippon Telegraph and Telephone Corporation Technical Reference for High-Speed Digital Leased Circuit Services, Third Edition, 1990.

- GO-MVIP, Multi-Vendor Integration Protocol, MVIP-90, Release 1.1, 1994

- GO-MVIP, H-MVIP Standard, Release1.1a, 1997

PMC-Sierra

PM8316 TEMUX-84

DATASHEET PMC-1991437

ISSUE 4

HIGH DENSITY T1/E1 FRAMER WITH INTEGRATED VT/TU MAPPER AND M13 MUX

### 4 APPLICATION EXAMPLES

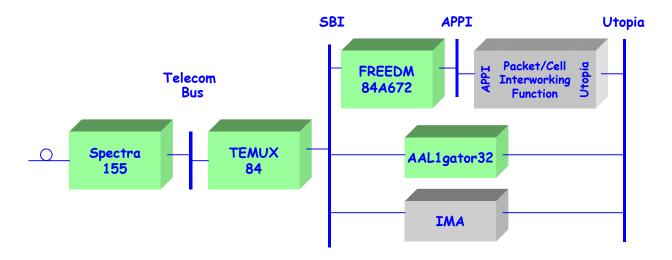

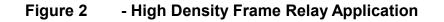

Figure 1illustrates how frame relay (FREEDM84A672), circuit emulation (AAL1gator32) and ATM inverse multiplexing (IMA84) may all be supported on the same port with a common SBI bus as the enabling technology.

DATASHEET PMC-1991437

HIGH DENSITY T1/E1 FRAMER WITH INTEGRATED VT/TU MAPPER AND M13 MUX

ISSUE 4

Figure 3 - Fractional DS3 Application

DATASHEET PMC-1991437

PM8316 TEMUX-84

ISSUE 4

HIGH DENSITY T1/E1 FRAMER WITH INTEGRATED VT/TU MAPPER AND M13 MUX

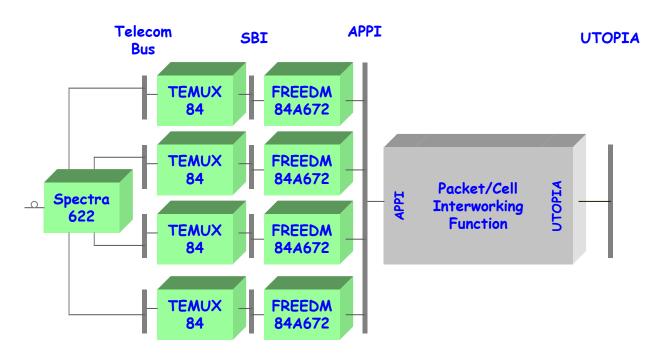

To support evolving fractional DS3 applications, flow-controlled ports provide access to SBI bus bandwidth. Several non-standard schemes have been devised to use a portion of the DS3 payload. Given that these protocols are subject to change, they are best supported by external programmable logic. Figure 3 illustrates one implementation. Other implementations and applications are possible.

In the ingress direction, the framed DS3 is presented to an FPGA, whose responsibility it is to identify the utilitized bits of the payload. Valid bits are indicated to the Ingress Flexible Bandwidth Port via an enable signal, IFBWEN. The bits are collected into bytes by the TEMUX-84 and inserted into the payload of the SBI Drop bus.

In the egress direction, an FPGA formats the payload of a DS3, while the TEMUX-84 inserts the DS3 frame overhead. The FPGA contains a data buffer. Based on the DS3 frame alignment dictated by the TMFPO signal, the FPGA inserts bits from the data buffer into the DS3 payload according to the protocol supported. To ensure the data buffer is replenished, the FPGA asserts the EFBWDREQ signal to initiate the transfer of a bit. The Egress Flexible Bandwidth Port responds by asserting EFWBEN coincident with EFWBDAT presenting valid data. The SBI Add bus participates by modulating its SAJUST\_REQ output to match the SBI data rate to that required to keep internal FIFOs centered.

DATASHEET PMC-1991437

PM8316 TEMUX-84

ISSUE 4

HIGH DENSITY T1/E1 FRAMER WITH INTEGRATED VT/TU MAPPER AND M13 MUX

## 5 BLOCK DIAGRAM

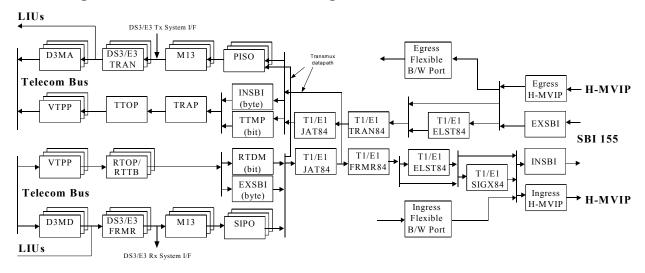

#### 5.1 Top Level Block Diagram

Figure 4 shows the complete TEMUX-84. T1 links can be multiplexed into the DS3s or can be mapped into the telecom bus as SONET VT1.5 virtual tributaries or as SDH TU-11 or TU-12 tributary units. E1 links can be mapped into the telecom bus as SONET VT2 virtual tributaries or as SDH TU-12 tributary units. System side access to the T1s and E1s is available as Synchronous H-MVIP interfaces or the SBI bus. DS3 line side access is via the clock and data interface for line interface units (LIUs) or DS3 mapped into the SONET/SDH telecom bus. Unchannelized DS3 system side access is available through the SBI bus.

#### Figure 4 - TEMUX-84 Block Diagram

DATASHEET PMC-1991437

ISSUE 4

HIGH DENSITY T1/E1 FRAMER WITH INTEGRATED VT/TU MAPPER AND M13 MUX

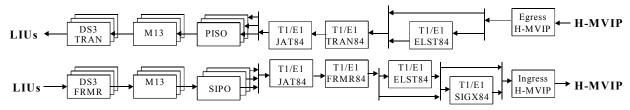

#### 5.2 M13 Multiplexer Mode Block Diagram

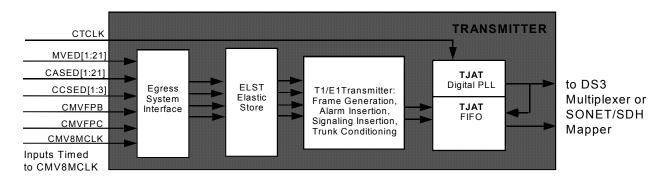

Figure 5 shows the TEMUX-84, configured as a M13 multiplexer, connected to a synchronous H-MVIP system side bus. In this example the TEMUX-84 provides synchronous access to the fully channelized T1s (access to all DS0s) multiplexed into the DS3. There is also synchronous H-MVIP access to all channel associated signaling channels (CAS). Additional H-MVIP interfaces can be used to provide synchronous access to the common channel signaling channels (CCS), although this same information is available within the data H-MVIP signals.

DATASHEET PMC-1991437

ISSUE 4

HIGH DENSITY T1/E1 FRAMER WITH INTEGRATED VT/TU MAPPER AND M13 MUX

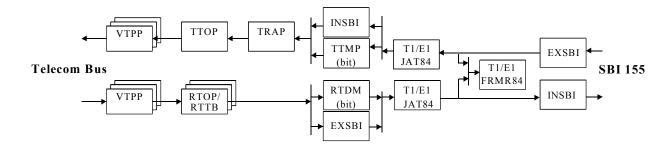

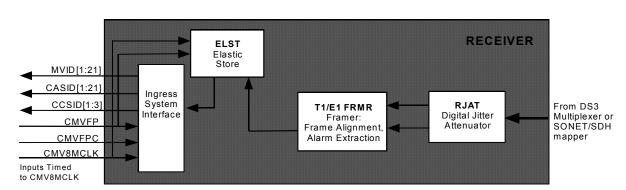

## 5.3 VT/TU Mapper Only Mode Block Diagram

Figure 6 shows the TEMUX-84 configured as a VT or TU mapper. In this mode the TEMUX-84 bypasses the T1 and E1 framers and provides access for up to 84 independent unframed 1.544 Mbit/s streams or 63 independent unframed 2.048 Mbit/s streams. The 1.544 Mbit/s and 2.048 Mbit/s streams can be accessed on the system side via the SBI bus. The T1 or E1 framers can be used to monitor the passing traffic in either the ingress or egress direction. The M13 Multiplexer mode operates in much the same way as the VT and TU mapper shown in Figure 6.

### Figure 6 - VT/TU Mapper Block Diagram

DATASHEET PMC-1991437

PM8316 TEMUX-84

ISSUE 4

HIGH DENSITY T1/E1 FRAMER WITH INTEGRATED VT/TU MAPPER AND M13 MUX

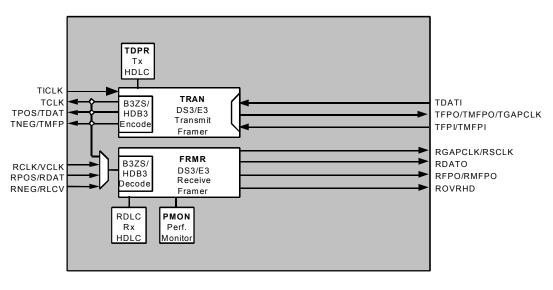

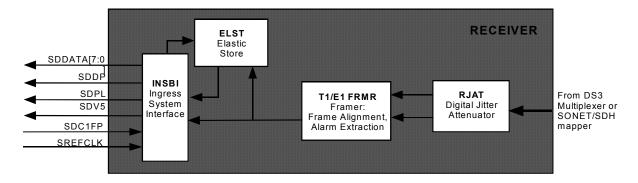

# 5.4 DS3/E3 Framer Only Block Diagram

Figure 7 shows the TEMUX-84 configured as a DS3 or E3 framer. In this mode the TEMUX-84 provides access up to three full DS3/E3 unchannelized payloads. The payload access (right side of diagram) has two clock and data interfacing modes, one utilizing a gapped clock to mask out the DS3/E3 overhead bits and the second utilizing an ungapped clock with overhead indications on a separate overhead signal. The SBI bus can also be used to provide access to the unchannelized DS3/E3.

3X

DATASHEET PMC-1991437

ISSUE 4

HIGH DENSITY T1/E1 FRAMER WITH INTEGRATED VT/TU MAPPER AND M13 MUX

### 6 DESCRIPTION

The PM8316 High Density T1/E1 Framer with Integrated VT/TU Mappers and M13 Multiplexers (TEMUX-84) is a feature-rich device for use in any applications requiring high density link termination over T1 and E1 (G.747) channelized DS3 or T1 and E1 channelized SONET/SDH facilities.

The TEMUX-84 supports asynchronous multiplexing and demultiplexing of 84 DS1s or 63 E1s into three DS3 signals as specified by ANSI T1.107, Bell Communications Research TR-TSY-000009 and ITU-T Rec. G.747. It supports bit asynchronous or byte synchronous mapping and demapping of 84 T1s or 63 E1s into SONET/SDH as specified by ANSI T1.105, Bell Communications Research GR-253-CORE and ITU-T Recommendation G.707. The TEMUX-84 also supports mapping of 63 T1s into SDH via TU-12s. Up to 84 Transparent VT1.5s and TU-11s or 63 Transparent VT2s and TU-12s can be transferred between the SONET/SDH interface and the SBI bus interface.

This device can also be configured as a DS3 or E3 framer, providing external access to the full DS3 or E3 payload, or a VT/TU mapper, providing access to unframed 1.544 Mbit/s and 2.048 Mbit/s links.

The TEMUX-84 can be used as a SONET/SDH VT/TU mapper or M13 multiplexer with performance monitoring in either the ingress or egress direction for up to 84 T1s or 63 E1s. In this configuration the T1 and E1 transmit framers are disabled and either the ingress or egress T1 or E1 signals are routed to the T1 or E1 framers for performance monitoring purposes.

Each of the T1 and E1 framers and transmitters is independently software configurable, allowing timing master and feature selection without changes to external wiring. T1 and E1 tributaries may be mixed at a VC-3/TUG-3/DS3 granularity.

In the ingress direction, each of the 84 T1 links is either demultiplexed from a channelized DS3 or extracted from SONET VT1.5, TU-11 or TU-12 mapped bus. Each T1 framer can be configured to frame to the common DS1 signal formats (SF, SLC®96, ESF) or to be bypassed (unframed mode). Each T1 framer detects the presence of Yellow and AIS patterns and also integrates Yellow, Red, and AIS alarms.

T1 performance monitoring with accumulation of CRC-6 errors, framing bit errors, out-of-frame events, and changes of frame alignment is provided. The TEMUX-84 also detects the presence of ESF bit oriented codes, and detects and terminates HDLC messages on the ESF data link. The HDLC messages are terminated in a 128 byte FIFO. An elastic store that optionally supports slip

DATASHEET PMC-1991437

PM8316 TEMUX-84

ISSUE 4

HIGH DENSITY T1/E1 FRAMER WITH INTEGRATED VT/TU MAPPER AND M13 MUX

buffering and adaptation to backplane timing is provided, as is a signaling extractor that supports signaling debounce, signaling freezing and interrupt on signaling state change on a per-DS0 basis. The TEMUX-84 also supports inband loopback code generation and detection, idle code substitution, digital milliwatt code insertion, data link extraction, trunk conditioning, data sign and magnitude inversion, and pattern generation and detection on a per-DS0 basis.

In the egress direction, framing is generated for 84 T1s into either a DS3 multiplex or a SONET/SDH mapped add bus. Each T1 transmitter frames to SF or ESF DS1 formats, or framing can be optionally disabled. The TEMUX-84 supports signaling insertion, idle code substitution, data insertion, line loopback, data inversion and zero-code suppression on a per-DS0 basis. PRBS generation and detection is supported on a framed and unframed T1 basis.

In the ingress direction, each of the 63 E1 links is either demultiplexed from a DS3 according to ITU-T Rec. G.747 or extracted from SONET/SDH VT2 or TU-12 mapped bus. Each E1 framer detects and indicates the presence of remote alarm and AIS patterns and also integrates Red and AIS alarms.

The E1 framers support detection of various alarm conditions such as loss of frame, loss of signaling multiframe and loss of CRC multiframe. The E1 framers also support reception of remote alarm signal, remote multiframe alarm signal, alarm indication signal, and time slot 16 alarm indication signal.

E1 performance monitoring with accumulation of CRC-4 errors, far end block errors and framing bit errors is provided. The TEMUX-84 provides a receive HDLC controller for the detection and termination of messages on the national use bits. Detection of the 4-bit Sa-bit codewords defined in ITU-T G.704 and ETSI 300-233 is supported. V5.2 link ID signal detection is also supported. An interrupt may be generated on any change of state of the Sa codewords. An elastic store for slip buffering and rate adaptation to backplane timing is provided, as is a signaling extractor that supports signaling debounce, signaling freezing, idle code substitution, digital milliwatt tone substitution, data inversion, and signaling bit fixing on a per-channel basis. Receive side data and signaling trunk conditioning is also provided.

In the egress direction, framing is generated for 63 E1s into either a DS3 multiplex according to ITU-T Rec. G.747 or a SONET/SDH mapped add bus. Each E1 transmitter generates framing for a basic G.704 E1 signal. The signaling multiframe alignment structure and the CRC multiframe structure may be optionally inserted. Framing can be optionally disabled. Transmission of the 4-bit Sa codewords defined in ITU-T G.704 and ETSI 300-233 is supported. PRBS generation or detection is supported on a framed and unframed E1 basis.

DATASHEET PMC-1991437

PM8316 TEMUX-84

ISSUE 4

HIGH DENSITY T1/E1 FRAMER WITH INTEGRATED VT/TU MAPPER AND M13 MUX

The TEMUX-84 can generate a low jitter transmit clock from a variety of clock references, and also provides jitter attenuation in the receive path. Three jitter attenuated recovered T1/E1 clocks can be routed outside the TEMUX-84 for network timing applications.

In synchronous backplane systems, 8 Mbit/s H-MVIP interfaces are provided for access to 2016 DS0 channels, channel associated signaling (CAS) for all 2016 DS0 channels and common channel signaling (CCS) for all 84 T1s or 63 E1s (or combination thereof). The CCS signaling H-MVIP interface is independent of the DS0 channel and CAS H-MVIP access. The use of any of the H-MVIP interfaces requires that common clocks and frame pulse be used along with T1 slip buffers.

A Scaleable Bandwidth Interconnect (SBI) high density byte serial system interface provides higher levels of integration and dense interconnect. The SBI bus interconnects up to 84 T1s or 63 E1 both synchronously or asynchronously. The SBI allows transmit timing to be mastered by either the TEMUX-84 or link layer device connected to the SBI bus. In addition to framed T1s and E1s the TEMUX-84 can transport unframed T1 or E1 links and framed or unframed DS3 or E3 links over the SBI bus.

When configured as a DS3 multiplexer/demultiplexer or DS3 framer, the TEMUX-84 accepts and outputs either digital B3ZS-encoded bipolar or unipolar signals compatible with M23 and C-bit parity applications.

In the DS3 receive direction, the TEMUX-84 frames to DS3 signals with a maximum average reframe time of 1.5 ms in the presence of 10<sup>-3</sup> bit error rate and detects line code violations, loss of signal, framing bit errors, parity errors, C-bit parity errors, far end block errors, AIS, far end receive failure and idle code. The DS3 framer is an off-line framer, indicating both out of frame (OOF) and change of frame alignment (COFA) events. The error events (C-BIT, FEBE, etc.) are still indicated while the framer is OOF, based on the previous frame alignment. When in C-bit parity mode, the Path Maintenance Data Link and the Far End Alarm and Control (FEAC) channels are extracted. HDLC receivers are provided for Path Maintenance Data Link support. In addition, valid bit-oriented codes in the FEAC channels are detected and are available through the microprocessor port.

Error event accumulation is also provided by the TEMUX-84. Framing bit errors, line code violations, excessive zeros occurrences, parity errors, C-bit parity errors, and far end block errors are accumulated. Error accumulation continues even while the off-line framers are indicating OOF. The counters are intended to be polled once per second, and are sized so as not to saturate at a 10<sup>-3</sup> bit error rate. Transfer of count values to holding registers is initiated through the microprocessor interface.

DATASHEET PMC-1991437

PM8316 TEMUX-84

ISSUE 4

HIGH DENSITY T1/E1 FRAMER WITH INTEGRATED VT/TU MAPPER AND M13 MUX

In the DS3 transmit direction, the TEMUX-84 inserts DS3 framing, X and P bits. When enabled for C-bit parity operation, bit-oriented code transmitters and HDLC transmitters are provided for insertion of the FEAC channels and the Path Maintenance Data Links into the appropriate overhead bits. Alarm Indication Signals, Far End Receive Failure and idle signal can be inserted using either internal registers or can be configured for automatic insertion upon received errors. When M23 operation is selected, the C-bit Parity ID bit (the first C-bit of the first M sub-frame) is forced to toggle so that downstream equipment will not confuse an M23-formatted stream with stuck-at-1 C-bits for C-bit Parity application. Transmit timing is from an external reference or from the receive direction clock.

The TEMUX-84 also supports diagnostic options which allow it to insert, when appropriate for the transmit framing format, parity or path parity errors, F-bit framing errors, M-bit framing errors, invalid X or P-bits, line code violations, all-zeros, AIS, Remote Alarm Indications, and Remote End Alarms. A Pseudo Random Binary Sequence (PRBS) can be inserted into a DS3 payload and checked in the receive DS3 payload for bit errors. A fixed 100100... pattern is available for insertion directly into the B3ZS encoder for proper pulse mask shape verification.

The TEMUX-84 may be used as an E3 framer for the transport of framed but unchannelized E3 data streams complying to the ITU-T Recommendations G.751 or G.832. The line interface may be configured as either unipolar or HDB3-encoded.

When configured in DS3 multiplexer mode, seven 6312 kbit/s data streams are demultiplexed and multiplexed into and out of each DS3 signal. Bit stuffing and rate adaptation is performed. The C-bits are set appropriately, with the option of inserting DS2 loopback requests. Interrupts can be generated upon detection of loopback requests in the received DS3. AIS may be inserted in the any of the 6312 kbit/s tributaries in both the multiplex and demultiplex directions. C-bit parity is supported by sourcing a 6.3062723 MHz clock, which corresponds to a stuffing ratio of 100%.

Framing to the demultiplexed 6312 kbit/s data streams supports DS2 (ANSI TI.107) frame formats. The maximum average reframe time is 7ms for DS2. Far end receive failure is detected and M-bit and F-bit errors are accumulated. The DS2 framer is an off-line framer, indicating both OOF and COFA events. Error events (FERF, MERR, FERR, PERR, RAI, framing word errors) are still indicated while the DS2 framer is indicating OOF, based on the previous alignment.

Each of the seven 6312 kbit/s multiplexers per DS3 may be independently configured to multiplex and demultiplex four 1544 kbit/s DS1s or three 2048 kbit/s according to ITU-T Rec. G.747 into and out of a DS2 formatted

DATASHEET PMC-1991437

PM8316 TEMUX-84

ISSUE 4

HIGH DENSITY T1/E1 FRAMER WITH INTEGRATED VT/TU MAPPER AND M13 MUX

signal. Tributary frequency deviations are accommodated using internal FIFOs and bit stuffing. The C-bits are set appropriately, with the option of inserting DS1 loopback requests. Interrupts can be generated upon detection of loopback requests in the received DS2. AIS may be inserted in any of the low speed tributaries in both multiplex and demultiplex directions.

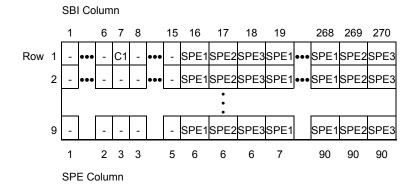

When configured as a DS3 or E3 framer the unchannelized payload of the DS3 and E3 links are available to an external device.