# MFC2000

# **Multifunctional Peripheral Controller 2000**

**Hardware Description**

#### **Ordering Information**

| Marketing Name | Device Set Order No. |          |         |          |         |

|----------------|----------------------|----------|---------|----------|---------|

|                |                      | Part No. | Package | Part No. | Package |

| MFC2000        | XXX-XXX-XXX          | XXXXX    |         |          |         |

#### **Revision History**

| Revision | Date     | Comments                                                     |

|----------|----------|--------------------------------------------------------------|

| А        | 04/07/00 | Initial, internal, preliminary release of document.          |

| А        | 06/21/00 | Second internal, preliminary release with revisions tracked. |

#### © 2000, Conexant Systems, Inc. All Rights Reserved.

Information in this document is provided in connection with Conexant Systems, Inc. ("Conexant") products. These materials are provided by Conexant as a service to its customers and may be used for informational purposes only. Conexant assumes no responsibility for errors or omissions in these materials. Conexant may make changes to specifications and product descriptions at any time, without notice. Conexant makes no commitment to update the information contained herein. Conexant shall have no responsibility whatsoever for conflicts or incompatibilities arising from future changes to its specifications and product descriptions.

No license, express or implied, by estoppel or otherwise, to any intellectual property rights is granted by this document. Except as provided in Conexant's Terms and Conditions of Sale for such products, Conexant assumes no liability whatsoever.

THESE MATERIALS ARE PROVIDED "AS IS" WITHOUT WARRANTY OF ANY KIND, EITHER EXPRESS OR IMPLIED, RELATING TO SALE AND/OR USE OF CONEXANT PRODUCTS INCLUDING LIABILITY OR WARRANTIES RELATING TO FITNESS FOR A PARTICULAR PURPOSE, MERCHANTABILITY, OR INFRINGEMENT OF ANY PATENT, COPYRIGHT OR OTHER INTELLECTUAL PROPERTY RIGHT. Conexant further does not warrant the accuracy or completeness of the information, text, graphics or other items contained within these materials. Conexant shall not be liable for any special, indirect, incidental, or consequential damages, including without limitation, lost revenues or lost profits, which may result from the use of these materials.

Conexant products are not intended for use in medical, life saving or life sustaining applications. Conexant customers using or selling Conexant products for use in such applications do so at their own risk and agree to fully indemnify Conexant for any damages resulting from such improper use or sale.

The following are trademarks of Conexant Systems, Inc.: Conexant, the Conexant C symbol, "What's Next in Communications Technologies", and SmartDAA. Product names or services listed in this publication are for identification purposes only, and may be trademarks of third parties. Third-party brands and names are the property of their respective owners.

**Reader Response:** Conexant strives to produce quality documentation and welcomes your feedback. Please send comments and suggestions to conexant.tech.pubs@conexant.com. For technical questions, contact your local Conexant sales office or field applications engineer.

# Contents

| 1. | INTRODUCTION                                             | 1-1 |

|----|----------------------------------------------------------|-----|

|    | 1.1 SCOPE                                                |     |

|    | 1.2 SYSTEM OVERVIEW                                      | 1-1 |

|    | 1.3 REFERENCE DOCUMENTATION                              | 1-5 |

| 2. | MFC2000 SUMMARY                                          | 2-1 |

|    | 2.1 MFC2000 DEVICE FAMILY                                | 2-1 |

|    | 2.2 MFC2000 SYSTEM BLOCK DIAGRAM                         | 2-1 |

| 3. | HARDWARE INTERFACE                                       |     |

|    | 3.1 PIN DESCRIPTION                                      |     |

|    | 3.2 MAXIMUM RATINGS                                      |     |

|    | 3.3 ELECTRICAL CHARACTERISTICS                           |     |

|    | 3.4 PIN LAYOUT                                           |     |

| 4. | CPU AND BUS INTERFACE                                    |     |

|    | 4.1 MEMORY MAP AND CHIP SELECT DESCRIPTION               |     |

|    | 4.2 CACHE MEMORY CONTROLLER                              |     |

|    | 4.3 SIU                                                  |     |

|    | 4.4 INTERRUPT CONTROLLER                                 |     |

|    | 4.5 DRAM CONTROLLER (INCLUDING BATTERY DRAM)             |     |

|    | 4.6 FLASH MEMORY CONTROLLER<br>4.7 DMA CONTROLLER        |     |

| -  |                                                          |     |

| 5. |                                                          |     |

|    | 5.1 RESET LOGIC/BATTERY BACKUP                           |     |

|    | 5.2 WATCHDOG TIMER                                       |     |

| 6. | FAX TIMING CONTROL INTERFACE                             | 6-1 |

|    | 6.1 PLL                                                  |     |

|    | 6.2 FAX TIMING LOGIC                                     | -   |

|    |                                                          |     |

|    | 6.4 SCAN CONTROL TIMING<br>6.5 FAX TIMING REGISTERS      |     |

| 7  | VIDEO/SCANNER CONTROLLER                                 |     |

| 1. |                                                          |     |

|    | 7.1 SCANNER CONTROLLER                                   |     |

|    | 7.2 SERIAL PROGRAMMING INTERFACE<br>7.3 VIDEO CONTROLLER |     |

| •  |                                                          |     |

| 8. | ADC                                                      |     |

|    | 8.1 PADC AND SCAN ANALOG FRONT END                       |     |

|    | 8.2 TADC                                                 |     |

| 9.  | BI-LE | VEL RESOLUTION CONVERSION                             | 9-1   |

|-----|-------|-------------------------------------------------------|-------|

|     |       | UNCTIONAL DESCRIPTION                                 |       |

|     | 9.2 R | EGISTER DESCRIPTION                                   | 9-6   |

|     | 9.3 R | ESOLUTION CONVERSION PROGRAMMING EXAMPLES             | 9-15  |

| 10. | EXTE  | RNAL PRINT ASIC INTERFACE                             |       |

|     | 10.1  | INTERFACE BETWEEN THE MFC2000 AND EXTERNAL PRINT ASIC |       |

| 11. | BIT R | OTATION LOGIC                                         | 11-1  |

|     | 11.1  | FUNCTIONAL DESCRIPTION                                |       |

|     | 11.2  | BLOCK DIAGRAM                                         |       |

|     | 11.3  | REGISTER DESCRIPTION                                  |       |

|     | 11.4  | FIRMWARE OPERATION                                    |       |

| 12. | PRIN  | TER AND SCANNER STEPPER MOTOR INTERFACE               |       |

|     | 12.1  | VERTICAL PRINT STEPPER MOTOR INTERFACE                |       |

|     | 12.2  | SCANNER STEPPER MOTOR INTERFACE                       |       |

| 13. | GENE  | ERAL PURPOSE INPUTS/OUTPUTS (GPIO)                    |       |

|     | 13.1  | GPIO SIGNALS                                          |       |

|     | 13.2  | GPO/GPI SIGNALS                                       |       |

|     | 13.3  | GPIO CONTROL AND DATA REGISTERS                       |       |

| 14. | СОМ   | PRESSOR AND DECOMPRESSOR                              | 14-1  |

|     | 14.1  | FUNCTIONAL DESCRIPTION                                | 14-1  |

|     | 14.2  | REGISTER DESCRIPTION                                  | 14-2  |

| 15. | SYNC  | CHRONOUS/ASYNCHRONOUS SERIAL INTERFACE (SASIF)        | 15-1  |

|     | 15.1  | FUNCTIONAL DESCRIPTION                                |       |

|     | 15.2  | REGISTER DESCRIPTION                                  |       |

|     | 15.3  | SASIF TIMING                                          |       |

|     | 15.4  | FIRMWARE OPERATION                                    | 15-16 |

| 16. | USB   | INTERFACE                                             |       |

|     | 16.1  | FUNCTION DESCRIPTION                                  |       |

|     | 16.2  | REGISTER DESCRIPTION                                  |       |

|     | 16.3  | FIRMWARE OPERATION                                    |       |

| 17. | BI-DI | RECTIONAL PARALLEL PERIPHERAL INTERFACE               |       |

|     | 17.1  | OPERATIONAL MODES                                     |       |

|     | 17.2  | ADDITIONAL FEATURES                                   |       |

|     | 17.3  | FUNCTIONAL DESCRIPTION                                |       |

|     | 17.4  | REGISTER DESCRIPTION                                  | 17-4  |

|     | 17.5  | TIMING                                                |       |

|     | 17.6  | FIRMWARE OPERATION                                    |       |

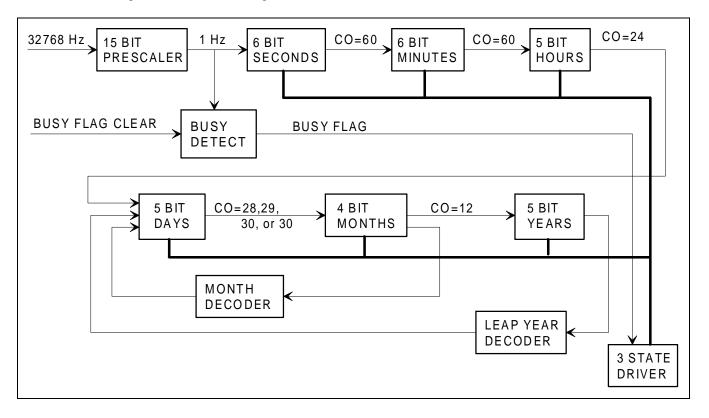

| 18. | REAL | -TIME CLOCK                              |       |

|-----|------|------------------------------------------|-------|

|     | 18.1 | DESCRIPTION                              |       |

|     | 18.2 | REAL-TIME CLOCK (RTC) REGISTERS          |       |

|     | 18.3 | RTC OPERATIONS                           |       |

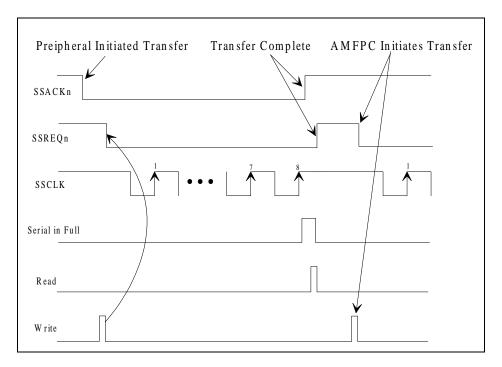

| 19. | SYNC | HRONOUS SERIAL INTERFACE (SSIF)          |       |

|     | 19.1 | INTRODUCTION AND FEATURES                |       |

|     | 19.2 | REGISTER DESCRIPTION                     |       |

|     | 19.3 | SSIF TIMING                              |       |

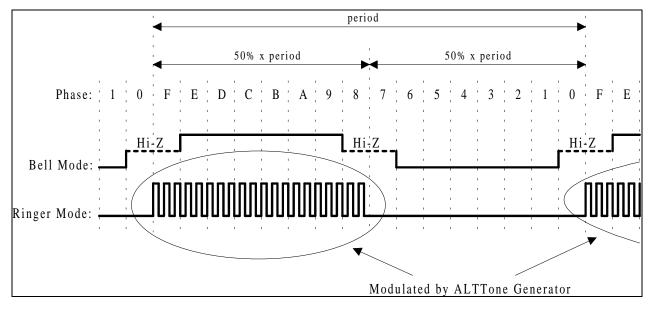

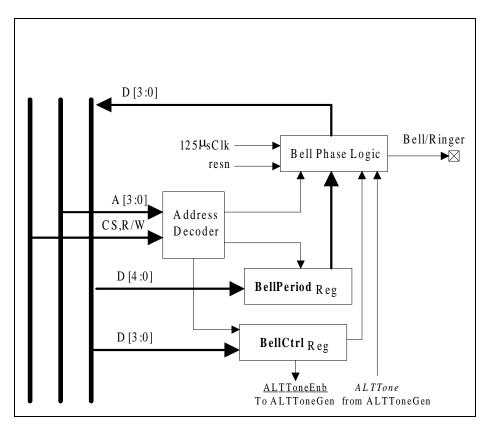

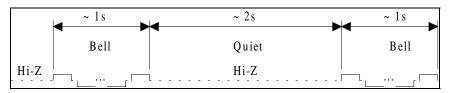

| 20. | PROC | GRAMMABLE TONE GENERATORS                |       |

|     | 20.1 | INTRODUCTION                             |       |

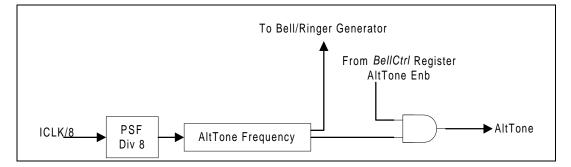

|     | 20.2 | BELL/RINGER GENERATOR                    |       |

|     | 20.3 | TONE GENERATOR                           |       |

| 21. | PWM  | LOGIC                                    |       |

|     | 21.1 | FUNCTIONAL DESCRIPTION                   |       |

|     | 21.2 | REGISTER DESCRIPTION                     | 21-2  |

| 22. | CALL | ING PARTY CONTROL (CPC)                  |       |

|     | 22.1 | REGISTERS DESCRIPTION                    | 22-5  |

| 23. | SSD_ | P80                                      |       |

|     | 23.1 | FUNCTION DESCRIPTION                     |       |

|     | 23.2 | REGISTER DESCRIPTION                     | 23-3  |

|     | 23.3 | FIRMWARE OPERATION                       |       |

| 24. | COU  | ITACH IMAGING DSP BUS SUBSYSTEM          |       |

|     | 24.1 | COUNTACH IMAGING DSP SUBSYSTEM           |       |

|     | 24.2 | COUNTACH IMAGING DSP BUS UNIT            |       |

|     | 24.3 | ARM BUS INTERFACE                        | 24-8  |

|     | 24.4 | COUNTACH IMAGING DSP SUBSYSTEM INTERFACE | 24-11 |

|     | 24.5 | COUNTACH DMA CONTROLLER                  |       |

|     | 24.6 | VIDEO/SCANNER INTERFACE                  |       |

|     | 24.7 | (S)DRAM CONTROLLER ((S)DRAMC)            |       |

|     | 24.8 | REGISTER DESCRIPTION                     |       |

| 25. | CONF | IGURATION                                |       |

|     | 25.1 | HARDWARE VERSION                         |       |

|     | 25.2 | PRODUCT CODE                             |       |

# Figures

| Figure 1-1. MFP System Diagram Using MFC2000                                               | 1-1  |

|--------------------------------------------------------------------------------------------|------|

| Figure 1-2: MFC2000 Function Diagram                                                       | 1-4  |

| Figure 2-1. MFC2000 Organization                                                           |      |

| Figure 3-1. MFC2000 BGA Bottom View                                                        | 3-10 |

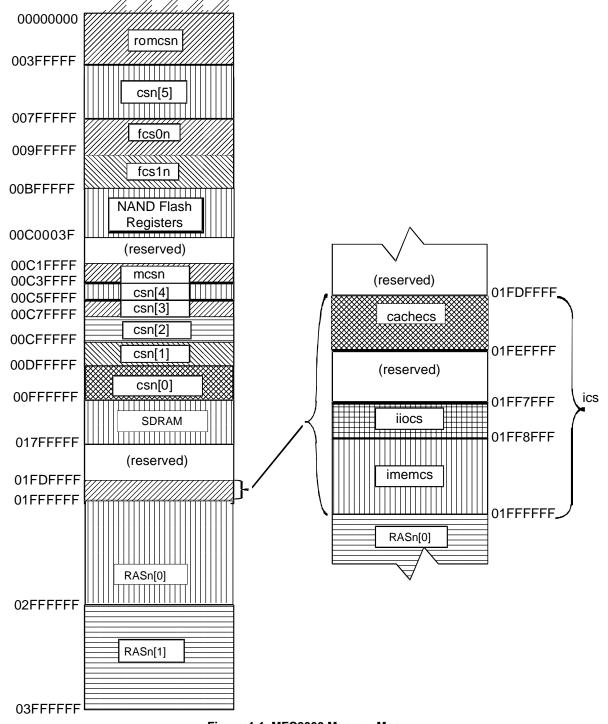

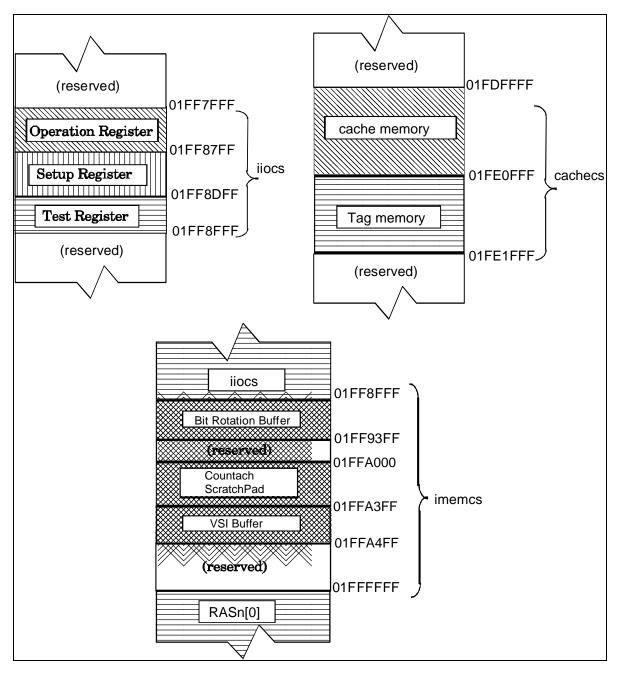

| Figure 4-1. MFC2000 Memory Map                                                             | 4-6  |

| Figure 4-2. MFC2000 Internal Memory Map                                                    | 4-7  |

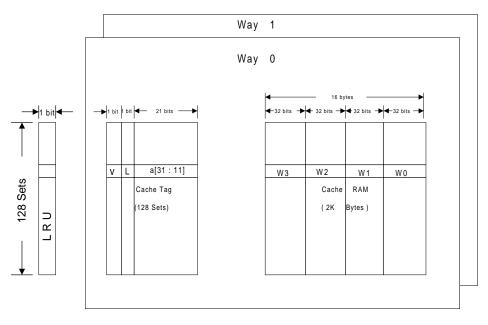

| Figure 4-3. MFC2000 Cache Organization                                                     | 4-19 |

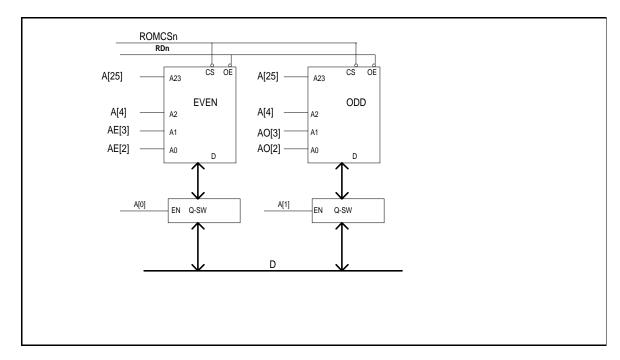

| Figure 4-4. 2-Way Interleave ROM Connection                                                | 4-26 |

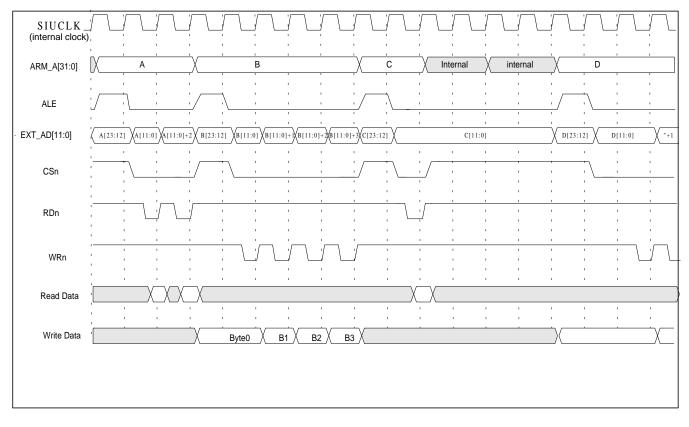

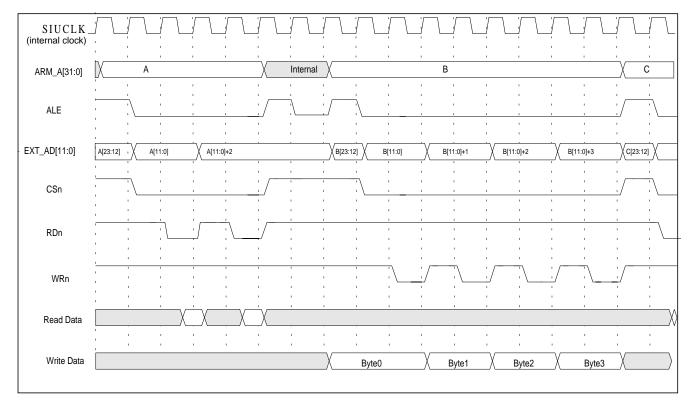

| Figure 4-5. Zero Wait State, Single Access, Normal Read, Normal Write                      | 4-36 |

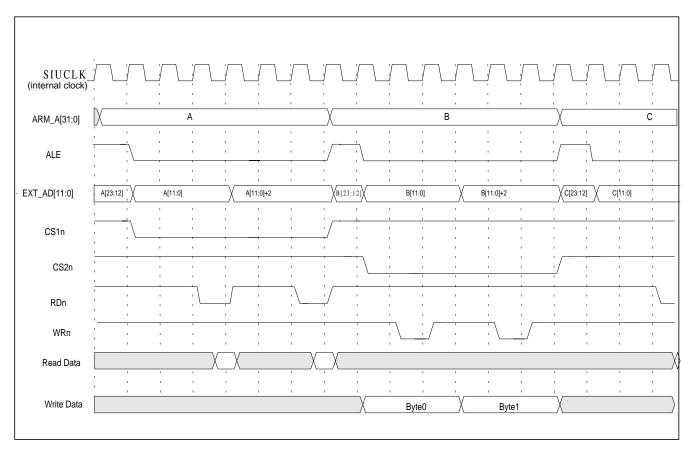

| Figure 4-6. One Wait State, Single Access, One Read, One Write                             | 4-37 |

| Figure 4-7. Two Wait States, Single Access, Read On Delayed (CS1n), Write Early Off (CS2n) | 4-38 |

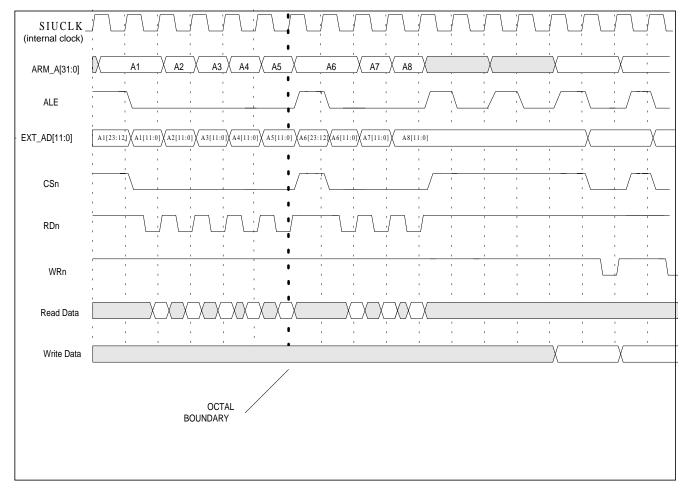

| Figure 4-8. Zero Wait State, Burst Access, Normal Read, Normal Write                       | 4-39 |

| Figure 4-9. Fast Page Mode ROM Access—1,0,0 Read Access Followed by 1,1,1,1, Write Access  | 4-40 |

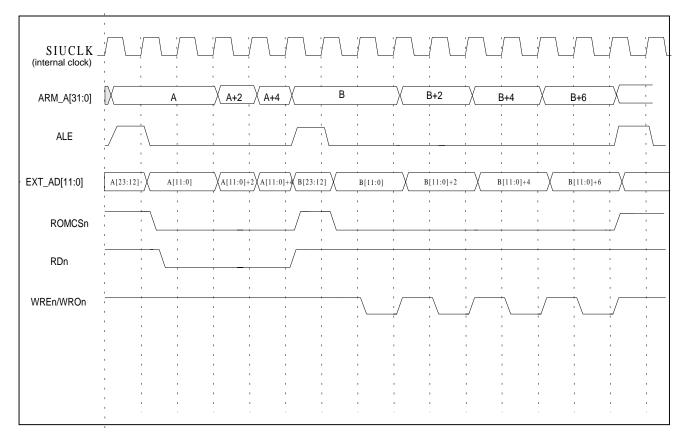

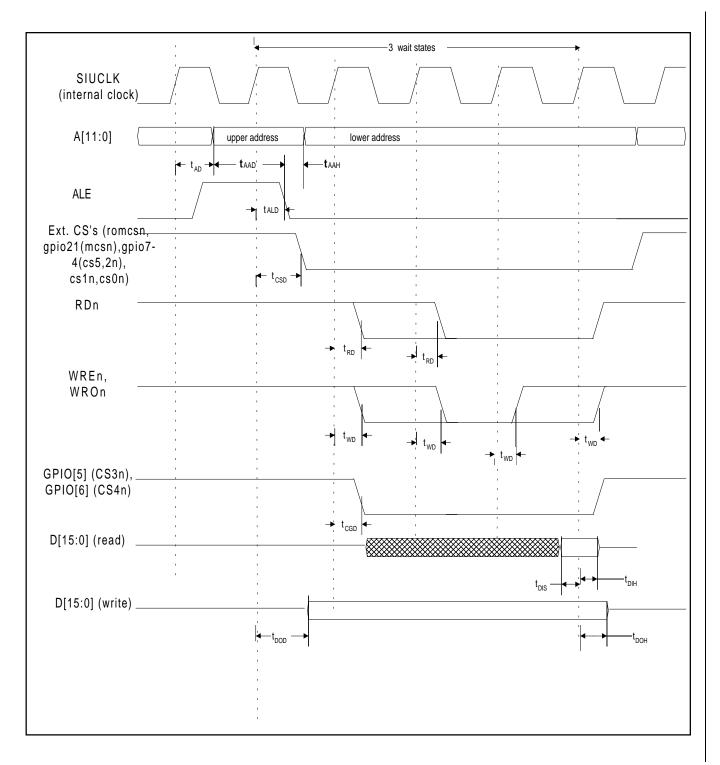

| Figure 4-10. System Bus Timing—Read/Write with Wait States                                 | 4-41 |

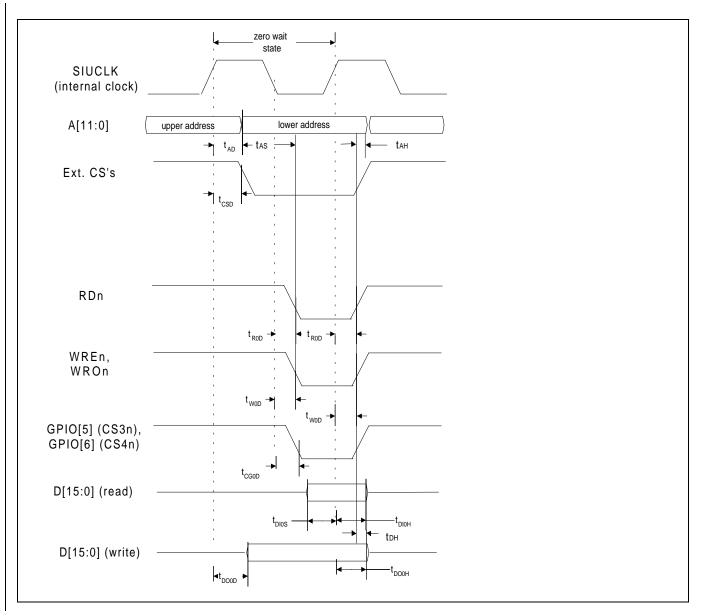

| Figure 4-11. System Bus Timing—Zero-Wait-State Read/Write                                  | 4-42 |

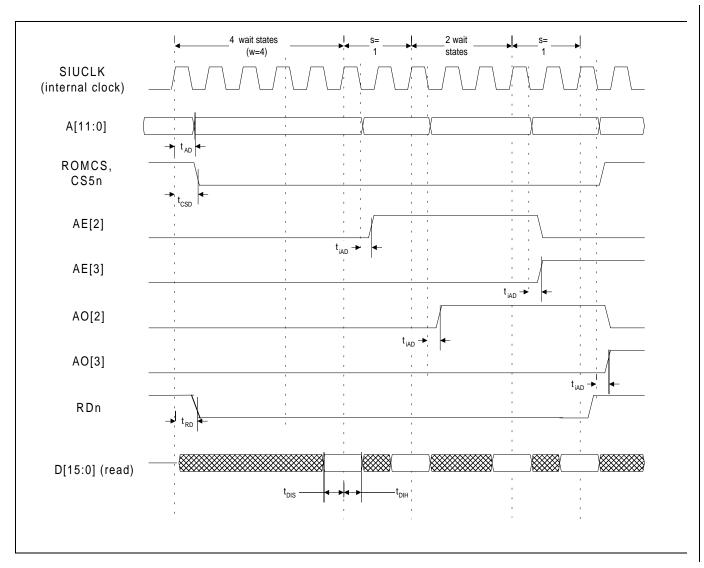

| Figure 4-12. System Bus Timing—2-Way Interleave Read Timing (S = 1)                        | 4-43 |

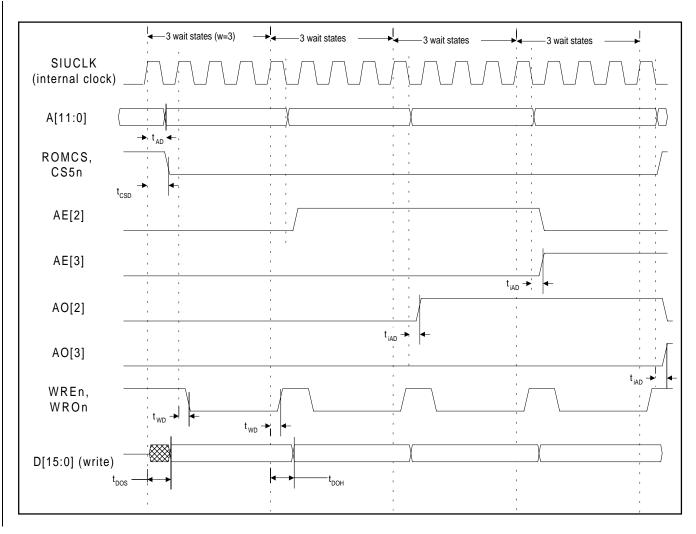

| Figure 4-13. System Bus Timing—2-Way Interleave Write Timing (S = 0 or 1)                  |      |

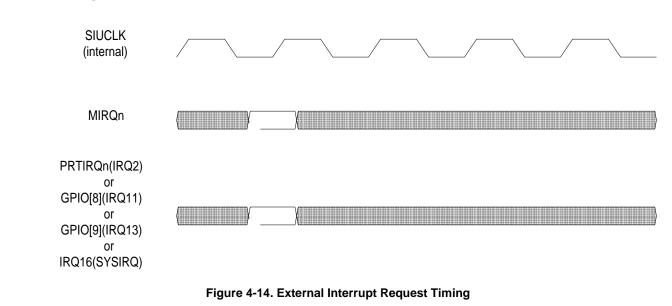

| Figure 4-14. External Interrupt Request Timing                                             | 4-54 |

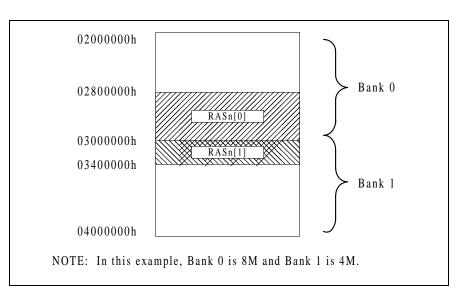

| Figure 4-15. DRAM Bank/Address Map                                                         | 4-56 |

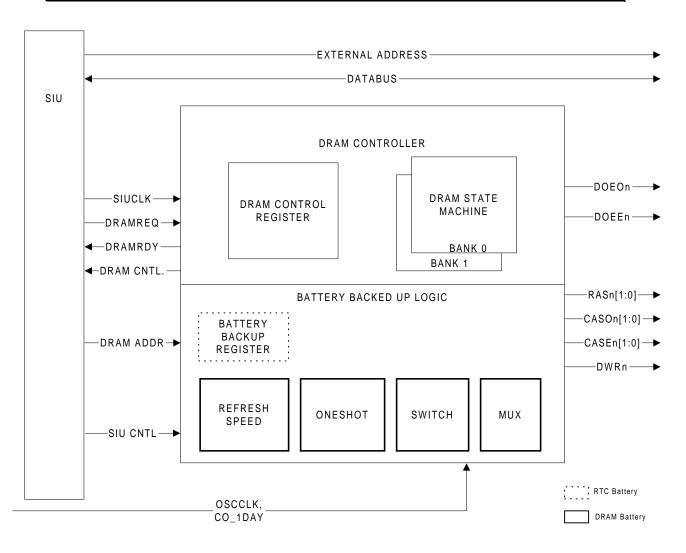

| Figure 4-16. Simplified DRAM Controller Block Diagram                                      | 4-59 |

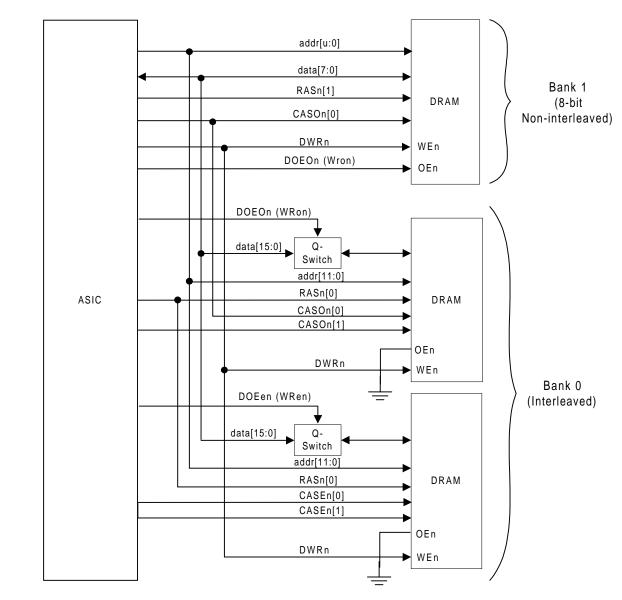

| Figure 4-17. DRAM Interface Example                                                        | 4-60 |

| Figure 4-18. 8-bit Memory Data Bus                                                         | 4-65 |

| Figure 4-19. 16-bit Memory Data Bus                                                        | 4-65 |

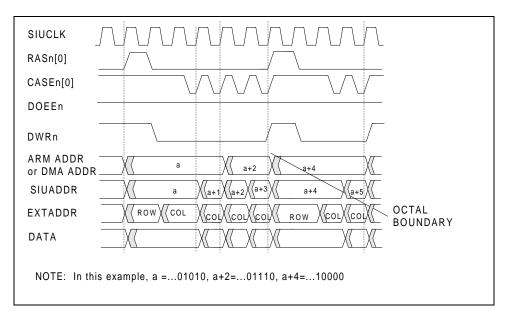

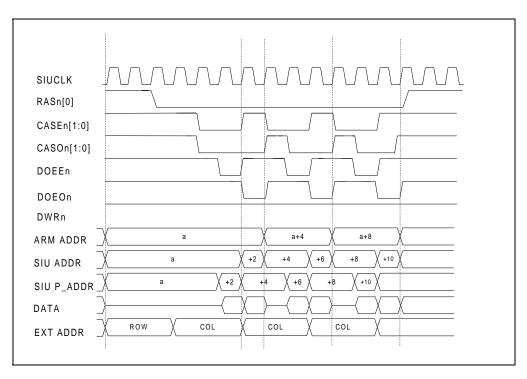

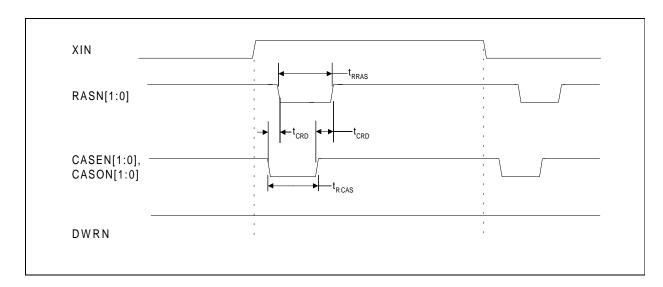

| Figure 4-20. CASn Non-Interleaved 8-bit DRAM Read                                          | 4-66 |

| Figure 4-21. 2-Way Interleaved Memory with Halfword Bursts of Data                         | 4-66 |

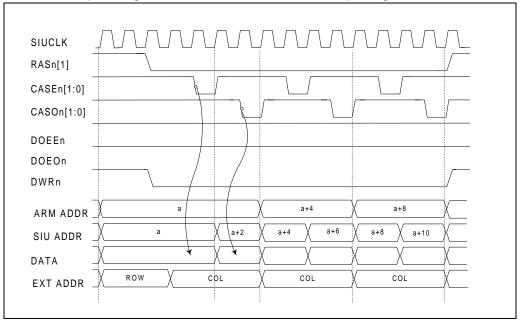

| Figure 4-22. 2-Way Interleaved DRAM Read (3 words)                                         | 4-67 |

| Figure 4-23. 2-Way Interleaved DRAM Write                                                  | 4-67 |

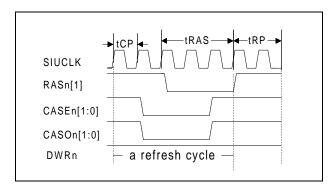

| Figure 4-24. Refresh Cycle                                                                 | 4-68 |

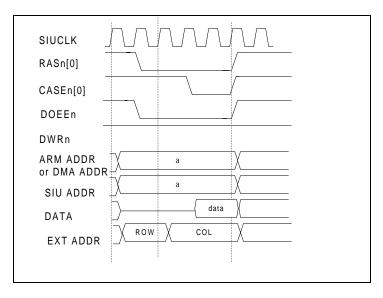

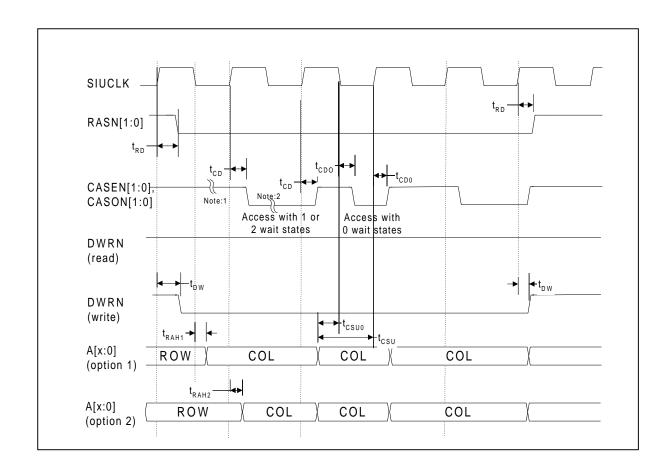

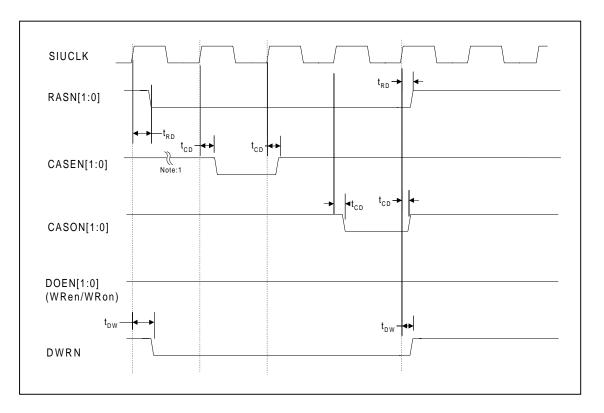

| Figure 4-25. DRAM Timing—Read, Write and Wait States for Non-interleave Mode               | 4-68 |

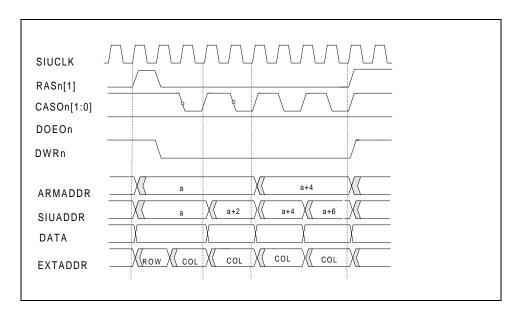

| Figure 4-26. DRAM Timing for 2-way Interleave Write                                        | 4-69 |

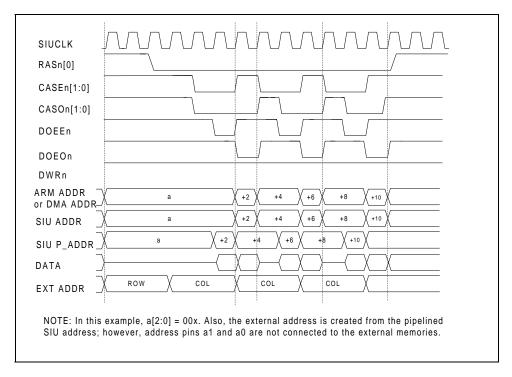

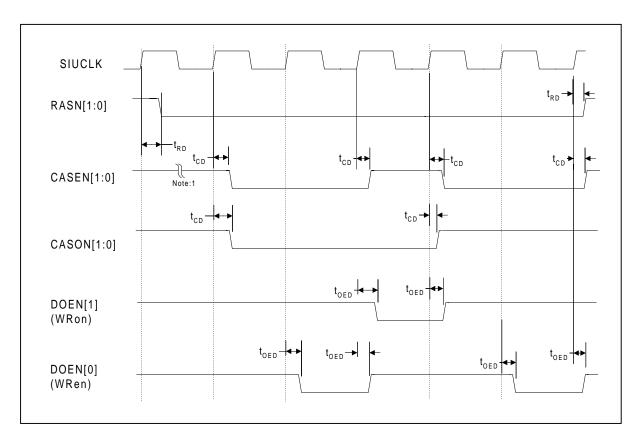

| Figure 4-27. DRAM Timing—Read for 2-way interleave mode                                    | 4-69 |

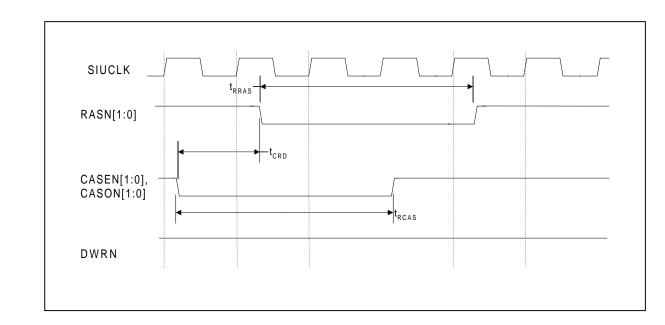

| Figure 4-28. DRAM Refresh Timing                                                           | 4-70 |

| Figure 4-29. DRAM Battery Refresh Timing                                                   | 4-70 |

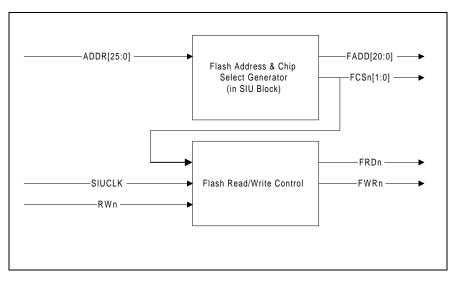

| Figure 4-30. Flash Control Block Diagram                                                   | 4-73 |

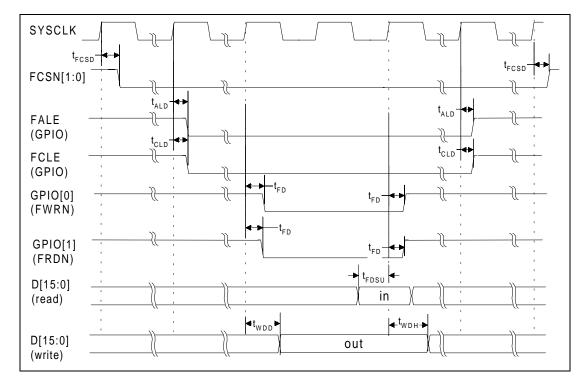

| Figure 4-31. NAND-Type Flash Memory Access with Two Wait States                            | 4-75 |

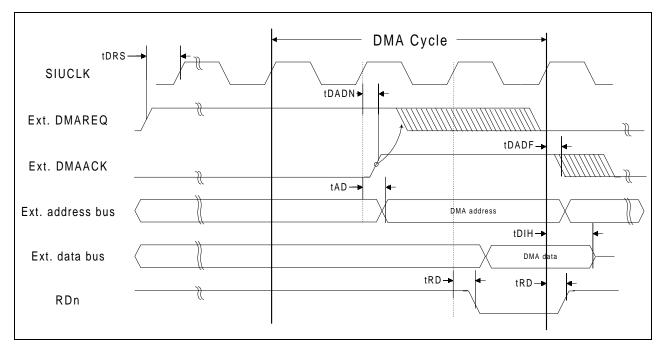

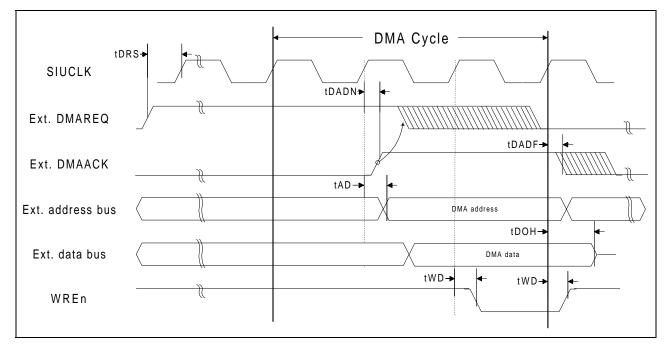

| Figure 4-32: External DMA Read Timing (Single Access, One Wait State)                      | 4-80 |

| Figure 4-33. External DMA Write Timing (Single Access, One Wait State)                     | 4-81 |

| Figure 4-34. USB Logical Channels Block Diagram                                            | 4-82 |

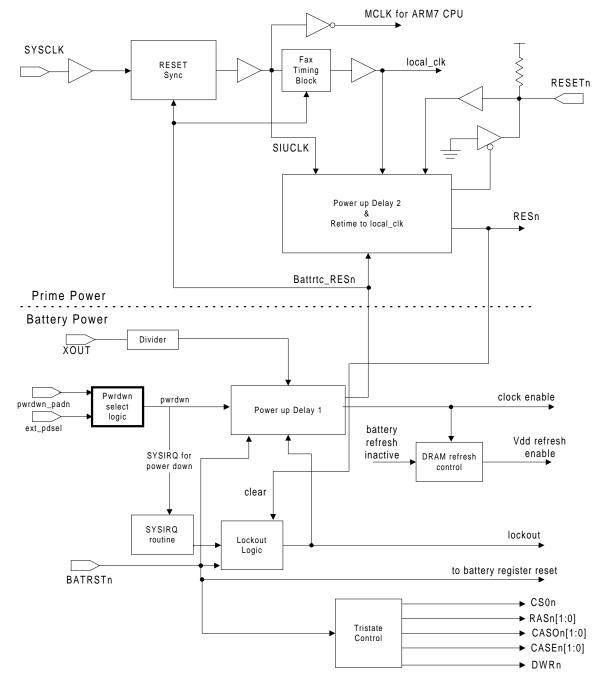

| Figure 5-1. Power Reset Block Diagram                                                      |      |

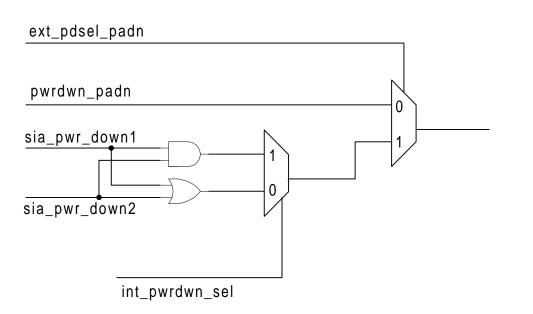

| Figure 5-2. Power-down Select Logic                               | 5-3  |

|-------------------------------------------------------------------|------|

| Figure 5-3. Power Reset Timing Diagram                            |      |

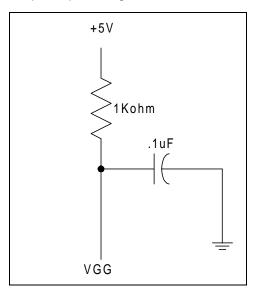

| Figure 5-4. +5v Prime Power Signal and VGG                        |      |

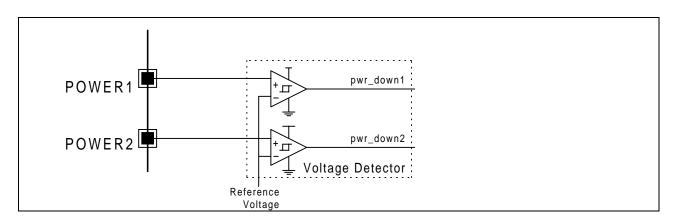

| Figure 5-5. Internal Power Detection                              | 5-10 |

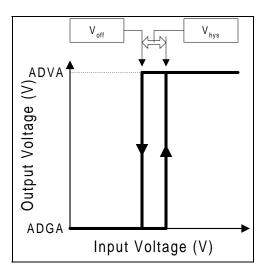

| Figure 5-6. Figure Caption Required                               | 5-10 |

| Figure 5-7. Voltage Divider Circuit                               |      |

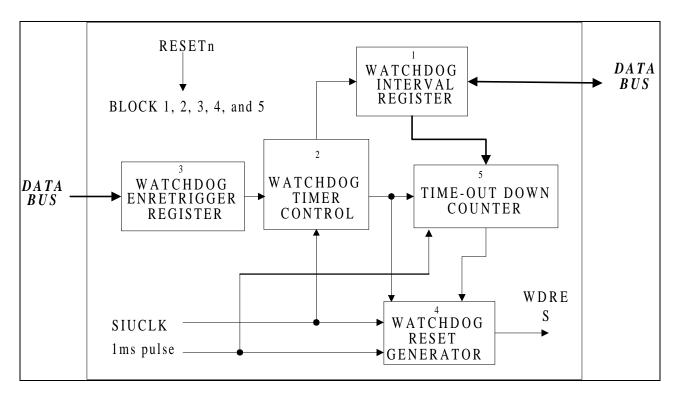

| Figure 5-8. Watchdog Timer Block Diagram                          |      |

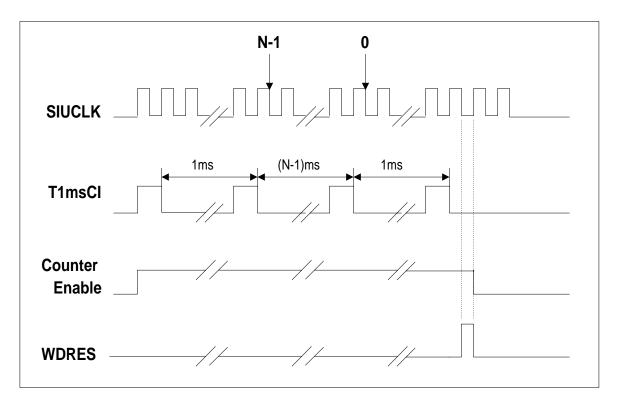

| Figure 5-9. Watchdog Time-Out Timing Diagram                      | 5-13 |

| Figure 6-1. Fax Timing Control Logic Block Diagram                |      |

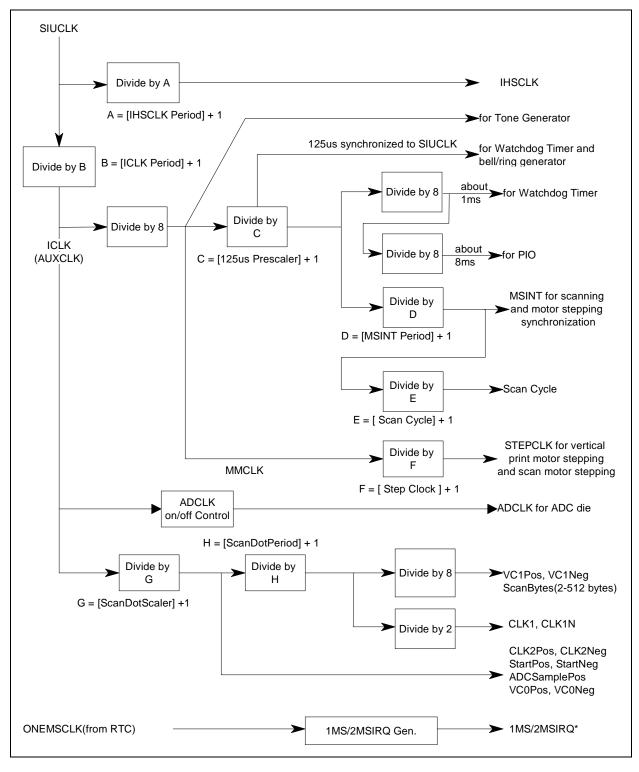

| Figure 6-2. MFC2000 Timing Chain                                  | 6-3  |

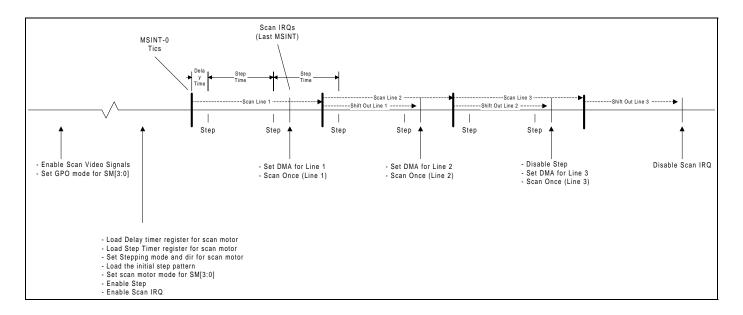

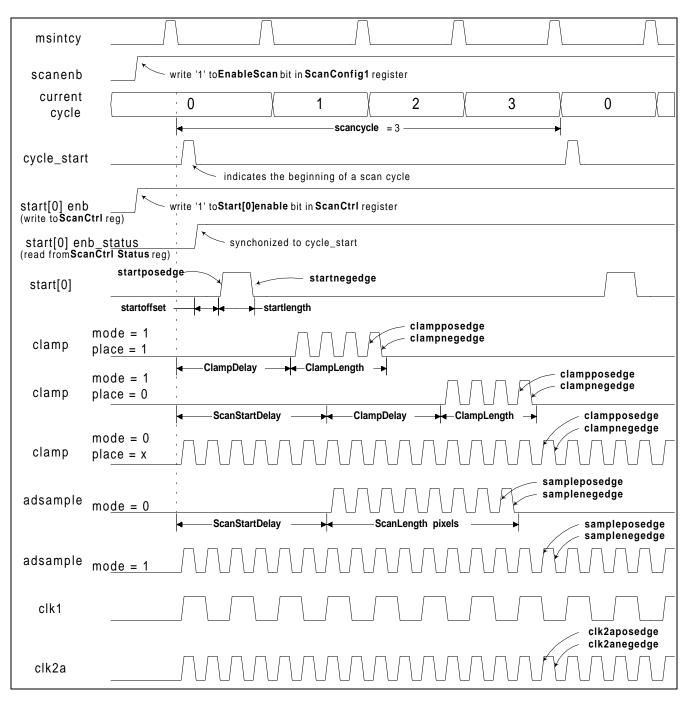

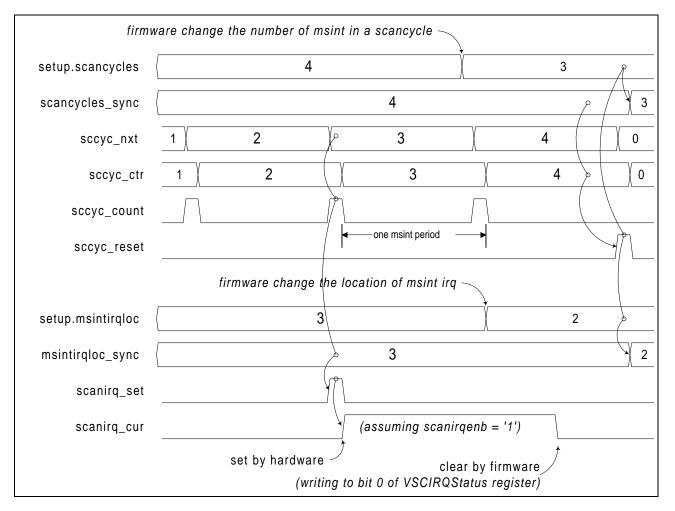

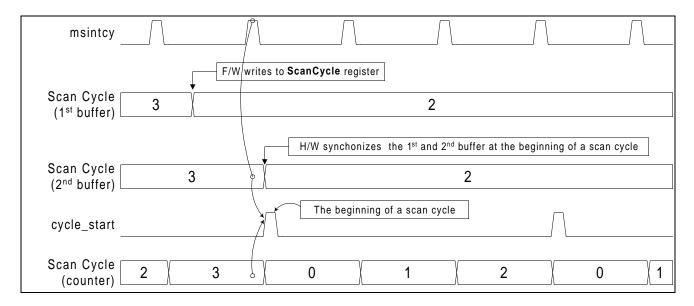

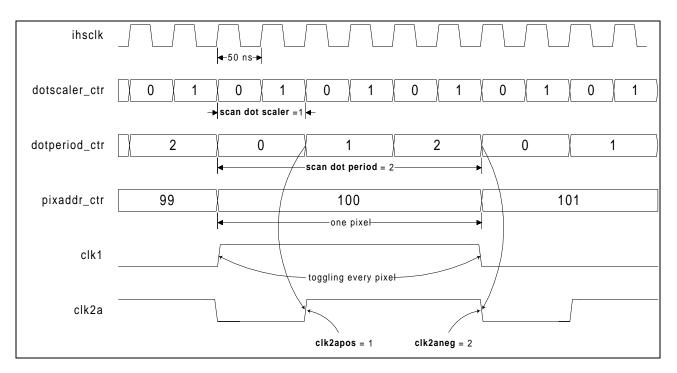

| Figure 6-3. Scan Control Timing                                   |      |

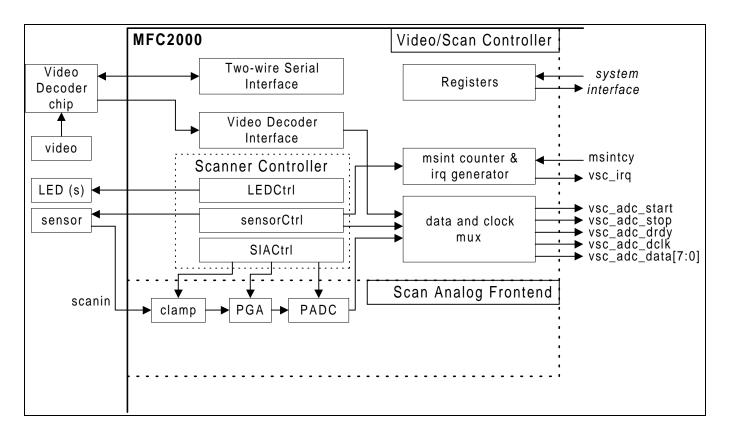

| Figure 7-1. Video/Scanner Controller Block Diagram                |      |

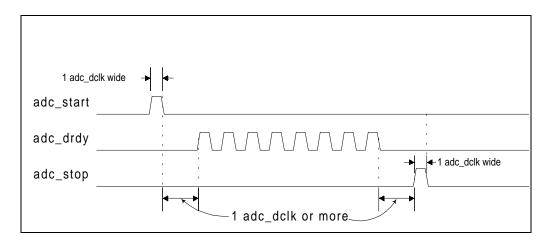

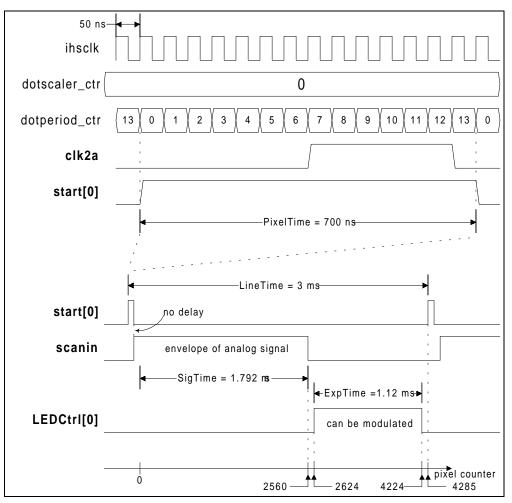

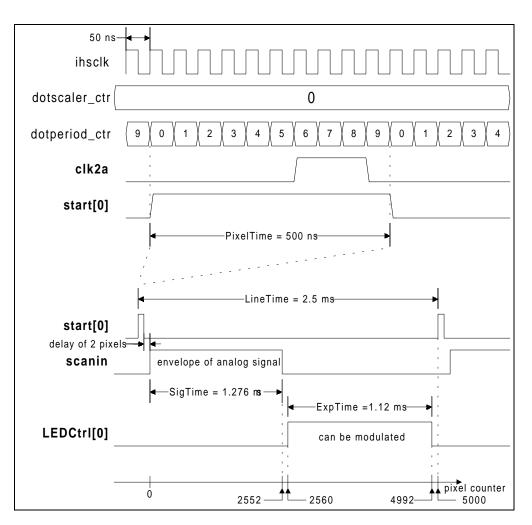

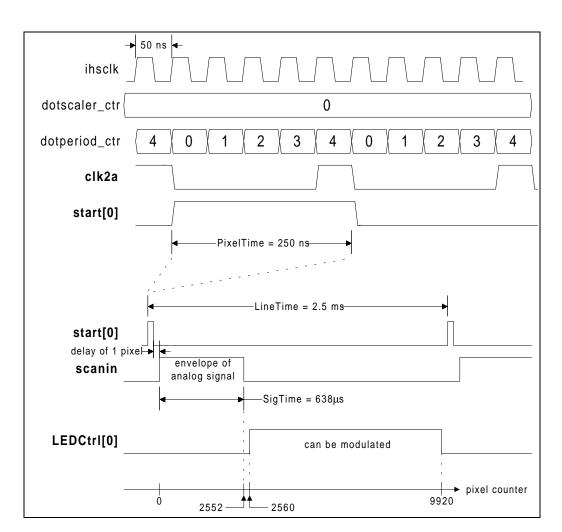

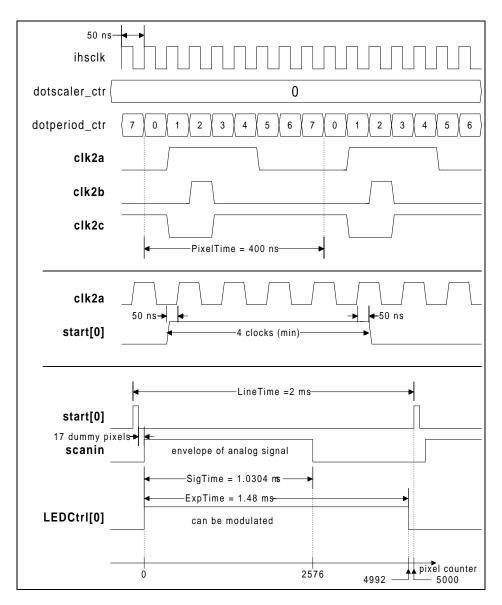

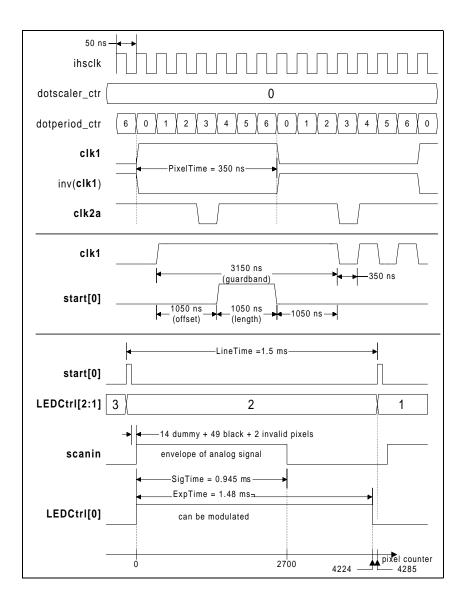

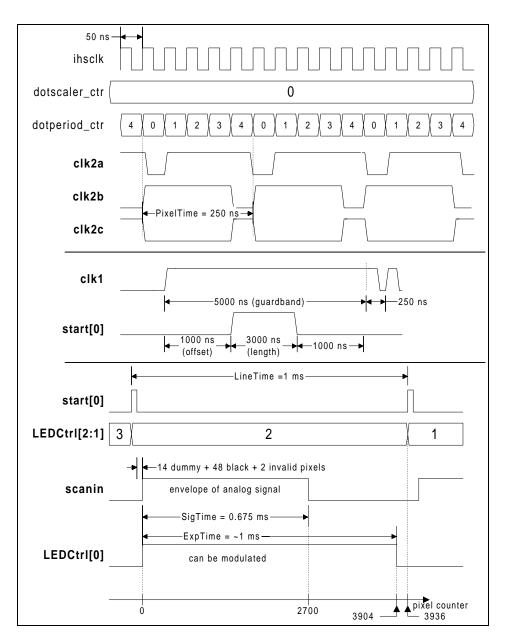

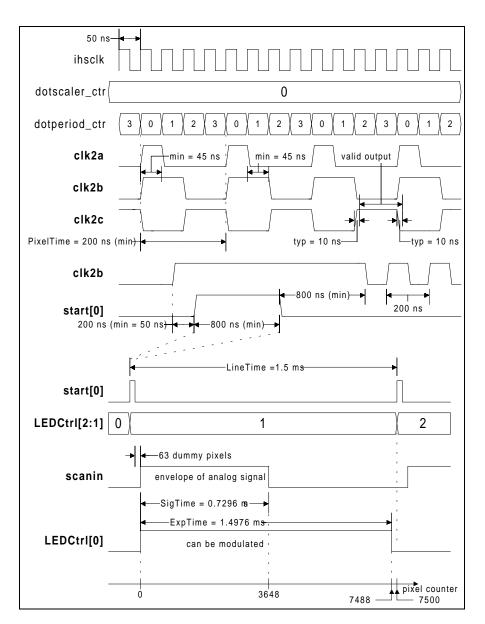

| Figure 7-2. Untitled Timing Diagram                               |      |

| Figure 7-3. Untitled Timing Diagram                               |      |

| Figure 7-4. Untitled Timing Diagram                               |      |

| Figure 7-5. Untitled Timing Diagram                               |      |

| Figure 7-6. Untitled Timing Diagram                               |      |

| Figure 7-7. Untitled Timing Diagram                               |      |

| Figure 7-8. Untitled Timing Diagram                               |      |

| Figure 7-9. Untitled Timing Diagram                               |      |

| Figure 7-10. Untitled Timing Diagram                              |      |

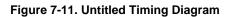

| Figure 7-11. Untitled Timing Diagram                              |      |

| Figure 7-12. Untitled Timing Diagram                              |      |

| Figure 7-13. Untitled Timing Diagram                              |      |

| Figure 7-14. Untitled Timing Diagram                              |      |

| Figure 7-15. Untitled Timing Diagram                              |      |

| Figure 7-16. Untitled Timing Diagram                              |      |

| Figure 7-17. Untitled Timing Diagram                              |      |

| Figure 7-18. Untitled Timing Diagram                              |      |

| Figure 7-19. Untitled Timing Diagram                              |      |

| Figure 7-20. Untitled Timing Diagram                              |      |

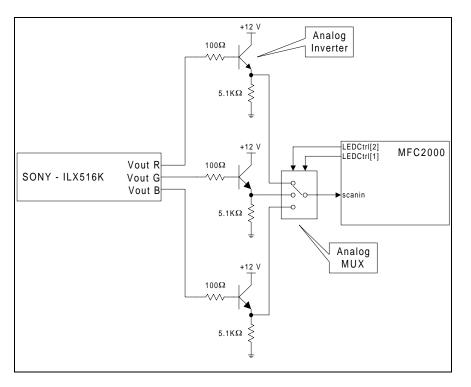

| Figure 7-21. External circuit required for SONY–ILX516K interface |      |

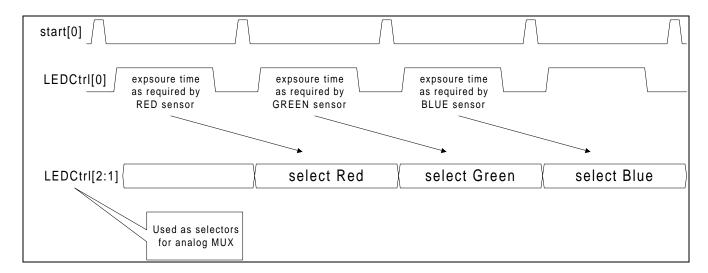

| Figure 7-22. LED timing for SONY–ILX516K                          |      |

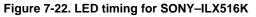

| Figure 7-23. Serial Programming Interface, Physical Connection    |      |

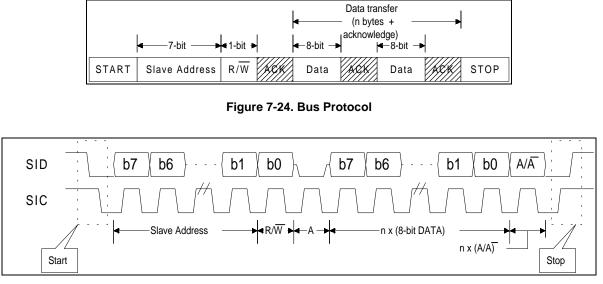

| Figure 7-24. Bus Protocol                                         |      |

| Figure 7-25. Serial Programming Interface, Timing Diagram         |      |

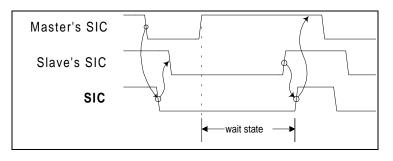

| Figure 7-26. Stretching the Low Period of the Clock               |      |

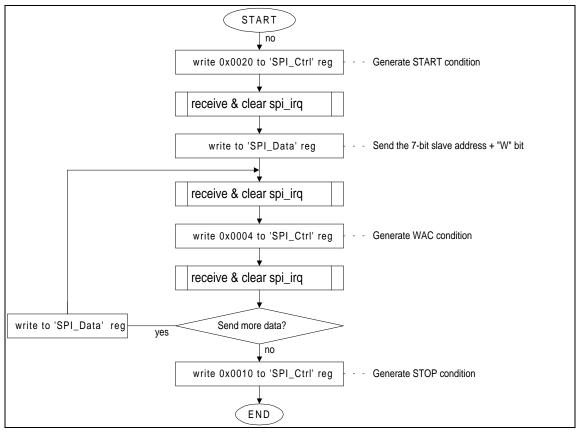

| Figure 7-27. Firmware Operation—Transmission                      |      |

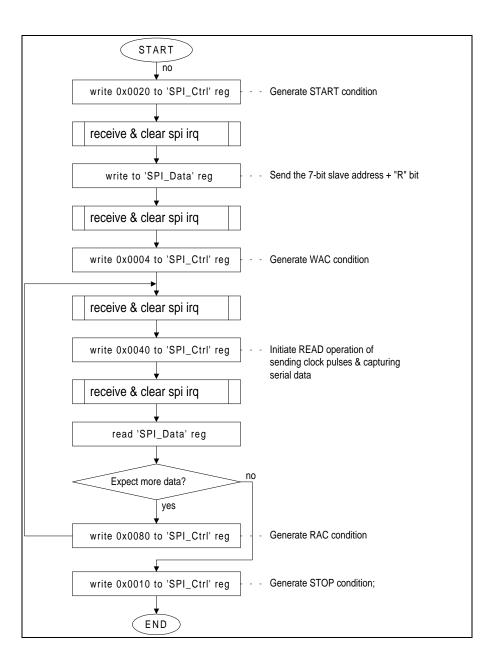

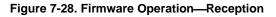

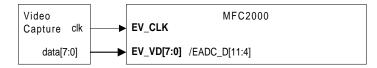

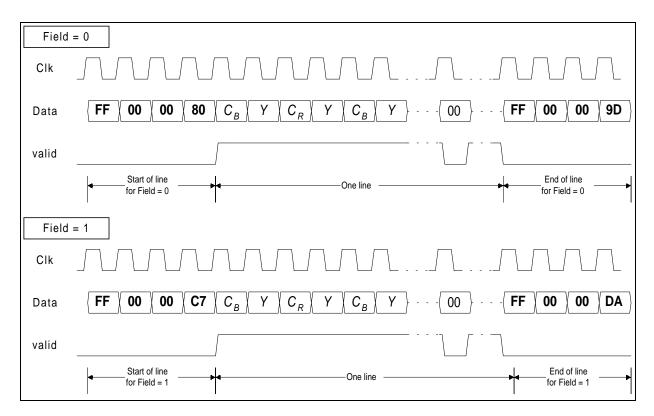

| Figure 7-28. Firmware Operation—Reception                         |      |

| Figure 7-29. Connection to External Video Capture Device          |      |

| Figure 7-30. Untitled Timing Diagram                              |      |

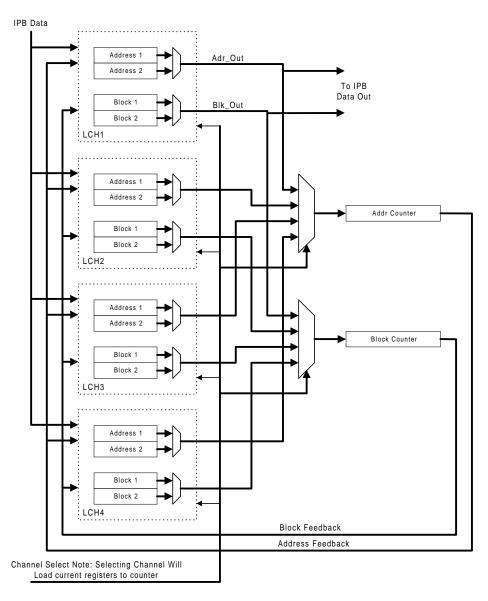

| Figure 7-31. DMA Operation                                                                            | 7-55  |

|-------------------------------------------------------------------------------------------------------|-------|

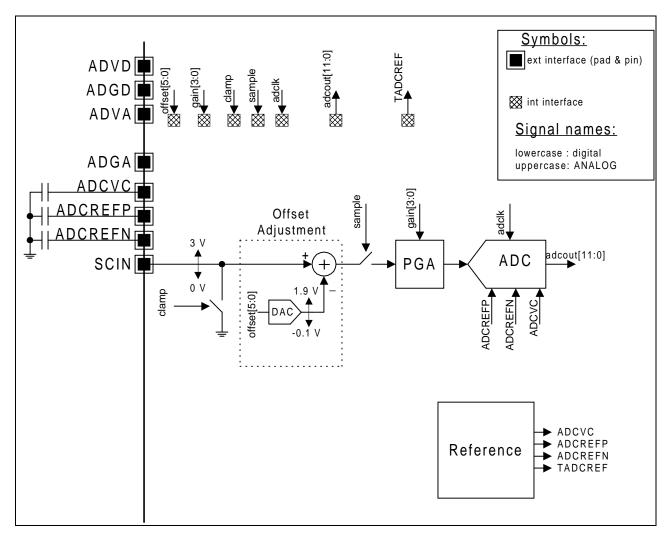

| Figure 8-1. Untitled Figure                                                                           | 8-1   |

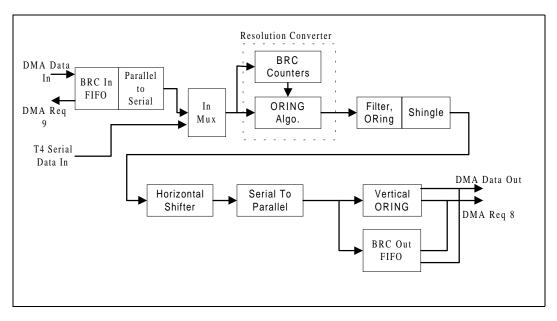

| Figure 9-1: Bi-level Resolution Conversion Block Diagram                                              | 9-2   |

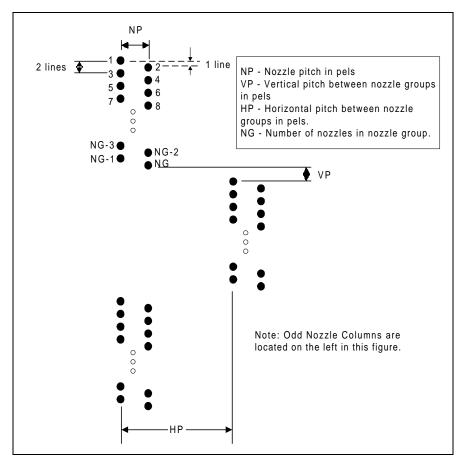

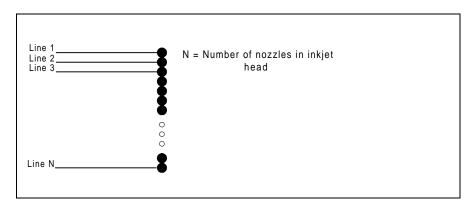

| Figure 9-2. The Physical Nozzle Diagram for Typical Inkjet Heads                                      | 9-5   |

| Figure 9-3. Untitled Figure                                                                           | 9-5   |

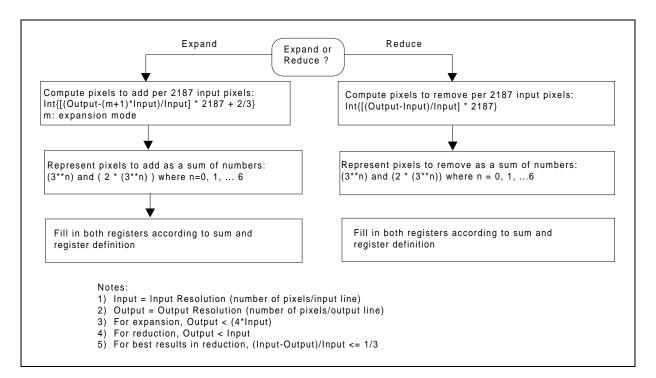

| Figure 9-4: Resolution Conversion Programming                                                         | 9-15  |

| Figure 10-1. Print ASIC Interface                                                                     | 10-2  |

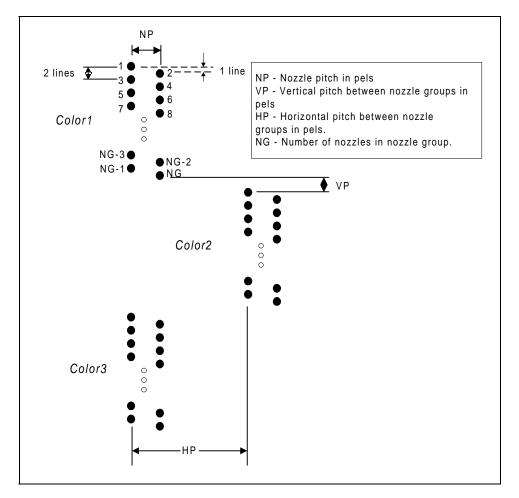

| Figure 11-1. Nozzle Diagram of a Typical Programmable Inkjet Head                                     | 11-1  |

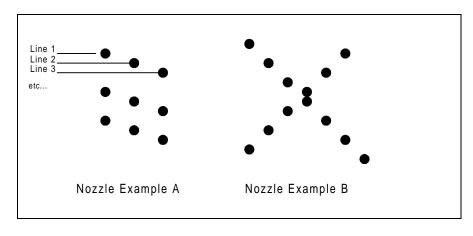

| Figure 11-2. Examples of Nozzle Head Configurations                                                   | 11-2  |

| Figure 11-3. Nozzle Configuration by Bit Rotation Block (Regardless of Physical Nozzle Configuration) | 11-2  |

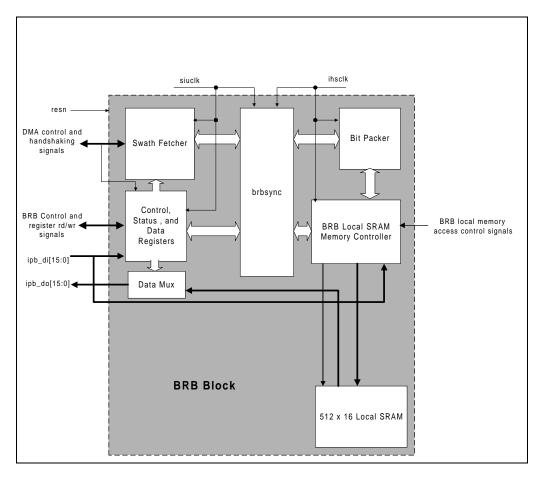

| Figure 11-4. MFC2000 Bit Rotation Block Diagram                                                       | 11-3  |

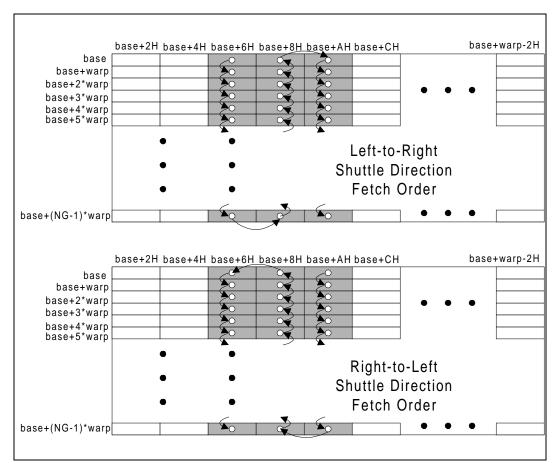

| Figure 11-5. Fetcher DMA Channel Fetch Order                                                          | 11-4  |

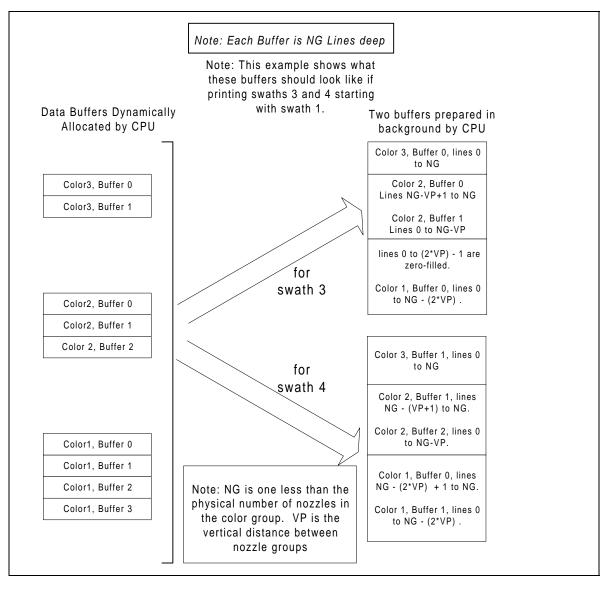

| Figure 11-6. CPU Background Print Data Preparation                                                    | 11-12 |

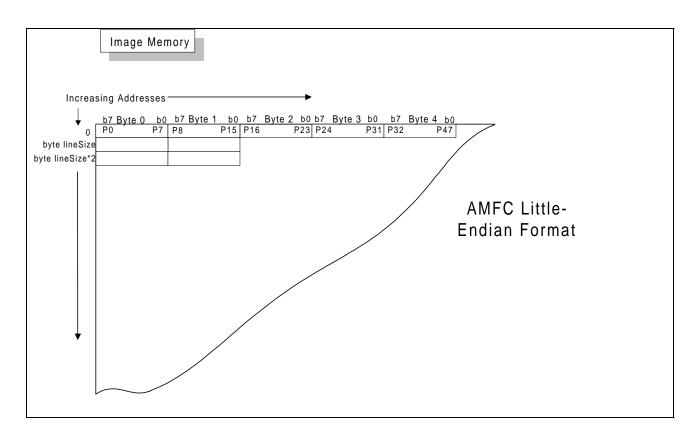

| Figure 11-7. MFC2000 Little-Endian Format                                                             | 11-13 |

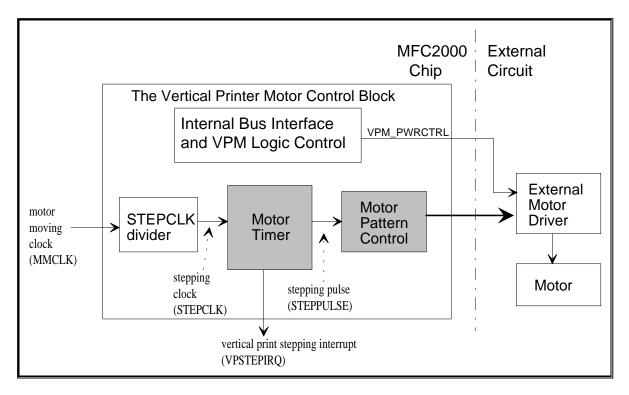

| Figure 12-1. Vertical Printer Motor Control Block Diagram                                             | 12-1  |

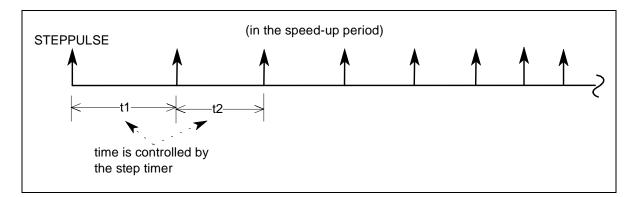

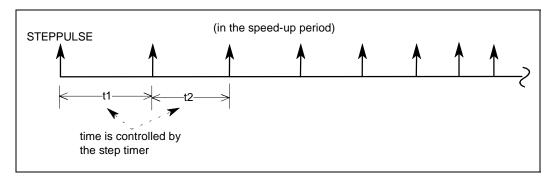

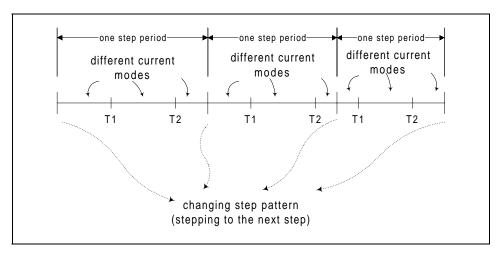

| Figure 12-2. Stepping Timing                                                                          | 12-2  |

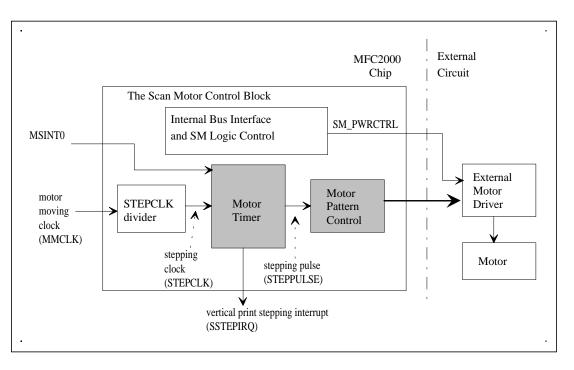

| Figure 12-3. Scan Motor Control Diagram                                                               | 12-5  |

| Figure 12-4. Stepping Timing                                                                          | 12-7  |

| Figure 12-5: Current Control Diagram                                                                  | 12-9  |

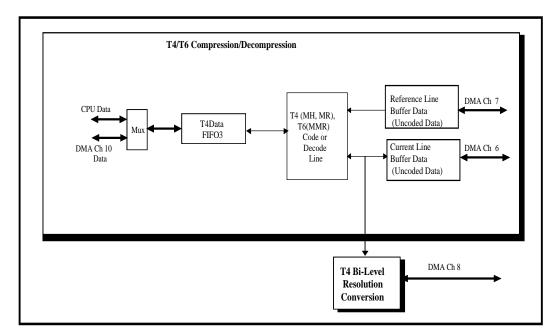

| Figure 14-1. Data Flow for Compression/Decompression                                                  | 14-1  |

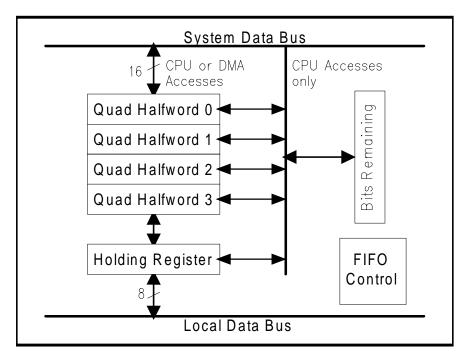

| Figure 14-2. Compressor/Decompressor FIFO Structure                                                   | 14-2  |

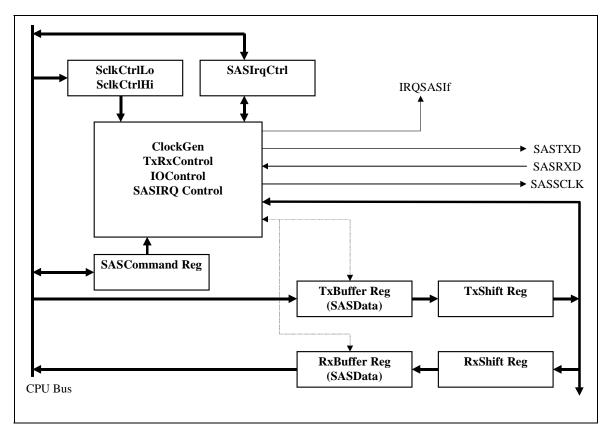

| Figure 15-1. SASIF Block Diagram                                                                      | 15-2  |

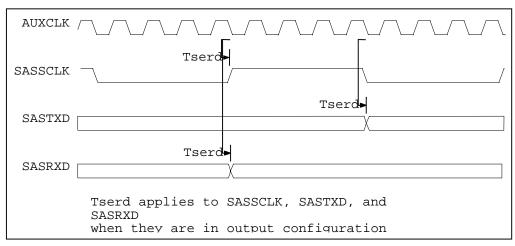

| Figure 15-2. SASSCLK Timing Diagram                                                                   | 15-12 |

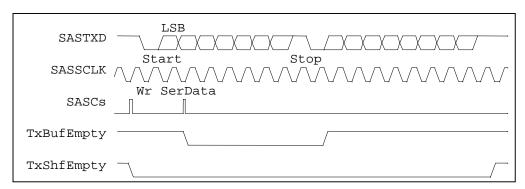

| Figure 15-3. Synchronous Mode Timing                                                                  | 15-13 |

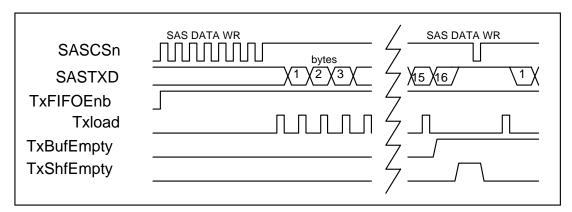

| Figure 15-4. Asynchronous Transmitter Timing                                                          | 15-14 |

| Figure 17-1. Parallel Port Interface Controller Block Diagram                                         | 17-3  |

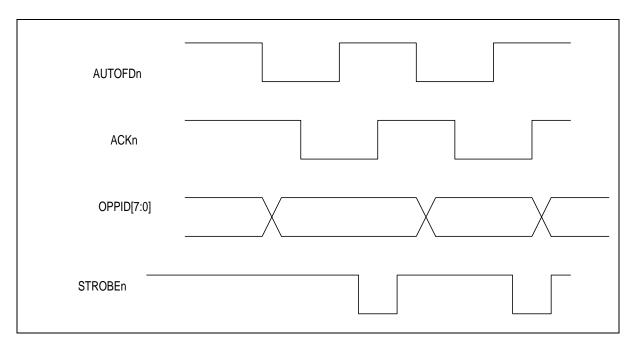

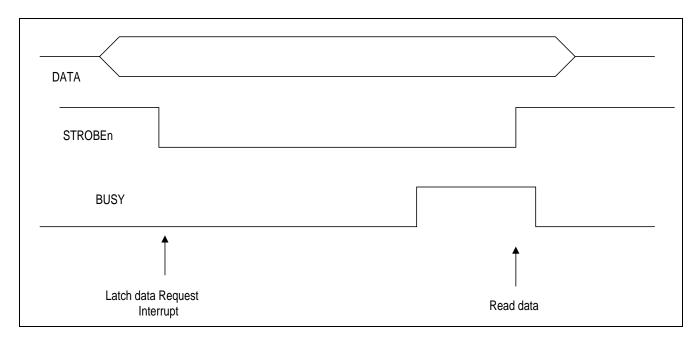

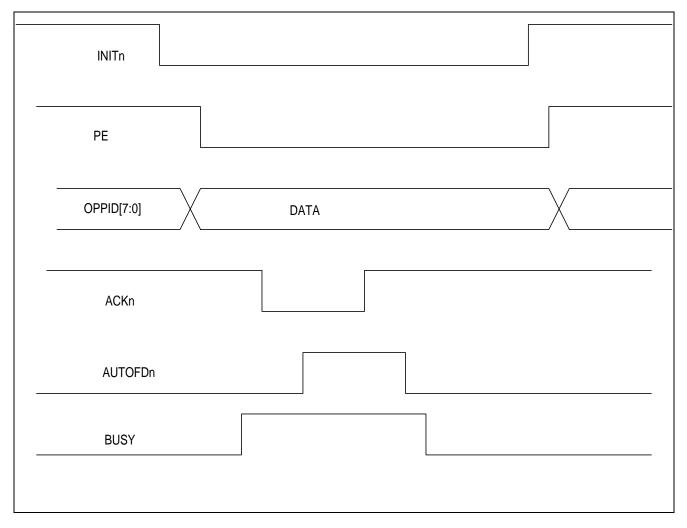

| Figure 17-2. Compatibility Mode Timing Diagram                                                        | 17-16 |

| Figure 17-3. Nibble Mode Data Transfer Cycle                                                          | 17-17 |

| Figure 17-4. BYTE Mode Data Transfer Cycle                                                            | 17-18 |

| Figure 17-5. ECP Mode Timing Diagram                                                                  | 17-19 |

| Figure 17-6. Reverse ECP Transfer Timing                                                              | 17-20 |

| Figure 17-7. Error Cycle Timing Diagram                                                               | 17-21 |

| Figure 18-1. RTC Block Diagram                                                                        | 18-1  |

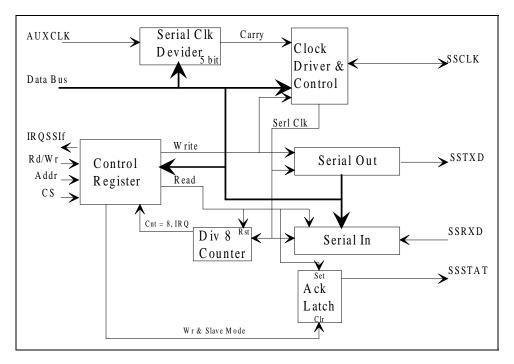

| Figure 19-1. SSIF Block Diagram                                                                       | 19-1  |

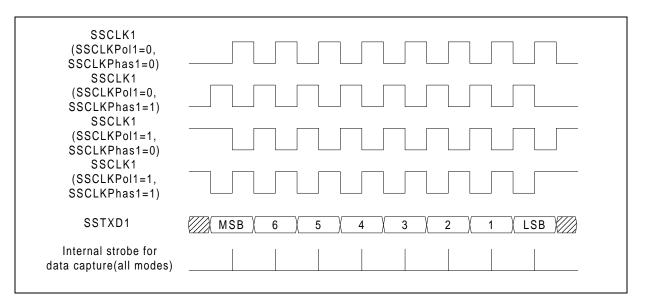

| Figure 19-2. SSCLK1 Diagram                                                                           | 19-3  |

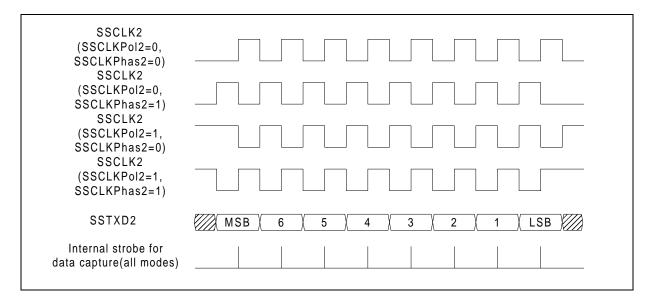

| Figure 19-3. SSCLK2 Diagram                                                                           | 19-6  |

| Figure 19-4. Timing Diagram                                                                           | 19-8  |

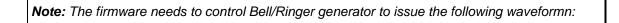

| Figure 20-1. Bell/Ringer Timing                                                                       | 20-1  |

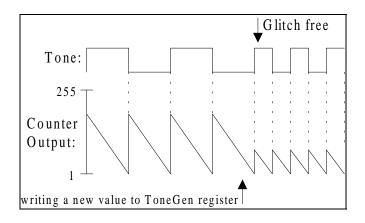

| Figure 20-2. Bell/Ringer Block Diagram                                                                | 20-2  |

| Figure 20-3. Bell/Ringer Generator Waveform                                                           | 20-3  |

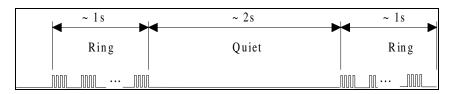

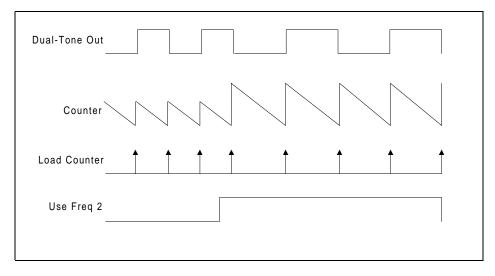

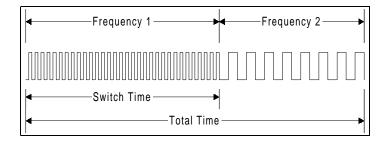

| Figure 20-4. Tone Generator Frequency Change                                                          | 20-6  |

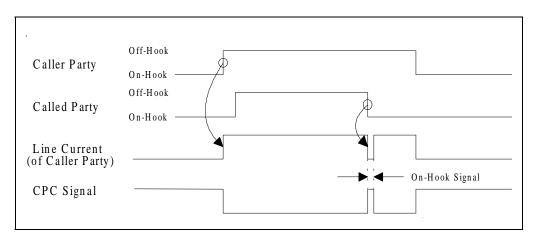

| Figure 22-1: CPC Signal                            | 22-1  |

|----------------------------------------------------|-------|

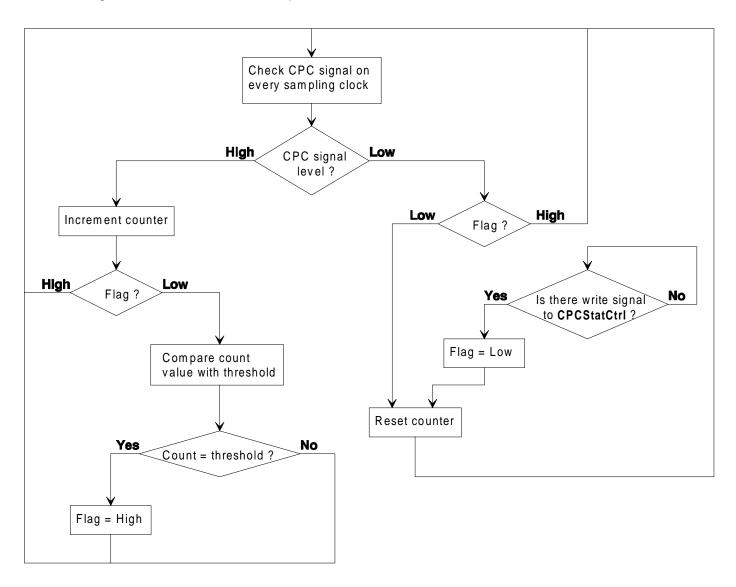

| Figure 22-2. CPC Operation Flowchart               | 22-2  |

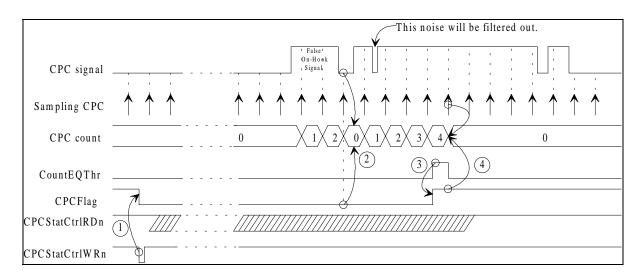

| Figure 22-3: CPC Operation (with CPCThreshold = 4) | 22-3  |

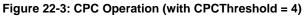

| Figure 22-4: CPC Block Diagram                     | 22-4  |

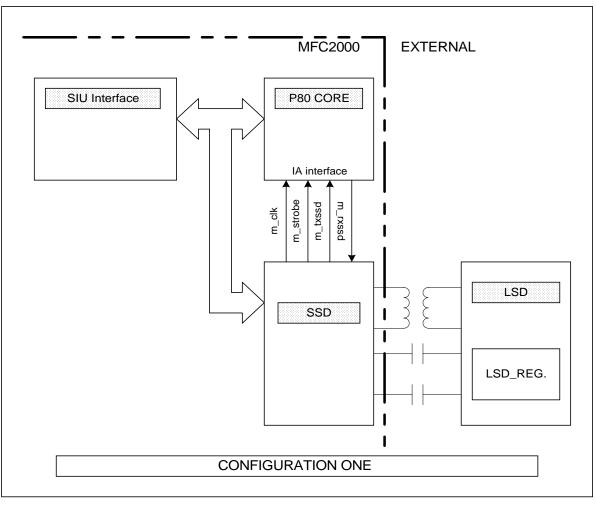

| Figure 23-1. System Configuration One              | 23-1  |

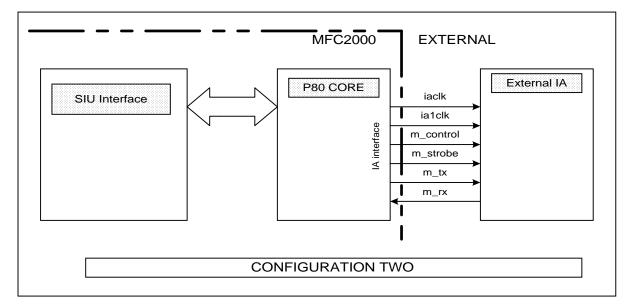

| Figure 23-2. System Configuration Two              | 23-2  |

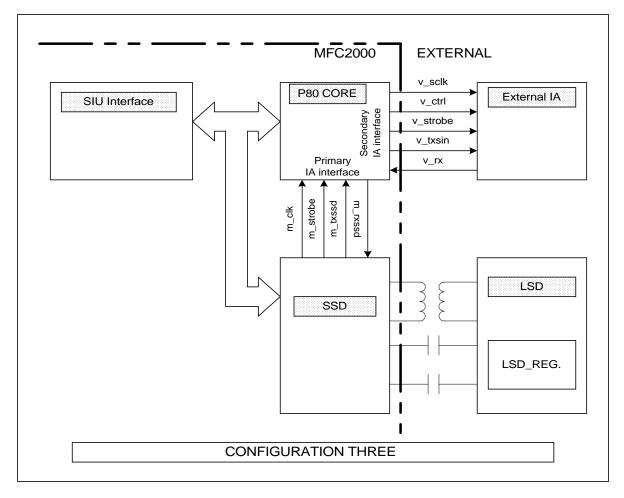

| Figure 23-3. System Configuration Three            | 23-2  |

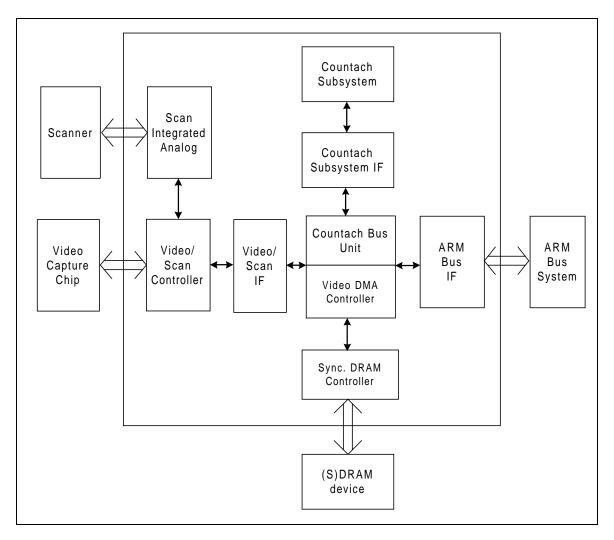

| Figure 24-1. The ARM Bus System Block Diagram      |       |

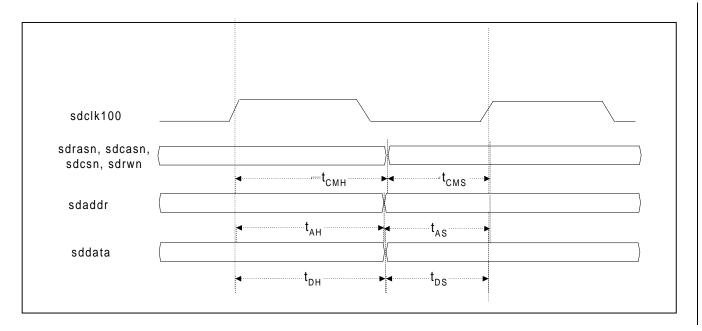

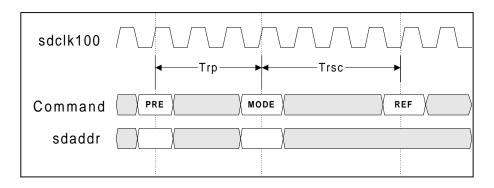

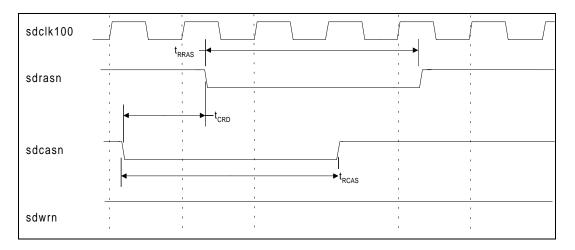

| Figure 24-2. SDRAM Setup and Hold Timing           | 24-29 |

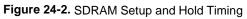

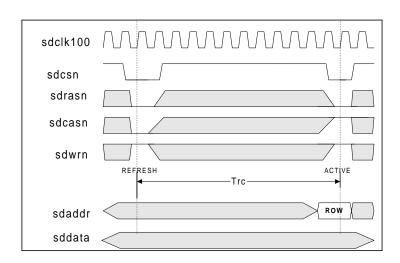

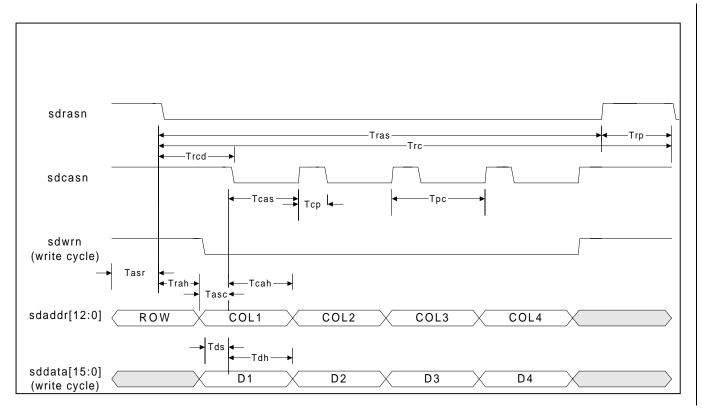

| Figure 24-3. SDRAM Read or Write Timing            | 24-30 |

| Figure 24-4. SDRAM Mode Timing                     | 24-30 |

| Figure 24-5. SDRAM Refresh Timing                  | 24-30 |

| Figure 24-6. FPDRAM Timing (Read or Write)         | 24-31 |

| Figure 24-7. FPDRAM Timing (Refresh)               | 24-33 |

# Tables

| Table 1-1. Reference Documentation                                     |  |

|------------------------------------------------------------------------|--|

| Table 2-1. MFC2000 Device Family                                       |  |

| Table 3-1. Pin Description (1 of 6)                                    |  |

| Table 3-2. Maximum Ratings                                             |  |

| Table 3-3. Digital Input Characteristics                               |  |

| Table 3-4. Output Characteristics                                      |  |

| Table 3-5. Power Supply Requirements                                   |  |

| Table 3-6. Battery Power Supply Current Requirements                   |  |

| Table 4-1. Fixed-Location and Size Chip Selects                        |  |

| Table 4-2. Operation Register Map (1 of 9)                             |  |

| Table 4-3. Setup Registers (1 of 2)                                    |  |

| Table 4-4. Cache Tag Data Format (for Test Mode Read/Write Operation)  |  |

| Table 4-5. Access Modes for Reading ROM                                |  |

| Table 4-6. Read Operation (Internal Peripheral Gets Data From Memory)  |  |

| Table 4-7. Write Operation (Internal Peripheral Puts Data Into Memory) |  |

| Table 4-8. Read/Write with Wait States Timing Parameters               |  |

| Table 4-9. MFC2000 Interrupt and Reset Signals                         |  |

| Table 4-10. Programmable Resolution of Timer1 and Timer2               |  |

| Table 4-11. DRAM Wait State Configurations                             |  |

| Table 4-12. Address Multiplexing—Part 1                                |  |

| Table 4-13. Address Multiplexing—Part 2                                |  |

| Table 4-14. DRAM Row/Column Configuration                              |  |

| Table 4-15. DRAM Timing Parameters                                     |  |

| Table 4-16. Feature Matrix                                             |  |

| Table 4-17. DMA Channel Functions and Characteristics                  |  |

| Table 4-18 DMA Channel 3 Control Bit Sssignment                        |  |

| Table 6-1. Operation Mode Frequencies                                  |  |

| Table 7-1. Register setup for Rohm–IA3008–ZE22                         |  |

| Table 7-2. Register setup for Dyna–DL507–07UAH                         |  |

| Table 7-3. Register setup for Mitsubishi-GT3R216                       |  |

| Table 7-4. Register Setup for Toshiba–CIPS218MC300                     |  |

| Table 7-5. Register Setup for NEC – $\mu$ PD3724                       |  |

| Table 7-6. Register setup for NEC – $\mu$ PD3794                       |  |

| Table 7-7. Register Setup for SONY – ILX516K                           |  |

| Table 8-1. Untitled Table                                              |  |

| Table 8-2. Untitled Table                                              |  |

| Table 8-3. Offset Adjustment on DAC                                    |  |

| Table 8-4. Programmable Gain Amplifier (PGA)                           |  |

| Table 8-5. Pipelined ADC (PADC)                                        |  |

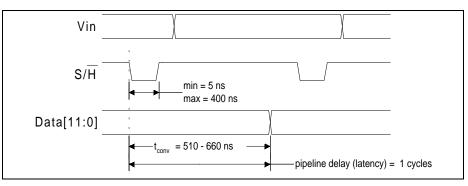

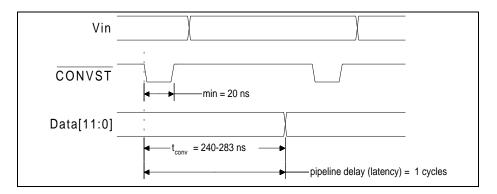

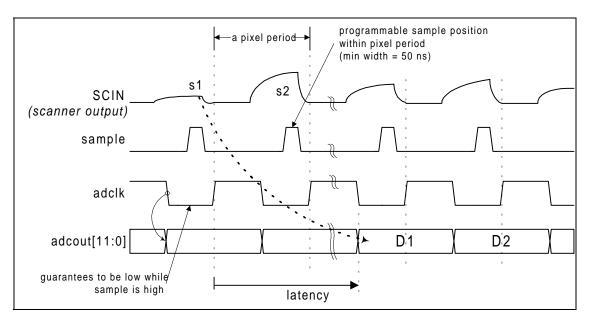

| Table 8-6. PADC Timing Diagram                                 | 8-4   |

|----------------------------------------------------------------|-------|

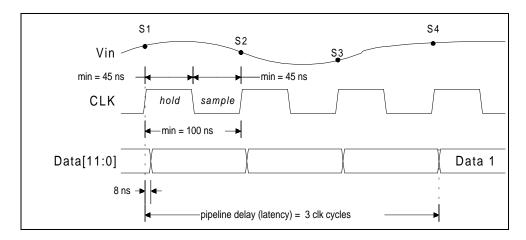

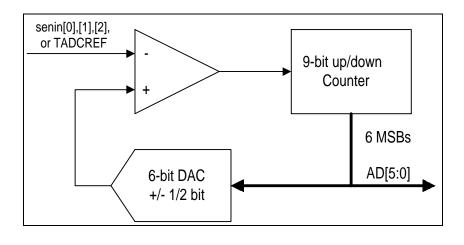

| Table 8-7. TADC Block Diagram                                  | 8-5   |

| Table 9-1. Untitled Table                                      |       |

| Table 9-2: Procedure to determine Pixels to remove             |       |

| Table 9-3: Resolution Conversion Examples                      |       |

| Table 12-1. Full Step/Single Phase Excitation                  | 12-3  |

| Table 12-2. Full Step/Two Phase Excitation                     | 12-3  |

| Table 12-3. Half-Step Excitation                               | 12-3  |

| Table 12-4. Full Step/Single Phase Excitation                  | 12-7  |

| Table 12-5. Full Step/Two Phase Excitation                     | 12-7  |

| Table 12-6. Half-Step Excitation                               | 12-8  |

| Table 18-1. RTC Crystal Specifications for 32.768 kHz          | 18-4  |

| Table 20-1. Bell/Ringer Setting                                | 20-2  |

| Table 23-1. SSD Registers                                      |       |

| Table 23-2. P80 CORE Registers                                 | 23-5  |

| Table 24-1. Needs a title                                      |       |

| Table 24-2. DMA Channels: Functionality and Priorities         |       |

| Table 24-3. DMA Parameters Scratch Pad Addresses               | 24-13 |

| Table 24-4: Supported FPDRAM Chip Characteristics              |       |

| Table 24-5: Supported SDRAM Chip Characteristics               |       |

| Table 24-6. Untitled table                                     | 24-25 |

| Table 24-7. Untitled table                                     |       |

| Table 24-8. Untitled table                                     |       |

| Table 24-9. SDRAM Setup and Hold Timing                        | 24-29 |

| Table 24-10. Timing Parameters for 16-bit SDRAM Read and Write | 24-31 |

| Table 24-11. Timing Parameters for 8-bit SDRAM Read and Write  | 24-31 |

| Table 24-12. 60ns Timing                                       |       |

| Table 24-13. 50ns Timing                                       |       |

| Table 24-14. FPDRAM Timing (Refresh)                           | 24-33 |

This page is intentionally blank

# 1. Introduction

### 1.1 Scope

This document defines and describes all hardware functions of the MFC2000 chip. The MFC2000 design is based on the MFC1000 design with many minor modifications/enhancements. It has several new key functions to accomplish the following:

- Support a full color MFP

- Enhance connectivity to the PC

- Provide an internal Fax Modem

- Connect to external Conexant video chips

# 1.2 System Overview

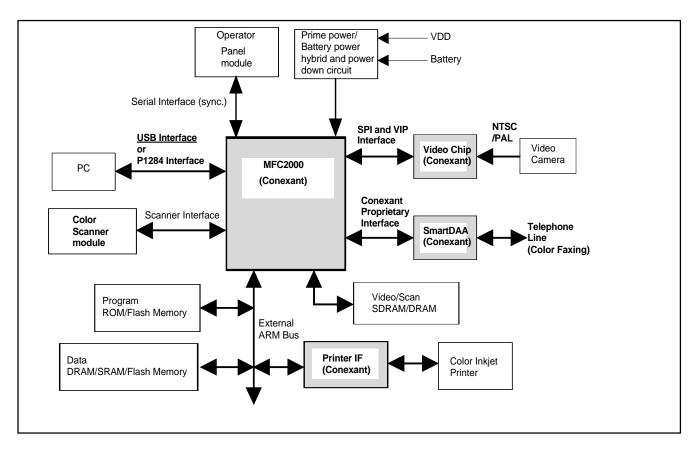

The Conexant Multi-Functional Peripheral Controller 2000 (MFC2000) device set hardware, core code, application code, and evaluation system comprise a full color Multi-Functional Peripheral (MFP) system-needing only a power supply, scanner, printer mechanism, and paper path components to complete the machine. The standard device set hardware includes Conexant's MFC2000 chip, Conexant's SmartDAA or IA chip, and a Printer Interface chip. Optionally, a Conexant video chip with VIP interface can be used to support the video capture function. If V.17 or V.34 faxing without voice is required, the internal V.17/V.34 Fax Modem in the MFC2000 chip is used and the MFC2000 is connected to the external Conexant SmartDAA or IA chip. If the voice/speech function is required, the external Voice Fax Modem device from Conexant will be needed. Any other external interface device can be supported by using the external ARM for CPU and DMA accesses or by using the internal serial interface. An MFP system-level block diagram using the MFC 2000 is illustrated in Figure 1-1.

Figure 1-1. MFP System Diagram Using MFC2000

### 1.2.1 Integrated Full Color MFP Controller (MFC2000)

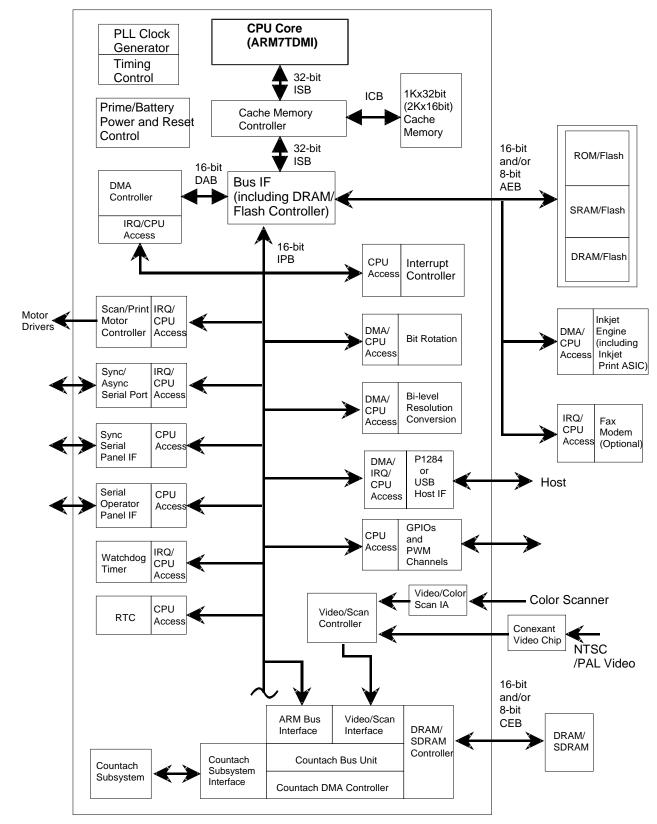

The MFC2000 provides the majority of the electronics necessary to build a color scan and color inkjet printer based MFP whose electronics are integrated into a one-chip solution including one CPU (ARM7TDMI) and two DSPs (Countach Imaging DSP subsystem and P80 core).

Full printer and copier functionality is provided by the following:

- 1284 parallel port interface

- USB serial port interface

- Color scanner interface/controller

- Countach Imaging DSP subsystem for video/scan/compression process

- Flash memory controller

- SDRAM/DRAM controllers

- Resolution conversion logic

- Inkjet data formatter

- External inkjet printing

In addition, the MFC2000 performs facsimile control/monitoring, compression/decompression, and 33.6 Kbps Fax Modem functions (P80 core). The MFC2000 interfaces with major MFP machine components like external modems, SmartDAA, external Fax IA, motors, sensors, external video chip, and operator control panel. The ARM7TDMI-embedded processor provides an external 48-MB direct memory access capability. An integrated 12-bit Pipeline ADC (PADC) and countach subsystem (DSP subsystem, combined with an advanced Conexant proprietary color image processing algorithm, provides state of the art image processing performance on any type of images, including text/half-tone and color images.

The full color MFP Engine provides the hardware and software necessary to develop a full-color Multifunctional Peripheral including an architecture for color printing, color faxing, color scanning, video capturing, and color copying. It also supports many of these operations concurrently.

#### 1.2.1.1 Printing

The MFC2000 Controller supports color inkjet printing. Print speed throughput capabilities are inversely proportional to resolution and also depend on the external printer interface. For host printing, the host sends the image data with the print resolution; the MFC2000 performs no resolution conversion. If host printing and faxing need to be performed for the same image, the printing image data must be sent to the MFP. The MFC2000 converts the printing image data to the faxing image data locally and then faxes it out. An external printer interface chip is designed to support inkjet print mechanism/head subsystems. Different external printer interface chips can be designed and used to support other inkjet mechanisms and heads according to customer requirements.

#### 1.2.1.2 Faxing

Both host-based color faxing and standalone color faxing are supported in addition to monochrome faxing. Hostbased faxing can take place by using a Class One connection via the USB serial port or the P1284 parallel port. For host faxing, the host sends the image data with the fax resolution; the MFC2000 performs no resolution conversion. For standalone faxing, the resolution conversion is supported by the MFC2000. The standalone color scan-to-fax function is supported using the advanced Conexant proprietary color image processing technology:

- Shading correction

- Gamma correction

- Pixel-based dark-level correction

- Color/monochrome image processing

- Color conversion

- JPEG

- Multi-level resolution conversion.

#### 1.2.1.3 Scanning

For the color scan-to-PC function, up to 8 bits of scan data per pixel can be sent to the host. JPEG compression can be used to reduce the PC upload speed.

#### 1.2.1.4 Copying

The MFC2000 and associated firmware supports several modes of copying including standard, fine, superfine, and photo. Multiple copies of a single image can be made with a single pass. The standalone color/monochrome copy function is supported by using MFC2000's Inkjet print formatter, the external printer interface, and the advanced Conexant proprietary color image processing system.

#### 1.2.2 MFC2000 Evaluation System

The Conexant MFC2000 Evaluation System provides demonstration, prototype development, and evaluation capabilities to full color MFP developers using the MFC2000 Engine device set. The MFC2000 Evaluation system provides flexibility for visibility and access, i.e., plug-on board for the modem, sockets for programmable parts, and connectors for an emulator (refer to Figure 1-2). Jumper options and test points are provided throughout the MFC2000 evaluation Main Board. The MFC2000 Evaluation System is the most convenient environment for the developer needing to experiment with the several interfaces encountered in the full color MFP, for example, color printer functions.

#### 1.2.3 New Function Highlights

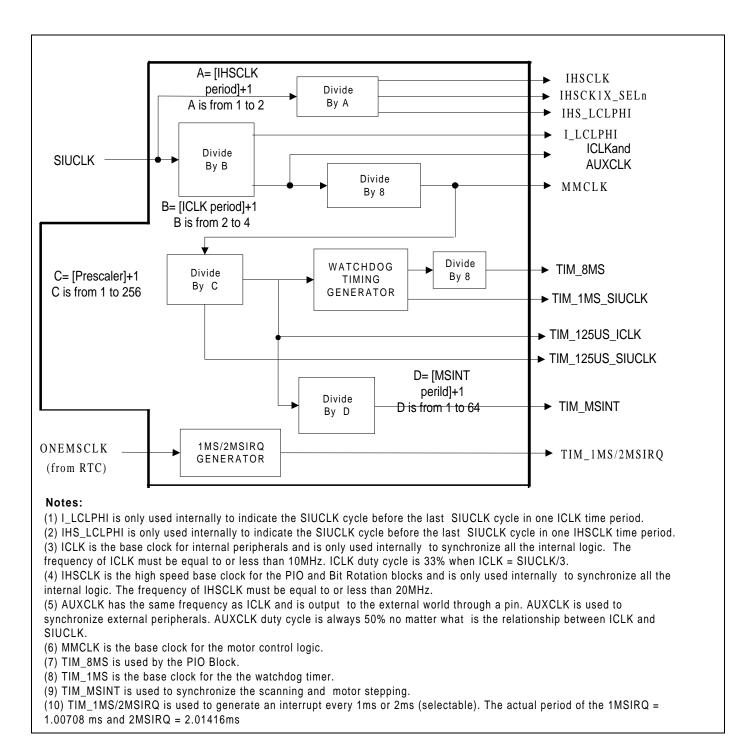

- PLL Clock Generation for several different clocks needed for ARM CPU, Countach Imaging DSP, Fax Modem core, and USB Interface

- 4 KB 2-way Set Associative Instruction Cache

- USB Interface (including USB Transceiver) to PC

- Video/ Color Scan Controller (up to 600 dpi) (including programmable ADC sampling rate)

- Countach Imaging DSP Subsystem for pixel-based dark level correction, shading correction, gamma correction, video/color scan image processing, color science and JPEG

- Countach Bus System which includes Countach Subsystem Interface, ARM Bus Interface, Video/Scan Interface, Countach Bus Unit, Countach DMA Controller, and SDRAM Controller.

- SmartDAA/IA Interface

- P80 Core + ARM IPB interface logic (V.34 Fax Modem core)

- Two Sync. Serial Interfaces

- Color Scan IA which includes Color Scan analog Front End, 12-bit PADC, Power-down Voltage Detection Circuit, and TADC reference voltage.

- SPI and VIP interface to the external Conexant video chip

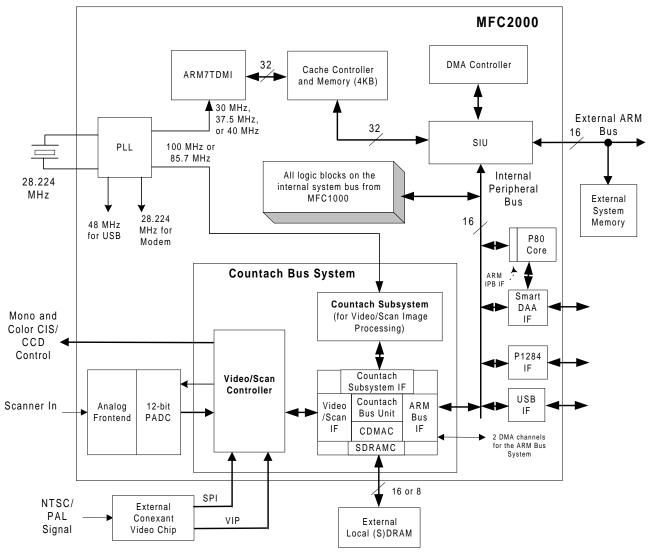

Figure 1-2: MFC2000 Function Diagram

# 1.3 Reference Documentation

| Document                                     | Number |

|----------------------------------------------|--------|

| MFC2000 Data Sheet                           | 100505 |

| MFC2000 Firmware Architecture                | 100972 |

| MFC2000 Hardware Description (this document) | 100723 |

| MFC2000 Programmer's Reference Manual        | 100971 |

#### Table 1-1. Reference Documentation

This page is intentionally blank

# 2. MFC2000 Summary

### 2.1 MFC2000 Device Family

The MFC2000 contains an internal 32-bit RISC Processor with 64-MB address space, the Countach Imaging DSP (Conexant's DSP) subsystem including embedded data and program memory, and dedicated circuitry optimized for color scanning, color faxing, color copying, color printing, and multifunctional control and monitoring. The device family with relevant features is described in Table 2-1.

| Device No.  | Product Code | Data Modem<br>Function | Voice Codec/Speaker<br>Phone Functions | Smart DAA Support |

|-------------|--------------|------------------------|----------------------------------------|-------------------|

| CX0720X-11  | BFH          | Yes                    | Yes                                    | Yes               |

| CX0720X-12  | BDH          | Yes                    | No                                     | Yes               |

| CX0720X -13 | BBH          | No                     | Yes                                    | Yes               |

| CX0720X -14 | B9H          | No                     | No                                     | Yes               |

| CX0720X-15  | B8H          | No                     | No                                     | No                |

Table 2-1. MFC2000 Device Family

### 2.2 MFC2000 System Block Diagram

The MFC2000 contains the ARM7TDMI RISC Processor (described separately in ARM7TDMI Manuals), Countach Imaging DSP, Modem DSP, and specialized hardware needed for the Multifunctional machine control and scanner and fax signal processing. The Countach Imaging DSP subsystem is on a separate data bus. Therefore, the ARM system data bus can operate in parallel with the Countach Imaging DSP subsystem data bus for most operations except the interaction time between two buses. The two-bus architecture is very important to provide enough bandwidth for full color MFP products. Figure 2-1 shows the MFP2000's two-bus architecture. The ARM Bus System (ABS) has two masters—ARM CPU and DMA Controller. They provide accesses to all specialized hardware functions including the Countach Imaging DSP subsystem as a peripheral on the ARM Bus System. ABS has several sections. The System Interface Unit (SIU) is the control center. The ARM CPU and Cache Controller are on the Internal System Bus (ISB). The Cache Memory is on the Internal Cache Bus (ICB). The DMA Controller is on the DMA Bus (DAB). All internal peripherals are on the Internal Peripheral Bus (IPB). The SmartDAA/IA Interface and P80 core are on the IPB of the ARM Bus System. The ARM7TDMI runs at a clock rate 40 MHz, 37.5 MHz, or 30 MHz. All external peripherals are on the ARM External Bus (AEB). There is a separate bus system for the Countach Imaging DSP subsystem called Countach Bus System (CBS). There are three sections, the Video/Scan Interface, the ARM Bus Interface, and the countach subsystem interface. The external SDRAM/DRAM is on the Countach External Bus (CEB).

Figure 2-1. MFC2000 Organization

# 3. Hardware Interface

# 3.1 Pin Description

| Table 3-1. Pin Description (1 | of 6) |

|-------------------------------|-------|

|-------------------------------|-------|

| Pin Name                                | Pin No.                                                                         | I/O | Input<br>Type | Output<br>Type | Pin Description                                                                                                                                                                                           |

|-----------------------------------------|---------------------------------------------------------------------------------|-----|---------------|----------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| PRTIRQn                                 | U14                                                                             | I   | HU5VT         | -              | (Hysteresis, Pull up) Interrupt from the external printing ASIC (active low)                                                                                                                              |

| AUXCLK                                  | K20                                                                             | 0   | -             | 2XT3V          | Auxiliary clock output for using as the master clock for external devices                                                                                                                                 |

| A[11:0]/A[23:12]                        | A20,B20,B19,B<br>18,B17,C20,C1<br>9,C18,C17,D20,<br>D19,D18                     | I/O | 5VT           | 3XT5VT         | Address bus (12-bit), A[23:12] and A[11:0] are muxed out through same pins.                                                                                                                               |

| ALE                                     | C16                                                                             | 0   | -             | 2XT5VT         | Address Latch output signal for latching A[23:12] externally                                                                                                                                              |

| AE[2]/GPO[14]/SSTXD2/<br>ROM_CONFIG[0]  | A19                                                                             | I/O | D5VT          | 2XT5VT         | (Pull down) Address bit for external ROM mux in<br>the ROM interleave access mode or GPO[14] or<br>TX data output for SSIF2 (ROM_CONFIG[0] input<br>during the reset period)                              |

| AO[2]/GPO[15]/SSSTAT2/RO<br>M_CONFIG[1] | A18                                                                             | I/O | D5VT          | 2XT5VT         | (Pull down) Address bit for external ROM mux in<br>the ROM interleave access mode or GPO[15] or<br>Status input for SSIF2 (ROM_CONFIG[1] input<br>during the reset period)                                |

| AE[3]/GPO[16]/<br>CLK_CONFIG[0]         | A17                                                                             | I/O | D5VT          | 2XT5VT         | (Pull down) Address bit for external ROM mux in<br>the ROM interleave access mode or GPO[16]<br>(CLK_CONFIG[0] input during the reset period)                                                             |

| AO[3]/GPO[17]/<br>CLK_CONFIG[1]         | D16                                                                             | I/O | D5VT          | 2XT5VT         | (Pull down) Address bit for external ROM mux in<br>the ROM interleave access mode or GPO[17]<br>(CLK_CONFIG[1] input during the reset period)                                                             |

| D[15:0]                                 | A12,B12,C12,A<br>13,B13,C13,D1<br>3,A14,B14,C14,<br>A15,B15,C15,D<br>15,A16,B16 | I/O | 5VT           | 2XT5VT         | Data bus (16-bit)                                                                                                                                                                                         |

| RDn                                     | D12                                                                             | 0   | -             | 3XT5VT         | Read strobe (active low)                                                                                                                                                                                  |

| WREn/DOEEn                              | B9                                                                              | 0   | -             | 4XT5VT         | Write strobe for the lower byte (active low) or<br>DRAM output enables selects used for non-<br>interleave mode and interleave modes. DOEEn is<br>used for reading the even address bank (active<br>low). |

| WROn/DOEOn                              | C9                                                                              | 0   | -             | 4XT5VT         | Write strobe for the higher byte (active low) or<br>DRAM output enables selects used for non-<br>interleave mode and interleave modes. DOEOn is<br>used for reading the odd address bank (active<br>low). |

| ROMCSn                                  | D10                                                                             | 0   | -             | 2XT5VT         | ROM chip select (active low)                                                                                                                                                                              |

| CS[1]n                                  | A9                                                                              | 0   | -             | 2XT5VT         | I/O chip select (active low).                                                                                                                                                                             |

| CS[0]n                                  | G18                                                                             | 0   | 3V            | 2XT3V          | SRAM chip select (active low) (VRTC powered)                                                                                                                                                              |

| RASn[1:0]                               | F19,F18                                                                         | 0   | -             | 2XT3V          | DRAM row Address select for bank 0 and 1(active low) (VDRAM powered)                                                                                                                                      |

| CASOn[1:0]                              | E17,F20                                                                         | 0   | -             | 2XT3V          | DRAM column odd address selects used for non-<br>interleave mode and interleave mode. (VDRAM<br>powered)                                                                                                  |

| Table 3-1. | Pin | Descriptio | n (2 of 6) |

|------------|-----|------------|------------|

|            |     | Decomptio  |            |

| Pin Name                      | Pin No. | I/O | Input<br>Type | Output<br>Type | Pin Description                                                                                                                                                                   |

|-------------------------------|---------|-----|---------------|----------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| CASEn[1:0]                    | E20,E19 | 0   | -             | 2XT3V          | DRAM column even address selects used for non-<br>interleave mode and interleave mode. (VDRAM<br>powered)                                                                         |

| DWRn                          | D17     | 0   | -             | 2XT3V          | DRAM write. (VDRAM powered)                                                                                                                                                       |

| DMAACK2                       | K19     | 0   | -             | 1XT5VT         | External DMA acknowledge output (channel 2).                                                                                                                                      |

| DMAREQ2                       | F4      | I   | H5VT          | -              | (Hysteresis) External DMA request input (channel 2).                                                                                                                              |

| FCS0n/PWM[1]                  | D9      | 0   | -             | 2XT5VT         | Flash memory chip select 0 or PWM channel 1 output                                                                                                                                |

| FCS1n/PWM[2]                  | A8      | 0   | -             | 2XT5VT         | Flash memory chip select 1 or PWM channel 2 output signal.                                                                                                                        |

| RESETn                        | K18     | I/O | HU5VT         | 2XT5VT         | (Hysteresis, Pull up) MFC2000 Reset input/output                                                                                                                                  |

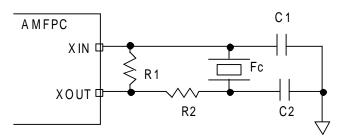

| XIN                           | G20     | I   | OSC           | -              | Crystal oscillator input pin for RTC. (VRTC powered)                                                                                                                              |

| XOUT                          | H20     | 0   | -             | OSC            | Crystal oscillator output pin for RTC. (VRTC powered)                                                                                                                             |

| PWRDWNn                       | H18     | I   | H3V           | -              | (Hysteresis) Indicate the loss of prime power (result in SYSIRQ). (VRTC powered)                                                                                                  |

| WPROTn                        | H19     | 0   | -             | 1XT3V          | Write Protect during loss of VDD power. <b>Note</b> : The functional logic is powered by RTC battery power, but the output drive is powered by DRAM battery power. (VRTC powered) |

| BATRSTn                       | G17     | I   | H3V           | -              | (Hysteresis) Battery power reset input. (VRTC powered)                                                                                                                            |

| EXT_PWRDWN_SELn               | G19     | I   | H3V           | -              | (Hysteresis) External power-down detector select input (active low)(VRTC powered)                                                                                                 |

| SC_START[0]                   | V8      | 0   | -             | 1XT3V          | Scanner shift gate control 0                                                                                                                                                      |

| SC_CLK1/SC_CLK2A              | U9      | 0   | -             | 1XT3V          | Scanner clock.                                                                                                                                                                    |

| SC_LEDCTRL[0]                 | U7      | 0   | -             | 1XT3V          | Scanner LED control 0                                                                                                                                                             |

| SC_LEDCTRL[1]/<br>SC_START[1] | Y8      | 0   | -             | 1XT3V          | Scanner LED control 1 or Scanner shift gate control 1                                                                                                                             |

| SC_LEDCTRL[2]/<br>SC_START[2] | W8      | 0   | -             | 1XT3V          | Scanner LED control 2 or Scanner shift gate control 2                                                                                                                             |

| SSTXD1                        | J19     | 0   | -             | 2XT3V          | TX data for SSIF1                                                                                                                                                                 |

| SSRXD1                        | H17     | I   | HU5VT         | -              | (Hysteresis, Pull up) RX data for SSIF1                                                                                                                                           |

| SSCLK1                        | J20     | I/O | H5VT          | 2XT5VT         | (Hysteresis) Clock input or output for SSIF1                                                                                                                                      |

| GPIO[0]/FWRn/CLAMP            | J4      | I/O | H5VT          | 2XT5VT         | (Hysteresis) GPIO[0] or flash write enable signal<br>for NAND-type flash memory or scanner clamp<br>control output                                                                |

| GPIO[1]/FRDn                  | M3      | I/O | H5VT          | 2XT5VT         | (Hysteresis) GPIO[1] or flash read enable signal for NAND-type flash memory.                                                                                                      |

| GPIO[2]/DMAREQ1/ SSCLK2       | V1      | I/O | H5VT          | 2XT5VT         | (Hysteresis) GPIO[2] or DMA channel 1 request input or clock input/output for SSIF2.                                                                                              |

| GPIO[3]/DMAACK1/ SSRXD2       | U4      | I/O | H5VT          | 2XT5VT         | (Hysteresis) GPIO[3] or DMA channel 1<br>acknowledge or RX data for SSIF2                                                                                                         |

| GPIO[4]/CS[2]n                | U3      | I/O | H5VT          | 2XT5VT         | (Hysteresis) GPIO[4] or I/O chip select [2] (active low)                                                                                                                          |

| GPIO[5]/CS[3]n/PWM[3]         | U2      | I/O | H5VT          | 2XT5VT         | (Hysteresis) GPIO[5]or I/O chip select [3] (active low) or PWM channel 3 output                                                                                                   |

| Pin Name                               | Pin No.     | I/O | Input<br>Type | Output<br>Type | Pin Description                                                                                        |

|----------------------------------------|-------------|-----|---------------|----------------|--------------------------------------------------------------------------------------------------------|

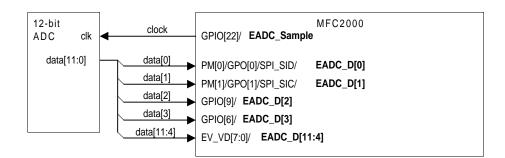

| GPIO[6]/CS[4]n/ EADC_D[3]              | U1          | I/O | H5VT          | 2XT5VT         | (Hysteresis) GPIO[6] or I/O chip select [4] (active low) or external ADC data [3] input                |

| GPIO[7]/CS[5]n/                        | Τ4          | I/O | H5VT          | 2XT5VT         | (Hysteresis) GPIO[7] or I/O chip select [5] (active low).                                              |

| GPIO[8]/IRQ[11]/<br>SSSTAT1/SC_CLK1/2B | Т3          | I/O | H5VT          | 2XT5VT         | (Hysteresis) GPIO[8] or external interrupt [11] or status input for SSIF1 or scan clock output         |

| GPIO[9]/IRQ[13]/ EADC_D[2]             | T2          | I/O | H5VT          | 2XT5VT         | (Hysteresis) GPIO[9] or external interrupt [13] or external ADC data [2] input                         |

| GPIO[10]/RING_DETECT/PW<br>M[4]        | T1          | I/O | H5VT          | 2XT5VT         | (Hysteresis) GPIO[10] or ring detection input or<br>PWM channel 4 output                               |

| GPIO[11]/CPCIN/PWM[0]/ALT<br>TONE      | R4          | I/O | H5VT          | 2XT5VT         | (Hysteresis) GPIO[11] or calling party control input<br>or ALTTONE output                              |

| GPIO[12]/SASCLK/<br>SMPWRCTRL          | R3          | I/O | H5VT          | 2XT5VT         | (Hysteresis) GPIO[12] or clock input/output for SASIF or Scan Motor Power Control output               |

| GPIO[13]/SASTXD/<br>PMPWRCTRL          | R2          | I/O | H5VT          | 2XT5VT         | (Hysteresis) GPIO[13] or TX data output for SASIF<br>or Print Motor Power Control output               |

| GPIO[14]/SASRXD/ RINGER                | R1          | I/O | H5VT          | 2XT5VT         | (Hysteresis) GPIO[14] or RX data input for SASIF or ringer output                                      |

| GPIO[15]/IRQ[16]/<br>SC_CLK1/2C        | P4          | I/O | H5VT          | 2XT5VT         | (Hysteresis) GPIO[15] or external interrupt [16] or scan clock output                                  |

| GPIO[16]/M_TXSIN                       | P3          | I/O | H5VT          | 2XT5VT         | (Hysteresis) GPIO[16] or internal modem                                                                |

| GPIO[17]/M_CLKIN                       | P2          | I/O | H5VT          | 2XT5VT         | (Hysteresis) GPIO[17] or internal modem                                                                |

| GPIO[18]/M_RXOUT                       | P1          | I/O | H5VT          | 2XT5VT         | (Hysteresis) GPIO[18] or internal modem                                                                |

| GPIO[19]/M_SCK/MIRQn                   | N4          | I/O | H5VT          | 2XT5VT         | (Hysteresis) GPIO[19] or internal modem or external modem interrupt input                              |

| GPIO[20]/M_STROBE/ MCSn                | N3          | I/O | H5VT          | 2XT5VT         | (Hysteresis) GPIO[20] or internal modem or external modem chip select                                  |

| GPIO[21]/M_CNTRL_SIN                   | N2          | I/O | H5VT          | 2XT5VT         | (Hysteresis) GPIO[21] or internal modem                                                                |

| GPIO[22]/EADC_Sample                   | N1          | I/O | H5VT          | 2XT5VT         | (Hysteresis) GPIO[22] or external ADC sample signal output                                             |

| SM[3:0]/<br>GPO[7:4]                   | V7,W7,Y7,U6 | 0   | -             | 1XT3V          | Scan motor control [3:0] pins or GPO[7:4] pins.                                                        |

| PM[0]/SPI_SID/<br>EADC_D[0]/GPO[0]     | U8          | I/O | 5VT           | 1XT5VT         | Print motor control [0] output or GPO[0] output or data output for SPI or external ADC data [0] input  |

| PM[1]/SPI_SIC/<br>EADC_D[1]/GPO[1]     | W9          | I/O | 5VT           | 1XT5VT         | Print motor control [1] output or GPO[1] output or clock output for SPI or external ADC data [1] input |

| PM[2]/SMI0/GPO[2]                      | Y9          | 0   | -             | 1XT3V          | Print motor control [2] output or GPO[2] output or scan motor current control 0.                       |

| PM[3]/SMI1/GPO[3]                      | Y12         | 0   | -             | 2XT3V          | Print motor control [3] output or GPO[3] output or scan motor current control 1.                       |

| TONE                                   | V9          | I/O | H5VT          | 1XT5VT         | (Hysteresis) Tone output signal.                                                                       |

| PIODIR                                 | C1          | 0   | -             | 2XT3V          | PIOD[7:0] is output when PIODIR is high and<br>PIOD[7:0] is input when PIODIR is low.                  |

| STROBEn                                | A2          | 1   | H5VT          | -              | (Hysteresis) Input from PC (active low)                                                                |

| AUTOFDn                                | G3          | 1   | H5VT          | -              | (Hysteresis) Input from PC (active low)                                                                |

| SLCTINn                                | G2          | 1   | H5VT          | -              | (Hysteresis) Input from PC (active low)                                                                |

| INITn                                  | G1          | 1   | H5VT          | -              | (Hysteresis) Input from PC (active low)                                                                |

| BUSY                                   | A1          | 0   | -             | 2XT3V          | PIO Returned status to PC                                                                              |

| ACKn                                   | D3          | 0   | -             | 2XT3V          | PIO Returned status to PC (active low)                                                                 |

| Table | 3-1.  | Pin | Descri | ption ( | (4 of              | 6) |

|-------|-------|-----|--------|---------|--------------------|----|

| IUNIO | • • • |     | 000011 |         | ( <b>- - - - -</b> | v, |

| Pin Name     | Pin No.                                                                         | I/O | Input<br>Type | Output<br>Type | Pin Description                                                                                                                             |

|--------------|---------------------------------------------------------------------------------|-----|---------------|----------------|---------------------------------------------------------------------------------------------------------------------------------------------|

| SLCTOUT      | C3                                                                              | 0   | -             | 2XT3V          | PIO Returned status to PC                                                                                                                   |

| PE           | B2                                                                              | 0   | -             | 2XT3V          | PIO Returned status to PC                                                                                                                   |

| FAULTn       | B1                                                                              | 0   | -             | 2XT3V          | PIO Returned status to PC (active low)                                                                                                      |

| PIOD[7:0]    | D2,D1,C2,H4,H<br>3,H2,H1,G4                                                     | I/O | H5VT          | 2XT5VT         | (Hysteresis) Driven by PC or MFC2000 and used<br>to send data or address depending on which mode<br>is used                                 |

| TESTER_MODE  | J2                                                                              | I   | HD5VT         | -              | (Hysteresis) For test only, It must be 'low' for the normal operation                                                                       |

| ADCREFp      | Y3                                                                              | Ι   |               |                | Positive reference voltage for the scan PADC                                                                                                |

| ADCREFn      | Y2                                                                              | Ι   |               |                | Negative reference voltage for the scan PADC                                                                                                |

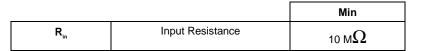

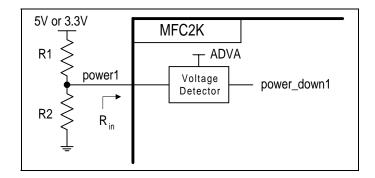

| POWER1       | Y1                                                                              | Ι   |               |                | Voltage input for power-down detection circuit 1                                                                                            |

| POWER2       | W4                                                                              | I   |               |                | Voltage input for power-down detection circuit 2                                                                                            |

| ADGA         | Y5                                                                              | -   |               |                | Scan PADC analog ground                                                                                                                     |

| ADVA         | V5                                                                              | -   |               |                | Scan PADC analog Power                                                                                                                      |

| ADGD         | U5                                                                              | -   |               |                | Scan PADC digital ground                                                                                                                    |

| SDAA_SPKR    | V12                                                                             | 0   |               |                | Analog telephone line monitoring output from SSD                                                                                            |

| ADCV         | Y4                                                                              | -   |               |                | Scan PADC internal ground                                                                                                                   |

| SCIN         | W5                                                                              | I   |               |                | Analog scan input signal                                                                                                                    |

| SENIN[2:0]   | V6,W6,Y6                                                                        | I   |               |                | Analog sensor inputs for TADC                                                                                                               |

| ТСК          | W3                                                                              | I   | HD5VT         | -              | (Hysteresis, Pull down) Test clock input for JTAG.<br>It is positive edge-triggered.                                                        |

| TMS          | W2                                                                              | I   | HU5VT         | -              | (Hysteresis, Pull up) Test mode select input for JTAG. Selects the next state in the TAP state machine.                                     |

| TRSTn        | W1                                                                              | I   | HD5VT         | -              | (Hysteresis, Pull down) Suggestion by Lauterbach<br>for JTAG: connect this signal to RESETn in normal<br>mode and disconnect in debug mode. |

| TDI          | V4                                                                              | I   | HU5VT         | -              | (Hysteresis, Pull up) Test data input for JTAG.<br>Serial data input to the JTAG shift register.                                            |

| TDO          | V3                                                                              | 0   | -             | 1XT5VT         | Test data output for JTAG. Serial data output from the JTAG shift register.                                                                 |

| TEST         | V2                                                                              | I   | HD5VT         | -              | (Hysteresis, Pull down) For test only, It must be<br>'low' for the normal operation.                                                        |

| SCANMOD      | J1                                                                              | I   | HD5VT         | -              | (Hysteresis, Pull down) For the scan test only, It must be 'low' for normal operations.                                                     |

| P80_SEL      | J3                                                                              | I   | H3V           | -              | P80 DSP test and DFT scan mode select, This pin is only used for the test mode.                                                             |

| PLLREF_XIN   | Y15                                                                             | I   | OSC           | -              | Crystal input pin for PLL                                                                                                                   |

| PLLREF_XOUT  | W15                                                                             | 0   | -             | OSC            | Crystal output pin for PLL                                                                                                                  |

| PLLVDD       | U15                                                                             | -   |               |                | +3.3V digital power for PLL                                                                                                                 |

| PLLVSS       | U16                                                                             | -   |               |                | +3.3V digital ground for PLL                                                                                                                |

| SDDATA[15:0] | N20,P17,P18,P<br>19,P20,R17,R1<br>8,R19,R20,T17,<br>T18,T19,T20,U1<br>7,U18,U19 | I/O | 5VT           | 2XT5VT         | Countach (S)DRAM data bus (16 bits)                                                                                                         |

| Table 3-1. Pin Description (5 of | of 6) |  |

|----------------------------------|-------|--|

|----------------------------------|-------|--|

| Pin Name                     | Pin No.                                                             | I/O | Input<br>Type | Output<br>Type | Pin Description                                                                                                                                                                              |

|------------------------------|---------------------------------------------------------------------|-----|---------------|----------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| SDADDR[12:0]                 | V20,W20,Y20,<br>W19,Y19,W18,<br>Y18,W17,Y17,V<br>16,W16,Y16,V1<br>5 | 0   | -             | 2XT3V          | Countach (S)DRAM address bus (13 pins)                                                                                                                                                       |

| SDCASn                       | U20                                                                 | 0   | -             | 2XT3V          | Countach (S)DRAM column address strobe (active low)                                                                                                                                          |

| SDRASn                       | V19                                                                 | 0   | -             | 2XT3V          | Countach (S)DRAM row address strobe (active low)                                                                                                                                             |

| SDWRn                        | V18                                                                 | 0   | -             | 2XT3V          | Countach (S)DRAM write strobe (active low)                                                                                                                                                   |

| SDCSn                        | V17                                                                 | 0   | -             | 2XT3V          | Countach (S)DRAM chip select                                                                                                                                                                 |

| SDCLK100MHz                  | M19                                                                 | 0   | 5VT           | 2XT5VT         | Countach (S)DRAM clock                                                                                                                                                                       |

| USB_Dp                       | B8                                                                  | I/O |               |                | Positive data input/output pin for USB                                                                                                                                                       |

| USB_Dn                       | C8                                                                  | I/O |               |                | Negative data input/output pin for USB                                                                                                                                                       |

| SDAA_PWRCLK                  | E1                                                                  | I/O |               |                | Positive power/clock output from SSD                                                                                                                                                         |

| SDAA_PWRCLKn                 | E2                                                                  | I/O |               |                | Negative power/clock output from SSD                                                                                                                                                         |

| SDAA_DIBp                    | E4                                                                  | I/O |               |                | Positive data input/output pin for SDAA                                                                                                                                                      |

| SDAA_DIBn                    | E3                                                                  | I/O |               |                | Negative data input/output pin for SDAA                                                                                                                                                      |

| EV_VD[0]/EADC_D[4]/ MREQn    | W12                                                                 | I/O | 3V            | 2XT3V          | External video data [0] input for VIP or external ADC data [4] input or Memory Request (active low)-indicates that the following cycle is a memory access.                                   |

| EV_VD[1]/EADC_D[5]           | U12                                                                 | I/O | 3V            | 2XT3V          | External video data [1] input for VIP or external ADC data [5] input                                                                                                                         |

| EV_VD[2]/EADC_D[6]/ OPCn     | Y13                                                                 | I/O | 3V            | 2XT3V          | External video data [2] input for VIP or external<br>ADC data [6] input or Op Code fetch (active low)-<br>LOW indicates that the processor is fetching an<br>instruction from memory.        |

| EV_VD[3]/EADC_D[7]           | W13                                                                 | I/O | 3V            | 2XT3V          | External video data [3] input for VIP or external ADC data [7] input                                                                                                                         |