# Microprocessor SPARClite cmos

# 32-bit Embedded Controller MB86830 Series

# MB86831/832/833/834/835/836

#### **■ DESCRIPTION**

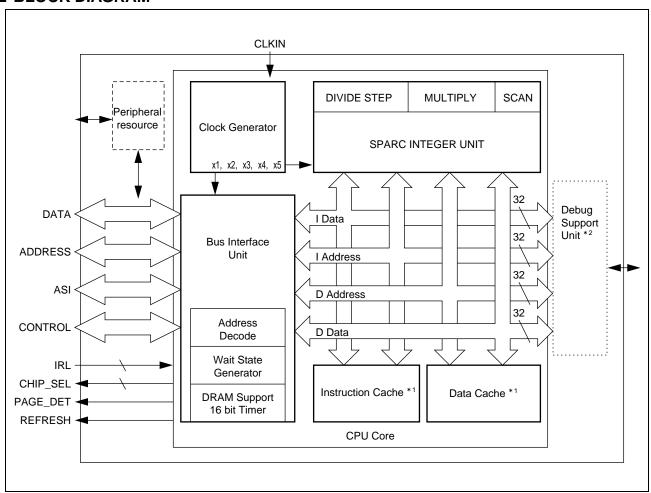

The MB86830 series is a SPARClite \*¹ series of RISC architecture processors, providing high performance for a variety of embedded applications. Conforming to the SPARC \*² architecture, the MB86830 series is upward codecompatible with the conventional products in the SPARClite family. When running at 100 MHz, the MB86830 series provides performance of 121 VAX-MIPS.

The MB86830 series has on-chip data and instruction caches, allowing the processor to operate independently of the wait time for external memory. The independent instruction bus and internal data bus serve as high-bandwidth interfaces between the IU (integer unit) and caches. The MB86830 series also contains an internal multiplier circuit that facilitates interfacing with external devices, thereby providing high performance with continuous cache hits. The DRAM controller supports both of EDO and fast-page mode DRAMs. The interrupt controller (IRC) supports eight channels of interrupts, allowing a trigger mode and mask to be set for each of the channels. To get the most out of the system with a minimum number of external circuits, the MB86830 series supports chip select output, programmable wait state generator, and page mode DRAM interfaces.

The combination of these features of the MB86830 series achieves high levels of speed, flexibility, and efficiency, making it a line of ideal controllers for a variety of low-cost, high-performance embedded systems.

- \*1: SPARClite is a trademark of SPARC International, Inc. in the United States. Fujitsu Microelectronics, Inc. has been granted permission to use the trademark.

- \*2: SPARC is a registered trademark of SPARC International, Inc. in the United States. SPARC is based on technology developed by Sun Microsystems, Inc.

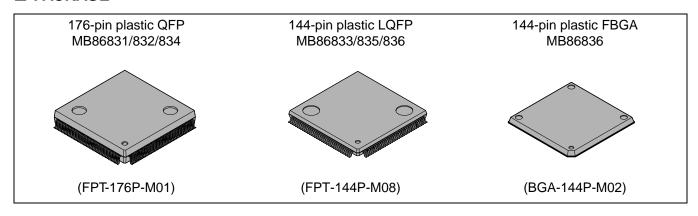

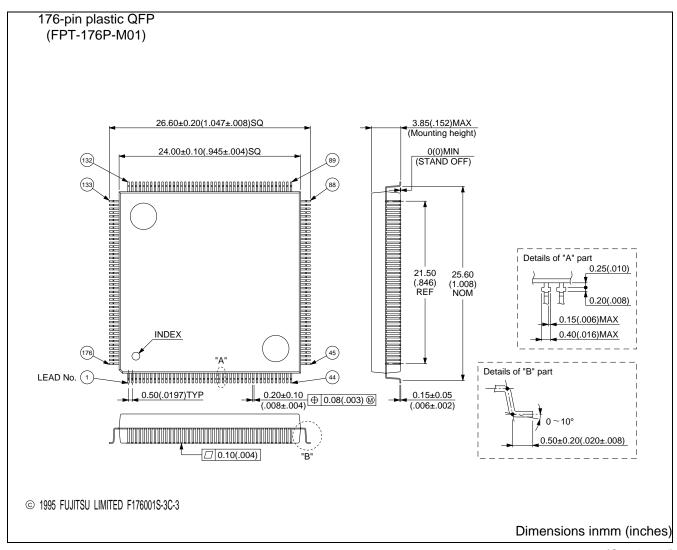

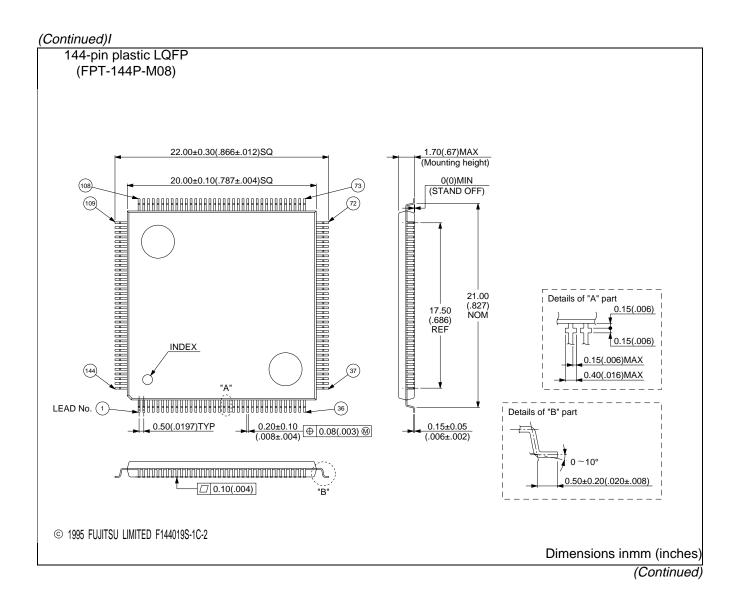

#### **■ PACKAGE**

#### **■ FEATURES**

• IU (integer unit)

Maximum operating frequency: 120 MHz SPARC architecture V8E conforming

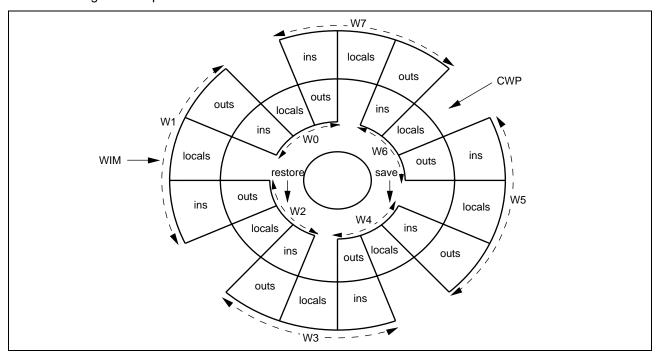

With 32-bits general register :136 / register window : 8

Instruction cash

The entry lock function is supported

• Data cache

No cash controlling function supported

The entry lock function is supported

• BIU (bus interface unit)

Purifetchi baffa :1 Write buffer :4

The burst mode is supported

Programmable chip selection function :6

Programmable weight state control :6

For 8/16/32-bits bus

Automatic insertion function of idling cycle after ROM region is accessed

For burst mode ROM

- With internal clock multiplication circuit

- Sleep mode (low power consumption mode) supported

- With DRAM controller (except on the MB86836)

- With interrupt request controller (IRC)

- On-chip general-purpose 16-bit timer (MB86836 only):1 channel (equivalent to the MB86942)

- Support for the JTAG test port (MB86836 only)

#### **■ PRODUCT LINEUP**

| Part number                        | MDaaaa                                | MDaaaaa                  | MDaaaaa                                   | MDoood                                    | MDOOOF                                    | MDOOOO                                                                                       |

|------------------------------------|---------------------------------------|--------------------------|-------------------------------------------|-------------------------------------------|-------------------------------------------|----------------------------------------------------------------------------------------------|

| Item                               | MB86831                               | MB86832                  | MB86833                                   | MB86834                                   | MB86835                                   | MB86836                                                                                      |

| CPU maximum frequency (MHz)        | 66/80                                 | 66/80/100                | 66                                        | 108/120                                   | 84                                        | 90/108*1                                                                                     |

| BUS maximum frequency (MHz)        | 4                                     | 10                       | 33                                        |                                           | 40                                        |                                                                                              |

| Ancillary Version Register         | (0000)16                              | (0001)16                 | (0002)16                                  | (0003)16                                  | (0004)16                                  | (0001)16                                                                                     |

| Instruction cache                  | 4 KB/2 way                            | 8 KB/2 way               | 1 KB/Direct                               | 16 KB/2 way                               | 4 KB/2 way                                | 8 KB/2 way                                                                                   |

| Data cache                         | 2 KB/2 way                            | 8 KB/2 way               | 1 KB/Direct                               | 16 KB/2 way                               | 2 KB/2 way                                | 8 KB/2 way                                                                                   |

| Cache size change function         | No                                    | 8/4/2/1 KB<br>selectable |                                           | N                                         | 0                                         |                                                                                              |

| ADR pin                            | ADR-                                  | <27:2>                   | ADR<23:2>                                 | ADR<27:2>                                 | ADR<                                      | 23:2>                                                                                        |

| ADR enhancement (ASISEL)           | No                                    | ADR<31:2>                | ADR<27:2>                                 | ADR<31:2>                                 | ADR<                                      | 27:2>                                                                                        |

| Clock gear function                | No                                    |                          |                                           |                                           |                                           |                                                                                              |

| DSU                                | No                                    | Yes                      | No                                        | Yes                                       | N                                         | 0                                                                                            |

| DRAM controller                    | 4b                                    | ank                      | 1bank                                     | 4bank                                     | 1bank                                     | No                                                                                           |

| JTAG test port                     |                                       |                          | No                                        |                                           |                                           | Yes                                                                                          |

| General porpose 16-bit timer*2     |                                       |                          | No                                        |                                           |                                           | 1ch                                                                                          |

| Internal pull-up/down resister pin | P63                                   | P63,<br>P162 to P164     |                                           |                                           | P41 to<br>P44, P79                        |                                                                                              |

| Internal power supply (VDD3)       |                                       | 3.3 V                    |                                           | 2.5 V                                     | 3.3 V                                     | 2.5 V                                                                                        |

| I/O power supply (VDD5)            |                                       | 3.3 V to 5.0 V           | 1                                         |                                           | 3.3 V                                     |                                                                                              |

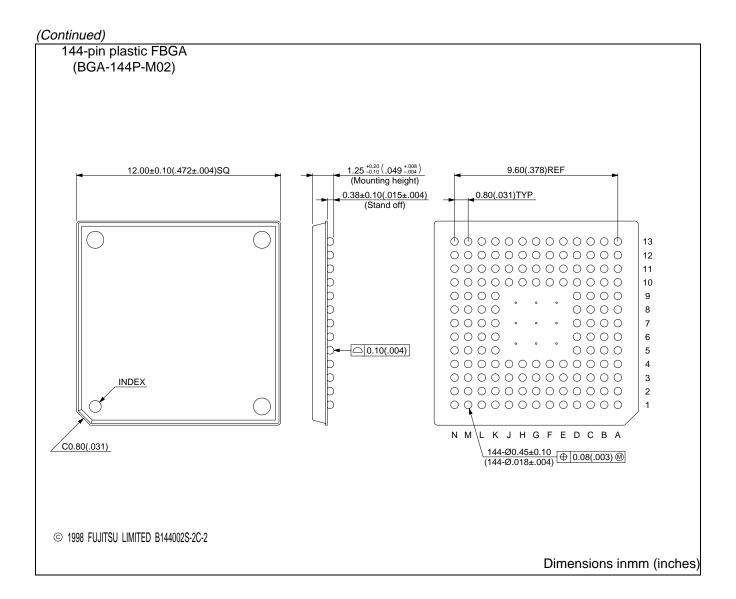

| Package                            | SQFP176<br>FPT-176P-M01<br>24 × 24 mm |                          | LQFP144<br>FPT-144P-<br>M08<br>20 × 20 mm | SQFP176<br>FPT-176P-<br>M01<br>24 × 24 mm | LQFP144<br>FPT-144P-<br>M08<br>20 × 20 mm | LQFP144<br>FPT-144P-<br>M08<br>20 × 20<br>mm<br>FBGA144<br>BGA-<br>144P-M02<br>12 × 12<br>mm |

<sup>\*1:</sup>MB86836 108 MHz version is under developement.

<sup>\*2:</sup> The general-purpose timer on the MB86836 is a subset of the prescaler-integrated 16-bit timer on the MB86942. For the type supporting only the internal clock mode, refer to the document for the MB86941/942.

#### **■ FOR PACKAGE AND PART NUMBER**

| Package      | MB86831 | MB86832 | MB86833 | MB86834 | MB86835 | MB86836 |

|--------------|---------|---------|---------|---------|---------|---------|

| FPT-176P-M01 | Yes     | Yes     | No      | Yes     | No      | No      |

| FPT-144P-M08 | No      | No      | Yes     | No      | Yes     | Yes     |

| BGA-144P-M02 | No      | No      | No      | No      | No      | Yes     |

Note: Refer to "PACKAGE DIMENSIONS" for details in each package.

#### **■ DIFFERENCES**

#### 1.Package

MB86831/832/834 : QFP176MB86833/835/836 : LQFP144

• MB86836 : FBGA144

#### 2.Pin array

• MB86831/832/834: The pin is interchangeable. However, the terminal of MB86834 is the pull-up resistor none.

• MB86833/835 : The pin is interchangeable.

• MB86836 : MB86833/835, from which DRAMC related pins are deleted and to which one channel of general-purpose 16-bit timer and the JTAG pin are added.

#### 3. Maximum operation frequency

• MB86831 : 66MHz/80MHz

MB86832: 66MHz/80MHz/100MHz

• MB86833 : 66MHz

• MB86834 : 108MHz/120MHz

• MB86835 : 84MHz

• MB86836: 90MHz/108MHz

#### 4. Power-supply voltage

| Power-supply voltage          | MB86831 | MB86832        | MB86833 | MB86834 | MB86835 | MB86836 |

|-------------------------------|---------|----------------|---------|---------|---------|---------|

| Internal power-supply voltage |         | 3.3 V          |         | 2.5 V   | 3.3 V   | 2.5 V   |

| I/O power-supply voltage      |         | 3.3 V or 5.0 V |         | 3.3 V   | 3.3 V   | 3.3 V   |

<sup>\*:</sup> The power-supply voltage is different (Refer to "ELECTRIC CHARACTERISTICS") depending on the condition of the operation frequency.

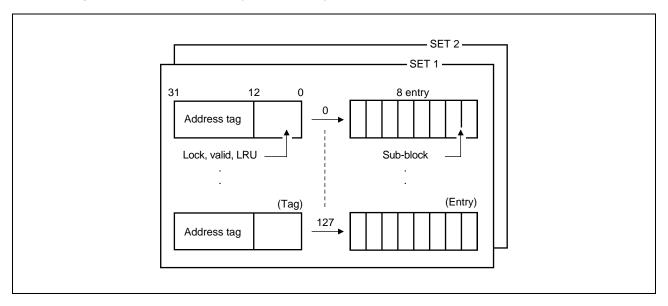

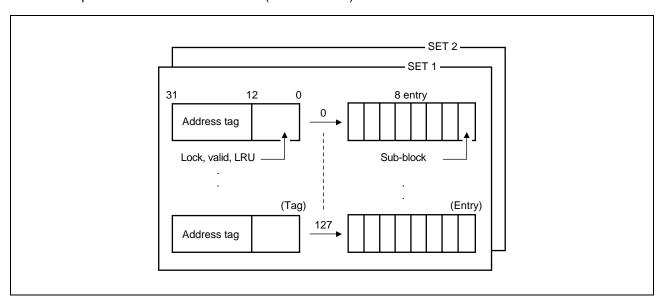

#### 5. Cache memory

| Cache memory     | MB86831    | MB86832    | MB86833     | MB86834     | MB86835    | MB86836    |

|------------------|------------|------------|-------------|-------------|------------|------------|

| Instruction cash | 4 KB/2 way | 8 KB/2 way | 1 KB/Direct | 16 KB/2 way | 4 KB/2 way | 8 KB/2 way |

| Data cash        | 2 KB/2 way | 8 KB/2 way | 1 KB/Direct | 16 KB/2 way | 2 KB/2 way | 8 KB/2 way |

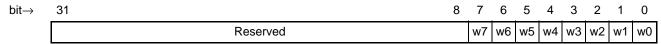

#### 6.Register

| Register name                                         | MB86831/832/833/835/836 | MB86834                                                                              |

|-------------------------------------------------------|-------------------------|--------------------------------------------------------------------------------------|

| Instruction Cache Invalidate<br>Register<br>(ICINVLD) |                         | Map of<br>ASI = 0x0c, ADR = 0x00008000(Bank1)<br>ASI = 0x0c, ADR = 0x80008000(Bank2) |

| Data Cache Invalidate<br>Register<br>(DCINVLD)        |                         | Map of<br>ASI = 0x0e, ADR = 0x00008000(Bank1)<br>ASI = 0x0e, ADR = 0x80008000(Bank2) |

| Register name                     | MB86831 | MB86832 | MB86833 | MB86834 | MB86835 | MB86836            |

|-----------------------------------|---------|---------|---------|---------|---------|--------------------|

| Ancillary Version Register (VER2) | (00)16  | (01)16  | (02)16  | (03)16  | (04)16  | (01) <sub>16</sub> |

#### 7.Clock gear

• MB86832/833/834/835/836 : Supported

• MB86831 : No supported

#### 8.External signal

| Item                                   | MB86831            | MB86832                                                                                                            | MB86833             | MB86834            | MB86835             | MB86836 |  |  |

|----------------------------------------|--------------------|--------------------------------------------------------------------------------------------------------------------|---------------------|--------------------|---------------------|---------|--|--|

| ASISEL pin function                    | No                 | No Multiplex of ADR<31:28> ADR<27:24> ADR<31:28> and ASI<3:0> and ASI<3:0> Multiplex of ADR<31:28> and ASI<3:0> AS |                     |                    |                     |         |  |  |

| DSU (debugging support unit)           | No                 | Yes                                                                                                                | No                  | Yes                | N                   | lo      |  |  |

| DRAM controller                        | 4Bank<br>supported | 4Bank<br>supported                                                                                                 | 1Bank<br>supported* | 4Bank<br>supported | 1Bank<br>supported* | No      |  |  |

| General-purpose<br>16-bit timer        |                    | No                                                                                                                 |                     |                    |                     |         |  |  |

| JTAG                                   |                    |                                                                                                                    | Support             |                    |                     |         |  |  |

| Pull-up resistor or pull-down resistor | Inclusion          | aclusion No                                                                                                        |                     |                    |                     |         |  |  |

<sup>\*:</sup>RAS1# to RAS3# and DWE1# to DWE3# deletion.

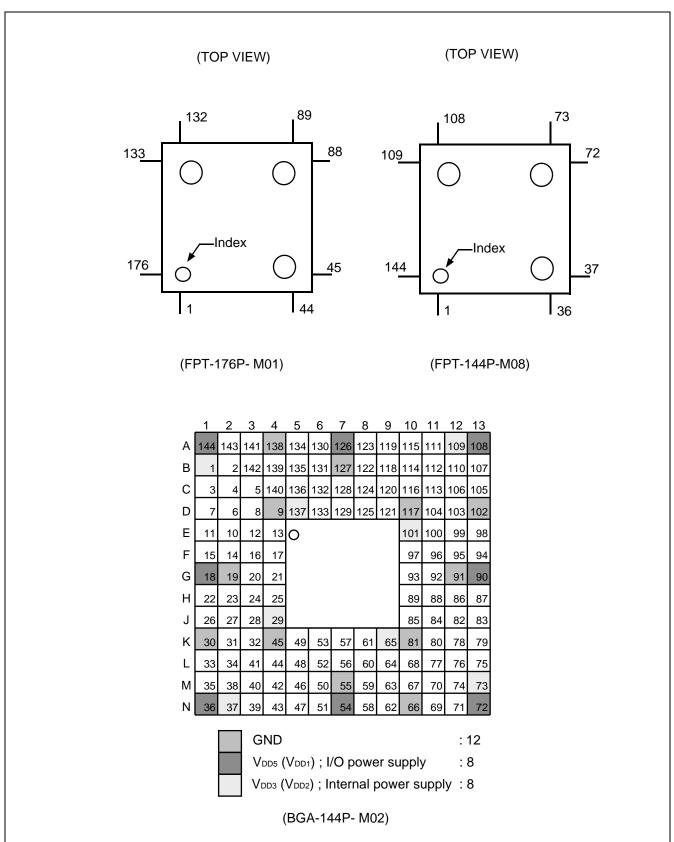

#### **■ PIN ASSIGNMENT**

#### • MB86831/832/834

| 2         D<31>         38         BMODE8#         74         OVF#         110         READY#         146         PDOWN           3         D<30>         39         Vss         75         SAMEPAGE#         111         Vops         147         WKUP#           4         D<29>         40         D<3>         76         AS#         112         ADR<12>         148         RESETI           5         D<28>         41         D<2>         77         Vbp3         113         ADR<13>         149         Vss           6         Vss         42         D<1>         78         RDWR#         114         ADR<14>         150         IDLEEN           7         BMODE16#         43         D<0>         79         RDVBW#         115         ADR<15>         151         CLKSE           8         D<27>         44         Vpp3         80         CSS#         116         Vss         152         CLKSE           9         D<26>         45         Vss         81         CS4#         117         ADR<16>         153         CLKSE           10         D<25         46         DWE2#         83         Vss         119                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | Pin<br>no. | Pin symbol       |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------|------------------|------------|------------------|------------|------------------|------------|------------------|------------|------------------|

| 3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 1          | V <sub>DD3</sub> | 37         | D<4>             | 73         | BMREQ#           | 109        | ADR<11>          | 145        | FLOAT#           |

| 4         D<29>         40         D<3>         76         AS#         112         ADR<12>         148         RESET           5         D<28>         41         D<2>         77         Vod3         113         ADR<13>         149         Vss           6         Vss         42         D<1>         78         RDWR#         114         ADR<14>         150         IDLEEN           7         BMODE 16#         43         D<0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 2          | D<31>            | 38         | BMODE8#          | 74         | OVF#             | 110        | READY#           | 146        | PDOWN#           |

| 5         D<28>         41         D<2>         77         V <sub>DD3</sub> 113         ADR<13>         149         V <sub>SS</sub> 6         Vss         42         D<1>         78         RDWR#         114         ADR<14>         150         IDLEEN           7         BMODE16#         43         D<0>         79         RDYOUT#         115         ADR<15>         151         CLKSEL           8         D<27>         44         V <sub>DD3</sub> 80         CSS#         116         V <sub>SS</sub> 152         CLKSEL           10         D<25>         46         DWE3#         82         V <sub>DD3</sub> 118         ADR<16>         153         CLKEX           11         D<24>         47         DWE2#         83         V <sub>SS</sub> 119         ADR<18>         155         V <sub>DD3</sub> 12         V <sub>DD5</sub> 48         DWE1#         84         CS3#         120         ADR<19>         156         IRQ11           13         D<23>         49         DWE0#         85         CS2#         121         V <sub>DD5</sub> 157         IRQ10           14         D<22>         50         V <sub>SS</sub> 86         CS1#                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 3          | D<30>            | 39         | Vss              | 75         | SAMEPAGE#        | 111        | V <sub>DD3</sub> | 147        | WKUP#            |

| 6                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 4          | D<29>            | 40         | D<3>             | 76         | AS#              | 112        | ADR<12>          | 148        | RESET#           |

| 7         BMODE16#         43         D<0>         79         RDYOUT#         115         ADR<15>         151         CLKSEL           8         D<27>         44         VDD3         80         CS5#         116         Vss         152         CLKSEL           9         D<26>         45         Vss         81         CS4#         117         ADR<16>         153         CLKEX           10         D<25>         46         DWE3#         82         VDD05         118         ADR<17>         154         CLKIN           11         D<24>         47         DWE2#         83         Vss         119         ADR<18>         155         VDD05           12         VDD05         48         DWE1#         84         CS3#         120         ADR<18>         156         IRQ10           13         D<23>         49         DWE0#         85         CS2#         121         VDD05         157         IRQ10           14         D<22>         50         Vss         86         CS1#         122         ADR<20>         158         IRQ9           15         D<21>         51         VDD5         87         CS0#         123 <td>5</td> <td>D&lt;28&gt;</td> <td>41</td> <td>D&lt;2&gt;</td> <td>77</td> <td>V<sub>DD3</sub></td> <td>113</td> <td>ADR&lt;13&gt;</td> <td>149</td> <td>Vss</td>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 5          | D<28>            | 41         | D<2>             | 77         | V <sub>DD3</sub> | 113        | ADR<13>          | 149        | Vss              |

| 8         D<27>         44         Vod3         80         CS5#         116         Vss         152         CLKSEL           9         D<26>         45         Vss         81         CS4#         117         ADR<16>         153         CLKEX           10         D<25>         46         DWE3#         82         VDD5         118         ADR<17>         154         CLKIN           11         D<24>         47         DWE2#         83         Vss         119         ADR<18>         155         VDD5           12         VDD5         48         DWE1#         84         CS3#         120         ADR<19>         156         IRQ11           13         D<23>         49         DWE0#         85         CS2#         121         VDD5         157         IRQ10           14         D<22>         50         Vss         86         CS1#         122         ADR<20>         158         IRQ9           15         D<21>         51         VDD5         87         CS0#         123         ADR<21                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 6          | Vss              | 42         | D<1>             | 78         | RDWR#            | 114        | ADR<14>          | 150        | IDLEEN           |

| 9 D<26> 45 Vss 81 CS4# 117 ADR<16> 153 CLKEX 10 D<25> 46 DWE3# 82 Vods 118 ADR<17> 154 CLKIN 11 D<24> 47 DWE2# 83 Vss 119 ADR<18> 155 Vods 12 Vods 48 DWE1# 84 CS3# 120 ADR<19> 156 IRQ11 13 D<23> 49 DWE0# 85 CS2# 121 Vods 157 IRQ10 14 D<22> 50 Vss 86 CS1# 122 ADR<20> 158 IRQ9 15 D<21> 51 Vods 87 CS0# 123 ADR<21> 159 IRQ8 16 D<20> 52 RAS0# 88 Vss 124 ADR<22> 160 Vss 17 Vss 53 RAS1# 89 Vdd3 125 ADR<23> 161 Reserve 18 D<19> 54 RAS2# 90 BE3# 126 MEXC# 162 [ASISEL 19 D<18> 55 RAS3# 91 BE2# 127 Vss 163 [EMUBRK 20 D<17> 56 Vdd3 92 BE1# 128 ADR<24> 164 [EMUENB 21 D<16> 57 CAS0# 93 BE0# 129 ADR<25> 165 Vdd3 22 BTEST# 58 CAS1# 94 Vss 130 ADR<25> 166 [EMUSD 24 D<15> OCAS3# 96 Reserved 132 Vdd3 Vss 169 [EMUSD 25 D<14> 61 Vss 97 Reserved 133 Vss 169 [EMUSD 26 D<13> 62 DOE# 98 ADR<2> 134 ASI 29 D<11> 65 LOCK# 101 ADR<24> 137 ASI 20 D<15> 66 CESS# 100 Vdd3 SAS 21 D<15> OCAS0# 93 ADR<25> 167 [EMUSD 25 D<14> 61 Vss 97 Reserved 133 Vss 169 [EMUSD 26 D<13> 62 DOE# 98 ADR<2> 134 ASI 29 D<11> 65 LOCK# 101 ADR<24> 137 ASI 20 D<15> 60 CESS# 100 Vdd3 ADR<25> 136 [EMUSD 25 D<14> 61 Vss 97 Reserved 133 Vss 169 [EMUSD 26 D<13> 62 DOE# 98 ADR<2> 134 ASI<25  170 Vdd3 30 D<10> 66 CTEST# 100 ADR<26> 136 [EMUSD 31 D<29 D<11> 65 LOCK# 101 ADR<27> 140 IRC<25  IRC<26  IRC<26 | 7          | BMODE16#         | 43         | D<0>             | 79         | RDYOUT#          | 115        | ADR<15>          | 151        | CLKSEL1          |

| 10                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 8          | D<27>            | 44         | V <sub>DD3</sub> | 80         | CS5#             | 116        | Vss              | 152        | CLKSEL0          |

| 11                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 9          | D<26>            | 45         | Vss              | 81         | CS4#             | 117        | ADR<16>          | 153        | CLKEXT           |

| 12                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 10         | D<25>            | 46         | DWE3#            | 82         | V <sub>DD5</sub> | 118        | ADR<17>          | 154        | CLKIN            |

| 13                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 11         | D<24>            | 47         | DWE2#            | 83         | Vss              | 119        | ADR<18>          | 155        | V <sub>DD5</sub> |

| 14         D<22>         50         Vss         86         CS1#         122         ADR<20>         158         IRQ9           15         D<21>         51         Vods         87         CS0#         123         ADR<21>         159         IRQ8           16         D<20>         52         RAS0#         88         Vss         124         ADR<22>         160         Vss           17         Vss         53         RAS1#         89         Vbd3         125         ADR<23>         161         Reserved           18         D<19>         54         RAS2#         90         BE3#         126         MEXC#         162         [ASISEL           19         D<18>         55         RAS3#         91         BE2#         127         Vss         163         [EMUBRK           20         D<17>         56         Vod3         92         BE1#         128         ADR<24>         164         [EMUBRK           21         D<16>         57         CAS0#         93         BE0#         129         ADR<25>         165         Vod3           22         BTEST#         58         CAS1#         94         Vss         130                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 12         | V <sub>DD5</sub> | 48         | DWE1#            | 84         | CS3#             | 120        | ADR<19>          | 156        | IRQ11            |

| 15                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 13         | D<23>            | 49         | DWE0#            | 85         | CS2#             | 121        | V <sub>DD5</sub> | 157        | IRQ10            |

| 16                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 14         | D<22>            | 50         | Vss              | 86         | CS1#             | 122        | ADR<20>          | 158        | IRQ9             |

| 17                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 15         | D<21>            | 51         | V <sub>DD5</sub> | 87         | CS0#             | 123        | ADR<21>          | 159        | IRQ8             |

| 18         D<19>         54         RAS2#         90         BE3#         126         MEXC#         162         [ASISEL IP]           19         D<18>         55         RAS3#         91         BE2#         127         Vss         163         [EMUBRK           20         D<17>         56         VDD3         92         BE1#         128         ADR<24>         164         [EMUENB           21         D<16>         57         CAS0#         93         BE0#         129         ADR<25>         165         VDD3           22         BTEST#         58         CAS1#         94         Vss         130         ADR<26>         166         [EMUSD           23         VDD3         59         CAS2#         95         NONCACHE#         131         ADR<27>         167         [EMUSD           24         D<15>         60         CAS3#         96         Reserved         132         VDD3         16         [EMUSD           25         D<14>         61         Vss         97         Reserved         133         Vss         169         [EMUSD           26         D<13>         62         DOE#         98         ADR<<2>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 16         | D<20>            | 52         | RAS0#            | 88         | Vss              | 124        | ADR<22>          | 160        | Vss              |

| 19                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 17         | Vss              | 53         | RAS1#            | 89         | V <sub>DD3</sub> | 125        | ADR<23>          | 161        | Reserved         |

| 20         D<17>         56         VDD3         92         BE1#         128         ADR<24>         164         [EMUENB           21         D<16>         57         CASO#         93         BE0#         129         ADR<25>         165         VDD3           22         BTEST#         58         CAS1#         94         Vss         130         ADR<26>         166         [EMUSD           23         VDD3         59         CAS2#         95         NONCACHE#         131         ADR<27>         167         [EMUSD           24         D<15>         60         CAS3#         96         Reserved         132         VDD3         16         [EMUSD           25         D<14>         61         Vss         97         Reserved         133         Vss         169         [EMUSD           26         D<13>         62         DOE#         98         ADR<2>         134         ASI<3>[/ADR<28>]         170         VDD5           27         D<12>         63         CLKSEL2 *         99         ADR<3>         135         ASI<2>[/ADR<29>]         171         Vss           28         Vss         64         ERROR#         100                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 18         | D<19>            | 54         | RAS2#            | 90         | BE3#             | 126        | MEXC#            | 162        | [ASISEL *]       |

| 21         D<16>         57         CASO#         93         BEO#         129         ADR<25>         165         VDD3           22         BTEST#         58         CAS1#         94         Vss         130         ADR<26>         166         [EMUSD           23         VDD3         59         CAS2#         95         NONCACHE#         131         ADR<27>         167         [EMUSD           24         D<15>         60         CAS3#         96         Reserved         132         VDD3         16         [EMUSD           25         D<14>         61         Vss         97         Reserved         133         Vss         169         [EMUSD           26         D<13>         62         DOE#         98         ADR<2>         134         ASI<3>[/ADR<28>]         170         VDD5           27         D<12>         63         CLKSEL2 *         99         ADR<3>         135         ASI<2>[/ADR<29>]         171         Vss           28         Vss         64         ERROR#         100         VDD5         136         ASI<1>[/ADR<30>]         172         [EMUD3           29         D<11>         65         LOCK#         101<                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 19         | D<18>            | 55         | RAS3#            | 91         | BE2#             | 127        | Vss              | 163        | [EMUBRK# *]      |

| 22         BTEST#         58         CAS1#         94         Vss         130         ADR<26>         166         [EMUSD           23         Vddd         59         CAS2#         95         NONCACHE#         131         ADR<27>         167         [EMUSD           24         D<15>         60         CAS3#         96         Reserved         132         Vddd         166         [EMUSD           25         D<14>         61         Vss         97         Reserved         133         Vss         169         [EMUSD           26         D<14>         61         Vss         97         Reserved         133         Vss         169         [EMUSD           26         D<14>         62         DOE#         98         ADR<2>         134         ASI<3>[/ADR<28>]         170         Vdds           27         D<12>         63         CLKSEL2 *         99         ADR<3>         135         ASI<2>[/ADR<29>]         171         Vss           28         Vss         64         ERROR#         100         Vdds         136         ASI<1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 20         | D<17>            | 56         | V <sub>DD3</sub> | 92         | BE1#             | 128        | ADR<24>          | 164        | [EMUENB# *]      |

| 23         VDD3         59         CAS2#         95         NONCACHE#         131         ADR<27>         167         [EMUSD           24         D<15>         60         CAS3#         96         Reserved         132         VDD3         16         [EMUSD           25         D<14>         61         Vss         97         Reserved         133         Vss         169         [EMUSD           26         D<13>         62         DOE#         98         ADR<2>         134         ASI<3>[/ADR<28>]         170         VDD5           27         D<12>         63         CLKSEL2 *         99         ADR<3>         135         ASI<2>[/ADR<29>]         171         Vss           28         Vss         64         ERROR#         100         VDD5         136         ASI<1>[/ADR<30>]         172         [EMUD3           29         D<11>         65         LOCK#         101         ADR<4>         137         ASI<0>[/ADR<31>]         173         [EMUD3           30         D<10>         66         CTEST#         102         ADR<5>         138         Vss         174         [EMUD3           31         D<9>         67         VDD5                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 21         | D<16>            | 57         | CAS0#            | 93         | BE0#             | 129        | ADR<25>          | 165        | V <sub>DD3</sub> |

| 24         D<15>         60         CAS3#         96         Reserved         132         VDD3         16         [EMUSD           25         D<14>         61         Vss         97         Reserved         133         Vss         169         [EMUSD           26         D<13>         62         DOE#         98         ADR<2>         134         ASI<3>[/ADR<28>]         170         VDD5           27         D<12>         63         CLKSEL2 *         99         ADR<3>         135         ASI<2>[/ADR<29>]         171         Vss           28         Vss         64         ERROR#         100         VDD5         136         ASI<1>[/ADR<30>]         172         [EMUD3           29         D<11>         65         LOCK#         101         ADR<4>         137         ASI<0>[/ADR<31>]         173         [EMUD3           30         D<10>         66         CTEST#         102         ADR<5>         138         Vss         174         [EMUD3           31         D<9>         67         VDD5         103         ADR<6>         139         VDD5         175         [EMUD3           32         D<8>         68         BREQ#         <                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 22         | BTEST#           | 58         | CAS1#            | 94         | Vss              | 130        | ADR<26>          | 166        | [EMUSD3]         |

| 25         D<14>         61         Vss         97         Reserved         133         Vss         169         [EMUSD           26         D<13>         62         DOE#         98         ADR<2>         134         ASI<3>[/ADR<28>]         170         VDD5           27         D<12>         63         CLKSEL2 *         99         ADR<3>         135         ASI<2>[/ADR<29>]         171         Vss           28         Vss         64         ERROR#         100         VDD5         136         ASI<1>[/ADR<30>]         172         [EMUD3           29         D<11>         65         LOCK#         101         ADR<4>         137         ASI<0>[/ADR<31>]         173         [EMUD2           30         D<10>         66         CTEST#         102         ADR<5>         138         Vss         174         [EMUD2           31         D<9>         67         VDD5         103         ADR<6>         139         VDD5         175         [EMUD0           32         D<8>         68         BREQ#         104         ADR<7>         140         IRL<3>/IRQ15         176         Vss           33         VDD5         69         PBREQ#                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 23         | V <sub>DD3</sub> | 59         | CAS2#            | 95         | NONCACHE#        | 131        | ADR<27>          | 167        | [EMUSD2]         |

| 26         D<13>         62         DOE#         98         ADR<2>         134         ASI<3>[/ADR<28>]         170         VDD5           27         D<12>         63         CLKSEL2 *         99         ADR<3>         135         ASI<2>[/ADR<29>]         171         Vss           28         Vss         64         ERROR#         100         VDD5         136         ASI<1>[/ADR<30>]         172         [EMUD3           29         D<11>         65         LOCK#         101         ADR<4>         137         ASI<0>[/ADR<31>]         173         [EMUD3           30         D<10>         66         CTEST#         102         ADR<5>         138         Vss         174         [EMUD4           31         D<9>         67         VDD5         103         ADR<6>         139         VDD5         175         [EMUD4           32         D<8>         68         BREQ#         104         ADR<7>         140         IRL<3>/IRQ15         176         Vss           33         VDD5         69         PBREQ#         105         Vss         141         IRL<2>/IRQ14           34         D<7>         70         BGRNT#         106         ADR<8> <td>24</td> <td>D&lt;15&gt;</td> <td>60</td> <td>CAS3#</td> <td>96</td> <td>Reserved</td> <td>132</td> <td>V<sub>DD3</sub></td> <td>16</td> <td>[EMUSD1]</td>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 24         | D<15>            | 60         | CAS3#            | 96         | Reserved         | 132        | V <sub>DD3</sub> | 16         | [EMUSD1]         |

| 27         D<12>         63         CLKSEL2 *         99         ADR<3>         135         ASI<2>[/ADR<29>]         171         Vss           28         Vss         64         ERROR#         100         Vdds         136         ASI<1>[/ADR<30>]         172         [EMUD3           29         D<11>         65         LOCK#         101         ADR<4>         137         ASI<0>[/ADR<31>]         173         [EMUD2           30         D<10>         66         CTEST#         102         ADR<5>         138         Vss         174         [EMUD0           31         D<9>         67         Vdds         103         ADR<6>         139         Vdds         175         [EMUD0           32         D<8>         68         BREQ#         104         ADR<7>         140         IRL<3>/IRQ15         176         Vss           33         Vdds         69         PBREQ#         105         Vss         141         IRL<2>/IRQ14           34         D<7>         70         BGRNT#         106         ADR<8>         142         IRL<1>/IRQ13           35         D<6>         71         BMACK#         107         ADR<9>         143         IRL<0>/IR                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 25         | D<14>            | 61         | Vss              | 97         | Reserved         | 133        | Vss              | 169        | [EMUSD0]         |

| 28         Vss         64         ERROR#         100         Vdds         136         ASI<1>[/ADR<30>]         172         [EMUD3           29         D<11>         65         LOCK#         101         ADR<4>         137         ASI<0>[/ADR<31>]         173         [EMUD3           30         D<10>         66         CTEST#         102         ADR<5>         138         Vss         174         [EMUD3           31         D<9>         67         Vdds         103         ADR<6>         139         Vdds         175         [EMUD3           32         D<8>         68         BREQ#         104         ADR<7>         140         IRL<3>/IRQ15         176         Vss           33         Vdds         69         PBREQ#         105         Vss         141         IRL<2>/IRQ14           34         D<7>         70         BGRNT#         106         ADR<8>         142         IRL<1>/IRQ13           35         D<6>         71         BMACK#         107         ADR<9>         143         IRL<0>/IRQ12                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 26         | D<13>            | 62         | DOE#             | 98         | ADR<2>           | 134        | ASI<3>[/ADR<28>] | 170        | V <sub>DD5</sub> |

| 29         D<11>         65         LOCK#         101         ADR<4>         137         ASI<0>[/ADR<31>]         173         [EMUD2           30         D<10>         66         CTEST#         102         ADR<5>         138         Vss         174         [EMUD0           31         D<9>         67         VDD5         103         ADR<6>         139         VDD5         175         [EMUD0           32         D<8>         68         BREQ#         104         ADR<7>         140         IRL<3>/IRQ15         176         Vss           33         VDD5         69         PBREQ#         105         Vss         141         IRL<2>/IRQ14           34         D<7>         70         BGRNT#         106         ADR<8>         142         IRL<1>/IRQ13           35         D<6>         71         BMACK#         107         ADR<9>         143         IRL<0>/IRQ12                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 27         | D<12>            | 63         | CLKSEL2 *        | 99         | ADR<3>           | 135        | ASI<2>[/ADR<29>] | 171        | Vss              |