# MOS INTEGRATED CIRCUIT $\mu$ PD78P218A

### **8-BIT SINGLE-CHIP MICROCOMPUTER**

#### DESCRIPTION

The  $\mu$ PD78P218A, a product of the 78K/II series, is an 8-bit single-chip microcomputer which one-time PROM or EPROM in place of the mask ROM in the  $\mu$ PD78218A. Since the  $\mu$ PD78P218A is user-programmable, it is suitable for system development evaluation and small production.

Functions are described in detail in the following user's manuals, which should be read when carrying out design work

$\mu PD78218A$  Subseries User's Manual Hardware Volume: IEM-755 78K/II Series User's Manual Instruction Volume: IEU-754

#### **FEATURES**

- Upward compatibility with the µPD78214 subseries (pin compatibility)

- Compatibility with the  $\mu$ PD78218A (except PROM programming)

- High-speed instruction execution (at 12 MHz operation): 333ns

- On-chip memory

- PROM: 32K bytes

µPD78P218ADW : Reprogrammable (suitable for system evaluation)

µPD78P218ACW, GC: Programmable only once (suitable for small production)

- RAM: 1024 bytes

- QTOP™ microcomputer compatibility

- **Remarks** The QTOP microcomputer is a general term for one-time PROM incorporated single-chip microcomputers offered by NEC, which cover totally program writing, marking, screening and verification.

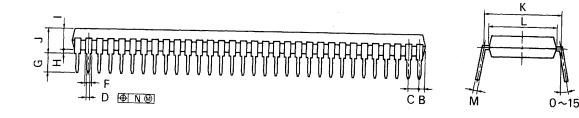

#### ORDERING INFORMATION

| Ordering Code    | Package                                                      | On-Chip ROM   |

|------------------|--------------------------------------------------------------|---------------|

| μPD78P218ACW     | 64-pin plastic shrink DIP (750 mil)                          | One-time PROM |

| μPD78P218AGC-AB8 | 64-pin plastic QFP (🗆 14 mm)                                 | One-time PROM |

| μPD78P218ADW     | 64-pin ceramic shrink DIP (CERDIP)<br>(with window) (750mil) | EPROM         |

#### **QUALITY GRADE**

Standard

Please refer to "Quality grade on NEC Semiconductor Devices" (Document number IEI-1209) published by NEC Corporation to know the specification of quality grade on the devices and its recommended applications. In this manual, PROM indicates the features common to the one-time PROM products and the EPROM.

The information in this document is subject to change without notice.

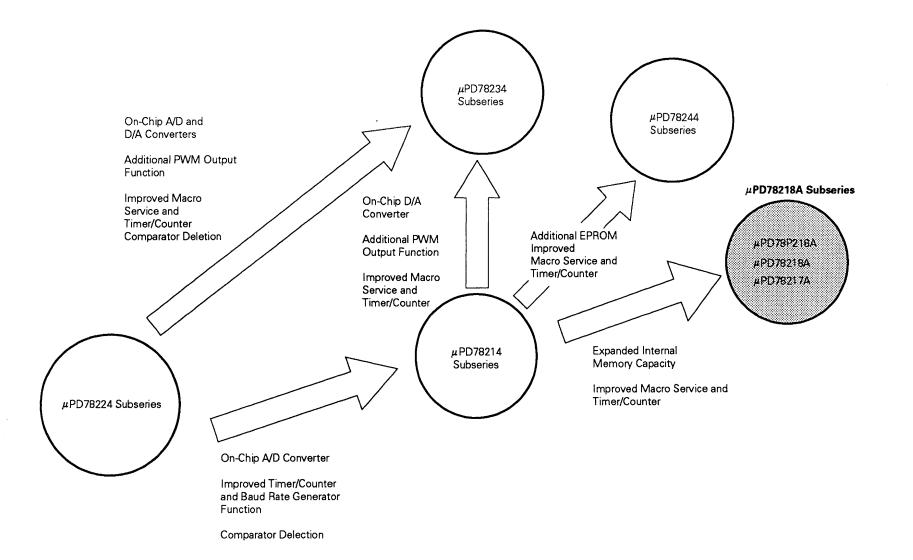

78K/II Product Developments

N

$\mu$ PD78P218A

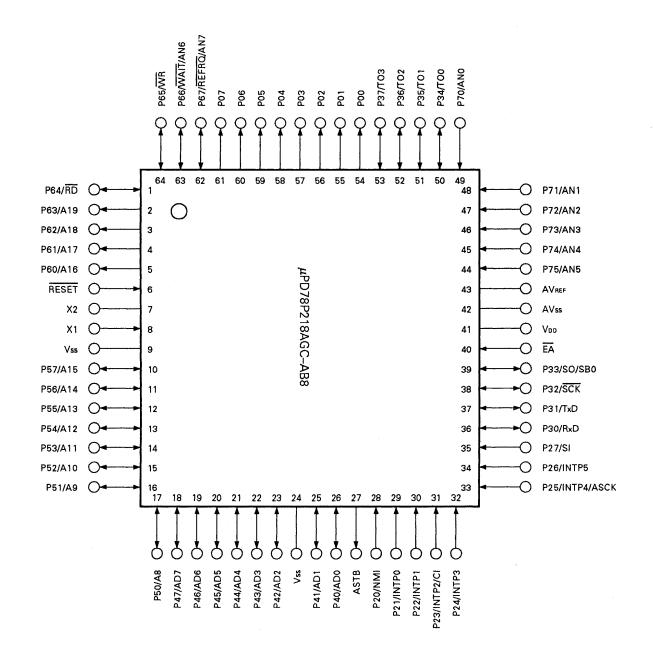

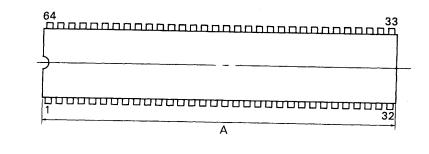

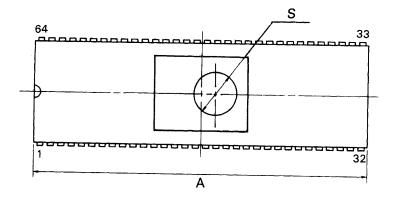

#### PIN CONFIGURATION (TOP VIEW)

(1) Normal operating modes

|               |                            |    | /                            |    |             |                |

|---------------|----------------------------|----|------------------------------|----|-------------|----------------|

| P03           | ○                          | 1  | $\mathbf{\circ}$             | 64 | <b></b> O   | P02            |

| P04           | `⊖                         | 2  |                              | 63 | 0           | P01            |

| P05           | ○                          | 3  |                              | 62 | <b></b> O   | P00            |

| P06           | ○                          | 4  |                              | 61 | <b></b> 0   | P37/TO3        |

| P07           | ○                          | 5  |                              | 60 | <b>←→</b> O | P36/TO2        |

| P67/REFRQ/AN7 | ○                          | 6  |                              | 59 | <b></b> ►O  | P35/TO1        |

| P66/WAIT/AN6  | ○                          | 7  |                              | 58 | <b></b> 0   | P34/TO0        |

| P65/WR        | 0                          | 8  |                              | 57 | 0           | P70/AN0        |

| P64/RD        | 0                          | 9  |                              | 56 | <b></b> 0   | P71/AN1        |

| P63/A19       | ○                          | 10 |                              | 55 | 0           | P72/AN2        |

| P62/A18       | 0-                         | 11 |                              | 54 |             | P73/AN3        |

| P61/A17       | 0                          | 12 |                              | 53 | 0           | P74/AN4        |

| P60/A16       | 0-                         | 13 | μP                           | 52 | <b>←</b> O  | P75/AN5        |

| RESET         | 0                          | 14 | D78<br>D78                   | 51 |             | AVREF          |

| X2            | $\circ$                    | 15 | uPD78P218ACW<br>uPD78P218ADW | 50 | 0           | AVss           |

| X1            | 0                          | 16 | 8A(                          | 49 | 0           | Vdd            |

| Vss           | 0                          | 17 | N N                          | 48 | <b></b> O   | ĒĀ             |

| P57/A15       | 0                          | 18 |                              | 47 | <b></b> 0   | P33/SO/SB0     |

| P56/A14       | ○→→                        | 19 |                              | 46 | <b></b> O   | P32/SCK        |

| P55/A13       | ○◄-►                       | 20 |                              | 45 | <b>→→</b> O | P31/TxD        |

| P54/A12       | 0                          | 21 |                              | 44 | <b></b> O   | P30/RxD        |

| P53/A11       | 0                          | 22 |                              | 43 |             | P27/SI         |

| P52/A10       | ○                          | 23 |                              | 42 | 0           | P26/INTP5      |

| P51/A9        | ○>                         | 24 |                              | 41 | <b>-</b> O  | P25/INTP4/ASCK |

| P50/A8        | $\bigcirc \bullet \bullet$ | 25 |                              | 40 | <b></b> 0   | P24/INTP3      |

| P47/AD7       | ○>                         | 26 |                              | 39 | 0           | P23/INTP2/CI   |

| P46/AD6       | ○>                         | 27 |                              | 38 | 0           | P22/INTP1      |

| P45/AD5       | ○                          | 28 |                              | 37 | 0           | P21/INTP0      |

| P44/AD4       | ○                          | 29 |                              | 36 | 0           | P20/NMI        |

| P43/AD3       | ○                          | 30 |                              | 35 | <b></b> O   | ASTB           |

| P42/AD2       | ○→→                        | 31 |                              | 34 | <b></b> O   | P40/AD0        |

| Vss           | 0                          | 32 |                              | 33 | <b>→</b> •0 | P41/AD1        |

|               | -                          |    |                              |    |             |                |

(a) 64-pin plastic shrink DIP and 64-pin ceramic shrink DIP (CERDIP) (with window)

(b) 64-pin plastic QFP

NEC

4

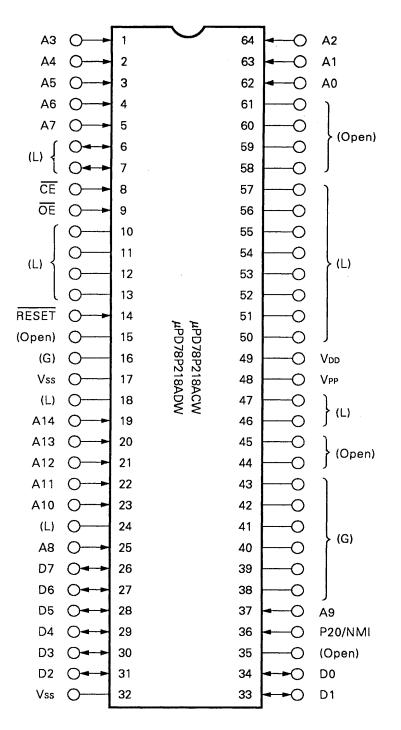

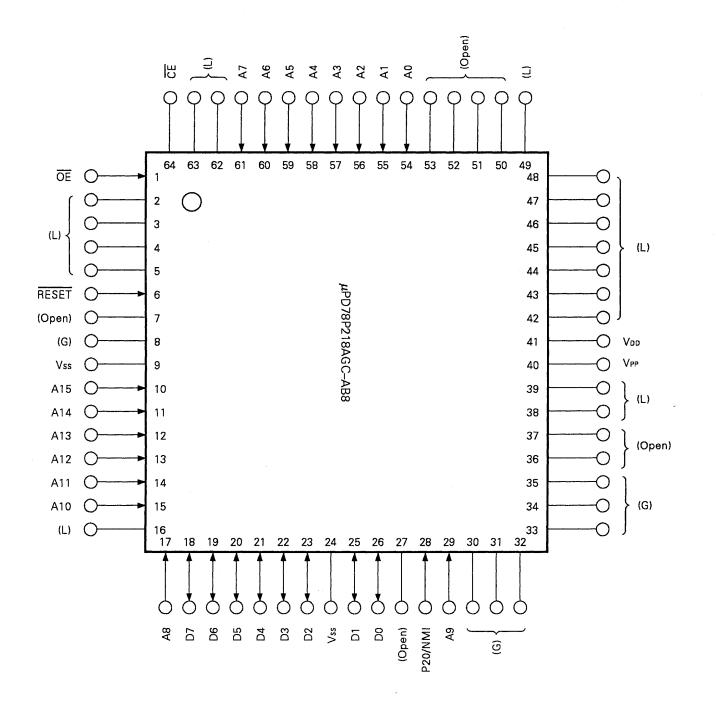

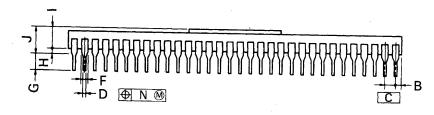

- (2) PROM programming mode (P20/NMI = 12.5 V, RESET = L)

- (a) 64-pin plastic shrink DIP and 64-pin ceramic shrink DIP (CERDIP) (with window)

- Note Processing for pins which are not used in the PROM programming mode is indicated in parentheses.

- L : Connect these pins independently to Vss via a 10 k $\Omega$  resistor.

- G : Connect these pins to Vss.

Open : Leave open.

$\star$

(b) 64-pin plastic QFP

Processing for pins which are not used in the PROM programming mode is indicated in parentheses. Note L

: Connect these pins independently to Vss via a 10  $k\Omega$  resistor.

G : Connect these pins to Vss.

Open : Leave open.

6

★

| P00 to P07       | : Port 0                     | RD         | : Read Strobe              |

|------------------|------------------------------|------------|----------------------------|

| P20 to P27       | : Port 2                     | WR         | : Write Strobe             |

| P30 to P37       | : Port 3                     | WAIT       | : Wait                     |

| P40 to P47       | : Port 4                     | ASTB       | : Address Strobe           |

| P50 to P57       | : Port 5                     | REFRQ      | : Refresh Request          |

| P60 to P67       | : Port 6                     | RESET      | : Reset                    |

| P70 to P75       | : Port 7                     | X1, X2     | : Crystal                  |

| TO0 to TO3       | : Timer Output               | ĒĀ         | : External Access          |

| CI               | : Clock input                | AN0 to AN7 | : Analog Input             |

| R×D              | : Receive Data               | AVREF      | : Reference Voltage        |

| T <sub>×</sub> D | : Transmit Data              | AVss       | : Analog Ground            |

| SCK              | : Serial Clock               | Vdd        | : Power Supply             |

| ASCK             | : Asynchronous Serial Clock  | Vss        | : Ground                   |

| SB0              | : Serial Bus                 | CE         | : Chip Enable              |

| SI               | : Serial Input               | OE         | : Output Enable            |

| SO               | : Serial Output              | Vpp        | : Programming Power Supply |

| NMI              | : Non-maskable interrupt     |            |                            |

| INTP0 to INTP5   | : Interrupt From Peripherals |            |                            |

| AD0 to AD7       | : Address/Data Bus           |            |                            |

| A8 to A19        | : Address Bus                |            |                            |

.

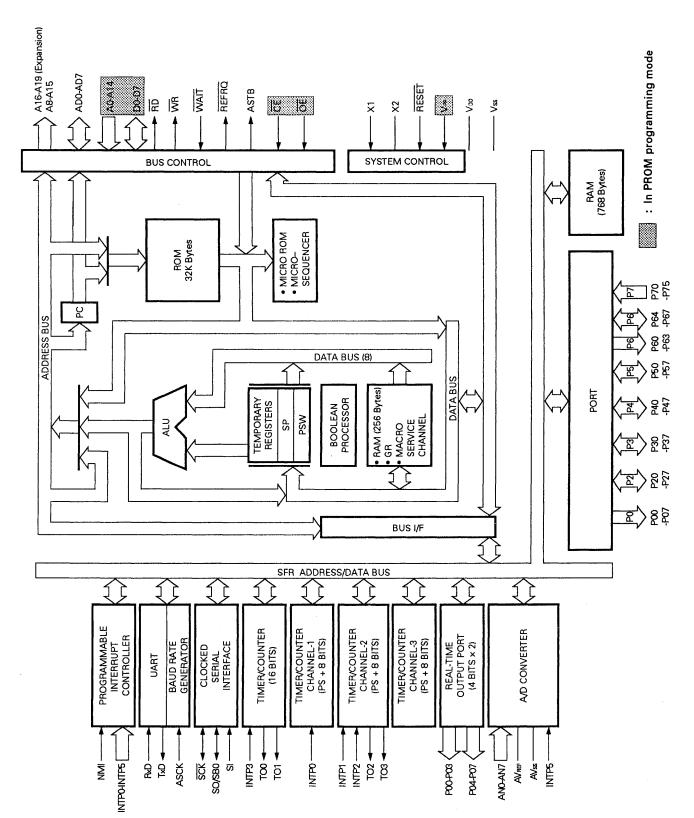

#### **INTERNAL BLOCK DIAGRAM**

8

.

#### CONTENTS

| 1. | DIFFERENCE BETWEEN µPD78218A AND µPD78214 SUBSERIES                                     | 0 |

|----|-----------------------------------------------------------------------------------------|---|

| 2. | PIN FUNCTIONS1                                                                          | 1 |

|    | 2.1 NORMAL OPERATING MODE                                                               |   |

|    | 2.2 PROM PROGRAMMING MODE                                                               | 3 |

| 3. | PROGRAMMING1                                                                            | 4 |

|    | 3.1 OPERATING MODE1                                                                     | 4 |

|    | 3.2 PROM WRITE PROCEDURE1                                                               |   |

|    | 3.3 PROM READ PROCEDURE                                                                 | 7 |

| 4. | ERASURE CHARACTERISTICS (µPD78P218ADW ONLY)1                                            | 8 |

| 5. | ERASURE WINDOW SEALING (µPD78P218ADW ONLY)1                                             | 8 |

| 6. | SCREENING OF ONE-TIME PROM PRODUCTS1                                                    | 8 |

| 7. | ELECTRICAL SPECIFICATIONS1                                                              | 9 |

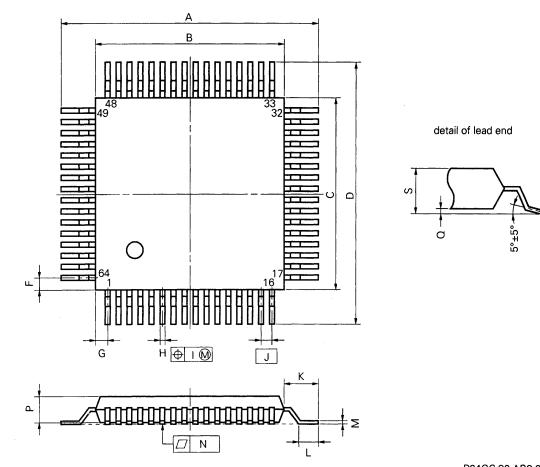

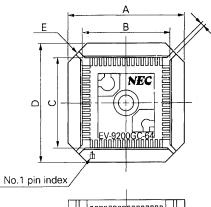

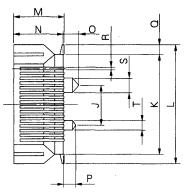

| 8. | PACKAGE INFORMATION                                                                     | 9 |

| 9. | RECOMMENDED SOLDERING CONDITIONS                                                        | 2 |

| AP | PENDIX A. DEVELOPMENT TOOLS                                                             | 3 |

| AP | PENDIX B. EXTERNAL VIEW OF CONVERSION SOCKET<br>AND RECOMMENDED BOARD MOUNTING PATTERN4 | 5 |

| AP | PENDIX C. RELATED DOCUMENTS                                                             | 7 |

| Series                                                                         |                          |                                                                                                                                                                          | µPD78218A Subseries                                                                    |                                                 |                                                                                                                                                                                                                                                             | μPD78214 Subseries                                                                                                                                                                                                                                                              | Subseries                                                                                            |                     |

|--------------------------------------------------------------------------------|--------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------|-------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------|---------------------|

| Product Name                                                                   | ime                      | μ <sup>PD78217A</sup>                                                                                                                                                    | µPD78218A                                                                              | μPD78P218A                                      | μΡD78212                                                                                                                                                                                                                                                    | µPD78213                                                                                                                                                                                                                                                                        | μΡD78214                                                                                             | µPD78P214           |

| Minimum instruction cycle<br>(at 12 MHz operation)                             | ycle                     | 500 ns                                                                                                                                                                   | 333 ns                                                                                 | su                                              | 333 ns                                                                                                                                                                                                                                                      | 500 ns                                                                                                                                                                                                                                                                          | 333 ns                                                                                               | US                  |

| PUSH PSW instruction execution time (number of clocks)                         | n execution<br>s)        | When the stack area is Other than above: 8                                                                                                                               | s internal dual-port RAM: 6                                                            | 9                                               | When the stack are<br>Other than above: 7                                                                                                                                                                                                                   | When the stack area is internal dual-port RAM: 5 or 7 Other than above: 7 or 9                                                                                                                                                                                                  | rt RAM: 5 or 7                                                                                       |                     |

| Supply voltage range                                                           |                          | +5 V ±                                                                                                                                                                   | 10%                                                                                    | +5 V ± 0.3 V                                    |                                                                                                                                                                                                                                                             | +5 V ± 10                                                                                                                                                                                                                                                                       | %                                                                                                    |                     |

| On-chip<br>memory                                                              | ROM                      | ROM-less                                                                                                                                                                 | 32K bytes<br>(Mask ROM)                                                                | 32K bytes<br>(PROM)                             | 8K bytes<br>(Mask ROM)                                                                                                                                                                                                                                      | ROM-less                                                                                                                                                                                                                                                                        | 16K bytes<br>(Mask ROM)                                                                              | 16K bytes<br>(PROM) |

|                                                                                | RAM                      |                                                                                                                                                                          | 1024 bytes                                                                             |                                                 | 384 bytes                                                                                                                                                                                                                                                   |                                                                                                                                                                                                                                                                                 | 512 bytes                                                                                            |                     |

| Number of I/O pins                                                             |                          | 96                                                                                                                                                                       | 54                                                                                     |                                                 | 54                                                                                                                                                                                                                                                          | œ                                                                                                                                                                                                                                                                               | 54                                                                                                   |                     |

| AVREF input voltage                                                            |                          |                                                                                                                                                                          | 3.6 V to V <sub>DD</sub>                                                               |                                                 |                                                                                                                                                                                                                                                             | 3.4 V                                                                                                                                                                                                                                                                           | 3.4 V to V <sub>DD</sub>                                                                             |                     |

| Restrictions concerning input voltage                                          | input                    | 0V to AV <sub>REF</sub> pin voltage is al<br>during A/D conversion only                                                                                                  | e is applied to pins relevant to A/D conversion only                                   | nt to A/D conversion                            | Constant 0V to AVREF pin voltag<br>register ANI0 to ANI2 bits only.                                                                                                                                                                                         | И <sub>REF</sub> pin voltage is ap<br>NI2 bits only.                                                                                                                                                                                                                            | Constant OV to AVREF pin voltage is applied to pins selected by ADM register ANI0 to ANI2 bits only. | d by ADM            |

| 16-bit timer/counter one-shot pulse<br>output                                  | ne-shot pulse            |                                                                                                                                                                          | Yes                                                                                    |                                                 |                                                                                                                                                                                                                                                             | No                                                                                                                                                                                                                                                                              | 0                                                                                                    |                     |

| Macro service counter bit width                                                | r bit width              | 8-/16-bit select capability (except type A)                                                                                                                              | ity (except type A)                                                                    |                                                 |                                                                                                                                                                                                                                                             | only 8-bit                                                                                                                                                                                                                                                                      | 8-bit                                                                                                |                     |

| Macro service type C MPD, MPT<br>increment                                     | MPD, MPT                 |                                                                                                                                                                          | 16-bit increment                                                                       |                                                 | Only low-order 8-bi                                                                                                                                                                                                                                         | its increment (High≺                                                                                                                                                                                                                                                            | Only low-order 8-bits increment (High-order 8 bits are unchanged.)                                   | anged.)             |

| Macro service execution time                                                   | ion time                 | Varies depending on mode.                                                                                                                                                |                                                                                        | Please refer to users manual with each product. | oduct.                                                                                                                                                                                                                                                      |                                                                                                                                                                                                                                                                                 |                                                                                                      |                     |

| Restrictions in data transfer from<br>memory of macro service type<br>A to SFR | ansfer from<br>vice type | Generates when addree<br>is 0FED0H to 0FEDFH                                                                                                                             | Generates when address range of transfer source buffer (memory)<br>is 0FED0H to 0FEDFH | rce buffer (memory)                             | Generates when t                                                                                                                                                                                                                                            | ransfer data is in the                                                                                                                                                                                                                                                          | Generates when transfer data is in the range of D0H to DFH.                                          | Ť                   |

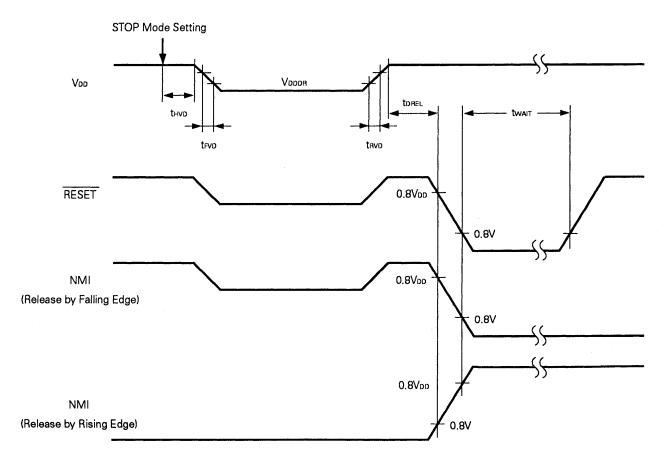

| Stabilization time for oscillation when STOP mode is released                  | oscillation<br>released  | Dedicated counter 15  <br>counter 16 bits                                                                                                                                | Dedicated counter 15 bits or <u>NMI</u> active pulse width + dedicated counter 16 bits | width + dedicated                               | <u>NMI</u> active pulse v                                                                                                                                                                                                                                   | NMI active pulse width + dedicated counter 16 bits                                                                                                                                                                                                                              | ounter 16 bits                                                                                       |                     |

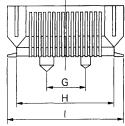

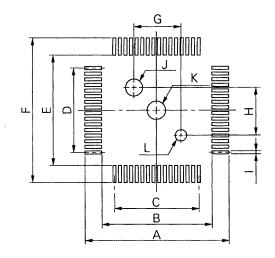

| Package                                                                        |                          | <ul> <li>64-pin plastic shrink DIP (750 mil)</li> <li>64-pin plastic QFP (□14 mm)</li> <li>64-pin ceramic shrink DIP (CERD)</li> <li>(750mil):μPD78P218A only</li> </ul> | DIP (750 mil)<br>⊐14 mm)<br>k DIP (CERDIP) (with window)<br>A only                     | (wop                                            | <ul> <li>64-pin plastic shrink DIP (750 mil)</li> <li>64-pin plastic OUIP: Except μPD7</li> <li>68-pin plastic OF9 ( Π 14 mm)</li> <li>74-pin plastic OFP ( Π 20 mm)</li> <li>64-pin ceramic shrink DIP (CERD)</li> <li>(750mil): μPD78P214 only</li> </ul> | <ul> <li>64-pin plastic shrink DIP (750 mil)</li> <li>64-pin plastic QUIP: Except μPD78212</li> <li>68-pin plastic QFP ( □ 14 mm)</li> <li>74-pin plastic QFP ( □ 20 mm)</li> <li>64-pin ceramic shrink DIP (CERDIP) (with window)</li> <li>(750mil): μPD78P214 only</li> </ul> | 12<br>2<br>(with window)                                                                             |                     |

#### 1. DIFFERENCES BETWEEN $\mu$ PD78218A AND $\mu$ PD78214 SUBSERIES

#### 2. PIN FUNCTIONS

#### 2.1 NORMAL OPERATING MODE

#### (1) Ports

| Pin Name   | 1/0              | Dual-<br>Function Pin | Function                                                                                                                                                                                                       |

|------------|------------------|-----------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| P00 to P07 | Output           |                       | Port 0 (P0):<br>Use enabled as a real-time output port (4 bits × 2)<br>Transistor drive possible                                                                                                               |

| P20        |                  | NMI                   |                                                                                                                                                                                                                |

| P21        |                  | INTP0                 | Port 2 (P2):                                                                                                                                                                                                   |

| P22        | 1                | INTP1                 | P20 is disabled for use as a general-purpose port (nonmaskable interrupt).                                                                                                                                     |

| P23        | Input            | INTP2/CI              | However, input level can be checked in the interrupt routine.                                                                                                                                                  |

| P24        |                  | INTP3                 | Specification of the internal pull-up resistor for P22 to P27 by software in 6-bit units is possible.                                                                                                          |

| P25        |                  | INTP/ASCK             | is possible.                                                                                                                                                                                                   |

| P26        |                  | INTP5                 |                                                                                                                                                                                                                |

| P27        |                  | SI                    |                                                                                                                                                                                                                |

| P30        |                  | RxD                   | Port 3 (P3):                                                                                                                                                                                                   |

| P31        | Input/           | TxD                   | Input/output specifiable bit-wise.                                                                                                                                                                             |

| P32        | output           | SCK                   | Concerning input mode pins, specification of the internal pull-up resistor by software                                                                                                                         |

| P33        | 1                | SO/SB0                | at one time is possible.                                                                                                                                                                                       |

| P34 to P37 | 1                | TO0 to TO3            |                                                                                                                                                                                                                |

| P40 to P47 | Input/<br>output | AD0 to AD7            | Port 4 (P4):<br>Input/output specifiable in 8-bit units at one time.<br>Specification of the internal pull-up resistor by software in 8-bit units at one time is<br>possible.<br>LED direct drive is possible. |

| P50 to P57 | Input/<br>output | A8 to A15             | Port 5 (P5):<br>Input/output specifiable bit-wise.<br>Concerning input mode pins, specification of the internal pull-up resistor by software<br>at one time is possible.<br>LED direct drive capability.       |

| P60 to P63 | Output           | A16 to A19            | Port 6 (P6):                                                                                                                                                                                                   |

| P64        |                  | RD                    | Input/output specifiable bit-wise for P64 to P67.                                                                                                                                                              |

| P65        | Input/           | WR                    | Concerning input mode pins, specification of the internal pull-up resistor by software                                                                                                                         |

| P66        | output           | WAIT/AN6              | at one time is possible for P64 to P67.                                                                                                                                                                        |

| P67        |                  | REFRQ/AN7             |                                                                                                                                                                                                                |

| P70 to P75 | Input            | AN0 to AN5            | Port 7 (P7)                                                                                                                                                                                                    |

#### (2) Other Than Ports

| Pin Name   | 1/0              | Function                                                                                       | Dual-<br>Function Pin  |

|------------|------------------|------------------------------------------------------------------------------------------------|------------------------|

| TO0 to TO3 | Output           | Timer output                                                                                   | P34 to P37             |

| CI         | Input            | Count clock input to 8-bit timer/counter 2                                                     | P23 /INTP2             |

| RxD        | Input            | Serial data input (UART)                                                                       | P30                    |

| TxD        | Output           | Serial data output (UART)                                                                      | P31                    |

| ASCK       | Input            | Baud rate clock input (UART)                                                                   | P25/INTP4              |

| SB0        | Input<br>/output | Serial data input/output (SBI)                                                                 | P33/SO                 |

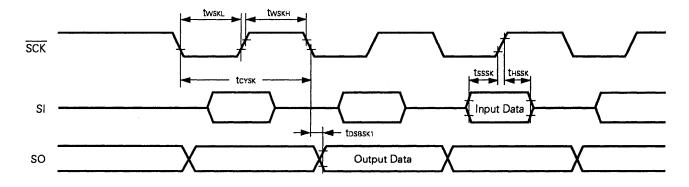

| SI         | Input            | Serial data input (3-wire serial I/O)                                                          | P27                    |

| SO         | Output           | Serial data output (3-wire serial I/O)                                                         | P33/SB0                |

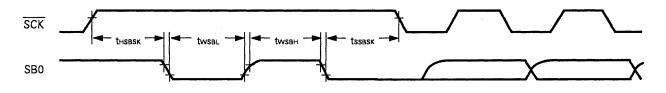

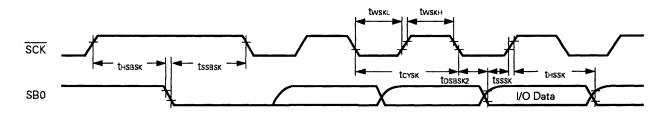

| SLK        | Input<br>/output | Serial clock input/output (SBI, 3-wire serial I/O)                                             | P32                    |

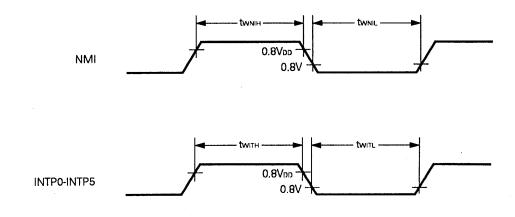

| NMI        |                  |                                                                                                | P20                    |

| INTP0      |                  |                                                                                                | P21                    |

| INTP1      |                  |                                                                                                | P22                    |

| INTP2      | Input            | External interrupt request                                                                     | P23/CI                 |

| INTP3      |                  |                                                                                                | P24                    |

| INTP4      |                  |                                                                                                | P25/ASCK               |

| INTP5      |                  |                                                                                                | P26                    |

| AD0 to AD7 | Input<br>/output | Time multiplexing address/data bus (external memory connection)                                | P40 to P47             |

| A8 to A15  | Output           | Higher address bus (external memory connection)                                                | P50 to P57             |

| A16 to A19 | Output           | Expanded higher adderss (external memory connection)                                           | P60 to P63             |

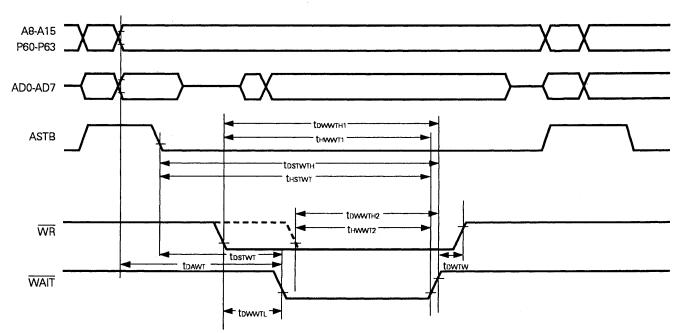

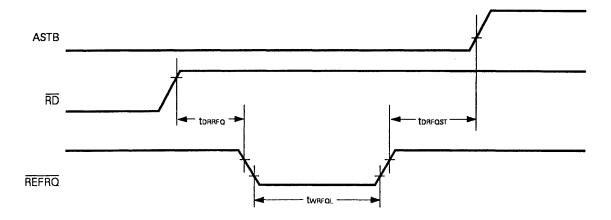

| RD         | Output           | Read strobe for external memory                                                                | P64                    |

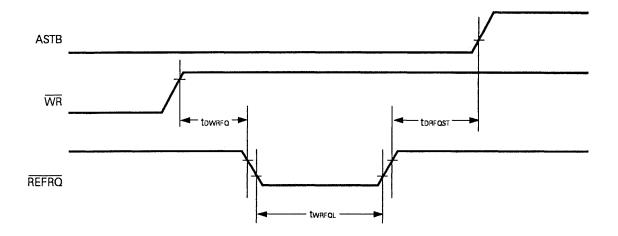

| WR         | Output           | Write strobe into external memory                                                              | P65                    |

| WAIT       | Input            | Wait insert                                                                                    | P66/AN6                |

| ASTB       | Output           | Latch timing output of time-multiplexing addresses (A0 to A7)<br>(in external memory accessed) |                        |

| REFRQ      | Output           | Refresh pulse output to external pseudo-static memory                                          | P67/AN7                |

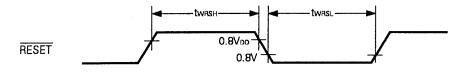

| RESET      | Input            | Chip reset                                                                                     |                        |

| X1         | Input            |                                                                                                |                        |

| X2         |                  | Crystal connection for system clock oscillation (clock input to X1 enabled)                    |                        |

| ĒĀ         | Input            | ROM-less operation specification (external access in the same space as internal ROM).          |                        |

| AN0 to AN5 |                  | · · · · · · · · · · · · · · · · · · ·                                                          | P70 to P75             |

| AN6, AN7   | Input            | Analog voltage input for A/D converter                                                         | P66/WAIT,<br>P67/REFRQ |

| AVREF      |                  | Reference voltage application for A/D converter                                                |                        |

| AVss       |                  | GND for A/D converter                                                                          |                        |

| Voo        |                  | Positive power supply                                                                          | 1 —                    |

| Vss        |                  | GND                                                                                            | 1                      |

## 2.2 PROM PROGRAMMING MODE (P20/NMI = +12.5 V, RESET = L)

| Pin Name  | Input/Output | Function              |  |

|-----------|--------------|-----------------------|--|

| P20/NMI   |              |                       |  |

| RESET     | Input        | PROM programming mode |  |

| A0 to A14 |              | Address bus           |  |

| D0 to D7  | Input/output | Data bus              |  |

| ĈĒ        |              | PROM enable input     |  |

| ŌĒ        | - Input      | Read strobe for PROM  |  |

| Vpp       |              | Write power supply    |  |

| Vdd       |              | Positive power supply |  |

| Vss       |              | GND                   |  |

#### 3. PROGRAMMING

The on-chip program memory of the  $\mu$ PD78P218A is a 32768×8-bit electrically programmable PROM. For PROM programming mode is set using the NMI and RESET pins.

The programming characteristics are compatible with the  $\mu$ PD27C256A.

#### 3.1 OPERATING MODE

When +6 V and +12.5 V are applied to V<sub>DD</sub> pin and V<sub>PP</sub> pin, respectively, the  $\mu$ PD78P218A is set to the programwrite/verify mode. This mode can be reset to the operating mode described in Table 3-1 by setting  $\overline{CE}$  and  $\overline{OE}$  pins. In the read mode, the  $\mu$ PD78P218A can read the PROM contents.

| Pin<br>Mode     | NMI      | RESET | ĈĒ | ŌĒ  | Vpp | νοσ      | D0 to D7       |             |

|-----------------|----------|-------|----|-----|-----|----------|----------------|-------------|

| Program write   |          |       | L  | н   |     |          | Data input     |             |

| Program verify  | + 12.5 V |       |    | н   | L   | + 12.5 V | + 6 V          | Data output |

| Program inhibit |          | L     | н  | н   |     |          | High-impedance |             |

| Read            |          |       |    | L   | L   |          |                | Data output |

| Output disable  |          |       |    |     | L   | н        | + 5 V          | + 5 V + 5 V |

| Standby         |          |       | н  | L/H |     |          | High-impedance |             |

#### **Table 3-1 PROM Programming Operating Mode**

Note When V<sub>PP</sub> is set to +12.5 V and V<sub>DD</sub> is set to +6 V, it is inhibited to set both  $\overline{CE}$  and  $\overline{OE}$  to L.

## NEC

#### 3.2 PROM WRITE PROCEDURE

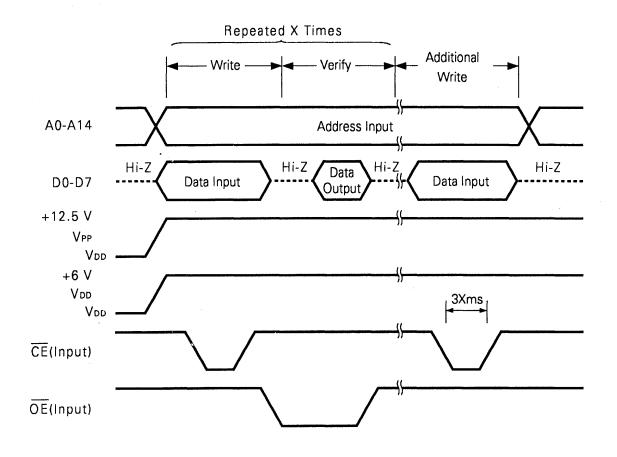

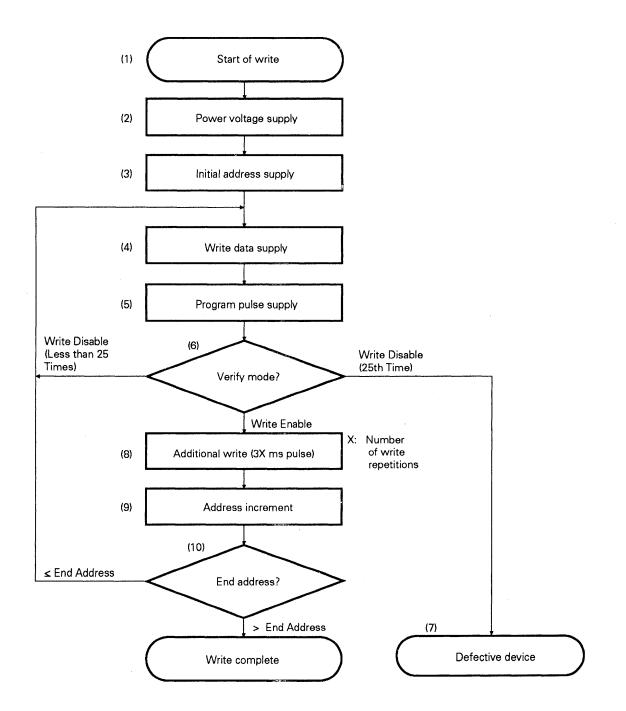

PROM write can be executed at high speeds using the following procedure:

- (1) Fix the RESET pin to the low level. Apply +12.5 V to the NMI pin. Treat all other unused pins as shown in **PIN CONFIGURATION (2)**.

- (2) Apply +6 V to the  $V_{DD}$  pin and +12.5 V to the  $V_{PP}$  pin.

- (3) Supply the initial address.

- (4) Supply write data.

- (5) Supply a 1 ms program pulse (active low) to the  $\overline{CE}$  pin.

- (6) Set the verify mode. If data has been written, procedure to step (8). If data has not been written, repeat steps

(4) to (6). If data cannot yet be written after repeating the three steps 25 times, proceed to step (7).

- (7) Stop carrying out the write operation assuming that the device is defective.

- (8) Supply write data and then supply (number of repetitions of steps (4) to (6): X) × 3ms program pulses (additional write).

- (9) Increment the address.

- (10) Repeat steps (4) to (9) up to the final address.

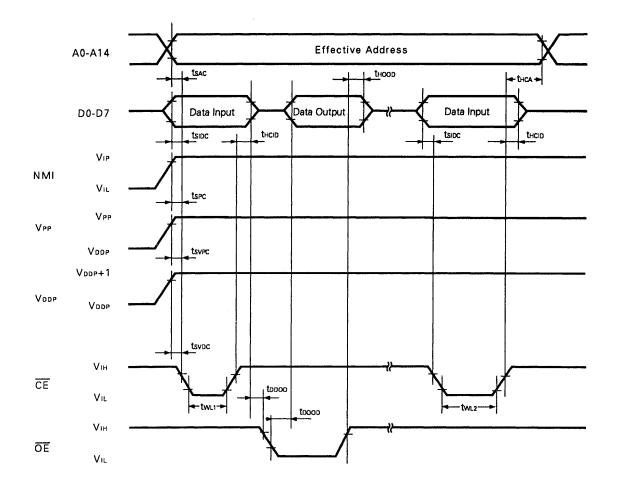

The timings in steps (2) to (8) are shown in Fig. 3-1.

#### 3.3 PROM READ PROCEDURE

NEC

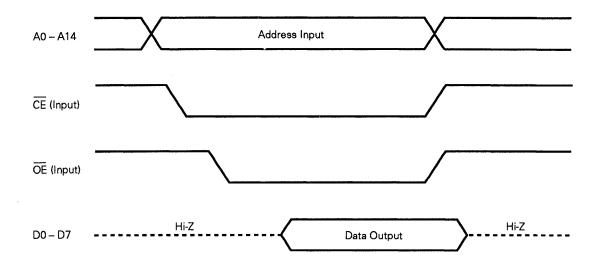

PROM contents can be read into the external data bus (D0 to D7) using the following procedure:

(1) Fix the RESET pin to the low level. Apply +12.5 V to the NMI pin. Treat all other unused pins as shown in **PIN CONFIGURATION (2)**.

- (2) Apply +5 V to the  $V_{DD}$  and  $V_{PP}$  pins.

- (3) Input the address of the data to be read to the A0 to A14 pins.

- (4) Set the read mode.

- (5) Output data to the D0 to D7 pins.

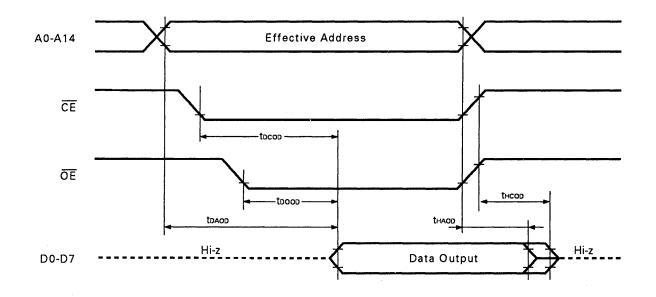

The timings in steps (2) to (5) are shown in Fig.3-3.

#### Fig. 3-3 PROM Read Timings

#### 4. ERASURE CHARACTERISTICS (µPD78P218ADW ONLY)

The µPD78P218ADW can erase the programmed data content (FFH) by applying light having wavelengths of less than about 400 nm.

To erase the  $\mu$ PD78P218ADW program memory contents, normally apply ultraviolet rays having a wavelength of 254 nm. The total radiation required to erase the  $\mu$ PD78P218ADW contents completely is a minimum of 15 W·s /cm<sup>2</sup> (ultraviolet strength × erasure time). The erasure time is approximately 15 to 20 minutes (when a 12000  $\mu$ W/ cm<sup>2</sup> ultraviolet lamp is used). The erase time may possible become longer due to deterioration in the performance of the ultraviolet lamp or fouling of the package window.

For the erasure operation, place the  $\mu$ PD78P218ADW within 2.5 cm from the ultraviolet lamp. Use the ultraviolet lamp with the filter removed.

#### 5. ERASURE WINDOW SEALING (µPD78P218ADW ONLY)

Except when erasing EPROM contents, apply a protective seal to the erasure window. This is important to prevent the EPROM contents from being inadvertently erased due to light other than the erasure lamp or the internal circuits other than the EPROM form error due to light.

#### 6. SCREENING OF ONE-TIME PROM PRODUCTS

By reason of their structure, one-time PROM products ( $\mu$ PD78P218ACW and  $\mu$ PD78P218AGC-AB8) cannot be fully tested by NEC prior to shipment. After the necessary data has been written, it is recommended that screening be performed for PROM verification after high-temperature storage under the following conditions.

| Storage Temperature | Storage Period |

|---------------------|----------------|

| 125 ºC              | 24 hrs.        |

Under the generic name "QTOP microcomputer", NEC offers a charged service covering one-time PROM writing, marking, screening and verifications. Please consult our sales representative for details.

#### 7. ELECTRICAL SPECIFICATIONS

#### ABSOLUTE MAXIMUM RATINGS (Ta = +25 °C)

| PARAMETER             | SYMBOL | TEST CONDITIONS       | RATING             | UNIT |

|-----------------------|--------|-----------------------|--------------------|------|

|                       | VDD    |                       | -0.5 to +7.0       | v    |

| Supply voltage        | AVREF  |                       | -0.5 to VDD +0.5   | v    |

|                       | AVss   |                       | -0.5 to +0.5       | V    |

|                       | Vii    |                       | -0.5 to VDD +0.5   | v    |

| Input voltage         | Vız    | *1                    | -0.5 to AVREF +0.5 | V    |

|                       | Vis    | *2                    | -0.5 to +13.5      | v    |

| Output voltage        | Vo     |                       | -0.5 to VDD +0.5   | v    |

| 0                     |        | 1 pin                 | 15                 | mA   |

| Output current low    | lor    | All output pins total | 100                | mA   |

| Output current high   | 1      | 1 pin                 | -10                | mA   |

|                       | Іон    | All output pins total | -50                | mA   |

| Operating temperature | Topt   | -                     | 40 to +85          | °C   |

| Storage temperature   | Tstg   |                       | 65 to +150         | °C   |

- \* 1. Those of pins P70/AN0 to P75/AN5, P66/WAIT/AN6, P67/REFRQ/AN7 which are used as A/D converter input pins.

- 2. Pins P20/NMI, EA/VPP and P21/INTP0/A9 in PROM programming mode.

- Note Product quality may suffer if the absolute maximum rating is exceeded for even a single parameter or even  $\star$  momentarily. The absolute maximum ratings are rated values at which the product is on the verge of suffering physical damage, and therefore the product must be used under conditions which ensure that the absolute maximum ratings are not exceeded.

#### **OPERATING CONDITIONS**

| CLOCK FREQUENCY      | OPERATING TEMPERATURE (Topt) | SUPPLY VOLTAGE (VDD) |

|----------------------|------------------------------|----------------------|

| 4 MHz ≤ fxx ≤ 12 MHz | –40 to +85 ℃                 | +5.0 ± 0.3 V         |

#### CAPACITANCE (Ta = +25 °C, V<sub>DD</sub> = V<sub>SS</sub> = 0 V)

| PARAMETER          | SYMBOL | TEST CONDITIONS       | MIN. | TYP. | MAX. | UNIT |

|--------------------|--------|-----------------------|------|------|------|------|

| Input capacitance  | Сι     | f = 1 MHz unmeasured  |      |      | 20   | pF   |

| Output capacitance | Co     | pins returned to 0 V. |      |      | 20   | pF   |

| I/O capacitance    | Сю     |                       |      |      | 20   | pF   |

| RESONATOR                                          | RECOMMENDED<br>CIRCUIT | PARAMETER                                     | MIN. | MAX. | UNIT |

|----------------------------------------------------|------------------------|-----------------------------------------------|------|------|------|

| Ceramic<br>resonator<br>or<br>crystal<br>resonator | $V_{ss} X1 X2$         | Oscillator frequency (fxx)                    | 4    | 12   | MHz  |

| External                                           | X1 X2                  | X1 input frequency (fx)                       | 4    | 12   | MHz  |

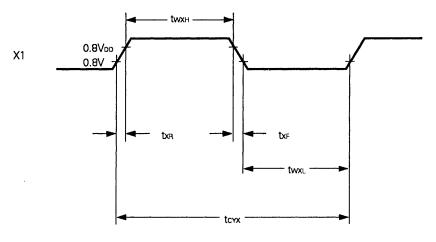

| clock                                              |                        | X1 input rising/falling time<br>(txe, tx=)    | 0    | 30   | ns   |

|                                                    |                        | X1 input high/low level width<br>(twxн, twxเ) | 30   | 130  | ns   |

#### OSCILLATOR CHARACTERISTICS (Ta = -40 to +85 °C, VD0 = +5.0 $\pm$ 0.3 V, Vss = 0 V)

Note When the system clock oscillator is used, the following points should be noted concerning wiring in the section enclosed by dots, in order to prevent the effects of wiring capacitance, etc.

- . Keep the wiring as short as possible.

- . Do not cross any other signal lines.

- . Keep away from lines carrying a high fluctuating current.

- . Ensure that oscillator capacitor connection points are always at the same potential as Vss. Do not ground in a ground pattern in which a high current flows.

- . Do not take a signal from the oscillator.

#### DC CHARACTERISTICS (Ta = -40 to +85 °C, $V_{DD}$ = +5.0 ±0.3 V, $V_{BB}$ = 0 V)

| PARAMETER                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | SYMBOL |         | TEST CONDITIONS                    | MIN.    | TYP. | MAX.  | UNIT |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------|---------|------------------------------------|---------|------|-------|------|

| Input voltage low                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | Vil    |         |                                    |         |      | 0.8   | v    |

| <u></u>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | Vін1   | Pins    | except for <b>*1</b> and <b>*2</b> | 2.2     |      | Vdd   | v    |

| Input voltage high                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | ViH2   | Pin o   | f •1                               | 2.2     |      | AVREF | v    |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | Vінз   | Pin o   | f *2                               | 0.8Vpd  |      | VDD   | V    |

| Output voltage low                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | Vol1   | lol = 1 | lo∟ = 2.0 mA                       |         |      | 0.45  | v    |

| Output voltage low                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | Vol2   | lог = 1 | 8.0 mA <b>*3</b>                   |         |      | 1.0   | v    |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | Vон1   | Іон =   | –1.0 mA                            | Vpp-1.0 |      |       | v    |

| Output voltage high                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | Voh2   | Іон =   | –100 μ <b>Α</b>                    | Vpp-0.5 |      |       | v    |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | Vонз   | Іон =   | –5.0 mA <b>*4</b>                  | 2.0     |      |       | v    |

| X1 input current low                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | lı.    | 0 V ≤   | Vi ≤ ViL                           |         |      | -100  | μΑ   |

| X1 input current high                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | ħн     | Vінз ≤  | Vi ≤ Vdd                           |         |      | 100   | μА   |