# Advanced Micro

**Devices**

## Am29CPL154H-25/30

### **CMOS 512-Word Field-Programmable Controller (FPC)**

### **DISTINCTIVE CHARACTERISTICS**

- Implements complex state machines

- High-speed, low-power CMOS EPROM technology

- Functional upgrade from the Am29CPL151

- Eight conditional inputs (each can be registered as a programmable option), 16 outputs

- Up to 30-MHz maximum frequency

- 512-word by 36-bit CMOS EPROM

- Space-saving 28-pin OTP plastic SKINNYDIPe and PLCC packages and windowed ceramic SKINNYDIP package

- 28 instructions

- Conditional branching, conditional looping, conditional subroutine call, multiway branch

### **GENERAL DESCRIPTION**

The Am29CPL154 is a CMOS, single-chip Field Programmable Controller (FPC). It allows implementation of complex state machines and controllers by programming the appropriate sequence of instructions. Jumps, loops, and subroutine calls, conditionally executed based on the test inputs, provide the designer with powerful control flow primitives.

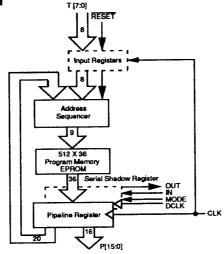

Intelligent control may be distributed throughout the system by using FPCs to control various self-contained functional units, such as register file/ALU, I/O, interrupt, diagnostic, and bus control units. An address sequencer, the heart of the FPC, provides the address to an internal 512-word by 36-bit EPROM.

The Am29CPL154 is manufactured in CMOS technology and offers a space-saving 300-mil SKINNYDIP package. A pin-compatible smaller FPC is offered as the Am29CPL151 with a 64 x 32 memory.

This UV-erasable and reprogrammable device utilizes proven floating-gate CMOS EPROM technology to ensure high reliability, easy programming, and better than 99.9% programming yields. The Am29CPL154 is offered in both windowed and One-Time Programmable (OTP) packages. OTP plastic SKINNYDIP and PLCC devices are ideal for volume production.

### SIMPLIFIED BLOCK DIAGRAM

SKINNYDIP and SSR are registered trademarks of Advanced Micro Devices, Inc.

Publication # 10136 Rev. C Amendment /0 Issue Oate: January 1989

10136-001A

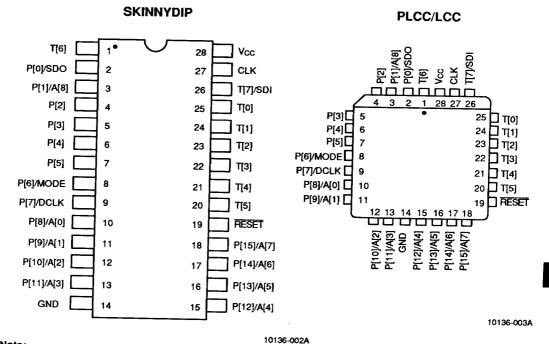

### **CONNECTION DIAGRAMS Top View**

Note:

Pin 1 is marked for orientation.

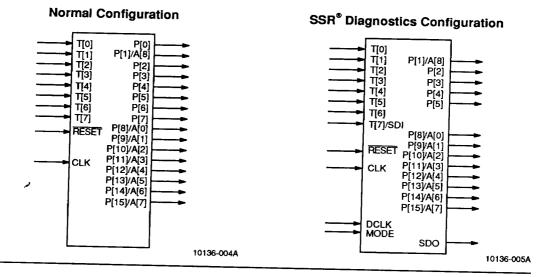

### **LOGIC SYMBOLS**

Am29CPL154

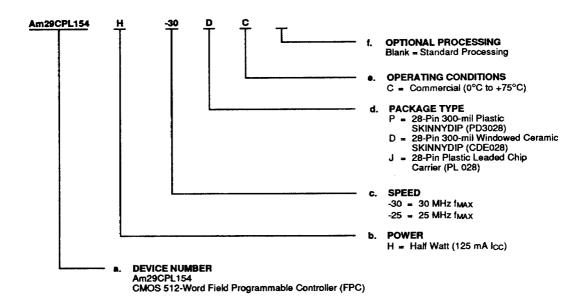

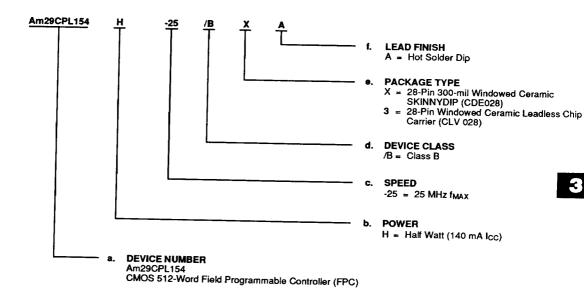

### ORDERING INFORMATION **Commercial Products**

AMD products for commercial applications are available with several ordering options. The order number (Valid Combination) is formed by a combination of: a. Device Number

- b. Power

- c. Speed

- d. Package Type

e. Operating Conditions

- f. Optional Processing

| Valid Combinations |            |  |  |  |  |  |  |

|--------------------|------------|--|--|--|--|--|--|

| Am29CPL154H-30     | PC. DC. JC |  |  |  |  |  |  |

| Am29CPL154H-25     | FO, DO, 30 |  |  |  |  |  |  |

#### **Valid Combinations**

The Valid Combinations table lists configurations planned to be supported in volume for this device. Consult the local AMD sales office to confirm availability of specific valid combinations, and to check on newly released combinations.

Note: Marked with AMD logo.

### **ORDERING INFORMATION APL Products**

AMD products for Aerospace and Defense applications are available with several ordering options. APL (Approved Products List) products are fully compliant with MIL-STD-883 requirements. The order number (Valid Combination) is formed by a combination of:

a. Device Number

- b. Power c. Speed

- d. Device Class

- e. Package Type Lead Finish

| Valid Combinations |            |  |  |  |  |  |  |  |

|--------------------|------------|--|--|--|--|--|--|--|

| Am29CPL154H-25     | /BXA, /B3A |  |  |  |  |  |  |  |

#### **Valid Combinations**

The Valid Combinations table lists configurations planned to be supported in volume for this device. Consult the local AMD sales office to confirm availability of specific valid combinations, and to check on newly released combinations.

Note: Marked with AMD logo.

**Group A Tests**

Group A tests consists of Subgroups 1, 2, 3, 7, 8, 9, 10, 11,

<sup>\*</sup> These pins available only in SSR mode.

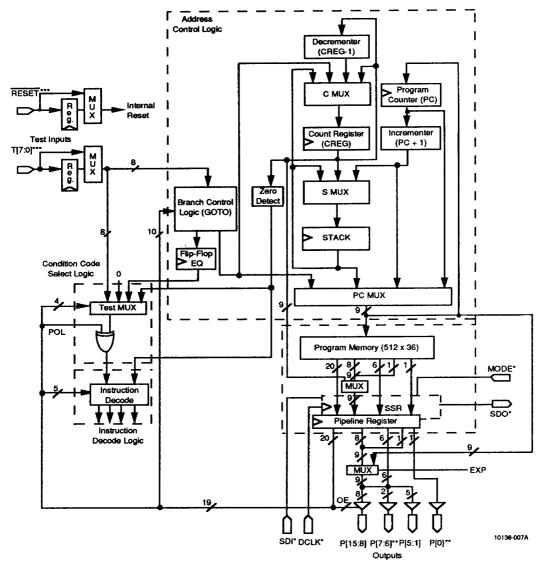

10136-007A

Figure 1. Am29CPL154 Detailed Block Diagram

<sup>\*\*</sup> These pins available only in normal mode.

<sup>\*\*\*</sup> Each of the T[7:0] and RESET inputs can be individually registered or left unregistered as a programmable option.

### PIN DESCRIPTION

#### CLK

### Clock Input

The rising edge of the clock latches the program counter, count register (CREG), subroutine register (SREG), pipeline register, and EQ flag. The rising edge of the clock also latches the test input registers and the RESET register if their respective configuration bits are set to enable internal synchronizing registers.

### P[15:8]/A[7:0] Outputs

The upper eight general-purpose control outputs are enabled by the OE signal from the pipeline register. When OE is HIGH, P[15:8] are enabled and when LOW, P[15:8] are disabled.

A controller Expansion (EXP) cell can be programmed to set pins P[1] and P[15:8] to output the program address A[8] and A[7:0] from the PC MUX. These can be used to address external registered memories to provide more control outputs.

The contents of the internal count register (CREG) can also be routed to the control output pins P[1] and P[15:8], using the OUTPUT instruction. Thus, the control outputs can be changed dynamically.

### P[7:0] [DCLK, MODE, SDO] Outputs

The lower eight general-purpose control outputs are permanently enabled. In the SSR diagnostic configuration, P[7] becomes the diagnostic clock input DCLK, P[6] becomes the diagnostic control input MODE, and P[0] becomes the serial Data Output [SDO].

### RESET

## Optionally Registered Reset Input; Active LOW

When the reset input is LOW, the output of the PC MUX is forced to the uppermost program address (511). On the next rising edge of the clock, this address (511) is loaded into the program counter; the instruction at location 511 is loaded into the pipeline register, and the EQ flag is cleared. A programmable configuration bit allows the option of making this a registered input. If RESET is internally registered, the first rising edge of the clock latches it. On the next rising edge of the clock, the EQ flip-flop is cleared and the contents of memory location 511 are loaded into the pipeline register. The default state of this input is registered.

# T[7:0] [SDI] Optionally Registered Test Inputs

In conditional instructions, the TEST inputs can be used as individual condition codes selected by the TEST field in the pipeline register. The T[7:0] inputs can also be used as a branch address when performing a program branch or as a count value to be loaded into the CREG. When this is done, a ninth bit from the microword is added as the MSB of the test inputs to yield a nine-bit value. Each of these inputs has an EPROM bit associated with it. This bit may be programmed such that the corresponding input becomes an unregistered input. The default state of these inputs is registered. In SSR diagnostics mode, T[7] becomes the Serial Data Input (SDI).

### **FUNCTIONAL DESCRIPTION**

Figure 1, the detailed block diagram of the Am29CPL154, shows logic blocks and interconnecting buses that permit parallel performance of different operations in a single instruction. The FPC consists of four main logic blocks: the program memory, address control logic, condition code selection logic, and instruction decode. A fifth optional block is the Serial Shadow Register (SSR).

The program memory contains the user-defined instruction flow and output sequence. The address control logic addresses the program memory. This control logic supports high-level instruction functions including conditional branches, subroutine calls and returns, loops, and multiway branches. The condition code selection logic selects the condition code input to be tested when a conditional instruction is executed. The polarity of the selected condition code input is controlled by the POL bit in the microword. The instruction decode generates the control signals necessary to perform the instruction specified by the instruction part (P[35:16]) of the microword. The SSR enables in-system testing to isolate problems down to the IC level.

### **Program Memory**

The FPC program memory is a 512-word by 36-bit EPROM with a 36-bit pipeline register at its output. The upper 20 bits (P[35:16]) of the pipeline register are internal to the FPC and form the instruction to control address sequencing. The format for instructions is: a one-bit synchronous Output Enable OE, a five-bit OPCODE,

a one-bit test polarity select POL, a four-bit TEST condition select field, and a nine-bit immediate DATA field. The DATA field is used to provide branch addresses, test input masks, and counter values.

The lower 16 bits (P[15:0]) of the pipeline register are brought out as user-defined, general-purpose control outputs. The upper eight control outputs (P[15:8]) are disabled when OE is programmed as a LOW. The lower eight control bits (P[7:0]) are always enabled.

Outputs P[1] and P[15:8] will contain the next instruction address when the optional bit EXP is set. The contents of the count register are also available at P[1] and P[15:18] by using the OUTPUT instruction regardless of whether the EXP bit is set.

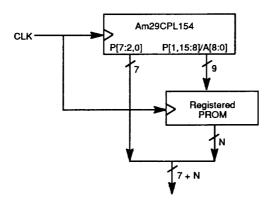

### Controlling External PROM

By programming the EXP bit, PC MUX is output over pins P[1,15:8]/A[8:0]. This feature can be used to extend the width of the output control word when external registered memories are used. In the diagram below, the Am29CPL154 controls external registered PROMs to provide an output control word (7 + N) bits wide (where N is the bit width of the PROMs).

When the OUTPUT instruction is executed, the CREG contents are output over pins P[1], P[15:8]/A[8], A[7:0] on the following cycle. Consequently, if the CREG contents must be read after programming the EXP cell, the system design should be modified to handle this exception.

Figure 2. Controlling External PROM

10136-006A

### **Address Control Logic**

The address control logic consists of four smaller logic blocks. These are:

PC GRP - Program counter multiplexer (PCMUX), program counter register (PC) and

program counter register (PC) and combinatorial incrementer (PC + 1)

STACK - 17-word by 9-bit-wide stack with subroutine mux (S MUX)

ino max (o mox)

- Count register (CREG) with counter mux (C MUX), combinatorial decrementer

(CREG-1), and zero detect

GOTO - Multifunction branch control logic

### PC GRP

CNTR

The PC GRP consists of a 4:1 multiplexer, a program counter (PC) register, and a 9-bit combinatorial incrementer (PC + 1). It selects the PC, PC + 1, the branch address, or the top of stack as the next instruction address input to the program memory and the PC.

When RESET is internally registered, the first clock edge after RESET goes LOW latches RESET internally. The next clock edge loads the contents of location 511 decimal into the instruction-pipeline register and clears the EQ flag. A programmable configuration bit allows the option of bypassing the synchronizing register. In this case, after RESET goes LOW, the output of the PC MUX is forced to all "1"s (address 511 decimal) during the setup time, and the first clock edge loads the contents of location 511 decimal into the instruction-pipeline register and clears the EQ flag. Note: by default, the RESET input is registered.

### **STACK**

This 17-deep, 9-bit-wide stack block consists of a 3:1 multiplexer (S MUX) that stores the data into the topmost location of the stack. The STACK register is incremented by one after an item is written onto the STACK (post-incremented) and decremented by one before an item is read from the STACK (pre-decremented). The S MUX chooses from three sources: PC +1, count register, and the top of the stack (for holding). PC + 1 is the input source when doing subroutine calls. PC MUX is the output destination when a return-from-subroutine instruction is performed. The PSHCNTR and POPCNTR instructions can be used for nested counts up to the depth of the STACK. Table 1 shows how the stack operates when more than 17 values are pushed. Table 2 shows how the stack operates when more than 17 values are popped.

### **CNTR**

The CNTR block consists of a nine-bit, four-to-one multiplexer (C MUX), driving a nine-bit register (CREG); a six-bit combinatorial decrementer (CREG-1); and a zero-detection circuit. The CNTR logic block is typically used for timing functions and iterative loop counting.

The CMUX has the following input sources: top of stack, the branch-logic output, CREG - 1, and the CREG (for holding).

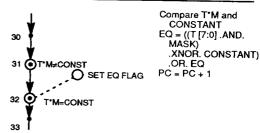

### **GOTO**

The GOTO logic block serves three functions:

- It provides a nine-bit count value from the DATA field in the pipeline register (P[24:16]) or from the TEST inputs T[7:0] masked by the DATA field P[23:16]. This is represented by T\*M.

- It provides a branch address from the DATA field in the pipeline register P[24:16] or from the TEST inputs T[7:0] masked by the 8 LSBs of the DATA field P[23:16]. This is represented by T\*M. The MSB or ninth bit of the branch address will be the MSB of the DATA field.

- It compares T[7:0] masked by the MASK field P[23:16], called T\*M, to the CONSTANT field from the pipeline register P[31:24]. If a match occurs, the EQ flip-flop is set. EQ remains unchanged if there is no match. Constant field bits that correspond to masked test bits must be zero.

The EQ flag can be tested by the condition code selection logic. Multiple tests of any group of T inputs in a manner analogous to sum-of-products can be performed since a no-match comparison does not reset the EQ flag. Any conditional branch on EQ will reset the EQ flag. Conditional returns on EQ will not change the EQ flag. RESET input LOW will reset the EQ flag.

Note: A zero in the MASK field blocks the corresponding bit in the TEST field; a one activates the corresponding bit.

The constant field bits that correspond to masked test field bits must be zero. A zero is substituted for masked test field bits. The "POL" bit is a "don't care" when using test inputs to load registers.

Note that when the inputs are internally registered (programmable option) they must meet the register setup time on the cycle preceding the one in which they are to be used.

### **Condition Code Selection Logic**

The condition code selection logic consists of a 16:1 multiplexer. The 16 condition inputs are the eight test bits, the EQ flag, CREG ZERO status, and six UNCOND test conditions connected to zero for the unconditional mode. The TEST field in the pipeline register (P[28:25]) selects one of the 16 conditions. If one of the UNCOND is chosen, and the POL bit is a one, the instruction is executed with a "forced PASS" condition. If one of the UNCOND is chosen, and the POL bit is zero, the instruction is executed with a "forced FAIL" condition. See opcode descriptions for more details.

The polarity bit POL in the instruction allows the user to test for either a pass or fail condition. Refer to Table 3 for details.

Note that when the inputs are internally registered (programmable option) they must meet the register setup time on the cycle preceding the one in which they are to be used.

### Instruction Decode

The instruction decoder is a PLA that generates the control for 28 different instructions. The decoder inputs include the OPCODE field P[34:30], the zero detection flag from the CNTR, and the selected test condition code from the condition code selection logic.

### **Operational Modes**

Am29CPL154 operates as а nine-bit microcontroller in normal mode, and there are several configuration bits that can be programmed to modify this normal operation. The EXP bit allows the nine program address lines from the PC MUX to be output on the output pins (P[1,15:8]) so that a user can expand the width of the control lines by using external registered memories. The SSR bit allows on-chip diagnostic capabilities for in-system testing. The remaining bits serve to individually select whether the input pins will be synchronized or not. The default setting of these bits (unprogrammed,1) will cause each pin to be synchronized, and so programming a given bit (to 0) will cause that corresponding input to become internally unsynchronized.

TABLE 1.

| STACK<br>LOCATION | PSH |

|-------------------|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|

| 1                 | 1   | 2   | 3   | 4   | 5   | 6   | 7   | 8   | 9   | 10  | 11  | 12  | 13  | 14  | 15  | 16  | 17  | 18  | 19  |

| 2                 | Х   | 1   | 2   | 3   | 4   | 5   | 6   | 7   | 8   | 9   | 10  | 11  | 12  | 13  | 14  | 15  | 16  | 17  | 18  |

| 3                 | х   | ×   | 1   | 2   | 3   | 4   | 5   | 6   | 7   | 8   | 9   | 10  | 11  | 12  | 13  | 14  | 15  | 16  | 17  |

| 4                 | Х   | X   | Х   | 1   | 2   | 3   | 4   | 5   | 6   | 7   | 8   | 9   | 10  | 11  | 12  | 13  | 14  | 15  | 16  |

| 5                 | x   | Х   | Х   | X   | 1   | 2   | 3   | 4   | 5   | 6   | 7   | 8   | 9   | 10  | 11  | 12  | 13  | 14  | 15  |

| 6                 | x   | х   | X   | X   | Х   | 1   | 2   | 3   | 4   | 5   | 6   | 7   | 8   | 9   | 10  | 11  | 12  | 13  | 14  |

| 7                 | ×   | х   | X   | Х   | Х   | х   | 1   | 2   | 3   | 4   | 5   | 6   | 7   | 8   | 9   | 10  | 11  | 12  | 13  |

| 8                 | x   | х   | Х   | X   | X   | Х   | х   | 1   | 2   | 3   | 4   | 5   | 6   | 7   | 8   | 9   | 10  | 11  | 12  |

| 9                 | х   | х   | Х   | X   | X   | Х   | х   | х   | 1   | 2   | 3   | 4   | 5   | 6   | 7   | 8   | 9   | 10  | 11  |

| 10                | x   | X   | Х   | Х   | х   | х   | х   | х   | х   | 1   | 2   | 3   | 4   | 5   | 6   | 7   | 8   | 9   | 10  |

| 11                | x   | х   | X.  | Х   | ×   | х   | х   | х   | х   | Х   | 1   | 2   | 3   | 4   | 5   | 6   | 7   | 8   | 9   |

| 12                | х   | х   | Х   | Х   | х   | ×   | х   | ×   | х   | х   | х   | 1   | 2   | 3   | 4   | 5   | 6   | 7   | 8   |

| 13                | х   | х   | х   | х   | х   | х   | Х   | х   | х   | х   | х   | х   | 1   | 2   | 3   | 4   | 5   | 6   | 7   |

| 14                | х   | ×   | х   | х   | Х   | ×   | х   | х   | х   | х   | х   | x   | х   | 1   | 2   | 3   | 4   | 5   | 6   |

| 15                | x   | ×   | х   | х   | Х   | х   | х   | x   | х   | ×   | х   | х   | х   | ×   | 1   | 2   | 3   | 4   | 5   |

| 16                | X   | х   | х   | ×   | X   | х   | х   | х   | х   | x   | х   | ×   | x   | х   | x   | 1   | 2   | 3   | 4   |

| 17                | X   | Х   | х   | X   | Х   | х   | х   | х   | х   | х   | х   | ×   | х   | х   | ×   | х   | 1   | 2   | 3   |

TABLE 2.

| STACK<br>LOCATION | POP |

|-------------------|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|

| 1                 | 19  | 18  | 17  | 16  | 15  | 14  | 13  | 12  | 11  | 10  | 9   | 8   | 7   | 6   | 5   | 4   | 3   | 18  | 17  |

| 2                 | 18  | 17  | 16  | 15  | 14  | 13  | 12  | 11  | 10  | 9   | 8   | 7   | 6   | 5   | 4   | 3   | 18  | 17  | 16  |

| 3                 | 17  | 16  | 15  | 14  | 13  | 12  | 11  | 10  | 9   | 8   | 7   | 6   | 5   | 4   | 3   | 18  | 17  | 16  | 15  |

| 4                 | 16  | 15  | 14  | 13  | 12  | 11  | 10  | 9   | 8   | 7   | 6   | 5   | 4   | 3   | 18  | 17  | 16  | 15  | 14  |

| 5                 | 15  | 14  | 13  | 12  | 11  | 10  | 9   | В   | 7   | 6   | 5   | 4   | 3   | 10  | 17  | 16  | 15  | 14  | 13  |

| 6                 | 14  | 13  | 12  | 11  | 10  | 9   | 8   | 7   | 6   | 5   | 4   | 3   | 18  | 17  | 16  | 15  | 14  | 13  | 12  |

| 7                 | 13  | 12  | 11  | 10  | 9   | 8   | 7   | 6   | 5   | 4   | 3   | 18  | 17  | 16  | 15  | 14  | 13  | 12  | 11  |

| 8                 | 12  | 11  | 10  | 9   | 8   | 7   | 6   | 5   | 4   | 3   | 18  | 17  | 16  | 15  | 14  | 13  | 12  | 11  | 10  |

| 9                 | 11  | 10  | 9   | 8   | 7   | 6   | 5   | 4   | 3   | 18  | 17  | 16  | 15  | 14  | 13  | 12  | 11  | 10  | 9   |

| 10                | 10  | 9   | 8   | 7   | 6   | 5   | 4   | 3   | 18  | 17  | 16  | 15  | 14  | 13  | 12  | 11  | 10  | 9   | 8   |

| 11                | 9   | 8   | 7   | 6   | 5   | 4   | 3   | 18  | 17  | 16  | 15  | 14  | 13  | 12  | 11  | 10  | 9   | 8   | 7   |

| 12                | 8   | 7   | 6   | 5   | 4   | 3   | 18  | 17  | 16  | 15  | 14  | 13  | 12  | 11  | 10  | 9   | 8   | 7   | 6   |

| 13                | 7   | 6   | 5   | 4   | 3   | 18  | 17  | 16  | 15  | 14  | 13  | 12  | 11  | 10  | 9   | 8   | 7   | 6   | 5   |

| 14                | 6   | 5   | 4   | 3   | 18  | 17  | 16  | 15  | 14  | 13  | 12  | 11  | 10  | 9   | В   | 7   | 6   | 5   | 4   |

| 15                | 5   | 4   | 3   | 18  | 17  | 16  | 15  | 14  | 13  | 12  | 11  | 10  | 9   | 8   | 7   | 6   | 5   | 4   | 3   |

| 16                | 4   | 3   | 18  | 17  | 16  | 15  | 14  | 13  | 12  | 11  | 10  | 9   | 8   | 7   | 6   | 5   | 4   | 3   | 18  |

| 17                | 3   | 18  | 17  | 16  | 15  | 14  | 13  | 12  | 11  | 10  | 9   | 8   | 7   | 6   | 5   | 4   | 3   | 18  | 17  |

10136-008A

### **Am29CPL154 General Instruction Format**

TEST OE DATA USER-DEFINED

WHERE: OE

= Synchronous Output Enable for P[15:8].

**OPCODE** A five-bit opcode field for selecting one of the 27 single-data-field instructions. POL A one-bit test condition polarity select (refer to Table 3).

TEST A four-bit test condition select.

> TEST[28:25] **UNDER TEST** 0000 0001 0010 0011 0100 0101 0110 0111 1000 1001 **CREG ZERO** 1010-1111 **UNCONDITIONAL** [0]

DATA = A nine-bit conditional branch address, test input mask, or counter value field designated as PL in instruction mnemonics.

Table 3

| Input Condition<br>Being Tested | POL | Test<br>Result |

|---------------------------------|-----|----------------|

| 0                               | 0   | Fail           |

| 0                               | 1   | Pass           |

| 1                               | 0   | Pass           |

| 1                               | 1   | Fail           |

## **Am29CPL154 Comparison Instruction Format**

32 15 CONSTANT USER-DEFINED **OUTPUTS**

10136-009A

WHERE:

OE Synchronous Output Enable for P[15:8]. OPCODE

= Compare instruction (binary 100).

CONSTANT = An eight-bit constant for equal-to comparison with T\*M. MASK

= An eight-bit mask field for masking the incoming T[7:0] inputs.

Am29CPL154

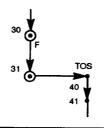

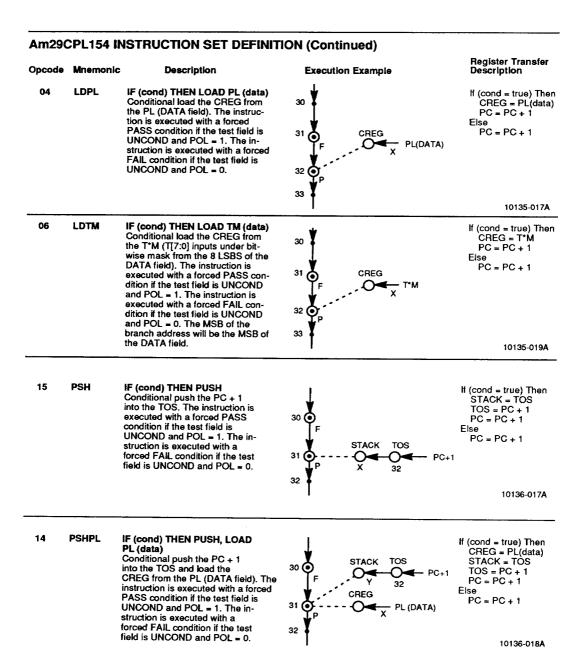

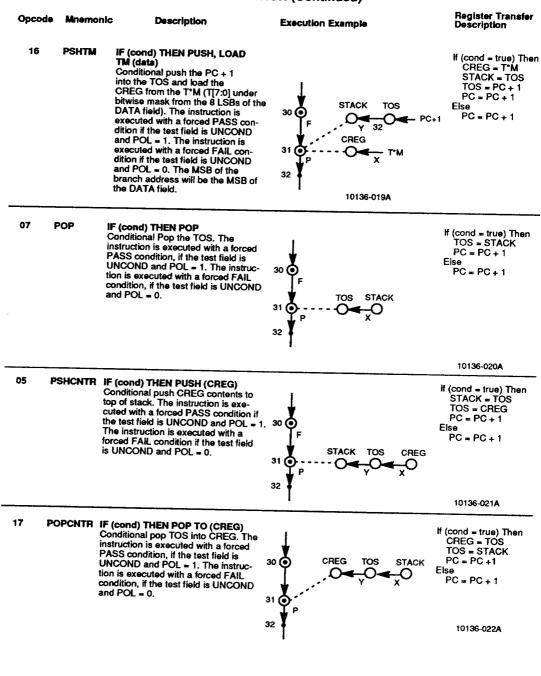

### Am29CPL154 INSTRUCTION SET DEFINITION

- = Other instruction

- Instruction being described

- O = Register in part

P = Test Pass

F = Test Fail

X,Y are arbitrary values in the CREG or STACK

### Opcode Mnemonic

19

**GOTOPL**

### Description

IF (cond) THEN GOTO PL (data)

Conditional branch to the address in the PL (DATA field). The EQ flag will be reset if the test field selects it and the condition passes. The instruction is executed with a forced PASS condition if the test field is UNCOND and POL = 1. The instruction is executed with a forced FAIL condition if the test field is UNCOND and POL = 0.

**Execution Example**

#### Register Transfer Description

If (cond = true) Then PC = PL(data) Fise PC = PC + 1

10135-009A

#### IF GOTOTM

IF (cond) THEN GOTO TM (data)

Conditional branch to the address defined by the T\*M (T[7:0] under bitwise mask from the 8 LSBS of the DATA field). This instruction is intended for multiway branches. The EQ flag will be reset if the test field selects it and the condition passes. The instruction is executed with a forced PASS condition if the test field is UNCOND and POL = 1. The instruction is executed with a forced FAIL condition if the test field is UNCOND and POL = 0. The MSB of the branch address will be the MSB of the DATA field.

If (cond = true) Then PC = T\*M Else

PC = PC + 1

10135-011A

#### 03

GOTOSTK IF (cond) THEN GOTO (STACK) Conditional branch to the address at the top of the stack, or else continue. The EQ flag will be reset if the test field selects it and the condition passes. The instruction is executed with a forced PASS condition if the test field is UNCOND and POL = 1. The instruction is executed with a forced FAIL condition if the test field is UNCOND and POL = 0.

If (cond = true) Then PC = TOS Else PC = PC + 1

10136-010A

#### 18 **FORK**

IF (cond) THEN GOTO PL (data) ELSE GOTO (STACK)

Conditional branch to the address in the PL (DATA field) or the TOS. A branch to PL is taken if the condition is true and a branch to TOS if false. The EQ flag will be reset if the test field selects it and the condition passes. The instruction is executed with a forced PASS condition if the test field is UNCOND and POL = 1. The instruction is executed with a forced FAIL condition if the test field is UNCOND and POL = 0.

If (cond = true) Then PC = PL(data) Else PC = TOS

10136-011A

3-108

Am29CPL154

#### Register Transfer Opcode Mnemonic Description **Execution Example** Description 1C CALPL IF (cond) THEN CALL PL (data) If (cond = true) Then Conditional jump to subroutine STACK TOS STACK = TOS at the address in the PL (DATA -PC+1 30 @ TOS = PC + 1 field). The PC + 1 is pushed into 32 the TOS as the return address. PC = PL(data) Else The EQ flag will be reset if the PL (DATA) PC = PC + 1test field selects it and the 31 condition passes. The instruction is 32 executed with a forced PASS condition if the test field is UNCOND and POL = 1. The instruction is exe cuted with a forced FAIL condition if 33 the test field is UNCOND and POL = 0 10136-012A 1E IF (cond) THEN CALL TM (data), CALTM If (cond = true) Then Conditional jump to subroutine at the address specified by the T\*M STACK = TOS TOS = PC + 1 (T[7:0] under bitwise mask from the SREG TOS PC = T\*M 8 LSBs of the DATA field). The Else PC + 1 is pushed into the TOS as the 32 PC = PC + 1 return address. The EQ flag will be reset if the test field selects it and the condition passes. The instruction is 32 executed with a forced PASS condition if the test field is UNCOND and POL = 1. The instruction is executed with a forced FAIL condition if the 10136-013A test field is UNCOND and POL = 0. The MSB of the branch address will be the MSB of the DATA field. 02 RET IF (cond) THEN RET STACK TOS If (cond = true) Then Conditional return from sub-PC = TOS routine. The TOS provides 30 TOS = STACK 32 the return from subroutine Else address and the stack is PC = PC + 1 31 popped. The instruction is executed with a forced PASS condition if the test field is 32 UNCOND and POL = 1. The instruction is executed with a TOS STACK forced FAIL condition if the test field is UNCOND and POL = 0. 10136-014A 00 RETPL IF (cond) THEN RET, LOAD If (cond = true) Then STACK TOS PL (data) Conditional return from sub-PC = TOS **←** PC+1 30 TOS = STACK routine and load the CREG 32 CREG = PL(data) from the PL (DATA field). Else The TOS provides the 31 PC = PC + 1 return from subroutine address and the STACK is 32 popped. The instruction is exe-TOS STACK cuted with a forced PASS condition if the test field is UNCOND and POL = 1. The 33 CREG instruction is executed with a forced FAIL condition if the test O PL (DATA) 10136-015A field is UNCOND and POL = 0.

Am29CPL154

10136-015A

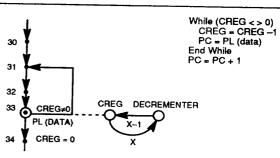

#### Am29CPL154 INSTRUCTION SET DEFINITION (Continued) Register Transfer **Execution Example** Description Opcode Mnemonic Description 0B DEC IF (cond) THEN DEC If (cond = true) Then 30 CREG = CREG -1 Conditional decrement of the CREG. The instruction is PC = PC + 1executed with a forced PASS Else 31 condition if the test field is UN-PC = PC + 1COND and POL = 1. The in-CREG DECREMENTER struction is executed with a 32 forced FAIL condition if the test field is UNCOND and POL = 0. 33 10135-029A OC DECPL WHILE (CREG < > 0) WAIT While (CREG < > 0) **ELSE LOAD PL (data)** CRÈG = CREG -1 Conditional Hold until the counter PC = PCEnd While is equal to zero, then load CREG from the PL (DATA field). This CREG = PL(data) instruction is intended for timing PC = PC + 1waveform generation. If the CREG CREG DECREMENTER is not equal to zero, the same instruction is refetched while CREG 30 is decremented. Timing is complete when the CREG is equal to zero. causing the next instruction to be CREG≠0 fetched and the CREG to be reloaded from PL. This instruction 10135-030A CREG=0 32 does not depend on the pass/fail PL (DATA) condition. 0E **DECTM** WHILE (CREG < > 0) WAIT While (CREG < > 0) ELSE LOAD TM (data) CREG = CREG -1 Conditional Hold until the counter is PC = PC equal to zero, then load CREG from End While the T\*M (T[7:0] under bitwise mask CREG = T\*M from the 8 LSBs of the DATA field). PC = PC + 1This instruction is intended for timing CREG DECREMENTER waveform generation. If the CREG is not equal to zero, the same instruct-30 tion is refetched while the CREG is decremented. Timing is complete CREG#0 when the CREG is equal to zero, causing the next instruction to be CREG fetched and the CREG to be reloaded from T\*M. This instruction does not depend on the pass/fail condition. The MSB of the branch 10135-031A address will be the MSB of the DATA field 1D DECGOPL If (cond) THEN GOTO PL (data) While (cond = false) ELSE WHILE (CREG <> 0) WAIT If (CREG < > 0) Conditional Hold/Count. The current CREG = CREG -1 PC = PC instruction will be refetched and the CREG decremented until the condi-Else PC = PC + 1 tion under test becomes true or the counter is equal to zero. If the condi-CREG DECREMENTER End While PC = PL (data) tion becomes true, a branch to the 30 address in the PL (DATA field) is executed. If the counter becomes zero without the condition becoming true, a CONTINUE is executed. The F and CREG#0 EQ flag will be reset if the test field PL (DATA) selects it and the condition passes. 32 The instruction is executed with a forced PASS condition if the test 10135-032A field is UNCOND and POL = 1. The instruction is executed with a forced FAIL condition if the test field is UNCOND and POL = 0.

#### Opcode Mnemonic

WAITPL

WAITTM

1A

1B

### Description IF (cond) THEN GOTO PL (data)

### **Execution Example**

#### Register Transfer Description

If (cond = true) Then PC = PL (data) Fise

PC = PC

**ELSE WAIT** Conditional Hold. The current instruction will be refetched and executed until the condition under

test becomes true. When true, a branch to the address in the PL (DATA field) is executed. The EQ flag will be reset if the test field selects it and the condition passes. The instruction is executed with a forced PASS condition if the test field is UNCOND and POL = 1. The instruction is executed with a forced FAIL condition if the test field is UNCOND

PL (DATA)

10135-033A

and POL = 0.

**ELSE WAIT** Conditional Hold. The current instruction will be refetched and executed until the condition under test becomes true. When the condition is true, a branch to the T\*M address (T[7:0] under bitwise mask from the eight LSBs of the DATA field) is executed. The EQ flag will be reset if the test field selects it and the condition passes. The instruction is executed with a forced PASS condition, if the test field is UNCOND and POL = 1. The instruction is executed with a forced FAIL condition, if the test field is UNCOND and POL = 0. The MSB of the branch address will be the MSB of the DATA field.

IF (cond) THEN GOTO TM (data),

If (cond = true) Then PC = T\*M Else PC = PC

10136-023A

08 LPPL

WHILE (CREG < > 0) LOOP

TO PL (data) Conditional loop to the address in the PL (DATA field). This instruction is intended to be placed at the bottom of an iterative loop. If the CREG is not equal to zero, it is decremented (signifying completion of an iteration), and a branch to the PL (DATA field) (top of the loop) is executed. If the CREG is equal to zero, looping is complete and the next sequential instruction is executed. This instruction does not depend on the pass/fail condition. The EQ flag will be reset if the test field selects it and CREG is not equal to zero.

10135-034A

#### Register Transfer Description **Execution Example** Opcode Mnemonic Description While (CREG < > 0) 0A **LPTM** WHILE (CREG < > 0) LOOP CREG = CREG -1 TO TM (data) PC = T\*M Conditional loop to the address End While T\*M (T[7:0] under bitwise mask PC = PC + 1from the eight LSBs of the DATA field). This instruction should be 31 placed at the bottom of an iterative loop. If CREG is not equal to zero, 32 it is decremented (signifying com-CREG DECREMENTER CREG ≠ 0 pletion of an iteration), and a 33 6 branch to the address specified by T°M (top of the loop) is executed. If CREG is equal to zero, looping is CREG = 0 complete and the next sequential 10136-024A instruction is executed. This does not depend on the pass/fail condition. The EQ flag will be reset if the test field selects it and CREG is not equal to zero. The MSB of the branch address will be the MSB of the DATA field. While (CREG < > 0) WHILE (CREG < > 0) LOOP TO 0F LPSTK CREG = CREG -1 (STACK) Conditional loop to the address in PC = TOS 30 End While the TOS. If CREG ≠ 0, the CREG TOS = STACK is decremened and a branch to PC = PC + 131 the TOS address is executed. If the CREG = 0, looping is complete, the stack is popped, and the next 32 sequential instruction is executed. CREG DECREMENTER CREG ≠0 This instruction does not depend 33 on the pass/fail condition. The EQ TOS flag will be reset if the test field selects it and CREG is not equal to CREG ~ 0 zero. STACK 10136-025A PC = PC + 10D CONT CONTINUE The next sequential instruction is fetched unconditionally. This 30 instruction can be used to reset the EQ flag by selecting EQ in the TEST field. 31 32 10135-036A

| Орсо | de Mnemonic | Description                                                                                                                                                                                                                                                                                                                                                                                                                                             | Execution Example                           | Register Transfer<br>Description                                                  |

|------|-------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------|-----------------------------------------------------------------------------------|

| 01   |             | IF (cond) THEN OUTPUT The CREG contents will be output on pins P[1] and P[15:8] during the next clock cycle. Care should be taken to ensure that the outputs are enabled for the next sequential instruction by setting the microcode bit OE = 1. The instruction is executed with a forced PASS condition, if the test field is UNCOND and POL = 1. The instruction is executed with a forced FAIL condition, if the test field is UNCOND and POL = 0. | 30 P Pipeline Register 31 P P[1] and P[15:8 | # (cond = ture) Then P[1] and P[15:8] = CREG PC = PC + 1 Else PC = PC + 1  CREG X |

|      |             |                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                             |                                                                                   |

#### 10-13 CMP (100XX binary)

CMP TM (mask) TO PL (constant) This instruction performs bitwise Exclusive-OR of T\*M (T[7:0] under bitwise mask from the MASK field) with CONSTANT (P[31:24]). If T\*M equals CONSTANT, the EQ flag is set to one, which may be branched on in a following instruction. If not equal, the EQ flag is unaffected. This allows sequences of compares, in a manner analogous to sum-to-products, to be performed which can be followed by a single conditional branch if one or more of the comparisons are true. Note: The EQ flag is set to zero on reset or when EQ is selected as the test condition in a branch. Conditional returns on EQ leave the flag unchanged. Constant field bits that correspond to masked test field bits must be zero. This instruction does not depend on the pass/fail condition.

10135-037A

### INSTRUCTIONS BASED ON TEST CONDITIONS

|             |          |                                                       |           | Conditio       | n Pass      |            |           | Con   | dition Fa | ali        |       |

|-------------|----------|-------------------------------------------------------|-----------|----------------|-------------|------------|-----------|-------|-----------|------------|-------|

| Op-<br>code | Mnemonic | Assembler<br>Statement                                | PC<br>MUX | STACK          | CREG        | EQ<br>FLAG | PC<br>MUX | STACK | CREG      | EQ<br>FLAG | Notes |

| 00          | RETPL    | IF (cond) THEN RET,<br>LOAD PL (data)                 | TOS       | Pop            | Load<br>PL  | NC         | PC + 1    | Hold  | Hold      | NC         | 5     |

| 01          | OUTPUT   | IF (cond) THEN<br>OUTPUT                              | PC+1      | Hold           | Hold        | NC         | PC + 1    | Hold  | Hold      | NC         | 1     |

| 02          | RET      | IF (cond) THEN RET                                    | TOS       | Рор            | Hold        | NC         | PC + 1    | Hold  | Hold      | NC         | 5     |

| 03          | GOTOSTK  | IF (cond) THEN<br>GOTO (STACK)                        | TOS       | Hold           | Hold        | Reset      | PC + 1    | Hold  | Hold      | NC         | 3     |

| 04          | LDPL     | IF (cond) THEN LOAD<br>PL (data)                      | PC + 1    | Hold           | Load<br>PL  | NC         | PC + 1    | Hold  | Hold      | NC         |       |

| 05          | PSHCNTR  | IF (cond) THEN<br>PUSH (CREG)                         | PC + 1    | Push<br>CREG   | Hold        | NC         | PC + 1    | Hold  | Hold      | NC         | 6     |

| 06          | LDTM     | IF (cond) THEN LOAD<br>TM (data)                      | PC + 1    | Hold           | Load<br>TM  | NC         | PC + 1    | Hold  | Hold      | NC         |       |

| 07          | POP      | IF (cond) THEN<br>POP                                 | PC+1      | Рор            | Hold        | NC         | PC + 1    | Hold  | Hold      | NC         | 5     |

| 0B          | DEC      | IF (cond) THEN DEC                                    | PC+1      | Hold           | DEC         | NC         | PC + 1    | Hold  | Hold      | NC         |       |

| 14          | PSHPL    | IF (cond) THEN PUSH,<br>LOAD PL (data)                | PC + 1    | Push<br>PC + 1 | Load<br>PL  | NC         | PC + 1    | Hold  | Hold      | NC         | 6     |

| 15          | PSH      | IF (cond) THEN PUSH                                   | PC + 1    | Push<br>PC + 1 | Hold        | NC         | PC + 1    | Hold  | Hold      | NC         | 6     |

| 16          | PSHTM    | IF (cond) THEN PUSH,<br>LOAD TM (data)                | PC + 1    | Push<br>PC + 1 | Load<br>TM  | NC         | PC + 1    | Hold  | Hold      | NC         | 6     |

| 17          | POPCNTR  | IF (cond) THEN<br>POP TO (CREG)                       | PC+1      | Рор            | Load<br>TOS | NC         | PC + 1    | Hold  | Hold      | NC         | 5     |

| 18          | FORK     | IF (cond) THEN GOTO<br>PL (data) ELSE GOTO<br>(STACK) | PL        | Hold           | Hold        | Reset      | TOS       | Hold  | Hold      | NC         | 3     |

| 19          | GOTOPL   | IF (cond) THEN GOTO<br>PL (data)                      | PL        | Hold           | Hold        | Reset      | PC + 1    | Hold  | Hold      | NC         | 3     |

| 1A          | WAITPL   | IF (cond) THEN GOTO<br>PL (data) ELSE WAIT            | PL        | Hold           | Hold        | Reset      | PC        | Hold  | Hold      | NC         | 3     |

| 1B          | WAITTM   | IF (cond) THEN GOTO<br>TM (data), ELSE<br>WAIT        | ТМ        | Hold           | Hold        | Reset      | PC        | Hold  | Hold      | NC         | 3     |

| 1C          | CALPL    | IF (cond) THEN CALL<br>PL (data)                      | PL        | Push<br>PC + 1 | Hold        | Reset      | PC + 1    | Hoid  | Hold      | NC         | 3,6   |

| 1E          | CALTM    | IF (cond) THEN CALL<br>TM (data)                      | ТМ        | Push<br>PC + 1 | Hold        | Reset      | PC + 1    | Hold  | Hold      | NC         | 3,6   |

| 1F          | GOTOTM   | IF (cond) THEN GOTO<br>TM (data)                      | TM        | Hold           | Hold        | Reset      | PC + 1    | Hold  | Hold      | NC         | 3     |

Key: PC

- Program Counter

TOS

- Top of Stack

CREG

- Counter Register

PL

= Pipeline (data) Field

TM (data) = Test Inputs Masked by DATA Field

TM (mask) = Test Inputs Masked by MASK Field

DEC

= Decrement

NC

■ No Change

### Notes:

- 1. If condition Passes, Output CREG contents on next clock cycle.

- 2. If Condition = EQ, reset EQ flag.

- 3. If Condition = EQ and Conditon Passes, reset EQ flag.

- 4. If Condition = EQ and CREG ≠ 0, reset EQ flag.

- 5. When Stack is popped, the next value in the Stack is transferred to TOS.

- 6. When Stack is pushed, TOS is transferred to next available Stack location before value is written into TOS.

- 7. Set EQ Flag if CONST field = T\*M.

### INSTRUCTIONS DEPENDENT ON CREG

|            |          | •                                                |           | CREG  | = 0        |            |           |       |      |            |       |

|------------|----------|--------------------------------------------------|-----------|-------|------------|------------|-----------|-------|------|------------|-------|

| Op-        | Mnemonic | Assembler<br>Statement                           | PC<br>MUX | STACK | CREG       | EQ<br>FLAG | PC<br>MUX | STACK | CREG | EQ<br>FLAG | Notes |

| 80         | LPPL     | WHILE (CREG < > 0)<br>LOOP TO PL (data)          | PC + 1    | Hold  | Hold       | NC         | PL        | Hold  | DEC  | Reset      | 4     |

| 0 <b>A</b> | LPTM     | WHILE (CREG < > 0)<br>LOOP TO TM (data)          | PC + 1    | Hold  | Hold       | NC         | TM        | Hold  | DEC  | Reset      | 4     |

| 0C         | DECPL    | WHILE (CREG <> 0)<br>WAIT ELSE LOAD<br>PL (data) | PC + 1    | Hold  | Load<br>PL | NC         | PC        | Hold  | DEC  | NC         |       |

| 0E         | DECTM    | WHILE (CREG <> 0) WAIT ELSE LOAD TM (data)       | PC + 1    | Hold  | Load<br>TM | NC         | PC        | Hold  | DEC  | NC         |       |

| 0F         | LPSTK    | WHILE (CREG <> 0)<br>LOOP TO (STACK)             | PC + 1    | Рор   | Hold       | NC         | TOS       | Hold  | DEC  | Reset      | 4     |

### INSTRUCTIONS DEPENDENT ON TEST CONDITION AND CREG VALUE

|                      | THE CITE OF THE COLOR  |                                                 |            |       |      |            |           |       |      |            |       |        |  |

|----------------------|------------------------|-------------------------------------------------|------------|-------|------|------------|-----------|-------|------|------------|-------|--------|--|

|                      |                        |                                                 |            |       | Con  | dition Pa  | 195       |       |      |            |       |        |  |

| Op-<br>code Mnemonic | Assembler<br>Statement | CREG<br>Content                                 | PC<br>MUX  | STACK | CREG | EQ<br>FLAG | PC<br>MUX | STACK | CREG | EQ<br>FLAG | Notes |        |  |

|                      |                        | IF (cond)                                       |            |       |      |            | T         |       |      |            |       | 110103 |  |

| 1D                   | THE                    | THEN GOTO                                       | <b>≠</b> 0 | PL    | Hold | Hold       | Reset     | PC    | Hold | DEC        | NC    |        |  |

| ם טו                 | D200012                | GOPL PL (data) ELSE WHILE 0 PL (CREG <> 0) WAIT | PL         | Hold  | Hold | Reset      | PC + 1    | Hold  | Hold | NC         | 3     |        |  |

### **UNCONDITIONAL INSTRUCTIONS**

| Opcode                     | Mnemonic | Assembler Statement            | PC<br>MUX | STACK | CREG | EQ<br>FLAG | Notes |

|----------------------------|----------|--------------------------------|-----------|-------|------|------------|-------|

| 0D                         | CONT     | CONTINUE                       | PC+1      | Hold  | Hold | NC         | 2     |

| 10-13<br>(Binary<br>100XX) | СМР      | CMP TM (mask) TO PL (constant) | PC + 1    | Hold  | Hold | Set        | 7     |

Key: PC

= Program Counter

SREG

= Stack Register

CREG

= Counter Register

PL

= Pipeline (data) Field

TM (data) = Test Inputs Masked by DATA Field

TM (mask) = Test Inputs Masked by MASK Field

DEC NC

= Decrement

= No Change

### Notes:

- 1. If condition Passes, Output CREG contents on next clock cycle.

- 2. If Condition = EQ, reset EQ flag.

- 3. If Condition = EQ and Conditon Passes, reset EQ flag.

- 4. If Condition = EQ and CREG ≠ 0, reset EQ flag.

- 5. When Stack is popped, the next value in the Stack is transferred to TOS.

- 6. When Stack is pushed, TOS is transferred to next available Stack location before value is written into TOS.

- 7. Set EQ Flag if CONST field = T\*M.

Am29CPL154

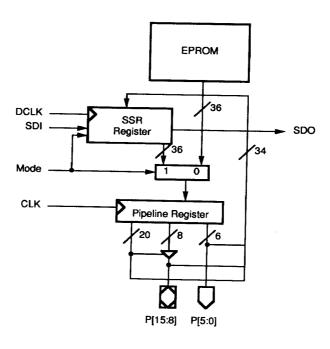

### Am29CPL154 SSR Diagnostics Option

As a programmable option, the Am29CPL154 FPC may be configured to contain Serial Shadow Register (SSR) diagnostics capability. SSR diagnostics is a simple, straightforward method of in-system testing to isolate problems down to the IC level.

The SSR diagnostics configuration activates a 36-bitwide D-type register called a "shadow" register, on the pipeline register inputs. The shadow register can be serially loaded from the SDI pin, parallel loaded from the pipeline register, or held. The pipeline register can be loaded from the Program Memory in normal mode or from the shadow register during diagnostics. A redefinition of four device pins is required to control the different diagnostics functions. T[7] also functions as the Serial Data Input (SDI), P[0] becomes the Serial Data Output (SDO), P[7] becomes the diagnostic clock (DCLK), and P[6] becomes the diagnostic mode control (MODE). The various diagnostic and normal modes are shown in table 4.

Serially loading a test instruction into the shadow register and parallel loading the shadow register contents into the pipeline register forces execution of the test instruction. The test result can then be clocked into the pipeline register as in normal operation mode, parallel loaded into the shadow register, and serially shifted out for system diagnostics.

Table 4

|                   |      | Inputs  |          |                | Outputs                                                                        |                                     |                                                            |

|-------------------|------|---------|----------|----------------|--------------------------------------------------------------------------------|-------------------------------------|------------------------------------------------------------|

| SDI               | MODE | DCLK    | CLK      | SDO            | Shadow<br>Register                                                             | Pipeline<br>Register                | Operation                                                  |

| Х                 | L    | Î       | H, L, ↓  | S <sub>0</sub> | $\begin{array}{c} S_{i-1} \leftarrow S_i \\ S_{35} \leftarrow SDI \end{array}$ | Hold                                | Serial Right - Shift<br>Shadow Register                    |

| T [7]<br>(Note 1) | L    | H, L, ↓ | 1        | S <sub>0</sub> | Hold                                                                           | P <sub>i</sub> ← EPROM <sub>i</sub> | Normal Operation;<br>Load Pipeline<br>Register from EPROM  |

| L                 | Н    | 1       | Н, L, ↓  | L              | S <sub>i</sub> ← P <sub>i</sub>                                                | Hold                                | Load Shadow Register<br>from Pipeline Register<br>(Note 2) |

| ×                 | Н    | H, L, ↓ | <b>↑</b> | SDI            | Hold                                                                           | P <sub>i</sub> ← S <sub>i</sub>     | Load Pipeline Register<br>from Shadow Register             |

| Н                 | Н    | 1       | H, L, ↓  | Н              | Hold                                                                           | Hold                                | Hold Shadow Register                                       |

#### Notes:

- 1. During normal operation, this pin behaves as the T[7] test input.

- S7, S6 are undefined. S[15:8] load from the source driving pins P[15:8]. If P[35] in the microword is a ONE, S[15:8] are loaded from the pipeline register. If P[35] in the microword is a ZERO, S[15:8] are loaded from an external source.

Kev

H = HIGH

L = LOW X = Don't Care

1 = LOW-to-HIGH transition

↓ = HIGH-to-LOW transition

10136-027A

Figure 3. SSR Diagnostics Logic

### **Erasure**

In order to fully erase all memory locations, it is necessary to expose the memory array to a standard ultraviolet light source having a wavelength of 2537 angstroms. The minimum recommended dose (UV intensity x exposure time) is 15 Wsec/cm². For a UV lamp with a 12 mW/cm² power rating, the exposure time would be about 30 minutes. The device should be located one inch from the source in a direct line.

It should be noted that erasure will begin with exposure to light having wavelengths less than 4000 angstroms.

To prevent exposure to sunlight or fluorescent lighting, an opaque label should be affixed over the window after programming.

OTP (One-Time Programmable) Am29CPL154 devices are available in plastic and are ideal for volume production. They can be inventoried unprogrammed and used with current software revisions; there is no window to be covered to prevent light from changing data.

### **ABSOLUTE MAXIMUM RATINGS**

-65°C to +150°C Storage Temperature

ings may cause permanent device failure. Functionality at or above these limits is not implied. Exposure to Absolute Maximum Ratings for extended periods may affect device reliabil-

Ambient Temperature with

**Power Applied** Supply Voltage with -55°C to +125°C

Respect to Ground DC Input Voltage

-0.5 V to +7.0 V -0.3 V to Vcc + 0.3 V

DC Output or I/O Pin Voltage

-0.3 V to Vcc + 0.3 V

DC Input Current Stresses above those listed under Absolute Maximum Rat-

ity. Programming conditions may differ.

-10 mA to +10 mA

### **OPERATING RANGES**

Commerciai (C) Devices

Ambient Temperature (T<sub>A</sub>)

Operating in Free Air

Supply Voltage (Vcc)

0°C to +75°C

with Respect to Ground

+4.5 V to +5.5 V

Operating ranges define those limits between which the func-

tionality of the device is guaranteed.

### DC CHARACTERISTICS over COMMERCIAL operating range unless otherwise specified

| Parameter<br>Symbol | Parameter Description                        | Test Condition                                             | s                 |                                                                              | Min. | Max.       | Unit |

|---------------------|----------------------------------------------|------------------------------------------------------------|-------------------|------------------------------------------------------------------------------|------|------------|------|

| V <sub>OH</sub>     | Output HIGH Voltage                          | I <sub>OH</sub> = -3.0 mA                                  | V <sub>IN</sub> = | V <sub>IH</sub> or V <sub>IL</sub><br>Min.                                   | 2.4  |            | ٧    |

| Vol                 | Output LOW Voltage                           | lo <sub>L</sub> = 16 mA                                    |                   | 0.5                                                                          | ٧    |            |      |

| ViH                 | Input HIGH Voltage                           | Guaranteed Inp<br>Voltage for all Ir                       | 2.0               |                                                                              | ٧    |            |      |

| VIL                 | Input LOW Voltage                            | Guaranteed Inp<br>Voltage for all Ir                       |                   | 8.0                                                                          | V    |            |      |

| let                 | Input HIGH Leakage<br>Current                | V <sub>IN</sub> = V <sub>CC</sub> - 0.5<br>(Note 2)        |                   | 10                                                                           | μA   |            |      |

| IIL                 | Input LOW Leakage<br>Current                 | V <sub>IN</sub> = 0.5 V, V <sub>CC</sub>                   | ; = Max.          | (Note 2)                                                                     |      | -10        | μА   |

| lozн                | Off-State Output Leakage<br>Current HIGH     | Vout = 2.4 V, V<br>VIN = VIH of VIL                        |                   | <b>C.</b>                                                                    |      | 10         | μА   |

| lozL                | Off-State Output Leakage<br>Current LOW      | Vout = 0.5 V, V<br>Vin = ViH or Vil.                       |                   | <b>x.</b>                                                                    |      | -10        | μА   |

| lcc                 | Supply Current                               | Outputs Open (lour = 0 mA) Vcc = Max.                      | CMOS<br>TTL       | V <sub>IN</sub> = GND or V <sub>CC</sub><br>V <sub>IN</sub> = 0.5 V or 2.4 V |      | 115<br>125 | mA   |

| C <sub>PD</sub>     | Power Dissipation<br>Capacitance<br>(Note 3) | V <sub>CC</sub> = Max.<br>T <sub>A</sub> = 25°C<br>No Load |                   |                                                                              | 100  | рҒ Турк    | al   |

#### Notes:

- 1. These are absolute values with respect to device ground and all overshoots due to system and/or tester noise are included.

- 2. I/O pin leakage is the worst case of I<sub>IL</sub> and I<sub>OZL</sub> (or I<sub>IH</sub> and I<sub>OZH</sub>).

- 3. The dynamic current consumption is: tcc (Total) = tcc (Static) + (Cpp + nCt) Vcc (f/2), where f is the clock frequency, Ct = the output load capacitance, and n is the number of loads.

### **CAPACITANCE** (Note 1)

| Parameter<br>Symbol | Parameter Description | on     | Test Conditio             | ns                                 | Max. | Unit |

|---------------------|-----------------------|--------|---------------------------|------------------------------------|------|------|

| CIN                 | Input Capacitance     | RESET  | V <sub>IN</sub> = 2.0 V   | V <sub>CC</sub> = 4.5 V to 5.5 V   | 25   | †    |

|                     |                       | Others |                           | _ T <sub>A</sub> = -55°C to +125°C | 15   | pF   |

| Соит                | Output Capacitance    |        | $V_{OUT} = 2.0 \text{ V}$ | f = 1 MHz                          | 15   | 1    |

#### Note:

These parameters are not 100% tested, but are evaluated at initial characterization and at any time the design is modified where capacitance may be affected.

## SWITCHING CHARACTERISTICS over COMMERCIAL operating range (Note 2)

|     | Parameter        |                                     |                             | H-          | 30   | H-25 |      |      |  |

|-----|------------------|-------------------------------------|-----------------------------|-------------|------|------|------|------|--|

| No. | Symbol           | Parameter                           | Parameter Description       |             | Max. | Min. | Max. | Unit |  |

| 1   | tco              | CLK to P[15                         | 5:0]                        |             | 18   |      | 20   | ns   |  |

| 2   |                  | CLK to A[8:                         | 0]                          |             | 30   |      | 36   | ns   |  |

| 3   | ts               | T[7:0] to CL                        | K, Registered               | 8           |      | 8    |      | ns   |  |

| 4   |                  | T[7:0] to CL<br>(Note 3)            | K, Asynchronous             | 33          |      | 40   |      | ns   |  |

| 5   |                  | RESET to CLK, Registered            |                             | 12          |      | 12   |      | ns   |  |

| 6   |                  | RESET to CLK, Asynchronous (Note 3) |                             | 30          |      | 40   |      | ns   |  |

| 7   | tH               | CLK to Τ[7:0                        | )]                          | 0           |      | 0    |      | ns   |  |

| 8   | (Note 4)         | CLK to RESI                         | ĒĪ                          | 0           |      | 0    |      | ns   |  |

| 9   | t <sub>PZX</sub> | CLK to P[15                         | :8] Enable                  |             | 33   |      | 40   | ns   |  |

| 10  | t <sub>PXZ</sub> | CLK to P[15                         | :8] Disable                 |             | 33   |      | 40   | ns   |  |

| 11  | twL              |                                     | LOW                         | 14          |      | 16   | -40  |      |  |

| 12  | tw⊢              | CLK Width                           | HIGH                        | 14          |      | 16   |      | ns   |  |

| 13  | tр               | CLK Period (Note 3)                 |                             | 33          |      | 40   |      | ns   |  |

| 14  | fmax             |                                     | equency (1/t <sub>P</sub> ) | <del></del> |      |      |      | ns   |  |

|     |                  |                                     | equency (mp)                | 30          |      | 25   |      | MHz  |  |

#### Note:

- 2. See Switching Test Circuit for test conditions.

- 3. These parameters are measured indirectly on unprogrammed devices. They are determined as follows:

- a. Measure delay from input (T[7:0], RESET, or CLK) to EPROM address out in test mode. This will measure the delay through the sequence logic.

- b. Measure setup time from T[7:0] input through EPROM test columns to pipeline register in verify test column mode. This will measure the delay through the EPROM and register setup.

- c. Measure delay from T[7:0] input to EPROM address out in verify test column mode. This will measure the delay through the logic and P[15:0] outputs.

To calculate the desired parameter measurement, the following formula is used:

Measurement (a) + Measurement (b) - Measurement (c)

CLK PERIOD:

RESET to CLK setup time:

CLK (a) + (b) - (c) = CLK PERIOD

RESET (a) + (b) - (c) = RESET to CLK setup time

T[7:0] to CLK setup time:

T[7:0] (a) + (b) - (c) = T[7:0] to CLK setup time

4. These hold time parameters are tested on a sample basis.

### **SWITCHING CHARACTERISTICS over COMMERCIAL operating range (Continued)**

|                   | Parameter       |                       |      | H-   | -30  | H-   | 25   |      |

|-------------------|-----------------|-----------------------|------|------|------|------|------|------|

| No.               | Symbol          | Parameter Description |      | Min. | Max. | Min. | Max. | Unit |

| SSR Configuration |                 |                       |      |      |      |      |      |      |

| 15                | t <sub>PD</sub> | Mode to SDC           |      |      | 25   |      | 30   | ns   |

| 16                |                 | SDI to SDO            |      |      | 25   |      | 30   | ns   |

| 17                | tco             | DCLK to SDC           | )    |      | 32   |      | 36   | ns   |

| 18                | ts              | Mode to CLK           |      | 25   |      | 30   |      | ns   |

| 19                |                 | Mode to DCLK          |      | 25   |      | 30   |      | ns   |

| 20                |                 | SDI to DCLK           |      | 25   |      | 30   |      | ns   |

| 21                |                 | P[15:8] to DCLK       |      | 25   |      | 30   |      | ns   |

| 22                | tн              | CLK to Mode           |      | 6    |      | 6    |      | ns   |

| 23                | (Note 1)        | DCLK to Mod           | е    | 0    |      | 0    |      | ns   |

| 24                |                 | DCLK to SDI           |      | 0    |      | 0    |      | ns   |

| 25                |                 | DCLK to P[15:8]       |      | 0    |      | 0    |      | ns   |

| 26                | tw∟             | DCLK Width            | LOW  | 20   |      | 25   |      | ns   |

| 27                | twн             |                       | HIGH | 20   |      | 25   |      | ns   |

| 28                | t₽              | DCLK Period           |      | 40   |      | 50   |      | ns   |

### Note:

<sup>1.</sup> These hold time parameters are tested on a sample basis.

### **ABSOLUTE MAXIMUM RATINGS**

Storage Temperature -65°C to +150°C

Ambient Temperature with Power Applied

-55°C to +125°C

Supply Voltage with

Respect to Ground

-0.5 V to +7.0 V

DC Input Voltage -0.3 V to V<sub>CC</sub> + 0.3 V

DC Output or I/O Pin Voltage DC Input Current -0.3 V to V<sub>CC</sub> + 0.3 V -10 mA to +10 mA

Stresses above those listed under Absolute Maximum Ratings may cause permanent device failure. Functionality at or above these limits is not implied. Exposure to Absolute Maximum Ratings for extended periods may affect device reliability. Programming conditions may differ. Absolute Maximum Ratings are for system design reference; parameters given are not tested.

### **OPERATING RANGES**

### Military (M) Devices

Ambient Temperature (T<sub>A</sub>)

-55°C to +125°C

Operating in Free Air

Supply Voltage (Vcc) with

+4.5 V to +5.5 V

Respect to Ground

Operating Ranges define those limits between which the functionality of the device is guaranteed.

#### Note:

Military products are tested at T<sub>C</sub> = 25°C, 125°C and -55°C.

## DC CHARACTERISTICS over MILITARY operating range unless otherwise specified

| Parameter<br>Symbol | Parameter Description                        | Test Conditio                                                                       |                                                                  | ungo umess ome                                                                 | Min.  | Max.       | Unit |

|---------------------|----------------------------------------------|-------------------------------------------------------------------------------------|------------------------------------------------------------------|--------------------------------------------------------------------------------|-------|------------|------|

| Vон                 | Output HIGH Voltage                          | I <sub>OH</sub> = -1.0 mA                                                           |                                                                  | V <sub>IN</sub> = V <sub>IH</sub> or V <sub>IL</sub><br>V <sub>CC</sub> = Min. | 2.4   |            | V    |

| V <sub>OL</sub>     | Output LOW Voltage                           | I <sub>OL</sub> = 12 mA                                                             |                                                                  | V <sub>IN</sub> = V <sub>IH</sub> or V <sub>IL</sub><br>V <sub>CC</sub> = Min. |       | 0.5        | ٧    |

| VH                  | Input HIGH Voltage                           | Guaranteed In<br>Voltage for all                                                    | Guaranteed Input Logical HIGH<br>Voltage for all Inputs (Note 1) |                                                                                |       |            | ٧    |

| ViL                 | Input LOW Voltage                            | Guaranteed Input Logical LOW<br>Voltage for all Inputs (Note 1)                     |                                                                  |                                                                                |       | 0.8        | V    |

| Ін                  | Input HIGH Leakage<br>Current                | $V_{IN} = V_{CC} - 0.5 \text{ V}, V_{CC} = \text{Max}.$ (Note 2)                    |                                                                  |                                                                                |       | 10         | μА   |

| l <sub>IL</sub>     | Input LOW Leakage<br>Current                 | V <sub>IN</sub> = 0.5 V, V <sub>CC</sub> = Max. (Note 2)                            |                                                                  |                                                                                |       | -10        | μА   |

| ЮZН                 | Off-State Output Leakage<br>Current HIGH     | V <sub>OUT</sub> = 2.4 V, V<br>V <sub>IN</sub> = V <sub>IH</sub> or V <sub>IL</sub> | / <sub>CC</sub> = Ma<br>(Note 2)                                 | х.                                                                             |       | 10         | μА   |

| lozL                | Off-State Output Leakage<br>Current LOW      |                                                                                     | cc = Ma                                                          |                                                                                |       | -10        | μА   |

| Icc                 | Supply Current                               | Outputs Open (Iout = 0 mA) Vcc = Max.                                               | CMOS<br>TTL                                                      | V <sub>IN</sub> = GND or V <sub>CC</sub><br>V <sub>IN</sub> = 0.5 V or 2.4 V   |       | 130<br>140 | mA   |

| C <sub>PD</sub>     | Power Dissipation<br>Capacitance<br>(Note 3) | Vcc = Max.<br>T <sub>A</sub> = 25°C<br>No Load                                      |                                                                  |                                                                                | 100 j | oF Typica  | al   |

#### Notes:

- 1. These are absolute values with respect to device ground and all overshoots due to system and/or tester noise are included.

- 2. I/O pin leakage is the worst case of I<sub>IL</sub> and I<sub>OZL</sub> (or I<sub>IH</sub> and I<sub>OZH</sub>).

- The dynamic current consumption is: lcc (Total) = lcc (Static) + (CpD + nCL) Vcc (f/2), where f is the clock frequency, C<sub>L</sub> = the output load capacitance, and n is the number of loads.

### **CAPACITANCE (Note 1)**

| Parameter<br>Symbol | Parameter Descripti | on     | Test Condition           | ns                               | Max. | Unit  |

|---------------------|---------------------|--------|--------------------------|----------------------------------|------|-------|

| CiN                 | Input Capacitance   | RESET  | V <sub>IN</sub> = 2.0 V  | V <sub>CC</sub> = 4.5 V to 5.5 V | 25   |       |

|                     |                     | Others |                          | T <sub>A</sub> = -55°C to +125°C | 15   | DF    |

| Соит                | Output Capacitance  |        | V <sub>OUT</sub> = 2.0 V | f = 1 MHz                        | 15   | 1 ' : |

#### Note:

# SWITCHING CHARACTERISTICS over MILITARY operating range (for APL Products, Group A, Subgroups 9, 10, 11 are tested unless otherwise noted) (Note 2)

| No. Parameter<br>No. Symbol |                  |                          |                             | Н    | -25  |      |

|-----------------------------|------------------|--------------------------|-----------------------------|------|------|------|

|                             |                  | Parameter                | Description                 | Min. | Max. | Unit |

| 1                           | tco              | CLK to P[15              | :0]                         |      | 25   | ns   |

| 2                           |                  | CLK to A[8:              | 0]                          |      | 40   | ns   |

| 3                           | ts               | T[7:0] to CL             | K, Registered               | 10   |      | ns   |

| 4                           |                  | T[7:0] to CL<br>(Note 3) | K, Asynchronous             | 40   |      | ns   |

| 5                           |                  | RESET to CLK, Registered |                             | 16   |      | ns   |

| 6                           |                  | RESET to CI<br>(Note 2)  | K, Asynchronous             | 40   |      | ns   |

| 7                           | tн               | CLK to T[7:0]            |                             | 0    |      | ns   |

| 8                           | (Note 4)         | CLK to RES               | ET                          | 0    |      | ns   |

| 9                           | tpzx             | CLK to P[15              | :8] Enable                  |      | 40   | ns   |

| 10                          | texz             | CLK to P[15              | :8] Disable                 |      | 35   | ns   |

| 11                          | tw.              | CLK Width                | LOW                         | 20   |      | ns   |

| 12                          | twn              | HIGH                     |                             | 20   |      | ns   |

| 13                          | tр               | CLK Period (Note 3)      |                             | 40   |      | ns   |

| 14                          | f <sub>MAX</sub> | Maximum Fr               | equency (1/t <sub>P</sub> ) | 25   |      | MHz  |

#### Note:

- 2. See Switching Test Circuit for test conditions.

- 3. These parameters are measured indirectly on unprogrammed devices. They are determined as follows:

- a. Measure delay from input (T[7:0], FIESET, or CLK) to EPROM address out in test mode. This will measure the delay through the sequence logic.

- b. Measure setup time from T[7:0] input through EPROM test columns to pipeline register in verify test column mode. This will measure the delay through the EPROM and register setup.

- Measure delay from T[7:0] input to EPROM address out in verify test column mode. This will measure the delay through the logic and P[15:0] outputs.

To calculate the desired parameter measurement, the following formula is used:

Measurement (a) + Measurement (b) - Measurement (c)

**CLK PERIOD:**

CLK (a) + (b) - (c) = CLK PERIOD

T[7:0] to CLK setup time:

T[7:0] (a) + (b) - (c) = T[7:0] to CLK setup time

4. These hold time parameters are tested on a sample basis.

RESET to CLK setup time:

RESET (a) + (b) - (c) = RESET to CLK setup time

These parameters are not 100% tested, but are evaluated at initial characterization and at any time the design is modified where capacitance may be affected.

## **SWITCHING CHARACTERISTICS over MILITARY operating range (Continued)**

|        | Davamatar           |               | *************************************** |     | H-25   |      |

|--------|---------------------|---------------|-----------------------------------------|-----|--------|------|

| No.    | Parameter<br>Symbol | Parameter De  | escription                              | Mir | . Max. | Unit |

| SSR Co | nfiguration         |               |                                         |     |        |      |

| 15     | tpD                 | Mode to SDO   |                                         |     | 30     | ns   |

| 16     |                     | SDI to SDO    |                                         |     | 30     | ns   |

| 17     | tco                 | DCLK to SDC   |                                         |     | 30     | ns   |

| 18     | ts                  | Mode to CLK   |                                         | 30  |        | ns   |

| 19     |                     | Mode to DCL   | <                                       | 30  |        | ns   |

| 20     | 1                   | SDI to DCLK   |                                         | 30  |        | ns   |

| 21     |                     | P[15:8] to DC | LK                                      | 30  |        | กร   |

| 22     | tн                  | CLK to Mode   |                                         | 6   |        | ns   |

| 23     | (Note 1)            | DCLK to Mod   | e                                       | 0   |        | ns   |

| 24     |                     | DCLK to SDI   |                                         | 0   |        | ns   |

| 25     |                     | DCLK to P[15  | DCLK to P[15:8]                         |     |        | ns   |

| 26     | twL                 | DCLK Width    | LOW                                     | 30  |        | ns   |

| 27     | twн                 |               | HIGH                                    | 30  |        | ns   |

| 28     | tр                  | DCLK Period   |                                         | 60  |        | ns   |

### Note:

1. These hold time parameters are tested on a sample basis.

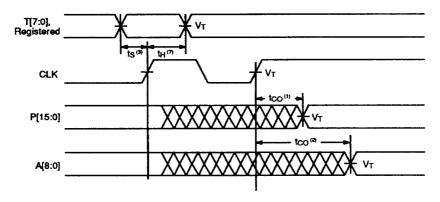

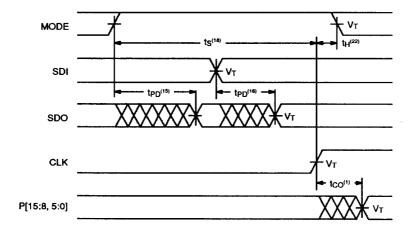

# **SWITCHING WAVEFORMS Normal Configuration**

Registered Test Inputs

10136-028A

10136-029A

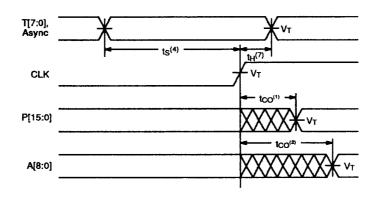

**Asynchronous Test Inputs**

# **SWITCHING WAVEFORMS (Continued) Normal Configuration** RESET, Registered CLK tco(1) P[15:0] 10136-030A Registered RESET RESET, Async CLK P[15:0] 10136-031A Asynchronous RESET CLK P[15:8] 10136-032A CLK to Output Disable/Enable twH(12) CLK 10136-033A

Am29CPL154

Clock Width/Period

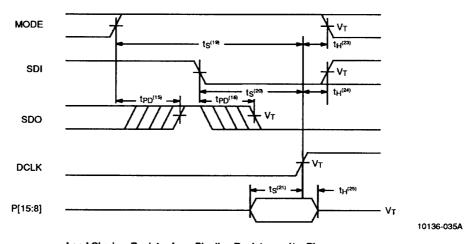

# **SWITCHING WAVEFORMS (Continued) SSR Configuration**

Load Pipeline Register from Shadow Register

10136-034A

Load Shadow Register from Pipeline Register and/or Pins

3-129

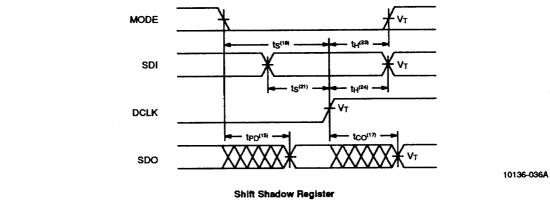

# **SWITCHING WAVEFORMS (Continued) SSR Configuration**

DCLK tp(28)

DCLK Width/Period

10136-037A

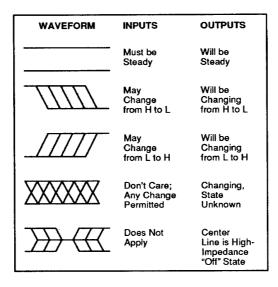

### **KEY TO SWITCHING WAVEFORMS**

KS000010-PAL

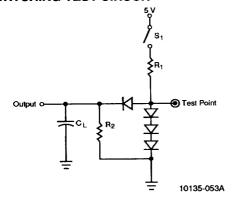

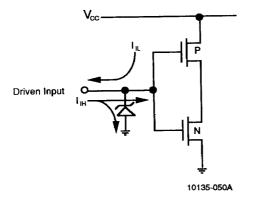

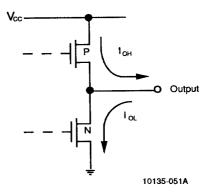

### **SWITCHING TEST CIRCUIT**

Three

10135-054A

| -State Outputs | Two-State | Outputs |

|----------------|-----------|---------|

|----------------|-----------|---------|

|               |                              |       | Commercial     |                | Commercial Military |                | Military                                                                     |  | Measured |

|---------------|------------------------------|-------|----------------|----------------|---------------------|----------------|------------------------------------------------------------------------------|--|----------|

| Specification | S <sub>1</sub>               | CL    | R <sub>1</sub> | R <sub>2</sub> | R₁                  | R <sub>2</sub> | Output Value                                                                 |  |          |

| tpp, tco      | Closed                       |       |                |                |                     |                | 1.5 V                                                                        |  |          |

| tpzx          | Z → H: Open<br>Z → L: Closed | 50 pF | 667 Ω          | 5 kΩ           | 667 Ω               | 5 kΩ           | 1.5 V                                                                        |  |          |

| texz          | H → Z: Open<br>L → Z: Closed | 5 pF  |                |                |                     |                | $H \rightarrow Z$ : $V_{OH} - 0.5 V$<br>$L \rightarrow Z$ : $V_{OL} + 0.5 V$ |  |          |

Note:

Pulse generator for all pulses: Rate  $\leq$  1.0 MHz;  $Z_O = 50~\Omega$ :  $t_r \leq$  2.5 ns.

3-130 Am29CPL154

### **TEST PHILOSOPHY AND METHODS**

The following eight points describe AMD's philosophy for high volume, high speed automatic testing.

- Ensure that the part is adequately decoupled at the test head. Large changes in V<sub>CC</sub> current as the device switches may cause erroneous function failures due to V<sub>CC</sub> changes.

- Do not leave inputs floating during any tests, as they may start to oscillate at high frequency.