## **LXT6251A**

### 21 E1 SDH Mapper

#### **Datasheet**

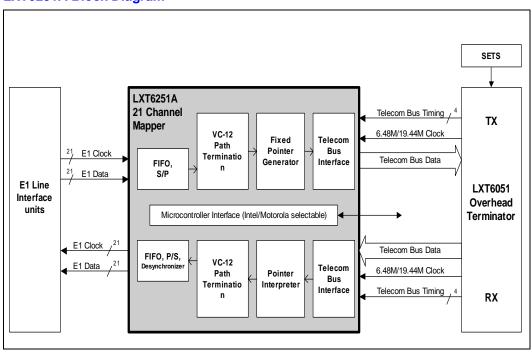

The LXT6251A 21E1 Mapper performs asynchronous mapping and demapping of 21 E1 PDH signals into SDH. The PDH side interfaces with E1 LIUs and framers via NRZ Clock & Data, while the SDH side uses a standard Telecom bus interface. Further processing by the companion LXT6051 Overhead Terminator chip creates the final STM-0 or STM-1 signal. One mapper provides complete processing of 21 E1s in STM-0, while three mappers can process 63 E1s in STM-1.

The LXT6251A is compliant with the latest releases of ITU-T G.703 and G.707. It provides all the alarm and control features to easily implement the multiplexer specified in ITU-T G.783.

## **Applications**

- 21 or 63 E1 Terminal or ADM SDH Multiplexer

- Digital Cross Connect System

- Digital Loop Carrier Systems (NGDLC)

- Microwave Radio System

### **Product Features**

- Maps and Demaps 21 E1 signals between PDH and SDH networks via VC-12 asynchronous mapping.

- Multiplexes the 21 VC-12 signals into seven interleaved TUG-2 structures for STM-0 or a TUG-3 structure for STM-1 applications.

- Configurable as a flexible Add/Drop Multiplexer for up to 21 E1 tributaries, with each E1 I/O port assignable to any TU time slot within an AU-3 or TUG-3.

- Performs VC-12 path overhead processing for all 21 VC-12s, including V5, J2 Path Trace, and K4 Enhanced RDI.

- Records TU pointer alarms (TU-AIS, TU-LOP), BIP-2 and REI error counts, TIM and PLM alarms, and all other V5 POH alarms for all 21 tributaries.

- NRZ Data and Clock interface for E1 tributary access.

- Microprocessor/SEMF interface to set Signal Label, J2 Path Trace, access alarms and counters

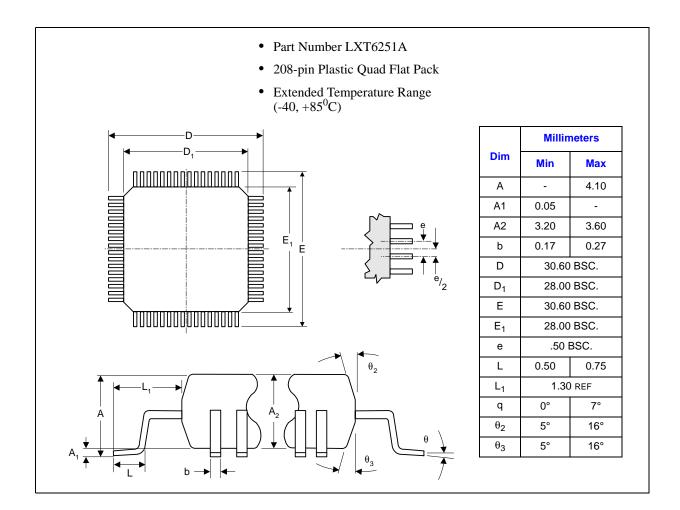

- Low power CMOS technology with 3.3V core and 5V I/O, available in PQFP-208 package.

Order Number: 249300-001

January 2001

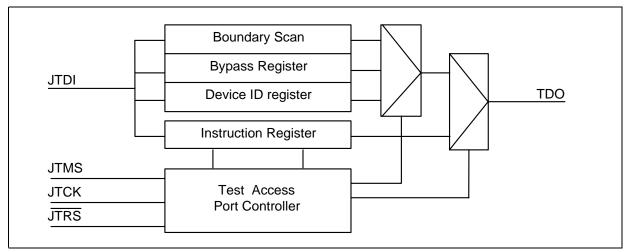

■ IEEE 1149.1 (JTAG) support.

Information in this document is provided in connection with Intel<sup>®</sup> products. No license, express or implied, by estoppel or otherwise, to any intellectual property rights is granted by this document. Except as provided in Intel's Terms and Conditions of Sale for such products, Intel assumes no liability whatsoever, and Intel disclaims any express or implied warranty, relating to sale and/or use of Intel products including liability or warranties relating to fitness for a particular purpose, merchantability, or infringement of any patent, copyright or other intellectual property right. Intel products are not intended for use in medical, life saving, or life sustaining applications.

Intel may make changes to specifications and product descriptions at any time, without notice.

Designers must not rely on the absence or characteristics of any features or instructions marked "reserved" or "undefined." Intel reserves these for future definition and shall have no responsibility whatsoever for conflicts or incompatibilities arising from future changes to them.

The LXT6251A may contain design defects or errors known as errata which may cause the product to deviate from published specifications. Current characterized errata are available on request.

Contact your local Intel sales office or your distributor to obtain the latest specifications and before placing your product order.

Copies of documents which have an ordering number and are referenced in this document, or other Intel literature may be obtained by calling 1-800-548-4725 or by visiting Intel's website at http://www.intel.com.

Copyright © Intel Corporation, 2001

\*Third-party brands and names are the property of their respective owners.

| 1.0 | Bloc  | k Diag  | ram                                          | 7        |

|-----|-------|---------|----------------------------------------------|----------|

| 2.0 | Pin A | Assigni | ments and Signal Descriptions                | 8        |

| 3.0 | Fund  | ctional | Description                                  | 16       |

|     | 3.1   |         | uction                                       |          |

|     | 3.2   |         | ve Section, Terminal Mode                    |          |

|     | 0.2   | 3.2.1   | Receive Alarms                               |          |

|     |       | 0.2     | 3.2.1.1 Parity Alarm                         |          |

|     |       |         | 3.2.1.2 Loss of Multiframe                   |          |

|     | 3.3   | High C  | Order Path Adaptation                        | 18       |

|     |       | 3.3.1   | Alarms and Status                            | 18       |

|     |       |         | 3.3.1.1 TU-AIS                               | 18       |

|     |       |         | 3.3.1.2 TU Loss of Pointer (LOP)             | 19       |

|     | 3.4   | Low O   | Order Path Termination                       |          |

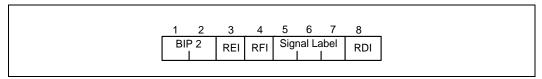

|     |       | 3.4.1   | V5 Processing                                |          |

|     |       |         | 3.4.1.1 BIP-2 Errors (V5, bits 1,2)          |          |

|     |       |         | 3.4.1.2 REI Detection (V5, bit 3)            |          |

|     |       |         | 3.4.1.3 RFI Detection (V5, bit 4)            |          |

|     |       |         | 3.4.1.4 Signal Label Mismatch (V5, bits 5-7) |          |

|     |       |         | 3.4.1.5 Unequipped Detection (V5, bits 5-7)  | ۱∠<br>21 |

|     |       |         | 3.4.1.7 RDI Detection (V5, bit 8)            |          |

|     |       | 3.4.2   | J2 Processing                                |          |

|     |       | 0       | 3.4.2.1 J2 Memory Access                     |          |

|     |       |         | 3.4.2.2 CRC-7 Error                          |          |

|     |       |         | 3.4.2.3 Trace Identifier Mismatch            |          |

|     |       | 3.4.3   | N2 Processing                                | 23       |

|     |       | 3.4.4   | K4 Processing                                | 23       |

|     |       |         | 3.4.4.1 Enhanced RDI                         | 23       |

|     |       | 3.4.5   | Summary of Alarms causing E1 AIS             | 23       |

|     |       |         | 3.4.5.1 TU-AIS Alarm                         |          |

|     |       |         | 3.4.5.2 TU-LOP Alarm                         |          |

|     |       |         | 3.4.5.3 Signal Label Mismatch                |          |

|     |       |         | 3.4.5.4 Unequipped Alarm                     |          |

|     | 2.5   | Low     | 3.4.5.5 J2 Path Label Mismatch               |          |

|     | 3.5   | 3.5.1   | Order Path Adaptation  Desynchronizer        |          |

| 4.0 | Tran  | smit S  | ection, Terminal Mode                        |          |

|     | 4.1   |         | order Path Adaptation                        |          |

|     | 4.2   |         | Order Path Termination                       |          |

|     | 7.2   | 4.2.1   | V5 Processing                                |          |

|     |       | 1.4.1   | 4.2.1.1 BIP-2                                |          |

|     |       |         | 4.2.1.2 REI Bit                              |          |

|     |       |         | 4.2.1.3 RFI Bit                              |          |

|     |       |         | 4.2.1.4 Signal Label                         |          |

|     |       |         | 4.2.1.5 RDI Bit                              | 27       |

|     |      | 4.2.2 J2 Processing                           | 27               |

|-----|------|-----------------------------------------------|------------------|

|     |      | 4.2.2.1 J2 Memory Access                      | 28               |

|     |      | 4.2.3 K4 Processing                           | 28               |

|     |      | 4.2.4 N2 Processing                           | 28               |

|     | 4.3  | High Order Path Adaptation                    | 29               |

| 5.0 | Add  | Drop Configuration                            | 30               |

|     | 5.1  | ADM Receive                                   |                  |

|     | 5.2  | ADM Transmit                                  |                  |

|     | 0.2  | 5.2.1 Data Pass-Through                       |                  |

|     |      | 5.2.1.1 PTSOH                                 |                  |

|     |      | 5.2.1.2 PTTUGx                                |                  |

|     |      | 5.2.2 MTBDATA Drive Enable                    |                  |

| 6.0 | Ann  | ication Information                           |                  |

|     | 6.1  | Port Mapping Configuration                    |                  |

|     | 6.2  | Telecom Bus Interface                         |                  |

|     | 0.2  | 6.2.1 Multiplexer Telecom Bus, Terminal Mode  |                  |

|     |      | 6.2.2 Multiplexer Telecom Bus, ADM Mode       |                  |

|     |      | 6.2.3 MTBDATA Output Enable                   |                  |

|     |      | 6.2.4 Demultiplexer Telecom Bus               |                  |

|     |      | 6.2.5 Telecom Bus Timing                      |                  |

|     | 6.3  | Serial/Remote Alarm Processing Port           |                  |

|     |      | _                                             |                  |

| 7.0 | Test | Specifications                                | 42               |

| 8.0 | Micr | oprocessor Interface & Register Definition    | ons50            |

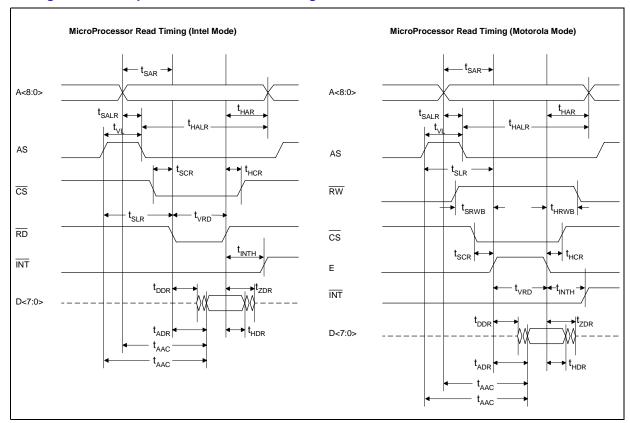

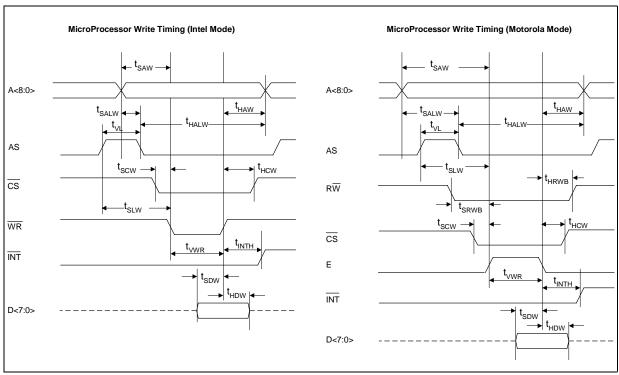

|     | 8.1  | Microprocessor Interface                      | 50               |

|     |      | 8.1.1 Intel Interface                         | 50               |

|     |      | 8.1.2 Motorola Interface                      | 50               |

|     | 8.2  | Interrupt Handling                            | 51               |

|     |      | 8.2.1 Interrupt Sources                       | 51               |

|     |      | 8.2.1.1 Interrupt Identification              | 51               |

|     |      | 8.2.2 Interrupt Enables                       | 51               |

|     |      | 8.2.3 Interrupt Clearing                      | 52               |

|     |      | 8.2.4 UpdateEn Configuration Bit              | 52               |

|     | 8.3  | Register Address Map                          | 52               |

|     |      | 8.3.1 Counter Access                          | 53               |

|     |      | 8.3.2 Register Notations and Definitions      | 53               |

|     | 8.4  | Configuration Registers                       | 55               |

|     |      | 8.4.1 GLOB_CONF—Global Configuration (000     | )H)55            |

|     |      | 8.4.2 TADD_CONF—Transmit Add Configuration    | on (003–001H)56  |

|     |      | 8.4.3 TU_TS_CONF—TU Time Slot Configurat      | ion (161–175H)57 |

|     |      | 8.4.4 SIGLA_SET—Signal Label Setting (xEH)    | 57               |

|     |      | 8.4.5 J2_MRST—J2 Memory Reset (008H)          | 57               |

|     |      | 8.4.6 J2_ESDATA—J2 Expected String Data (>    | (CH)58           |

|     |      | 8.4.7 J2_TSDATA—J2 Transmit String Data (x    | FH)58            |

|     |      | 8.4.8 ERRI_CONF—Error Insert Configuration    | (xDH)58          |

|     |      | 8.4.9 INT_CONF—Interrupt Configuration Regi   | ster (00BH)59    |

|     |      | 8.4.10 CHIP_ID—Chip Identification Number (00 | AH)59            |

|     | 8.5  | Interrupt Registers                           | 60               |

|     |      |                                               |                  |

|                |       | 8.5.1 GLOB_INTS—Global Interrupt Source (00CH)                       |     |

|----------------|-------|----------------------------------------------------------------------|-----|

|                |       | 8.5.2 TRIB_ISRC—Tributary Interrupt Source Identification (00F–00DH) | 60  |

|                |       | 8.5.3 TRIB_INT—Tributary Interrupt (x1-x0H)                          |     |

|                |       | 8.5.4 TRIB_INTE—Tributary Interrupt Enable (x5–x4H)                  |     |

|                | 8.6   | Status and Control Registers                                         |     |

|                |       | 8.6.1 TRIB_STA—Tributary Status (x3–x2H)                             | 63  |

|                |       | 8.6.2 BIP2_ERRCNT—BIP2 Error Counter (x7–x6H)                        | 63  |

|                |       | 8.6.3 REI_CNT—Remote Error Indication (REI) Counter (x9–x8H)         | 64  |

|                |       | 8.6.4 K4_STA—K4 Status (xAH)                                         |     |

|                |       | 8.6.5 V5_STA—V5 Status Register (xBH)                                | 64  |

| 9.0            | Testa | ability Modes                                                        | 66  |

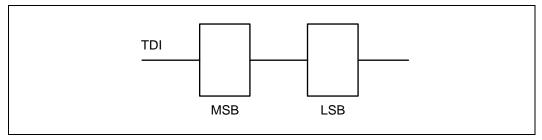

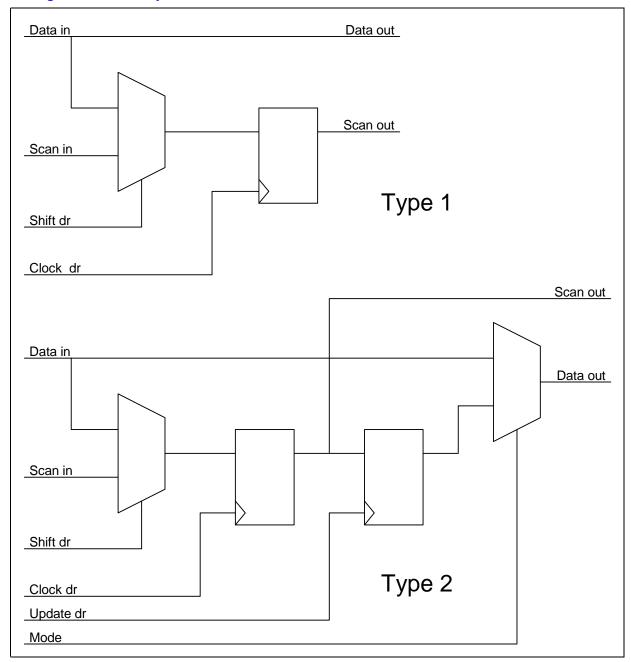

|                | 9.1   | IEEE 1149.1 Boundary Scan Description                                | 66  |

|                |       | 9.1.1 Instruction Register and Definitions                           |     |

|                |       | 9.1.1.1 EXTEST ('b00)                                                |     |

|                |       | 9.1.1.2 SAMPLE/PRELOAD ('b01)                                        | 68  |

|                |       | 9.1.1.3 BYPASS ('b11)                                                |     |

|                |       | 9.1.1.4 IDCODE ('b10)                                                |     |

|                |       | 9.1.2 Boundary Scan Register                                         | 68  |

| 10.0           | Pack  | age Specification                                                    | 75  |

| 11.0           | Gloss | sary                                                                 | 76  |

| 11.0           | 0103. | sar y                                                                | / 0 |

| <b>Figures</b> |       |                                                                      |     |

| 9000           | 1     | LXT6251A Block Diagram                                               | 7   |

|                | 2     | LXT6251A Pin Assignments                                             |     |

|                | 3     | LXT6251A Block Diagram                                               |     |

|                | 4     | V1/V2 Pointer Diagram                                                |     |

|                | 5     | V5 Byte                                                              |     |

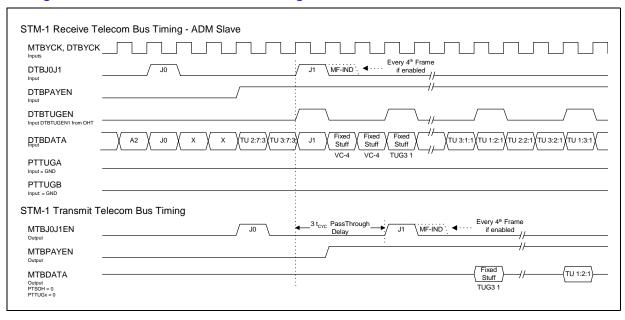

|                | 6     | Add/Drop Configuration Data Flow                                     |     |

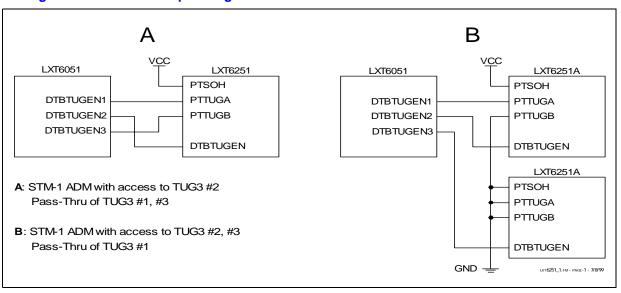

|                | 7     | ADM Multi-chip Configuration                                         |     |

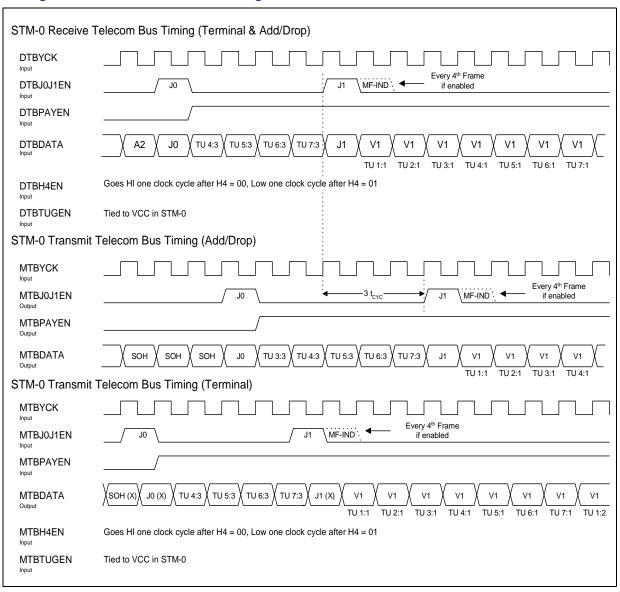

|                | 8     | STM-0 Telecom Bus Timing                                             |     |

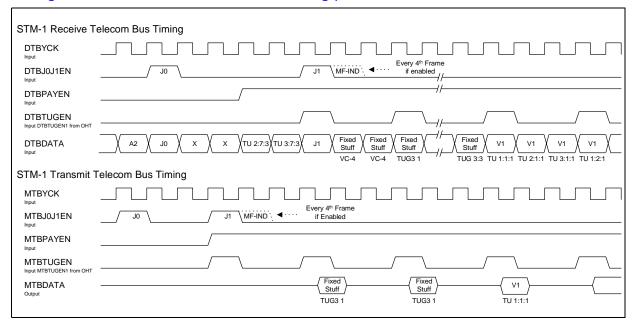

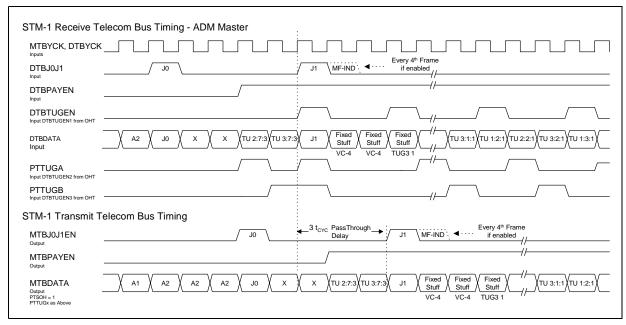

|                | 9     | Terminal STM-1 Telecom Bus Timing (                                  |     |

|                | 10    | ADM STM-1 Telecom Bus Timing (                                       |     |

|                | 11    | ADM STM-1 Telecom Bus Timing w/ PTSOH = 0                            |     |

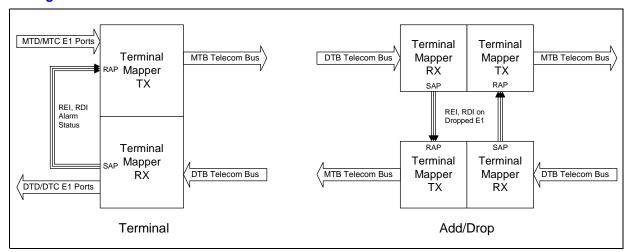

|                | 12    | SAP Bus Connections for Terminal & ADM                               |     |

|                | 13    | SAP Bus Frame Format                                                 |     |

|                | 14    | Tributary Timing                                                     |     |

|                | 15    | Receive Telecom Bus Timing                                           |     |

|                | 16    | Transmit Telecom Bus Timing - Terminal                               |     |

|                | 17    | Transmit Telecom Bus Timing - ADM Parameters                         |     |

|                | 18    | Microprocessor Data Read Timing                                      |     |

|                | 19    | Microprocessor Data Write Timing                                     |     |

|                | 20    | Test Access Port                                                     |     |

|                | 21    | Instruction Register                                                 |     |

|                | 22    | Boundary Scan Cells                                                  |     |

|                |       |                                                                      |     |

## LXT6251A — 21 E1 SDH Mapper

**Datasheet**

## **Tables**

| 1 Signal Description Nomenclature                    | g  |

|------------------------------------------------------|----|

| 2 Pin Descriptions                                   | 9  |

| 3 Power, Ground, and No Connects                     |    |

| 4 Enhanced RDI Interpretation                        |    |

| 5 Enhanced RDI Generation                            |    |

| 6 Multiplex Telecom Bus Drive Matrix                 | 32 |

| 7 E1 Port Time Slot Assignment                       |    |

| 8 Absolute Maximum Ratings                           | 42 |

| 9 Operating Conditions                               | 42 |

| 10 5 V Digital I/O Characteristics                   | 42 |

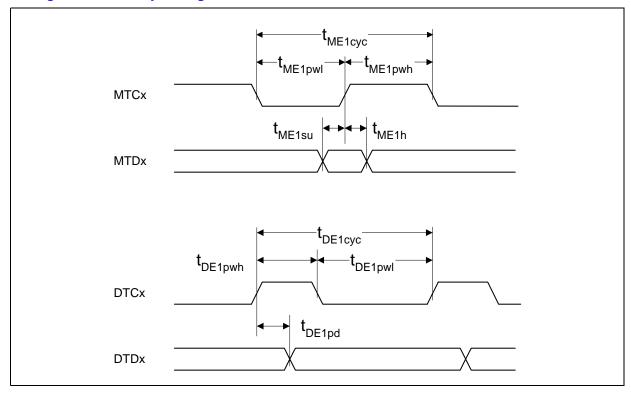

| 11 Tributary Timing Parameters                       | 43 |

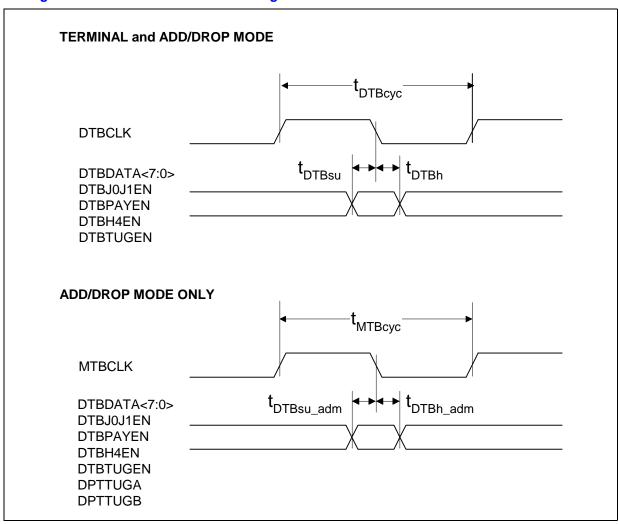

| 12 Receive Telecom Bus Timing Parameters             |    |

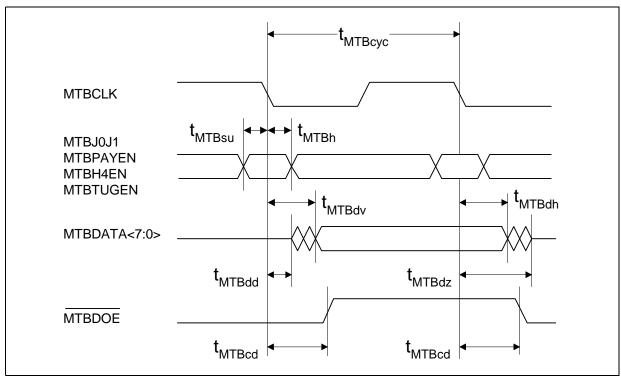

| 13 Transmit Telecom Bus Timing - Terminal Parameters | 45 |

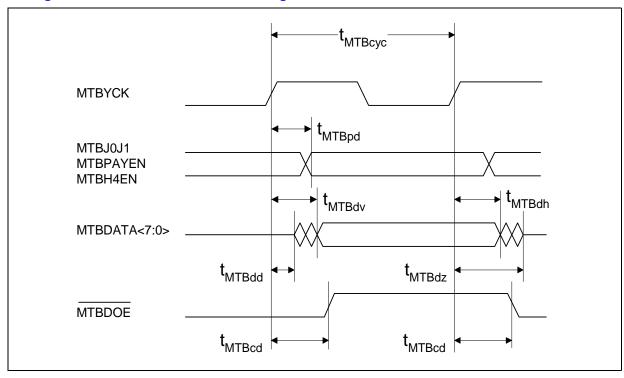

| 14 Transmit Telecom Bus Timing - ADM Parameters      | 46 |

| 15 Microprocessor Data Read Timing Parameters        | 47 |

| 16 Microprocessor Data Write Timing Parameters       |    |

| 17 Register Address Map                              |    |

| 18 JTAG Pin Description                              |    |

| 19 JTAG Scan Chain                                   | 70 |

# 1.0 Block Diagram

Figure 1. LXT6251A Block Diagram

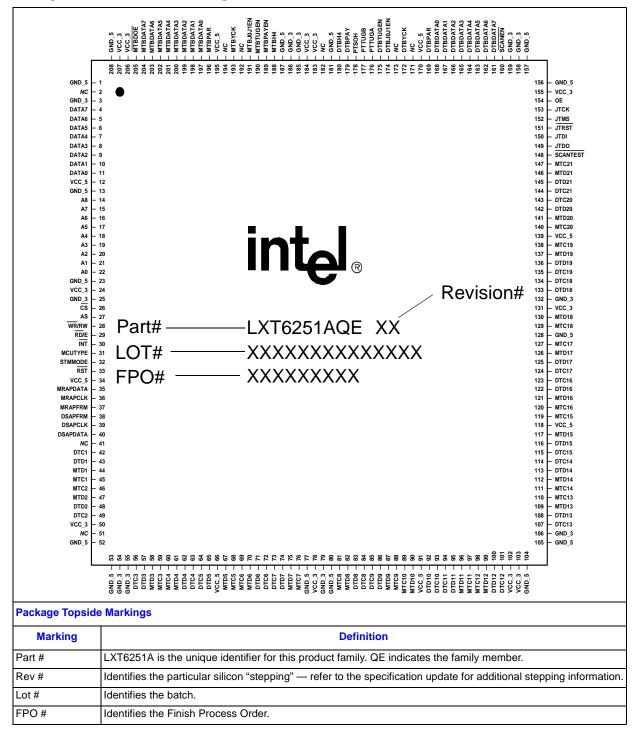

## 2.0 Pin Assignments and Signal Descriptions

Figure 2. LXT6251A Pin Assignments

**Table 1. Signal Description Nomenclature**

| Туре               | Description               |  |

|--------------------|---------------------------|--|

| I                  | Standard input signal     |  |

| 0                  | Standard output signal    |  |

| I/O                | Input and output signal   |  |

| TTLin <sup>1</sup> | Supports TTL input levels |  |

| HiZ <sup>1</sup>   | High Impedance            |  |

Some signals indicate buffer strength. For example, HiZ-4ma indicates a high-impedance buffer capable of sourcing 4 ma.

Table 2. Pin Descriptions (Sheet 1 of 7)

| Pin# | Name  | Туре        | Function                                                                             |

|------|-------|-------------|--------------------------------------------------------------------------------------|

|      |       | E1 Tra      | nsmit and Receive Ports                                                              |

| 44   | MTD1  | I<br>TTL in | <b>Transmit Tributary NRZ Data Port # 1.</b> Input E1 NRZ data input at 2.048 Mbit/s |

| 47   | MTD2  | I<br>TTL in | Transmit Tributary NRZ Data Port # 2                                                 |

| 58   | MTD3  | I<br>TTL in | Transmit Tributary NRZ Data Port # 3                                                 |

| 61   | MTD4  | I<br>TTL in | Transmit Tributary NRZ Data Port # 4                                                 |

| 67   | MTD5  | I<br>TTL in | Transmit Tributary NRZ Data Port # 5                                                 |

| 70   | MTD6  | I<br>TTL in | Transmit Tributary NRZ Data Port # 6                                                 |

| 75   | MTD7  | I<br>TTL in | Transmit Tributary NRZ Data Port # 7                                                 |

| 82   | MTD8  | I<br>TTL in | Transmit Tributary NRZ Data Port # 8                                                 |

| 87   | MTD9  | I<br>TTL in | Transmit Tributary NRZ Data Port # 9                                                 |

| 90   | MTD10 | I<br>TTL in | Transmit Tributary NRZ Data Port # 10                                                |

| 96   | MTD11 | I<br>TTL in | Transmit Tributary NRZ Data Port # 11                                                |

| 99   | MTD12 | I<br>TTL in | Transmit Tributary NRZ Data Port # 12                                                |

| 109  | MTD13 | I<br>TTL in | Transmit Tributary NRZ Data Port # 13                                                |

| 112  | MTD14 | I<br>TTL in | Transmit Tributary NRZ Data Port # 14                                                |

| 117  | MTD15 | I<br>TTL in | Transmit Tributary NRZ Data Port # 15                                                |

| 121  | MTD16 | I<br>TTL in | Transmit Tributary NRZ Data Port # 16                                                |

Table 2. Pin Descriptions (Continued) (Sheet 2 of 7)

| Pin # | Name  | Туре        | Function                                                      |

|-------|-------|-------------|---------------------------------------------------------------|

| 126   | MTD17 | I<br>TTL in | Transmit Tributary NRZ Data Port # 17                         |

| 130   | MTD18 | I<br>TTL in | Transmit Tributary NRZ Data Port # 18                         |

| 137   | MTD19 | I<br>TTL in | Transmit Tributary NRZ Data Port # 19                         |

| 141   | MTD20 | I<br>TTL in | Transmit Tributary NRZ Data Port # 20                         |

| 146   | MTD21 | I<br>TTL in | Transmit Tributary NRZ Data Port # 21                         |

| 45    | MTC1  | I<br>TTL in | Transmit Tributary Clock Port # 1 Input E1 clock at 2.048 MHz |

| 46    | MTC2  | I<br>TTL in | Transmit Tributary Clock Port # 2                             |

| 59    | MTC3  | I<br>TTL in | Transmit Tributary Clock Port # 3                             |

| 60    | MTC4  | I<br>TTL in | Transmit Tributary Clock Port # 4                             |

| 68    | MTC5  | I<br>TTL in | Transmit Tributary Clock Port # 5                             |

| 69    | MTC6  | I<br>TTL in | Transmit Tributary Clock Port # 6                             |

| 76    | MTC7  | I<br>TTL in | Transmit Tributary Clock Port # 7                             |

| 81    | MTC8  | I<br>TTL in | Transmit Tributary Clock Port # 8                             |

| 88    | MTC9  | I<br>TTL in | Transmit Tributary Clock Port # 9                             |

| 89    | MTC10 | I<br>TTL in | Transmit Tributary Clock Port # 10                            |

| 97    | MTC11 | I<br>TTL in | Transmit Tributary Clock Port # 11                            |

| 98    | MTC12 | I<br>TTL in | Transmit Tributary Clock Port # 12                            |

| 110   | MTC13 | I<br>TTL in | Transmit Tributary Clock Port # 13                            |

| 111   | MTC14 | I<br>TTL in | Transmit Tributary Clock Port # 14                            |

| 119   | MTC15 | I<br>TTL in | Transmit Tributary Clock Port # 15                            |

| 120   | MTC16 | I<br>TTL in | Transmit Tributary Clock Port # 16                            |

| 127   | MTC17 | I<br>TTL in | Transmit Tributary Clock Port # 17                            |

| 129   | MTC18 | I<br>TTL in | Transmit Tributary Clock Port # 18                            |

Table 2. Pin Descriptions (Continued) (Sheet 3 of 7)

| Pin# | Name  | Туре           | Function                                                                                              |

|------|-------|----------------|-------------------------------------------------------------------------------------------------------|

| 138  | MTC19 | I<br>TTL in    | Transmit Tributary Clock Port # 19                                                                    |

| 140  | MTC20 | I<br>TTL in    | Transmit Tributary Clock Port # 20                                                                    |

| 147  | MTC21 | I<br>TTL in    | Transmit Tributary Clock Port # 21                                                                    |

| 43   | DTD1  | O<br>HiZ - 2mA | Receive Tributary NRZ Data Port #1 Received E1 NRZ data output from the demapped VC-12 at 2.048Mbit/s |

| 48   | DTD2  | O<br>HiZ - 2mA | Receive Tributary NRZ Data Port # 2                                                                   |

| 57   | DTD3  | O<br>HiZ - 2mA | Receive Tributary NRZ Data Port # 3                                                                   |

| 62   | DTD4  | O<br>HiZ - 2mA | Receive Tributary NRZ Data Port # 4                                                                   |

| 65   | DTD5  | O<br>HiZ - 2mA | Receive Tributary NRZ Data Port # 5                                                                   |

| 71   | DTD6  | O<br>HiZ - 2mA | Receive Tributary NRZ Data Port # 6                                                                   |

| 74   | DTD7  | O<br>HiZ - 2mA | Receive Tributary NRZ Data Port # 7                                                                   |

| 83   | DTD8  | O<br>HiZ - 2mA | Receive Tributary NRZ Data Port # 8                                                                   |

| 86   | DTD9  | O<br>HiZ - 2mA | Receive Tributary NRZ Data Port # 9                                                                   |

| 92   | DTD10 | O<br>HiZ - 2mA | Receive Tributary NRZ Data Port # 10                                                                  |

| 95   | DTD11 | O<br>HiZ - 2mA | Receive Tributary NRZ Data Port # 11                                                                  |

| 100  | DTD12 | O<br>HiZ - 2mA | Receive Tributary NRZ Data Port # 12                                                                  |

| 108  | DTD13 | O<br>HiZ - 2mA | Receive Tributary NRZ Data Port # 13                                                                  |

| 113  | DTD14 | O<br>HiZ - 2mA | Receive Tributary NRZ Data Port # 14                                                                  |

| 116  | DTD15 | O<br>HiZ - 2mA | Receive Tributary NRZ Data Port # 15                                                                  |

| 122  | DTD16 | O<br>HiZ - 2mA | Receive Tributary NRZ Data Port # 16                                                                  |

| 125  | DTD17 | O<br>HiZ - 2mA | Receive Tributary NRZ Data Port # 17                                                                  |

| 133  | DTD18 | O<br>HiZ - 2mA | Receive Tributary NRZ Data Port # 18                                                                  |

| 136  | DTD19 | O<br>HiZ - 2mA | Receive Tributary NRZ Data Port # 19                                                                  |

| 142  | DTD20 | O<br>HiZ - 2mA | Receive Tributary NRZ Data Port # 20                                                                  |

Table 2. Pin Descriptions (Continued) (Sheet 4 of 7)

| Pin# | Name  | Туре           | Function                                                                                                                                        |

|------|-------|----------------|-------------------------------------------------------------------------------------------------------------------------------------------------|

| 145  | DTD21 | O<br>HiZ - 2mA | Receive Tributary NRZ Data Port # 21                                                                                                            |

| 42   | DTC1  | O<br>HiZ - 2mA | Receive Tributary Clock Port # 1. Received E1 clock at 2.048 MHz recovered from VC-12. This clock is gapped, data is valid on the falling edge. |

| 49   | DTC2  | O<br>HiZ - 2mA | Receive Tributary Clock Port # 2                                                                                                                |

| 56   | DTC3  | O<br>HiZ - 2mA | Receive Tributary Clock Port # 3                                                                                                                |

| 63   | DTC4  | O<br>HiZ - 2mA | Receive Tributary Clock Port # 4                                                                                                                |

| 64   | DTC5  | O<br>HiZ - 2mA | Receive Tributary Clock Port # 5                                                                                                                |

| 72   | DTC6  | O<br>HiZ - 2mA | Receive Tributary Clock Port # 6                                                                                                                |

| 73   | DTC7  | O<br>HiZ - 2mA | Receive Tributary Clock Port # 7                                                                                                                |

| 84   | DTC8  | O<br>HiZ - 2mA | Receive Tributary Clock Port # 8                                                                                                                |

| 85   | DTC9  | O<br>HiZ - 2mA | Receive Tributary Clock Port # 9                                                                                                                |

| 93   | DTC10 | O<br>HiZ - 2mA | Receive Tributary Clock Port # 10                                                                                                               |

| 94   | DTC11 | O<br>HiZ - 2mA | Receive Tributary Clock Port # 11                                                                                                               |

| 101  | DTC12 | O<br>HiZ - 2mA | Receive Tributary Clock Port # 12                                                                                                               |

| 107  | DTC13 | O<br>HiZ - 2mA | Receive Tributary Clock Port # 13                                                                                                               |

| 114  | DTC14 | O<br>HiZ - 2mA | Receive Tributary Clock Port # 14                                                                                                               |

| 115  | DTC15 | O<br>HiZ - 2mA | Receive Tributary Clock Port # 15                                                                                                               |

| 123  | DTC16 | O<br>HiZ - 2mA | Receive Tributary Clock Port # 16                                                                                                               |

| 124  | DTC17 | O<br>HiZ - 2mA | Receive Tributary Clock Port # 17                                                                                                               |

| 134  | DTC18 | O<br>HiZ - 2mA | Receive Tributary Clock Port # 18                                                                                                               |

| 135  | DTC19 | O<br>HiZ - 2mA | Receive Tributary Clock Port # 19                                                                                                               |

| 143  | DTC20 | O<br>HiZ - 2mA | Receive Tributary Clock Port # 20                                                                                                               |

| 144  | DTC21 | O<br>HiZ - 2mA | Receive Tributary Clock Port # 21                                                                                                               |

|      | •     | Те             | elecom Bus Interface                                                                                                                            |

Table 2. Pin Descriptions (Continued) (Sheet 5 of 7)

| Pin#      | Name          | Туре               | Function                                                                                                                                                                                                                                                                                                                                                         |

|-----------|---------------|--------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 204-197   | MTBDATA <7:0> | O<br>HiZ - 4mA     | Multiplex Telecom Bus Data 7 to 0. This is a byte wide data output at 19.44 Mbit/s for STM-1 or 6.48 Mbit/s for STM-0. The output in STM-1 may be tri-stated for certain bytes depending on the configuration of the device.                                                                                                                                     |

| 196       | MTBPAR        | O<br>HiZ - 4mA     | Multiplex Telecom Bus Parity. This is the parity check signal calculated on the MTBDATA byte only. It is an odd parity and is always a calculated value (i.e. the value is not passed through in ADM).                                                                                                                                                           |

| 193       | МТВҮСК        | I<br>TTLin         | Multiplexer Telecom Bus Clock. This clock drives the multiplexer section at 6.48 MHz for STM-0 or 19.44MHz for STM-1.                                                                                                                                                                                                                                            |

| 191       | MTBJ0J1EN     | I/O<br>TTLin - 4mA | Multiplex Telecom Bus Frame indicator. This indicates the presence of the J0 and J1 bytes on the MTBDATA bus. Optionally configurable to also indicate H4 multiframe position, instead of using MTBH4EN.                                                                                                                                                         |

| 188       | MTBH4EN       | I/O<br>TTLin - 4mA | Multiplex Telecom Bus H4 multiframe Indicator. An output in ADM mode, this is a 2 KHz signal that indicates the location of the 00 value of H4. As input in terminal mode, the signal is sampled during the J1 byte position given by MTBJ0J1EN.                                                                                                                 |

| 189       | MTBPAYEN      | I/O<br>TTLin - 4mA | Multiplex Telecom Bus Payload Enable. Indicates the position of VC-4 in the STM-1 mode or VC-3 in the STM-0 mode. In an ADM configuration the pin is an output while in the terminal mode it is an input.                                                                                                                                                        |

| 190       | MTBTUGEN      | I<br>TTLin         | Multiplexer Telecom Bus TUG Enable. This pin is used in STM-1 terminal applications and controls the TUG-3 in which the LXT6251A will generate data. This pin should be tied to Vcc for STM-0 terminal applications.                                                                                                                                             |

| 205       | MTBDOE        | O<br>HiZ - 4mA     | <b>Multiplexer Telecom Bus Output Enable.</b> Active Low output enable signal that mirrors the internal MTBDATA data bus control. Its function is to enable an <i>external</i> tri-state bus driver that should be used when the device is installed in a multi-card/backplane environment. Usually reserved for STM-1 use, the signal is always active in STM-0 |

| 161 - 168 | DTBDATA <7:0> | I<br>TTLin         | <b>Demultiplexer Telecom Bus Data 7.</b> This is a byte wide data input at 19.44 Mbit/s for STM-1 or 6.48 Mbit/s for STM-0. In STM-1 mode, the data is ignored if DTBTUGEN is Low.                                                                                                                                                                               |

| 169       | DTBPAR        | I<br>TTLin         | <b>Telecom Bus Parity.</b> This is parity check calculated on the DTBDATA byte only. It is an odd parity.                                                                                                                                                                                                                                                        |

| 172       | DTBYCK        | I<br>TTLin         | <b>Demultiplexer Telecom Bus Clock.</b> This clock drives the demultiplexer section at 6.48 MHz for STM-0 or 19.44MHz for STM-1                                                                                                                                                                                                                                  |

| 174       | DTBJ0J1EN     | l<br>TTLin         | Demultiplexer Telecom Bus Frame Indicator. This indicates the position of J0 and J1 bytes on the DTBDATA bus. Optionally configurable to also detect H4 multiframe position, instead of using DTBH4EN.                                                                                                                                                           |

| 180       | DTBH4EN       | I<br>TTLin         | <b>Demultiplexer Telecom Bus H4 multiframe Indicator.</b> This is a 2 KHz signal that indicates the location of the 00 value of H4. This signal is sampled during the J1 pulse from DTBJ0J1EN.                                                                                                                                                                   |

| 179       | DTBPAYEN      | I<br>TTL-in        | <b>Demultiplexer Telecom Bus Payload Enable.</b> Indicates the position of VC-4 in the STM-1 mode or VC-3 in the STM-0 mode. This pin is always an input.                                                                                                                                                                                                        |

| 175       | DTBTUGEN      | I<br>TTLin         | <b>Demultiplexer Telecom Bus TUG Enable.</b> This pin is used in STM-1 applications and indicates the proper TUG-3 payload the demultiplexer section should process. This pin is tied to VCC for STM-0 applications.                                                                                                                                             |

Table 2. Pin Descriptions (Continued) (Sheet 6 of 7)

| Pin#  | Name      | Туре             | Function                                                                                                                                                                                                                                                                                                                                          |

|-------|-----------|------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 176   | PTTUGA    | I<br>TTLin       | Pass-Trough TUG Enable-A. A High on this pin indicates the TUG data received coincident with the pulse is to be passed through to the MTBDATA output. Refer to "Add/Drop Configuration" on page 30 for use of this pin. This pin should be tied Low in STM-0 configuration or if unused.                                                          |

| 177   | PTTUGB    | I<br>TTLin       | Pass-Trough TUG Enable-B. A High on this pin indicates the TUG data received coincident with the pulse is to be passed through to the MTBDATA output. Refer to "Add/Drop Configuration" on page 30 for use of this pin. This pin should be tied Low in STM-0 configuration or if unused.                                                          |

| 178   | PTSOH     | I<br>TTLin       | Pass-Trough SOH Enable. A High on this pin indicates the SOH data, HPOH data, and VC-4 fixed stuff (STM-1) received on the telecom bus is to be passed through to the MTBDATA output. Refer to "Add/Drop Configuration" on page 30 for use of this pin. This pin should be tied to ground in STM-0 or STM-1 terminal configurations or if unused. |

|       | •         | Serial           | Alarm Indication Ports                                                                                                                                                                                                                                                                                                                            |

| 40    | DSAPDATA  | O<br>HiZ - 2mA   | Serial Alarm Data. Output which provides a rapid indication of the V5 byte parity error, TU-AIS, TU-Loss of pointer, Unequipped detect, Trace ID mismatch, Signal Label mismatch and VC-AIS alarm status for all 21 VC-12 channels. Refer to "Serial/Remote Alarm Processing Port" on page 40 for details.                                        |

| 39    | DSAPCLK   | O<br>HiZ - 2mA   | Serial Alarm Clock. Clock frequency is nominally 1.62MHz.                                                                                                                                                                                                                                                                                         |

| 38    | DSAPFRM   | O<br>HiZ - 2mA   | <b>Serial Alarm Frame.</b> Frame indicator active during the first bit of the DSAPDATA data frame.                                                                                                                                                                                                                                                |

| 35    | MRAPDATA  | I<br>TTLin       | Serial Alarm Data. Input that contains indication of alarm status resulting from the V5 byte parity error, TU-AIS, TU-Loss of pointer, Unequipped detect, Trace ID mismatch, and Signal Label mismatch, and VC-AIS for all 21 VC-12 channels. Refer to "Serial/Remote Alarm Processing Port" on page 40 for details.                              |

| 36    | MRAPCLK   | I<br>TTLin       | Serial Alarm Clock input. The clock frequency is nominally 1.62MHz                                                                                                                                                                                                                                                                                |

| 37    | MRAPFRM   | I<br>TTLin       | <b>Serial Alarm Frame.</b> Frame indicator that must be active during the first bit of the data frame on MRAPDATA.                                                                                                                                                                                                                                |

|       |           | M                | licroprocessor Bus                                                                                                                                                                                                                                                                                                                                |

| 14-22 | A<8:0>    | I<br>TTLin       | Address Bus. A nine bit address port for microprocessor access.                                                                                                                                                                                                                                                                                   |

| 4-11  | DATA<7:0> | I/O<br>TTLin-6mA | <b>Data Bus.</b> Eight bit I/O data port for the microprocessor to read and write data, commands, and status information to and from the device.                                                                                                                                                                                                  |

| 28    | WR/RW     | I<br>TTLin       | Write signal (Intel); Read/Write signal (Motorola)                                                                                                                                                                                                                                                                                                |

| 29    | RD/E      | TTLin            | Read signal (Intel); Enable signal (Motorola)                                                                                                                                                                                                                                                                                                     |

| 26    | CS        | I                | Chip Select. Active Low signal to enable microprocessor RD or WR action.                                                                                                                                                                                                                                                                          |

| 31    | MCUTYPE   | I<br>TTLin       | Motorola/Intel Interface Mode Select. Low = Intel,<br>High = Motorola                                                                                                                                                                                                                                                                             |

| 30    | INT       | O<br>HiZ - 4mA   | Interrupt. Active Low interrupt indication.                                                                                                                                                                                                                                                                                                       |

Table 2. Pin Descriptions (Continued) (Sheet 7 of 7)

| Pin # | Name                              | Туре              | Function                                                                                                                                                                                                                                                                            |  |  |

|-------|-----------------------------------|-------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| 27    | AS                                | TTLin             | Address Latch Enable. Used by chip for systems where address and data busses are multiplexed. Latches A<8:0> on the falling edge. If address and data are not multiplexed, this pin should be tied High.                                                                            |  |  |

|       | JTAG Boundary Scan Test Functions |                   |                                                                                                                                                                                                                                                                                     |  |  |

| 148   | SCANTEST                          | TTLin-48PU        | Active Low Scan Test mode select with ~48 KOhm Pull-up resistor. Should be left unconnected for normal operation.                                                                                                                                                                   |  |  |

| 160   | SCANEN                            | ITTLin-48PU       | Active Low Scan Enable with ~48 KOhm Pull-up resistor. Controls all Scan FF muxes. Should be left unconnected for normal operation.                                                                                                                                                 |  |  |

| 153   | JTCK                              | I<br>TTLin-48PU   | <b>JTAG Clock.</b> This signal has a ~48 K $\Omega$ Pull-up resistor. Clock for the boundary scan circuitry. See "IEEE 1149.1 Boundary Scan Description" on page 66 for details.                                                                                                    |  |  |

| 152   | JTMS                              | I<br>TTLin-48PU   | Test Mode Select. This signal has a ~48K $\Omega$ Pull-up resistor. This pin determine state of TAP controller.                                                                                                                                                                     |  |  |

| 151   | JTRS                              | I<br>TTLin-35PD   | Active low Reset. This signal has a $\sim 35 \mathrm{K}\Omega$ Pull-down resistor. Should be left unconnected for normal device usage.                                                                                                                                              |  |  |

| 150   | JTDI                              | ITTLin-48PU       | <b>Data Input.</b> This signal has a $\sim$ 48K $\Omega$ Pull-up resistor. Input signal used to shift in instructions and data. Should be left unconnected for normal device usage.                                                                                                 |  |  |

| 149   | JTDO                              | O<br>HiZ-2mA      | Data Output. Output signal used to shift out instruction and data.                                                                                                                                                                                                                  |  |  |

|       |                                   | Co                | entrol Functions                                                                                                                                                                                                                                                                    |  |  |

| 154   | OEN                               | I<br>TTLin-48PU   | Output Enable. This signal has a ~48KOhm Pull-up resistor. Used to disable all output pins for bed of nails type testing or other applications. When Low, all outputs are in high impedance and all bidirectional pins are inputs. Should be left unconnected for normal operation. |  |  |

| 33    | RST                               | I<br>TTLin-108PUS | Chip Master Reset. This signal has a ~108KOhm Pull-up resistor. A low will reset all registers to default conditions. Input logic is a schmidt trigger type.                                                                                                                        |  |  |

| 32    | STMMODE                           | I<br>TTLin        | STM Mode Select. Low = STM-0, High = STM-1                                                                                                                                                                                                                                          |  |  |

**Table 3. Power, Ground, and No Connects**

| Pin#                                                              | Name  | Туре | Power Supply                                |  |

|-------------------------------------------------------------------|-------|------|---------------------------------------------|--|

| 12, 34, 66, 91, 118, 139, 170, 195                                | VCC_5 |      | 5V Supply for I/O ring                      |  |

| 1, 13, 23, 52, 53, 77, 80, 104, 105, 128, 156, 157, 181, 187, 208 | GND_5 |      | GND 5 Volts. Ground pins for 5 Volt supply. |  |

| 24, 50, 78, 102, 103, 131, 155, 183, 184, 206, 207                | VCC_3 |      | 3 V supply for core                         |  |

| 3, 25, 54, 55, 79, 106, 132, 158, 159, 185, 186                   | GND_3 |      | GND 3 Volts. Ground pins for 3 Volt supply. |  |

| 2, 41, 51, 171, 173, 182, 192, 194                                | NC    |      | Not Connected. Unused                       |  |

## 3.0 Functional Description

### 3.1 Introduction

The LXT6251A performs mapping and demapping of 21 channels of E1 PDH tributaries into and out of the SDH hierarchy. It supports two system configurations, terminal or Add/Drop multiplexing, and two operating frequencies, STM-0 or STM-1. In the terminal configuration, the transmit section maps 21 tributaries of E1 data into 21 VC-12 virtual containers, formatted as a C-3 in STM-0 or as a TUG-3 in STM-1. The terminal receiver processes either a C3 or a TUG-3 payload and outputs 21 E1 tributaries after processing the VC-12 path overhead. In the Add/Drop configuration, the receiver processes any number of TU-12 containers up to its capacity of 21, and passes the non-dropped portion of the payload to the transmitter where the added E1/TU-12 tributaries are multiplexed and output.

The discussion will focus first on the terminal functions, which describe the E1 to SDH process used in the terminal mode as well as those E1 channels in the add/drop mode. Following the terminal functions, the configuration details of the add/drop mode are presented. Further details about the configuration of the LXT6251A with the LXT6051 in different system configurations can be found in a companion document, Application Note LXT6051/LXT6251A SDH Chipset."

### 3.2 Receive Section, Terminal Mode

At the Telecom Bus input point (DTBDATA), the Mapper expects to receive byte wide data that has been processed by the LXT6051 OHT or an other overhead terminator up to the higher order path terminator (HPT) point. The Mapper thus receives data that minimally contains C-3 or C-4 payload data along with the Telecom Bus timing signals DTBJ0J1EN, DTBPAYEN, DTBH4EN, and DTBTUGEN (STM-1 only) which synchronize the internal timing generator to the data. The timing generator in turn drives 21 identical demapper blocks to process the appropriate TU-12 signals.

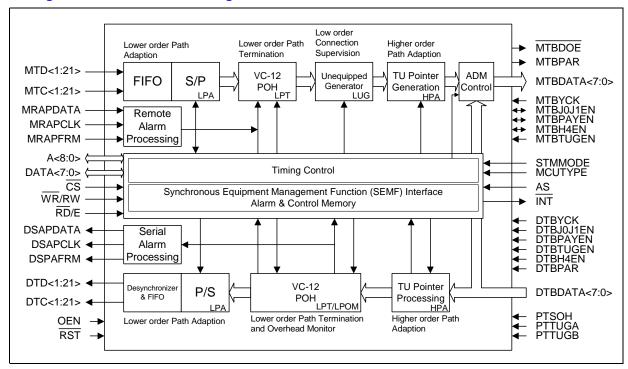

Refer to "Telecom Bus Interface" on page 35 for a detailed discussion of the Telecom bus signals. Refer to the block diagram below for the following discussion of a single TU-12 demultiplexer block. The remaining 20 blocks operate in an identical manner but with different timing signals.

Figure 3. LXT6251A Block Diagram

#### 3.2.1 Receive Alarms

There are two alarms associated with the Telecom bus interface.

#### 3.2.1.1 Parity Alarm

The receive telecom bus data integrity is monitored with a single odd parity bit. The parity is calculated over the DTBDATA bus only. The mapper checks the parity for errors every 500mS multiframe and indicates an alarm in "GLOB\_INTS—Global Interrupt Source (00CH)" on page 60 if there are more than 16 errors within the 500mS time window. The interrupt is maskable in "INT\_CONF—Interrupt Configuration Register (00BH)" on page 59.

#### 3.2.1.2 Loss of Multiframe

A loss of multiframe alarm is detected if the DTBH4EN signal is always low. The alarm status and interrupt is indicated in "GLOB\_INTS—Global Interrupt Source (00CH)" on page 60.

Consequent Actions:

• An LOM alarm will cause the SF alarm bit on the SAP bus to be high for all 21 tributaries. The SF alarm is used to indicate errors that should cause a VC path protection event. The SAP bus is described in detail in "Serial/Remote Alarm Processing Port" on page 40.

### 3.3 High Order Path Adaptation

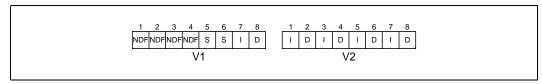

Within each of the 21 TU-12 demapper blocks, the telecom bus data bytes first enter the higher order path adaptation (HPA) block for TU-12 pointer interpretation. The TU-12 pointer is contained in the V1 and V2 bytes shown below. The 8 bits of V2 and the 2 LSB bits of V1, shown as I and D bits, represent a binary number that represents the number of TU-12 bytes between the V5 POH byte and V2. The SS bits identify Tributary type, and the remaining 4 bits represent a New Data Flag (NDF). Based on the incoming J0J1, Payload, and H4 timing signals, the V1 and V2 bytes are located and interpreted. The pointer interpreter state machine follows the state diagram provided in the Appendix of ITU-T G.783. The variable N in that specification, which specifies the number of invalid pointers required to enter the Loss of Pointer state, is set to eight (8) in the LXT6251A. When a valid pointer is found (a valid pointer defined as being between the values 0 and 139), the pointer processing block will synchronize the TU timing block and remove the Loss of Pointer (LOP) alarm.

Figure 4. V1/V2 Pointer Diagram

After achieving a normal pointer state, the processor will continually monitor V1 and V2 for the following events:

- Positive Justification from the inversion of the I bits (3 of 5 majority decision)

- Negative Justification from the inversion of the D bits (3 of 5 majority decision)

- New pointer value from 3 new valid values in a row

- New pointer value from single NDF indication (if in Normal or AIS state only)

- All 1's condition on the V1/V2 bytes

- Invalid pointer values occurring 8 times in a row to trigger a LOP alarm

- Reception of NDF indication 8 times in a row to trigger a LOP alarm

#### 3.3.1 Alarms and Status

#### 3.3.1.1 TU-AIS

If 3 consecutive TU pointers in the all 1's (AIS) state are detected, the TU-AIS status bit in "TRIB\_STA—Tributary Status (x3–x2H)" on page 63 is set. It is cleared when either the LOP or Normal states are entered. Whenever the TU-AIS status changes the TU-AIS interrupt bit in "TRIB\_INT—Tributary Interrupt (x1–x0H)" on page 61 is set.

Consequent Actions:

- An RDI Indication will be sent to the transmitter via the SAP interface. The RDI indication will be set on the transmitted V5 byte unless the XmtLptRdiEn bit in "ERRI\_CONF—Error Insert Configuration (xDH)" on page 58 is set to 0

- Outgoing E1 data on DTDx will be forced to AIS with derived 2.048MHz clock on DTCx

#### 3.3.1.2 TU Loss of Pointer (LOP)

If an invalid pointer state is detected in the TU pointer, the TU-LOP status bit in "TRIB\_STA—Tributary Status (x3-x2H)" on page 63 is set. An invalid pointer state is entered from either the normal or AIS pointer state after 8 consecutive invalid pointer values or 8 consecutive NDF pointers are detected. It is exited when either the LOP or Normal states are entered at which time the TU-LOP status bit in "TRIB\_STA—Tributary Status (x3-x2H)" on page 63 is cleared. Whenever the TU-LOP status changes the TU-LOP interrupt bit in "TRIB\_INT—Tributary Interrupt (x1-x0H)" on page 61 is set.

#### Consequent Actions:

- An RDI alarm will be sent to the transmitter via the SAP interface. The RDI alarm will be set in the transmitted V5 byte unless the XmtLptRdiEn bit in "ERRI\_CONF—Error Insert Configuration (xDH)" on page 58 is set to 0

- Outgoing E1 data on DTDx will be forced to AIS with derived 2.048 MHz clock on DTCx.

### 3.4 Low Order Path Termination

After the TU Timing control has been updated by the pointer interpreter, the received data is processed by the lower order path termination (LPT) block which terminates the POH bytes of each VC-12, and records all information extractable from the POH for processing by the microprocessor. For the V5 byte this includes counting BIP-2 and REI errors and monitoring the RDI, RFI and signal label bits. For the J2 Path Trace byte this includes monitoring the Path trace identification and CRC-7 alarms, and for the K4 byte this includes monitoring enhanced RDI information. All alarm indications and counts are available via the microprocessor interface, with the RDI, REI, VC-AIS, and BIP errors additionally fed to the Serial alarm port (SAP) for real-time tributary alarm indication and remote alarm processing.

Figure 5. V5 Byte

### 3.4.1 V5 Processing

### 3.4.1.1 BIP-2 Errors (V5, bits 1,2)

The LPT block continually calculates the BIP-2 value by generating a two-bit parity, starting with V5. After receiving the 140 bytes in a multiframe, the calculated value is compared with the first two bits of the next V5 and if a mismatch between the calculated and received BIP-2 is detected a BIP-2 error interrupt is generated in "TRIB\_INT—Tributary Interrupt (x1-x0H)" on page 61. BIP-2 mismatches are also counted with results available in "BIP2\_ERRCNT—BIP2 Error Counter (x7-x6H)" on page 63. The BIP2 counters can be configured from "GLOB\_CONF—Global Configuration (000H)" on page 55 to count either two possible counts per multiframe (bit count) or one possible count per multiframe (block count). The counter will count to a maximum of 4095, which exceeds the maximum number of bit alarms in one second and the maximum number of block errors in two seconds. If the counter overflows, an Overflow interrupt is generated in "TRIB\_INT—Tributary Interrupt (x1-x0H)" on page 61 and the count recycles to zero.

To read the BIP counter registers, the microprocessor must first perform a write (any value) to either (x6H,x7H), then wait at least three cycles of DTBYCK (0.5uS in STM-0) before reading the two registers. The write action latches the counter value into the two registers, and clears the counter to zero.

#### Consequent Actions:

• REI indication will be sent to the transmitter via the SAP interface. The REI indication will be set on the transmitted V5 byte unless the XmtLptReiEn bit in "ERRI\_CONF—Error Insert Configuration (xDH)" on page 58 is set to 0.

#### 3.4.1.2 **REI Detection (V5, bit 3)**

The LPT block continually monitors the value of the REI bit and sets the REI interrupt bit in "TRIB\_INT—Tributary Interrupt (x1-x0H)" on page 61 whenever it is found to be '1' (an event).

These events are also counted with results available in "REI\_CNT—Remote Error Indication (REI) Counter (x9–x8H)" on page 64. The counter will count to a maximum of 2047, which is more than the maximum number of REI alarms within one second. If the counter overflows, an Overflow interrupt is generated in "TRIB\_INT—Tributary Interrupt (x1–x0H)" on page 61 and the count recycles to zero.

To read the REI counter registers, the microprocessor must first perform a write (any value) to either register (x8H, x9H), then wait at least three cycles of DTBYCK (0.5uS in STM-0) before reading the two registers. The write action latches the counter values into the two registers, and clears the counter to zero.

Consequent Actions: none

#### 3.4.1.3 **RFI Detection (V5, bit 4)**

The LPT block continually monitors the value of the RFI bit and updates the RFI status bit in "TRIB\_STA—Tributary Status (x3–x2H)" on page 63 with its detected value (there is no filtering or hysteresis on this bit). Whenever the RFI status bit changes the RFI interrupt bit in "TRIB\_INT—Tributary Interrupt (x1–x0H)" on page 61 is set.

Consequent Actions: none

#### 3.4.1.4 Signal Label Mismatch (V5, bits 5-7)

A signal label mismatch (SLM) status bit will be set in "TRIB\_STA—Tributary Status (x3–x2H)" on page 63 if the signal label does not match a valid pattern that can be processed by this chip for five multiframes. Valid label values are 000 (Unequipped), 001 (Equipped, non-specific), and 010 (Equipped, asynchronous). It is cleared when the signal label equals a valid pattern for five multiframes.

Whenever the SLM status bit changes the SLM interrupt bit in "TRIB\_INT—Tributary Interrupt (x1-x0H)" on page 61 is set.

#### Consequent Actions:

• Outgoing E1 data on DTDx will be forced to AIS with derived 2.048MHz clock on DTCx

#### 3.4.1.5 Unequipped Detection (V5, bits 5-7)

The Unequipped (UNEQP) status bit will be set in "TRIB\_STA—Tributary Status (x3–x2H)" on page 63 if a '000' is detected in the signal label for five consecutive multiframes. It is cleared when the signal label equals a pattern other than '000' for five consecutive multiframes.

Whenever the UNEQP status bit changes the UNEQP interrupt bit in "TRIB\_INT—Tributary Interrupt (x1-x0H)" on page 61 is set.

#### Consequent Actions:

- If the global Unequipped configuration is <u>not</u> set to Supervisory, an RDI Indication will be sent to the transmitter via the SAP interface. The RDI indication will be set on the transmitted V5 byte unless the XmtLptRdiEn bit in "ERRI\_CONF—Error Insert Configuration (xDH)" on page 58 is set to 0. No indication is sent in Supervisory mode.

- Outgoing E1 data on DTDx will be forced to AIS with derived 2.048MHz clock on DTCx

#### 3.4.1.6 VC-AIS Detection (V5, bits 5-7)

If the signal label is detected as '111' in any one multiframe, a VC-AIS alarm will be indicated on the SAP bus. There is no internal alarm or interrupt associated with this alarm, and no hysteresis filtering. If the SAP bus is used to control protection switching at the TU-12 level, it is recommended that hysteresis filtering be added to this alarm in the external circuit.

VC-AIS is treated like a signal label mismatch. Thus, consequent actions follow SLM actions.

Consequent Actions:

• A VC-AIS/SF Indication will be output on the SAP interface.

#### **3.4.1.7** RDI Detection (V5, bit 8)

The LPT block continually monitors the value of the RDI bit and updates the RDI status bit in "TRIB\_STA—Tributary Status (x3–x2H)" on page 63 with its detected value (after five consecutive frames). Whenever the RDI status bit changes the RDI interrupt bit in "TRIB\_INT—Tributary Interrupt (x1–x0H)" on page 61 is set.

Consequent Actions: none

### 3.4.2 J2 Processing

J2 Trace Identifier processing is supported on a per tributary basis for both transmit and receive paths. Within the receive section of each tributary, the RxJ2Access bit in "TRIB\_INTE—Tributary Interrupt Enable (x5-x4H)" on page 62 controls the support for J2 processing. When RxJ2Access is a '1', both the J2 Path Label Mismatch and the CRC-7 error detection alarms are completely masked. In this state the microprocessor is also able to access the J2 RAM cell of the tributary. This is the default state after a power-up condition. When RxJ2Access is '0', the two alarms are enabled, and the microprocessor cannot access the J2 RAM.

#### 3.4.2.1 J2 Memory Access

The J2 RAM for each tributary is indirectly accessible by the microprocessor. That is, there is a single data port to access the data, while the address is internally generated and automatically incremented as the J2 RAM byte is read or written. The following procedure should be followed to correctly program the J2 RAM.

- Ensure that RxJ2Access is set to '1' in "TRIB\_INTE—Tributary Interrupt Enable (x5-x4H)" on page 62.

- Write (any value) to J2\_MRST-- J2 Memory reset\_(008H) page 50. This resets the global counter used to generate the RAM address. This step is only required once if multiple tributaries are being programmed.

- Write the 16 bytes of the J2 word consecutively to "J2\_ESDATA—J2 Expected String Data (xCH)" on page 58. Each toggle of the write (or read) will increment the internal counter in DMA fashion.

If write verification is desired, the microprocessor can now read 16 bytes in DMA fashion. The internal address counter resets to 0 after the 16 writes.

Once the RAM is filled and verified, the RxJ2Access bit can be set to '0' to enable the alarms.

Note that all 16 bytes should be written to the RAM by the microprocessor. The CRC-7 byte is not needed in the receiver RAM (the received CRC-7 byte is compared with a calculated value only), however the microprocessor must write some value on the first write to align the remaining 15 words in the RAM.

During normal operation with J2 support, the RxJ2Access bit should be set to '0', allowing the alarms associated with J2 to be generated. As data is received, each J2 byte is analyzed until the CRC-7 byte is found, which is distinguished from the other 15 bytes by having a 1 in the most significant bit. The CRC-7 byte is stored, then the following 15 bytes are used to calculate a CRC-7 value and compared with successive locations in the RAM. The CRC-7 byte is never compared with the contents of the J2 RAM.

Two alarms can be generated: the Trace Identifier Mismatch (TIM) and the CRC-7 mismatch (CRC7).

#### 3.4.2.2 CRC-7 Error

The chip calculates the CRC-7 value over the 15 bytes of the received J2 string. This value will be compared with the received CRC-7 byte. If the calculated and received CRC-7 bytes do not match, the J2 CRC-7 error (CRC7Err) status bit is set in "TRIB\_STA—Tributary Status (x3–x2H)" on page 63. If the calculated and received CRC-7 bytes do match, the CRC7Err status bit is cleared.

Whenever the CRC7Err status bit changes the CRC7Err interrupt bit in "TRIB\_INT—Tributary Interrupt (x1-x0H)" on page 61 is set.

Consequent Actions: none

#### 3.4.2.3 Trace Identifier Mismatch

The chip compares the received J2 string with the one stored in memory. If the calculated CRC-7 matches that of the received value, but there are errors in the comparison of the remaining 15 bytes, the TIM status bit is set in "TRIB\_STA—Tributary Status (x3-x2H)" on page 63. There is no filtering of this alarm, since the CRC-7 match will indicate the J2 word has been received without error. The TIM status bit is cleared when the J2 string is received without errors.

Whenever the TIM status bit changes the TIM interrupt bit in "TRIB\_INT—Tributary Interrupt (x1-x0H)" on page 61 is set.

#### **Consequent Actions:**

- An RDI Indication will be sent to the transmitter via the SAP interface

- Outgoing E1 data toward the PDH network will be forced to AIS with derived 2.048MHz clock

### 3.4.3 N2 Processing

N2 processing is not implemented at this time.

### 3.4.4 K4 Processing

The K4 byte contains a protection function and an Enhanced RDI (ERDI) function. The LXT6251A supports the ERDI function. No alarms or interrupts will be generated based only on the K4 ERDI information The V5 RDI bit generates the alarms.

#### 3.4.4.1 Enhanced RDI

Upon detection of a V5 RDI alarm, "K4\_STA—K4 Status (xAH)" on page 64 can be accessed to determine the nature of the RDI alarm, assuming the trail termination source supports the K4 ERDI processing. The following defects are supported in the ERDI

Table 4. Enhanced RDI Interpretation

| K4, bit 5 | K4, bit 6 | K4, bit 7 | Alarm                  |

|-----------|-----------|-----------|------------------------|

| 0         | Х         | Х         | No Alarm               |

| 1         | 0         | 0         | Non-specific RDI alarm |

| 1         | 1         | 1         | Non-specific RDI alarm |

| 1         | 0         | 1         | TU-AIS, TU-LOP         |

| 1         | 1         | 0         | TIM, UNEQ              |

**NOTE:** The bit numbers above reference a byte whose least significant bit is bit 8.

### 3.4.5 Summary of Alarms causing E1 AIS

A number of alarms cause the LXT6251A to generate an all 1's AIS signal at the E1 output port. The following list summarizes those alarm and the conditions.

#### **3.4.5.1 TU-AIS Alarm**

V1/V2 = FFh for 8 consecutive multiframes

#### **3.4.5.2 TU-LOP Alarm**

V1/V2 invalid for 8 consecutive multiframes

#### 3.4.5.3 Signal Label Mismatch

Signal Label invalid for 5 consecutive multiframes. A VC-AIS is also considered as an SLM.

#### 3.4.5.4 Unequipped Alarm

Signal Label set to '000' for 5 consecutive multiframes (either supervisory or non-supervisory mode)

#### 3.4.5.5 J2 Path Label Mismatch

16 byte J2 string has correct CRC-7 but does not match expected value.

The AIS consequent action from these alarms cannot be disabled with the exception of the J2 mismatch, which can be disabled via the use of the RxJ2Access bit. A Loss of multiframe should also cause an E1 AIS condition, however there is no direct action taken by the device to generate the AIS, the incoming Telecom bus data should already be in AIS.

### 3.5 Low Order Path Adaptation

After processing by the Path Overhead Terminator, the data is passed to the lower order path adaptation (LPA) block. First, the three C1C2 bits are processed and a majority decision made as to the value of the two stuffing indicator bits. A majority of 1's for Cx indicates the associated Sx bit is data, while majority Ø's indicates the Sx bit is stuff and should be ignored. This is then used along with other timing inputs to extract the E1 payload data.

The data at this point is still parallel and therefore needs to be converted to serial and a relatively smooth 2.048MHz clock generated. The degapper circuit performs these functions.

### 3.5.1 Desynchronizer

The LXT6251A implements a bit leaking function to reduce the multiplexing jitter that is created during both the E1 to VC-12 stuffing process and SDH pointer movements at both the AU and TU level. The input to the degapper is the byte parallel clock, byte data, TU timing information, and indications of pointer movement from the TU level. The degapper block first interprets the stuffing indicators and extracts the proper data, then attempts to smooth the clock, anticipating gaps created by the frame, TU pointer movements, and stuffing. The output of the degapper directly feeds to output pins (DTCx/DTDx) and consists of a relatively smooth E1 clock (and NRZ data) in which the large gaps from pointer movements have been distributed over a period of time. In order for the E1 output to conform to G.783 residual jitter requirements, an external jitter attenuation circuit is required, such as that available in Intel's octal digital interface, the LXT6282 or Intel's LXT318 Line Interface with Jitter Attenuator.

### 21 E1 SDH Mapper — LXT6251A

The external jitter attenuator must meet the following specifications or the final output jitter cannot be guaranteed to meet ITU G.783:

- Loop Bandwidth of 3 Hz or lower

- An elastic buffer of at least 32 bits

- First or second order loop. Second order is recommended for best performance

### 4.0 Transmit Section, Terminal Mode

At the MTDx/MTCx input pins, the Mapper expects to receive asynchronous E1 signals in the form of NRZ data and clock. The mapper also requires the Telecom Bus timing signals MTBJ0J1EN, MTBPAYEN, MTBH4EN, and MTBTUGEN (STM-1 only) to drive the internal timing machine. Refer to "Telecom Bus Interface" on page 35 for details on these timing signals.

The E1 signal must be valid and within frequency tolerance. Should there be a Loss of Signal alarm on an E1 input to the line interface circuits prior to the LXT6251A, it is the responsibility of the LIU or other external element to generate a valid E1 clock and AIS signal. The LXT6251A does not support a method to generate a mapped E1 AIS signal.

### 4.1 Low Order Path Adaptation

The E1 data and clock pairs immediately enter the first-in first-out memory within the lower order path adaptation (LPA) block. The LPA block receives timing information from the master timing control block to identify the frame positions of the Information (I) bytes, the stuffing indicators C1C2, and the stuffing bits S1 and S2. This timing, along with the depth of the FIFO is used to determine the stuffing decisions for each multiframe. The data out of the FIFO is converted to parallel bytes at each I byte position, and the appropriate stuffing indicators and stuffing bits added during the appropriate time slots. The output of the LPA block thus consists of a C12 container, which includes I bytes, R bytes, and stuffing indicator bytes also containing four O bits. The LXT6251A sets both the R bytes and the O bits to '0'.

### 4.2 Low Order Path Termination

Next the LPT function adds the path overhead bytes V5, J2, N2, and K4. The following descriptions detail the POH bytes and the supported bits within each byte.

### 4.2.1 V5 Processing

#### 4.2.1.1 BIP-2

As the LPT block is generating the VC-12, a 2 bit Bit Interleave Parity (BIP-2) value is being calculated on all the bytes. At the end of the multiframe, the BIP-2 value is inserted into the following V5 byte (see Figure 4).

To aid the system designer in the testing phase, the LXT6251A includes a BIP error generator that is enabled by setting the BipInv bit in "ERRI\_CONF—Error Insert Configuration (xDH)" on page 58. The default value is '0', and the BIP value is not affected. When set to '1', the calculated BIP value will be inverted on every V5 byte, simulating a degraded VC-12 for a receiver.

#### 4.2.1.2 REI Bit

The Remote Error Indication bit is updated every multiframe by monitoring the receive side status data on the Remote Alarm Port (RAP). The RAP port is further described in "Serial/Remote Alarm Processing Port" on page 40. If the corresponding receive side TU-12 tributary detects BIP-2 errors, the RAP port will indicate to the transmit LPT block that the REI bit should be set to '1'.

Two bits in "ERRI\_CONF—Error Insert Configuration (xDH)" on page 58 can modify the setting of the REI bit. First, the XmtLptReiEn bit can be set to '0' to disable the automatic response to the RAP data. By default this bit is set to '1'. Second, the XmtLptRdiFrc can be set to '1' to force the REI bit to be set to '1' as long as this register bit is set. By default this bit is set to '0'.

#### 4.2.1.3 RFI Bit

The Remote Failure Indication bit as of yet has no standard definition that would allow automatic generation with the LXT6251A. Therefore, the RFI bit can only be set by the microprocessor via the RFISet bit in "SIGLA\_SET—Signal Label Setting (xEH)" on page 57.

#### 4.2.1.4 Signal Label