# Am6112

# Microprocessor-Compatible 12-Bit A/D Converter

## **DISTINCTIVE CHARACTERISTICS**

- First totally monolithic, high-speed 12-bit ADC

- 6 µs typical conversion time

- Internal precision voltage reference

- No missing codes

- Easy interfacing with 8- and 16-bit microprocessors

- Internal command register for programmable modes of operation

- Offset binary or two's complement output code

- 0 to 10 V, or ±5 V input range

- 24-pin package

- Segmented DAC architecture for monotonic operation

- Available in two accuracy ranges

# **GENERAL DESCRIPTION**

The Am6112 is a fully monolithic microprocessor-compatible 12-bit high-speed analog-to-digital converter. The Am6112 high-speed ADC contains a precision reference, DAC, comparator, SAR, scale resistors, output three-state buffers and comprehensive control logic, enabling the device to be interfaced with a variety of microprocessors. The Am6112 is capable of completing a 12-bit conversion in typically 6 µs and can handle input voltage ranges of 0 to +10 V, and  $\pm 5$  V without external components.

The Am6112 has four modes of microprocessor operation, and a stand-alone mode. These modes are software programmable, except for the stand-alone mode. Applications include analog I/O subsystems, servocontrol, and high-speed digital signal processing of analog events.

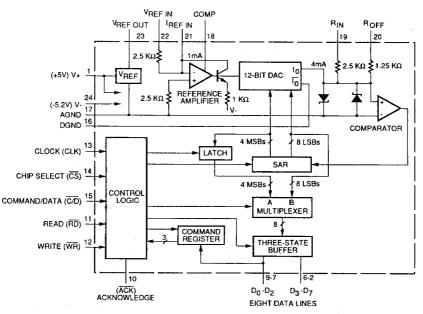

# **BLOCK DIAGRAM**

01910-001A

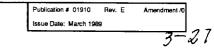

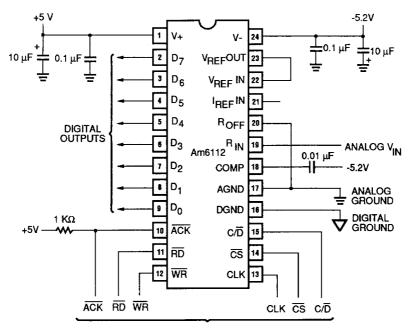

#### **CONNECTION DIAGRAM Top View**

Note: Pin 1 is marked for orientation.

01910-002A

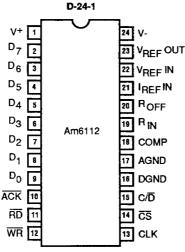

### **ORDERING INFORMATION**

#### **Standard Products**

AMD standard products are available in several packages and operating ranges. The ordering number (Valid Combination) is a. Device Number formed by a combination of:

# **PIN DESCRIPTION**

# ACK

Active-LOW digital open-collector output used to indicate conversion complete and data valid. In Modes 0, 1, and 2  $\overrightarrow{ACK}$  is gated internally with  $\overrightarrow{RD}$  and  $\overrightarrow{WR}$  in order to generate WAIT states for the host processor. In Modes 3 and 4  $\overrightarrow{ACK}$  is ungated and reflects the converter status at all times.

ACK = 1 means a conversion is in progress.

ACK = 0 means that conversion is complete.

# AGND

Analog ground.

# C/D

Digital input used in conjunction with  $\overline{WR}$  to load command register and in conjunction with  $\overline{RD}$  (except for Mode 2) to select HIGH or LOW byte for READ. When C/D is HIGH and  $\overline{WR}$  is asserted, data present on  $D_0 - D_2$  are loaded into the command register to set up output code and conversion mode. When C/D is LOW and  $\overline{RD}$  is asserted, the lower byte (8 LSBs) is output to  $D_0 - D_7$  ( $D_0$  is the LSB). When C/D is HIGH and  $\overline{RD}$  is asserted, the upper byte (4 MSBs) is output to  $D_0 - D_3$ . In Mode 2 the output data control is done internally and is not accessible via the C/D pin.

# CLK

Clock input controls the internal ADC conversion process.

# COMP

Compensation pin for the internal reference amplifier. Connect a 0.01  $\mu F$  capacitor to V–.

# CS

Active-LOW digital input used to enable the Am6112 for I/O operations and to initiate conversions in Mode 2 (see Status Truth Table). If the Am6112 has been initialized for Mode 2,  $\overline{CS}$  HIGH will hold the SAR reset and the HIGH-to-LOW transition of  $\overline{CS}$  will start the first conversion. After  $\overline{CS}$  is LOW and the first conversion is completed in Mode 2, subsequent conversions are initiated by  $\overline{RD}$ .

# $D_0 - D_7$

Three-state data lines.  $D_0 - D_2$  are bidirectional data lines, while  $D_3 - D_7$  are strictly output data lines. Data is loaded into the internal command register via  $D_0 - D_2$  to select one of four modes of operation.  $D_0 - D_7$  are used to output the eight LSBs ( $B_0 - B_7$ ).  $D_0 - D_3$  are used to output the four MSBs ( $B_8 - B_{11}$ ) of the 12-bit data.  $D_4 -$   $D_7$  output the sign bit (B\_{11}) when two's complement output code is selected.  $D_0$  is the LSB and  $D_7$  is the MSB in this format.

## DGND

Digital ground.

## IREFIN

External reference current input.

# RD

Active-LOW digital input which starts conversions in Modes 1 and 2 and reads the SAR data in all modes. When used in conjunction with  $\overline{WR}$ ,  $\overline{RD}$  forces the Am6112 into a Mode 4 (stand-alone) conversion cycle. SAR data is read in two bytes. The reading of the HIGH byte (B<sub>8</sub> – B<sub>11</sub>) or LOW byte is user-selectable via the C/D pin (see Status Truth Table) except during Mode 2 (DMA-Compatible Mode).

## R<sub>IN</sub>

Analog voltage input.

## ROFF

Offset voltage input. Leave open or ground for unipolar operation. Connect to AGND for high-speed unipolar operation. Connect to  $V_{\text{REF}}OUT$  (buffered) for bipolar operation.

# V+

+5-V power supply input.

## **V**–

-5.2-V power supply input.

## VREFOUT

2.5-V internal voltage reference output.

### VREFIN

Connected to an external voltage reference or  $V_{\text{REF}}OUT$  to establish a reference current for the DAC bit currents.

# WR

Active-LOW digital input which resets the SAR and starts a conversion cycle in Modes 0 and 3. When used in conjunction with  $\overline{RD}$ ,  $\overline{WR}$  forces the Am6112 into a Mode 4 (stand-alone) conversion cycle. When  $\overline{WR}$  is asserted with the C/D pin held HIGH, data present on D<sub>0</sub>, D<sub>1</sub>, and D<sub>2</sub> (pins 9, 8, and 7 respectively) are loaded into the command register to set up output code (offset binary or two's complement) and conversion mode (Modes 0 – 3).

# **MAXIMUM RATINGS**

| Storage Temperature                 | -65 to +150°C  |

|-------------------------------------|----------------|

| Lead Temperature (Soldering 60 sec) | 300°C          |

| Max Package Dissipation             | 1 W            |

| V+ to DGND                          | –0.3 to +7.0 V |

| V- to DGND                          | +0.3 to −7.0 V |

| Max Differential V+ to V-           | ±12 V          |

| Digital Inputs to DGND              | 0.5 to +6.0 V  |

| AGND to DGND                        | ±1 V           |

| VREF Max Output Current             | 15 mA          |

| Max Input Current at IREFIN         | 2 mA           |

| Voltage at VREFIN, IREFIN           | V-to V+        |

| Voltage at RIN, ROFF                | ±18 V          |

| Open-Collector Voltage              | ۷+             |

Stresses above those listed under MAXIMUM RATINGS may cause permanent device failure. Functionality at or above these limits is not implied. Exposure to absolute maximum ratings for extended periods may affect device reliability.

# **OPERATING RANGES**

Operating Temperature Die Size

0 to +70°C 0.142 x 0.176 in.

Operating ranges define those limits between which the functionality of the device is guaranteed.

# DC CHARACTERISTICS

(These specifications apply for V+ = +5 V  $\pm$ 5%, V- = -5.2 V +5%, VREF connected per test circuit, TA = 0 to +70°C, fcLock = 150 kHz, 0 to 10-V input range, RoFF connected to AGND stand-alone mode, unless otherwise stated.)

| Parameter                           | Descri                                                  | otion                                                                                                           | Test Conditions                                              | Min.     | Тур.       | Max.       | Unit                   |

|-------------------------------------|---------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------|----------|------------|------------|------------------------|

| Transfer Ch                         | aracteristics                                           |                                                                                                                 |                                                              |          |            |            |                        |

| Symbol                              | Resolution                                              |                                                                                                                 |                                                              | 12       | 12         | 12         | Bits                   |

| DNL                                 | Differential Nonlinearity                               | Am6112                                                                                                          | T <sub>A</sub> = +25°C                                       |          | ±0.5       | ±1         | LSB                    |

|                                     | ,                                                       |                                                                                                                 |                                                              | •        | ±0.5       | ±2         |                        |

|                                     |                                                         | Am6112-10                                                                                                       | T <sub>A</sub> = +25°C                                       |          | ±1.0       | ±2         |                        |

|                                     |                                                         | AMOTTE TO                                                                                                       | 1, - +20 0                                                   |          | ±1.0       | ±3         | ļ                      |

| LIN                                 | Linearity                                               | Am6112                                                                                                          | T <sub>A</sub> = +25°C                                       |          | ±0.8       | ±2         | LSB                    |

| Lut                                 | Encarty                                                 | Valie I I L                                                                                                     |                                                              |          | ±0.8       | ±2         |                        |

|                                     | ]                                                       | Am6112-10                                                                                                       | T <sub>A</sub> = +25°C                                       |          | ±0.8       | ±2         |                        |

|                                     |                                                         | Amorizio                                                                                                        | 1, = +23 0                                                   |          | ±0.8       | ±2         |                        |

|                                     | Inherent Quantization Erro                              | *                                                                                                               |                                                              | -        | 1010       | ±1/2       | LSB                    |

| -                                   | Unipolar Gain Error                                     |                                                                                                                 | V <sub>IN</sub> = 0 to +10 V                                 |          | ±5         | ±172       | LSB                    |

|                                     | Unipolar Offset Error                                   |                                                                                                                 | V <sub>IN</sub> = 010 +10 V                                  |          | ±3         | ±10        | LSB                    |

|                                     | Bipolar Gain Error RoFF Co                              | nnected to V                                                                                                    | $V_{iN} = -5 V \text{ to } +5 V$                             |          | ±5         | ±10<br>±20 | LSB                    |

|                                     | Bipolar Offset Error R <sub>OFF</sub> C                 |                                                                                                                 | V <sub>IN</sub> = -5 V to +5 V                               |          | ±2         | ±20        | LSB                    |

| +PSR                                | Positive Power Supply Set                               | ositivity                                                                                                       | V+ = +5 V ±5%                                                |          | 0.02       | 0.3        | %FS                    |

| -PSR                                | Negative Power Supply Se                                |                                                                                                                 | V- = -5.2 V ±5%                                              |          | 0.02       | 0.15       | %FS                    |

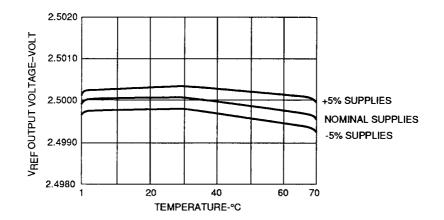

| Internal Ref                        |                                                         | should be a second s | 1 1 - 5.2 1 1570                                             | L        | 0.02       | 0.10       | 701 0                  |

| V <sub>REF</sub>                    | Reference Voltage V <sub>REFOUT</sub>                   | Connected to V                                                                                                  | 1 1                                                          | 2.490    | 2.5        | 2.510      | v                      |

| ΔV <sub>REF</sub> /V <sub>REF</sub> | Load Regulation                                         | CONTRACTED TO V REFIN                                                                                           | $I_{REF} = 1 \text{ mA}$<br>$I_{REF} = 0 \text{ mA to 4 mA}$ | 2.490    | 0.04       | 0.2        | ۷<br>%V <sub>ref</sub> |

| $\Delta V_{REF} / V_{REF}$          | Line Regulation                                         | ·····                                                                                                           | $V_{HEF} = 0.000 \text{ mA to 4 mA}$<br>V+ = +5 V ±5%.       |          | 0.04       | 0.2        | 70 V REF               |

| / V REF / V REF                     | Line Regulation                                         |                                                                                                                 | -5.2 V ±5%                                                   |          | 0.02       | 0.3        | o/ \ /                 |

| Analog Inpu                         | + (Di= 10)                                              |                                                                                                                 | ~5.2 ¥ 15 %                                                  | l        | 0.02       | 0.3        | %V <sub>ref</sub>      |

| Analog Inpu                         | · · · · · · · · · · · · · · · · · · ·                   |                                                                                                                 | -T                                                           |          |            | 1          |                        |

| R <sub>IN</sub>                     | Input Resistance<br>±5 V                                |                                                                                                                 |                                                              |          | 2.5        |            | kΩ                     |

|                                     | 0 to 10 V                                               |                                                                                                                 |                                                              |          | 2.5        |            | kΩ                     |

| C <sub>IN</sub>                     | Input Capacitance                                       |                                                                                                                 |                                                              |          | 2.3        |            | 1.52                   |

| UIN                                 | R <sub>IN</sub> , R <sub>OFF</sub> , V <sub>REFIN</sub> |                                                                                                                 |                                                              |          | 4          |            | pF                     |

| Digital Input                       |                                                         |                                                                                                                 |                                                              |          | . 4        |            | . h⊦                   |

| Digital input                       |                                                         |                                                                                                                 |                                                              |          |            | 1          | r                      |

| <u></u>                             | Logic Level Input Voltag                                | e                                                                                                               |                                                              | 0.0      |            |            | - <del>.</del>         |

| V <sub>IH</sub>                     | Logic 1                                                 |                                                                                                                 |                                                              | 2.0      |            |            | V V                    |

| V <sub>IL</sub>                     | Logic 0                                                 |                                                                                                                 |                                                              |          |            | 0.8        | V                      |

|                                     | Logic Level Input Currer                                | It                                                                                                              | V 07V                                                        |          | 1.0        | 10         |                        |

| <u> I<sub>н</sub></u>               | Logic 1<br>Logic 0                                      |                                                                                                                 | $V_{iN} = 2.7 V$<br>$V_{iN} = 0.4 V$                         |          | 1.0<br>0.1 | 10         | μΑ                     |

|                                     | CLOCK                                                   |                                                                                                                 | V <sub>IN</sub> = 0.4 V                                      |          | 4          | 5          | μA<br>pF               |

| C <sub>IN</sub>                     |                                                         |                                                                                                                 | 1                                                            | l        |            | L          | <u> </u>               |

| Digital Outp                        | · · · · · · · · · · · · · · · · · · ·                   |                                                                                                                 |                                                              | <u> </u> |            | 1          | <b></b>                |

| M                                   | Logic Level Output Volta                                | iges                                                                                                            | 400 4                                                        |          | 25         | <u> </u>   | v                      |

| V <sub>oH</sub>                     | Logic 1                                                 |                                                                                                                 | $I_{OH} = -400 \ \mu A$ $I_{OL} = 4 \ m A$                   | 2.4      | 3.5        | 0.5        |                        |

| VoL                                 | Logic 0<br>Output Short-Circuit Curre                   |                                                                                                                 | $V_{o} = 2.4 \text{ V}$                                      |          | 0.38       | 0.5        |                        |

| lsc                                 |                                                         |                                                                                                                 |                                                              |          |            | <u> </u>   | mA                     |

| l <sub>оzн</sub>                    | Three-State Leakage HIG                                 |                                                                                                                 | $V_o = 2.4 V$                                                |          | 0.01       | 2          | μΑ                     |

| loz                                 | Three-State Leakage LOV<br>Three-State Leakage HIG      |                                                                                                                 | $V_{o} = 0.4 V$<br>$V_{o} = 2.4 V$                           |          | 0.1        | 2          | μΑ                     |

| l <sub>ozh</sub>                    | Three-State Leakage HIG                                 |                                                                                                                 | $V_0 = 2.4 V$<br>$V_0 = 0.4 V$                               |          | 1.0<br>0.1 | 10<br>5    | μΑ                     |

| loz Bawar Baau                      |                                                         |                                                                                                                 | $v_0 = 0.4 v$                                                | I        | L          | 1 2        | μA                     |

| Power Requ                          |                                                         |                                                                                                                 |                                                              | r        |            | 1          | <u> </u>               |

| <u> +</u>                           | Positive Supply Current                                 | <u>_</u>                                                                                                        |                                                              |          | 30         | 45         | mA                     |

| F                                   | Negative Supply Current                                 |                                                                                                                 |                                                              | -75      | -50        | -          | mA                     |

| Po                                  | Power Dissipation                                       |                                                                                                                 |                                                              |          | 410        | 646        | mW                     |

| V+                                  | Positive Supply Range                                   |                                                                                                                 |                                                              | 4.75     | 5.00       | 5.25       | V                      |

| V-                                  | Negative Supply Range                                   |                                                                                                                 | 1                                                            | -4.94    | -5.20      | -5.46      | V I                    |

# SYSTEM TIMING

(These specifications apply for V+ = +5 V, V- = -5.2 V, V\_{REF} connected per test circuit,  $T_A = +25^{\circ}C$ , 0 to +10-V input range, unles otherwise stated.)

| Symbol               | Descriptions                                                  | Min. | Тур. | Max. | Unit |

|----------------------|---------------------------------------------------------------|------|------|------|------|

| t <sub>gonv</sub>    | Conversion Time R <sub>OFF</sub> Connected to AGND (unipolar) |      | 6    | 10*  | μs   |

| t <sub>conv</sub>    | Conversion Time R <sub>orr</sub> Open (unipolar)              |      | 15   |      | μs   |

| CLK T <sub>THL</sub> | CLK HIGH to LOW                                               |      |      | 100  | ns   |

| CLK T <sub>TLH</sub> | CLK LOW to HIGH                                               |      | 5    | 10   | ns   |

| CLK Duty Cycle       | % Time for which CLK is HIGH                                  | 30   | 50   | 70   | %    |

| CLK Freq             | CLK Frequency RoFF Connected to AGND (unipolar)               |      | 2•0  |      | MHz  |

## **DEFINITION OF TERMS**

**Resolution:** The number of possible analog input levels an A/D will resolve. Expressed as either the number of output bits, or 1 part in  $2^n$  where n is the number of bits.

**Differential Nonlinearity:** The deviation between the actual code width of an A/D from the ideal code width. The code width is defined as the range of analog input which produces a given digital output code. An ideal value of a code width is equivalent to FSR/2<sup>n</sup>, where FSR is full-scale range and n is the number of bits.

Linearity: The deviation of each individual code from an ideal straight line transfer curve between zero and full scale, with the straight line measured from the middle of each particular code.

Inherent Quantization Error: Quantization Error is a direct consequence of the resolution of the A/D. All analog voltages within a given range are represented by a single digital output code. There is, therefore, an *inherent*  $\pm$ 1/2 LSB conversion error even for a perfect A/D.

Gain Error: Defined as the difference between the analog input levels required to produce the first and the

last digital output code transitions with gain error as a measure of the deviation between the actual gain from the ideal gain.

**Unipolar Offset Error:** Difference between the ideal (+1/2 LSB) and the actual analog input level required to produce the first digital code transition  $(00 \dots .00 \text{ to } 00 \dots .01)$  over the complete temperature range.

**Bipolar Offset Error:** Difference between the ideal (1/2 FSR - 1/2 LSB) and the actual analog input level required to produce the major carry output digital code transition (from  $01 \dots 11$  to  $10 \dots 00$ ).

**Power Supply Sensitivity:** A measure of the change in gain of the A/D resulting from a change in supply voltage. Usually expressed in total %FS for a percentage change in supply voltage.

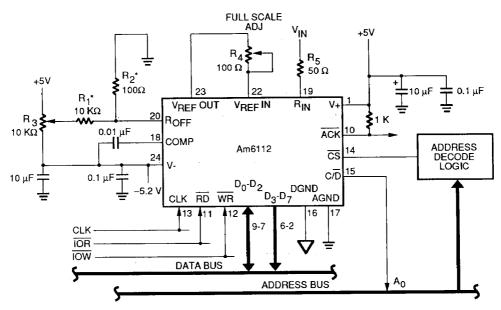

**Conversion Time:** The measure of how long it takes for the A/D to arrive at the correct digital output code. It is the time between ACK HIGH to ACK LOW which signifies that the conversion is completed. TEST CIRCUIT—Top View Unipolar—Stand Alone—R<sub>OFF</sub> Connected to Analog Ground

CONTROL INPUTS AND EXTERNAL CLOCK

01910-003A

01910-004A

## CALIBRATION

#### **Unipolar Configuration (Figure 1)**

The Am6112 contains all the active components required to perform a complete 12-bit A/D conversion (except clock). All that is necessary, in most situations, is the connection of the power supplies (+5 V and -5.2 V), analog input, and conversion initiation command, discussed later. The Am6112 has a nominal 1/2 LSB offset so that the exact analog input for a given code will be in the middle of the code. If the gain error (full-scale) trim is not required, short pin 22 to 23 and delete Rs. If offset trim is not required delete R1, R2, and R3.

#### **Unipolar Calibration (Figure 1)**

The initial offset error can be trimmed by R<sub>3</sub>. The first A/D transition (0000 0000 0000 to 0000 0000 0001) should occur for an input level of  $\pm 1/2$  LSB (1.22 mV). While continuously monitoring the A/D output, adjust R<sub>3</sub> for 50% duty cycle of the LSB (D<sub>0</sub>).

The gain error (full-scale) trim is done by applying a signal 1-1/2 LSBs below the nominal full scale (9.9963 V for a 10-V input range). R4 is trimmed to give the last transition (1111 1111 1110 to 1111 1111 1111). While continuously monitoring the A/D output, adjust R4 for 50% duty cycle of the LSB (D<sub>0</sub>).

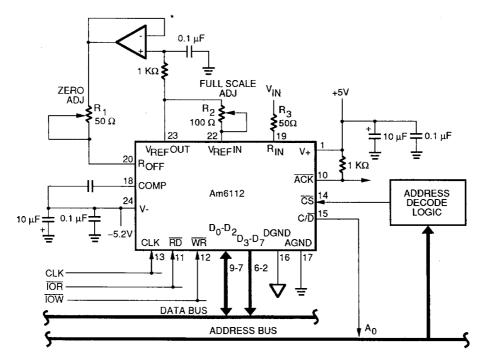

#### **Bipolar Configuration (Figure 2)**

If calibration is not required delete R1, R2, and R3.

#### **Bipolar Calibration (Figure 2)**

Bipolar calibration is similar to unipolar calibration. First, a signal +1/2 LSB (-4.9976 V) above negative full-scale (-4.9988 V for the  $\pm$ 5 V input range) is applied to R<sub>3</sub> and potentiometer R<sub>1</sub> is trimmed to give the first transition (0000 0000 0000 0000 0001). Then a signal 1/2 LSB (4.9963 V) below positive full-scale (4.9976 V), is applied and potentiometer R<sub>2</sub> is trimmed to give the give the give the last transition (1111 1111 1110 to 1111 1111).

\*Remove  $R_2$  and make  $R_1 = 1 M\Omega$  for lowest noise, medium speed operation.

01910-005A

Figure 1. Am6112 Unipolar Configuration ( $R_{orr}$  low impedance  $\rightarrow$  high speed)

\*A low impedance Op Amp is recommended for optimum performance due to fast switching currents appearing at  $R_{OFF}\,.$

01910-006A

Figure 2. Am6112 Unipolar Configuration

#### THEORY OF OPERATION

The Am6112 is a fully microprocessor-compatible programmable 12-bit A/D converter. The device is initialized by writing a 3-bit word into the internal command register via the bidirectional data pins  $D_0 - D_2$ ; in this operation, bits  $D_1$  and  $D_2$  configure the converter into one of four modes, while  $D_0$  provides the choice of either offset-binary or two's complement output code. A fifth mode is a unique stand-alone mode in which the internal command register is programmed whenever the control inputs Read (RD) and Write (WR) are LOW together.

The Am6112 has the standard microprocessor peripheral control lines, Chip Select ( $\overline{CS}$ ), Write ( $\overline{WR}$ ), Read ( $\overline{RD}$ ), plus one additional line, Command/Data ( $C/\overline{D}$ ). The C/ $\overline{D}$  control qualifies both the read and write operations. It defines a write operation as either an initialization or an external start conversion command, and during read cycles it steers either the upper or lower data byte to the data outputs.

The Am6112 requires an external clock (CLK) to control the conversion speed. The status output acknowledge

(ACK) indicates whether a conversion is in progress (HIGH) or completed (LOW). Conversion starts on the next falling edge of the clock after the triggering event. Conversion finishes 12.5 clock cycles later.

The Successive Approximation Register performs the analog-to-digital conversion by sequentially testing the effect of removing the bit currents (B<sub>11</sub> to B<sub>0</sub>) of the D/A converter, which are all steered to the A/D summing node. The bit currents are binary scaled versions of the reference current flowing into the D/A converter reference amplifier, and the voltage comparator decides whether the bit currents should be removed or retained. The reference current is obtained from the internal reference voltage source using the scale resistor connected to V<sub>REF</sub>OUT. The Am6112 contains the necessary gain and range selection resistors enabling bipolar signals between -5 V and +5 V, and unipolar signals from 0 to +10 V to be digitized. The device operates from +5 V and -5.2 V supplies.

| STATUS TRUTH TABLE                                                           |                                                    |       |    |    |  |  |  |

|------------------------------------------------------------------------------|----------------------------------------------------|-------|----|----|--|--|--|

|                                                                              | Control Logic Inputs<br>CS RD WR C/D Am6112 Status |       |    |    |  |  |  |

|                                                                              |                                                    |       | RD | ĈŜ |  |  |  |

| Output Data Lines (D <sub>7</sub> – D <sub>0</sub> ) in High-Impedance State | X                                                  | Х     | X  | 1  |  |  |  |

| Forced to Stand-Alone Mode Operation                                         | 0                                                  | 0     | 0  | 0  |  |  |  |

| Write into Command Register to Select Mode of Operat                         | 1                                                  | 1 0 1 |    | 0  |  |  |  |

| Read eight LSBs (Low Byte), Except in Mode 2                                 | 0                                                  | 1     | 0  | 0  |  |  |  |

| Read four MSBs (High Byte), Except in Mode 2                                 | 1                                                  | 1     | Ō  | 0  |  |  |  |

| Start Conversion (Modes 0, 3 and Stand-Alone)                                | 0                                                  | 0     | 1  | Ō  |  |  |  |

| Start Conversion, (Modes 1, 2)                                               | 0                                                  | 1     | Ó  | Ō  |  |  |  |

# **APPLICATIONS INFORMATION**

Depending on the processor used and throughput rate required, the user can select up to five operating modes.

In Mode 0, the conversion cycle is started by an active write (WR) and the next two read ( $\overline{\text{ND}}$ ) commands send the data out. The status of the command/data ( $C/\overline{D}$ ) line determines whether the output data consists of the eight LSBs or four MSBs. In this mode, as well as Modes 1 and 2, the  $\overline{\text{ACK}}$  line reflects the ADC's status during an active read period.  $\overline{\text{ACK}}$  can then be used to extend the I/O read cycle if desired.

In Mode 1, a conversion cycle is started by an active read. This mode is well-suited to microprocessors such as the Z80° and Z8000° which have data-block transfer as part of their repertoire.  $\overrightarrow{ACK}$  only reflects the ADC's status when  $\overrightarrow{CS}$ ,  $\overrightarrow{RD}$ , and  $\overrightarrow{CD}$  are LOW. The first conversion after initialization is invalid.

Mode 2 puts the A/D converter under control of a DMA controller such as the Am9517A. During DMA transfer, the microprocessor is disabled, and the Am9517A provides all the signals to control the conversion process. In Mode 2, the A/D converter internally controls the output \*280 and 2800 are trademarks of Zilog, Inc.

of the data bytes. The first read signal sends out the eight LSBs and simultaneously saves the four MSBs into an internal latch. The LOW-to-HIGH transition of the first read initiates another conversion cycle. A second read cycle sends out the latched MSBs at the same time the A/D converter is performing the next conversion.  $C/\overline{D}$  is ignored. The first conversion after initialization is triggered by  $\overline{CS}$  and should be ignored.

Mode 3 is similar to Mode 0 except that the  $\overline{ACK}$  line reflects the A/D converter's true status. This difference in the decoding of the  $\overline{ACK}$  line provides flexibility in the microprocessor hand-shaking. Although tying the  $\overline{ACK}$ line to the microprocessor's Wait input pin might reduce throughput, by adding additional Wait states, it does guarantee full 12-bit conversion cycles.

Mode 4 is a unique and stand-alone mode, in which the internal command register is preprogrammed to operate with offset binary data output format. Mode 4 is programmed whenever RD and WR are LOW together. This situation is an illegal state with any microprocessorbased system. To summarize, the Am6112 has five operating modes, two possible output codes (Two's complement or offset binary) and two possible input modes (unipolar or bipolar). Four of the operating modes are microprocessor-compatible and one operating mode is stand-alone. Before using one of the microprocessor-compatible modes, the Am6112 must first be initialized to the appropriate operating mode and output code by asserting WR and bringing C/D HIGH with the appropriate data present on  $D_0 - D_2$ . This initialization need be done only once for any given mode and code. Conversions may be triggered by WR or by RD. Modes 0 and 3 are triggered by WR and differ only in their treatment of  $\overline{ACK}$ . In

Mode 0  $\overline{ACK}$  is gated by  $\overline{RD}$ . The typical application for this mode is with a microprocessor, where one command (WR) will start conversion and two reads; ( $\overline{RD}$ ) will get the digitized data. The gated  $\overline{ACK}$  is used to insert Wait states on read. Modes 1 and 2 are triggered by  $\overline{RD}$ and gate  $\overline{ACK}$  with  $\overline{RD}$ , as in Mode 0. Mode 2 (DMA compatible) is the fastest throughput mode.

Stand-alone mode conversions are triggered by asserting  $\overline{WR}$  and  $\overline{RD}$ , as shown in the Timing Diagram. ACK reflects true converter status in stand-alone mode, as it does in Mode 3.

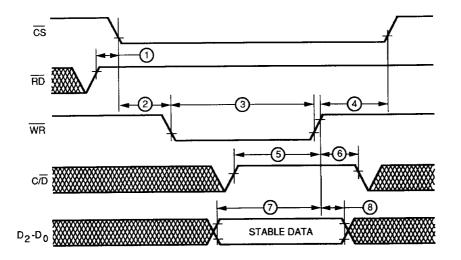

### INITIALIZATION TIMING TABLE

| Number | Parameters            | Description                     | Min. | Тур. | Max. | Unit |

|--------|-----------------------|---------------------------------|------|------|------|------|

| 1      | tro cs                | RD HIGH to CS LOW (RD Setup)    | - 10 |      |      | ns   |

| 2      | tscs-wa               | CSLOW to WRLOW (CS Setup)       | 10   |      |      | ns   |

| 3      | twa                   | WR Pulse Width                  | 100  |      |      | ns   |

| 4      |                       | WR HIGH to CS LOW (WR Hold)     | 10   |      |      | ns   |

| 5      | t <sub>sc/0</sub> _wR | C/D HIGH to WR HIGH (C/D Setup) | 100  | 30   |      | ns   |

| 6      | t <sub>HC/0</sub> -wa | WR HIGH to C/D HIGH (C/D Hold)  | 10   |      |      | ns   |

| 7      | t <sub>sp-we</sub>    | Data Setup Time                 | 100  |      |      | ns   |

| 8      | t <sub>HD</sub>       | Data Hold Time                  | 20   |      |      | ns   |

#### INITIALIZATION TIMING DIAGRAM

01910-007A

#### Am6112 COMMAND REGISTER DECODING

|    | Comr | mand B | its  | Mode Description       |                       |                       |

|----|------|--------|------|------------------------|-----------------------|-----------------------|

| D, | D,   | D,     | Mode | Conversions Started by | ACK Output Gated with | C/D Function          |

| 0  | 0    | 0/1    | 0    | WR                     | RD • CS               | Read LOW or HIGH Byte |

| 0  | 1    | 0/1    | 1    | RD                     | RD • CS • C/D         | Read LOW or HIGH Byte |

| 1  | 0    | 0/1    | 2    | RD                     | RD • ČS               | Ignored               |

| 1  | 1    | 0/1    | 3    | WR                     | CS                    | Read LOW or HIGH Byte |

| x  | x    | X*     | 4    | WR                     | CS                    | Read LOW or HIGH Byte |

Notes:  $D_0 - 1$  — Two's complement output code  $D_0 = 0$  — Offset binary output code X = Don't care

\*Mode 4 always uses offset binary output code.

| Number | Parameters              | Descriptions                      | Min. | Тур. | Max.                   | Unit               |

|--------|-------------------------|-----------------------------------|------|------|------------------------|--------------------|

| 1      | twee                    | WR LOW                            | 100  |      |                        | ns                 |

| 2      | t <sub>c/01</sub> wi    | C/D LOW to WR LOW Setup           | 10   |      |                        | ins                |

| 3      |                         | CS LOW to WR LOW Setup            | 20   |      |                        | ns                 |

| 4      | twn c/DL                | WR HIGH to C/D LOW Hold           | 10   |      |                        | ns                 |

| 5      | t <sub>wn – csn</sub>   | WR HIGH to CS HIGH Hold           | 20   |      |                        | ns                 |

| 6      | twn - cch               | WR HIGH to CC HIGH Delay (Note 1) |      |      | t <sub>cLK</sub> + 50* | ns                 |

| 7      | tosl - ACKL             | CS LOW to ACK LOW Delay           |      | 50   | 100                    | ns                 |

| 8      | tosh - ACKH             | CS HIGH to ACK HIGH Delay         | 40   | 75   | 150                    | ns                 |

| 9      |                         | CS LOW to RD LOW                  | 20   |      |                        | ns                 |

| 10     |                         | RD LOW                            | 100  |      |                        | ns                 |

| 11     |                         | C/D to RD LOW Setup               | 20   |      |                        | nsi                |

| 12     | t <sub>conv</sub>       | Conversion Time                   |      |      | 12 • 5                 | t <sub>cux</sub> * |

| 13     | t <sub>RH — C/D</sub>   | RD HIGH to C/D Hold               | 10   | 1    |                        | ns                 |

| 14     | t <sub>BL-ACKH</sub>    | RD LOW to ACK HIGH Delay          |      | 100  | 200                    | ns                 |

| 15     |                         | RD HIGH to ACK LOW Delay          |      | 50   | 100                    | ns                 |

| 16     | t <sub>RL - DTVLD</sub> | RD LOW to Data Delay              |      | 50   | 100                    | ns                 |

| 17     | CSH- DTVLD              | RD HIGH to Data Hold              | 20   | 60   | 75                     | ns                 |

| 18     | t <sub>RH</sub> csH     | RD HIGH to CS HIGH                | 20   |      |                        | ns                 |

\*Note: t<sub>CLK</sub> = One Clock Period.

Note 1. CC is an internal line and is shown for clarity.

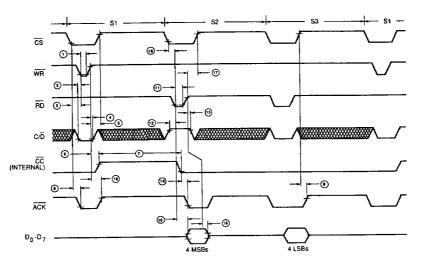

#### MODE 0 TIMING DIAGRAM

S1 --- Start a conversion cycle with an active WR.

01910-008A

- S<sub>2</sub> Read first data byte. The four MSBs become valid six clock periods after CC goes HIGH. Therefore, the four MSBs may be read during S<sub>2</sub> while the conversion cycle is in progress. If conversion is done (CC going LOW) prior to S<sub>2</sub>, then either the four MSBs or the eight LSBs may be read first and the ACK signal during S<sub>2</sub> and S<sub>3</sub> is the same as during S<sub>1</sub>. If the conversion time is longer than S<sub>1</sub> + S<sub>2</sub>, then the ACK signal can be used to extend the active part of S<sub>2</sub>.

- S<sub>3</sub> Read second data byte.

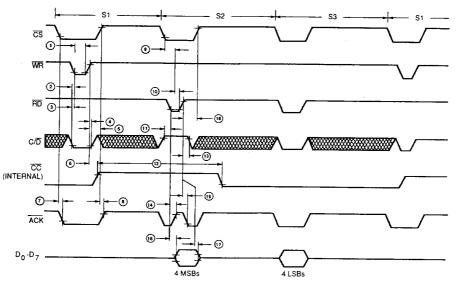

#### MODE 1 TIMING TABLE

| Number | Parameters            | Description                       | Min. | Тур. | Max.                    | Unit |

|--------|-----------------------|-----------------------------------|------|------|-------------------------|------|

| 1      |                       | CS LOW to RD LOW Setup            | 20   |      |                         | ns   |

| 2      | t <sub>ap</sub>       | RDLOW                             | 100  |      |                         | ns   |

| 3      | t <sub>an Can</sub>   | RD HIGH to CS HIGH                | 20   |      |                         | ns   |

| 4      | t <sub>cro</sub> cs∟  | C/D to RD LOW Setup               | 10   |      |                         | ns   |

| 5      | t <sub>BH</sub> — c/D | RD HIGH to C/D Hold               | 10   |      |                         | ns   |

| 6      |                       | RD HIGH to CC HIGH Delay (Note 1) |      |      | t <sub>ci_K</sub> + 50* | ns   |

| 7      | t <sub>conv</sub>     | Conversion Time                   |      |      | 12 • 5                  | ns   |

| 8      | tosL - ACKL           | CS LOW to ACK LOW Delay           |      | 50   | 100                     | ns   |

| 9      |                       | CS HIGH to ACK HIGH Delay         |      | 75   | 150                     | . ns |

| 10     |                       | RD HIGH to Data Delay             |      | 50   | 100                     | ns   |

| 11     |                       | RD HIGH to Data Hold              | 20   | 60   | 75                      | ns   |

\*Note: t<sub>CLK</sub> = One Clock Period.

Note 1. CC is an internal line and is shown for clarity.

#### MODE 1 TIMING DIAGRAM

01910-009A

- S<sub>1</sub> Start the first conversion cycle with an active RD. The 8 LSBs read are not valid.

- S<sub>2</sub> Read the first four MSBs. The four MSBs become valid six clock periods after CC goes high. Therefore, the four MSBs may be read *during* S<sub>2</sub> while the conversion cycle is in progress. If conversion ends prior to S<sub>2</sub>, then either the four MSBs or the 8 LSBs may be read first and the ACK signal during S<sub>2</sub> is the same as during S<sub>1</sub>. If the conversion time is longer than S<sub>2</sub>, then the ACK signal can be used to extend the active part of S<sub>2</sub>. C/D must be LOW to give a valid ACK signal.

- $S_3$  and  $S_1 Read the first eight LSBs and start the next conversion cycle.$

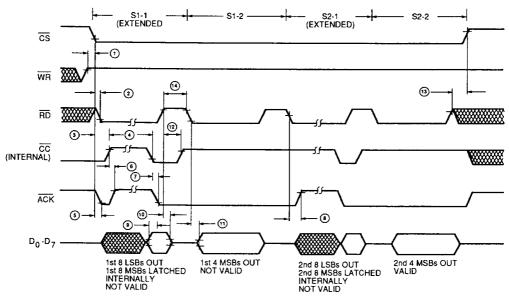

### MODE 2 TIMING TABLE

| Number | Parameters              | Description                        | Min. | Тур. | Max.                   | Unit               |

|--------|-------------------------|------------------------------------|------|------|------------------------|--------------------|

| 1      | t <sub>wH</sub> _⊂s⊾    | WR HIGH to CS LOW Setup            | 10   |      |                        | ns                 |

| 2      |                         | CS LOW to RD LOW Setup             | 10   |      |                        | ns                 |

| 3      | tosl-coh                | CS LOW to CC HIGH Delay (Note 1)   |      |      | t <sub>cuk</sub> + 50* | ns                 |

| 4      | t <sub>conv</sub>       | Conversion Time                    |      |      | 12 • 5                 | t <sub>c⊔s</sub> * |

| 5      | tosi - ACKL             | CS LOW to ACK LOW Delay            |      | 50   | 100                    | ns                 |

| 6      | CCH-ACKH                | CC HIGH to ACK HIGH Delay (Note 1) |      | 50   | 100                    | ns                 |

| _7     |                         | CC LOW to ACK LOW Delay (Note 1)   |      | 50   | 100                    | ns                 |

| 8      |                         | RD LOW to ACK HIGH Delay           |      | 100  | 200                    | ns                 |

| 9      |                         | Data to ACK LOW                    | 20   | 50   |                        | ns                 |

| 10     | t <sub>RH - DTHLD</sub> | RD HIGH to Data Hold               | 20   | 60   | 75                     | ns                 |

| 11     |                         | RD LOW to Data Delay               |      | 50   | 100                    | ns                 |

| 12     | t <sub>RH-CCH</sub>     | RD HIGH to CC HIGH Delay (Note 1)  |      |      | t <sub>ськ</sub> + 50* | ns                 |

| 13     | t <sub>RH</sub> _csH    | RD HIGH to CS HIGH                 | 10   |      |                        | ns                 |

| 14     | t <sub>en</sub>         | RD HIGH                            | 50   |      |                        | ns                 |

\*Note:  $t_{CLK} = One Clock Period.$

Note 1. CC is an internal line and is shown for clarity.

#### MODE 2 TIMING DIAGRAM

01910-010A

- S<sub>1-1</sub> Start first conversion with  $\overline{CS}$  going LOW. First four MSBs are latched internally. First eight LSBs are valid when  $\overline{CC}$  goes LOW. Note that S<sub>1-1</sub> cycle is extended by the insertion of wait states using the  $\overline{ACK}$  signal. Second conversion starts after  $\overline{RD}$  goes HIGH. Data is invalid.

- S1.2 Read first four MSBs. Note that this cycle is not extended. Data is invalid.

- $S_{2-1} \rightarrow$  This cycle is similar to the  $S_{1-1}$  cycle.

- S22 This cycle is similar to the S12 cycle except that conversion cycles are inhibited after CS goes HIGH.

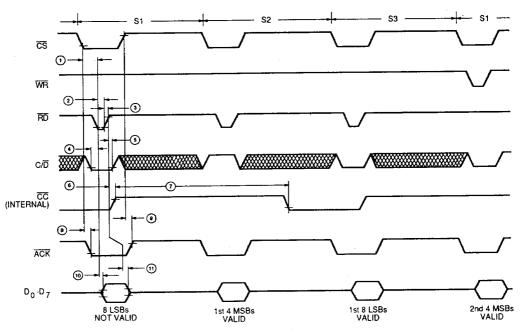

## MODE 3 TIMING TABLE

| Number | Parameters             | Description                       | Min.                  | Тур.                  | Max.                   | Unit               |

|--------|------------------------|-----------------------------------|-----------------------|-----------------------|------------------------|--------------------|

| 1      | twee                   | WRLOW                             | 100                   |                       |                        | ns                 |

| 2      | t <sub>c/p</sub> -wL   | C/D LOW to WR LOW Setup           | 10                    |                       |                        | ns                 |

| 3      |                        | CS LOW to WR LOW Setup            | 20                    |                       |                        | ns                 |

| 4      | twn-c/DL               | WR HIGH to C/D LOW Hold           | 10                    |                       |                        | ns                 |

| 5      | twn_csn                | WR HIGH to CS HIGH Setup          | 20                    |                       |                        | ns                 |

| 6      | t <sub>wh - cch</sub>  | WR HIGH to CC HIGH Delay (Note 1) |                       |                       | t <sub>cuk</sub> + 50* | ns                 |

| 7      | t <sub>conv</sub>      | Conversion Time                   |                       |                       | 12 • 5                 | t <sub>cuk</sub> * |

| 8      |                        | CS LOW to ACK LOW Delay           |                       | 50                    | 100                    | ns                 |

| 9      | tёян аскн              | CS HIGH to ACK HIGH Delay         | 40                    | 75                    | 150                    | ns                 |

| 10     |                        | CS LOW to RD LOW Setup            | 20                    |                       |                        | ns                 |

| 11     |                        | RD LOW                            | 100                   |                       |                        | ns                 |

| 12     |                        | C/D HIGH to RD LOW Setup          | 10                    |                       |                        | ns                 |

| 13     | t <sub>ян — с/бн</sub> | RD HIGH to C/D HIGH Hold          | 10                    |                       |                        | ns                 |

| 14     |                        | CC LOW to ACK LOW Delay (Note 1)  |                       | 50                    | 100                    | ns                 |

| 15     |                        | RD LOW to Data Delay              |                       | 50                    | 100                    | ns                 |

| 16     | tosh - DTHLD           | RD HIGH to Data Hold              | 20                    | 60                    | 75                     | ns                 |

| 17     | t <sub>RH</sub> – csH  | RD HIGH to CS HIGH                | 10                    |                       |                        | ns                 |

| 18     |                        | WR HIGH to ACK HIGH Delay         | t <sub>ськ</sub> + 40 | t <sub>сык</sub> + 75 | t <sub>ськ</sub> + 150 | ns                 |

\*Note: t<sub>CLK</sub> = One Clock Period.

Note 1. CC is an internal line and is shown for clarity.

#### MODE 3 TIMING DIAGRAM

01910-011A

- $S_1$  Start a conversion cycle with an active  $\overline{WR}$ .

- $S_2 Read first data byte.$  The four MSBs become valid six clock periods after  $\overline{CC}$  goes HIGH. Therefore, the four MSBs may be read during  $S_2$  while conversion cycle is in progress. If conversion is done ( $\overline{CC}$  has gone LOW) prior to  $S_2$ , then either the four MSBs or the eight LSBs may be read first and the  $\overline{ACK}$  signal during  $S_2$  and  $S_3$  is the same as during  $S_1$ . If conversion ends during active part of  $S_2$  ( $\overline{CS}$  LOW)  $\overline{ACK}$  output is as shown above. If the conversion time is longer than  $S_1 + S_2$ , then the  $\overline{ACK}$  output can be used to extend the active part of  $S_2$ .

- S<sub>3</sub> Read second data byte.

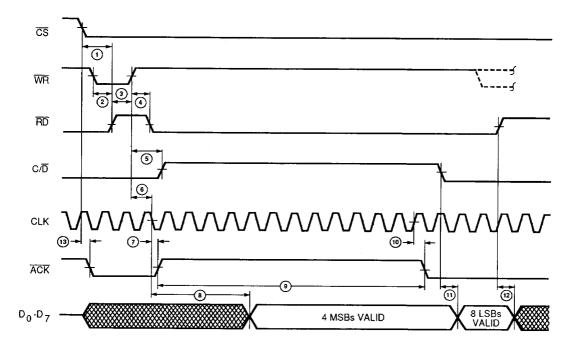

#### Am6112 STAND-ALONE MODE TIMING

| Number | Parameters                | Description                 | Min. | Тур.                         | Max.                         | Unit              |

|--------|---------------------------|-----------------------------|------|------------------------------|------------------------------|-------------------|

| 1      | t <sub>csl-BL</sub>       | CS LOW to RD LOW Setup      | 100  |                              |                              | ns                |

| 2      | t <sub>wl-AL</sub>        | WR LOW to RD LOW Setup      | 100  |                              |                              | ns                |

| 3      | t <sub>en – wh</sub>      | RD HIGH to WR HIGH Setup    | 10   |                              |                              | ns                |

| 4      | t <sub>wн вн</sub>        | WR HIGH to RD HIGH Hold     | 20   |                              |                              | ns                |

| 5      | twn_c/dl                  | WR HIGH to C/D LOW Hold     | 10   |                              | 1 t <sub>cLK</sub> *         | ns                |

| 6      |                           | WR HIGH to CLK LOW Setup    | 50   |                              |                              | ns                |

| 7      | t <sub>clk-ackh</sub>     | CLK LOW to ACK HIGH Delay   |      | 100                          | 200                          | ns                |

| 8      | toukl - UBVLD             | CLK LOW to Upper Byte Valid |      | 4.5 t <sub>cLx</sub> * + 130 | 4.5 t <sub>сцк</sub> * + 200 | ns                |

| 9      | t <sub>conv</sub>         | Conversion Time             |      |                              | 12 • 5                       | t <sub>cu</sub> * |

| 10     | t <sub>olk</sub> -ackl    | CLK HIGH to ACK LOW         |      | 50                           | 100                          | ns                |

| 11     | t <sub>c/dl</sub> - LBVLD | C/D LOW to Lower Byte Valid |      | 50                           | 150                          | ns                |

| 12     |                           | RD HIGH to Data Hold        | 20   |                              |                              | ns                |

| 13     | tosl - ACKL               | CS LOW to ACK LOW Delay     |      | 50                           | 100                          | ńs                |

\*Note: t<sub>CLK</sub> = One Clock Period.

#### STAND-ALONE TIMING DIAGRAM

01910-012A

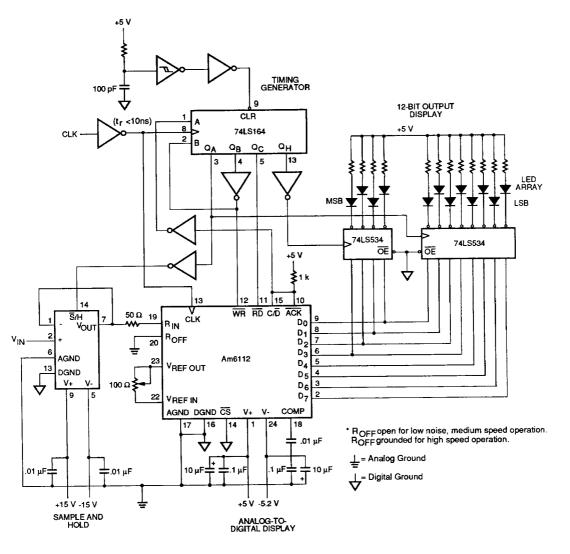

#### AM6112 STAND-ALONE APPLICATION CIRCUIT UNIPOLAR MODE

01910-013A

T-90-20

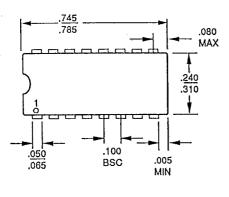

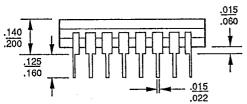

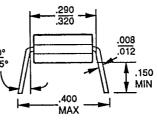

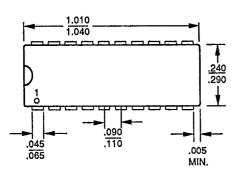

# PHYSICAL DIMENSIONS CD 016

07319B

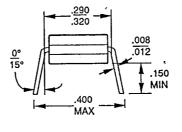

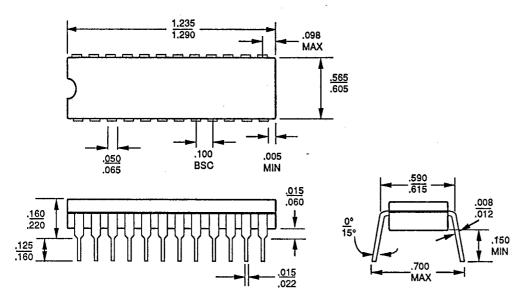

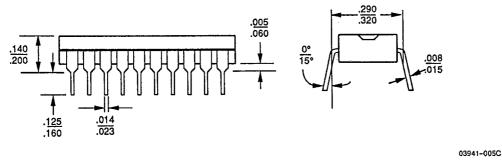

CD 020

03941-004C

4–2

T-90-20

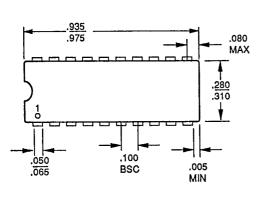

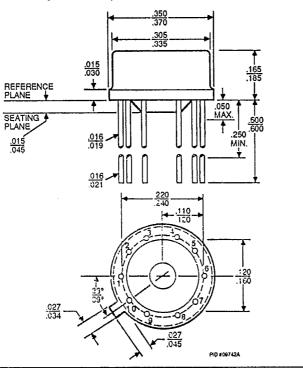

PHYSICAL DIMENSIONS (continued) CD 024

.

03067-008A

4--3

T-90-20

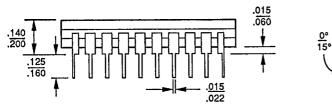

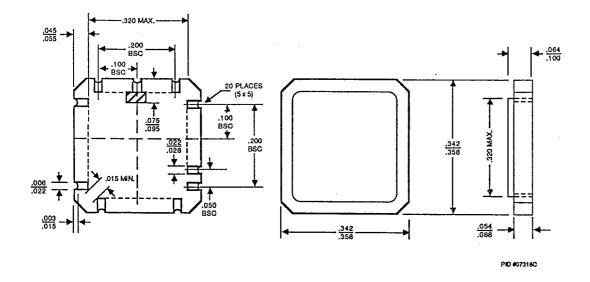

PD 020

4–4