# Low Cost, Laser Trimmed, Precision IC Op Amp

AD517

### **FEATURES**

Low Input Bias Current: 1nA max (AD517L)

Low Input Offset Current: 0.25nA max (AD517L)

Low V<sub>OS</sub>: 50µV max (AD517L), 150µV max (AD517J)

Low V<sub>OS</sub> Drift: 1.3µV/°C (AD517L)

Internal Compensation

MiL-Standard Parts Available

8-Pin TO-99 Hermetic Metal Can

Available in Chip Form

### PRODUCT DESCRIPTION

The AD517 is a high accuracy monolithic op amp featuring extremely low offset voltages and input currents. Analog Devices' thermally-balanced layout and superior IC processing combine to produce a truly precision device at low cost.

The AD517 is laser trimmed at the wafer level (LWT) to produce offset voltages less than  $50\mu V$  and offset voltage drifts less than  $1.3\mu V/C$  unnulled. Superbeta input transistors provide extremely low input bias currents of 1nA max and offset currents as low as 0.25nA max. While these figures are comparable to presently available BIFET amplifiers at room temperature, the AD517 input currents decrease, rather than increase, at elevated temperatures. Open-loop gain in many IC amplifiers is degraded under loaded conditions due to thermal gradients on the chip. However, the AD517 layout is balanced along a thermal axis, maintaining open-loop gain in excess of 1,000,000 for a wide range of load resistances.

The input stage of the AD517 is fully protected, allowing differential input voltages of up to  $\pm V_S$  without degradation of gain or bias current due to reverse breakdown. The output stage is short-circuit protected and is capable of driving a load capacitance up to 1000pF.

The AD517 is well suited to applications requiring high precision and excellent long-term stability at low cost, such as stable references, followers, bridge instruments and analog computation circuits.

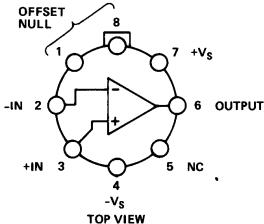

## PIN CONFIGURATION

The circuit is packaged in a hermetically sealed TO-99 metal can, and is available in three performance versions (J, K, and L) specified over the commercial 0 to +70°C range; and one version (AD517S) specified over the extended temperature range, -55°C to +125°C.

## PRODUCT HIGHLIGHTS

- 1. Offset voltage is 100% tested and guaranteed on all models.

- The AD517 exhibits extremely low input bias currents without sacrificing CMRR (over 100dB) or offset voltage stability.

- The AD517 inputs are protected (to ±V<sub>S</sub>), preventing offset voltage and bias current degradation due to reverse breakdown of the input transistors.

- Internal compensation is provided, eliminating the need for additional components (often required by high accuracy IC op amps).

- 5. The AD517 can directly replace 725, 108, and AD510 amplifiers. In addition, it can replace 741-type amplifiers if the offset-nulling potentiometer is removed.

- Thermally-balanced layout insures high open-loop gain independent of thermal gradients induced by output loading, offset nulling, and power supply variations.

- 7. Chips are available.

## AD517 — SPECIFICATIONS (@ +25°C and $V_s = \pm 15V$ dc)

| Model .                                                                                                                                           | Min                        | AD517J<br>Typ                               | Max                    | Min                        | AD517K<br>Typ                               | Max                   | Min                        | AD517L<br>Typ                               | Max                   | Min                        | AD517S<br>Typ                               | Max                   | Units                                                              |

|---------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------|---------------------------------------------|------------------------|----------------------------|---------------------------------------------|-----------------------|----------------------------|---------------------------------------------|-----------------------|----------------------------|---------------------------------------------|-----------------------|--------------------------------------------------------------------|

| OPEN LOOP GAIN $V_O = \pm 10V, R_L \ge 2k\Omega$ $T_{min} \text{ to } T_{max}, R_L = 2k\Omega$                                                    | 10 <sup>6</sup><br>500,000 |                                             |                        | 10 <sup>6</sup><br>500,000 | )                                           |                       | 10 <sup>6</sup><br>500,000 | )                                           |                       | 10 <sup>4</sup><br>250,000 | )                                           |                       | V/V<br>V/V                                                         |

| OUTPUT CHARACTERISTICS Voltage @ R <sub>L</sub> = 2kΩ, T <sub>min</sub> to T <sub>max</sub> Load Capacitance Output Current Short Circuit Current | ±10                        | 1000<br>25                                  |                        | <b>±10</b>                 | 1000<br>25                                  |                       | <b>±10</b>                 | 1000<br>25                                  |                       | ±10                        | 1000<br>25                                  |                       | V<br>pF<br>mA<br>mA                                                |

| FREQUENCY RESPONSE Unity Gain Small Signal Full Power Response Slew Rate, Unity Gain                                                              |                            | 250<br>1.5<br>0.10                          |                        |                            | 250<br>1.5<br>0.10                          |                       |                            | 250<br>1.5<br>0.10                          | i                     |                            | 250<br>1.5<br>0.10                          |                       | kHz<br>kHz<br>V/μs                                                 |

| INPUT OFFSET VOLTAGE Initial Offset Input Offset vs. Temp. Input Offset vs. Supply T <sub>min</sub> to T <sub>max</sub>                           |                            |                                             | 150<br>3.0<br>25<br>40 |                            |                                             | 75<br>1.8<br>10<br>15 |                            |                                             | 50<br>1.3<br>10<br>15 |                            |                                             | 75<br>1.8<br>10<br>20 | μV<br>μV/°C<br>μV/V<br>μV/V                                        |

| INPUT BIAS CURRENT Initial T <sub>min</sub> to T <sub>max</sub> vs. Temp, T <sub>min</sub> to T <sub>max</sub>                                    |                            |                                             | 5<br>8<br>±20          |                            |                                             | 2<br>3.5<br>±10       |                            |                                             | 1.0<br>1.5<br>±4      |                            |                                             | 2.0<br>10<br>±10      | nA<br>nA<br>pA/℃                                                   |

| INPUT OFFSET CURRENT Initial T <sub>min</sub> to T <sub>max</sub>                                                                                 |                            |                                             | 1.0<br>1.5             |                            | -                                           | <b>0.75</b><br>1.25   |                            |                                             | <b>0.2</b> 5<br>0.4   |                            |                                             | 2.0<br>10             | nA<br>nA                                                           |

| INPUT IMPEDANCE Differential Common Mode                                                                                                          |                            | 15  1.5<br>2.0×10                           | y"                     |                            | 20  1.5<br>2.0 × 10                         | )"                    |                            | 20∥1.5<br>2.0×10                            | <u>r</u>              |                            | 20  1.5<br>2.0×10                           | ۳                     | MΩ∥pF<br>Ω                                                         |

| INPUT VOLTAGE RANGE Differential Common Mode Rejection Common Mode Rejection T <sub>min</sub> to T <sub>max</sub>                                 | 94<br>94                   | ± V <sub>S</sub>                            |                        | 110<br>110                 | ±V <sub>S</sub>                             |                       | 110<br>100                 | ±Vs                                         |                       | 110<br>1 <del>00</del>     | ±Vs                                         |                       | V<br>dB<br>dB                                                      |

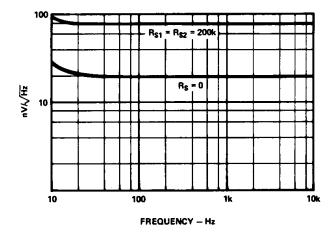

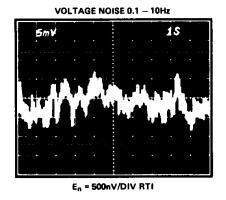

| INPUT NOISE  Voltage, 0. 1Hz to 10Hz  f = 10Hz  f = 100Hz  f = 1kHz  Current, f = 10kHz  f = 100Hz  f = 1kHz                                      |                            | 2<br>35<br>25<br>20<br>0.05<br>0.03<br>0.03 |                        |                            | 2<br>35<br>25<br>20<br>0.05<br>0.03<br>0.03 |                       |                            | 2<br>35<br>25<br>20<br>0.05<br>0.03<br>0.03 |                       |                            | 2<br>35<br>25<br>20<br>0.05<br>0.03<br>0.03 |                       | µV p-p<br>nV/√H2<br>nV/√H2<br>nV/√H2<br>pA/√H2<br>pA/√H2<br>pA/√H2 |

| POWER SUPPLY Rated Performance Operating Quiescent Current                                                                                        | ±5                         | ± 15                                        | ± 18                   | ±5                         | ± 15                                        | ± 18                  | ±5                         | ± 15                                        | ± 18                  | ±5                         | ±15                                         | ± 18                  | V<br>V<br>mA                                                       |

| TEMPERATURE RANGE Operating, Rated Performance Storage                                                                                            | 0<br>-65                   |                                             | + 70<br>+ 150          | 0<br>- 65                  |                                             | + 70<br>+ 150         | 0<br>-65                   |                                             | + 70<br>+ 150         | - 55<br>- 65               |                                             | + 125<br>+ 150        | °C<br>°C                                                           |

| PACKAGE OPTION <sup>1</sup> TO-99 Style (H-08B) J and S Grade Chips Also Available                                                                |                            | AD517JI                                     | н                      |                            | AD517K                                      | Н                     |                            | AD517L                                      | н                     |                            | AD517S                                      | н                     |                                                                    |

NOTES

For outline information see Package Information section.

Specifications subject to change without notice.

Specifications shown in boldface are tested on all production units at final electrical test. Results from those tests are used to calculate outgoing quality levels. All min and max specifications are guaranteed, although only those shown in boldface are tested on all production units.

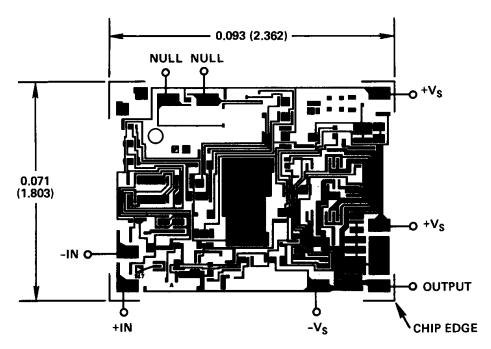

## **CHIP DIMENSIONS AND BONDING DIAGRAM**

Contact factory for latest dimensions. Dimensions shown in inches and (mm).

THE AD517 IS AVAILABLE IN LASER-TRIMMED CHIP FORM.

## **AD517**—Typical Performance Curves

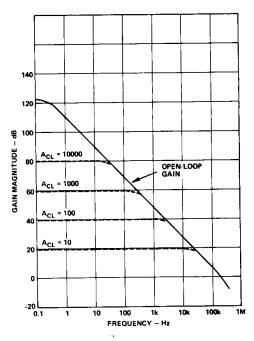

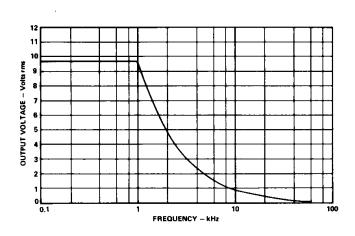

Small-Signal Gain vs. Frequency

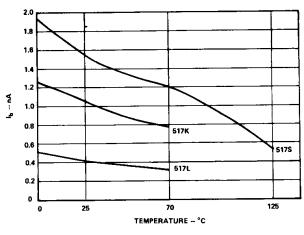

Input Bias Current vs. Temperature

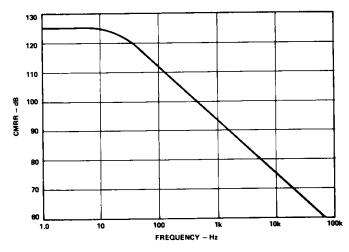

CMRR vs. Frequency

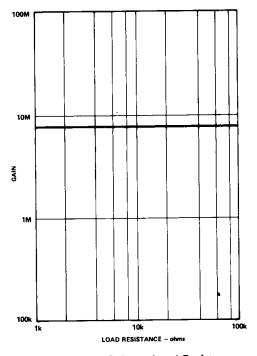

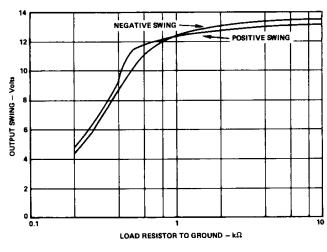

Open-Loop Gain vs. Load Resistance

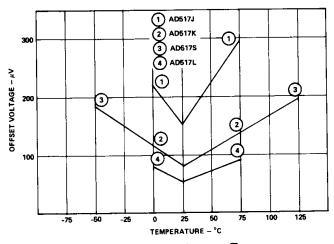

Untrimmed Offset Voltage vs. Temperature

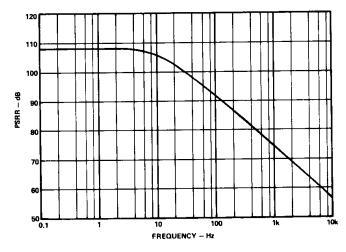

PSRR vs. Frequency

Maximum Undistorted Output vs. Frequency (Distortion ≤ 1%)

Output Voltage vs. Load Resistance

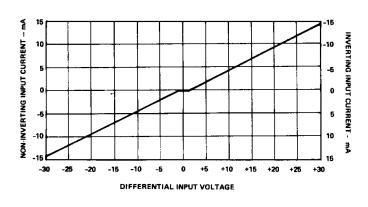

Input Current vs. Differential Input Voltage

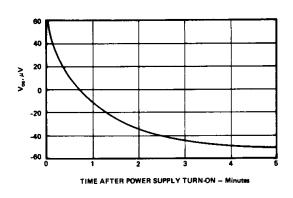

Warm-Up Offset Voltage Drift

Total Input Noise Voltage vs. Frequency

Low Frequency Voltage Noise (0.1 to 10Hz)

## **AD517**—Applications

### **NULLING THE AD517**

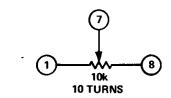

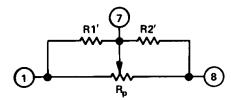

The internally-trimmed offset voltage of the AD517 will be low enough for most circuits without further nulling. However, in high precision applications, the AD517 may be nulled using either of the following methods:

Figure 1A shows a simple circuit using a  $10k\Omega$ , ten-turn potentiometer. This circuit allows nulling to within several microvolts.

The circuit of Figure 1B is recommended in applications where nulling to within  $1\mu V$  is desired. This circuit has the advantage that potentiometer instability effects are reduced by a factor of ten. Values of  $R_1$  and  $R_2$  are calculated as follows:

- 1. Null the offset to zero using a standard 10k pot, as shown in Figure 1A.

- 2. Measure pot halves R<sub>1</sub> and R<sub>2</sub>.

- 3. Calculate:

$$R_{1}' = \frac{R_{1} \times 50k\Omega}{50k\Omega - R_{1}}$$

$R_{2}' = \frac{R_{2} \times 50k\Omega}{50k\Omega - R_{2}}$

- 4. Replace the pot with R<sub>1</sub>' and R<sub>2</sub>' using the closest value 1% metal film resistors.

- 5. Use a 100k, ten-turn pot for R<sub>p</sub> to complete the nulling.

A. Simple

B. High Precision

Figure 1. Nulling Circuits

## AN INSTRUMENT INPUT AMPLIFIER USING THE AD517L

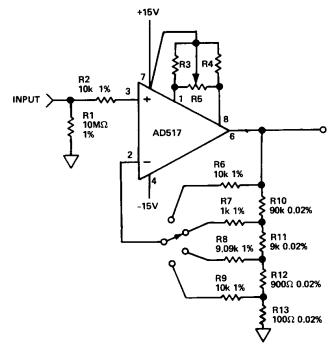

The circuit shown in Figure 2 represents a typical input stage for laboratory instruments and panel meters. The amplifier is non-inverting and offers selectable gains from 1 to 1000 in decade steps.

Input impedance of this amplifier is 10 megohms, determined by resistor  $R_1$ . The offset nulling network comprised of  $R_3$ ,  $R_4$  and  $R_5$  is the same one described earlier. If a less precise adjustment can be tolerated, a single 10k potentiometer can be substituted for  $R_3$ ,  $R_4$  and  $R_5$ .

Figure 2. Stable Instrument Input Amplifier

Gain switching is accomplished in the feedback network. The divider consisting of R<sub>10</sub>, R<sub>11</sub>, R<sub>12</sub> and R<sub>13</sub> determines the gain by dividing the output and returning it to the inverting input of the amplifier. The ratio tolerances of these resistors uniquely determine the gain of the amplifier. The impedance seen by the inverting input is held constant at 10k ohms by R<sub>6</sub>, R<sub>7</sub> R<sub>8</sub> or R<sub>9</sub> depending on the gain selected. Since input bias currents flow through equal resistances, the offset voltages produced will cancel each other. The input offset currents will produce an insignificant offset voltage on the order of 1 microvolt. If this offset is nulled out at the highest gain selected, it will be nulled on all ranges.

The AD517 offers excellent temperature stability in this circuit. Once the offset has been zeroed, the error produced by offset current drift will remain quite low due to the extremely low offset current drift of the AD517. A FET-input op amp would not work well in this application, since the input offset currents would double for each 10°C increase in temperature, soon exceeding the input offset currents of the AD517.