# **SIEMENS**

# 2.5-A High Performance Smart Power Stepper-Motor Driver with Diagnostic Interface

**TLE 5250**

SPT-IC

#### Overview

#### **Features**

- Single phase driver for stepper motor 2.5 A

- Low ON-resistance (typical 0.3 Ω)

- Wide supply range 6 V to 45 V

- Wide current range 10 mA to 3 A

- Fast nominal/actual comparator for micro stepper mode

- Wide temperature range

- Short circuit protection

- Under voltage shutdown

- Overtemperature shutdown

- Serial diagnostic interface

- Fast freewheeling diodes

- TTL-compatible inputs

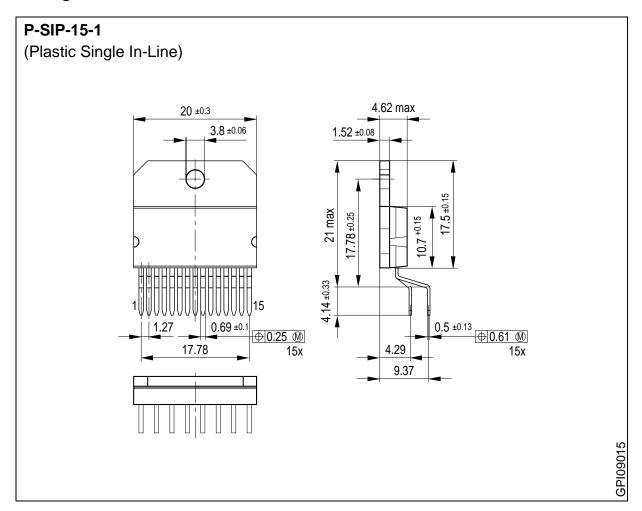

| Туре     | Ordering Code | Package    |

|----------|---------------|------------|

| TLE 5250 | Q67000-A9103  | P-SIP-15-1 |

#### **Description**

TLE 5250 is a monolithic IC in Smart Power technology for controlling and regulating the motor current in one phase of a bipolar stepping motor. There are other applications in driving DC motors and inductive loads that are operated on constant current.

The device has TTL-compatible logic inputs, includes a H-bridge with integrated, fast free-wheeling diodes plus dynamic limiting of the motor current by a chopper mode. The nominal current can be set continuously by a control voltage. Microstep mode can be produced by applying a sinusoidal control voltage. Two TLE 5250s, with a minimum of external circuitry and a single supply voltage, form a complete system - that can be driven direct by an MC- for two-phase, bipolar stepping motors with output current of up to 2.5 A per phase. The outputs of the IC are internally protected against shorted to ground, supply voltage and shorted load. The output stages are also disabled by undervoltage and overtemperature. All fault functions can be detected by the internal diagnostics, which can be read out serially.

SIEMENS TLE 5250

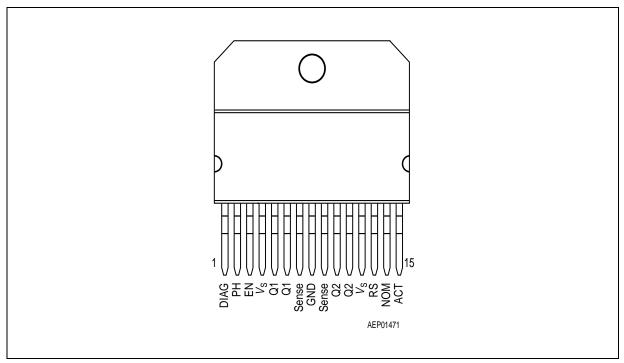

Figure 1 Pin Configuration (top view)

# **Pin Definitions and Functions**

| Pin No. | Symbol  | Function                                                                                                                              |

|---------|---------|---------------------------------------------------------------------------------------------------------------------------------------|

| 1       | DIAG    | Open-drain diagnostics output                                                                                                         |

| 2       | PH      | Input for determining source/sink on outputs Q1 and Q2; when Enable = Low, this pin serves as clock input for reading out diagnostics |

| 3       | EN      | Input for activating or turning off device (all output transistors turned off); Enable High = output active, Enable Low = diagnostics |

| 4, 12   | $V_{S}$ | Supply voltage of IC                                                                                                                  |

| 5, 6    | Q1      | Power output with integrated free-wheeling diodes                                                                                     |

| 7, 9    | Sense   | Actual-current output: shared, open-source output of sink transistors                                                                 |

| 8       | GND     | Ground                                                                                                                                |

| 10, 11  | Q2      | Power output with integrated free-wheeling diodes                                                                                     |

| 13      | RS      | Determines turning back on of sink transistor by internally driven, external RC element or external TTL trigger signal                |

| 14      | NOM     | Input for reference potential (nominal current) for nominal/actual comparator                                                         |

| 15      | ACT     | Input for actual current for nominal/actual comparator                                                                                |

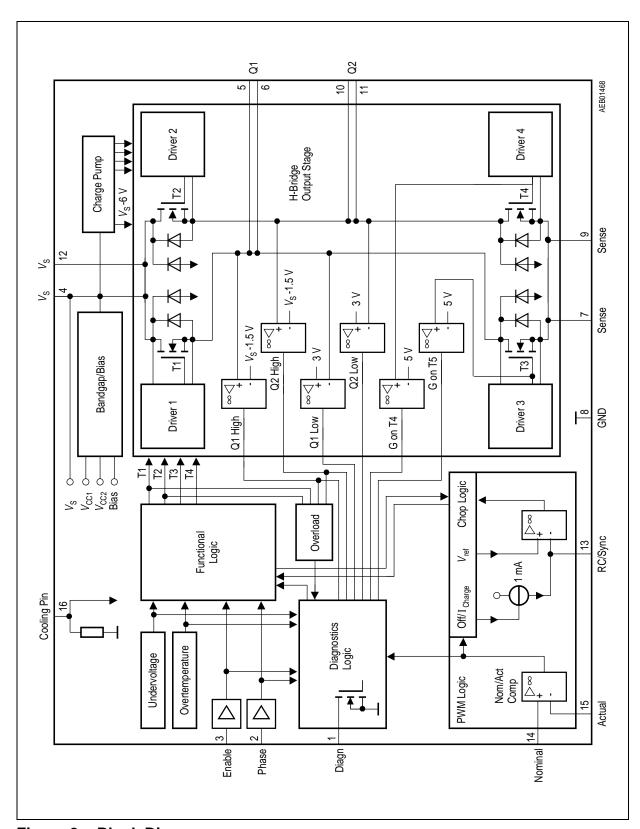

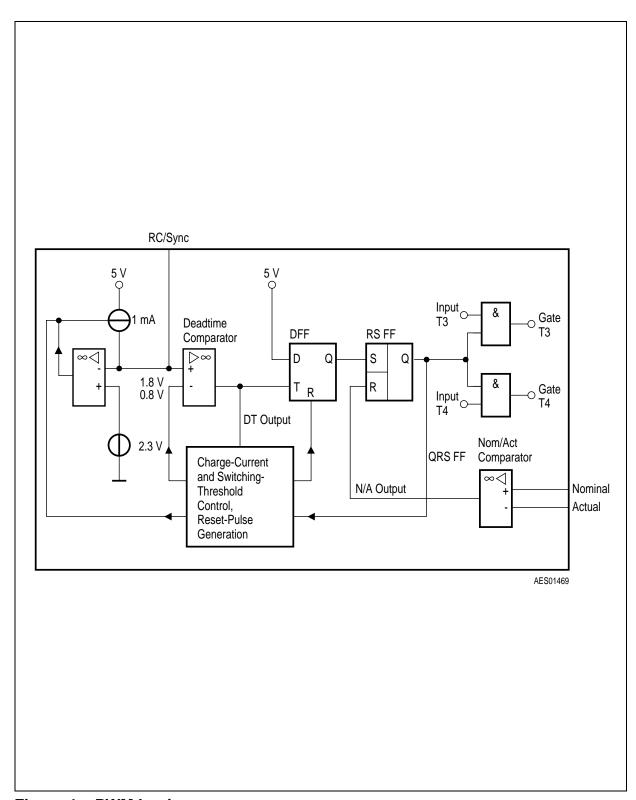

Figure 2 Block Diagram

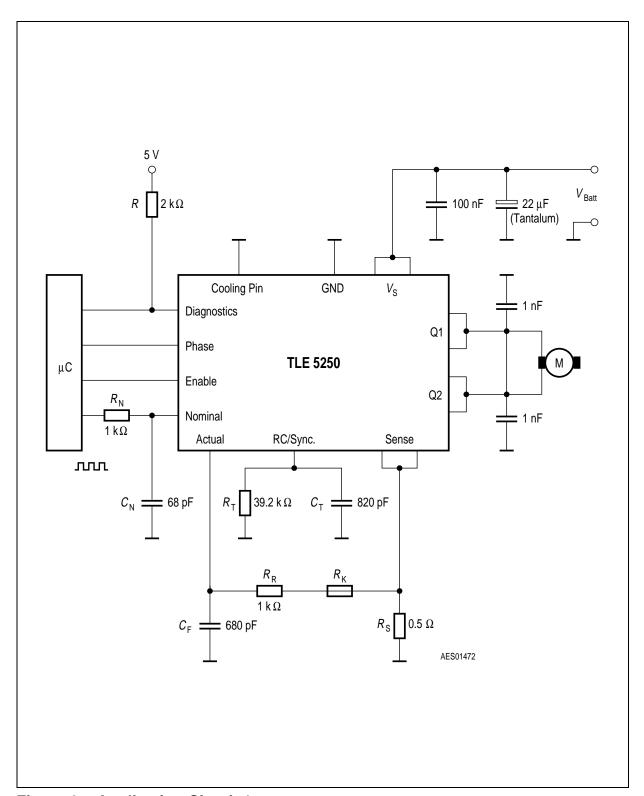

#### Application

Two TLE 5250 drivers are required to operate a bipolar stepping motor. To implement full-step operation, a squarewave voltage with the required stepping frequency is applied to the phase input of the upper driver, and the same squarewave voltage, but offset in phase by  $90^{\circ}$ el, to the phase input of the lower driver. Motor-current limiting is produced by a DC signal that is applied to both nominal-current inputs. In microstep operation the nominal current tracks sinusoidally and synchronously with the required stepping frequency. This produces a sinusoidal current in the motor windings to ensure very smooth running and a high stepping frequency. If an instantaneous nominal value (sine or cosine) is held on the second driver, it is possible to set a certain angle of rotation while the motor is stationary. The motor current produced by this depends on nominal voltage and sense resistance (normally  $0.5~\Omega$ ), i.e.

$$I_{\mathsf{M}}[\mathsf{V}] = \frac{V_{\mathsf{nom}}[\mathsf{V}]}{R_{\mathsf{S}}[\Omega]}$$

The actual voltage should be thoroughly filtered for precise current regulation, especially in microstep operation. So the actual input is accessible, and an RC element is necessary between the Sense output and Actual input. The resistance  $R_{\rm R}$  should correspond to the internal resistance of the nominal-current input-voltage source to prevent additional voltage offset on the nominal/actual comparator.

### **Circuit Description**

#### **Outputs**

Outputs Q1 and Q2 are fed by push-pull output stages. Four integrated free-wheeling diodes referred to ground or the supply voltage protect the integrated circuit against reverse voltages from an inductive load.

#### **Enable and Phase**

Outputs Q1 and Q2 can be disabled by a voltage  $V_{lnh}$  of  $\leq 0.8$  V on the Enable pin. The sink transistors are enabled by  $V_{lnh} \geq 2$  V.

The voltage on the Phase input determines the phase of the output current. Output Q1 acts as a sink for  $V_{Ph} \le 0.8 \text{ V}$  and as a source for  $V_{Ph} \ge 2 \text{ V}$ .

For output Q2 this is reversed: sink for  $V_{Ph} \ge 2 \text{ V}$  and source for  $V_{Ph} \le 0.8 \text{ V}$ .

The sink transistors are chopped. Low signal on the Enable pin plus a clock signal on the Phase pin enable readout of the multiplexer.

#### **Nominal-Current Input**

The peak current in the motor winding is defined by the voltage on the Nominal input. This is compared by a fast comparator to the voltage drop on the actual-current sensor. If the nominal current is exceeded, the sink transistors of the outputs are turned off by the logic.

## **RC/Sync Input**

The outputs are turned on by the signal applied to the RC input. Synchronization is possible by TTL signal or chopper mode with an external RC combination.

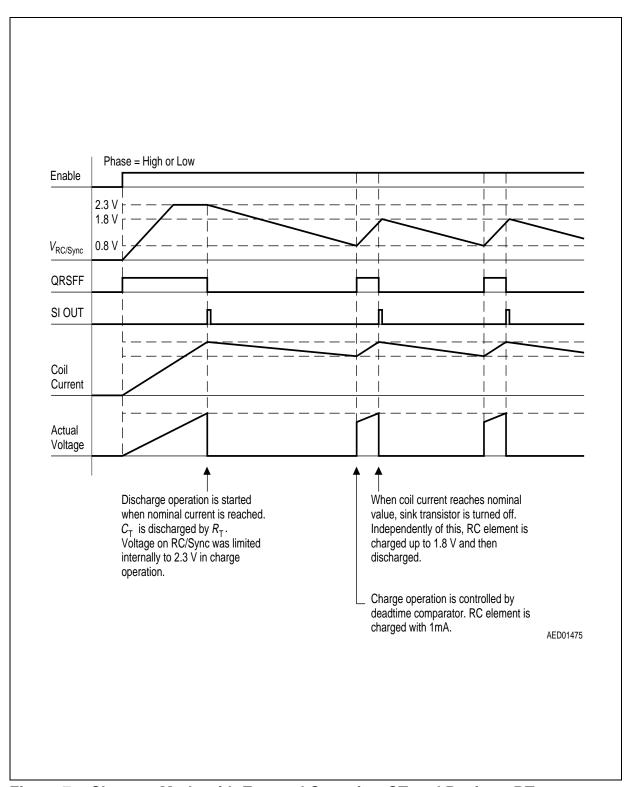

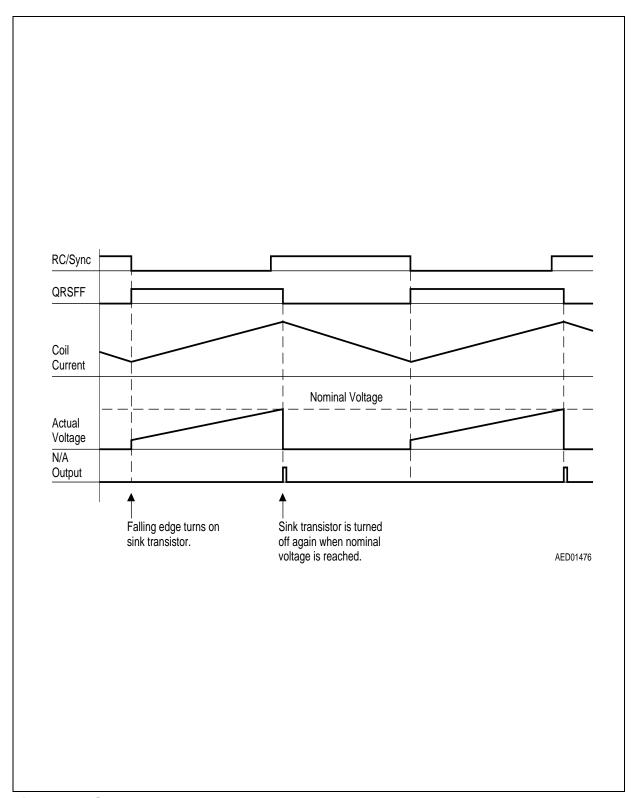

#### **Chopper Mode**

After the supply voltage is applied, capacitor CT is charged with constant current of 1 mA. A regulator limits the maximum voltage on the capacitor to 2.3 V. As a result of the rising current in the motor winding, the voltage on the actual sensor increases. Once the value defined by the nominal-current input is exceeded, the fast comparator resets an RS flipflop. Thus sink transistors T3 and T4 are turned off by the logic. The charge current is turned off and the parallel RT discharges CT.

The internal logic is designed so that capacitor CT is always charged before the discharge operation is triggered. This guarantees a constant charge time, even for very small coil currents (see **Figure 7**).

#### **Sync Operation**

If a sync signal with TTL level is applied to the RC input, the negative edge will set the RS flipflop - by way of the combined Schmitt trigger and monoflop - if the voltage on the current sensor is smaller than the nominal value on the nominal-current input. As in chopper mode, the appropriate output transistors conduct. They are again turned off by resetting the RS flipflop when the voltage on the current sensor becomes greater than the nominal value (see **Figure 8**).

#### **Output-Stage Control**

This part of the circuit handles turn-off of the output stages when the output is shorted to ground. There is separate current monitoring for this purpose in the source transistors. The temperature of the output stages is also monitored. If this exceeds 175 °C, all output stages are turned off, and then turned on again when the temperature drops. Undervoltage also causes turn-off of the transistors in the output stages. These possible fault states are stored in the diagnostics register.

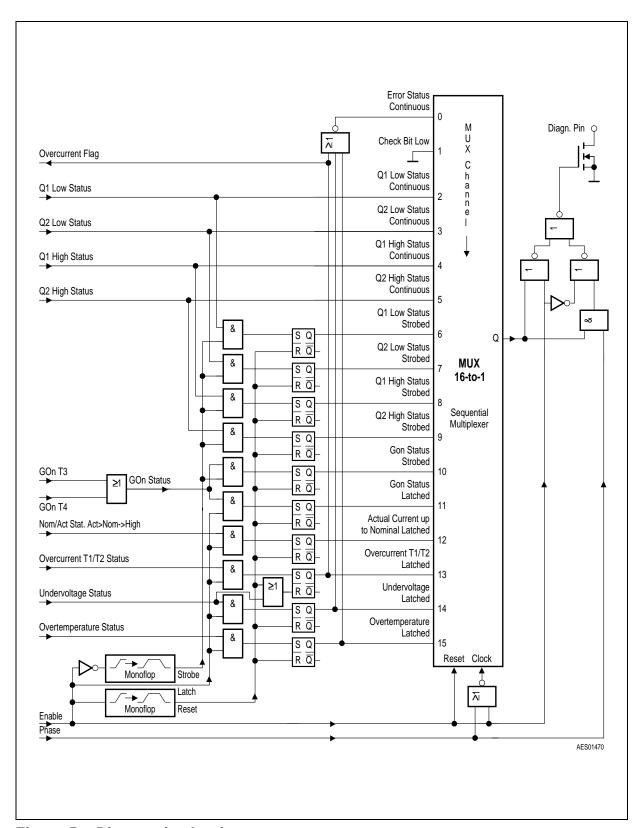

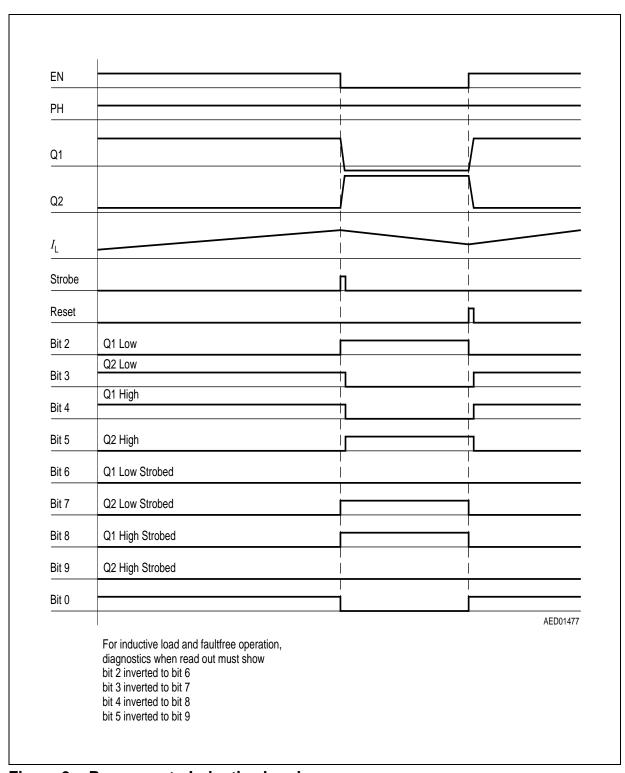

#### **Diagnostics**

The information from the different parts of the circuit is collected in the diagnostics and stored in the fault logic. The information is read out on the Diagnostics output (open collector).

The fault logic consists of a 16-bit multiplexer that switches information in three categories through to the Diagnostics output.

Bit 0 always appears inverted on DIAG when EN is High. This means that, if there is overcurrent on the upper transistor, undervoltage or overtemperature, it will be signaled immediately on the Diagnostics output. DIAG changes from High to Low.

Bit 1: check bit.

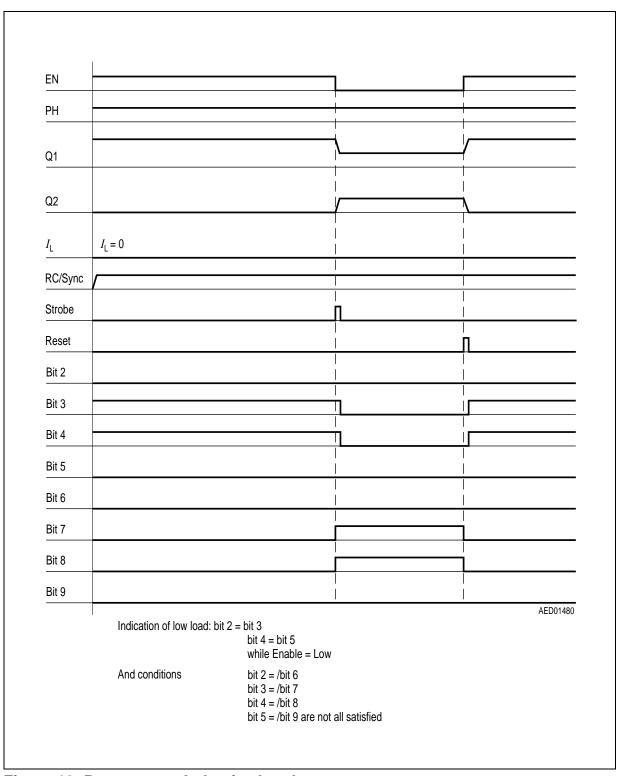

Bits 2, 3, 4 and 5 indicate the momentary status of the comparators on the two outputs (see **Figure 2**). Changes in the status of the comparators for output monitoring can be observed on DIAG when EN is Low and the counter of the multiplexer is on 2, 3, 4 or 5. This is necessary for detecting underload.

Bits 6, 7, 8, 9

The monoflop generates a short strobe signal when the EN edge changes from High to Low. The status of the comparators for output monitoring is stored with this signal and can be read out in bits 6, 7, 8 and 9.

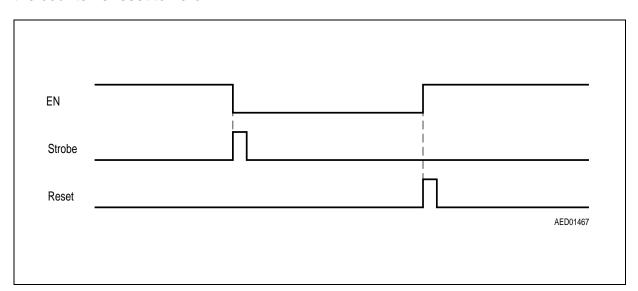

When Enable is Low, the Phase input is used as a clock input. As the edge rises, an internal counter is incremented and the corresponding channel of the multiplexer is switched through. As the edge falls, the signal is output inverted. When Enable is High, the counter is reset to zero.

Figure 3

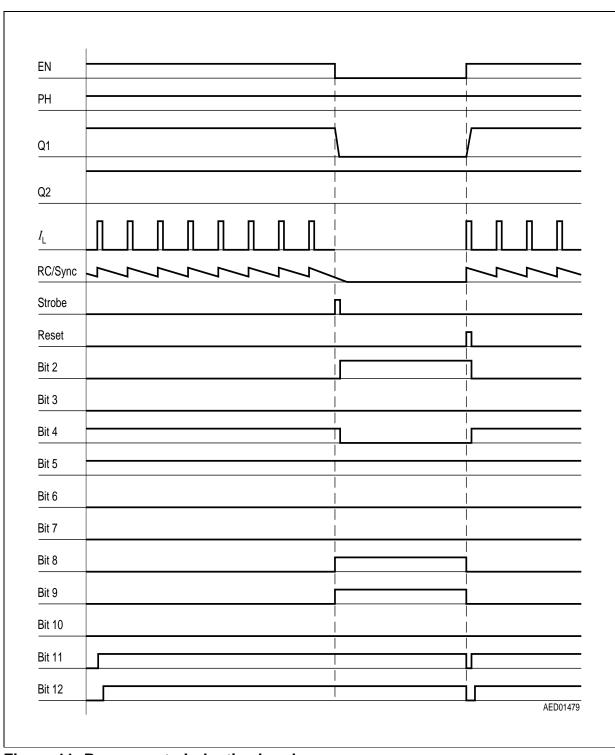

#### Bits 10, 11

With these bits it is possible to detect the status of the gate voltages of the lower outputstage transistors T3 and T4. Bit 10: status for EN edge transition. Bit 11: whether the lower transistor has at all been turned on.

Bit 12 indicates whether the nominal/actual comparator has switched. The comparator switches when the output current is regulated.

#### Bits 13, 14, 15

These bits indicate the presence of overcurrent, undervoltage or overtemperature. A fault is ORed and output direct by bit 0 on DI.

When the multiplexer is read out, bits 0 through 15 are output once non-inverted (Phase = Low) and once inverted (Phase = High).

#### **Bit Assignment in Error Register**

- Bit 0 = High for overtemperature/undervoltage/overcurrent

- Bit 1 = always High

- Bit 2 = High when sink transistor Q1 turned on

- Bit 3 = High when sink transistor Q2 turned on

- Bit 4 = High when source transistor Q1 turned on

- Bit 5 = High when source transistor Q2 turned on

- Bits 2-5 = momentary states for readout

- Bit 6 = bit 2 state for falling edge of Enable signal

- Bit 7 = bit 3 state for falling edge of Enable signal

- Bit 8 = bit 4 state for falling edge of Enable signal

- Bit 9 = bit 5 state for falling edge of Enable signal

- Bits 6-10 represent status of outputs for negative change in edge of Enable signal

- Bit 11 = High if gate-source voltage of sink transistors is > 5 V at moment of readout

- Bits 11-15 are set if event occurs during switching (Enable = High)

- Bit 11 = High if sink transistor  $V_{GS} > 5 \text{ V}$

- Bit 12 = High if actual current lower than nominal current

- Bit 13 = High if overcurrent detected on source transistors

- Bit 14 = High if undervoltage detected

- Bit 15 = High if thermal link tripped

The memories are erased by a rising edge on the Enable input.

# **Logic Assignment: Control Inputs, Output Transistors**

| Enable                                                  | L           | L           | Н                | Н                |

|---------------------------------------------------------|-------------|-------------|------------------|------------------|

| Phase                                                   | L           | Н           | L                | Н                |

| Output Q1                                               | /           | /           | L                | Н                |

| Output Q2                                               | /           | /           | Н                | L                |

| Transistor T1 Transistor T2 Transistor T3 Transistor T4 | X<br>X<br>X | X<br>X<br>X | X<br>-<br>-<br>X | -<br>X<br>X<br>- |

L = Low voltage level, input open

H = High voltage levelX = transistor turned off- = transistor conducting

transistor conducting, switched in current limiting

/ = output high-impedance

Figure 4 PWM Logic

Figure 5 Diagnostics Logic

# **Absolute Maximum Ratings**

$T_{\rm J}$  = - 40 to 150  $^{\circ}$ C

| Parameter                | Symbol  | Lir   | Unit |   |

|--------------------------|---------|-------|------|---|

|                          |         | min.  | max. |   |

| Supply voltage           | $V_{S}$ | - 0.3 | 45   | V |

| Supply current           | $I_{S}$ | 0     | 3    | А |

| Peak currents on outputs | $I_{Q}$ | - 3   | 3    | А |

#### **Diode Forward Currents**

| Diode to + $V_{\rm S}$               | $I_{FH}$         | _     | 3   | Α  |

|--------------------------------------|------------------|-------|-----|----|

| Diode to sense                       | $I_{FL}$         | _     | 3   | Α  |

| Output current on actual-current pin | I <sub>Act</sub> | -     | 3   | А  |

| Voltage on actual-current pin        | $V_{Act}$        | - 0.3 | 5   | V  |

| Ground current, pin 6                | $I_{GND}$        | _     | 3   | А  |

| Chip temperature                     | $T_{C}$          | - 40  | 150 | °C |

| Storage temperature                  | $T_{stg}$        | _     | 125 | °C |

#### **Thermal Resistances**

| Junction to ambient | $R_{thjA}$ | _ | 70 | K/W |

|---------------------|------------|---|----|-----|

| Junction case       | $R_{thjC}$ | _ | 3  | K/W |

# **Operating Range**

| Supply voltage                          | $V_{S}$   | 6           | 40  | V  |

|-----------------------------------------|-----------|-------------|-----|----|

| Input voltage<br>Enable, Phase, RC/Sync | $V_{I}$   | - 0.3       | 5.5 | V  |

| Voltage on nominal pin                  | $V_{NOM}$ | - 0.3       | 2   | V  |

| Voltage on actual pin                   | $V_{ACT}$ | _           | 2   | V  |

| Output current Q1, Q2                   | $I_{Q}$   | - 2.5       | 2.5 | А  |

| Junction temperature                    | $T_{J}$   | <b>- 40</b> | 150 | °C |

# **Enable and Phase Inputs**

| H input voltage | $V_{IH}$ | 2 | _   | ٧ |

|-----------------|----------|---|-----|---|

| L input voltage | $V_{IL}$ | _ | 0.8 | V |

# **Characteristics**

$V_{\rm S}$  = 6 to 25 V;  $T_{\rm J}$   $\leq$  150 °C

| Parameter      | Symbol  | Limit Values |      |      | Unit | Test Condition |

|----------------|---------|--------------|------|------|------|----------------|

|                |         | min.         | typ. | max. |      |                |

| Supply current | $I_{S}$ | _            | _    | 11   | mΑ   | Enable = High  |

# Output Q1, Q2

| Turn-on resistance of output transistors           | $R_{DS\;ON}$ | 0.3 | _  | 0.5 | Ω  | <i>I</i> = 2.5 A, 150 °C       |

|----------------------------------------------------|--------------|-----|----|-----|----|--------------------------------|

| Phase deadtime                                     | $t_{D}$      | _   | 10 | _   | μs | _                              |

| Diode forward voltage output to + $V_{\rm S}$      | $V_{\sf FQ}$ | _   | _  | 1.5 | V  | <i>I</i> <sub>FH</sub> = 2.5 V |

| Diode forward voltage actual-current pin to output | _            | _   | _  | 1.5 | V  | I <sub>FH</sub> = 2.5 V        |

## **Nominal Current**

| Input current                                      | $I_{18}$     | 0   | 1 | 2 | μΑ | _ |

|----------------------------------------------------|--------------|-----|---|---|----|---|

| Offset voltage measured for 0 V actual/nominal pin | $V_{I(8-4)}$ | - 4 | _ | 8 | mV | _ |

#### **Actual Current**

| Turn-off delay of nom/act comparator | $t_{\sf d}$ | _          | _ | 0.5 | μs | _ |

|--------------------------------------|-------------|------------|---|-----|----|---|

| Common-mode error                    | $V_{Comm}$  | <b>-</b> 5 | _ | 10  | mV | _ |

# RC/Sync

| Sync frequency                | f                 | _          | 20     | 100 | kHz    | _                                       |

|-------------------------------|-------------------|------------|--------|-----|--------|-----------------------------------------|

| Trigger threshold lower upper | $V_{tL} \ V_{tH}$ | 0.8<br>1.7 | _<br>_ | 1 2 | V<br>V | _<br>_                                  |

| Maximum charge voltage        | $V_{Chm}$         | 2.2        | 2.3    | 2.4 | V      | $R = 39 \text{ k}\Omega$<br>C = 820  pF |

# Characteristics (cont'd)

| Parameter                                                | Symbol           | Limit Values |      |          | Unit | <b>Test Condition</b>            |

|----------------------------------------------------------|------------------|--------------|------|----------|------|----------------------------------|

|                                                          |                  | min.         | typ. | max.     |      |                                  |

| Undervoltage Cutout                                      |                  |              |      |          |      |                                  |

| Disable                                                  | $V_{UDIAG}$      | 4            | _    | <u> </u> | V    | _                                |

| Enable                                                   | $V_{UEN}$        | _            | _    | 5.3      | V    | _                                |

| Hysteresis                                               | $V_{UH}$         | _            | _    | 400      | mV   | _                                |

| Diagnostics Output  Activating delay (Enable High → Low) | $t_{def}$        | _            | _    | 400      | ns   | _                                |

| Delay phase low to high                                  | t <sub>ddr</sub> | _            | _    | 500      | ns   | Enable = Low $V_{\rm S}$ > 5.5 V |

| Delay phase high to low                                  | t <sub>ddf</sub> | _            | _    | 450      | ns   | Enable = Low $V_{\rm S}$ > 5.5 V |

| Output voltage low                                       | $V_{Diag}$       | _            | _    | 0.4      | V    | $I_{\rm QL}$ = 5 mA              |

| Leakage current high                                     | $I_{Diag}$       | _            | _    | 10       | μΑ   | $V_{\text{OH}} = 5 \text{ V}$    |

Figure 6 Application Circuit 1

SIEMENS TLE 5250

Figure 7 Chopper Mode with External Capacitor CT and Resistor RT

Figure 8 Synchron Mode

Figure 9 Response to Inductive Loads a) Normal Operation (no current regulation)

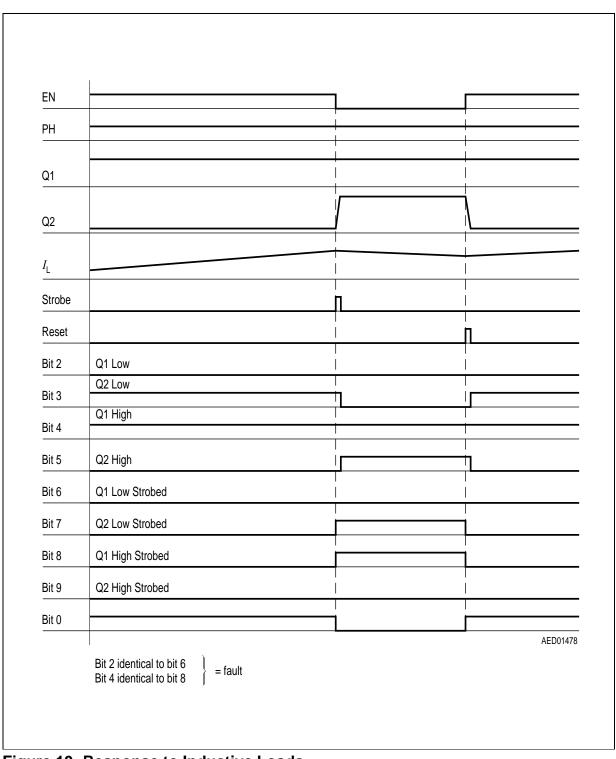

Figure 10 Response to Inductive Loads b) Q1 Shorted to +  $V_{\rm S}$  (Phase = High)

Figure 11 Response to Inductive Loads c) Q2 Shorted to +  $V_{\rm S}$  (Phase = High)

Figure 12 Response to Inductive Loads d) Low Load

## **Package Outlines**

#### **Sorts of Packing**

Package outlines for tubes, trays etc. are contained in our Data Book "Package Information".

Dimensions in mm