## Multi-Channel Digital Audio Decoders

#### • CS4923/4/5/6/7/8 features

- Optional Virtual 3D Output

- Simulated Surround and Programmable Effects

- Real Time Autodetection of Dolby Digital<sup>®</sup>, DTS<sup>®</sup>, MPEG Multi-Channel and PCM

- Flexible 6-channel master or slave output

- CS4923/4/5/6/7/8/9 features

- IEC60958/61937 transmitter for compresseddata or linear-PCM output

- Dedicated 8 kilobyte input buffer

- DAC clock via analog phase-locked loop

- Dedicated byte wide or serial host interface

- Multiple compressed data input modes

- PES layer decode for A/V synchronization

- 96-kHz-capable PCM I/O, master or slave

- Optional external memory and auto-boot

- +3.3-V CMOS low-power, 44-pin package

- CS4923/4/5/6 features

- Capable of Dolby Digital<sup>®</sup> Group A Performance

- Dolby bass manager and crossover filters

- Dolby Surround Pro Logic<sup>®</sup> Decoding

- CS4925/7: MPEG-2 Multi-Channel Decoder

- CS4926/8: DTS Multi-Channel Decoder

- CS4929: AAC 2-Channel (Low Complexity) and MPEG-2 Stereo Decoder

#### Description

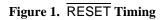

The CS4923/4/5/6/7/8 is a family of multi-channel digital audio decoders, with the exception of the CS4929 as the only stereo digital audio decoder. The CS4923/4/5/6 are designed for Dolby Digital and MPEG-2 Stereo decoding. In addition the CS4925 adds MPEG-2 multi-channel decoding capability and the CS4926 provides DTS decoding. The CS4927 is an MPEG-2 multi-channel decoder and the CS4928 is a DTS multi-channel decoder. The CS4929 is an AAC 2-channel and MPEG-2 stereo decoder. Each one of the CS4923/4/5/6/7/8/9 provides a complete and flexible solution for multi-channel (or stereo in the case of the CS4929) audio decoding in home A/V receiver/amplifiers, DVD movie players, out-board decoders, laser-disc players, HDTV sets, head-end decoders, set-top boxes, and similar products.

Cirrus Logic's Crystal Audio Division provides a complete set of audio decoder and auxiliary audio DSP application programs for various applications. For all complementary analog and digital audio I/O, Crystal Audio also provides a complete set of high-quality audio peripherals including: multimedia CODECs, stereo A/D and D/A converters and IEC60958 interfaces. Of special note, the CS4226 is a complementary CODEC providing a digital receiver, stereo A/D converters, and six 20-bit DACs in one package.

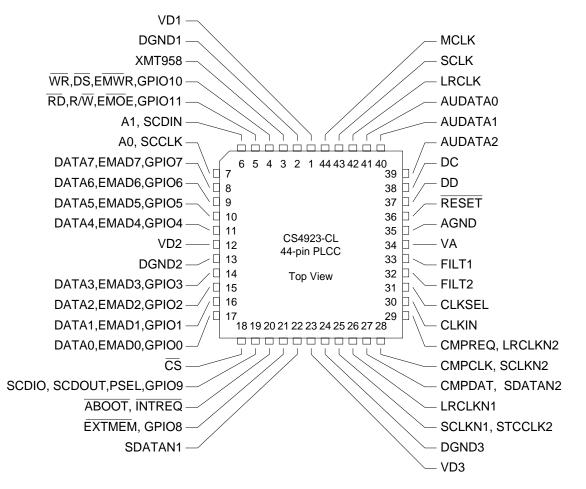

#### **ORDERING INFORMATION**

| CS4923xx-CL | 44-pin PLCC ( $xx = ROM$ revision) |

|-------------|------------------------------------|

| CRD4923     | Reference design with CS4226       |

| CDB4923     | Evaluation board                   |

Preliminary Product Information

This document contains information for a new product. Cirrus Logic reserves the right to modify this product without notice.

CIRRUS LOGIC® P.O. Box 17847, Austin, Texas 78760 (512) 445 7222 FAX: (512) 445 7581 http://www.cirrus.com

Copyright © Cirrus Logic, Inc. 1999 (All Rights Reserved)

#### **TABLE OF CONTENTS**

| 1. | CHARACTERISTICS AND SPECIFICATIONS                      |    |

|----|---------------------------------------------------------|----|

|    | ABSOLUTE MAXIMUM RATINGS                                | 4  |

|    | RECOMMENDED OPERATING CONDITIONS                        | 4  |

|    | DIGITAL D.C. CHARACTERISTICS                            | 4  |

|    | POWER SUPPLY CHARACTERISTICS                            | 4  |

|    | SWITCHING CHARACTERISTICS—RESET                         |    |

|    | SWITCHING CHARACTERISTICS—CMPDAT, CMPCLK                |    |

|    | SWITCHING CHARACTERISTICS—CLKIN                         | 7  |

|    | SWITCHING CHARACTERISTICS-INTEL® HOST MODE              | 8  |

|    | SWITCHING CHARACTERISTICS-MOTOROLA® HOST MODE           | 10 |

|    | SWITCHING CHARACTERISTICS—DIGITAL AUDIO INPUT           | 16 |

|    | SWITCHING CHARACTERISTICS—DIGITAL AUDIO OUTPUT          |    |

| 2. | FAMILY OVERVIEW                                         | 20 |

|    | 2.1 Multi-channel Decoder Family of Parts               |    |

|    | 2.2 Document Strategy                                   |    |

|    | 2.2.1 Hardware Documentation                            | 22 |

|    | 2.2.2 CS4923/4/5/6/7/8/9 Application Code User's Guides | 22 |

|    | 2.3 Using the CS4923/4/5/6/7/8/9                        | 22 |

| 3. | TYPICAL CONNECTION DIAGRAMS                             |    |

|    | 3.1 Multiplexed Pins                                    |    |

|    | 3.2 Termination Requirements                            |    |

|    | 3.3 Phase Locked Loop Filter                            |    |

| 4. | POWER                                                   |    |

|    | 4.1 Decoupling                                          | 31 |

|    | 4.2 Analog Power Conditioning                           | 31 |

| _  | 4.3 Pads                                                |    |

| 5. | CLOCKING                                                |    |

| 6. | CONTROL                                                 |    |

|    | 6.1 Boot and Control Mode Overview                      |    |

|    | 6.2 Parallel Host Interface                             |    |

|    | 6.2.1 Intel Parallel Host Mode                          |    |

|    | 6.2.2 Motorola Parallel Host Mode                       |    |

|    | 6.3 SPI Serial Host Interface                           |    |

|    | 6.3.1 SPI Write                                         |    |

|    | 6.3.2 SPI Read                                          | 37 |

|    |                                                         |    |

#### Contacting Cirrus Logic Support

For a complete listing of Direct Sales, Distributor, and Sales Representative contacts, visit the Cirrus Logic web site at: http://www.cirrus.com/corporate/contacts/

Dolby, Dolby Digital, and Pro Logic are registered trademarks of Dolby Laboratories Licensing Corporation.

Intel is a registered trademark of Intel Corporation.

Motorola is a registered trademark of Motorola, Inc.

I<sup>2</sup>C is a registered trademark of Philips Semiconductor.

All other names are trademarks, registered trademarks, or service marks of their respective companies.

Preliminary product information describes products which are in production, but for which full characterization data is not yet available. Advance product information describes products which are in development and subject to development changes. Cirrus Logic, Inc. has made best efforts to ensure that the information contained in this document is accurate and reliable. However, the information is subject to change without notice and is provided "AS IS" without warranty of any kind (express or implied). No responsibility is assumed by Cirrus Logic, Inc. for the use of this information, nor for infringements of patents or other rights of third parties. This document is the property of Cirrus Logic, Inc. and implies no license under patents, copyrights, trademarks, or trade secrets. No part of this publication may be copied, reproduced, stored in a retrieval system, or transmitted, in any form or by any means (electronic, mechanical, photographic, or otherwise) without the prior written consent of Cirrus Logic, Inc. Terms from any Cirrus Logic website or disk may be printed for use by the user. However, and part of the printout or electronic files may be copied, reproduced, stored in a retrieval system, or transmitted, in any form or by any means (electronic, mechanical, photographic, or otherwise) without the prior written consent of Cirrus Logic, Inc. Furthermore, no part of this publication may be used as a basis for manufacture or sale of any items without the prior written consent of Cirrus Logic, Inc. The names of products of Cirrus Logic, Inc. or other vendors and suppliers appearing in this document may be trademarks or service marks of their respective owners which may be registered in some jurisdictions. A list of Cirrus Logic, Inc. trademarks and service marks can be found at http://www.cirrus.com.

|    | 6.4 I <sup>2</sup> C Serial Host Interface | . 39 |

|----|--------------------------------------------|------|

|    | 6.4.1 I <sup>2</sup> C Write               | . 39 |

|    | 6.4.2 I <sup>2</sup> C Read                | . 39 |

|    | 6.5 External Memory                        |      |

|    | 6.5.1 External Memory and Autoboot         | . 43 |

| 7. | DIGITAL INPUT & OUTPUT                     | . 44 |

|    | 7.1 Digital Audio Formats                  | . 44 |

|    | 7.2 Digital Audio Input Port               | . 46 |

|    | 7.3 Compressed Data Input Port             | . 46 |

|    | 7.4 Parallel Digital Audio Data Input      | . 46 |

|    | 7.5 Digital Audio Output Port              | . 47 |

|    | 7.5.1 IEC60958 Output                      |      |

| 8. | PIN DESCRIPTIONS                           |      |

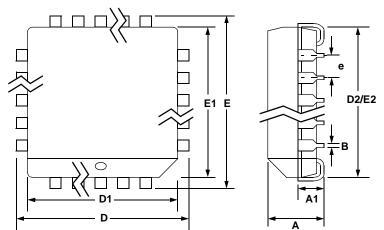

| 9. | PACKAGE DIMENSIONS                         | . 54 |

### LIST OF FIGURES

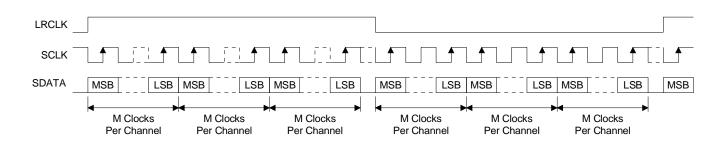

| Figure 2. Serial Compressed Data Timing6Figure 3. CLKIN with CLKSEL = VSS = PLL Enable.7Figure 4. CLKIN with CLKSEL = VD = PLL Bypass7Figure 5. Intel Parallel Host Mode Read Cycle.9Figure 6. Intel Parallel Host Mode Write Cycle.9Figure 7. Motorola Parallel Host Mode Read Cycle11Figure 9. SPI Control Port Timing.13Figure 10. I <sup>2</sup> C Control Port Timing13Figure 11. Digital Audio Input, Data and Clock Timing.17Figure 12. Digital Audio Output, Data and Clock Timing.19Figure 13. I <sup>2</sup> C Control.26Figure 14. I <sup>2</sup> C Control with External Memory26Figure 15. SPI Control with External Memory28Figure 17. Intel Parallel Control Mode29Figure 18. Motorola Parallel Control Mode20Figure 20. I <sup>2</sup> C Timing38Figure 21. External Memory Interface40Figure 22. Run-Time Memory Access42Figure 23. Autoboot Timing Diagram.43Figure 24. I <sup>2</sup> S Format45Figure 26. Right Justified Format.45Figure 27. Multi-Channel Format (M == 20)45 | Figure 1. RESET Timing                                   | 5  |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------|----|

| Figure 3. CLKIN with CLKSEL = VSS = PLL Enable.7Figure 4. CLKIN with CLKSEL = VD = PLL Bypass7Figure 5. Intel Parallel Host Mode Read Cycle.9Figure 6. Intel Parallel Host Mode Read Cycle9Figure 7. Motorola Parallel Host Mode Read Cycle11Figure 8. Motorola Parallel Host Mode Write Cycle11Figure 9. SPI Control Port Timing13Figure 10. I <sup>2</sup> C Control Port Timing15Figure 11. Digital Audio Input, Data and Clock Timing17Figure 12. Digital Audio Output, Data and Clock Timing19Figure 13. I <sup>2</sup> C Control with External Memory25Figure 14. I <sup>2</sup> C Control with External Memory26Figure 15. SPI Control with External Memory28Figure 16. SPI Control with External Memory28Figure 17. Intel Parallel Control Mode30Figure 21. External Memory Interface40Figure 21. External Memory Access42Figure 23. Autoboot Timing Diagram43Figure 24. I <sup>2</sup> S Format45Figure 26. Right Justified Format45Figure 26. Right Justified Format45                   | Figure 2. Serial Compressed Data Timing                  | 6  |

| Figure 4. CLKIN with CLKSEL = VD = PLL Bypass7Figure 5. Intel Parallel Host Mode Read Cycle9Figure 6. Intel Parallel Host Mode Read Cycle9Figure 7. Motorola Parallel Host Mode Read Cycle11Figure 8. Motorola Parallel Host Mode Write Cycle11Figure 9. SPI Control Port Timing13Figure 10. I <sup>2</sup> C Control Port Timing15Figure 11. Digital Audio Input, Data and Clock Timing17Figure 12. Digital Audio Output, Data and Clock Timing19Figure 13. I <sup>2</sup> C Control25Figure 14. I <sup>2</sup> C Control26Figure 15. SPI Control27Figure 16. SPI Control with External Memory28Figure 17. Intel Parallel Control Mode29Figure 19. SPI Timing30Figure 20. I <sup>2</sup> C Timing40Figure 21. External Memory Interface42Figure 23. Autoboot Timing Diagram43Figure 24. I <sup>2</sup> S Format45Figure 25. Left Justified Format45Figure 26. Right Justified45                                                                                                                   | Figure 3. CLKIN with CLKSEL = VSS = PLL Enable           | 7  |

| Figure 5. Intel Parallel Host Mode Read Cycle9Figure 6. Intel Parallel Host Mode Write Cycle9Figure 7. Motorola Parallel Host Mode Read Cycle11Figure 8. Motorola Parallel Host Mode Write Cycle11Figure 9. SPI Control Port Timing13Figure 10. I <sup>2</sup> C Control Port Timing17Figure 11. Digital Audio Input, Data and Clock Timing17Figure 12. Digital Audio Output, Data and Clock Timing19Figure 13. I <sup>2</sup> C Control25Figure 14. I <sup>2</sup> C Control with External Memory26Figure 15. SPI Control with External Memory26Figure 16. SPI Control with External Memory28Figure 17. Intel Parallel Control Mode30Figure 19. SPI Timing38Figure 20. I <sup>2</sup> C Timing40Figure 21. External Memory Interface42Figure 23. Autoboot Timing Diagram43Figure 24. I <sup>2</sup> S Format45Figure 25. Left Justified Format45Figure 26. Right Justified45                                                                                                                      | Figure 4. CLKIN with CLKSEL = VD = PLL Bypass            | 7  |

| Figure 6. Intel Parallel Host Mode Write Cycle9Figure 7. Motorola Parallel Host Mode Read Cycle11Figure 8. Motorola Parallel Host Mode Write Cycle11Figure 9. SPI Control Port Timing13Figure 10. I²C Control Port Timing15Figure 11. Digital Audio Input, Data and Clock Timing17Figure 12. Digital Audio Output, Data and Clock Timing19Figure 13. I²C Control25Figure 14. I²C Control with External Memory26Figure 15. SPI Control with External Memory26Figure 16. SPI Control Mode27Figure 17. Intel Parallel Control Mode28Figure 19. SPI Timing30Figure 20. I²C Timing40Figure 21. External Memory Interface42Figure 22. Run-Time Memory Access42Figure 23. Autoboot Timing Diagram43Figure 24. I²S Format45Figure 25. Left Justified45Figure 26. Right Justified45                                                                                                                                                                                                                         | Figure 5. Intel Parallel Host Mode Read Cycle            | 9  |

| Figure 7. Motorola Parallel Host Mode Read Cycle11Figure 8. Motorola Parallel Host Mode Write Cycle11Figure 9. SPI Control Port Timing13Figure 10. I²C Control Port Timing15Figure 11. Digital Audio Input, Data and Clock Timing17Figure 12. Digital Audio Output, Data and Clock Timing19Figure 13. I²C Control25Figure 14. I²C Control with External Memory26Figure 15. SPI Control27Figure 16. SPI Control with External Memory28Figure 17. Intel Parallel Control Mode29Figure 19. SPI Timing38Figure 20. I²C Timing40Figure 21. External Memory Interface42Figure 23. Autoboot Timing Diagram43Figure 24. I²S Format45Figure 25. Left Justified Format45Figure 26. Right Justified45                                                                                                                                                                                                                                                                                                         | Figure 6. Intel Parallel Host Mode Write Cycle           | 9  |

| Figure 8. Motorola Parallel Host Mode Write Cycle.11Figure 9. SPI Control Port Timing.13Figure 10. I²C Control Port Timing.15Figure 11. Digital Audio Input, Data and Clock Timing.17Figure 12. Digital Audio Output, Data and Clock Timing.19Figure 13. I²C Control.25Figure 14. I²C Control with External Memory.26Figure 15. SPI Control27Figure 16. SPI Control with External Memory.28Figure 17. Intel Parallel Control Mode.29Figure 19. SPI Timing.38Figure 20. I²C Timing40Figure 21. External Memory Interface42Figure 23. Autoboot Timing Diagram.43Figure 24. I²S Format.45Figure 25. Left Justified Format.45Figure 26. Right Justified.45                                                                                                                                                                                                                                                                                                                                             | Figure 7. Motorola Parallel Host Mode Read Cycle         | 11 |

| Figure 9. SPI Control Port Timing.13Figure 10. I²C Control Port Timing15Figure 11. Digital Audio Input, Data and Clock Timing.17Figure 12. Digital Audio Output, Data and Clock Timing19Figure 13. I²C Control.25Figure 14. I²C Control with External Memory26Figure 15. SPI Control.27Figure 16. SPI Control with External Memory28Figure 17. Intel Parallel Control Mode29Figure 18. Motorola Parallel Control Mode30Figure 20. I²C Timing38Figure 21. External Memory Interface42Figure 23. Autoboot Timing Diagram43Figure 24. I²S Format45Figure 25. Left Justified Format45                                                                                                                                                                                                                                                                                                                                                                                                                  | Figure 8. Motorola Parallel Host Mode Write Cýcle        | 11 |

| Figure 10. I²C Control Port Timing15Figure 11. Digital Audio Input, Data and Clock Timing17Figure 12. Digital Audio Output, Data and Clock Timing19Figure 13. I²C Control25Figure 14. I²C Control with External Memory26Figure 15. SPI Control27Figure 16. SPI Control with External Memory28Figure 17. Intel Parallel Control Mode29Figure 18. Motorola Parallel Control Mode30Figure 20. I²C Timing38Figure 21. External Memory Interface42Figure 23. Autoboot Timing Diagram43Figure 24. I²S Format45Figure 25. Left Justified Format45Figure 26. Right Justified45                                                                                                                                                                                                                                                                                                                                                                                                                             | Figure 9. SPI Control Port Timing                        |    |

| Figure 11. Digital Audio Input, Data and Clock Timing.17Figure 12. Digital Audio Output, Data and Clock Timing.19Figure 13. I <sup>2</sup> C Control.25Figure 14. I <sup>2</sup> C Control with External Memory.26Figure 15. SPI Control.27Figure 16. SPI Control with External Memory.28Figure 17. Intel Parallel Control Mode.29Figure 18. Motorola Parallel Control Mode.30Figure 20. I <sup>2</sup> C Timing.38Figure 21. External Memory Interface.42Figure 23. Autoboot Timing Diagram.43Figure 24. I <sup>2</sup> S Format.45Figure 25. Left Justified Format.45Figure 26. Right Justified.45                                                                                                                                                                                                                                                                                                                                                                                               | Figure 10. I <sup>2</sup> C Control Port Timing          |    |

| Figure 12. Digital Audio Output, Data and Clock Timing19Figure 13. I <sup>2</sup> C Control25Figure 14. I <sup>2</sup> C Control with External Memory26Figure 15. SPI Control27Figure 16. SPI Control with External Memory28Figure 17. Intel Parallel Control Mode29Figure 18. Motorola Parallel Control Mode30Figure 20. I <sup>2</sup> C Timing38Figure 21. External Memory Interface42Figure 23. Autoboot Timing Diagram43Figure 24. I <sup>2</sup> S Format45Figure 25. Left Justified Format45Figure 26. Right Justified45                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | Figure 11, Digital Audio Input, Data and Clock Timing    |    |

| Figure 13. I <sup>2</sup> C Control.25Figure 14. I <sup>2</sup> C Control with External Memory.26Figure 15. SPI Control.27Figure 16. SPI Control with External Memory.28Figure 17. Intel Parallel Control Mode.29Figure 18. Motorola Parallel Control Mode.30Figure 19. SPI Timing.38Figure 20. I <sup>2</sup> C Timing40Figure 21. External Memory Interface.42Figure 23. Autoboot Timing Diagram.43Figure 24. I <sup>2</sup> S Format45Figure 25. Left Justified Format45Figure 26. Right Justified.45                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | Figure 12. Digital Audio Output, Data and Clock Timing   |    |

| Figure 14. I <sup>2</sup> C Control with External Memory26Figure 15. SPI Control27Figure 16. SPI Control with External Memory28Figure 17. Intel Parallel Control Mode29Figure 18. Motorola Parallel Control Mode30Figure 19. SPI Timing38Figure 20. I <sup>2</sup> C Timing40Figure 21. External Memory Interface42Figure 22. Run-Time Memory Access42Figure 23. Autoboot Timing Diagram43Figure 24. I <sup>2</sup> S Format45Figure 25. Left Justified Format45Figure 26. Right Justified45                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | Figure 13. I <sup>2</sup> C Control                      |    |

| Figure 15. SPI Control27Figure 16. SPI Control with External Memory28Figure 17. Intel Parallel Control Mode29Figure 18. Motorola Parallel Control Mode30Figure 19. SPI Timing38Figure 20. I <sup>2</sup> C Timing40Figure 21. External Memory Interface42Figure 22. Run-Time Memory Access42Figure 23. Autoboot Timing Diagram43Figure 24. I <sup>2</sup> S Format45Figure 25. Left Justified Format45Figure 26. Right Justified45                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | Figure 14, I <sup>2</sup> C Control with External Memory |    |

| Figure 17. Intel Parallel Control Mode29Figure 18. Motorola Parallel Control Mode30Figure 19. SPI Timing38Figure 20. I <sup>2</sup> C Timing40Figure 21. External Memory Interface42Figure 22. Run-Time Memory Access42Figure 23. Autoboot Timing Diagram43Figure 24. I <sup>2</sup> S Format45Figure 25. Left Justified Format45Figure 26. Right Justified45                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | Figure 15. SPI Control                                   |    |

| Figure 17. Intel Parallel Control Mode29Figure 18. Motorola Parallel Control Mode30Figure 19. SPI Timing38Figure 20. I <sup>2</sup> C Timing40Figure 21. External Memory Interface42Figure 22. Run-Time Memory Access42Figure 23. Autoboot Timing Diagram43Figure 24. I <sup>2</sup> S Format45Figure 25. Left Justified Format45Figure 26. Right Justified45                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | Figure 16. SPI Control with External Memory              |    |

| Figure 18. Motorola Parallel Control Mode30Figure 19. SPI Timing38Figure 20. I²C Timing40Figure 21. External Memory Interface42Figure 22. Run-Time Memory Access42Figure 23. Autoboot Timing Diagram43Figure 24. I²S Format45Figure 25. Left Justified Format45Figure 26. Right Justified45                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | Figure 17. Intel Parallel Control Mode                   |    |

| Figure 20. I <sup>2</sup> C Timing       40         Figure 21. External Memory Interface       42         Figure 22. Run-Time Memory Access       42         Figure 23. Autoboot Timing Diagram       43         Figure 24. I <sup>2</sup> S Format       45         Figure 25. Left Justified Format       45         Figure 26. Right Justified       45                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | Figure 18. Motorola Parallel Control Mode                | 30 |

| Figure 20. I <sup>2</sup> C Timing       40         Figure 21. External Memory Interface       42         Figure 22. Run-Time Memory Access       42         Figure 23. Autoboot Timing Diagram       43         Figure 24. I <sup>2</sup> S Format       45         Figure 25. Left Justified Format       45         Figure 26. Right Justified       45                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | Figure 19. SPI Timing                                    | 38 |

| Figure 21. External Memory Interface       42         Figure 22. Run-Time Memory Access       42         Figure 23. Autoboot Timing Diagram       43         Figure 24. I <sup>2</sup> S Format       45         Figure 25. Left Justified Format       45         Figure 26. Right Justified       45                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | Figure 20. I <sup>2</sup> C Timing                       | 40 |

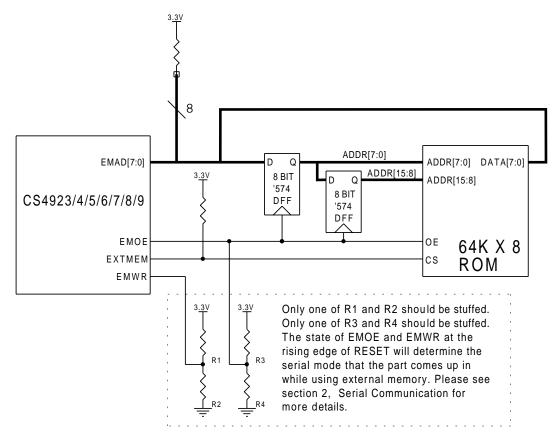

| Figure 23. Autoboot Timing Diagram                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | Figure 21. External Memory Interface                     | 42 |

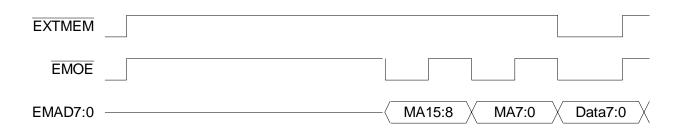

| Figure 23. Autoboot Timing Diagram                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | Figure 22. Run-Time Memory Access                        | 42 |

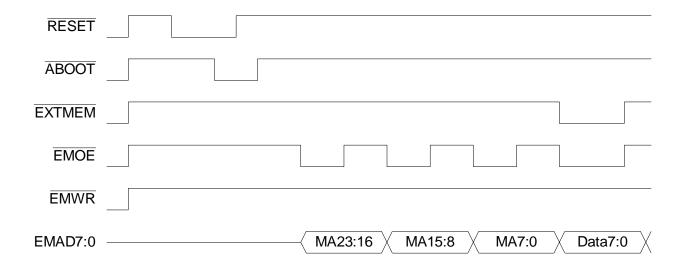

| Figure 24. I <sup>2</sup> S Format                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | Figure 23. Autoboot Timing Diagram                       | 43 |

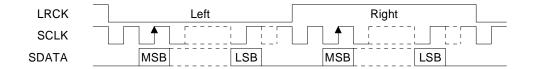

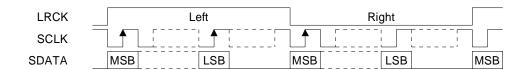

| Figure 25. Left Justified Format                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | Figure 24. I <sup>2</sup> S Format                       | 45 |

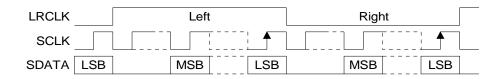

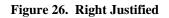

| Figure 26. Right Justified                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | Figure 25. Left Justified Format                         | 45 |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | Figure 26. Right Justified                               | 45 |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                          |    |

## LIST OF TABLES

| Table 1. Silicon Revisions                            |    |

|-------------------------------------------------------|----|

| Table 2. Host Modes                                   | 33 |

| Table 3. Host Memory Map                              |    |

| Table 4. Intel Parallel Host Mode Pin Assignments     |    |

| Table 5. Parallel Input/Output Registers              | 35 |

| Table 6. Motorola Parallel Host Mode Pin Assignments  |    |

| Table 7. SPI Serial Mode Pin Assignments              |    |

| Table 8. I <sup>2</sup> C Serial Mode Pin Assignments |    |

| Table 9. Memory Interface Pins                        | 41 |

| Table 10. Digital Audio Input Port                    |    |

| Table 11. Compressed Data Input Port                  |    |

| Table 12. Digital Audio Output Port                   | 47 |

| Table 13. MCLK/SCLK Master Mode Ratios                |    |

|                                                       |    |

#### 1. CHARACTERISTICS AND SPECIFICATIONS

## **ABSOLUTE MAXIMUM RATINGS**

(AGND, DGND = 0 V; all voltages with respect to 0 V)

| Parame                            | ter                                                | Symbol            | Min          | Max                 | Unit        |

|-----------------------------------|----------------------------------------------------|-------------------|--------------|---------------------|-------------|

| DC power supplies:                | Positive digital<br>Positive analog<br>  VA  –  VD | VD<br>VA          | -0.3<br>-0.3 | 3.63<br>3.63<br>0.4 | V<br>V<br>V |

| Input current, any pin except sup | plies                                              | l <sub>in</sub>   | -            | ±10                 | mA          |

| Digital input voltage             |                                                    | V <sub>IND</sub>  | -0.3         | 5.5                 | V           |

| Ambient operating temperature (   | power applied)                                     | T <sub>Amax</sub> | -55          | 125                 | °C          |

| Storage temperature               |                                                    | T <sub>stg</sub>  | -65          | 150                 | °C          |

**WARNING:** Operation at or beyond these limits may result in permanent damage to the device. Normal operation is not guaranteed at these extremes.

## **RECOMMENDED OPERATING CONDITIONS**

(AGND, DGND = 0 V; all voltages with respect to 0 V)

| Parameter                     |                  | Symbol         | Min  | Тур | Max  | Unit |

|-------------------------------|------------------|----------------|------|-----|------|------|

| DC power supplies:            | Positive digital | VD             | 3.13 | 3.3 | 3.47 | V    |

|                               | Positive analog  | VA             | 3.13 | 3.3 | 3.47 | V    |

|                               | VA  –  VD        |                | -    | -   | 0.4  | V    |

| Ambient operating temperature |                  | T <sub>A</sub> | 0    | -   | 70   | °C   |

## **DIGITAL D.C. CHARACTERISTICS**

(T<sub>A</sub> = 25 °C; VA, VD[3:1] = 3.3 V ±5%; measurements performed under static conditions.)

| Parameter                                            | Symbol          | Min          | Тур | Max      | Unit |

|------------------------------------------------------|-----------------|--------------|-----|----------|------|

| High-level input voltage                             | V <sub>IH</sub> | 2.0          | -   | -        | V    |

| Low-level input voltage                              | V <sub>IL</sub> | -            | -   | 0.8      | V    |

| High-level output voltage at $I_O = -4.0 \text{ mA}$ | V <sub>OH</sub> | VD 	imes 0.9 | -   | -        | V    |

| Low-level output voltage at $I_0 = 4.0 \text{ mA}$   | V <sub>OL</sub> | -            | -   | VD × 0.1 | V    |

| Input leakage current                                | l <sub>in</sub> | -            | -   | 1.0      | μA   |

## **POWER SUPPLY CHARACTERISTICS**

$(T_A = 25 \text{ °C}; \text{ VA}, \text{ VD}[3:1] = 3.3 \text{ V} \pm 5\%; \text{ measurements performed under operating conditions})$

|                       | Parameter                  | Symbol | Min | Тур | Max | Unit |

|-----------------------|----------------------------|--------|-----|-----|-----|------|

| Power supply current: | Digital operating: VD[3:1] |        | -   | 225 | 435 | mA   |

|                       | Analog operating: VA       |        | -   | 4   | 8   | mA   |

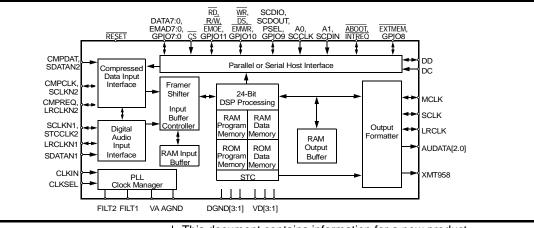

## SWITCHING CHARACTERISTICS—RESET

(T<sub>A</sub> = 25 °C; VA, VD = 3.3 V  $\pm$ 5%; Inputs: Logic 0 = DGND, Logic 1 = VD, C<sub>L</sub> = 20 pF)z

| Parameter                                     | Symbol              | Min | Max | Unit |

|-----------------------------------------------|---------------------|-----|-----|------|

| RESET minimum pulse width low                 | T <sub>rstl</sub>   | 100 | -   | ns   |

| All bidirectional pins high-Z after RESET low | T <sub>rst2z</sub>  | -   | 50  | ns   |

| Configuration bits setup before RESET high    | T <sub>rstsu</sub>  | 50  | -   | ns   |

| Configuration bits hold after RESET high      | T <sub>rsthld</sub> | 15  | -   | ns   |

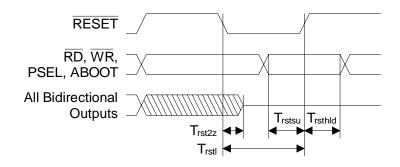

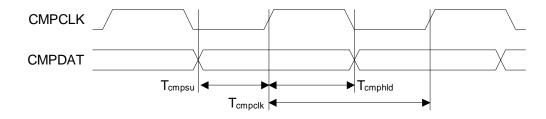

# **SWITCHING CHARACTERISTICS**—**CMPDAT, CMPCLK** (T<sub>A</sub> = 25 °C; VA, VD = 3.3 V $\pm$ 5%; Inputs: Logic 0 = DGND, Logic 1 = VD, C<sub>L</sub> = 20 pF)

| Parameter                                  | Symbol              | Min | Max | Unit |

|--------------------------------------------|---------------------|-----|-----|------|

| Serial compressed data clock CMPCLK period | T <sub>cmpclk</sub> | 37  | -   | ns   |

| CMPDAT setup before CMPCLK high            | T <sub>cmpsu</sub>  | 5   | -   | ns   |

| CMPDAT hold after CMPCLK high              | T <sub>cmphld</sub> | 3   | -   | ns   |

Figure 2. Serial Compressed Data Timing

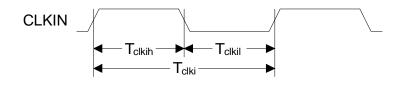

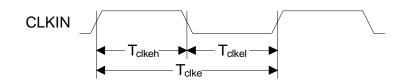

## SWITCHING CHARACTERISTICS—CLKIN

(T<sub>A</sub> = 25 °C; VA, VD = 3.3 V ±5%; Inputs: Logic 0 = DGND, Logic 1 = VD, C<sub>L</sub> = 20 pF)

| Parameter                                   | Symbol             | Min | Max  | Unit |

|---------------------------------------------|--------------------|-----|------|------|

| CLKIN period for internal DSP clock mode    | T <sub>clki</sub>  | 20  | 3800 | ns   |

| CLKIN high time for internal DSP clock mode | T <sub>clkih</sub> | 8   |      | ns   |

| CLKIN low time for internal DSP clock mode  | T <sub>clkil</sub> | 8   |      | ns   |

| CLKIN period for external DSP clock mode    | T <sub>clke</sub>  | 20  | 25   | ns   |

| CLKIN high time for external DSP clock mode | T <sub>clkeh</sub> | 9   |      | ns   |

| CLKIN low time for external DSP clock mode  | T <sub>clkel</sub> | 9   |      | ns   |

Figure 3. CLKIN with CLKSEL = VSS = PLL Enable

Figure 4. CLKIN with CLKSEL = VD = PLL Bypass

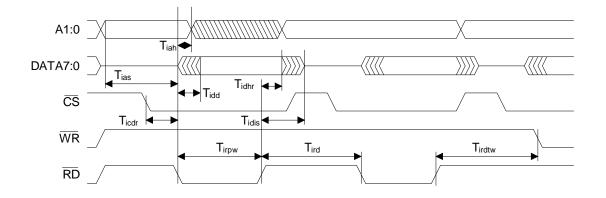

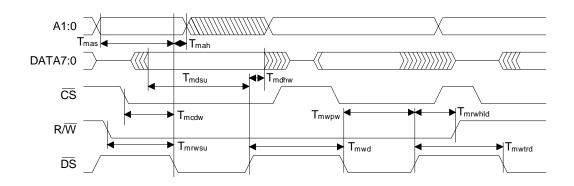

## SWITCHING CHARACTERISTICS—INTEL® HOST MODE

(T<sub>A</sub> = 25 °C; VA, VD = 3.3 V  $\pm$ 5%; Inputs: Logic 0 = DGND, Logic 1 = VD, C<sub>L</sub> = 20 pF)

| Parameter                                                                                                                     | Symbol             | Min                | Max         | Unit |    |

|-------------------------------------------------------------------------------------------------------------------------------|--------------------|--------------------|-------------|------|----|

| Address setup before $\overline{CS}$ and $\overline{RD}$ low or $\overline{CS}$ and $\overline{N}$                            | T <sub>ias</sub>   | 5                  | -           | ns   |    |

| Address hold time after $\overline{CS}$ and $\overline{RD}$ low or $\overline{CS}$ and                                        | d WR low           | T <sub>iah</sub>   | 5           | -    | ns |

| Delay between $\overline{RD}$ then $\overline{CS}$ low or $\overline{CS}$ then $\overline{RD}$ lo                             | w                  | T <sub>icdr</sub>  | 0           | 8    | ns |

| Data valid after CS and RD low                                                                                                |                    | T <sub>idd</sub>   | -           | 20   | ns |

| CS and RD low for read                                                                                                        | (Note 1)           | T <sub>irpw</sub>  | DCLK + 10   | -    | ns |

| Data hold time after CS or RD high                                                                                            |                    | T <sub>idhr</sub>  | 5           | -    | ns |

| Data high-Z after CS or RD high                                                                                               | (Note 2)           | T <sub>idis</sub>  | -           | 15   | ns |

| $\overline{\text{CS}}$ or $\overline{\text{RD}}$ high to $\overline{\text{CS}}$ and $\overline{\text{RD}}$ low for next read  | (Note 1)           | T <sub>ird</sub>   | 2*DCLK + 10 | -    | ns |

| $\overline{CS}$ or $\overline{RD}$ high to $\overline{CS}$ and $\overline{WR}$ low for next write                             | (Note 1)           | T <sub>irdtw</sub> | 2*DCLK + 10 | -    | ns |

| Delay between $\overline{WR}$ then $\overline{CS}$ low or $\overline{CS}$ then $\overline{WR}$ is                             | wc                 | T <sub>icdw</sub>  | 0           | 8    | ns |

| Data setup before CS or WR high                                                                                               |                    | T <sub>idsu</sub>  | 20          | -    | ns |

| CS and WR low for write                                                                                                       | T <sub>iwpw</sub>  | DCLK + 10          | -           | ns   |    |

| Data hold after $\overline{CS}$ or $\overline{WR}$ high                                                                       |                    | T <sub>idhw</sub>  | 5           | -    | ns |

| $\overline{\text{CS}}$ or $\overline{\text{WR}}$ high to $\overline{\text{CS}}$ and $\overline{\text{RD}}$ low for next read  | T <sub>iwtrd</sub> | 2*DCLK + 10        | -           | ns   |    |

| $\overline{\text{CS}}$ or $\overline{\text{WR}}$ high to $\overline{\text{CS}}$ and $\overline{\text{WR}}$ low for next write | (Note 1)           | T <sub>iwd</sub>   | 2*DCLK + 10 | -    | ns |

Notes: 1. Certain timing parameters are normalized to the DSP clock, DCLK, in nanoseconds. The DSP clock can be defined as follows:

External CLKIN Mode: DCLK == CLKIN/3 before and during boot DCLK == CLKIN after boot

Internal Clock Mode: DCLK == 10MHz before and during boot, i.e. DCLK == 100ns DCLK == 60 MHz after boot, i.e. DCLK == 16.7ns (this speed may depend on CLKIN, please see CS4923/4/5/6/7/8/9 Hardware User's Guide for more information)

2. This specification is characterized but not production tested.

Figure 5. Intel Parallel Host Mode Read Cycle

Figure 6. Intel Parallel Host Mode Write Cycle

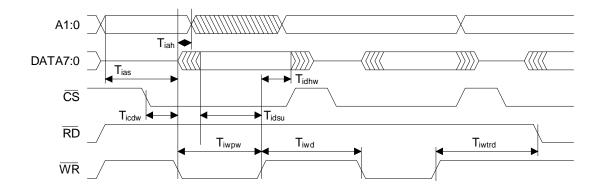

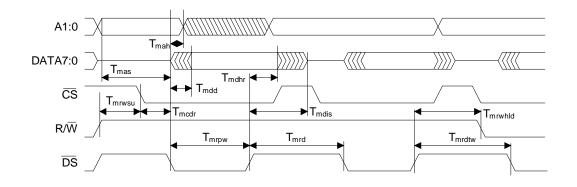

## SWITCHING CHARACTERISTICS—MOTOROLA® HOST MODE

(T<sub>A</sub> = 25 °C; VA, VD = 3.3 V  $\pm$ 5%; Inputs: Logic 0 = DGND, Logic 1 = VD, C<sub>L</sub> = 20 pF)

| Parameter                                                                                                                          | Symbol                  | Min         | Max | Unit |

|------------------------------------------------------------------------------------------------------------------------------------|-------------------------|-------------|-----|------|

| Address setup before CS and DS low                                                                                                 | T <sub>mas</sub>        | 5           | -   | ns   |

| Address hold time after $\overline{CS}$ and $\overline{DS}$ low                                                                    | T <sub>mah</sub>        | 5           | -   | ns   |

| Delay between $\overline{\text{DS}}$ then $\overline{\text{CS}}$ low or $\overline{\text{CS}}$ then $\overline{\text{DS}}$ low     | T <sub>mcdr</sub>       | 0           | ∞   | ns   |

| Data valid after $\overline{CS}$ and $\overline{DS}$ low with R/W high                                                             | T <sub>mdd</sub>        | -           | 20  | ns   |

| CS and DS low for read (Not                                                                                                        | e 3) T <sub>mrpw</sub>  | DCLK + 10   | -   | ns   |

| Data hold time after $\overline{CS}$ or $\overline{DS}$ high after read                                                            | T <sub>mdhr</sub>       | 5           | -   | ns   |

| Data high-Z after CS or DS high low after read (Not                                                                                | e 4) T <sub>mdis</sub>  | -           | 15  | ns   |

| $\overline{\text{CS}}$ or $\overline{\text{DS}}$ high to $\overline{\text{CS}}$ and $\overline{\text{DS}}$ low for next read (Not  | e 3) T <sub>mrd</sub>   | 2*DCLK + 10 | -   | ns   |

| $\overline{\text{CS}}$ or $\overline{\text{DS}}$ high to $\overline{\text{CS}}$ and $\overline{\text{DS}}$ low for next write (Not | e 3) T <sub>mrdtw</sub> | 2*DCLK + 10 | -   | ns   |

| Delay between $\overline{\text{DS}}$ then $\overline{\text{CS}}$ low or $\overline{\text{CS}}$ then $\overline{\text{DS}}$ low     | T <sub>mcdw</sub>       | 0           | ∞   | ns   |

| Data setup before CS or DS high                                                                                                    | T <sub>mdsu</sub>       | 20          | -   | ns   |

| CS and DS low for write (Not                                                                                                       | e 3) T <sub>mwpw</sub>  | DCLK + 10   | -   | ns   |

| $R/\overline{W}$ setup before $\overline{CS}$ or $\overline{DS}$ low                                                               | T <sub>mrwsu</sub>      | 5           | -   | ns   |

| $R/\overline{W}$ hold time after $\overline{CS}$ or $\overline{DS}$ high                                                           | T <sub>mrwhld</sub>     | 5           | -   | ns   |

| Data hold after CS or DS high                                                                                                      | T <sub>mdhw</sub>       | 5           | -   | ns   |

| $\overline{CS}$ or $\overline{DS}$ high to $\overline{CS}$ and $\overline{DS}$ low with R/ $\overline{W}$ high for next r (Not     |                         | 2*DCLK + 10 | -   | ns   |

| $\overline{\text{CS}}$ or $\overline{\text{DS}}$ high to $\overline{\text{CS}}$ and $\overline{\text{DS}}$ low for next write (Not | e 3) T <sub>mwd</sub>   | 2*DCLK + 10 | -   | ns   |

Notes: 3. Certain timing parameters are normalized to the DSP clock, DCLK, in nanoseconds. The DSP clock can be defined as follows:

External CLKIN Mode: DCLK == CLKIN/3 before and during boot DCLK == CLKIN after boot

Internal Clock Mode:

DCLK == 10MHz before and during boot, i.e. DCLK == 100ns DCLK == 60 MHz after boot, i.e. DCLK == 16.7ns (this speed may depend on CLKIN, please see CS4923/4/5/6/7/8/9 Hardware Users Guide for more information)

4. This specification is characterized but not production tested.

Figure 7. Motorola Parallel Host Mode Read Cycle

Figure 8. Motorola Parallel Host Mode Write Cycle

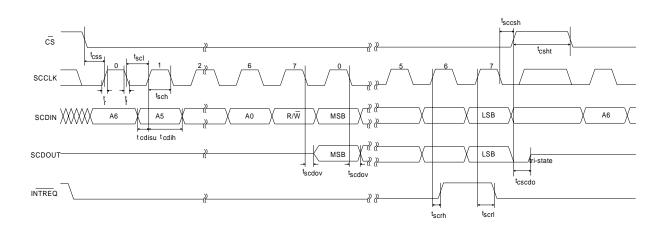

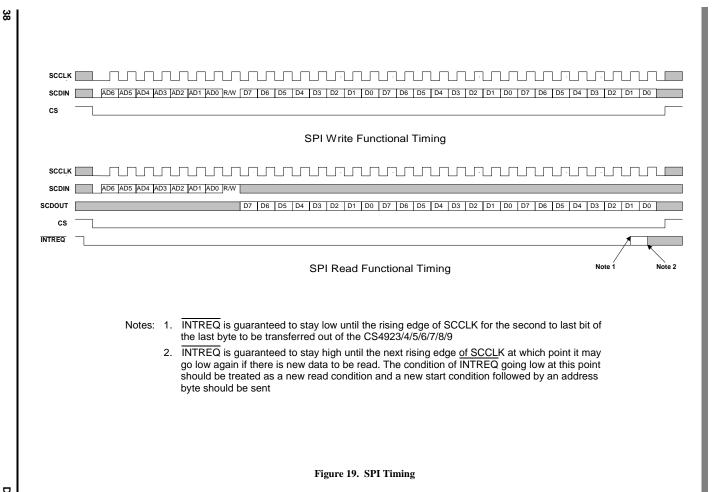

## SWITCHING CHARACTERISTICS—SPI CONTROL PORT

(T<sub>A</sub> = 25 °C; VA, VD = 3.3 V  $\pm$ 5%; Inputs: Logic 0 = DGND, Logic 1 = VD, C<sub>L</sub> = 20 pF)

| Parameter                                         |              | Symbol             | Min | Max          | Units |

|---------------------------------------------------|--------------|--------------------|-----|--------------|-------|

| SCCLK clock frequency                             | (Note 5)     | f <sub>sck</sub>   | -   | 2000         | kHz   |

| CS falling to SCCLK rising                        |              | t <sub>css</sub>   | 20  | -            | ns    |

| Rise time of SCCLK line                           | (Note 11)    | t <sub>r</sub>     | -   | 50           | ns    |

| Fall time of SCCLK lines                          | (Note 11)    | t <sub>f</sub>     | -   | 50           | ns    |

| SCCLK low time                                    |              | t <sub>scl</sub>   | 150 | -            | ns    |

| SCCLK high time                                   |              | t <sub>sch</sub>   | 150 | -            | ns    |

| Setup time SCDIN to SCCLK rising                  |              | t <sub>cdisu</sub> | 50  | -            | ns    |

| Hold time SCCLK rising to SCDIN                   | (Note 6)     | t <sub>cdih</sub>  | 50  | -            | ns    |

| Transition time from SCCLK to SCDOUT valid        | (Note 7)     | t <sub>scdov</sub> | -   | 40           | ns    |

| Time from SCCLK rising to INTREQ rising           | (Note 8)     | t <sub>scrh</sub>  | -   | 200          | ns    |

| Rise time for INTREQ                              | (Note 8)     | t <sub>rr</sub>    | -   | (Note<br>10) | ns    |

| Hold time for INTREQ from SCCLK rising            | (Note 9, 11) | t <sub>scrl</sub>  | 0   | -            | ns    |

| Time from SCCLK falling to $\overline{CS}$ rising |              | t <sub>sccsh</sub> | 20  | -            | ns    |

| High time between active $\overline{CS}$          |              | t <sub>csht</sub>  | 200 | -            | ns    |

| Time from $\overline{CS}$ rising to SCDOUT high-Z | (Note 11)    | t <sub>cscdo</sub> |     | 10           | ns    |

Notes: 5. The specification f<sub>sck</sub> indicates the maximum speed of the hardware. The system designer should be aware that the actual maximum speed of the communication port may be limited by the software. The relevant application code user's manual should be consulted for the software speed limitations.

- 6. Data must be held for sufficient time to bridge the 50 ns transition time of SCCLK.

- 7. SCDOUT should *not* be sampled during this time period.

- 8. INTREQ goes high only if there is no data to be read from the DSP at the rising edge of SCCLK for the second-to-last bit of the last byte of data during a read operation as shown.

- 9. If INTREQ goes high as indicated in Note 8, then INTREQ is guaranteed to remain high until the next rising edge of SCCLK. If there is more data to be read at this time, INTREQ goes active low again. Treat this condition as a new read transaction. Raise chip select to end the current read transaction and then drop it, followed by the 7-bit address and the R/W bit (set to 1 for a read) to start a new read transaction.

- 10. With a 4.7k Ohm pull-up resistor this value is typically 215ns. As this pin is open drain adjusting the pull up value will affect the rise time.

- 11. This time is by design and not tested.

Figure 9. SPI Control Port Timing

<del>1</del>3

DS262F2

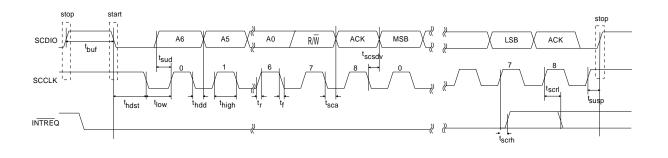

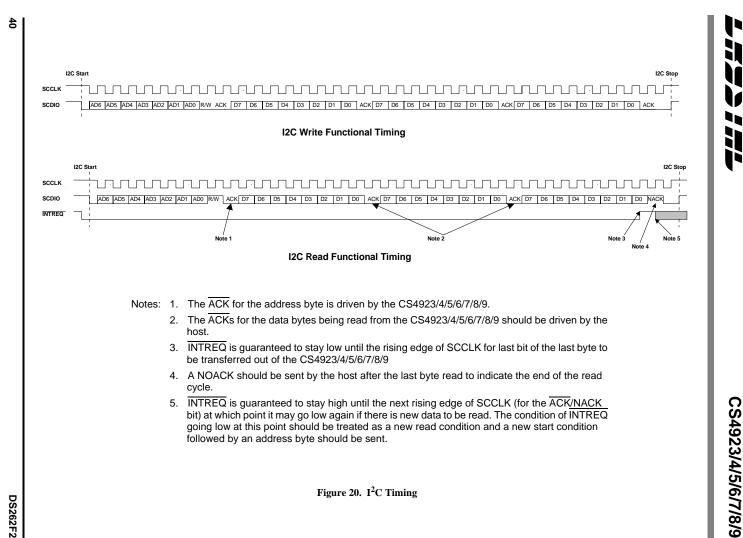

## SWITCHING CHARACTERISTICS— I<sup>2</sup>C<sup>®</sup> CONTROL PORT

(T<sub>A</sub> = 25 °C; VA, VD = 3.3 V  $\pm$ 5%; Inputs: Logic 0 = DGND, Logic 1 = VD, C<sub>L</sub> = 20 pF)

| Parameter                                              |                      | Symbol             | Min | Max          | Units |

|--------------------------------------------------------|----------------------|--------------------|-----|--------------|-------|

| SCCLK clock frequency                                  | (Note 12)            | f <sub>scl</sub>   |     | 400          | kHz   |

| Bus free time between transmissions                    |                      | t <sub>buf</sub>   | 4.7 |              | μs    |

| Start-condition hold time (prior to first clock pulse) |                      | t <sub>hdst</sub>  | 4.0 |              | μs    |

| Clock low time                                         |                      | t <sub>low</sub>   | 1.2 |              | μs    |

| Clock high time                                        |                      | t <sub>high</sub>  | 1.0 |              | μs    |

| SCDIO setup time to SCCLK rising                       |                      | t <sub>sud</sub>   | 250 |              | ns    |

| SCDIO hold time from SCCLK falling                     | (Note 13)            | t <sub>hdd</sub>   | 0   |              | μs    |

| Rise time of SCCLK                                     | (Note 14), (Note 18) | t <sub>r</sub>     |     | 50           | ns    |

| Fall time of SCCLK                                     | (Note 18)            | t <sub>f</sub>     |     | 300          | ns    |

| Time from SCCLK falling to CS4923/4/5/6/7/8/9 ACK      | (                    | t <sub>sca</sub>   |     | 40           | ns    |

| Time from SCCLK falling to SCDIO valid during read     | operation            | t <sub>scsdv</sub> |     | 40           | ns    |

| Time from SCCLK rising to INTREQ rising                | (Note 15)            | t <sub>scrh</sub>  |     | 200          | ns    |

| Hold time for INTREQ from SCCLK rising                 | (Note 16)            | t <sub>scrl</sub>  | 0   |              | ns    |

| Rise time for INTREQ                                   |                      | t <sub>rr</sub>    |     | (Note<br>17) | ns    |

| Setup time for stop condition                          |                      | t <sub>susp</sub>  | 4.7 |              | μs    |

- Notes: 12. The specification f<sub>scl</sub> indicates the maximum speed of the hardware. The system designer should be aware that the actual maximum speed of the communication port may be limited by the software. The relevant application code user's manual should be consulted for the software speed limitations.

- 13. Data must be held for sufficient time to bridge the 300-ns transition time of SCCLK. This hold time is by design and not tested.

- 14. This rise time is shorter than that recommended by the I<sup>2</sup>C specifications. For more information, see the section on SCP communications.

- 15. INTREQ goes high only if there is no data to be read from the DSP at the rising edge of SCCLK for the last data bit of the last byte of data during a read operation as shown.

- 16. If INTREQ goes high as indicated in Note 8, then INTREQ is guaranteed to remain high until the next rising edge of SCCLK. If there is more data to be read at this time, INTREQ goes active low again. Treat this condition as a new read transaction. Send a new start condition followed by the 7-bit address and the R/W bit (set to 1 for a read). This time is by design and is not tested.

- 17. With a 4.7k Ohm pull-up resistor this value is typically 215ns. As this pin is open drain adjusting the pull up value will affect the rise time.

- 18. This time is by design and not tested.

CS4923/4/5/6/7/8/9

Figure 10. I<sup>2</sup>C Control Port Timing

DS262F2

5

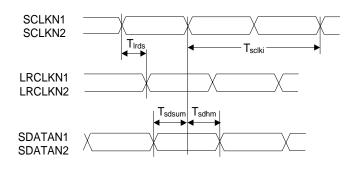

## SWITCHING CHARACTERISTICS—DIGITAL AUDIO INPUT

(T<sub>A</sub> = 25 °C; VA, VD = 3.3 V  $\pm$ 5%; Inputs: Logic 0 = DGND, Logic 1 = VD, C<sub>L</sub> = 20 pF)

| Parameter                                              |                   | Symbol             | Min | Max | Unit |

|--------------------------------------------------------|-------------------|--------------------|-----|-----|------|

| SCLKN1(2) period for both Master and Slave mode        | (Note 19)         | T <sub>sclki</sub> | 40  | -   | ns   |

| SCLKN1(2) duty cycle for Master and Slave mode         | (Note 19)         |                    | 45  | 55  | %    |

| Master Mode                                            |                   |                    |     |     |      |

| LRCLKN1(2) delay after SCLKN1(2) transition            | T <sub>Irds</sub> | -                  | 10  | ns  |      |

| SDATAN1(2) setup to SCLKN1(2) transition               | (Note 22)         | T <sub>sdsum</sub> | 10  | -   | ns   |

| SDATAN1(2) hold time after SCLKN1(2) transition        | (Note 22)         | T <sub>sdhm</sub>  | 5   | -   | ns   |

| Slave Mode                                             | (Note 23)         |                    |     |     |      |

| Time from active edge of SCLKN1(2) to LRCLKN1(2) trans | T <sub>stlr</sub> | 10                 | -   | ns  |      |

| Time from LRCLKN1(2) transition to SCLKN1(2) active e  | T <sub>Irts</sub> | 10                 | -   | ns  |      |

| SDATAN1(2) setup to SCLKN1(2) transition (Note 22)     |                   |                    | 5   | -   | ns   |

| SDATAN1(2) hold time after SCLKN1(2) transition        | T <sub>sdhs</sub> | 5                  | -   | ns  |      |

Notes: 19. Master mode timing specifications are characterized, not production tested.

- 20. Master mode is defined as the CS4923 driving LRCLKN1(2) and SCLKN1(2). Master or Slave mode can be programmed.

- 21. This timing parameter is defined from the non-active edge of SCLKN1(2). The active edge of SCLKN1(2) is the point at which the data is valid.

- 22. This timing parameter is defined from the active edge of SCLKN1(2). The active edge of SCLKN1(2) is the point at which the data is valid.

- 23. Slave mode is defined as SCLKN1(2) and LRCLKN1(2) being driven by an external source.

#### MASTER MODE

#### SLAVE MODE

Figure 11. Digital Audio Input, Data and Clock Timing

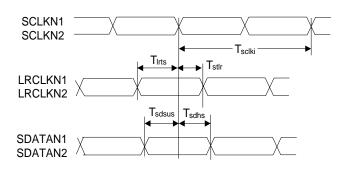

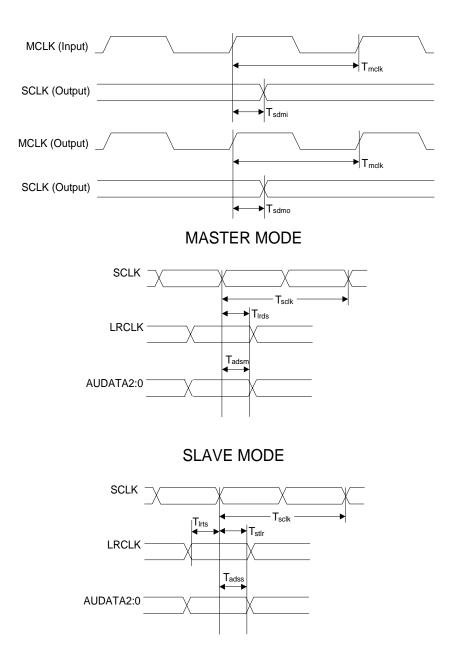

## SWITCHING CHARACTERISTICS—DIGITAL AUDIO OUTPUT

(T<sub>A</sub> = 25 °C; VA, VD = 3.3 V  $\pm$ 5%; measurements performed under static conditions.)

| Parameter                                    | Symbol            | Min               | Мах | Unit |    |

|----------------------------------------------|-------------------|-------------------|-----|------|----|

| MCLK period                                  | (Note 24)         | T <sub>mclk</sub> | 40  | -    | ns |

| MCLK duty cycle                              | (Note 24)         |                   | 40  | 60   | %  |

| SCLK period for Master or Slave mode         | (Note 25)         | T <sub>sclk</sub> | 40  | -    | ns |

| SCLK duty cycle for Master or Slave mode     | (Note 25)         |                   | 45  | 55   | %  |

| Master Mode                                  | (Note 25,26)      |                   |     |      |    |

| SCLK delay from MCLK rising edge, MCLK as a  | T <sub>sdmi</sub> |                   | 15  | ns   |    |

| SCLK delay from MCLK rising edge, MCLK as a  | an output         | T <sub>sdmo</sub> | -5  | 10   | ns |

| LRCLK delay from SCLK transition             | (Note 27)         | T <sub>Irds</sub> |     | 10   | ns |

| AUDATA2–0 delay from SCLK transition         | (Note 27)         | T <sub>adsm</sub> |     | 10   | ns |

| Slave Mode                                   | (Note 28)         |                   |     |      |    |

| Time from active edge of SCLKN1(2) to LRCLK  | T <sub>stlr</sub> | 10                | -   | ns   |    |

| Time from LRCLKN1(2) transition to SCLKN1(2) | T <sub>lrts</sub> | 10                | -   | ns   |    |

| AUDATA2–0 delay from SCLK transition         | (Note 27,29)      | T <sub>adss</sub> |     | 15   | ns |

Notes: 24. MCLK can be an input or an output. These specifications apply for both cases.

- 25. Master mode timing specifications are characterized, not production tested.

- 26. Master mode is defined as the CS4923 driving both SCLK and LRCLK. When MCLK is an input, it is divided to produce SCLK and LRCLK.

- 27. This timing parameter is defined from the non-active edge of SCLK. The active edge of SCLK is the point at which the data is valid.

- 28. Slave mode is defined as SCLK and LRCLK being driven by an external source.

- 29. This specification is characterized, not production tested.

Figure 12. Digital Audio Output, Data and Clock Timing

#### 2. FAMILY OVERVIEW

The CS4923, CS4924, CS4925, CS4926, CS4927, CS4928 and the CS4929 are system on a chip solutions for multi-channel (or stereo in the case of the CS4929) audio decompression and digital signal processing. Because the parts are primarily RAM-based, a download of application software is required each time the CS4923/4/5/6/7/8/9 is powered up. This document uses "download" and "code load" interchangeably. These terms should be interpreted as meaning the transfer of application code into the internal CS4923/4/5/6/7/8/9 memory from either an external microcontroller or through the autoboot procedure.

This document focuses on the electrical features and characteristics of these parts. The different features are described from a hardware design perspective. It should be understood that not all of the features portrayed in this document are supported by all of the versions of application code available. The application user's guides (see section 2.2.2) should be consulted to confirm which hardware features are supported by the software. This document will be valuable to both the hardware designer and the system programmer.

This data sheet covers the CS4923, CS4924, CS4925, CS4926, CS4927, CS4928 and CS4929. These parts are identical from an external electrical perspective. Internally each device has been tailored for supporting different decoding standards. For this document CS4923/4/5/6/7/8/9 has been replaced in certain places with CS492X for readability. Unless otherwise specified CS492X should be interpreted as applying to the CS4923, CS4924, CS4925, CS4926, CS4927, CS4928 and CS4929.

There are two revisions of silicon commercially available. The features available on Revision D are a super-set of those features available on Revision B. Differences between the revisions are pointed out when features are discussed within this document. The silicon revision for any chip can be determined by referencing Table 1 below.

| Revision B | Revision D |

|------------|------------|

| CS492301   | CS492305   |

| CS492401   | CS492405   |

| CS492501   | CS492505   |

| CS492603   | CS492604   |

|            | CS492705   |

|            | CS492804   |

|            | CS492906   |

**Table 1. Silicon Revisions**

These parts are generally targeted at two different market segments. The broadcast market where audio/video (A/V) synchronization is required, and the outboard decoder markets where audio/video synchronization is not required. The important differentiation is the format in which the data will be received by the CS4923/4/5/6/7/8/9. In systems where A/V synchronization is required from the CS4923/4/5/6/7/8/9, the incoming data is typically PES encoded. In an outboard decoder application the data typically comes in the IEC61937 format (as specified by the DVD consortium). An important point to remember is that the CS4923/4/5/6/7/8/9 will both support environments, but different downloads are required depending on the input data type.

Broadcast applications include (but are not limited to) set top box applications, DVDs and digital TVs. Outboard decoder applications include standalone decoders and audio/video receivers. Often times a system may be a hybrid between an outboard decoder and a broadcast system depending on its functionality.

As discussed above, compressed audio can be packed in IEC61937, PES, or elementary formats depending on the decoder environment. Each format is supported by a separate download of application code. Consult the relevant Application Code

User's Guide to determine which formats are supported by a particular application. A brief description of each format is presented below.

*Elementary* - an elementary bitstream consists only of compressed audio data (e.g., strictly the Dolby Digital bitstream); used primarily in broadcast environments.

*PES* - a Packetized Elementary Stream (PES) bitstream contains the elementary compressed audio stream and additional header information which can be used for A/V synchronization; used primarily in broadcast environments.

*IEC61937* - a method of packing compressed audio such that it can be delivered using a bi-phase encoded signal (e.g., S/PDIF output signal from DVD player); used primarily for outboard decoders where A/V synchronization is not required.

#### 2.1 Multi-channel Decoder Family of Parts

*CS4923 - Dolby Digital<sup>TM</sup> Audio Decoder.* The CS4923 is the original member of the family and is intended to be used if only Dolby Digital decoding is required. For Dolby Digital, post processing includes bass management, delays and Dolby Pro Logic decoding. Separate downloads can also be used to support stereo to 5.1 channel effects processing and stereo MPEG decoding.

*CS4924* - *Dolby Digital<sup>TM</sup> Source Product Decoder*. The CS4924 is the stereo version of the CS4923 designed for source products such as DVD, HDTV, and set-top boxes. Separate downloads are available for stereo decode of Dolby Digital and MPEG audio.

**CS4925** - International Multi-Channel DVD Audio Decoder. The CS4925 supports both Dolby Digital and MPEG-2 multi-channel formats. For both Dolby Digital and MPEG-2 multi-channel, post processing includes bass management and Dolby Pro Logic decoding. Separate downloads are available for decode of Dolby Digital and MPEG audio. Another code load can be used to support stereo to 5.1 channel effects processing.

*CS4926 - DTS/Dolby*<sup>®</sup> *Multi-Channel Audio Decoder*. The CS4926 supports both Dolby Digital and DTS, or Digital Theater Surround. For Dolby Digital, post processing includes bass management and Dolby Pro Logic. The Dolby Digital code and DTS code take separate code downloads. Separate downloads can also be used to support stereo to 5.1 channel effects processing and stereo MPEG decoding.

**CS4927 - MPEG-2 Multi-Channel Decoder.** The CS4927 supports MPEG-2 multi-channel decoding and should be used in applications where Dolby Digital decoding is not necessary. For MPEG-2 multi-channel decoding, post processing includes bass management and Dolby Pro Logic decoding. Another code load can be used to support stereo to 5.1 channel effects processing.

*CS4928 - DTS Multi-Channel Decoder.* The CS4928 supports DTS multi-channel decoding and should be used in applications where Dolby Digital decoding is not necessary. For DTS multi-channel decoding, post processing includes bass management. Separate downloads can also be used to support stereo to 5.1 channel effects processing and stereo MPEG decoding.

**CS4929 - AAC 2-Channel, (Low Complexity) and MPEG-2 Stereo Decoder.** The CS4929 is capable of decoding both 2-channel AAC and MPEG-2 audio. The CS4929 supports elementary and PES formats.

#### 2.2 Document Strategy

Multiple documents are needed to fully define, understand and implement the functionality of the CS4923/4/5/6/7/8/9. They can be split up into two basic groups: hardware and application code documentation. It should be noted that hardware and application code are co-dependent and one can not successfully use the device without an

understanding of both. The 'ANXXX' notation denotes the application note number under which the respective user's guide was released.

#### 2.2.1 Hardware Documentation

*CS4923/4/5/6/7/8/9 Family Data Sheet* - This document describes the electrical characteristics of the device from timing to base functionality. This is the hardware designers tool to learn the part's electrical and systems requirements.

AN115 - CS4923/4/5/6/7/8/9 Hardware User's Guide - describes the functional aspects of the device. An in depth description of communication, boot procedure, external memory and hardware configuration are given in this document. This document will be valuable to both the hardware designer and the system programmer.

#### 2.2.2 CS4923/4/5/6/7/8/9 Application Code User's Guides

The following application notes describe the application codes used with the CS4923/4/5/6/7/8/9. Whenever an application code user's guide is referred to, it should be assumed that one or more of the below documents are being referenced. The following list covers currently released application notes. This list will grow with each new application released. For a current list of released user's guides please see www.crystal.com and search for the part number.

AN120 - Dolby Digital User's Guide for the CS4923/4/5/6. This document covers the features available in the Dolby Digital code including delays, pink noise, bass management, Pro Logic, PCM pass through and Dolby Digital processing features. Optional appendices are available that document code for Dolby Virtual, Q-Surround and VMAx.

AN121 - MPEG User's Guide for the CS4925. This document covers the features available in the MPEG Multi-Channel code including delays, bass management, Pro Logic, and MPEG processing features.

AN122 - DTS User's Guide for the CS4926, CS4928. This document covers the features available in the DTS code including bass management and DTS processing features.

AN123 - Surround User's Guide for the CS4923/4/5/6/7/8. This code covers the different Stereo PCM to surround effects processing code. Optional appendices are available that document Crystal Original Surround, Circle Surround and Logic 7.

AN140 - Broadcast Systems Guide for the CS4923/4/5/6/7/8/9. This guide describes all application code (e.g. Dolby Digital, MPEG, AAC) designed for broadcast systems such as HDTV and set-top box receivers. This document also provides a discussion of broadcast system considerations and dependencies such as A/V synchronization and channel change procedures.

#### 2.3 Using the CS4923/4/5/6/7/8/9

No matter what application is being used on the chip, the following four steps are always followed to use the CS4923/4/5/6/7/8/9 in system.

- 1) Reset and/or Download Code Detailed information in AN115

- 2) Hardware Configuration Detailed information in AN115

- Application configuration Detailed information in the appropriate Application Code User's guide

- Kickstart This is the "Go" command to the CS492X once the system is properly configured. Information can be found in the appropriate Application Code User's guide.

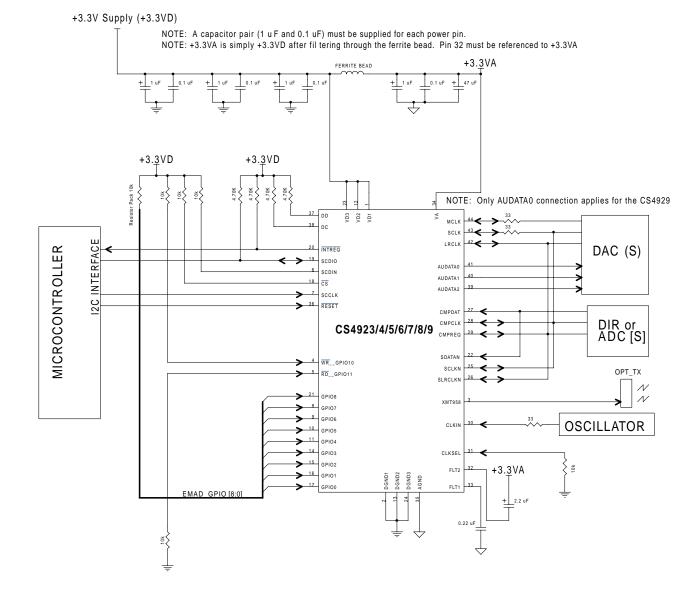

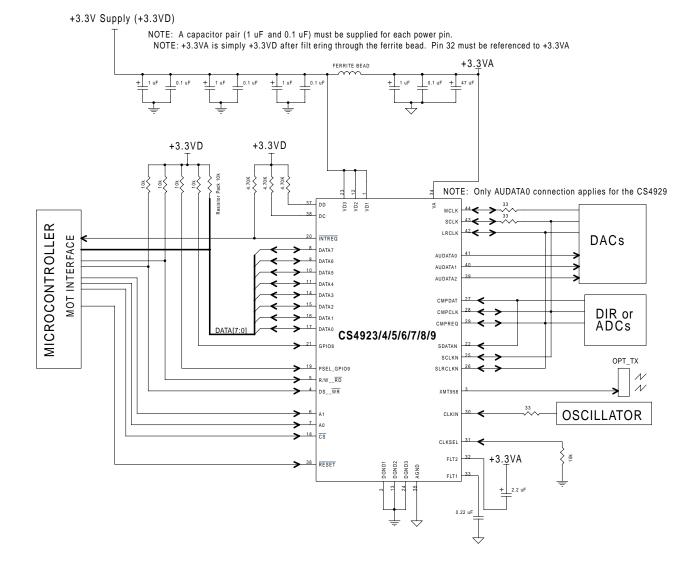

#### 3. TYPICAL CONNECTION DIAGRAMS

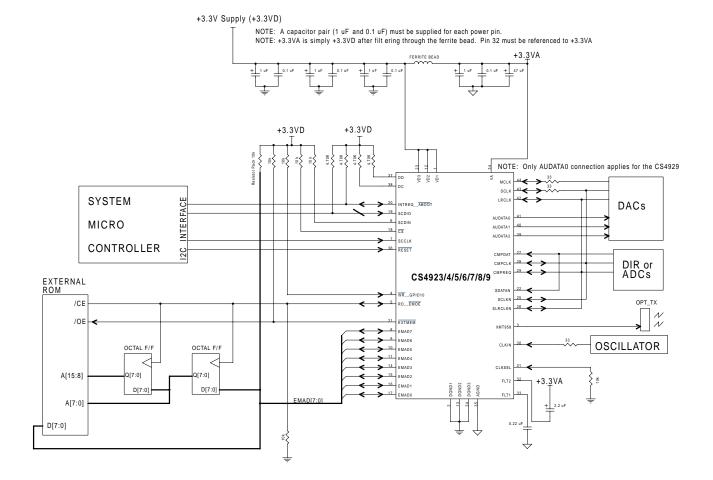

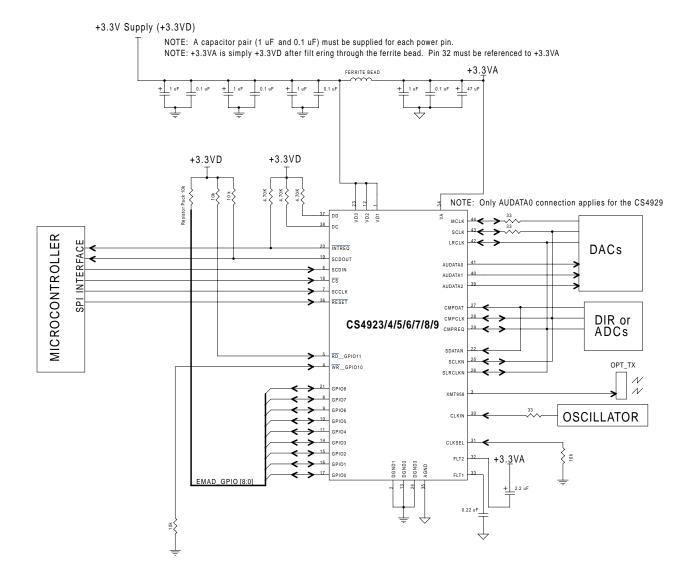

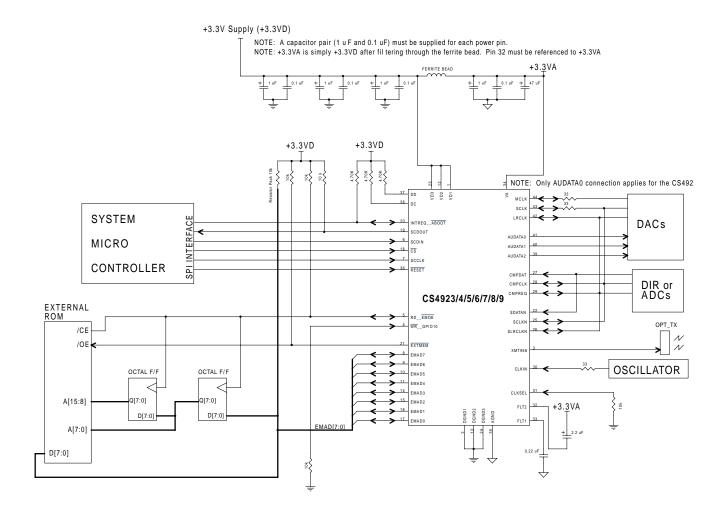

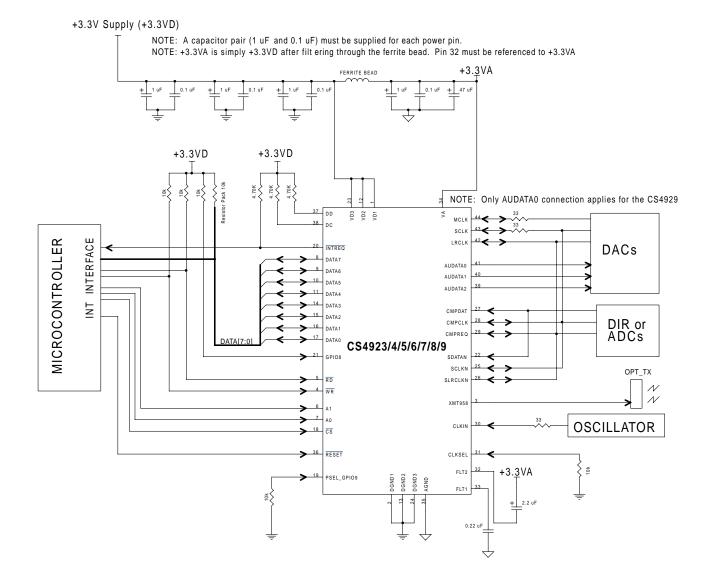

Six typical connection diagrams have been presented to illustrate using the device with the different communication modes available. They are as follows:

Figure 13: I<sup>2</sup>C Control

Figure 14: I<sup>2</sup>C Control with External Memory

Figure 15: SPI Control

Figure 16: SPI Control with External Memory

Figure 17: Intel Parallel Control Mode

Figure 18: Motorola Parallel Control Mode

The following should be noted when viewing the typical connection diagrams:

The pins are grouped functionally in each of the typical connection diagrams. Please be aware that the CS4923/4/5/6/7/8/9 symbol may appear differently in each diagram.

The external memory interface is only supported when a serial communication mode has been chosen.

The typical connection diagrams demonstrate the PLL being used (CLKSEL is pulled low). To enable external CLKIN, CLKSEL should be pulled high. The system designer must be aware that certain software features may not be available if external CLKIN is used as the DSP must run slower when external CLKIN is used. The system designer should also be aware of additional duty cycle requirements when using external CLKIN mode. It is highly suggested that the system designer take advantage of the PLL and pull CLKSEL low.

#### 3.1 Multiplexed Pins

The CS4923/4/5/6/7/8/9 family of digital signal processors (DSPs) incorporate a large amount of flexibility into a 44 pin package. Because of the high degree of integration, many of these pins are internally multiplexed to serve multiple purposes.

Some pins are designed to operate in one mode at power up, and serve a different purpose when the DSP is running. Other pins have functionality which can be controlled by the application running on the DSP. In order to better explain the behavior of the part, the pins which are multiplexed have been given multiple names. Each name is specific to the pin's operation in a particular mode.