## Am9513A

System Timing Controller

### **FINAL**

### **DISTINCTIVE CHARACTERISTICS**

- Five independent 16-bit counters

- High speed counting rates

- Up/down and binary/BCD counting

- Internal oscillator frequency source

- Tapped frequency scaler

- Programmable frequency output

- 8-bit or 16-bit bus interface

- Time-of-day option

- Alarm comparators on counters 1 and 2

- Complex duty cycle outputs

- One-shot or continuous outputs

- Programmable count/gate source selection

- Programmable input and output polarities

- Programmable gating functions

- Retriggering capability

- +5 volt power supply

- Standard 40-pin package

- SMD/DESC qualified

### **GENERAL DESCRIPTION**

The Am9513A System Timing Controller is an LSI circuit designed to service many types of counting, sequencing and timing applications. It provides the capability for programmable frequency synthesis, high resolution programmable duty cycle waveforms, retriggerable digital one-shots, time-of-day clocking, coincidence alarms, complex pulse generation, high resolution baud rate generation, frequency shift keying, stop-watching timing, event count accumulation, waveform analysis, etc. A variety of programmable operating modes and control features allows the Am9513A to be personalized for particular applications as well as dynamically reconfigured under program control.

The STC includes five general-purpose 16-bit counters. A variety of internal frequency sources and external pins may be selected as inputs for individual counters with software selectable active-high or active-low input polarity. Both hardware and software gating of each counter is available. Three-state outputs for each counter provide pulses or levels and can be active-high or active-low. The counters can be programmed to count up or down in either binary or BCD. The host processor may read an accumulated count at any time without disturbing the counting process. Any of the counters may be internally concatenated to form any effective counter length up to 80 bits.

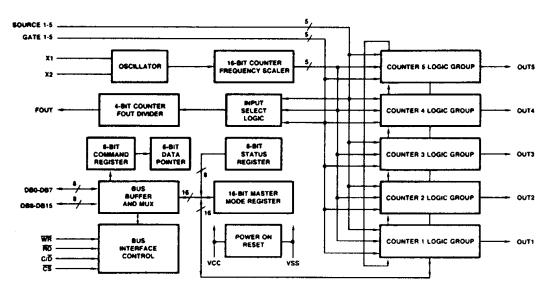

### **BLOCK DIAGRAM**

BD003381

Publication # Rev. Amendment F /0 Issue Date: August 1989

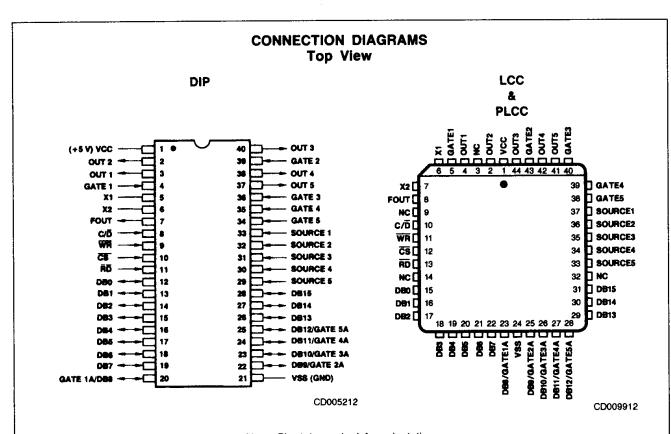

### Note: Pin 1 is marked for orientation.

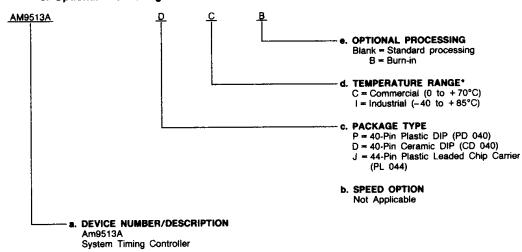

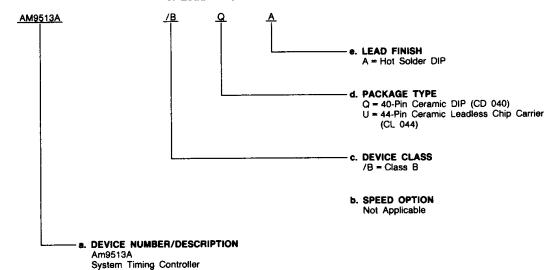

## ORDERING INFORMATION Standard Products

AMD standard products are available in several packages and operating ranges. The order number (Valid Combination) is formed by a combination of: a. Device Number

- b. Speed Option (if applicable)

- c. Package Type

- d. Temperature Range

- e. Optional Processing

# Valid Combinations AM9513A PC, DC, DCB, DIB, JC

\*This device is also available in Military temperature range.

Valid Combinations list configurations planned to be supported in volume for this device. Consult the local AMD sales office to confirm availability of specific valid combinations, to check on newly released combinations, and to obtain additional data on

**Valid Combinations**

AMD's standard military grade products.

### **ORDERING INFORMATION (continued)**

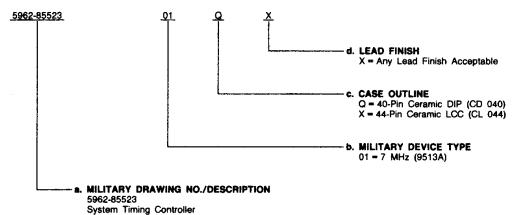

### Standard Military Drawing (SMD)/DESC Products

AMD products for Aerospace and Defense applications are available in several packages and operating ranges. Standard Military Drawing (SMD)/DESC products are fully compliant with MIL-STD-883C requirements. The order number (Valid Combination) for SMD/DESC products is formed by a combination of: a. Military Drawing Part Number

b. Device Type

c. Case Outline

d. Lead Finish

### **Valid Combinations**

| Valid Combinations |        |  |  |  |  |  |  |  |

|--------------------|--------|--|--|--|--|--|--|--|

| 5962-8552301       | QX, XX |  |  |  |  |  |  |  |

Valid Combinations list configurations planned to be supported in volume for this device. Consult the local AMD sales office to confirm availability of specific valid combinations or to check for newly released valid combinations.

### **Group A Tests**

Group A tests consist of Subgroups 1, 2, 3, 7, 8, 9, 10, 11.

2-118 Am9513A

### **ORDERING INFORMATION (continued)**

### **APL Products**

AMD products for Aerospace and Defense applications are available in several packages and operating ranges. APL (Approved Products List) products are fully compliant with MIL-STD-883C requirements. The order number (Valid Combination) for APL products is formed by a combination of: **a. Device Number**

- a. Device Number

- b. Speed Option (if applicable)

- c. Device Class

- d. Package Type

- e. Lead Finish

### **Valid Combinations**

|         | Valid Cor | nbinations |  |

|---------|-----------|------------|--|

| AM9513A |           | /BQA, /BUA |  |

Valid Combinations list configurations planned to be supported in volume for this device. Consult the local AMD sales office to confirm availability of specific valid combinations or to check for newly released valid combinations.

## Group A Tests

Group A tests consist of Subgroups 1, 2, 3, 7, 8, 9, 10, 11.

| Pin No.                 | Name                     | 1/0           | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|-------------------------|--------------------------|---------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1                       | vcc                      |               | +5 V Power Supply.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| 21                      | VSS                      | <del></del> - | Ground.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

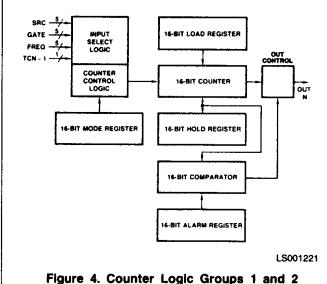

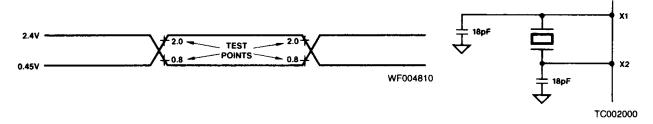

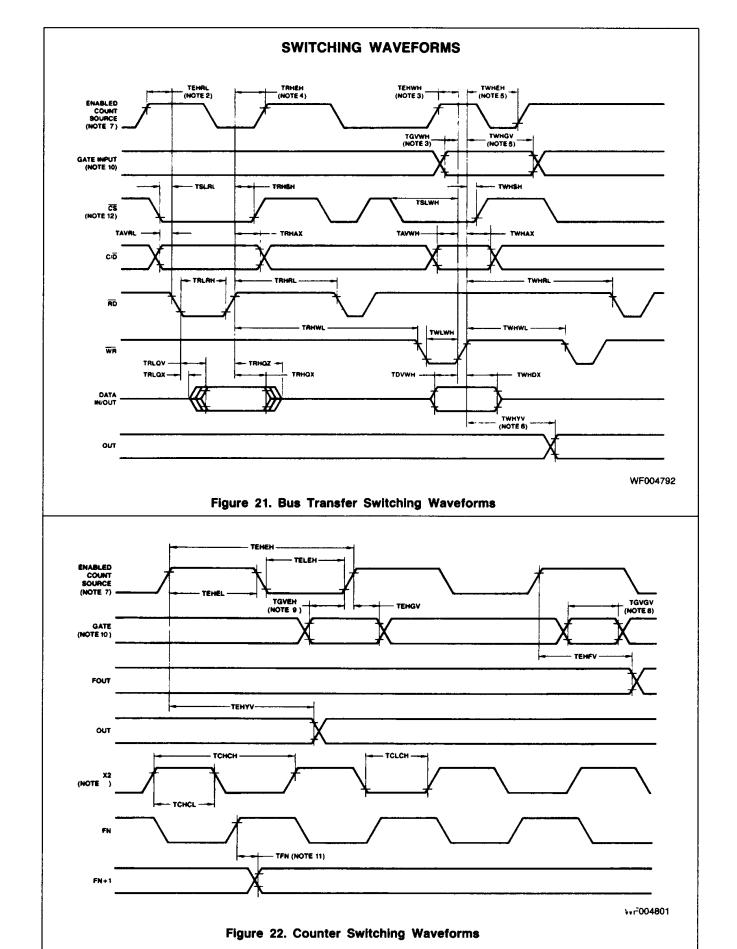

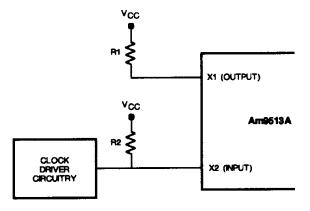

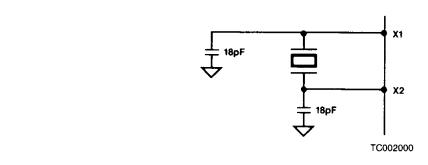

| 5, 6                    | X1, X2                   | O, I          | (Crystal). X1 and X2 are the connections for an external crystal used to determine the frequency of the internal oscillator. The crystal should be a parallel-resonant, fundamental-mode type. An RC or LC or other reactive network may be used instead of a crystal. For driving from an external frequency source, X1 should be left open and X2 should be connected to a TTL source and a pull-up resistor.                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| 7                       | FOUT                     | 0             | (Frequency Out). The FOUT output is derived from a 4-bit counter that may be programmed to divide its input by any integer value from 1 through 16 inclusive. The input to the counter is selected from any of 18 sources, including the internal scaled oscillator frequencies. FOUT may be gated on and off under softward control and when off will exhibit a low impedance to ground. Control over the various FOUT options resides in the Master Mode register. After power-up, FOUT provides a frequency that is 1/16 that of the oscillator The input source on power-up is F1.                                                                                                                                                                                                                                                                           |

| 4, 39,<br>36 – 34       | GATE1 - GATE5            | ı             | (Gate). The Gate inputs may be used to control the operations of individual counters by determining wher counting may proceed. The same Gate input may control up to three counters. Gate pins may also be selected as count sources for any of the counters and for the FOUT divider. The active polarity for a selected Gate input is programmed at each counter. Gating function options allow level-sensitive gating of edge-initiated gating. Other gating modes are available including one that allows the Gate input to select between two counter output frequencies. All gating functions may also be disabled. The active Gate input is conditioned by an auxiliary input when the unit is operating with an external 8-bit data bus. See Data Bus description. Schmitt-trigger circuitry on the GATE inputs allows slow transition times to be used. |

| 33 – 29                 | SRC1 - SRC5              | ı             | (Source). The Source inputs provide external signals that may be counted by any of the counters. Any Source line may be routed to any or all of the counters and the FOUT divider. The active polarity for a selected SRC input is programmed at each counter. Any duty cycle waveform will be accepted as long at the minimum pulse width is at least half the period of the maximum specified counting frequency for the part. Schmitt-trigger circuitry on the SRC inputs allows slow transition times to be used.                                                                                                                                                                                                                                                                                                                                            |

| 3, 2, 40,<br>38, 37     | OUT1 - OUT5              | 0             | (Counter). Each 3-state OUT signal is directly associated with a corresponding individual counter Depending on the counter configuration, the OUT signal may be a pulse, a square wave, or a complex duty cycle waveform. OUT pulse polarities are individually programmable. The output circuitry detects the counter state that would have been all bits zero in the absence of a reinitialization. That information is used to generate the selected waveform type. An optional output mode for Counters 1 and 2 overrides the normal output mode and provides a true OUT signal when the counter contents match the contents of an Alarm register.                                                                                                                                                                                                           |

| 12 - 19, 20,<br>22 - 28 | DB0 - DB7,<br>DB8 - DB15 | 1/0           | (Data Bus). The 16 bidirectional Data Bus lines are used for information exchanges with the host processor HIGH on a Data Bus line corresponds to one and LOW corresponds to zero. These lines act as inputs when WR and CS are active and as outputs when RD and CS are active. When CS is inactive, these pins are placed in a high-impedance state.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|                         |                          |               | After power-up or reset, the data bus will be configured for 8-bit width and will use only D80 through D87 D80 is the least significant and D87 is the most significant bit position. The data bus may be reconfigured for 16-bit width by changing a control bit in the Master Mode register. This is accomplished by writing an 8 bit command into the low-order D8 lines while holding the D813 – D815 lines at a logic high level Thereafter, all 16 lines can be used, with D80 as the least significant and D815 as the most significant bi position.                                                                                                                                                                                                                                                                                                      |

|                         |                          |               | When operating in the 8-bit data bus environment, DB8 – DB15 will never be driven active by the Am9513A. DB8 through DB12 may optionally be used as additional Gate inputs (see Figure 2). If unused they should be held HIGH. When pulled LOW, a GATENA signal will disable the action of the corresponding counter N gating. DB13 – DB15 should be held HIGH in 8-bit bus mode whenever CS and WR are simultaneously active.                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| 10                      | CS                       | ı             | (Chip Select). The active-low Chip Select input enables Read and Write operations on the data bus. Wher Chip Select is HIGH, the Read and Write inputs are ignored. The first Chip Select signal after power-up is used to clear the power-on reset circuitry. If Chip Select is tied to ground permanently, the power-on rese circuitry may not function. In such a configuration, the software reset command must be issued following power-up to reset the Am9513A.                                                                                                                                                                                                                                                                                                                                                                                           |

| 11                      | RD                       | Ī             | (Read). The active-low Read signal is conditioned by Chip Select and indicates that internal information is to be transferred to the data bus. The source will be determined by the port being addressed and, for Data Port reads, by the contents of the Data Pointer register. WR and RD should be mutually exclusive.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| 9                       | WA                       |               | (Write). The active-low Write signal is conditioned by Chip Select and indicates that data bus information is to be transferred to an internal location. The destination will be determined by the port being addressed and, for Data Port writes, by the contents of the Data Pointer register. WR and RD should be mutually exclusive.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| 8                       | C/Ď                      | ı             | (Control/Data). The Control/Data signal selects source and destination locations for Read and Write operations on the data bus. Control Write operations load the Command register and the Data Pointer Control Read operations output the Status register. Data Read and Data Write transfers communicate with all other internal registers. Indirect addressing at the data port is controlled internally by the Data Pointer register.                                                                                                                                                                                                                                                                                                                                                                                                                        |

2-120 Am9513A

| Signal        | Abbreviation | Type   | Pins |

|---------------|--------------|--------|------|

| + 5 Volts     | vcc          | Power  | 1    |

| Ground        | vss          | Power  | 1 ′  |

| Crystal       | X1, X2       | Ο, Ι   | 2    |

| Read          | RD           | Input  | 1    |

| Write         | WR           | input  | 1    |

| Chip Select   | CS           | Input  | 1    |

| Control/Data  | C/D          | Input  | 1    |

| Source N      | SRC          | Input  | 5    |

| Gate N        | GATE         | Input  | 5    |

| Data Bus      | DB           | 1/0    | 16   |

| Frequency Out | FOUT         | Output | 1    |

| Out N         | OUT          | Output | 5    |

Figure 1. Interface Signal Summary

Figure 1 summarizes the interface signals and their abbreviations for the STC.

| Dagkage        | Data Bus W | idth (MM14) |  |  |

|----------------|------------|-------------|--|--|

| Package<br>Pin | 16 Bits    | 8 Bits      |  |  |

| 12             | DB0        | DB0         |  |  |

| 13             | DB1        | DB1         |  |  |

| 14             | DB2        | DB2         |  |  |

| 15             | DB3        | DB3         |  |  |

| 16             | DB4        | DB4         |  |  |

| 17             | DB5        | DB5         |  |  |

| 18             | DB6        | DB6         |  |  |

| 19             | DB7        | D87         |  |  |

| 20             | DB8        | GATE 1A     |  |  |

| 22             | DB9        | GATE 2A     |  |  |

| 23             | DB10       | GATE 3A     |  |  |

| 24             | DB11       | GATE 4A     |  |  |

| 25             | DB12       | GATE 5A     |  |  |

| 26             | DB13       | (VIH)       |  |  |

| 27             | DB14       | (VIH)       |  |  |

| 28             | DB15       | (VIH)       |  |  |

Figure 2. Data Bus Assignments

### Interface Considerations

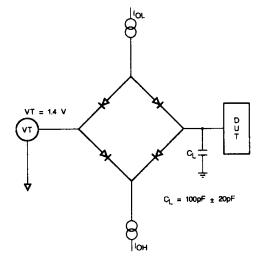

All of the input and output signals for the Am9513A are specified with logic levels compatible with those of standard TTL circuits. In addition to providing TTL compatible voltage levels, other output conditions are specified to help configure non-standard interface circuitry. The logic level specifications take into account all worst-case combinations of the three variables that affect the logic level thresholds: ambient temperature, supply voltage and processing parameters. A change in any of these toward nominal values will improve the actual operating margins and will increase noise immunity.

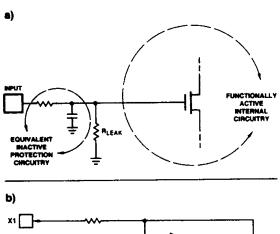

Unprotected open gate inputs of high quality MOS transistors exhibit very high resistances on the order of perhaps 10<sup>14</sup> ohms. It is easy, therefore, in some circumstances, for charge to enter the gate node of such an input faster than it can be discharged and consequently, for the gate voltage to rise high enough to break down the oxides and destroy the transistor.

All inputs to the Am9513A include protection networks to help prevent damaging accumulations of static charge. The protection circuitry is designed to slow the transitions of incoming current surges and to provide low-impedance discharge paths for voltages beyond the normal operating levels. Note, however, that input energy levels can nonetheless be too high to be successfully absorbed. Conventional design, storage, and handling precautions should be observed so that the protection networks themselves are not overstressed.

Within the limits of normal operation, the input protection circuitry is inactive and may be modeled as a lumped series RC as shown in Figure 3(a). The functionally active input connection during normal operation is the gate of a MOS transistor. No active sources or drains are connected to the inputs so that neither transient nor steady-state currents are impressed on the driving signals other than the charging or discharging of the input capacitance and the accumulated leakage associated with the protection network and the input circuit.

Figure 3. Input Circuitry

The only exception to the purely capacitive input case is the X2 crystal input. As shown in Figure 3(b) an internal resistor connects X1 and X2 in addition to the protection network. The resistor is a modestly high value of more than 100kohms.

Fanout from the driving circuitry into the Am9513A inputs will generally be limited by transition time considerations rather than DC current limitations when the loading is dominated by conventional MOS circuits. In an operating environment, all inputs should be terminated so they do not float and therefore will not accumulate stray static charges. Unused inputs should be tied directly to Ground or VCC, as appropriate. An input in use will have some type of logic output driving it, and termination during operation will not be a problem. Where inputs are driven from logic external to the card containing this chip, however, on-board termination should be provided to protect the chip when the board is unplugged (the input would otherwise float). A pull-up resistor or a simple inverter or gate will suffice.

#### **DETAILED DESCRIPTION**

The Am9513A System Timing Controller (STC) is a support device for processor oriented systems that is designed to enhance the available capability with respect to counting and timing operations. It provides the capability for programmable frequency synthesis, high resolution programmable duty cycle waveforms, retriggerable digital timing functions, time-of-day clocking, coincidence alarms, complex pulse generation, high resolution baud rate generation, frequency shift keying, stopwatching timing, event count accumulation, waveform analysis and many more. A variety of programmable operating modes and control features allow the Am9513A to be personalized for particular applications as well as dynamically reconfigured under program control.

The STC includes five general-purpose 16-bit counters. A variety of internal frequency sources and external pins may be selected as inputs for individual counters with software selectable active-high or active-low input polarity. Both hardware and software gating of each counter is available. Three-state outputs for each counter provide either pulses or levels. The counters can be programmed to count up or down in either binary or BCD. The accumulated count may be read without disturbing the counting process. Any of the counters may be internally concatenated to form an effective counter length of up to 80 bits.

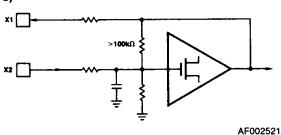

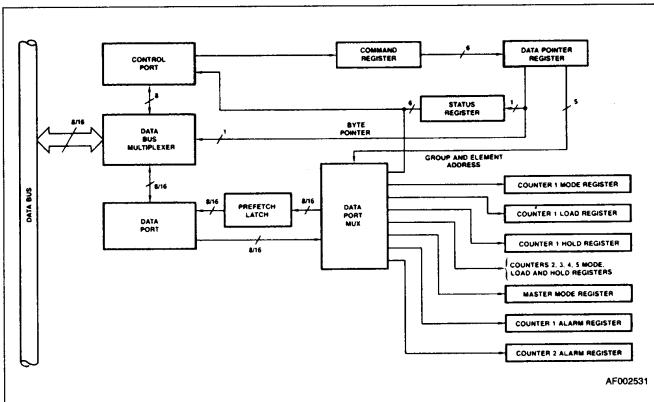

The Am9513A block diagrams indicate the interface signals and the basic flow of information. Internal control lines and the internal data bus have been omitted. The control and data registers are all connected to a common internal 16-bit bus. The external bus may be 8- or 16-bits wide; in the 8-bit mode, the internal 16-bit information is multiplexed to the low order data bus pins DB0 through DB7.

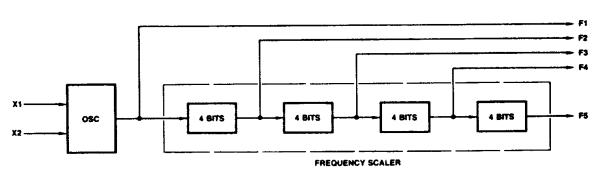

An internal oscillator provides a convenient source of frequencies for use as counter inputs. The oscillator's frequency is controlled at the X1 and X2 interface pins by an external reactive network such as a crystal. The oscillator output is divided by the Frequency Scaler to provide several subfrequencies. One of the scaled frequencies (or one of ten input signals) may be selected as an input to the FOUT divider and then comes out of the chip at the FOUT interface pin.

The STC is addressed by the external system as two locations: a Control port and a Data port. The Control port

provides direct access to the Status and Command registers, as well as allowing the user to update the Data Pointer register. The Data port is used to communicate with all other addressable internal locations. The Data Pointer register controls the Data port addressing.

Among the registers accessible through the Data port are the Master Mode register and five Counter Mode registers, one for each counter. The Master Mode register controls the programmable options that are not controlled by the Counter Mode registers.

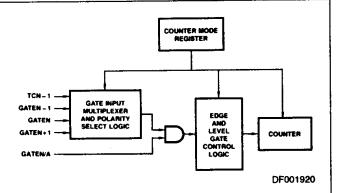

Each of the five general-purpose counters is 16-bits long and is independently controlled by its Counter Mode register. Through this register, a user can software select one of 16 sources as the counter input, a variety of gating and repetition modes, up or down counting in binary or BCD and active-high or active-low input and output polarities.

Associated with each counter are a Load register and a Hold register, both accessible through the Data port. The Load register is used to automatically reload the counter to any predefined value, thus controlling the effective count period. The Hold register is used to save count values without disturbing the count process, permitting the host processor to read intermediate counts. In addition, the Hold register may be used as a second Load register to generate a number of complex output waveforms.

All five counters have the same basic control logic and control registers. Counters 1 and 2 have additional Alarm registers and comparators associated with them, plus the extra logic necessary for operating in a 24-hour time-of-day mode. For real-time operation, the time-of-day logic will accept 50Hz, 60Hz or 100Hz input frequencies.

Each general counter has a single dedicated output pin. It may be turned off when the output is not of interest or may be configured in a variety of ways to drive interrupt controllers, Darlington buffers, bus drivers, etc. The counter inputs, on the other hand, are specifically not dedicated to any given interface line. Considerable versatility is available for configuring both the input and the gating of individual counters. This not only permits dynamic reassignment of inputs under software control, but also allows multiple counters to use a single input and a single gate pin to control more than one counter. Indeed, a single pin can be the gate for one counter and, at the same time, the count source for another.

GATE 5/ INPUT SELECT TOUT CONTROL COUNTER CONTROL LOGIC 16-BIT HOLD REGISTER

16-BIT MODE REGISTER

16-BIT HOLD REGISTER

LS001231

Figure 5. Counter Logic Groups 3, 4 and 5

SRC

Figure 6. Am9513A Register Access

|           | El       | ement Cyc | e        | Hold Cycle |

|-----------|----------|-----------|----------|------------|

|           | Mode     | Load      | Hold     | Hold       |

|           | Register | Register  | Register | Register   |

| Counter 1 | FF01     | FF09      | FF11     | FF19       |

| Counter 2 | FF02     | FF0A      | FF12     | FF1A       |

| Counter 3 | FF03     | FF0B      | FF13     | FF1B       |

| Counter 4 | FF04     | FF0C      | FF14     | FF1C       |

| Counter 5 | FF05     | FF0D      | FF15     | FF1D       |

Master Mode Register = FF17 Alarm 1 Register = FF07 Alarm 2 Register = FF0F Status Register = FF1F

#### Notes:

- 1. All codes are in hex.

- When used with an 8-bit bus, only the two low order hex digits should be written to the command port; the "FF" prefix should be used only for a 16-bit data bus interface.

Figure 8. Load Data Pointer Commands

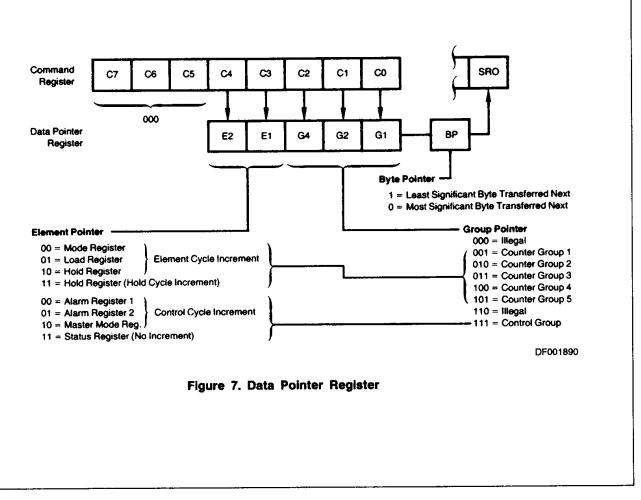

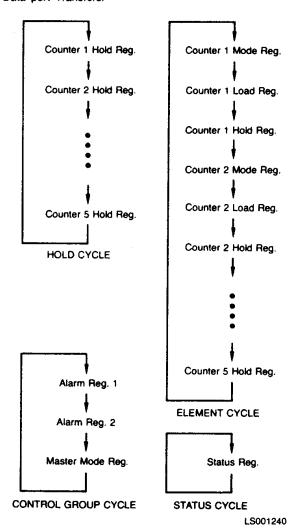

Sequencing is enabled by clearing Master Mode bit 14 (MM14) to zero. As shown in Figure 9 several types of sequencing are available depending on the data bus width being used and the initial Data Pointer value entered by command.

When E1 = 0 or E2 = 0 and G4, G2, G1 points to a Counter Group, the Data Pointer will proceed through the Element cycle. The Element field will automatically sequence through the three values 00, 01 and 10 starting with the value entered. When the transition from 10 to 00 occurs, the Group field will also be incremented by one. Note that the Element field in this case does not sequence to a value of 11. The Group field circulates only within the five Counter Group codes.

If E2, E1 = 11 and a Counter Group are selected, then only the Group field is sequenced. This is the Hold cycle. It allows the Hold registers to be sequentially accessed while bypassing the Mode and Load registers. The third type of sequencing is the Control cycle. If G4, G2, G1 = 111 and E2, E1  $\neq$  11, the Element Pointer will be incremented through the values 00, 01 and 10, with no change to the Group Pointer.

When G4, G2, G1 = 111 and E2, E1 = 11, no incrementing takes place and only the Status register will be available through the Data port. Note that the Status register can also always be read directly through the Control port.

For all these auto-sequencing modes, if an 8-bit data bus is used, the Byte pointer will toggle after every data transfer to allow the least and most significant bytes to be transferred before the Element or Group fields are incremented.

### **Prefetch Circuit**

To minimize the read access time to internal Am9513A registers, a prefetch circuit is used for all read operations through the Data port. Following each read or write operation through the Data port, the Data Pointer register is updated to point to the next register to be accessed. Immediately following this update, the new register data is transferred to a special prefetch latch at the interface pad logic. When the user performs a subsequent read of the Data port, the data bus drivers are enabled, outputting the prefetched data on the bus. Since the internal data register is accessed prior to the start of the read operation, its access time is transparent to the user. To keep the prefetched data consistent with the Data Pointer, prefetches are also performed after each write to the Data port and after execution of the "Load Data Pointer" com-

mand. The following rules should be kept in mind regarding Data port Transfers.

Figure 9. Data Pointer Sequencing

- 1. The Data Pointer register should always be reloaded before reading from the Data port if a command, other than "Load Data Pointer," was issued to the Am9513A following the last Data port read or write. The Data Pointer does not have to be loaded again if the first Data port transaction after a command entry is a write, since the Data port write will automatically cause a new prefetch to occur.

- 2. Operating modes N, O, Q, R and X allow the user to save the counter contents in the Hold register by applying an active-going gate edge. If the Data Pointer register had been pointing to the Hold register in question, the prefetched value will not correspond to the new value saved in the Hold Register. To avoid reading an incorrect value, a new "Load Data Pointer" command should be issued before attempting to read the saved data. A Data port write (to another register) will also initiate a prefetch; subsequent reads will access the recently saved Hold register data. Many systems will use the "saving" gate edge to interrupt the host CPU. In systems such as this, the interrupt service routine should issue a "Load Data Pointer" command prior to reading the saved data.

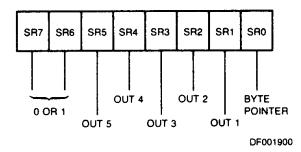

### Status Register

The 8-bit read-only Status register indicates the state of the Byte Pointer bit in the Data Pointer register and the state of the

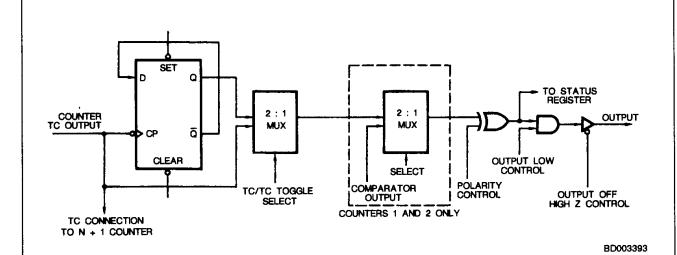

OUT signal for each of the general counters. See Figures 10 and 17. The OUT signals reported are those internal to the chip after the polarity-select logic and just before the three-state interface buffer circuitry. Bits SR6 and SR7 may be 0 or 1.

The Status register OUT bit reflects an active-high or active-low TC output or a TC Toggled output, as programmed in the Output Control Field of the Counter Mode register. That is, it reflects the exact state of the OUT pin. When the low-impedance to Ground Output option (CM2-CM0 = 000) is selected, the Status register will reflect an active-high TC Output. When a high-impedance Output option (CM2-CM0 = 100) is selected, the Status register will reflect an active-low TC output.

For Counters 1 and 2, the OUT pin will reflect the comparator output if the comparators are enabled. The Status register bit and OUT pin are active-high if CM2 = 0 and active-low if CM2 = 1. When the high-impedance option is selected and the comparator is enabled, the status register bit will reflect an active-high comparator output. When the low-impedance to Ground option is selected and the comparator is enabled, the status register bit will reflect an active-low comparator output.

The Status register is normally accessed by reading the Control port (see Figure 6) but may also be read via the Data port as part of the Control Group.

Figure 10. Status Register Bit Assignments

### **DATA PORT REGISTERS**

### **Counter Logic Groups**

As shown in Figures 4 and 5, each of the five Counter Logic Groups consists of a 16-bit general counter with associated control and output logic, a 16-bit Load register, a 16-bit Hold register and a 16-bit Mode register. In addition, Counter Groups 1 and 2 also include 16-bit Comparators and 16-bit Alarm registers. The comparator/alarm functions are controlled by the Master Mode register. The operation of the Counter Mode registers is the same for all five counters. The host CPU has both read and write access to all registers in the Counter Logic Groups through the Data port. The counter itself is never directly accessed.

### Load Register

The 16-bit read/write Load register is used to control the effective length of the general counter. Any 16-bit value may be written into the Load register. That value can then be transferred into the counter each time the Terminal Count (TC) occurs. "Terminal Count" is defined as that period of time when the counter contents would have been zero if an external value had not been transferred into the counter. Thus, the terminal count frequency can be the input frequency

divided by the value in the Load register. In all operating modes, either the Load or Hold register will be transferred into the counter when TC occurs. In cases where values are being accumulated in the counter, the Load register action can become transparent by filling the Load register with all zeros.

### **Hold Register**

The 16-bit read/write Hold register is dual-purpose. It can be used in the same way as the Load register, thus offering an alternate source for module definition for the counter. The Hold register may also be used to store accumulated counter values for later transfer to the host processor. This allows the count to be sampled while the counting process proceeds without interruption. Transfer of the counter contents into the Hold register is accomplished by the hardware interface in some operating modes or by software commands at any time.

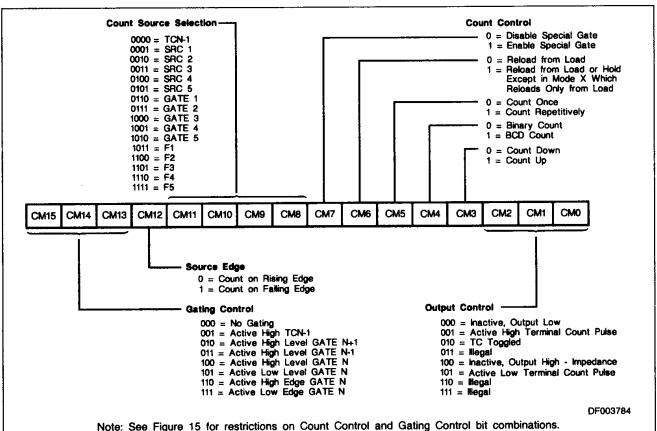

### Counter Mode Register

The 16-bit read/write Counter Mode register controls the gating, counting, output and source select functions within each Counter Logic Group. The "Counter Mode Control Options" section of this document describes the detailed control options available. Figure 16 shows the bit assignments for the Counter Mode registers.

### Alarm Registers and Comparators

Added functions are available in the Counter Logic Groups for Counters 1 and 2 (see Figure 4). Each contains a 16-bit Alarm register and a 16-bit Comparator. When the value in the counter reaches the value in the Alarm register, the Comparator output will go true. The Master Mode register contains control bits to individually enable/disable the comparators. When enabled, the comparator output appears on the OUT pin of the associated counter in place of the normal counter output. The output will remain true as long as the comparison is true, that is, until the next input causes the count to change. The polarity of the Comparator output will be active-high if the Output Control field of the Counter Mode register is 001 or 010 and active-low if the Output Control field is 101.

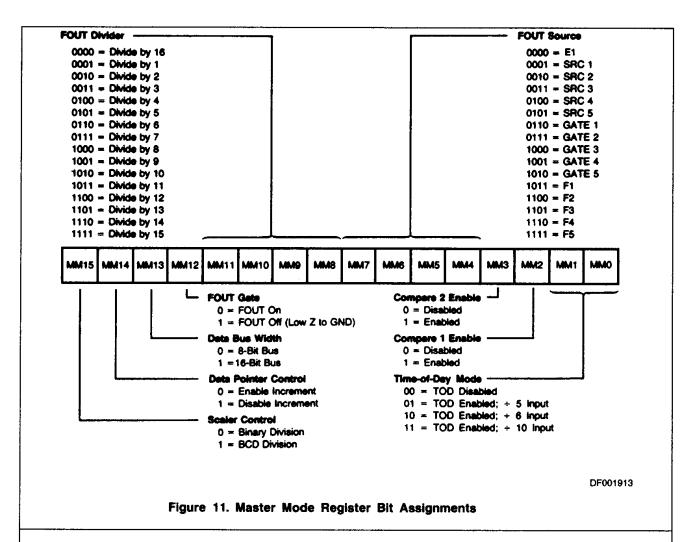

### MASTER MODE CONTROL OPTIONS

The 16-bit Master Mode (MM) register is used to control those internal activities that are not controlled by the individual Counter Mode registers. This includes frequency control, Time-of-Day operation, comparator controls, data bus width and data pointer sequencing. Figure 11 shows the bit assignments for the Master Mode register. This section describes the use of each control field.

Master Mode register bits MM12, MM13 and MM14 can be individually set and reset using commands issued to the Command register. In addition, they can all be changed by writing directly to the Master Mode register.

After power-on reset or a Master Reset command, the Master Mode register is cleared to an all zero condition. This results in the following configuration:

Time-of-Day disabled

Both Comparators disabled

FOUT Source is frequency F1

FOUT Divider set for divide-by-16

FOUT gated on

Data Bus 8 bits wide

Data Pointer Sequencing enabled

Frequency Scaler divides in binary

### Time-of-Day

Bits MM0 and MM1 of the Master Mode register specify the Time-of-Day (TOD) options. When MM0 = 0 and MM1 = 0, the special logic used to implement TOD is disabled, and Counters 1 and 2 will operate in exactly the same way as Counters 3, 4 and 5. When MM0 = 1 or MM1 = 1, additional counter decoding and control logic is enabled on Counters 1 and 2, which causes their decades to turn over at the counts that generate appropriate 24-hour TOD accumulations. For additional information, see the Time-of-Day chapter in the 9513A System timing controller technical manual.

### Comparator Enable

Bits MM2 and MM3 control the Comparators associated with Counters 1 and 2. When a Comparator is enabled, its output is substituted for the normal counter output on the associated OUT1 or OUT2 pin. The comparator output will be active-high if the output control field of the Counter Mode register is 001 or 010 and active-low for a code of 101. Once the compare output is true, it will remain so until the count changes and the comparison therefore goes false.

The two Comparators can always be used individually in any operating mode. One special case occurs when the Time-of-Day option is revoked and both Comparators are enabled. The operation of Comparator 2 will then be conditioned by Comparator 1 so that a full 32-bit compare must be true in order to generate a true signal on OUT2. OUT1 will continue, as usual, to reflect the state of the 16-bit comparison between Alarm 1 and Counter 1.

### **FOUT Source**

Master Mode bits MM4 through MM7 specify the source input for the FOUT divider. Fifteen inputs are available for selection, and they include the five Source pins, the five Gate pins and the five internal frequencies derived from the oscillator. The 16th combination of the four control bits (all zeros) is used to assure that an active frequency is available at the input to the FOUT divider following reset.

### **FOUT Divider**

Bits MM8 through MM11 specify the dividing ratio for the FOUT Divider. The FOUT source (selected by bits MM4 through MM7) is divided by an integer value between 1 and 16, inclusive, and is then passed to the FOUT output buffer. After power-on or reset, the FOUT divider is set to divide-by-16.

### **FOUT Gate**

Master Mode bit MM12 provides a software gating capability for the FOUT signal. When MM12 = 1, FOUT is off and in a low-impedance state to ground. MM12 may be set or cleared in conjunction with the loading of the other bits in the Master Mode register; alternatively, there are commands that allow MM12 to be individually set or cleared directly without changing any other Master Mode bits. After power-up or reset, FOUT is gated on.

When changing the FOUT divider ratio or FOUT source, transient pulses as short as half the period of the FOUT source may appear on the FOUT pin. Turning the FOUT gate on or off can also generate a transient. This should be considered when using FOUT as a system clock source.

#### **Bus Width**

Bit MM13 controls the multiplexer at the data bus interface in order to configure the part for an 8-bit or 16-bit external bus. The internal bus is always 16-bits wide. When MM13 = 1, 16-bit data is transferred directly between the internal bus and all 16 of the external bus lines. In this configuration, the Byte Pointer bit in the Data Pointer register remains set at all times. When MM13 = 0, 16-bit internal data is transferred a byte at a time to and from the eight low-order external data bus lines. The Byte Pointer bit toggles with each byte transfer in this mode.

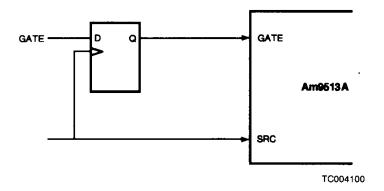

When the Am9513A is set to operate with an 8-bit data bus width, pins DB8 through DB15 are not used for the data bus and are available for other functions. Pins DB13 through DB15 should be tied high. Pins DB8 through DB12 are used as auxiliary gating inputs and are labeled GATE1A through GATE5A respectively. The auxiliary gate pin, GATENA, is logically ANDed with the gate input to Counter N, as shown in Figure 12. The output of the AND gate is then used as the gating signal for Counter N.

### **Data Pointer Sequencing**

Bit MM14 controls the Data Pointer logic to enable or disable the automatic sequencing functions. When MM14 = 1, the contents of the Data Pointer can be changed only directly by entering a command. When MM14 = 0, several types of automatic sequencing of the Data Pointer are available. These are described in the Data Pointer register section of this document.

Figure 12. Gating Control

Thus, the host processor, by controlling MM14, may repetitively read/write a single internal location, or may sequentially read/write groups of locations. Bit MM14 can be loaded by writing to the Master Mode register or can be set or cleared by software command.

#### **Scaler Ratios**

Master Mode bit MM15 controls the counting configuration of the Frequency Scaler counter. When MM15 = 0, the Scaler divides the oscillator frequency in binary steps so that each subfrequency is 1/16 of the preceding frequency. When MM15 = 1, the Scaler divides in BCD steps so that adjacent frequencies are related by ratios of 10 instead of 16 (see Figure 13).

AF002541

| Frequency | BCD<br>Scaling<br>MM15 = 1 | Binary<br>Scaling<br>MM15 = 0 |  |  |

|-----------|----------------------------|-------------------------------|--|--|

| F1        | OSC                        | OSC                           |  |  |

| F2        | F1 ÷ 10                    | F1 ÷ 16                       |  |  |

| F3        | F1 ÷ 100                   | F1 ÷ 256                      |  |  |

| F4        | F1 ÷ 1,000                 | F1 ÷ 4,096                    |  |  |

| F5        | F1 ÷ 10,000                | F1 ÷ 65,536                   |  |  |

Figure 13. Frequency Scaler Ratios

| Counter Mode                                                                                                                       |          | _              | _       |          | T =          | _             |     |          |      |     |          |          |

|------------------------------------------------------------------------------------------------------------------------------------|----------|----------------|---------|----------|--------------|---------------|-----|----------|------|-----|----------|----------|

|                                                                                                                                    | A        | В              | С       | D        | E            | F             | G   | Н        | 1    | J   | K        | L        |

| Special Gate (CM7)                                                                                                                 | 0        | 0              | 0       | 0        | 0            | 0             | 0   | 0        | 0    | 0   | 0        | 0        |

| Reload Source (CM6)                                                                                                                | 0        | 0              | 0       | 0        | 0            | 0             | 1   | 1        | 1    | 1   | 1        | 1        |

| Repetition (CM5)                                                                                                                   | 0        | 0              | 0       | 1        | 1            | 1             | 0   | 0        | 0    | 1   | 1        | 1        |

| Gate Control (CM15-CM13)                                                                                                           | 000      | LEVEL          | EDGE    | 000      | LEVEL        | EDGE          | 000 | LEVEL    | EDGE | 000 | LEVEL    | EDGE     |

| Count to TC once, then disarm                                                                                                      | X        | X              | X       | <u> </u> |              | ļ             |     | <u> </u> |      | ļ   |          |          |

| Count to TC twice, then disarm                                                                                                     | -        | ļ              | ļ       | ·        |              | <del></del> _ | X   | X        | X    |     | <u> </u> |          |

| Count to TC repeatedly without disarming                                                                                           | <u> </u> | <del></del>    | ļ       | X        | X            | X             | .,  |          |      | Х   | X        | X        |

| Gate input does not gate counter input                                                                                             | ×        | <del>  ,</del> | ļ       | X        | <del> </del> |               | X   |          |      | X   | ļ        | ļ        |

| Count only during active gate level                                                                                                |          | X              | <b></b> |          | X            |               |     | X        |      |     | X        | <u> </u> |

| Start count on active gate edge and stop count on next TC                                                                          |          |                | Х       | ···      |              | Х             |     |          |      |     |          |          |

| Start count on active gate edge and stop count on second TC                                                                        |          |                |         |          | <u></u>      |               |     |          | x    |     |          | ×        |

| No hardware retriggering                                                                                                           | Х        | Х              | Х       | Х        | Х            | Х             | Х   | X        | Х    | Х   | Х        | ×        |

| Reload counter from Load register on TC                                                                                            | Х        | Х              | Х       | Х        | Х            | Х             |     |          |      |     |          |          |

| Reload counter on each TC, alternating reload source between Load and Hold registers                                               |          |                |         |          |              |               | X   | х        | х    | Х   | Х        | х        |

| Transfer Load register into counter on each TC that gate is LOW, transfer Hold register into counter on each TC that gate is HIGH. |          |                |         |          |              |               |     |          |      |     |          |          |

| On active gate edge transfer counter into Hold register and then reload counter from Load register                                 |          |                |         |          |              |               |     |          |      |     |          |          |

|                                                                                                                                    |          |                |         |          |              |               |     |          |      |     |          |          |

| Counter Mode                                                                                                                       | М        | N              | 0       | Р        | a            | R             | S   | Т        | IJ   | ٧   | w        | ×        |

| Special Gate (CM7)                                                                                                                 | 1        | 1              | 1       | 1        | 1            | 1             | 1   | 1        | 1    | 1   | 1        | 1        |

| Reload Source (CM6)                                                                                                                | 0        | 0              | 0       | 0        | 0            | 0             | 1   | 1        | 1    | 1   | 1        | 1        |

| Repetition (CM5)                                                                                                                   | 0        | 0              | 0       | 1        | 1            | 1             | 0   | 0        | 0    | 1   | 1        | 1        |

| Gate Control (CM15-CM13)                                                                                                           | 000      | LEVEL          | EDGE    | 000      | LEVEL        | EDGE          | 000 | LEVEL    | EDGE | 000 | LEVEL    | EDGE     |

| Count to TC once, then disarm                                                                                                      |          | Х              | Х       |          |              |               |     |          |      |     |          |          |

| Count to TC twice, then disarm                                                                                                     |          |                |         |          |              |               | Х   |          |      |     |          |          |

| Count to TC repeatedly without disarming                                                                                           |          |                |         |          | X            | х             |     |          |      | Х   |          | Х        |

| Gate input does not gate counter input                                                                                             |          |                |         |          |              |               | Х   |          |      | Х   |          |          |

| Count only during active gate level                                                                                                |          | х              |         |          | Х            |               |     |          |      |     |          |          |

| Start count on active gate edge and stop count on next TC                                                                          |          |                | х       |          |              | х             |     |          |      |     |          | ×        |

| Start count on active gate edge and stop count on second TC                                                                        |          |                |         |          |              |               | -   |          | ·    |     |          |          |

| No hardware retriggering                                                                                                           |          |                |         |          |              |               | х   |          |      | х   |          | X        |

| Reload counter from Load register on TC                                                                                            |          | Х              | Х       |          | Х            | Х             |     |          |      |     |          | X        |

| Reload counter on each TC, alternating reload source between Load and Hold registers.                                              |          |                |         |          |              |               |     |          |      |     |          |          |

| Transfer Load register into counter on each TC that gate is LOW, transfer Hold register into counter on each TC that gate is HIGH. |          |                |         |          |              |               | х   |          |      | х   |          |          |

| On active gate edge transfer counter into Hold register and then reload counter from Load register                                 |          | х              | х       |          | х            | х             |     |          |      |     |          |          |

| On active gate edge transfer counter into Hold register, but counting continues                                                    |          |                |         |          |              |               |     |          |      |     |          | X        |

Notes: 1. Counter modes M, P, T, U and W are reserved and should not be used. 2. Mode X is available for Am9513A only.

Figure 14. Counter Mode Operating Summary

### **COUNTER MODE DESCRIPTIONS**

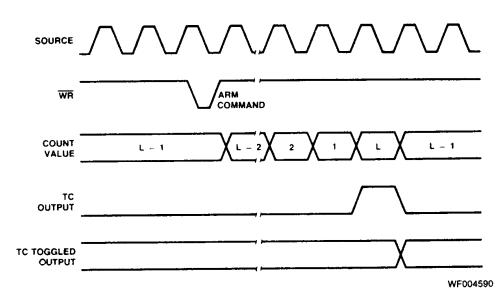

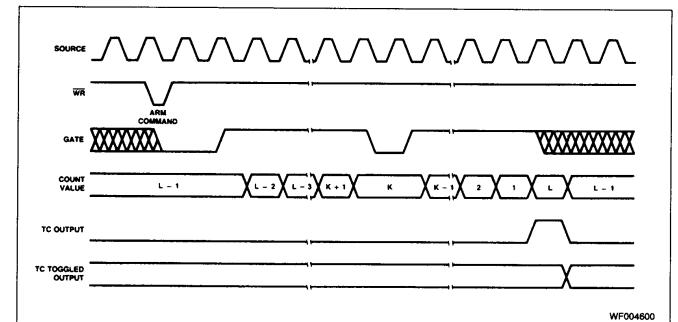

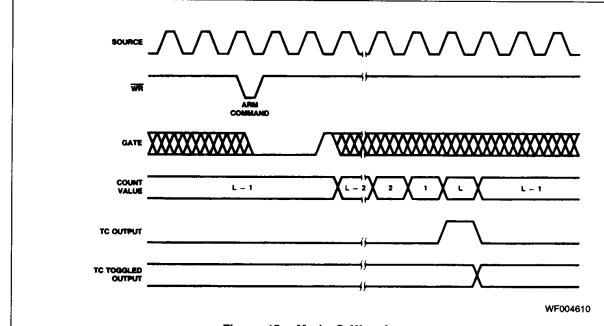

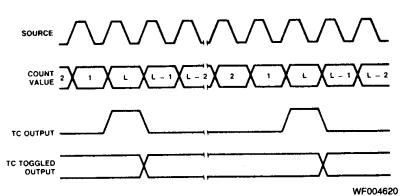

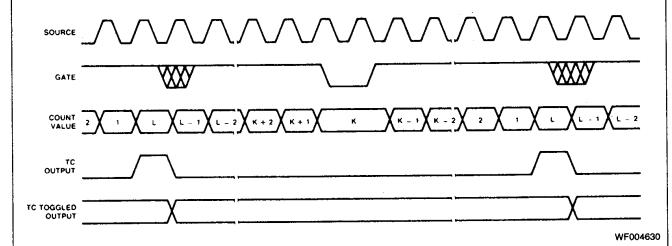

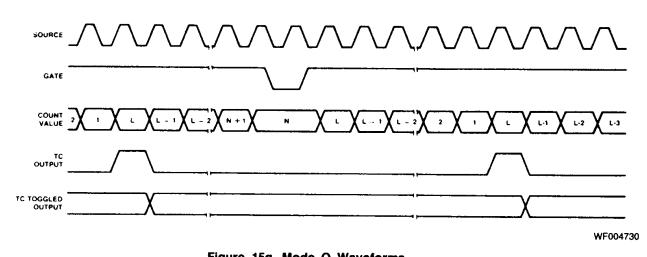

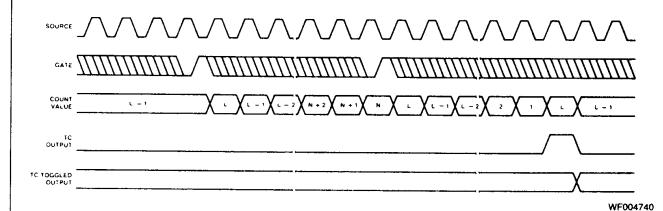

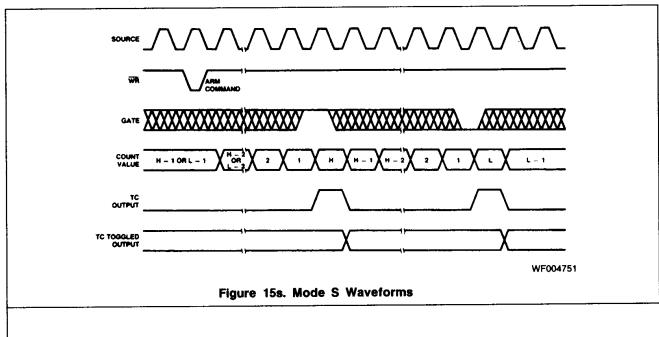

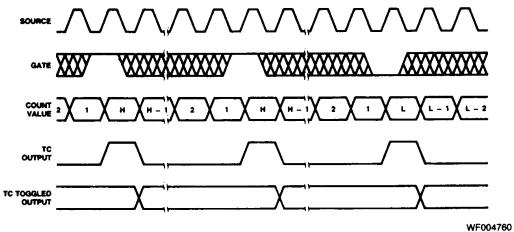

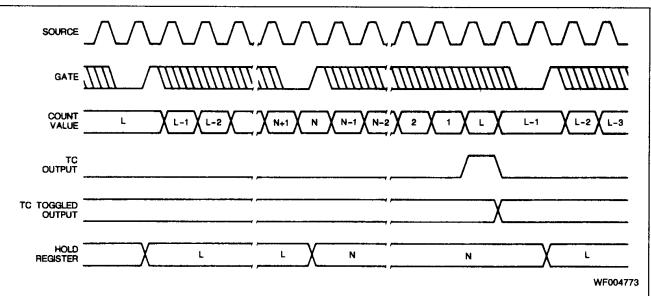

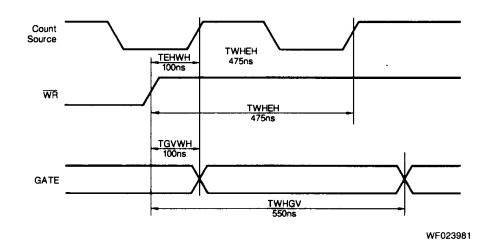

Counter Mode register bits CM15--CM13 and CM7--CM5 select the operating mode for each counter (see Figure 14). To simplify references to a particular mode, each mode is assigned a letter from A through X. Representative waveforms for the counter modes are illustrated in Figures 15a through 15v. (Because the letter suffix in the figure number is keyed to the mode, Figures 15m, 15p, 15t, 15u and 15w do not exist.) The figures assume down counting on rising source edges. Those modes which automatically disarm the counter (CM5 = 0) are shown with the WR plus entering the required ARM command; for modes which count repetitively (CM5 = 1),

the ARM command is omitted. The retriggering modes (N, O, Q and R) are shown with one retrigger operation. Both a TC output waveform and a TC Toggled output waveform are shown for each mode. The symbols L and H are used to represent count values equal to the Load and Hold register contents, respectively. The symbols K and N represent arbitrary count values. For each mode, the required bit pattern in the Counter Mode register is shown; "don't care" bits are marked "X." These figures are designed to clarify the mode descriptions; the Am9513A Electrical Specification should be used as the authoritative reference for timing relationships between signals.

2-128 Am9513A To keep the following mode descriptions concise and to the point, the phrase "source edges" is used to refer to active-going source edges only, not to inactive-going edges. Similarly, the phrase "gate edges" refers only to active-going gate edges. Also, again to avoid verbosity and euphuism, the descriptions of some modes state that a counter is stopped or disarmed "on a TC, inhibiting further counting." As is fully explained in the TC section of this document, for these modes the counter is actually stopped or disarmed following the active-going source edge which drives the counter out of TC. In other words, since a counter in the TC state always counts, irrespective of its gating or arming status, the stopping or disarming of the count sequence is delayed until TC is terminated.

### MODE A

## Software-Triggered Strobe with No Hardware Gating

| CM15 | CM14 | CM13 | CM12 | CM11 | CM10 | CM9 | CM8 |

|------|------|------|------|------|------|-----|-----|

| 0    | 0    | 0    | Х    | Х    | Х    | X   | Х   |

CM7

CM6

CM5

CM4

CM3

CM2

CM1

CM0

0

0

0

X

X

X

X

X

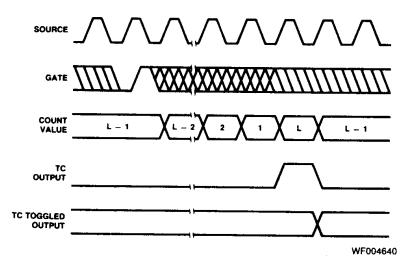

Mode A, shown in Figure 15a, is one of the simplest operating modes. The counter will be available for counting source edges when it is issued an ARM command. On each TC, the counter will reload from the Load register and automatically disarm itself, inhibiting further counting. Counting will resume when a new ARM command is issued.

## MODE B Software-Triggered Strobe with Level Gating

| CM15 | CM14  | CM13 | CM12 | CM11 | CM10 | CM9 | СМ8 |

|------|-------|------|------|------|------|-----|-----|

|      | LEVEL |      | Х    | Х    | Х    | Х   | Х   |

| CM7 | СМ6 | CM5 | CM4 | СМЗ | CM2 | CM1 | СМО |

|-----|-----|-----|-----|-----|-----|-----|-----|

| 0   | 0   | 0   | ×   | Х   | Х   | Х   | Х   |

Mode B, shown in Figure 15b, is identical to Mode A except that source edges are counted only when the assigned Gate is active. The counter must be armed before counting can occur. Once armed, the counter will count all source edges which occur while the Gate is active and disregard those edges which occur while the Gate is inactive. This permits the Gate to turn the count process on and off. On each TC the counter will reload from the Load register and automatically disarm itself, inhibiting further counting unitl a new ARM command is issued.

Figure 15a. Mode A Waveforms

Figure 15b. Mode B Waveforms

MODE C Hardware-Triggered Strobe

| CM15 | CM14 | CM13 | CM12 | CM11 | CM10 | СМ9 | CM8 |

|------|------|------|------|------|------|-----|-----|

|      | EDGE |      | Х    | Х    | Х    | Х   | Х   |

| CM7 | CM6 | CM5 | CM4 | СМЗ | CM2 | CM1 | CM0 |

|-----|-----|-----|-----|-----|-----|-----|-----|

| 0   | 0   | 0   | Х   | Х   | Х   | Х   | Х   |

Mode C, shown in Figure 15c, is identical to Mode A, except that counting will not begin until a Gate edge is applied to the

armed counter. The counter must be armed before application of the triggered Gate edge; Gate edges applied to a disarmed counter are disregarded. The counter will start counting on the first source edge after the triggering Gate edge and will continue counting until TC. At TC, the counter will reload from the Load register and automatically disarm itself. Counting will then remain inhibited until a new ARM command and a new Gate edge are applied in that order. Note that after application of a triggered Gate edge, the Gate input will be disregarded for the remainder of the count cycle. This differs from Mode B, where the Gate can be modulated throughout the count cycle to stop and start the counter.

Figure 15c. Mode C Waveforms

## MODE D

### Rate Generator with No Hardware Gating

| CM15 | CM14 | CM13 | CM12 | CM11 | CM10 | СМ9 | CM8 |

|------|------|------|------|------|------|-----|-----|

| 0    | 0    | 0    | Х    | Х    | Х    | Х   | Х   |

|      | ···  |      | +    | μ-   |      |     | ,   |

| CM7 | СМ6 | CM5 | CM4 | СМЗ | CM2 | CM1 | СМ0 |

|-----|-----|-----|-----|-----|-----|-----|-----|

| 0   | 0   | 1   | ×   | Х   | Х   | Х   | Х   |

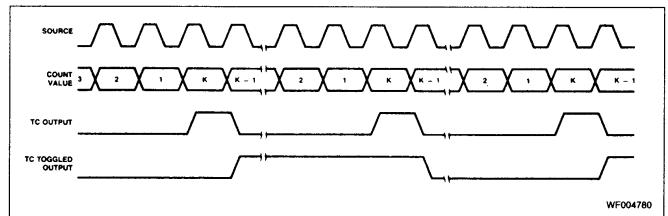

Mode D, shown in Figure 15d, is typically used in frequency generation applications. In this mode, the Gate input does not affect counter operation. Once armed, the counter will count to TC repetitively. On each TC, the counter will reload itself from the Load register; hence, the Load register value determines the time between TCs. A square wave rate generator may be obtained by specifying the TC Toggled output mode in the Counter Mode register.

### MODE E

### Rate Generator with Level Gating

| CM15 | CM14  | CM13 | CM12 | CM11 | CM10 | СМ9 | CM8 |

|------|-------|------|------|------|------|-----|-----|

|      | LEVEL |      | Х    | Х    | Х    | X   | Х   |

| CM7 | CM6 | CM5 | CM4 | СМЗ | CM2 | CM1 | СМО |

|-----|-----|-----|-----|-----|-----|-----|-----|

| 0   | 0   | 1   | Х   | Х   | Х   | Х   | Х   |

Mode E, shown in Figure 15e, is identical to Mode D, except the counter will only count those source edges which occur while the Gate input is active. This feature allows the counting process to be enabled and disabled under hardware control. A square wave rate generator may be obtained by specifying the TC Toggled output mode.

Figure 15d. Mode D Waveforms

Figure 15e. Mode E Waveforms

### MODE F

### Non-Retriggerable One-Shot

| CM15 | CM14 | CM13 | CM12 | CM11 | CM10 | СМ9 | CM8 |

|------|------|------|------|------|------|-----|-----|

|      | EDGE |      | Х    | Х    | Х    | Х   | Х   |

| CM7 | СМ6 | CM5 | CM4 | СМЗ | CM2 | CM1 | CM0 |

|-----|-----|-----|-----|-----|-----|-----|-----|

| 0   | 0   | 1   | Χ   | Х   | Х   | Х   | ×   |

Mode F, shown in Figure 15f, provides a non-retriggerable one-shot timing function. The counter must be armed before it will function. Application of a Gate edge to the armed counter will enable counting. When the counter reaches TC, it will reload itself from the Load register. The counter will then stop counting, awaiting a new Gate edge. Note that unlike Mode C, a new ARM command is not needed after TC, only a new Gate edge. After application of a triggering Gate edge, the Gate input is disregarded until TC.

### MODE G

## Software-Triggered Delayed Pulse One-Shot

| CM15 | CM14 | CM13 | CM12 | CM11 | CM10 | CM9 | CM8 |

|------|------|------|------|------|------|-----|-----|

| 0    | 0    | 0    | Х    | Х    | Х    | Х   | Х   |

|   | CM7 | CM6 | CM5 | CM4 | СМЗ | CM2 | CM1 | СМО |

|---|-----|-----|-----|-----|-----|-----|-----|-----|

| 1 | 0   | 1   | 0   | Х   | Х   | Х   | Х   | Х   |

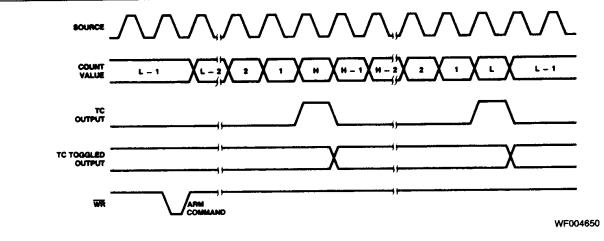

In Mode G, the Gate does not affect the counter's operation. Once armed, the counter will count to TC twice and then automatically disarm itself. For most applications, the counter will initially be loaded from the Load register either by a LOAD command or by the last TC of an earlier timing cycle. Upon counting to the first TC, the counter will reload itself from the Hold register. Counting will proceed until the second TC, when the counter will reload itself from the Load register and automatically disarm itself, inhibiting further counting. Counting can be resumed by issuing a new ARM command. A softwaretriggered delayed pulse one-shot may be generated by specifying the TC Toggled output mode in the Counter Mode register. The initial counter contents control the delay from the ARM command until the output pulse starts. The Hold register contents control the pulse duration. Mode G is shown in Figure 15g.

Figure 15f. Mode F Waveforms

Figure 15g. Mode G Waveforms

## MODE H

## Software-Triggered Delayed Pulse One-Shot with Hardware Gating

| LEVEL Y Y Y X     | CM15 | CM14  | CM13 | CM12 | CM11 | CM10 | CM9 | CM8 |

|-------------------|------|-------|------|------|------|------|-----|-----|

| LEVEL A A A A A A |      | LEVEL |      | Х    | Х    | Х    | X   | Х   |

| CM7 | CM6 | CM5 | CM4 | СМЗ | CM2 | CM1 | СМО |

|-----|-----|-----|-----|-----|-----|-----|-----|

| 0   | 1   | 0   | Х   | Х   | Х   | Х   | Х   |

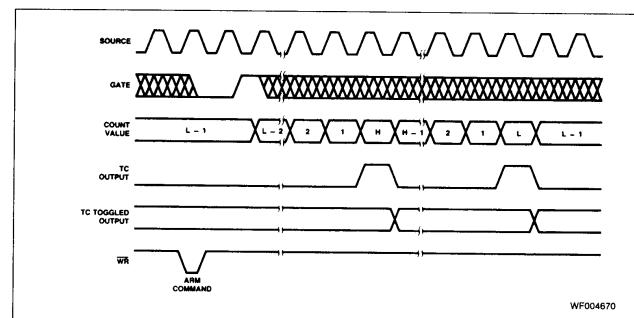

Mode H, shown in Figure 15h, is identical to Mode G except that the Gate input is used to qualify which source edges are to be counted. The counter must be armed for counting to occur. Once armed, the counter will count all source edges that occur while the Gate is active. This permits the Gate to turn the count process on and off. As with Mode G, the counter will be reloaded from the Hold register on the first TC and reloaded from the Load register and disarmed on the second TC. This mode allows the Gate to control the extension of both the initial output delay time and the pulse width.

## MODE | Hardware-Triggered Delayed Pulse Strobe

| CM15 | CM14 | CM13 | CM12 | CM11 | CM10 | CM9 | CM8 |

|------|------|------|------|------|------|-----|-----|

|      | EDGE | -    | Х    | Х    | Х    | Х   | Х   |

|      |      |      |      |      |      |     |     |

| CM7  | CM6  | CM5  | CM4  | СМЗ  | CM2  | CM1 | СМО |

Mode I, shown in Figure 15i, is identical to Mode G, except that counting will not begin until a Gate edge is applied to an armed counter. The counter must be armed before application of the triggering Gate edge; Gate edges applied to a disarmed counter are disregarded. An armed counter will start counting on the first source edge after the triggering Gate edge. Counting will then proceed in the same manner as in Mode G. After the second TC, the counter will disarm itself. An ARM command and Gate edge must be issued in this order to restart counting. Note that after application of a triggering Gate edge, the Gate input will be disregarded until the second TC. This differs from Mode H, where the Gate can be modulated throughout the count cycle to stop and start the counter.

Figure 15h. Mode H Waveforms

Figure 15i. Mode I Waveforms

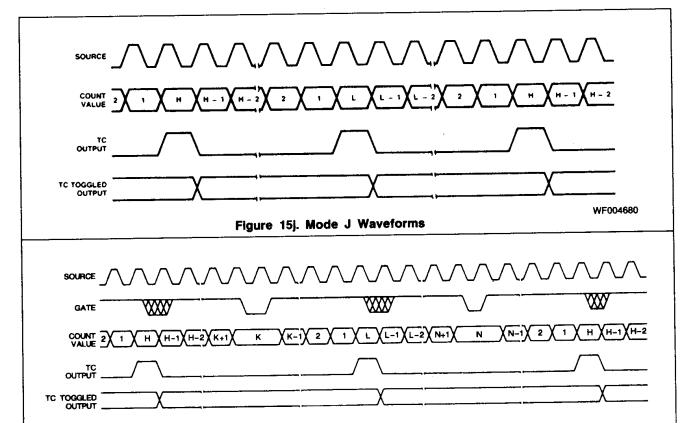

MODE J

Variable Duty Cycle Rate Generator with No

Hardware Gating

| CM15 | CM14 | CM13 | CM12 | CM11 | CM10 | CM9 | CM8 |

|------|------|------|------|------|------|-----|-----|

| 0    | 0    | 0    | Х    | Х    | Х    | Х   | Х   |

| CM7 | CM6 | CM5 | CM4 | СМЗ | CM2 | CM1 | СМО |

|-----|-----|-----|-----|-----|-----|-----|-----|

| 0   | 1   | 1   | Х   | Х   | Х   | Х   | X   |

Mode J, shown in Figure 15j, will find the greatest usage in frequency generation applications with variable duty cycle requirements. Once armed, the counter will count continuously until it is issued a DISARM command. On the first TC, the counter will be reloaded from the Hold register. Counting will then proceed until the second TC at which time the counter will be reloaded from the Load register. Counting will continue, with the reload source alternating on each TC, until a DISARM command is issued to the counter. (The third TC reloads from the Hold register, the fourth TC reloads from the Load register, etc.) A variable duty cycle output can be generated by specifying the TC Toggled output in the Counter Mode register. The Load and Hold values then directly control the output duty cycle, with high resolution available when relatively high count values are used.

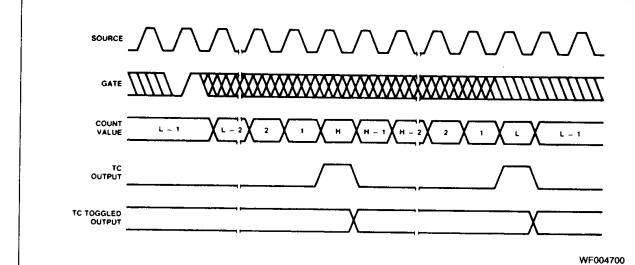

### MODE K

## Variable Duty Cycle Rate Generator with Level Gating

| CM15 | CM14  | CM13 | CM12 | CM11 | CM10 | СМ9 | CM8 |

|------|-------|------|------|------|------|-----|-----|

|      | LEVEL |      | Х    | Х    | Х    | Х   | Х   |

| CM7 | CM6 | CM5 | CM4 | СМЗ | CM2 | CM1 | СМО |

|-----|-----|-----|-----|-----|-----|-----|-----|

| 0   | 1   | 1   | Х   | Х   | Х   | Х   | Х   |

Mode K, shown in Figure 15k, is identical to Mode J, except that source edges are only counted when the Gate is active. The counter must be armed for counting to occur. Once armed, the counter will count all source edges which occur while Gate is active and disregard those source edges which occur while the Gate is inactive. This permits the Gate to turn the count process on and off. As with Mode J, the reload source used will alternate on each TC, starting with the Hold register on the first TC after any ARM command. When the TC Toggled output is used, this mode allows the Gate to modulate the duty cycle of the output waveform. It can affect both the HIGH and LOW portions of the output waveform.

Figure 15k. Mode K Waveforms

WF004691

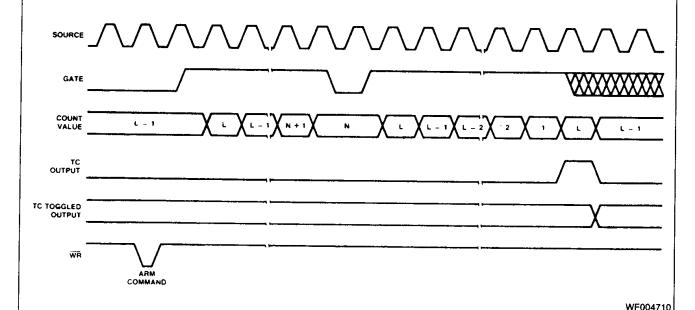

### MODE L

## Hardware-Triggered Delayed Pulse One-Shot

| CM15 | CM14 | CM13 | CM12 | CM11     | CM10 | CM9 | CM8 |

|------|------|------|------|----------|------|-----|-----|

|      | EDGE |      | Х    | Х        | Х    | X   | Х   |

|      |      |      |      | <u> </u> |      |     |     |

| CM7  | СМ6  | CM5  | CM4  | СМЗ      | CM2  | CM1 | СМО |

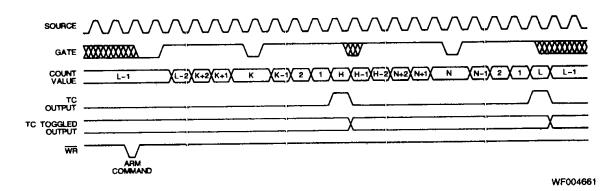

Mode L, shown in Figure 15I, is similar to Mode J except that counting will not begin until a Gate edge is applied to an armed counter. The counter must be armed before application of the triggering Gate edge; Gate edges applied to a disarmed counter are disregarded. The counter will start counting source edges after the triggering Gate edge, and counting will proceed until the second TC. Note that after application of a triggering Gate edge, the Gate input will be disregarded for the remainder of the count cycle. This differs from Mode K, where the gate can be modulated throughout the count cycle to stop and start the counter. On the first TC after application of the triggering Gate edge, the counter will be reloaded from the Hold register. On the second TC, the counter will be reloaded from the Load register, and counting will stop until a new gate edge is issued to the counter. Note that unlike Mode K, new Gate edges are required after every second TC to continue counting.

### MODE N

## Software-Triggered Strobe with Level Gating and Hardware Retriggering

| CM15                                    | CM14  | CM13 | CM12 | CM11 | CM10 | СМ9 | CM8 |

|-----------------------------------------|-------|------|------|------|------|-----|-----|

| *************************************** | LEVEL |      | ×    | Х    | Х    | Х   | Х   |

|                                         |       |      |      |      |      |     |     |

| CM7                                     | СМ6   | CM5  | CM4  | СМЗ  | CM2  | CM1 | СМО |

Mode N, shown in Figure 15n, provides a software-triggered strobe with level gating that is also hardware retriggerable. The counter must be issued an ARM command before counting can occur. Once armed, the counter will count all source edges which occur while the gate is active and disregard those source edges which occur while the Gate is inactive. This permits the Gate to turn the count process on and off. After the issuance of the ARM command and the application of an active Gate, the counter will count to TC. Upon reaching TC, the counter will reload from the Load register and automatically disarm itself, inhibiting further counting. Counting will resume upon the issuance of a new ARM command. All active-going Gate edges issued to an armed counter will cause a retrigger operation. Upon application of the Gate edge, the counter contents will be saved in the Hold register. On the first qualified source edge after application of the retriggering gate edge, the contents of the Load register will be transferred into the counter. Counting will resume on the second qualified source edge after the retriggering Gate edge. Qualified source edges are active-going edges which occur while the Gate is active.

Figure 15I. Mode L. Waveforms

### Figure 15n. Mode N Waveforms

## MODE O

### Software-Triggered Strobe with Edge Gating and Hardware Retriggering

| CM15 | CM14 | CM13 | CM12 | CM11 | CM10 | CM9 | CM8 |

|------|------|------|------|------|------|-----|-----|

|      | EDGE |      | Х    | Х    | Х    | Х   | Х   |

|      |      |      |      |      |      |     |     |

| CM7  | CM6  | CM5  | CM4  | СМЗ  | CM2  | CM1 | СМО |

Mode O, shown in Figure 15o, is similar Mode N, except that counting will not begin until an active-going Gate edge is applied to an armed counter and the Gate level is not used to

modulate counting. The counter must be armed before application of the triggering Gate edge; Gate edges applied to a disarmed counter are disregarded. Irrespective of the Gate ievel, the counter will count all source edges after the triggering Gate edge until the first TC. On the first TC, the counter will be reloaded from the Load register and disarmed. A new ARM command and a new Gate edge must be applied in that order to initiate a new counting cycle. Unlike Modes C, F, I and L, which disregard the Gate input once counting starts, in Mode O the count process will be retriggered on all activegoing Gate edges, including the first Gate edge used to start the counter. On each retriggering Gate edge, the counter contents will be transferred into the Hold register. On the first source edge after the retriggering Gate edge, the Load register contents will be transferred into the counter. Counting will resume on the second-source edge after a retrigger.

Figure 15o. Mode O Waveforms

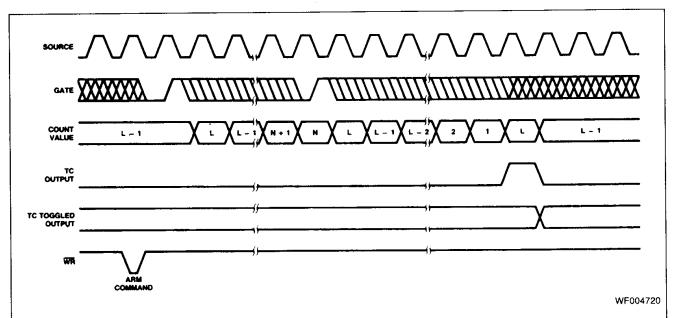

MODE Q

Rate Generator with Synchronization (Event Counter with Auto-Read/Reset)

| CM15 | CM14  | CM13 | CM12 | CM11 | CM10 | СМ9 | CM8 |

|------|-------|------|------|------|------|-----|-----|

|      | LEVEL |      | Х    | Х    | Х    | Х   | Х   |

|      |       |      |      |      |      |     |     |

| CM7  | CM6   | CM5  | CM4  | СМЗ  | CM2  | CM1 | СМО |

Mode Q, shown in Figure 15q, provides a rate generator with synchronization or an event counter with auto-read/reset. The counter must first be issued an ARM command before counting can occur. Once armed, the counter will count all source edges which occur while the Gate is active and disregard those edges which occur while the Gate is inactive. This permits the Gate to turn the count process on and off. After the issuance of an ARM command and the application of an active Gate, the counter will count to TC repetitively. On each TC, the counter will reload itself from the Load register. The counter may be retriggered at any time by presenting an active-going Gate edge to the Gate input. The retriggering Gate edge will transfer the contents of the counter into the Hold register. The first qualified source edge after the retriggering Gate edge will transfer the contents of the Load register into the Counter. Counting will resume on the second qualified source edge after the retriggering Gate edge. Qualified source edges are active-going edges which occur while the Gate is active.

## MODE R Retriggerable One-Shot

| CM15 | CM14 | CM13 | CM12 | CM11 | CM10 | CM9 | CM8 |

|------|------|------|------|------|------|-----|-----|

|      | EDGE |      | Х    | X    | Х    | Х   | Х   |

| CI | <b>v</b> 17 | CM6 | CM5 | CM4 | СМЗ | CM2 | CM1 | СМ0 |

|----|-------------|-----|-----|-----|-----|-----|-----|-----|

|    | 1           | 0   | 1   | Х   | Х   | Х   | X   | X   |

Mode R, shown in Figure 15r, is similar to Mode Q, except that edge gating rather than level gating is used. In other words, rather than use the Gate level to qualify which source edges to count, Gate edges are used to start the counting operation. The counter must be armed before application of the triggering Gate edge; Gate edges applied to a disarmed counter are disregarded. After application of a Gate edge, an armed counter will count all source edges until TC, irrespective of the Gate level. On the first TC, the counter will be reloaded from the Load register and stopped. Subsequent counting will not occur until a new Gate edge is applied. All Gate edges applied to the counter, including the first used to trigger counting, initiate a retrigger operation. Upon application of a Gate edge, the counter contents are saved in the Hold register. On the first source edge after the retriggering Gate edge, the Load register contents will be transferred into the counter. Counting will resume on the second source edge after the retriggering Gate edge.

Figure 15q. Mode Q Waveforms

Figure 15r. Mode R Waveforms

CM8

CM9

MODE S

### **RELOAD SOURCE**

| 0   | 0   | 0   | Х   | Х   | Х   | Х   | Х   |

|-----|-----|-----|-----|-----|-----|-----|-----|

| CM7 | CM6 | CM5 | CM4 | СМЗ | CM2 | CM1 | СМО |

| 1   | 1   | 0   | Y   | V   | V   | V   | V   |

CM15 CM14 CM13 CM12 CM11 CM10