# Agilent HDMP-2689 Quad 2.125/1.0625 GBd Fibre Channel General Purpose SerDes

Data Sheet

# Description

The HDMP-2689 SerDes chip transmits and receives high speed serial data over fiber optic or coaxial cable interfaces that conform to ANSI X3T11 Fibre Channel specification. It supports SerDes-only mode using a 10-bit data interface with optional 8B/10B encoding for fast backplane applications. The HDMP-2689 runs at 2.125 GBd or 1.0625 GBd data rates and provides parallel-to-serial and serial-to-parallel conversion on four independent channels contained in one package. An onchip phase locked loop (PLL) synthesizes the high speed transmit clock from a low speed (106.25 MHz) reference. Each receiver's on-chip PLL synchronizes directly to the incoming data stream, providing clock and data recovery. Both the transmitter and receiver support differential I/O for fiber optic component interfaces, which minimizes crosstalk and maximizes signal integrity. Chip control and status are accessed via the Media Independent Interface (MII) defined in IEEE 802.3.

# Features

- 1.0625GBd and 2.125 GBd serial data rates

- TX and RX data rates independently selectable for each channel

- Fibre Channel (T11) compatible

- High speed differential serial I/O with matched 50  $\Omega$  impedance

- Supports Fibre Channel Protocols FC0

- Dual mode SerDes operation with 10-bit parallel data interface and optional 8B/10B encode/decode

- Standard comma recognition for positive (0011111xxx) and negative (1100000xxx) disparity

- Source-centered, double data rate clocking of receive parallel data for 1.0625 GBd and 2.125 GBd serial rates

- Source synchronous double data rate clocking of transmit parallel data for 2.125 GBd serial rate

- Source synchronous single data rate clocking of transmit parallel data for 1.0625 GBd serial rate

- MII management interface for chip control and status

- 1.8V core power supply, 2.5V power supply for SSTL\_2 I/O

- Independent channel power-down for power savings

- SSTL\_2 compliant parallel I/O and byte clocks

- Low transmit jitter

- Pre-emphasis on serial outputs controllable via the management interface

- Loss of signal detection

- AC-coupled differential LVPECL reference clock input

- Input equalization

- Boundary scan IEEE 1149.1 compliant

- SerDes self-test capability using PRBS or user-defined patterns

- Local internal loop back of TX serial data to RX serial data by channel

- 289-pin PBGA

- Testjet compliant

**Agilent Technologies**

**Applications**

• Fibre Channel Arbitrated Loop

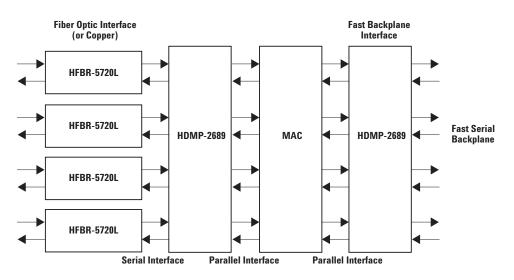

See Figure 1 for a diagram of typical applications.

Fast Serial Backplanes

Figure 1. HDMP-2689 Typical Applications.

#### **Functional Description**

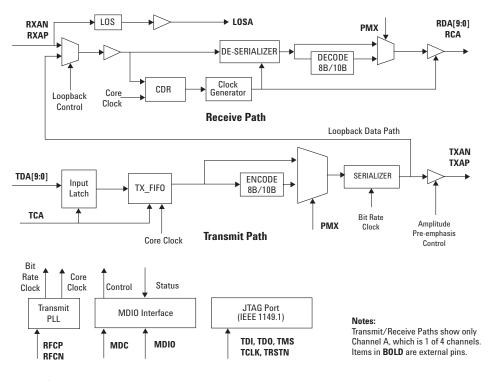

**Transmitter Description** The HDMP-2689 transmitter contains four independent channels and a single TX PLL which generates the serial rate transmit clock for all of the channels. The data is optionally encoded in 8B/10B format and serialized at 1.0625 GBd (half rate) or 2.125 GBd (full rate). The high-speed outputs can be interfaced directly to copper cables or PCB traces for electrical transmission or to a separate fiber optic module for optical transmission. See Figure 2 for a block diagram.

Figure 2. TX and RX Paths.

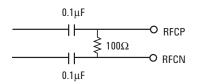

### **Reference Clock Input**

The HDMP-2689 accepts a differential LVPECL reference clock input at 106.25 MHz (see Figure 3 for configuration). This reference clock is used by the TX PLL to acquire frequency lock and generate the base frequency of operation.

Figure 3. Reference Clock Input Configuration.

#### **Data Input**

The transmitter is designed to accept either of two formats of parallel input data:

- 9-bit data consisting of an 8-bit word plus a 1-bit K character flag (Z), encoded on chip with 8B/10B

- 10-bit data already encoded in a DC-balanced code (over a minimum length of 20 bits) such as 8B/10B

The PMX pin is set to select the data format. Depending on the format, the data may undergo encoding before serialization. See Table 1 for PMX encoding definitions and data processing.

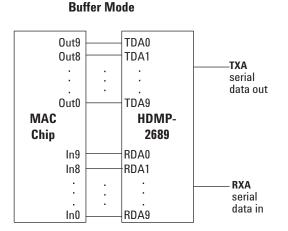

Table 2 contains a summary of the data formats. Note that for the buffer mode (PMX=0), bit a, which corresponds to TDn9, is serialized first. For example, for K28.5 (0011111010), if the MAC's Out0 through Out9 bits correspond to 0011111010, then the HDMP-2689's TDA9 through TDA0 are connected to the MAC's Out0 through Out 9. The TDA9 bit is serialized first. Similarly on the RX side, the very first bit received is RDA9 (MSB) which is In0 for the MAC. See Figure 4 for MAC to HDMP-2689 connections. (Channel A, shown in the figure, is representative of all four channels.)

For codec mode, the MAC's Out0 through Out9 should be connected to TDA0 through TDA9. For example, if 1bc=01 1011 1101 is coming from the MAC for encoding, Out0 (assuming this is the LSB from the MAC) is 1, Out1 is 0 and so on. After encoding, the result is a comma, 0011111010 (or 1100000101), with the leading 00 (or 11) bits coming first on the serial output. The RX side behaves in a similar fashion. The parallel input data arrives on SSTL\_2 inputs and is captured by data latches which are clocked by the local transmit clocks (TC[A-D]). The TX\_FIFO

phase aligns the data with the internal core clock.

## 8B/10B Encoding

The HDMP-2689 provides a global 8B/10B line coding option. The characters defined by this code ensure a DC balanced serial data stream, which enables clock recovery at the receiver. The 8B/10B code distinguishes D-characters, used for data transmission, from K-characters, used for control or protocol functions. A byte error code can be designated as the replacement data for an erroneous data word by programming bits 14 through 6 of management interface register 19.

#### Half Rate/Full Rate

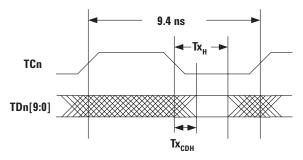

The HDMP-2689 supports two transmit data rates as detailed in Table 3. The 10-bit wide parallel data is multiplexed into a 1.0625 GBd (half rate) or 2.125 GBd (full rate) serial data stream using internally generated high-speed clocks. The data bits are transmitted sequentially from TDn[9] to TDn[0] (bit ordering for buffer and codec modes is shown in Table 2). The output serial data rate is selected by programming bit 15 in management interface register 17.

Figure 4. MAC to HDMP-2689 Interconnect.

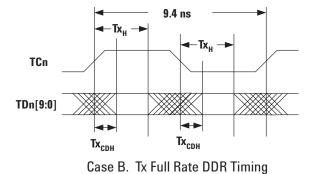

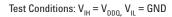

For half rate operation, the data is input in single data rate (SDR) mode. For SDR each parallel input data word is clocked in on the falling edge of the input transmit byte clock (TC[A-D]). The timing requirements are specified in Figure 9 Case A. For full rate operation, the data must be input in double data rate (DDR) mode, with one data word input on the rising edge of the input transmit byte clock (TC[A-D]) and the next word on the falling edge. Two data words are input every transmit byte clock cycle. The timing requirements for DDR operation are shown in Figure 9 Case B.

TC[A-D] always operates at 106.25 MHz.

The default settings for the HDMP-2689 are full rate operation and DDR.

#### **Serial Data Outputs**

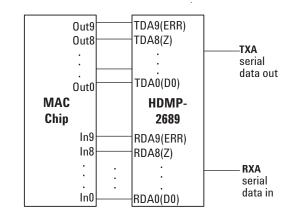

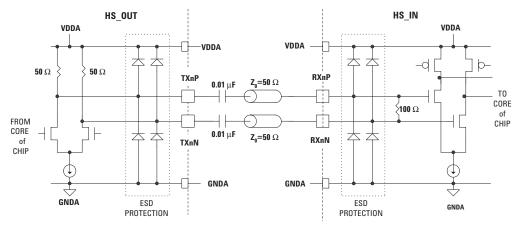

Through AC coupling, the highspeed outputs are capable of interfacing directly to copper cables or PCB traces for electrical transmission or to a separate fiber optic module for optical transmission (see Figure 5). These outputs include usercontrollable skin-loss equalization and amplitude control to improve performance when driving copper lines. In normal operation, the serialized TDn[9:0] data is placed at TXnP/N. The output drivers provide for controllable preemphasis and amplitude settings by programming management interface register 26 (see Figure 6). If pre-emphasis is used,  $0 \rightarrow 1$  and  $1 \rightarrow 0$  transitions on TXnP/N have greater amplitude than  $0 \rightarrow 0$  and  $1 \rightarrow 1$  transitions. This increased amplitude counteracts the effects of skin loss and dispersion on long PCB transmission lines. The serial outputs can also be disabled through register 26.

Notes: HS\_IN inputs should never be connected to ground as permanent damage to the device may result. Capacitors may be placed at the sending or receiving end.

Figure 5. High Speed Input and Output Configurations.

Note: The peaked value at the transition edge does not reach to VFEAK\_STATIC value because of the reflection between driver and package. The static value can be measured as the final value of a long (longer than 2 bits) 1 or 0 pulse with zero peaking.

Figure 6. High Speed Output Pre-Emphasis.

#### **Receiver Description**

The HDMP-2689 receiver contains four independent channels, each with its own input amplifier with equalization, clock recovery PLL, deserializer, comma detection and byte clock generation. Depending on the PMX mode, the data may also pass through an 8B/10B decoder.

#### **High Speed Input**

In normal operation, serial data is accepted at RXnP/N and converted into parallel data to drive RDn[9:0]. See Figure 5 for the input configuration. In parallel loopback mode, the internal serial output signal from the transmitter section is used to generate RDn[9:0]. Loopback is discussed in more detail in the section on Test.

#### **Receiver Loss of Signal**

When the peak-to-peak differential amplitude at the RXnP/N input is too small, LOSn is set to logic 1. When the signal at RXnP/ N is a valid amplitude, LOSn is set to logic 0.

If RXnP/N  $\geq$  300 mV peak-topeak differential, LOSn = logic 0 If 150 mV < RXnP/N < 300 mV peak-to-peak differential, LOSn is undefined If RXnP/N  $\leq$  150 mV peak-topeak differential, LOSn = logic 1

Optionally, through MII register 17, LOSn can also be forced to logic 1 if the receiver PLL is not locked.

#### **RX PLL/Clock Recovery**

The receiver frequency and phase locks onto the incoming serial data stream and recovers the bit clock. The RX PLL locks onto the input data by frequency locking onto the 106.25 MHz LVPECL reference clock and then phase locking onto the selected input data stream. The received clock locks to the incoming data or free runs at the selected frequency in the absence of incoming data. An internal signal detection circuit monitors the presence of the input and invokes phase detection as the data stream appears. Once bit locked, the receiver generates the highspeed sampling clock used to deserialize the data.

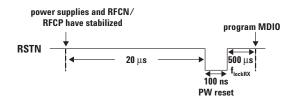

### **Byte Sync and Comma Detect**

As the 10-bit parallel data is recovered from the high-speed serial bit stream, the first seven bits of the K28.5+ positive disparity comma character (0011111xxx) and of the K28.5negative disparity comma character (1100000xxx) are detected. The proper parallel data edge is selected out of the bit stream so that the next comma character starts at RDn[9] in buffer mode. When a comma character is detected and realignment of the receive byte clock is necessary, the clocks are stretched (never slivered) to the next correct alignment position. The recovered clock will be aligned by the start of the next four-byte ordered set after K28.5+ or K28.5- is detected. By default, in buffer mode, the start of the next ordered set will be aligned with the falling edge of RCn. In codec mode (PMX=1), by default the RCn clock is not realigned, and the comma may appear at either edge. The default alignments may be changed by programming MII register 17. Unless comma edge alignment is disabled in MII register 17, comma characters must not be transmitted in consecutive bytes so that the receive byte clocks may maintain their proper recovered frequencies. Furthermore, RX byte align should be disabled (using MII register 24) if PRBS data is being received.

#### **SSTL 2 Outputs**

As discussed for the transmitter parallel inputs, the bit ordering is different for buffer and codec modes. See Figure 4 and earlier Data Input section for additional details.

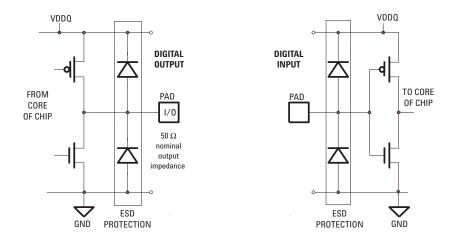

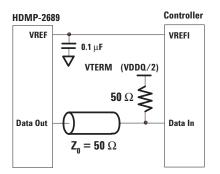

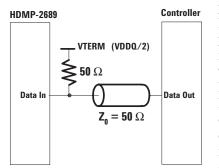

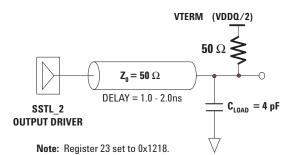

The HDMP-2689 presents the 10-bit parallel recovered data (RDn[9:0]), properly aligned to the receive byte clock (RCn) as shown in Figure 11 and Table 5, as single-ended SSTL\_2 compliant signals. The HDMP-2689 expects SSTL\_2 compatible signals at the TDn[9:0] and TCn pins. See Figure 7 for a simplified schematic of the input and output drivers, and Figure 8 for the recommended termination configuration. For proper operation of the terminated SSTL\_2 drivers, register 23 must be configured as described in Management Interface Registers, page 27. (Set register 23 to 0x1218). For best results use a low inductance VTERM plane to terminate the 50  $\Omega$  resistors close to the HDMP-2689 TX inputs. In addition, decouple the VTERM plane with 0.1 µF local to each 10-bit channel to reduce simultaneously switching output (SSO) noise on the inputs. The HDMP-2689 works with MAC devices whose VDDQ voltage is nominally 2.5 V. In addition, the HDMP-2689 provides a VREF output pin which may be used at the protocol IC in order to differentially detect a high or a low on RDn[9:0]. Alternatively, this voltage may be generated on the PCB using a resistor divider from VDDQ while ignoring the VREF output of the HDMP-2689.

Figure 7. Simplified Schematic of SSTL\_2 Input and Output Drivers.

a) Terminated SSTL 2 Connection, Rx

Figure 8. SSTL\_2 I/O Terminations.

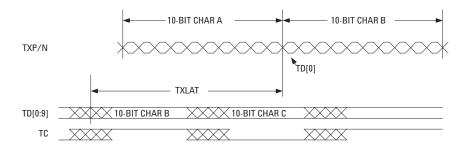

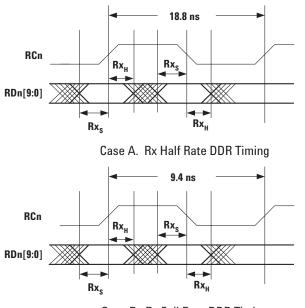

**Data Output and Clocking Modes** Table 5 describes the receive parallel interface clocking. In both half (1.0625 GBd serial ) and full (2.125 GBd serial) rate operation, the data is always presented as DDR, double data rate (See Figure 11, Cases A and B). In addition, the output clock is always source centered (SC), so the clock changes in the middle of the data period. Note that bit a, the first serial bit in a 10-bit word, corresponds to RDn9 (see Table 2).

#### **Configuration and Reset**

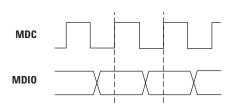

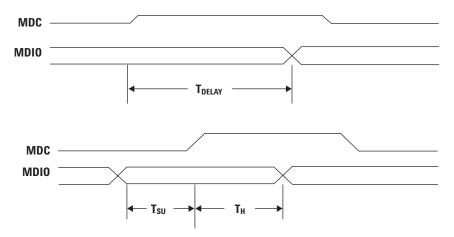

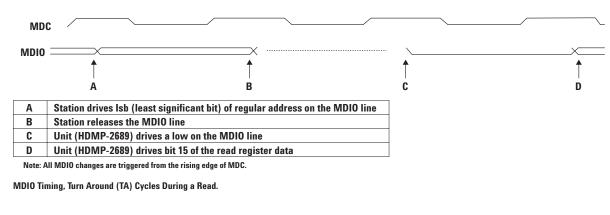

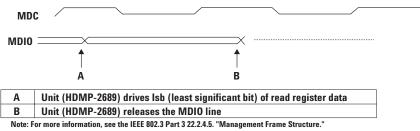

The HDMP-2689 is configured by a set of registers that can be accessed through the standard MII management interface defined in IEEE 802.3 clause 22. This interface is used by a management entity to control and gather status from the chip. It is a two-wire interface made up of a management data input/ output signal (MDIO) and a management data clock (MDC). Figure 15 shows the relationship between MDIO and MDC. Figure 16 and Figure 17 present a more detailed description of MDIO timing. Table 8 presents the format of a management frame (for more information, refer to IEEE 802.3). A management frame consists of a minimum 32-bit preamble, a start of frame indication, an operation code, a PHY address, a register address,

turnaround bits, data bits, and an idle. The order of bit transmission is left to right as shown in Table 8. MDIO timing is detailed in Table 9.

The three most significant bits of the PHY address are made up of the hard-wired address of the HDMP-2689. The two least significant bits represent the channel referenced in the frame. Two bits are sufficient to encode IDs for the four channels on the chip.

The standard management interface allows for 32 16-bit registers. The HDMP-2689 supports a subset of these registers. Management Interface Registers, pages 26–28, show the standard register definitions and specify which ones are supported in the HDMP-2689. Because the HDMP-2689 has four physical channels that operate independently, some of the registers are replicated four times, one for each channel. Other registers are common to all four channels, i.e. their bit values apply to all the channels. Still other registers are shared between the four channels, i.e. individual bits within a register apply to individual channels. The replicated registers are accessed using a PHY address made up of the three-bit chip ID and the appropriate two-bit channel ID (00, 01, 10, or 11). Common and shared registers are accessed using the chip ID and the 00 channel ID. Attempting to access common registers other than through channel A (00) must be avoided as it results in undefined behavior. The specific configuration and status information that can be set or read from HDMP-2689 is presented in the section titled Management Interface Registers. This section defines the complete assignment of management registers and specifies which registers are common to the four channels.

b) Terminated SSTL\_2 Connection, Tx

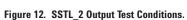

Reset is initiated externally with the assertion of the RSTN pin. Before asserting the RSTN pin, the power supply to the chip and the reference clock (RFCP/N) must be stable for at least 20  $\mu$ s. The RSTN pin must be held low for at least 100 ns. After reset is de-asserted, 500  $\mu$ s must elapse before initiating MDIO transactions (see Figure 13). Note that the transmit byte clocks (TCn) should be running and stable when reset is released to minimize the variation in transmit latency.

#### **Power Management**

The HDMP-2689 incorporates the ability to power down any channel which is unused. Both the channel and the associated output driver should be disabled by programming the unused channel's register 24, bit 0 and register 26, bit 7 both to logic 0. Additionally, the HDMP-2689 does not require a particular power turn-on sequence.

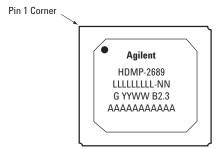

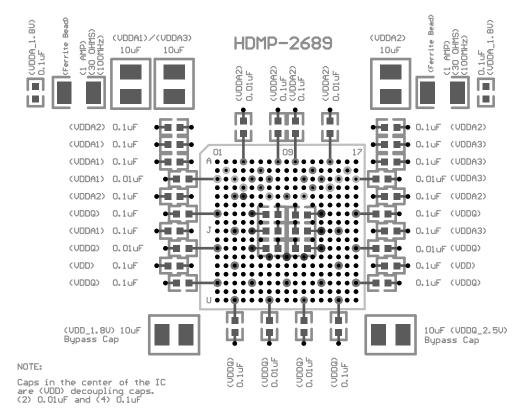

#### **Power Supply Decoupling**

Recommended power supply filtering and placement of decoupling capacitors for the HDMP-2689 are shown in Figure 22 and Figure 23.

# Test

The HDMP-2689 has several features to facilitate testing, including boundary scan, SerDes self-test, and loopback for link debugging. Boundary scan is implemented according to the IEEE 1149.1 standard. The instructions listed in Table 7 are supported. The HDMP-2689 also provides self-test capabilities with user-entered patterns or onchip generation of pseudorandom bit streams (PRBS 2<sup>7</sup>–1). The patterns can be looped back either internally or externally from the transmit serializer to the receive deserializer and are verified within the chip. These self-test mechanisms are initiated and the error status reported through the MII management interface. To run a self-test, first select the pattern or set of patterns, then configure the loopback and check the results. Once enabled, the test pattern is sent continuously. To select a user-defined pattern:

- Disable comma alignment by programming bit 1 of register 24 to logic 0.

- Program the pattern (any pattern except all 0's or all 1's) into bits 9 through 0 of register 25.

- To alternate the user pattern with its inverse, program bit 11 of register 25 to logic 1.

- Program bit 10 of register 25 to a logic 1 to enable the user register pattern to be sent.

To select PRBS data:

- Disable comma alignment by programming bit 1 of register 24 to logic 0.

- Program a non-zero seed for the pattern generator into bits 9 through 0 of register 25.

- To send the PRBS pattern inverted, program bit 11 of register 25 to logic 1.

- Program bit 12 of register 25 to a logic one to enable the PRBS pattern to be sent.

- To see the recovered PRBS data on the parallel interface, comma edge alignment should be disabled by programming bit 13 of register 17 to logic 0.

To run the self-test with either external or internal loopback:

- Set up either a user-defined pattern or PRBS data as outlined above.

- To run with internal loopback, program bit 13 of register 25 to logic 1.

- To run with external loopback, connect the high-speed output of the channel being tested (TXAP/N, TXBP/N, TXCP/N, TXDP/N) back to its high speed input (RXAP/N, RXBP/N, RXCP/N, RXDP/N). Bit 13 of register 25 must be logic 0 (default value after reset).

- Program bit 14 of register 25 to logic 0 if it is not already zero (default value after a reset). Bit 12 of register 27 (pattern failure detect) and bit 11 of register 27 (test run complete) should both now be logic 0.

- Program bit 14 of register 25 (pattern error monitor enable) to logic 1. This starts the pattern checking process. For a PRBS pattern 2 9 bytes are checked before the test is considered complete.

- Monitor bit 11 of register 27 to determine if a sufficient number of cycles have elapsed for test completion. When this bit is logic 1, bit 12 of register 27 signals pass (logic 0) or fail (logic 1).

To allow link debugging:

• Configure the HDMP-2689 for internal loopback (data provided at the parallel input is looped back to the parallel output after traversing the chip) via management interface register 25 bit 13. Note that for internal loopback in codec mode the receiver sees a loss of signal and error bit 9 (see Table 2) is set, unless the high speed inputs (ignored for internal loopback) are being driven.

## Table 1. PMX Encoding Definitions.

| РМХ | Mode   | Description                                                                                                                                              |

|-----|--------|----------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0   | Buffer | TX: Inputs are phase adjusted to transmit clock and serialized MSB (a) first.<br>RX: Serial data is byte aligned and presented with first bit (a) as MSB |

| 1   | Codec  | TX: Inputs are phase adjusted, 8B/10B encoded, and serialized.<br>RX: Serial data is byte aligned and 8B/10B decoded                                     |

#### Table 2. Data Formats (TDA/RDA is representative of all Transmit and Receive Data Ports).

| Pin       | PMX 0<br>Buffer | PMX 1<br>Codec                 |

|-----------|-----------------|--------------------------------|

| TDA9/RDA9 | а               | ERR (RX_LOS or decoding error) |

| TDA8/RDA8 | b               | Z                              |

| TDA7/RDA7 | С               | D7                             |

| TDA6/RDA6 | d               | D6                             |

| TDA5/RDA5 | е               | D5                             |

| TDA4/RDA4 | i               | D4                             |

| TDA3/RDA3 | f               | D3                             |

| TDA2/RDA2 | g               | D2                             |

| TDA1/RDA1 | h               | D1                             |

| TDA0/RDA0 | j               | D0                             |

|           |                 |                                |

Note: See Figure 4 for a connection diagram.

# Table 3. Transmitter Data Rate.

| Manage<br>Input Set | ment Register 17<br>tting | TXnP/N<br>Rate (GBd) | TCn<br>Rate (MHz) |  |

|---------------------|---------------------------|----------------------|-------------------|--|

| Case                | Full/Half                 |                      |                   |  |

| A                   | 0                         | 1.0625               | 106.25            |  |

| В                   | 1                         | 2.125                | 106.25            |  |

Case A. Tx Half Rate SDR Timing

#### Figure 9. Transmitter Timing Diagram.

#### Table 4. HDMP-2689 Transmitter Section Timing Characteristics,

$T_C$  = 0°C  $\,$  to  $T_C$  = 85°C,  $V_{DD0}$  = 2.3 to 2.7 V,  $V_{DD}$  = 1.7 to 1.9 V,  $V_{DDA}$  = 1.7 to 1.9 V  $\,$

| Symbol                             | Parameters                                                                                                                                                               | Units      | Min  | Тур        | Max |

|------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------|------|------------|-----|

| 1G                                 |                                                                                                                                                                          |            |      |            |     |

| Tx <sub>CDS</sub> <sup>[1,2]</sup> | Clock to data skew time; the data must be stable by T <sub>CDS</sub> after the clock edge to guarantee correct clocking of the data                                      | ps         |      |            | 300 |

| Tx <sub>H</sub> <sup>[2]</sup>     | Hold time; the time after the clock edge until which the data must remain stable to guarantee correct clocking of the data                                               | ps         | 2000 |            |     |

| t_TXlat_buffer <sup>[3]</sup>      | Transmitter latency; the time between the latching edge of the transmit byte clock<br>TCn and the leading edge of the first transmitted serial output bit in buffer mode | ns<br>bits |      | 80<br>85   |     |

| t_TXlat_codec <sup>[3]</sup>       | Transmitter latency; the time between the leading edge of the transmit byte clock<br>TCn and the leading edge of the first transmitted serial output bit in codec mode   | ns<br>bits |      | 90<br>95.5 |     |

| 2G                                 |                                                                                                                                                                          |            |      |            |     |

| Tx <sub>CDS</sub> <sup>[1,2]</sup> | Clock to data skew time; the data must be stable by T <sub>CDS</sub> after the clock edge to guarantee correct clocking of the data                                      | ps         |      |            | 300 |

| Tx <sub>H</sub> <sup>[2]</sup>     | Hold time; the time after the clock edge until which the data must remain stable to guarantee correct clocking of the data                                               | ps         | 2000 |            |     |

| t_TXlat_buffer <sup>[3]</sup>      | Transmitter latency; the time between the latching edge of the transmit byte clock<br>TCn and the leading edge of the first transmitted serial output bit in buffer mode | ns<br>bits |      | 65<br>138  |     |

| t_TXlat_codec <sup>[3]</sup>       | Transmitter latency; the time between the leading edge of the transmit byte clock<br>TCn and the leading edge of the first transmitted serial output bit in codec mode   | ns<br>bits |      | 70<br>149  |     |

Notes:

1. This clock-to-data skew time is equivalent to -300 ps setup time.

2. Measurement conditions were  $V_{IH}$  =  $V_{DDQ},\,V_{IL}$  = GND.

3. Due to the FIFO which aligns the phase of the internal chip clock with the transmit byte clock (TCn) and the asynchronous nature of the chip reset, the typical latency varies; a maximum of the typical range is given.

Figure 10. Transmitter Latency.

Table 5. Receiver Data Rate.

| Management Register 17<br>Input Setting |           | RXnP/N<br>Rate (GBd) | RCn<br>Rate (MHz) |

|-----------------------------------------|-----------|----------------------|-------------------|

| Case                                    | Full/Half |                      |                   |

| A                                       | 0         | 1.0625               | 53.125            |

| В                                       | 1         | 2.125                | 106.25            |

Case B. Rx Full Rate DDR Timing

Test Conditions:  $V_{IH} = V_{DDQ}, V_{IL} = GND$

Figure 11. Receiver Timing Diagram.

# HDMP-2689 Receiver Section Timing Characteristics,

| Symbol                         | Parameters                                                                                                                                                                                         | Units      | Min  | Тур      | Max  |

|--------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------|------|----------|------|

| PWreset                        | Width of reset pulse                                                                                                                                                                               | ns         | 100  |          |      |

| f lockRX                       | The time that the RX PLL takes to frequency lock to the data after reset                                                                                                                           | μs         |      |          | 500  |

| B_sync_lock                    | Bit Sync time after f lockRX                                                                                                                                                                       | bits       |      |          | 2500 |

| B_sync_rate                    | Bit Sync time after rate switch                                                                                                                                                                    | μs         |      |          | 100  |

| 1G                             |                                                                                                                                                                                                    |            |      |          |      |

| RX <sub>s</sub> <sup>[1]</sup> | Setup time: the time before the clock edge that the data will be stable                                                                                                                            | ps         | 2700 |          |      |

| RX <sub>H</sub> <sup>[1]</sup> | Hold time; the time after the clock edge until which the data will remain stable                                                                                                                   | ps         | 1500 |          |      |

| t_RXlat_buffer                 | Receiver latency; the timing between the leading edge of the first received serial<br>bit of a parallel data word and the leading edge of the corresponding parallel output<br>word in buffer mode | ns<br>bits |      | 50<br>53 |      |

| t_RXlat_codec                  | Receiver latency; the timing between the leading edge of the first received serial<br>bit of a parallel data word and the leading edge of the corresponding parallel output<br>word in codec mode  | ns<br>bits |      | 60<br>64 |      |

| 2G                             |                                                                                                                                                                                                    |            |      |          |      |

| RX s <sup>[1]</sup>            | Setup time: the time before the clock edge that the data will be stable                                                                                                                            | ps         | 1200 |          |      |

| RX <sub>H</sub> <sup>[1]</sup> | Hold time; the time after the clock edge until which the data will remain stable                                                                                                                   | ps         | 1400 |          |      |

| t_RXlat_buffer                 | Receiver latency; the timing between the leading edge of the first received serial                                                                                                                 | ns         |      | 30       |      |

|                                | bit of a parallel data word and the leading edge of the corresponding parallel output word in buffer mode                                                                                          | bits       |      | 64       |      |

| t_RXlat_codec                  | Receiver latency; the timing between the leading edge of the first received serial                                                                                                                 | ns         |      | 35       |      |

|                                | bit of a parallel data word and the leading edge of the corresponding parallel output<br>word in codec mode                                                                                        | bits       |      | 75       |      |

$T_{c} = 0^{\circ}C$  to  $T_{c} = 85^{\circ}C$ ,  $V_{DDQ} = 2.3$  to 2.7 V,  $V_{DD} = 1.7$  to 1.9 V,  $V_{DDA} = 1.7$  to 1.9 V

#### Notes:

1. Tested under load conditions described in Figure 12, with V<sub>IH</sub> = V<sub>REF</sub> + 0.18 and V<sub>IL</sub> = V<sub>REF</sub> - 0.18.

Figure 13. Externally Applied Reset (not to scale).

Figure 14. Receiver Latency.

#### Table 7. IEEE JTAG 1149.1 Instructions.

| Instruction | Opcode      | Description                                                                        |

|-------------|-------------|------------------------------------------------------------------------------------|

| EXTEST      | 00000_00000 | Causes boundary JTAG registers to capture their inputs, shift, and output to pads. |

| SAMPLE      | 00000_00010 | Causes boundary JTAG registers to capture their inputs.                            |

| CLAMP       | 00000_00100 | Causes boundary JTAG registers to output their values to pads.                     |

| HIGHZ       | 00000_01000 | Causes pads to be tri-stated.                                                      |

| BYPASS      | 11111_11111 | Connects the bypass register between TDI and TDO.                                  |

#### Table 8. Format of a Management Frame.

|       | Pr  | St | Op | PhyAdd | RegAdd | TA | Data | IDLE |

|-------|-----|----|----|--------|--------|----|------|------|

| Read  | 111 | 01 | 10 | aaaaa  | rrrr   | ZO |      | Z    |

| Write | 111 | 01 | 01 | aaaaa  | rrrrr  | 10 |      | Z    |

Figure 15. MDIO and MDC Timing.

#### Table 9. MDIO Timing Characteristics,

$T_C=0^\circ C~$  to  $T_C=85^\circ C,~V_{DDQ}=2.3$  to 2.7 V,  $V_{DD}=1.7$  to 1.9 V,  $V_{DDA}=1.7$  to 1.9 V

| Symbol             | Parameters                                         | Units | Min | Тур | Max |

|--------------------|----------------------------------------------------|-------|-----|-----|-----|

| Driving            |                                                    |       |     |     |     |

| T <sub>DELAY</sub> | MDC rising edge to MDIO data true or MDIO released | ns    | 0   |     | 300 |

| T <sub>MDC</sub>   | MDC frequency                                      | MHz   |     |     | 2.5 |

| Receiving          |                                                    |       |     |     |     |

| T <sub>SU</sub>    | Set up time: MDIO to MDC rising edge               | ns    |     |     | 10  |

| Т <sub>Н</sub>     | Hold time: MDC rising edge to MDIO changing        | ns    |     |     | 10  |

Note: For more information, see the IEEE 802.3 part 3 22.3.4, "MDIO timing relationship to MDC."

Figure 16. MDIO Timing, Driving and Receiving.

MDIO Timing, Last Bit of Read Register Data, Bus Released by the HDMP-2689.

Figure 17. MDIO Timing Diagrams.

#### Table 10. HDMP-2689 Absolute Maximum Ratings.

Sustained operation at or beyond any of these conditions may result in long-term reliability degradation or permanent damage, and is not recommended.

| Symbol              | Parameters                                                   | Units | Min   | Max                    |

|---------------------|--------------------------------------------------------------|-------|-------|------------------------|

| V <sub>DDQ</sub>    | I/O supply voltage                                           | V     | -0.5  | 4.0                    |

| V <sub>DD</sub>     | Supply voltage – digital core                                | V     | -0.5  | 3.0                    |

| V <sub>DDA</sub>    | Analog supply voltage                                        | V     | -0.5  | 3.0                    |

| T <sub>STG</sub>    | Storage temperature (not biased)                             | °C    | -55   | 125                    |

| T <sub>C</sub>      | Case temperature, measured at top center of the package      | °C    | 0     | 95                     |

| T <sub>J</sub>      | Junction temperature                                         | °C    | 0     | 110                    |

| V <sub>INHS</sub>   | High speed input voltage (single-ended)                      | V     | -0.5  | V <sub>DDA</sub> + 0.6 |

| VINLVPECL           | LVPECL input voltage (reference clock RFCP/N) (single-ended) | V     | -0.5  | V <sub>DDA</sub> + 0.6 |

| V <sub>INSSTL</sub> | SSTL_2 input voltage                                         | V     | -0.5  | V <sub>DDQ</sub> + 0.8 |

| ESD                 | Electrostatic Discharge, Class 1                             | V     | -1000 | 1000                   |

#### Table 11. Recommended Operating Conditions.

| Symbol           | Parameters                                              | Units          | Min | Тур | Max |

|------------------|---------------------------------------------------------|----------------|-----|-----|-----|

| V <sub>DDQ</sub> | I/O supply voltage                                      | V              | 2.3 | 2.5 | 2.7 |

| V <sub>DD</sub>  | Supply voltage – digital core                           | V              | 1.7 | 1.8 | 1.9 |

| V <sub>DDA</sub> | Analog supply voltage                                   | V              | 1.7 | 1.8 | 1.9 |

| T <sub>C</sub>   | Case temperature, measured at top center of the package | 0 <sup>0</sup> | 0   | 25  | 85  |

# Table 12. Guaranteed Operating Rates.

$T_{C}$  = 0°C  $\,$  to  $T_{C}$  = 85°C,  $V_{DDQ}$  = 2.3 to 2.7 V,  $V_{DD}$  = 1.7 to 1.9 V,  $V_{DDA}$  = 1.7 to 1.9 V

| Parallel Clock Rate (MHz) |       | Serial Baud Rate (GBd) |       | Serial Baud Rate (GBd) |       |

|---------------------------|-------|------------------------|-------|------------------------|-------|

| Min                       | Мах   | Min                    | Max   | Min                    | Max   |

| 106.2                     | 106.3 | 1.062                  | 1.063 | 2.124                  | 2.126 |

#### Table 13. Clock Specifications.

$T_{C}$  = 0°C  $\,$  to  $T_{C}$  = 85°C,  $V_{DDQ}$  = 2.3 to 2.7 V,  $V_{DD}$  = 1.7 to 1.9 V,  $V_{DDA}$  = 1.7 to 1.9 V  $\,$

| Symbol                | Parameters                                                                   | Units | Min  | Тур    | Max |

|-----------------------|------------------------------------------------------------------------------|-------|------|--------|-----|

| f                     | Reference Clock Nominal Frequency (RFCP/N)                                   | MHz   |      | 106.25 |     |

| Symm[RFCP, RFCN]      | Reference Clock Duty Cycle                                                   | %     | 40   |        | 60  |

| F <sub>TOL_full</sub> | Recovered Clock (RCn) to Reference Clock RFCP/N frequency tolerance          | ppm   | -100 |        | 100 |

| F <sub>TOL_half</sub> | Recovered Clock (RCn) to half the Reference Clock RFCP/N frequency tolerance | ppm   | -100 |        | 100 |

| Symm[RCn]             | Recovered Clock Duty Cycle                                                   | %     | 40   |        | 60  |

| f <sub>TCn</sub>      | Transmit Byte Clock Nominal Frequency                                        | MHz   |      | 106.25 |     |

| Symm[TCn]             | Transmit Byte Clock Duty Cycle                                               | %     | 40   |        | 60  |

Note: Transmit Clock and Reference Clock must be from the same frequency source.

#### Table 14. HDMP-2689 Power Dissipation.

| Parameters                      | Units                                                             | Min                                                                                | Тур                                                                                | Мах                                                                        |

|---------------------------------|-------------------------------------------------------------------|------------------------------------------------------------------------------------|------------------------------------------------------------------------------------|----------------------------------------------------------------------------|

| V <sub>DDA</sub> current supply | mA                                                                |                                                                                    | 500                                                                                | 590                                                                        |

| V <sub>DDQ</sub> current supply | mA                                                                |                                                                                    | 210                                                                                | 335                                                                        |

| V <sub>DD</sub> current supply  | mA                                                                |                                                                                    | 175                                                                                | 230                                                                        |

| SerDes total power dissipation  | W                                                                 |                                                                                    | 1.7                                                                                | 2.5                                                                        |

|                                 | V <sub>DDQ</sub> current supply<br>V <sub>DD</sub> current supply | V <sub>DDQ</sub> current supply     mA       V <sub>DD</sub> current supply     mA | V <sub>DDQ</sub> current supply     mA       V <sub>DD</sub> current supply     mA | VDDQ current supply     mA     210       VDD current supply     mA     175 |

$T_{C}$  = 0°C to  $T_{C}$  = 85°C,  $V_{DDQ}$  = 2.3 to 2.7 V,  $V_{DD}$  = 1.7 to 1.9 V,  $V_{DDA}$  = 1.7 to 1.9 V

Note:

1. Measurement conditions: full rate and half rate, random data. Maximum value covers both terminated and unterminated conditions.

#### Table 15. SSTL\_2 I/O Operating Conditions.

$T_{C}$  = 0°C to  $T_{C}$  = 85°C,  $V_{DDQ}$  = 2.3 to 2.7 V,  $V_{DD}$  = 1.7 to 1.9 V,  $V_{DDA}$  = 1.7 to 1.9 V

| Symbol                          | Parameters                                                       | Units | Min                      | Тур              | Max                      |

|---------------------------------|------------------------------------------------------------------|-------|--------------------------|------------------|--------------------------|

| V <sub>DDQ</sub> <sup>[1]</sup> | Supply Voltage used to derive the SSTL_2 input reference voltage | V     | 2.3                      | 2.5              | 2.7                      |

| V <sub>IH (DC)</sub>            | Input High voltage                                               | V     | V <sub>REF</sub> + 0.18  |                  | $V_{DDQ} + 0.3$          |

| V <sub>IL(DC)</sub>             | Input Low voltage                                                | V     | - 0.3                    |                  | V <sub>REF</sub> - 0.18  |

| V <sub>IH (AC)</sub>            | Input High voltage                                               | V     | V <sub>REF</sub> + 0.35  |                  | V <sub>DDQ</sub> + 0.3   |

| V <sub>IL(AC)</sub>             | Input Low voltage                                                | V     | - 0.3                    |                  | V <sub>REF</sub> - 0.35  |

| V <sub>REF</sub>                | SSTL_2 Output reference voltage                                  | V     | 1.15                     | 1.25             | 1.35                     |

| V <sub>TERM</sub>               | Termination voltage                                              | V     | V <sub>REF</sub> - 0.04  | V <sub>REF</sub> | V <sub>REF</sub> + 0.04  |

| V <sub>0H</sub> <sup>[2]</sup>  | Output High voltage                                              | V     | V <sub>TERM</sub> + 0.38 |                  |                          |

| V <sub>0L</sub> <sup>[2]</sup>  | Output Low voltage                                               | V     |                          |                  | V <sub>TERM</sub> - 0.38 |

Notes:

V<sub>DDQ</sub> is the MAC device I/O supply voltage.

See Figure 12 for measurement conditions.

# Table 16. HDMP-2689 CMOS I/O Operating Conditions.

$T_c = 0^{\circ}C$  to  $T_c = 85^{\circ}C$ ,  $V_{_{DDQ}} = 2.3$  to 2.7 V,  $V_{_{DD}} = 1.7$  to 1.9 V,  $V_{_{DDA}} = 1.7$  to 1.9 V, VDDQ is the FC-1MAC device I/O supply voltage.

| Symbol          | Parameters          | Units | Min Typ               | Max                  |

|-----------------|---------------------|-------|-----------------------|----------------------|

| V <sub>IH</sub> | Input High voltage  | V     | $0.7 \times V_{DDQ}$  | V <sub>DDQ</sub>     |

| V <sub>IL</sub> | Input Low voltage   | V     | GND                   | $0.3 \times V_{DDQ}$ |

| V <sub>OH</sub> | Output High voltage | V     | V <sub>DDQ</sub> -0.1 |                      |

| V <sub>OL</sub> | Output Low voltage  | V     | GND                   | 0.4                  |

#### Table 17. HDMP-2689 AC Electrical Specifications.

| Symbol                                       | Parameters                                                                        | Units | Min | Тур | Max              |

|----------------------------------------------|-----------------------------------------------------------------------------------|-------|-----|-----|------------------|

| t <sub>r, RFCP/N</sub>                       | RFCP/N LVPECL input rise time, $V_{\text{IL, LVPECL}}$ to $V_{\text{IH, LVPECL}}$ | ns    |     | 1.5 |                  |

| t <sub>f,RFCP/N</sub>                        | RFCP/N LVPECL input fall time, $V_{\text{IH, LVPECL}}$ to $V_{\text{IL, LVPECL}}$ | ns    |     | 1.5 |                  |

| t <sub>rd, HS_OUT</sub> <sup>[1, 5]</sup>    | HS_OUT differential rise time, 20% to 80%                                         | ps    |     | 150 |                  |

| t <sub>fd, HS_OUT</sub> <sup>[1, 5]</sup>    | HS_OUT differential fall time, 80% to 20%                                         | ps    |     | 150 |                  |

| t <sub>r,SSTL</sub> <sup>[2,3]</sup>         | SSTL output rise time, $V_{OL, SSTL}$ to $V_{OH, SSTL}$                           | ns    |     |     | 2.3              |

| t <sub>f,SSTL</sub> <sup>[2,3]</sup>         | SSTL output fall time, $V_{\rm OH,\ SSTL}$ to $V_{\rm OL,\ SSTL}$                 | ns    |     |     | 1.5              |

| V <sub>IP,HS_IN</sub> <sup>[4]</sup>         | HS_IN input pk-pk differential voltage                                            | V     | 0.3 |     | 1.6              |

| V <sub>PK,HS_OUT</sub> <sup>[1, 5]</sup>     | HS_OUT output pk-pk differential voltage, $(Z_0{=}50\Omega)^{[1]}$                | V     | 725 | 880 | 1050             |

| V <sub>Sustain,HS_OUT</sub> <sup>[1.5]</sup> | HS_OUT output sustain level differential voltage, (Z_0= 50 $\Omega)^{[1]}$        | V     | 675 | 830 | 1000             |

| V <sub>IP, LVPECL</sub>                      | RFCP, RFCN input swing (single ended)                                             | V     | 200 |     | V <sub>DDA</sub> |

# $T_{C}$ = 0°C to $T_{C}$ = 85°C, $V_{DDQ}$ = 2.3 to 2.7 V, $V_{DD}$ = 1.7 to 1.9 V, $V_{DDA}$ = 1.7 to 1.9 V

#### Notes:

1. Measured with 2 pF capacitive load.

2. See Figure 12 for test conditions.

3. SSTL\_2 AC Input Signals meet JEDEC Standard No. JESD8-9A test conditions (minimum slew rate 1.0V/ns). See JEDEC Table 3.

4. Note LOS pin description.

5. Measured at default settings, maximum amplitude and medium peaking (11111011).

# Table 18. HDMP-2689 Transmitter Section Output Jitter Characteristics.

$T_C$  = 0°C to  $T_C$  = 85°C,  $V_{DDQ}$  = 2.3 to 2.7 V,  $V_{DD}$  = 1.7 to 1.9 V,  $V_{DDA}$  = 1.7 to 1.9 V

| Symbol            | Parameters                                                           | Units | Min   | Тур         | Max     |

|-------------------|----------------------------------------------------------------------|-------|-------|-------------|---------|

| RJ <sup>[1]</sup> | Random Jitter at TXnP/N (1s deviation of 50% crossing point)         | ps    |       | 4           |         |

| DJ <sup>[2]</sup> | Deterministic Jitter at TXnP/N (peak to peak), K28.5+/K28.5- pattern | ps    |       | 10          |         |

| DJ <sup>[3]</sup> | Deterministic Jitter at TXnP/N (peak to peak), CRPAT pattern         | ps    |       | 15          |         |

| TJ                | Total Jitter (TJ=DJ+14*RJ) (K28.5+/K28.5- pattern)                   | ps    |       | 66          |         |

| J                 | Jitter Tolerance                                                     |       | Fibre | Channel con | npliant |

Notes:

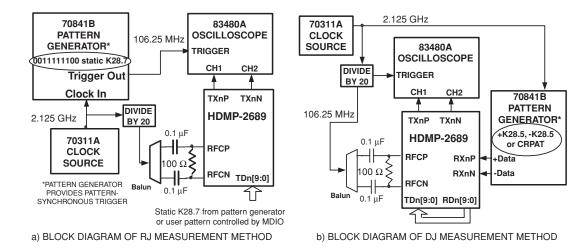

1. Defined by Fibre Channel specifications X3.230 - 1994 FC-PH, Annex A section A4.4 (oscilloscope method) and tested using setup shown in Figure 20.

2. Defined by Fibre Channel specifications X3.230 – 1994 FC-PH, Annex A section A4.4 and tested using the set up shown in Figure 20.

3. Defined by Fibre Channel Technical Report "Methodologies for Jitter specifications," Annex B, and tested using the set up shown in Figure 20.

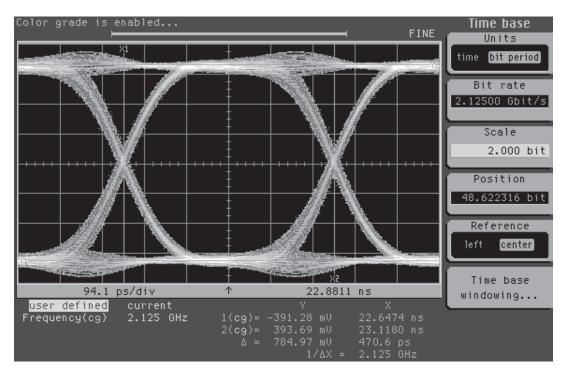

Figure 18. Serial Output Eye Diagram.

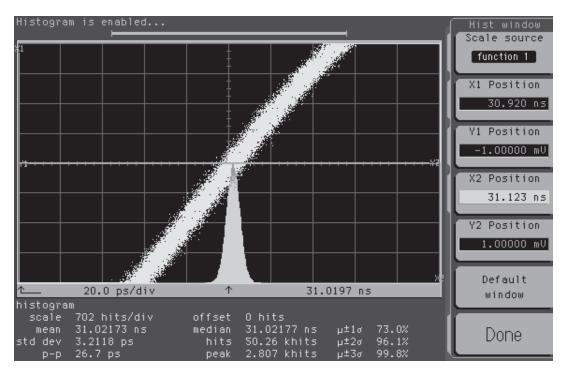

Figure 19. Serial Output Random Jitter with TX pre-emphasis off.

#### Figure 20. Transmitter DJ and RJ Measurement Method.

#### Table 19. Pin Input Capacitance.

| Symbol | Parameters                           | Units | Min | Тур | Max |

|--------|--------------------------------------|-------|-----|-----|-----|

| CINPUT | Input Capacitance on SSTL Input pins | pF    |     | 1.1 |     |

# **Package Information**

#### **Package Thermal Characteristics**

| Symbol              | Parameter                                                   | Units | Тур | Max  |

|---------------------|-------------------------------------------------------------|-------|-----|------|

| P <sub>Dmax</sub>   | Power Dissipation                                           | W     |     | 2.5  |

| $\theta_{JA}^{[1]}$ | Thermal Resistance: Junction to Ambient                     |       |     |      |

| 0.1                 | Air Flow (LFPM)                                             |       |     |      |

|                     | 0                                                           | °C/W  |     | 27.8 |

|                     | 200                                                         | °C/W  |     | 24.3 |

|                     | 400                                                         | °C/W  |     | 23.1 |

|                     | 600                                                         | °C/W  |     | 22.1 |

| $\Psi_{JT}^{[2]}$   | Thermal Characterization parameter: Junction to package top | °C/W  |     | 4.8  |

| $\Psi_{JB}^{[3]}$   | Thermal Characterization parameter: Junction to board       | °C/W  |     | 19.3 |

#### Notes:

Based on independent package testing done by Agilent,

1. θ<sub>JA</sub> is based on thermal measurement in still air environment at 25°C on a standard 4 x 4" FR4 PCB as specified in EIA/JESD 51-9.

2.  $\Psi_{JT}$  is used to determine the actual junction temperature in a given application, using the following equation:

$T_J = \Psi_{JT} \times P_D + T_T$  where  $T_T$  is the measured temperature on top center of the package (also known as Case temperature, Tc) and  $P_D$  is the power being dissipated.

3.  $\Psi_{JB}$  is used to determine the actual junction temperature in a given application, using the following equation:

$T_J = \Psi_{JB} \times P_D + T_B$  where  $T_B$  is measured board temperature, along the side of package at center on board surface and  $P_D$  is the power being dissipated.

| 4          | 1.76±0.21    | 0.56±0.06  | STANDARD |  |  |

|------------|--------------|------------|----------|--|--|

| NO. LAYERS | DIM "A"      | DIM "B"    | NOTES    |  |  |

| Р          | BGA THICKNES | S SCHEDULE |          |  |  |

$17^{16} 15^{14} 13^{12} 11^{10} 9 \ {}^8 \ {}^6 \ {}^6 \ {}^4 \ {}^2 \ {}^1$

A1 BALL PAD CORNER -

BOTTOM VIEW 289 Solder Balls

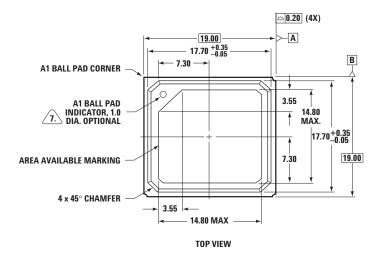

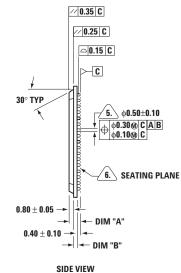

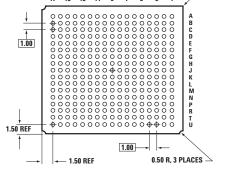

Figure 21. Package Layout and Marking Top View.

NOTES: UNLESS OTHERWISE SPECIFIED

- 1. All dimensions and tolerances conform to ASME Y14.5M-1994.

- 2. The basic solder ball grid pitch is 1.00 mm.

- 3. Solder ball matrix size is 17 x 17.

- 4. Number of solder balls is 289.

- 5. Dimension is measured at the maximum solder ball diameter. Parallel to primary datum C.

- 6. Primary datum C and seating plane are defined by the spherical crowns of the solder balls.

- 7. A1 ball pad corner I.D. for plate mold: marked by laser. Auto mold: dimple formed by mold cap.

- 8. This drawing conforms to the JEDEC registered outline MS-034/A.

#### Marking Diagram: Text Code

| manning brug |                                           |

|--------------|-------------------------------------------|

| Text Code    | Description                               |

| LLLLLLLL NM  | LLLLLLLL=Wafer Lot Number NN=Wafer Number |

| B2.3         | Die Revision                              |

| G YYWW       | G=Supplier Code                           |

|              | Date Code (YY=YEAR, WW=WEEK)              |

| ΑΑΑΑΑΑΑΑ     | A Country of Assembly                     |

|              |                                           |

Figure 22. Guidelines for Decoupling Capacitor Connections.

Figure 23. Recommended Decoupling Capacitor Placement.

# Pin Diagram

# Transceiver Pinout (Top View) (Rev 1.0)

# 19mm x 19mm body, 17mm by 17mm array, 289 pins populated, 1mm ball pitch

|   | 1     | 2     | 3     | 4     | 5     | 6     | 7     | 8     | 9     | 10    | 11    | 12    | 13    | 14    | 15    | 16    | 17    |   |

|---|-------|-------|-------|-------|-------|-------|-------|-------|-------|-------|-------|-------|-------|-------|-------|-------|-------|---|

| A | RXAP  | GNDA  | RXBP  | VDDA2 | TXAP  | GNDA  | TXBP  | VDDA2 | RFCP  | VDDA2 | TXCP  | GNDA  | TXDP  | VDDA2 | RXCP  | GNDA  | RXDP  | А |

| В | RXAN  | VDDA1 | RXBN  | GNDA  | TXAN  | VDDA2 | TXBN  | GNDA  | RFCN  | GNDA  | TXCN  | VDDA2 | TXDN  | GNDA  | RXCN  | VDDA3 | RXDN  | В |

| С | VDDA1 | GNDA  | VDDA1 | GNDA  | VDDA2 | GNDA  | VDDA2 | N/C   | GNDA  | N/C   | VDDA2 | GNDA  | VDDA2 | GNDA  | VDDA3 | GNDA  | VDDA3 | С |

| D | GNDIN | RSVN1 | GNDA  | VDDA1 | GNDA  | VDDA2 | GNDA  | GNDA  | GNDA  | RREFA | GNDA  | VDDA2 | GNDA  | VDDA3 | GNDA  | GND   | PMX   | D |

| E | GNDD  | RSVN2 | VDDQ  | VDD   | GNDA  | GNDA  | VDDA1 | GNDA  | VDDA2 | GNDA  | VDDA3 | GNDA  | GNDA  | GNDIN | N/C   | N/C   | GNDD  | Е |

| F | TCLK  | TMS   | TDO   | TDI   | RSTN  | GNDA  | VREF  | GND   | DVAD2 | DVAD1 | DVAD0 | F |

| G | VDDQ  | LOSA  | GNDD  | TRSTN | VDD   | GND   | VDD   | MDIO  | MDC   | LOSD  | VDDQ  | G |

| Н | RDA9  | RDA8  | RDA7  | RDA6  | GND   | GNDIN | RCD   | RDD7  | RDD8  | RDD9  | Н |

| J | GNDD  | RDA5  | VDDQ  | RCA   | VDD   | GND   | VDD   | RDD3  | VDDQ  | RDD6  | GNDD  | J |

| К | RDA4  | RDA3  | RDA0  | TDA7  | GND   | TDD7  | RDD0  | RDD4  | RDD5  | К |

| L | VDDQ  | RDA1  | GNDD  | TDA4  | VDD   | GND   | VDD   | TDD4  | GNDD  | RDD1  | VDDQ  | L |

| Μ | RDA2  | TDA8  | TCA   | TDA2  | LOSB  | GNDIN | VDD   | GND   | VDD   | GND   | VDD   | GNDIN | LOSC  | TDD2  | TCD   | TDD8  | RDD2  | М |

| N | GNDD  | TDA6  | VDDQ  | RDB9  | GNDD  | RDB4  | VDD   | GNDIN | VDD   | GNDIN | VDD   | RCC   | GNDD  | RDC9  | VDDQ  | TDD6  | GNDD  | Ν |

| Р | TDA9  | TDA3  | TDA0  | RDB7  | RDB5  | RDB1  | TDB8  | TDB4  | TDB0  | TCC   | TDC9  | RDC2  | RDC6  | RDC7  | TDD0  | TDD3  | TDD9  | Ρ |

| R | VDDQ  | TDA1  | GNDD  | RDB3  | VDDQ  | TDB9  | GNDD  | TDB3  | VDDQ  | TDC4  | GNDD  | RDC0  | VDDQ  | RDC5  | GNDD  | TDD1  | VDDQ  | R |

| Т | TDA5  | RDB8  | RCB   | RDB2  | TDB7  | TDB6  | TCB   | TDB2  | TDC0  | TDC3  | TDC5  | TDC6  | TDC8  | RDC3  | RDC4  | RDC8  | TDD5  | Т |

| U | GNDD  | RDB6  | VDDQ  | RDB0  | GNDD  | TDB5  | VDDQ  | TDB1  | GNDD  | TDC1  | VDDQ  | TDC2  | GNDD  | TDC7  | VDDQ  | RDC1  | GNDD  | U |

|   | 1     | 2     | 3     | 4     | 5     | 6     | 7     | 8     | 9     | 10    | 11    | 12    | 13    | 14    | 15    | 16    | 17    |   |

|   |       |       |       |       |       |       |       |       |       |       |       |       |       |       |       |       |       |   |

#### Notes:

GND, GNDIN, and GNDD may be connected together.

GNDA is recommended to be on a separate plane.

# I/O Type Definitions

| I/O <b>T</b> ype | Definition                      |

|------------------|---------------------------------|

| I-CMOS           | CMOS input                      |

| I/O-CMOS         | CMOS bi-directional             |

| 0-CMOS           | CMOS output                     |

| I-LVPECL         | LVPECL input                    |

| 0-SSTL2          | SSTL_2 output                   |

| I-SSTL2          | SSTL_2 input                    |

| HS_IN            | High speed input                |

| HS_OUT           | High speed output               |

| I-ANLG           | Analog input                    |

| 0-ANLG           | Analog output                   |

| 0-PVT            | PVT output                      |

| S                | Power supply or ground          |

| N/C              | No connection, must be floating |

| -                |                                 |

# **Pin List**

| I/O DEF                                                                              | INITION                                                            |          |                                                                                                                                                                                                                                                                                                                                         |

|--------------------------------------------------------------------------------------|--------------------------------------------------------------------|----------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Name                                                                                 | Pin                                                                | Туре     | Signal                                                                                                                                                                                                                                                                                                                                  |

| RSTN                                                                                 | F05                                                                | I-CMOS   | Chip Reset (FIFO Clear): Active Low                                                                                                                                                                                                                                                                                                     |

| DVAD0<br>DVAD1<br>DVAD2                                                              | F17<br>F16<br>F15                                                  | I-CMOS   | Device Address Input: 3 Bit input address with DVAD2 as MSB. Full address is the Device Address followed by the 2 bit Channel Address.                                                                                                                                                                                                  |

| PMX                                                                                  | D17                                                                | I-CMOS   | Enable CODEC or buffer mode (see Table 1)                                                                                                                                                                                                                                                                                               |

| N/C                                                                                  | C08, C10,<br>E15, E16                                              | N/C      | No Connect: must be left floating.                                                                                                                                                                                                                                                                                                      |

| MDIO                                                                                 | G14                                                                | I/O-CMOS | MDIO Input/Output: Used to read/write the MDIO registers.                                                                                                                                                                                                                                                                               |

| MDC                                                                                  | G15                                                                | I-CMOS   | MDIO Clock: Input clock to the MDIO control block.                                                                                                                                                                                                                                                                                      |

| RFCP<br>RFCN                                                                         | A09<br>B09                                                         | I-LVPECL | Differential Reference Input Clock: RFCP (+) and RFCN (-) is the 106.25 MHz differential clock pins supplied to the IC. The clock ismultiplied up to generate the serial bit clock and other internal clocks. This is a LVPECL input and assumes AC coupling and $100\Omega$ differentialinput termination into the pad (see Figure 3). |

| RCA<br>RCB<br>RCC<br>RCD                                                             | J04<br>T03<br>N12<br>H14                                           | 0-SSTL2  | Receiver Byte Clocks: Each receiver drives a 106.25 MHz or 53.125 MHz receive byte clock RCn.                                                                                                                                                                                                                                           |

| LOSA<br>LOSB<br>LOSC<br>LOSD                                                         | G02<br>M05<br>M13<br>G16                                           | 0-SSTL2  | $\label{eq:RX_LOS, Channels A-D: Receive channel loss of signal.} If RXnP/N \ge 300mV peak-to-peak differential, LOSn = logic 0  If 150 mV < RXnP/N < 300mV, LOSn undefined  If RXnP/N \le 150 mV peak-to-peak differential, LOSn = logic 1$                                                                                            |

| RDA0<br>RDA1<br>RDA2<br>RDA3<br>RDA4<br>RDA5<br>RDA6<br>RDA6<br>RDA7<br>RDA8<br>RDA9 | K03<br>L02<br>M01<br>K02<br>K01<br>J02<br>H04<br>H03<br>H02<br>H01 | 0-SSTL2  | Receive Data Pins, Channel A: Parallel data on this bus is valid on the rising and falling edge of RCA. See Table 2 for interpretation of this bus under different PMX settings. (See Figure 8 for termination)                                                                                                                         |

| RDB0<br>RDB1<br>RDB2<br>RDB3<br>RDB4<br>RDB5<br>RDB6<br>RDB7<br>RDB8<br>RDB9         | U04<br>P06<br>T04<br>R04<br>N06<br>P05<br>U02<br>P04<br>T02<br>N04 | 0-SSTL2  | Receive Data Pins, Channel B: Parallel data on this bus is valid on the rising and falling edge of RCB. See Table 2 for interpretation of this bus under different PMX settings. (See Figure 8 for termination)                                                                                                                         |

| RDC0<br>RDC1<br>RDC2<br>RDC3<br>RDC4<br>RDC5<br>RDC6<br>RDC7<br>RDC8<br>RDC9         | R12<br>U16<br>P12<br>T14<br>T15<br>R14<br>P13<br>P14<br>T16<br>N14 | 0-SSTL2  | Receive Data Pins, Channel C: Parallel data on this bus is valid on the rising and falling edge of RCC. See Table 2 for interpretation of this bus under different PMX settings. (See Figure 8 for termination)                                                                                                                         |

# Pin List, continued

| I/O DEF      | INITION    |          |                                                                                                                                                                                                                     |

|--------------|------------|----------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Name         | Pin        | Туре     | Signal                                                                                                                                                                                                              |

| RDD0<br>RDD1 | K15<br>L16 | 0-SSTL2  | Receive Data Pins, Channel D: Parallel data on this bus is valid on the rising and falling edges of RCD. See Table 2 for<br>interpretation of this bus under different PMX settings. (See Figure 8 for termination) |

| RDD2         | M17        |          |                                                                                                                                                                                                                     |

| RDD3         | J14        |          |                                                                                                                                                                                                                     |

| RDD4         | K16        |          |                                                                                                                                                                                                                     |

| RDD5         | K17        |          |                                                                                                                                                                                                                     |

| RDD6<br>RDD7 | J16<br>H15 |          |                                                                                                                                                                                                                     |

| RDD8         | H16        |          |                                                                                                                                                                                                                     |

| RDD9         | H17        |          |                                                                                                                                                                                                                     |

| RXAP         | A01        | HS_IN    | Received Serial Data Inputs: 0.01 $\mu$ F AC-coupled high-speed differential inputs (see Figyre 5).                                                                                                                 |

| RXAN         | B01        |          |                                                                                                                                                                                                                     |

| RXBP         | A03        |          |                                                                                                                                                                                                                     |

| RXBN         | B03        |          |                                                                                                                                                                                                                     |

| RXCP         | A15        |          |                                                                                                                                                                                                                     |

| RXCN<br>RXDP | B15<br>A17 |          |                                                                                                                                                                                                                     |

| RXDN         | B17        |          |                                                                                                                                                                                                                     |

| ТХАР         | A05        | HS OUT   | Transmitted Serial Data Outputs: 0.01 μF AC-coupled high-speed differential inputs (see Figyre 5). Note, if high speed                                                                                              |

| TXAN         | B05        |          | output driver is disabled, then both outputs are held at Logic 1.                                                                                                                                                   |

| ТХВР         | A07        |          |                                                                                                                                                                                                                     |

| TXBN         | B07        |          |                                                                                                                                                                                                                     |

| ТХСР         | A11        |          |                                                                                                                                                                                                                     |

| TXCN         | B11        |          |                                                                                                                                                                                                                     |

| TXDP<br>TXDN | A13<br>B13 |          |                                                                                                                                                                                                                     |

|              |            | 1.0071.0 |                                                                                                                                                                                                                     |

| TCA          | M03<br>T07 | I-SSTL2  | Transmit Byte Clock: These pins are used to latch transmit data for channels A, B, C, D into the IC. Must have the same                                                                                             |

| TCB<br>TCC   | P10        |          | frequency as reference clock.                                                                                                                                                                                       |

| TCD          | M15        |          |                                                                                                                                                                                                                     |

| TDI          | F04        | I-CMOS   | Scan Test Interface: TDI is the test data input, TDO is the test data output, TMS is the test mode select, TCLK is the test                                                                                         |

| TDO          | F03        | 0-CMOS   | clock, and TRSTN is the test reset pin (active low).                                                                                                                                                                |

| TMS          | F02        | I-CMOS   |                                                                                                                                                                                                                     |

| TCLK         | F01        | I-CMOS   |                                                                                                                                                                                                                     |

| TRSTN        | G04        | I-CMOS   |                                                                                                                                                                                                                     |

| TDA0         | P03        | I-SSTL2  | Data Inputs: Parallel data on this bus is clocked in by TCA. See timing diagram in Figure 9. See Table 2 for interpretation                                                                                         |

| TDA1<br>TDA2 | R02<br>M04 |          | of this bus under different PMX settings.                                                                                                                                                                           |

| TDA2<br>TDA3 | P02        |          |                                                                                                                                                                                                                     |

| TDA3         | L04        |          |                                                                                                                                                                                                                     |

| TDA5         | T01        |          |                                                                                                                                                                                                                     |

| TDA6         | N02        |          |                                                                                                                                                                                                                     |

| TDA7         | K04        |          |                                                                                                                                                                                                                     |

| TDA8         | M02        |          |                                                                                                                                                                                                                     |

| TDA9         | P01        |          |                                                                                                                                                                                                                     |

| TDB0         | P09        | I-SSTL2  | Data Inputs: Parallel data on this bus is clocked in by TCB. See timing diagram in Figure 9. See Table 2 for interpretation                                                                                         |

| TDB1         | U08        |          | of this bus under different PMX settings.                                                                                                                                                                           |

| TDB2         | T08        |          |                                                                                                                                                                                                                     |

| TDB3<br>TDB4 | R08<br>P08 |          |                                                                                                                                                                                                                     |

| TDB4<br>TDB5 | P08<br>U06 |          |                                                                                                                                                                                                                     |

| TDB5         | T06        |          |                                                                                                                                                                                                                     |