# HN27C101A Series

# 1M (128K x 8-bit) UV and OTP EPROM

### DESCRIPTION

The Hitachi HN27C101A is a 1-Megabit Ultraviolet Erasable and One-Time Programmable Electrically Programmable Read Only Memory organized as 131,072 x 8-bits.

The HN27C101A features fast address access times and low power dissipation. This combination makes the HN27C101A suitable for high speed microcomputer systems. The HN27C101A offers high speed programming using page programming mode.

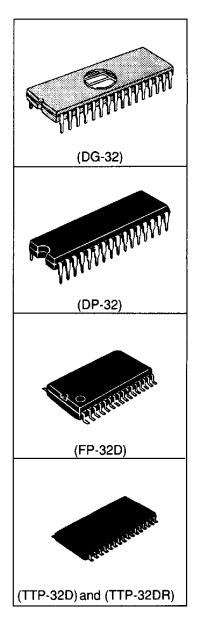

Hitachi's HN27C101A is offered in JEDEC-Standard Byte-Wide EPROM pinouts in 32-pin Ceramic and Plastic DIP and 32-lead Plastic SOP and TSOP packages. This allows socket replacement with Flash Memory and Mask ROMs. The HN27C101A TSOP package is offered in both standard and reverse bend pinouts.

The Ceramic DIP package is erasable by exposure to Ultraviolet light. The Plastic DIP, SOP and TSOP packaged devices are One-Time Programmable and once programmed, can not be rewritten.

#### **FEATURES**

· Fast Access Times:

100 ns/120 ns/150 ns/200 ns (max)

Single Power Supply:

V<sub>cc</sub> = 5 V ± 10%

• Low Power Dissipation:

Active Mode: 50 mW/MHz (typ)

Standby Mode: 5 μW (typ)

· High Speed Page and Word Programming:

Page Programming Time: 14 sec (typ)

· Programming Power Supply:

$V_{pp} = 12.5 \text{ V} \pm 0.3 \text{ V}$

Pin Arrangement:

JEDEC Standard Byte-Wide EPROM

Flash Memory and Mask ROM Compatible

Packages:

32-pin Ceramic DIP

32-pin Plastic DIP

32-lead Plastic SOP

32-lead Plastic TSOP (Type II)

### ORDERING INFORMATION

| Type No.       | Access Time | Package              |

|----------------|-------------|----------------------|

| HN27C101AG-10  | 100 ns      |                      |

| HN27C101AG-12  | 120 ns      | 32-pin Ceramic DIP   |

| HN27C101AG-15  | 150 ns      | (DG-32)              |

| HN27C101AG-20  | 200 ns      |                      |

| HN27C101AP-12  | 120 ns      | 32-pin Plastic DIP   |

| HN27C101AP-15  | 150 ns      | (DP-32)              |

| HN27C101AP-20  | 200 ns      |                      |

| HN27C101AFP-12 | 120 ns      | 32-lead Plastic SOP  |

| HN27C101AFP-15 | 150 ns      | (FP-32D)             |

| HN27C101AFP-20 | 200 ns      |                      |

| HN27C101ATT-12 | 120 ns      | 32-lead Plastic TSOP |

| HN27C101ATT-15 | 150 ns      | (TTP-32D)            |

| HN27C101ATT-20 | 200 ns      |                      |

| HN27C101ARR-12 | 120 ns      | 32-lead Plastic TSOP |

| HN27C101ARR-15 | 150 ns      | (TTP-32DR)           |

| HN27C101ARR-20 | 200 ns      | Reverse bend         |

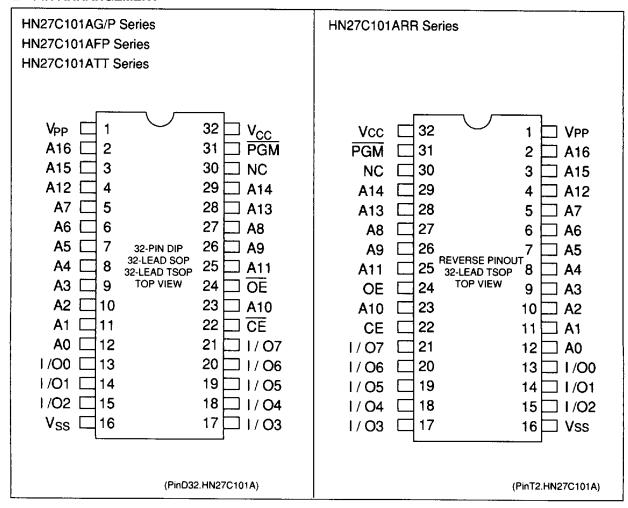

### **■ PIN ARRANGEMENT**

4496203 0025396 217

HITACHI

### **■ PIN DESCRIPTION**

| Pin Name                            | Function           |  |  |  |  |  |

|-------------------------------------|--------------------|--|--|--|--|--|

| A <sub>o</sub> - A <sub>16</sub>    | Address            |  |  |  |  |  |

| 1/O <sub>0</sub> - 1/O <sub>7</sub> | Input/Output       |  |  |  |  |  |

| CE                                  | Chip Enable        |  |  |  |  |  |

| ŌĒ                                  | Output Enable      |  |  |  |  |  |

| V <sub>cc</sub>                     | Power Supply       |  |  |  |  |  |

| V <sub>PP</sub>                     | Programming Supply |  |  |  |  |  |

| V <sub>ss</sub>                     | Ground             |  |  |  |  |  |

| PGM                                 | Programming Enable |  |  |  |  |  |

| NC                                  | No Connection      |  |  |  |  |  |

|                                     |                    |  |  |  |  |  |

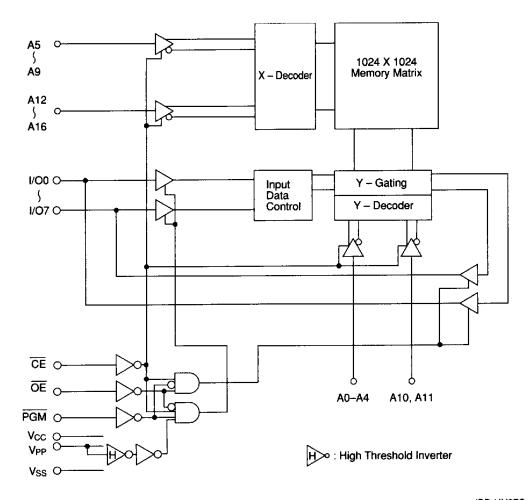

### **■ BLOCK DIAGRAM**

(BD.HN27C101A)

### **MODE SELECTION**

| Mode            | V <sub>PP</sub> | V <sub>cc</sub> | CE              | ŌĒ              | PGM             | A <sub>9</sub> | 1/0              |

|-----------------|-----------------|-----------------|-----------------|-----------------|-----------------|----------------|------------------|

| Read            | V <sub>cc</sub> | V <sub>cc</sub> | V <sub>IL</sub> | V <sub>IL</sub> | V <sub>IH</sub> | X 1            | D <sub>out</sub> |

| Output Disable  | V <sub>cc</sub> | V <sub>cc</sub> | V <sub>IL</sub> | V <sub>IH</sub> | V <sub>IH</sub> | X              | High-Z           |

| Standby         | V <sub>cc</sub> | V <sub>cc</sub> | V <sub>IH</sub> | Х               | Х               | X              | High-Z           |

| Program         | V <sub>PP</sub> | V <sub>cc</sub> | V <sub>IL</sub> | V <sub>IH</sub> | V <sub>IL</sub> | X              | D <sub>iN</sub>  |

| Program Verify  | V <sub>PP</sub> | V <sub>cc</sub> | VIL             | V, L            | V <sub>iH</sub> | Х              | D <sub>out</sub> |

| Page Data Latch | V <sub>PP</sub> | V <sub>cc</sub> | V <sub>IH</sub> | V <sub>tL</sub> | V <sub>IH</sub> | Х              | D <sub>IN</sub>  |

| Page Program    | V <sub>PP</sub> | V <sub>cc</sub> | V <sub>IH</sub> | V <sub>IH</sub> | V               | Х              | High-Z           |

| Program Inhibit | $V_{cc}$        | V <sub>cc</sub> | V <sub>IL</sub> | Vil             | Vil             | X              | High-Z           |

|                 | V <sub>pp</sub> | V <sub>cc</sub> | V <sub>IL</sub> | V <sub>IH</sub> | V <sub>IH</sub> | Х              | High-Z           |

|                 | V <sub>PP</sub> | V <sub>cc</sub> | V <sub>IH</sub> | VIL             | V <sub>IL</sub> | Х              | High-Z           |

|                 | V <sub>PP</sub> | V <sub>cc</sub> | V <sub>IH</sub> | V <sub>IH</sub> | V <sub>IH</sub> | Х              | High-Z           |

| Identifier      | V <sub>cc</sub> | V <sub>cc</sub> | V <sub>IL</sub> | V <sub>IL</sub> | V <sub>IH</sub> | V <sub>H</sub> | ID               |

- X = Don't Care.  $V_{pp}$  = 0 V to  $V_{CC}$ . 11.5 V  $\leq$  V<sub>H</sub>  $\leq$  12.5 V

## ■ ABSOLUTE MAXIMUM RATINGS

| Item                                       | Symbol            | Value                                                | Unit |

|--------------------------------------------|-------------------|------------------------------------------------------|------|

| Supply Voltage <sup>1</sup>                | V <sub>cc</sub>   | -0.6 to +7.0                                         | ٧    |

| Programming Voltage 1                      | V <sub>PP</sub>   | -0.6 to +13.5                                        | V    |

| All Input and Output Voltage 1.2           | VIN, VOUT         | -0.6 to +7.0                                         | V    |

| A <sub>9</sub> and OE Voltage <sup>2</sup> | V <sub>iD</sub>   | -0.6 to +13.0                                        | V    |

| Operating Temperature Range                | T <sub>OPR</sub>  | 0 to +70                                             | ° C  |

| Storage Temperature Range                  | T <sub>STG</sub>  | -65 to +125 <sup>3</sup><br>-55 to +125 <sup>4</sup> | ° C  |

| Storage Temperature Under Bias             | T <sub>BIAS</sub> | 0 to +80                                             | ° C  |

Notes:

- Relative to  $V_{ss}$ .  $V_{IN}$ ,  $V_{OUT}$ , and  $V_{ID}$  min = -1.0V for pulse width  $\leq$  20 ns. HN27C101AG.

- 3.

- HN27C101AP, HN27C101AFP, HN27C101ATT and HN27C101ARR.

# ■ CAPACITANCE $(T_a = 25^{\circ}C, f = 1 MHz)$

| Item               | Symbol           | Min. | Max. | Unit | Test Condition        |  |

|--------------------|------------------|------|------|------|-----------------------|--|

| Input Capacitance  | C <sub>IN</sub>  | -    | 10   | pF   | $V_{IN} = 0V$         |  |

| Output Capacitance | C <sub>OUT</sub> | -    | 15   | pF   | V <sub>OUT</sub> = 0V |  |

### HN27C101A Series

### DC ELECTRICAL CHARACTERISTICS FOR READ OPERATION

$(V_{CC} = 5V \pm 10\%, V_{PP} = V_{SS} \text{ to } V_{CC}, T_a = 0 \text{ to } 70^{\circ}\text{C})$

| ltem                              | Symbol           | Min.   | Тур. | Max.                             | Unit | Test Condition                                   |

|-----------------------------------|------------------|--------|------|----------------------------------|------|--------------------------------------------------|

| Input Leakage Current             | l <sub>u</sub>   | -      | -    | 2                                | μΑ   | V <sub>IN</sub> = 5.5 V                          |

| Output Leakage Current            | l <sub>LO</sub>  | -      | -    | 2                                | μΑ   | V <sub>OUT</sub> = 5.5 V/0.45 V                  |

| Operating V <sub>cc</sub> Current | I <sub>CC1</sub> | -      | -    | 30                               | mA   | $I_{OUT} = 0 \text{ mA}, \overline{CE} = V_{IL}$ |

|                                   | l <sub>cc2</sub> | -      | -    | 30                               | mA   | I <sub>OUT</sub> = 0 mA, f = 5 MHz               |

|                                   | l <sub>cc3</sub> | -      | -    | 50                               | mA   | I <sub>OUT</sub> = 0 mA, f = 10 MHz              |

| Standby V <sub>cc</sub> Current   | I <sub>SB</sub>  | -      | -    | 1                                | mA   | CE = V <sub>IH</sub>                             |

| V <sub>PP</sub> Current           | I <sub>PP1</sub> | -      | 1    | 20                               | μΑ   | V <sub>pp</sub> = 5.5 V                          |

| Input Voltage                     | V <sub>IH</sub>  | 2.2    | -    | V <sub>cc</sub> + 1 <sup>2</sup> | ٧    |                                                  |

|                                   | V <sub>IL</sub>  | -0.3 ¹ | -    | 0.8                              | >    |                                                  |

| Output Voltage                    | V <sub>OH</sub>  | 2.4    | -    | -                                | ٧    | I <sub>OH</sub> = -400 μA                        |

|                                   | V <sub>OL</sub>  | •      | -    | 0.45                             | ٧    | I <sub>OL</sub> = 2.1 mA                         |

Notes:

- 1.  $V_{IL}$  min = -1.0 V for pulse width  $\leq$  50 ns.

$V_{\rm H}^{\rm FL}$  max =  $V_{\rm CC}$  + 1.5 V for pulse width  $\leq$  20 ns. If  $V_{\rm H}$  is over the specified maximum value, Read operation can not be guaranteed.

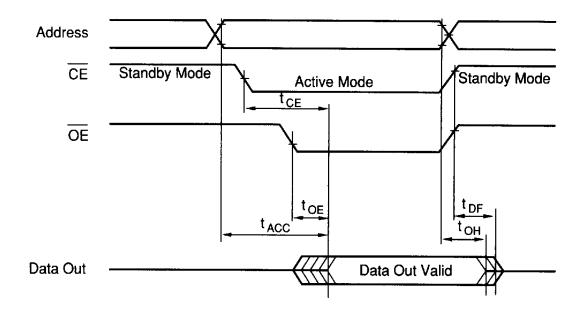

# ■ AC ELECTRICAL CHARACTERISTICS FOR READ OPERATION

$(V_{CC} = 5V \pm 10\%, V_{PP} = V_{SS} \text{ to } V_{CC}, T_a = 0 \text{ to } 70^{\circ}\text{C})$

### **Test Conditions**

· Input pulse levels:

0.45 V / 2.4 V

Input rise and fall times:

≤ 10 ns

Output load:

1 TTL Gate + 100 pF (Including scope and jig)

Reference levels for measuring timing: 0.8 V/2.0 V

|                                       |                  | -1   | 10   | -1   | 12   | -1   | 15   | -2   | 20   |      | Test                      |

|---------------------------------------|------------------|------|------|------|------|------|------|------|------|------|---------------------------|

| Item                                  | Symbol           | Min. | Мах. | Min. | Мах. | Min. | Мах. | Min. | Max. | Unit | Condition                 |

| Address Access Time                   | t <sub>ACC</sub> | -    | 100  | -    | 120  | -    | 150  | -    | 200  | ns   | CE = OE = V,L             |

| Chip Enable Access Time               | t <sub>ce</sub>  | -    | 100  | -    | 120  | -    | 150  | -    | 200  | ns   | OE = VIL                  |

| Output Enable Access<br>Time          | t <sub>OE</sub>  | •    | 60   | -    | 60   | -    | 70   | -    | 70   | ns   | CE = V <sub>IL</sub>      |

| Output Disable to High-Z <sup>1</sup> | t <sub>DF</sub>  | 0    | 50   | 0    | 50   | 0    | 50   | 0    | 50   | пѕ   | CE = V <sub>IL</sub>      |

| Output Hold to Address<br>Change      | t <sub>OH</sub>  | 0    | -    | 0    | -    | 0    | -    | 0    | -    | ns   | CE = OE = V <sub>IL</sub> |

Note:

$t_{\text{\tiny DF}}$  is defined as the time at which the output becomes an open circuit and data is no longer driven.

# 4

### ■ READ TIMING WAVEFORM

(TD.R.HN27C101A)

## ■ DC ELECTRICAL CHARACTERISTICS FOR PROGRAMMING OPERATIONS

$(V_{CC} = 6.25 \text{ V} \pm 0.25 \text{ V}, V_{PP} = 12.5 \text{ V} \pm 0.3 \text{ V}, T_a = 25 \text{ °C} \pm 5 \text{ °C})$

| Item                              | Symbol          | Min.               | Тур. | Max.                             | Unit | Test Condition                           |

|-----------------------------------|-----------------|--------------------|------|----------------------------------|------|------------------------------------------|

| Input Leakage Current             | l <sub>L1</sub> | -                  | -    | 2                                | μA   | V <sub>IN</sub> = 0 V to V <sub>CC</sub> |

| Operating V <sub>cc</sub> Current | I <sub>cc</sub> | -                  | -    | 30                               | mA   |                                          |

| Operating V <sub>PP</sub> Current | I <sub>PP</sub> | -                  | -    | 40                               | mA   | CE = PGM = V <sub>IL</sub>               |

| Input Voltage <sup>3</sup>        | V <sub>IH</sub> | 2.2                | -    | V <sub>cc</sub> +.5 <sup>6</sup> | >    |                                          |

|                                   | V <sub>IL</sub> | - 0.1 <sup>5</sup> | -    | 0.8                              | ٧    |                                          |

| Output Voltage                    | V <sub>OH</sub> | 2.4                | -    | -                                | ٧    | l <sub>OH</sub> = -400 μA                |

|                                   | V <sub>oL</sub> | -                  | -    | 0.45                             | ٧    | I <sub>OH</sub> = 2.1 mA                 |

Notes:

- V<sub>cc</sub> must be applied before V<sub>pp</sub> and removed after V<sub>pp</sub>.

- 2. V<sub>pp</sub> must not exceed 13 V, including overshoot.

- 3. Device reliability may be adversely affected if the device is installed or removed while  $V_{pp} = 12.5 \text{ V}$ .

- 4. Do not change  $V_{PP}$  from  $V_{IL}$  to 12.5 V or 12.5 V to  $V_{IL}$  when  $\overline{CE} = low$ .

- 5.  $V_{IL} \min = -0.6 \text{ V for pulse width} \le 20 \text{ ns.}$

- 6. If  $\tilde{V}_{H}$  is over the specified maximum value, programming operation can not be guaranteed.

# HN27C101A Series

# ■ AC ELECTRICAL CHARACTERISTICS FOR PROGRAMMING OPERATIONS

$(V_{\rm CC} = 6.25 \; V \pm 0.25 \; V, \, V_{\rm PP} = 12.5 \; v \pm 0.3 \; V, \, T_a = 25^{\circ} C \pm 5^{\circ} C)$

**Test Conditions**

Input pulse levels: 0.45 V / 2.4 V

Input rise and fall times: ≤ 20 ns

Reference levels for measuring timing: 0.8 V / 2.0V

| Item                                  | Symbol            | Min. | Тур. | Max. | Unit | Test Condition |

|---------------------------------------|-------------------|------|------|------|------|----------------|

| Address Setup Time                    | t <sub>AS</sub>   | 2    | -    | -    | μs   |                |

| Address Hold Time                     | t <sub>AH</sub>   | 0    | -    | -    | μs   |                |

| Data Setup Time                       | t <sub>os</sub>   | 2    | -    | -    | μs   |                |

| Data Hold Time                        | t <sub>oH</sub>   | 2    | -    | -    | μs   |                |

| Chip Enable Setup Time                | t <sub>ces</sub>  | 2    | -    | -    | μs   |                |

| V <sub>PP</sub> Setup Time            | t <sub>vPS</sub>  | 2    | -    | -    | μs   |                |

| V <sub>cc</sub> Setup Time            | t <sub>vcs</sub>  | 2    | -    | -    | μs   |                |

| Output Enable Setup Time              | t <sub>oes</sub>  | 2    | -    | -    | μs   |                |

| Output Disable Time                   | t <sub>of</sub>   | 0    | -    | 130  | ns   |                |

| PGM Initial Programming Pulse Width   | t <sub>PW</sub>   | 0.19 | 0.20 | 0.21 | ms   |                |

| PGM Overprogramming Pulse Width       | t <sub>opw</sub>  | 0.19 | -    | 5.25 | ms   |                |

| Data Valid from Output Enable Time    | t <sub>o∈</sub>   | 0    | -    | 150  | ns   |                |

| Output Enable Pulse During Data Latch | t <sub>LW</sub>   | 1    | -    | -    | μs   |                |

| Output Enable Hold Time               | t <sub>oeh</sub>  | 2    | -    | -    | μs   |                |

| Chip Enable Hold Time                 | t <sub>ceh</sub>  | 2    | -    |      | μs   |                |

| PGM Setup Time                        | t <sub>PGMS</sub> | 2    | -    | -    | μs   |                |

Note: 1. t<sub>DF</sub> is defined as the time at which the output becomes an open circuit and data is no longer driven.

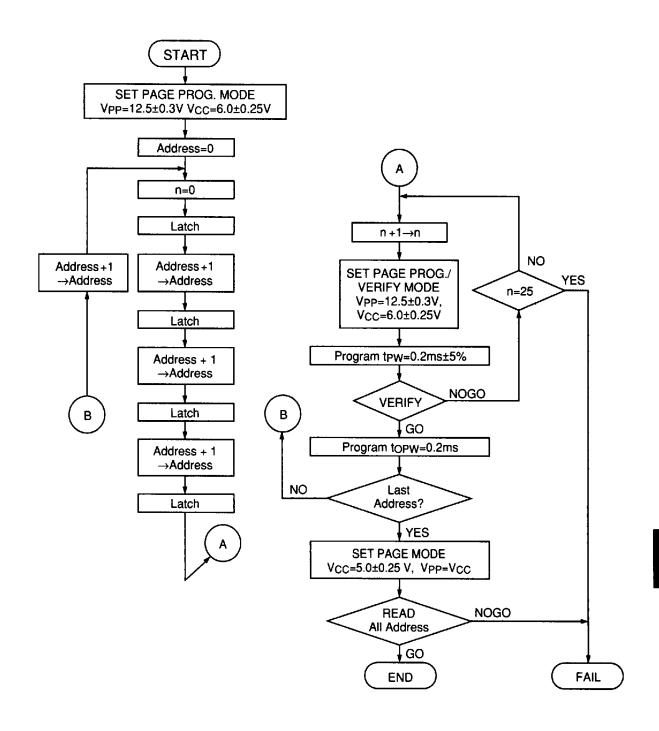

### **■ PAGE PROGRAMMING FLOWCHART**

The Hitachi HN27C101A can be programmed with the high performance Page Programming algorithm shown in the following flowchart. This algorithm provides a fast programming time without voltage stress to the device or deterioration in reliability of programmed data.

(FC.PP.HN27C101A)

4496203 0025402 340 **■ HITACHI**

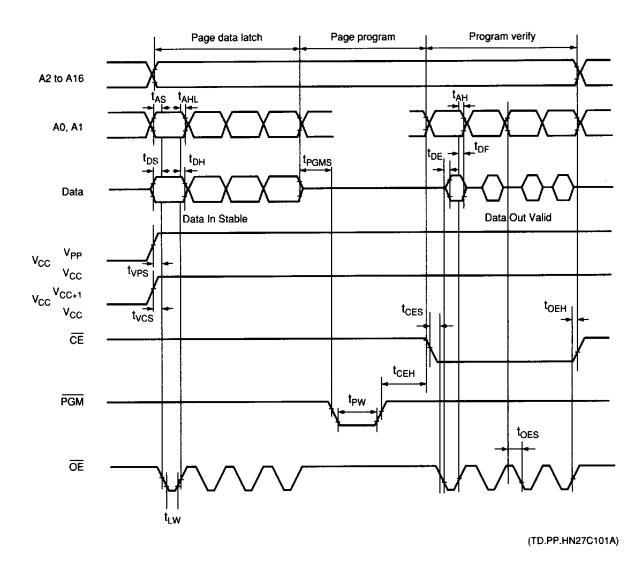

## **■ PAGE PROGRAMMING TIMING WAVEFORM**

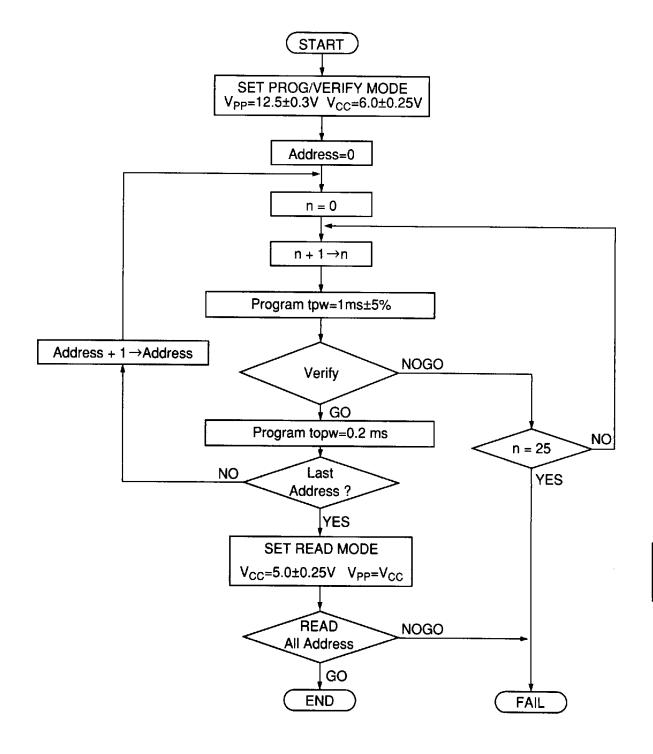

# **■ BYTE PROGRAMMING FLOWCHART**

The Hitachi HN27C101A can be programmed with the high performance Byte Programming algorithm shown in the following flowchart. This algorithm provides a fast programming time without voltage stress to the device or deterioration in reliability of programmed data.

(FC.P.HN27C101A)

🖿 4496203 0025404 113 🕶 🕒

**HITACHI**

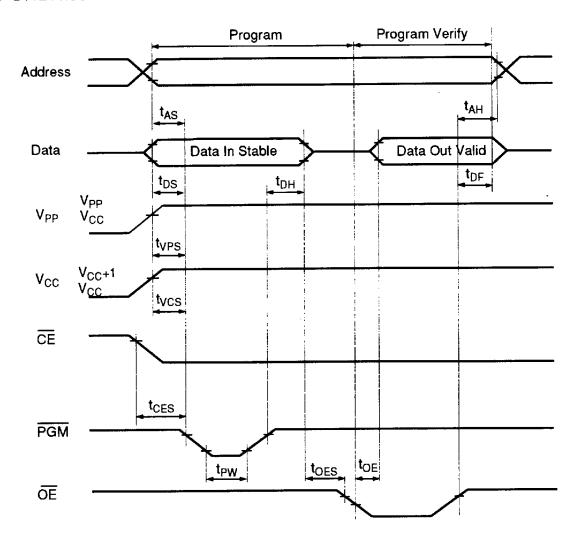

## **■ BYTE PROGRAMMING TIMING WAVEFORM**

(TD.P.HN27C101A)

### **■ ERASING THE HN27C101A**

The Hitachi HN27C101A Ceramic DIP package allow the device to be erased by exposure to ultraviolet light of 2537Å. All of the data is changed to "1" after this erasure procedure. The minimum integrated dose (UV intensity x exposure time) for erasure is 15 W-sec/cm².

## **■ DEVICE IDENTIFIER MODE DESCRIPTION**

The Device Identifier Mode allows binary codes to be read from the outputs that identify the manufacturer and the type of device. Using this mode with programming equipment, the device will automatically match its own erase and programming algorithm.

### **■ HN27C101A SERIES IDENTIFIER CODE**

| Identifier        | A <sub>o</sub>  | I/O, | I/O <sub>6</sub> | 1/O <sub>5</sub> | I/O <sub>4</sub> | I/O <sub>3</sub> | 1/O <sub>2</sub> | 1/0, | I/O <sub>0</sub> | Hex Data |

|-------------------|-----------------|------|------------------|------------------|------------------|------------------|------------------|------|------------------|----------|

| Manufacturer Code | V               | 0    | 0                | 0                | 0                | 0                | 1                | 1    | 1                | 07       |

| Device Code       | V <sub>IH</sub> | 0    | 0                | 1                | 1                | 1                | 0                | 0    | 0                | 38       |

Notes:

- 1.  $V_{cc} = 5.0 \text{ V} \pm 10\%$

- 2.  $A_9 = 12.0 \text{ V} \pm 0.5 \text{V}$

- 3.  $A_1^3 A_8$ ,  $A_{10} A_{16}$ ,  $\overline{CE}$ ,  $\overline{OE} = V_{1L}$ ,  $\overline{PGM} = V_{1H}$

- 4. X = Don't Care

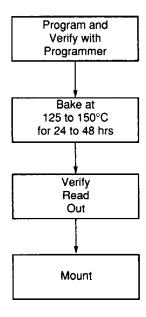

## ■ HN27C101AP/FP/TT/RR RECOMMENDED SCREENING CONDITIONS

Before mounting the HN27C101A plastic packages, please make the following screening (baking without bias) shown below:

(RSC.EPROM)