# ML6652 10/100Mbps Ethernet Fiber and Copper

Media Converter with Auto-Negotiation

### **GENERAL DESCRIPTION**

The ML6652 is a low cost multi-function / multi-standard single chip Media Converter that provides 10Mbps and 100Mbps signal conversion between twisted pair and fiber optic Ethernet technologies. The device supports conversion between:

> 10BASE-T and 10BASE-FL 100BASE-TX and 100BASE-FX/SX 100BASE-FX and 100BASE-SX FLP Bursts and FLNP Bursts

The device supports 10Mbps and 100Mbps operating data rates with Auto-Negotiation using 850nm or 1300nm optics. One or both of the fiber optic and twisted pair interfaces can be interfaced to industry standard miniature fiber optic components or Physical Media Dependent (PMD) modules using Positive Emitter Coupled Logic/Low Voltage Positive Emitter Coupled Logic (PECL/LVPECL) compatible modes. Support of other wavelengths is possible using the PECL/LVPECL interface.

### APPLICATIONS

- Single/Multi Port 10/100 Auto-Negotiating Media Converters

- Single/Multi Port 100BASE-FX/SX to100BASE-TX

Media Converters

- Single/Multi Port 10BASE-FL to 10BASE-T Media Converters

- Single/Multi Mode Fiber Converters

- Fiber Optic Front-End for Network Interface Cards (NICs), Repeaters, Bridges, Hubs and Switches

- Fiber-To-The-Desk/Building/Factory Floor as well as Home Connectivity Gateway/Demarcation Products

- Redundant Link Converters and Wavelength Converters

### FEATURES

- Complete implementation of fiber optic and twisted pair media interface

- Supports ISO/IEC 8802.3, IEEE 802.3 and TIA/EIA-785 Industry Standards, including full Auto-Negotiation for twisted pair and fiber optic media

- 850nm, 1300nm miniature fiber optic components and PMD modules

- Supports 1:1 receiver/transmitter transformer ratio for twisted pair

- Low latency

- Integrated voltage and current references

- Integrated twisted pair output wave shaping eliminates external filtering

- Integrated twisted pair 10BASE-T input filter and 100BASE-TX equalizer with baseline wander correction circuit

- Serial Management Interface

- Full and Half Duplex with Auto-Negotiation

- Integrated LED Driver

- Integrated Data Quantizer

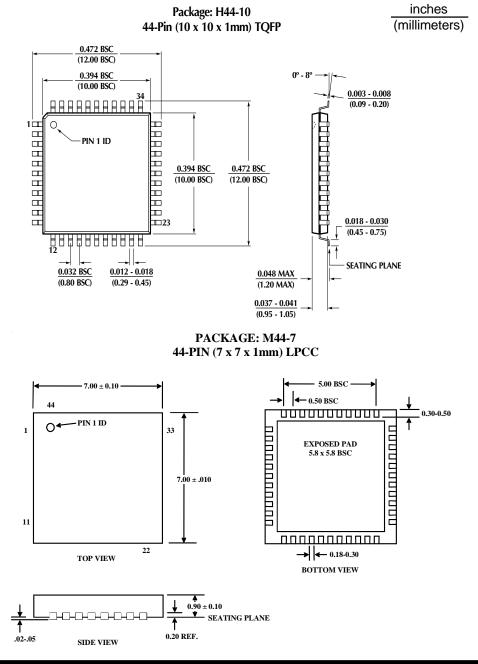

- Small 44-Pin TQFP and LPCC/QFN

- Low 3.3V power supply

- Integrated Link Integrity Warning (LIW)

### **TABLE OF CONTENTS**

| General Description                | 1  |

|------------------------------------|----|

| Features                           | 1  |

| Applications                       | 1  |

| Warranty Information               | 2  |

| Block Diagram                      | 3  |

| Pin Configuration                  | 4  |

| Pin Descriptions                   | 4  |

| General Description                | 13 |

| Functional Description             |    |

| Device Configuration               |    |

| Default Power Configuration        |    |

| Serial Management Interface        |    |

| Speed Selection                    |    |

| Operating Modes                    |    |

| Transparent Mode                   |    |

| Fiber Optic Input/Output Interface | 18 |

| Power Down Mode                    | 19 |

| Loopback Mode                      | 19 |

| Scrambler/Descrambler              | 19 |

| Output Off Mode                    | 19 |

| Backup Link Mode                   | 19 |

| LED Interface                      |    |

| Control Registers                  |    |

| Status Registers                   |    |

| Electrical Characteristics         |    |

| Physical Dimensions                |    |

| Order Information                  | 28 |

### WARRANTY

Micro Linear makes no representations or warranties with respect to the accuracy, utility, or completeness of the contents of this publication and reserves the right to make changes to specifications and product descriptions at any time without notice. No license, express or implied, by estoppel or otherwise, to any patents or other intellectual property rights is granted by this document. The circuits contained in this document are offered as possible applications only. Particular uses or applications may invalidate some of the specifications and/or product descriptions contained herein. The customer is urged to perform its own engineering review before deciding on a particular application. Micro Linear assumes no liability whatsoever, and disclaims any express or implied warranty, relating to sale and/or use of Micro Linear products including liability or warranties relating to merchantability, fitness for a particular purpose, or infringement of any intellectual property right. Micro Linear products are not designed for use in medical, life saving, or life sustaining applications. If this document is "Advance", its contents describe a Micro Linear product that is currently under development. All detailed specifications including pinouts and electrical specifications may be changed without notice. If this document is "Preliminary", its contents are based on early silicon measurements. Typical data is representative of the product but is subject to change without notice. Pinout and mechanical dimensions are final, its contents are based on a characterized product, and it is believed to be accurate at the time of publication. Final Data Sheets supersede all previously published versions. This document is Final.

© 2004 Micro Linear Corporation. All rights reserved. All other trademarks are the property of their respective owners.

Products described herein may be covered by one or more of the following U.S. patents: 4,897,611; 4,964,026; 5,027,116; 5,281,862; 5,283,483; 5,418,502; 5,508,570; 5,510,727; 5,523,940; 5,546,017; 5,559,470; 5,565,761; 5,592,128; 5,594,376; 5,652,479; 5,661,427; 5,663,874; 5,672,959; 5,689,167; 5,714,897; 5,717,798; 5,742,151; 5,747,977; 5,754,012; 5,757,174; 5,767,653; 5,777,514; 5,793,168; 5,798,635; 5,804,950; 5,808,455; 5,811,999; 5,818,207; 5,818,669; 5,825,165; 5,825,223; 5,838,723; 5,844,378; 5,844,941. Japan: 2,598,946; 2,619,299; 2,704,176; 2,821,714. Other patents are pending.

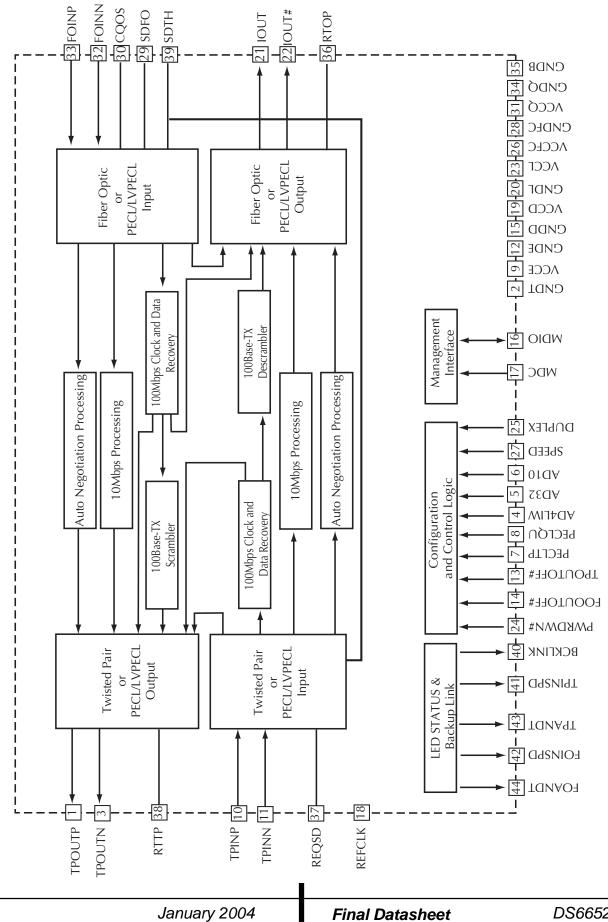

### **BLOCK DIAGRAM**

3

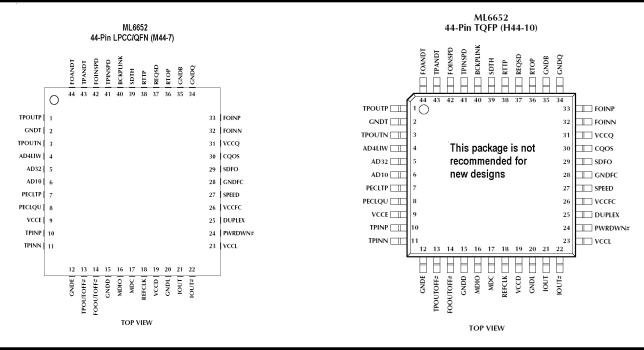

### **PIN CONFIGURATION**

### **PIN DESCRIPTIONS**

#### Signal names followed by "#" indicate active low input.

| Pin No. Signal Name I/O |        | I/O | Description                                                                                                                                                                                                                                                                      |

|-------------------------|--------|-----|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| CONFIG                  |        |     |                                                                                                                                                                                                                                                                                  |

| 4                       | AD4LIW | I   | Sets the value of the Physical Layer (PHY) address bit 4 for accessing the Serial<br>Management Interface, and determines if the Link Integrity Warning (LIW)<br>function is enabled or disabled.<br>The Link Integrity Warning (LIW) function can only be enabled when only one |

|   |      |   | SPEED is available through setting of SPEED (pin 27) and/or management<br>registers. When LIW is enabled and the input link is down at one interface to<br>the Media Converter, the transmitter output on that interface is turned off for<br>about 425ms every 3.8 seconds. It applies to both network interfaces and both<br>data rates. If the link at the other interface to the Media Converter is also<br>down, there is no output. The LIW function causes the Link Up indicator of the<br>link partner to blink.<br>Note: this pin is typically read a few microseconds after power-up, if it is tied<br>to supplies that do not track the ML6652 power improper results will occur.<br>Use VCCD (pin 19) as the pull up point, do not add decoupling capacitors to<br>this input pin (without thoroughly understanding your PCB layout dynamics the<br>safest course is to make short connections and do not add decoupling<br>capacitors to this input pin). |

|---|------|---|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 5 | AD32 | I | Sets the value of the PHY address bits 3 and 2 for accessing the Serial<br>Management Interface.<br>Note: this pin is typically read a few microseconds after power-up, if it is tied<br>to supplies that do not track the ML6652 power improper results will occur.<br>Use VCCD (pin 19) as the pull up point, do not add decoupling capacitors to<br>this input pin (without thoroughly understanding your PCB layout dynamics the<br>safest course is to make short connections and do not add decoupling<br>capacitors to this input pin).                                                                                                                                                                                                                                                                                                                                                                                                                         |

Downloaded from **Elcodis.com** electronic components distributor

| PIN     | PIN DESCRIPTIONS (continued) |     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |  |  |  |

|---------|------------------------------|-----|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| Pin No. | Signal Name                  | I/O | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |  |  |  |  |

| 6       | AD10                         | I   | Sets the value of the PHY address bits 1 and 0 for accessing the Serial<br>Management Interface.<br>Note: this pin is typically read a few microseconds after power-up, if it is tied<br>to supplies that do not track the ML6652 power improper results will occur.<br>Use VCCD (pin 19) as the pull up point, do not add decoupling capacitors to<br>this input pin (without thoroughly understanding your PCB layout dynamics the<br>safest course is to make short connections and do not add decoupling<br>capacitors to this input pin). |  |  |  |  |

| Pin Name    | AD4LIW       |            | AD32       |            | AD10       |            |

|-------------|--------------|------------|------------|------------|------------|------------|

| Input Level | LIW Function | PHYAD4 Bit | PHYAD3 Bit | PHYAD2 Bit | PHYAD1 Bit | PHYAD0 Bit |

| 0           | Disabled     | 0          | 0          | 0          | 0          | 0          |

| 1/3 of VCC  | Enabled      | 0          | 1          | 0          | 1          | 0          |

| 2/3 of VCC  | Enabled      | 1          | 1          | 1          | 1          | 1          |

| VCC         | Disabled     | 1          | 0          | 1          | 0          | 1          |

#### Table 1.

7 PECLTP I The copper interface is selected as shown in Table 2. When twisted pair interface is selected, the scrambler and descrambler are enabled by default and can be disabled with a management register bit. When using twisted pair interface, this pin also defines the maximum supported link distance. When the 10 meters maximum link length is selected, the input is not equalized before being sliced. Note: this pin is typically read a few microseconds after power-up, if it is tied to supplies that do not track the ML6652 power improper results will occur. Use VCCD (pin 19) as the pull up point, do not add decoupling capacitors to this input pin (without thoroughly understanding your PCB layout dynamics the safest course is to make short connections and do not add decoupling capacitors to this input pin).

| PECLTP<br>Voltage | Interfaces at<br>TPINP/TPINN and<br>TPOUTP/TPOUTN | PECLTP<br><30.3><br>Default | Copper<br>Length | SHORTTP<br><30.2><br>Default | Output<br>Current | LOWITPOUT<br><30.4> Default |

|-------------------|---------------------------------------------------|-----------------------------|------------------|------------------------------|-------------------|-----------------------------|

| 0                 | Twisted Pair                                      | 0                           | 100BASE-TX       | 0                            | Standard          | 0                           |

|                   |                                                   |                             | Standard         |                              |                   |                             |

| 1/3 of VCC        | PECL/LVPECL                                       | 1                           | PCB Traces       | 0                            | NA                | 0                           |

| 2/3 of VCC        | Twisted Pair                                      | 0                           | PCB Traces       | 1                            | Low               | 1                           |

| VCC               | Twisted Pair                                      | 0                           | 10m              | 1                            | Standard          | 0                           |

#### Table 2.

Downloaded from Elcodis.com electronic components distributor

5

Pin

| <b>IN D</b> | N DESCRIPTIONS (continued) |     |                                                                                                                                                                       |  |  |  |

|-------------|----------------------------|-----|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| n No.       | Signal Name                | I/O | Description                                                                                                                                                           |  |  |  |

| 8           | PECLQU                     | I   | The fiber interface is selected as shown in Table 3.<br>When using an LED driver and fiber optic receiver, this pin also defines the maximum supported link distance. |  |  |  |

When the 300m maximum link length is selected, the voltage thresholds for Signal Detect are increased.

| PECLQU<br>Voltage | Interfaces at<br>FOINP/FOINN and<br>IOUT/IOUT# | PECLQU<br><30.7><br>Default | Fiber Optic<br>Link Length<br>10BASE/100BASE | SHORTFO<br><30.5><br>Default | Wavelength | LONGWL<br><30.6><br>Default |

|-------------------|------------------------------------------------|-----------------------------|----------------------------------------------|------------------------------|------------|-----------------------------|

| 0                 | Quantizer and LED<br>Driver                    | 0                           | 2Km/300m                                     | 0                            | 850nm      | 0                           |

| 1/3 of VCC        | PECL/LVPECL                                    | 1                           | PCB Traces                                   | 0                            | NA         | 0                           |

| 2/3 of VCC        | Quantizer and LED<br>Driver                    | 0                           | 2Km/2Km                                      | 0                            | 1300nm     | 1                           |

| VCC               | Quantizer and LED<br>Driver                    | 0                           | 300m/300m                                    | 1                            | 850/1300nm | 0                           |

#### Table 3.

Note: The ML6652 fiber interface quantizer sensitivity can be adjusted via Register 30 bits 5, 6 and 7 to accomodate various cable lengths and signal intensity.

25 DUPLEX L This input can have one of three levels: VCC, VCC/2 or 0 Volts. This input has 80kΩ resistors internally connected to both VCC and Ground, generating VCC/ 2 at the input if left unconnected. Settings defined by the DUPLEX power up preset pin can be over written by the management interface. At power up the DUPLEX pin causes the following default values to be written to management register 30. Note: this pin is typically read a few microseconds after power-up, if it is tied to supplies that do not track the ML6652 power improper results will occur. Use VCCD (pin 19) as the pull up point, do not add decoupling capacitors to this input pin (without thoroughly understanding your PCB layout dynamics the safest course is to make short connections and do not add decoupling capacitors to this input pin).

| DUPLEX Voltage | TRANSPARENT#<br><30.11> Default | ADVERTFD#<br><30.10> Default | ADVERTHD#<br><30.15> Default |

|----------------|---------------------------------|------------------------------|------------------------------|

| 0              | 1                               | 1                            | 0                            |

| VCC/2          | 0                               | 0                            | 0                            |

| VCC            | 1                               | 0                            | 0                            |

Table 4.

|    | DESCRIPTION<br>Signal Name | NS (cont<br>I/O | inued)<br>Description                                                                                                                                                                                                                                                                                                                                                                                                        |

|----|----------------------------|-----------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|    |                            |                 | DUPLEX and SPEED can be used concurrently to set the power up mode of the ML6652 see Tables 4 and 6. For Mode details see the General Description section of this data sheet.                                                                                                                                                                                                                                                |

| 27 | SPEED                      | I               | This input can have one of three levels: VCC, VCC/2, and 0Volts. The input has $80k\Omega$ resistors internally connected to both VCC and Ground generating VCC/2 at the input, if left unconnected. Settings defined by the SPEED power up preset pin can be over written by the management interface. At power up the SPEED pin causes the following default values to be written to management register 30.               |

|    |                            |                 | Note: this pin is typically read a few microseconds after power-up. If it is tied to supplies that do not track the ML6652 power, improper results will occur. Use VCCD (pin 19) as the pull up point, do not add decoupling capacitors to this input pin (without thoroughly understanding your PCB layout dynamics the safest course is to make short connections and do not add decoupling capacitors to this input pin). |

| SPEED Voltage | DSBLAN <30.14><br>Default | SINGLESPEED <30.9><br>Default | SEL10Mbps <30.8><br>Default |

|---------------|---------------------------|-------------------------------|-----------------------------|

| 0             | 1                         | 1                             | 1                           |

| VCC/2         | 0                         | 0                             | 0                           |

| VCC           | 1                         | 1                             | 0                           |

### Table 5.

| Mode            | Operating Summary                                       | SPEED Voltage | <b>DUPLEX Voltage</b> |

|-----------------|---------------------------------------------------------|---------------|-----------------------|

| Forced 10       | 10Mbps data rate only available. The Duplex mode        | 0             | N/A                   |

|                 | is selected by the link partner.                        |               |                       |

| Forced 100      | 100Mbps data rate only available. The Duplex mode       | VCC           | N/A                   |

|                 | is selected by the link partner.                        |               |                       |

| Non-Transparent | Only the Half-Duplex mode is advertised. Both 10        | VCC/2         | 0                     |

| Half-Duplex     | and 100Mbps data rates are available. Only the data     |               |                       |

|                 | rate equivalent to the technology present at the fiber  |               |                       |

|                 | optic input interface is advertised.                    |               |                       |

| Non-Transparent | FLP Bursts are generated. Both HalfDuplex and           | VCC/2         | VCC                   |

|                 | Full-Duplex modes are advertised. Both 10 and           |               |                       |

|                 | 100Mbps data rates are available. Only the data rate    |               |                       |

|                 | equivalent to the technology present at the fiber optic |               |                       |

|                 | input interface is advertised.                          |               |                       |

| Transparent     |                                                         |               | VCC/2                 |

|                 | 100Mbps and Auto-Negotiation far end link partner       |               |                       |

|                 | signaling available.                                    |               |                       |

#### Table 6.

January 2004

7

| Pin No | . Signal Name  | 1/0      | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|--------|----------------|----------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| CONTR  |                |          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| 13     | TPOUTOFF#      | I (CMOS) | Active low, the output stage of the twisted pair output is turned off. Contains an on-chip $80k\Omega$ pull-up resister.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| 14     | FOOUTOFF#      | I (CMOS) | Active low, the output stage of the fiber optic output is turned off. Contains an on-chip $80k\Omega$ pull-up resister.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| 24     | PWRDWN#        | I (CMOS) | Active low, all the circuits are powered down. Configuration pins are read and register bits are initialized $5\mu s$ (typ) after a rising edge of PWRDWN#. Contains an on-chip $80k\Omega$ pull-up resister.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| DATA S | IGNAL INPUT/OU |          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| 1      | TPOUTP         | 0        | The two operating modes available for these pins are selected with the configuration pin PECLTP (pin 7) or the configuration bit PECLTP <30.3>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| 3      | TPOUTN         | 0        | Twisted Pair Interface Mode:<br>Transmit twisted pair positive and complementary outputs. These outputs form<br>a differential current output pair that drives Multi Level Transition (MLT-3)<br>waveforms into the network coupling transformer during 100Mbps mode,<br>Manchester encoded 10BASE-T data or Normal Link Pulses (NLPs) during<br>10Mbps mode, and Fast Link Pulse (FLP) Bursts during Auto-Negotiation.<br>TPOUTP and TPOUTN must have external pull up resistors to VCC (refer to<br>description of RTTP pin)<br>PECL/LVPECL Compatible Interface Mode:<br>PECL/LVPECL interface positive and complementary outputs. These outputs<br>form a differential current output pair that drives Non Return to Zero Inverted<br>(NRZI) encoded 100BASE-FX or 100BASE-SX symbols during 100Mbps mode,<br>Manchester encoded 10BASE-FL data or OPT_IDL during 10Mbps mode, and<br>Fiber Link Negotiation Pulse (FLNP) Bursts during Auto-Negotiation. TPOUTP<br>and TPOUTN must have external pull up resistors to VCC and be AC coupled<br>to the inputs of a fiber optic PMD module (refer to description of RTTP pin). A<br>resistor network may be needed to setup the common mode voltage at the<br>input pins of the PMD module |

| 38     | RIIP           | Ι        | Twisted pair PECL/LVPECL compatible driver bias resistor. An external resistor connected between RTTP and ground sets a constant bias current for the differential output driver circuitry TPOUTP/TPOUTN.<br>These output currents depend on the operating mode.<br>The recommended external component values are:<br><b>Twisted Pair Mode:</b><br>$2k\Omega$ , 1%, between RTTP and ground<br>$50\Omega$ , 1%, between TPOUTP and VCC<br>$50\Omega$ , 1%, between TPOUTP and VCC<br><b>PECL Compatible mode:</b><br>$2k\Omega$ , 1%, between RTTP and ground<br>Equivalent $62\Omega$ between TPOUTP and VCC<br>Equivalent $62\Omega$ between TPOUTP and VCC<br>Also AC coupled to the PMD inputs                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| 10     | TPINP          | I        | The two operating modes available for these pins are selected with the configuration pin PECLTP (Pin 7) or the configuration bit PECLTP <30.3>.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| 11     | TPINN          | I        | <b>Twisted Pair Interface Mode:</b><br>Receive twisted pair positive and complementary inputs. These inputs form a differential input pair that receives 100BASE-TX, FLP Burst, or 10BASE-T signal from the network. The common mode voltage is set internally and the differential input resistance is about $2k\Omega$ .<br>The network termination must be added externally. It should contain a $100\Omega$ resister between pin 10 and 11 as shown in Figure 1.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

8

| DINL |                           |                                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|------|---------------------------|-------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|      | DESCRIPTIC<br>Signal Name |                                     | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|      | orginaritatine            | Inpu<br>tran<br>circu<br>H10<br>equ | $\begin{array}{c c} & & & \\ \text{ML6652} \\ \text{sformer} \\ \text{uit Pulse} & 100\Omega \\ \text{ML6652} \\ 10 \\ 10 \\ 10 \\ 10 \\ 10 \\ 10 \\ 10 \\ 1$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| 37   | REQSD                     | 1                                   | <b>PECL/LVPECL Compatible Interface Mode:</b> PECL/LVPECL compatible interface positive and complementary inputs. Theseinputs form a differential input pair that receives 100BASE-FX, 100BASE-SX,FLNP Bursts, or 10BASE-FL signal from a fiber optic PMD. The PMD outputsshould be AC coupled to these inputs with .1µF capacitors. The common modevoltage is set internally with ~1kΩ or so resistors from each input pin to an on-chip voltage reference. The positive output of the PMD (high during the high-light state) must connect to TPINP and the complementary output of the PMDmust connect to TPINNThe two operating modes available for this pin are selected with theconfiguration pin PECLTP or the configuration bit PECLTP <30.3> <b>Twisted Pair Interface Mode:</b> Equalizer bias resistor pin. An external resistor connected between this pin andground sets internal currents that control the receiver's adaptive equalizertransfer function. The recommended resistor value is 5kΩ, 1% <b>PECL/LVPECL Compatible Interface Mode:</b> This input pin is connected to the Signal Detect (SD) output of a fiber opticPMD module. The voltage level at this pin is compared to the voltage level atpin SDTH to determine the logic value. If it is lower, then the input at TPINP/TPINN is rejected. If it is higher, then the input at TPINP/TPINN is passed to theinternal circuits |

|      | 02                        | •                                   | description of SDFO and REQSD pins. This pin is not used if the TPINP/TPINN<br>interface and the FOINP/FOINN are not setup for PECL/LVPECL compatible<br>mode. In such a case, the SDTH pin should be set to VCC                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| 21   | IOUT                      | 0                                   | The two operating modes available for these pins are selected with the configuration pin PECLQU or the configuration bit PECLQU <30.7>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| 22   | IOUT#                     | 0                                   | <b>Fiber Optic Interface Mode:</b><br>IOUT (pin 21) becomes the output connection to the cathode of an external fiber optic LED. The output data is NRZI encoded 100BASE-FX or 100BASE-SX symbols during 100Mbps mode, Manchester encoded 10BASE-FL data or OPT_IDL (10BASE-FL idle signal) during 10Mbps mode, and FLNP Bursts duringAuto-Negotiation.<br>IOUT# (pin 22) is optionally used to provide current peaking. If peaking is                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

9

ML6652

|         | DESCRIPTIC  | -   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|---------|-------------|-----|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Pin No. | Signal Name | I/O | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|         |             |     | <ul> <li>implemented, a 1kΩ off-chip resistor should be connected to ground and a 1nF capacitor connected to IOUT. These components determine the peaking current waveform. When peaking is not used, IOUT# should connect to VCC</li> <li><b>PECL/LVPECL Compatible Interface Mode:</b></li> <li>PECL/LVPECL interface positive and complementary outputs. These outputs form a differential current output pair that drives NRZI encoded 100BASE-SX or 100BASE-FX symbols during 100Mbps mode, Manchester encoded 10BASE-FL data or OPT_IDL during 10Mbps mode, and FLNP Bursts during Auto-Negotiation. IOUT and IOUT# are loaded with external resistors to VCC and AC coupled to the inputs of a fiber optic PMD module (refer to description of RTOP pin). A resistor network may be needed to setup the common mode voltage at the input pins of the PMD module</li> </ul>                                                                                                                                                                    |

| 36      | RTOP        | 0   | <ul> <li>Fiber optic LED or PECL/LVPECL driver bias resistor. An external resistor connected between RTOP and ground sets a constant bias current for the single ended LED driver or differential PECL/LVPECL driver circuitry. These output currents depend on the operating mode.</li> <li>The recommended external component values are:</li> <li>Fiber Optic Interface mode: (1% resistors, +/-10% currents) Indicated is the current into pin IOUT during the High-Light state.</li> <li>2.8kΩ between RTOP and ground for 50mA.</li> <li>2kΩ between RTOP and ground for 70mA.</li> <li>1.4kΩ between RTOP and ground for 100mA.</li> <li>PECL/LVPECLInterfacemode:</li> <li>1.4kΩ, 1%, between RTOP and ground for 10mA current.</li> <li>Equivalent 62Ω between IOUT and VCC.</li> <li>Equivalent 62Ω between IOUT# and VCC.</li> <li>Also AC coupled to PMD inputs</li> </ul>                                                                                                                                                               |

| 33      | FOINP       | I   | The two operating modes available for these pins and are selected with the                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| 32      | FOINN       | Ι   | <ul> <li>configuration pin PECLQU or the configuration bit PECLQU &lt;30.7&gt;</li> <li>Fiber Optic Interface Mode:</li> <li>Fiber optic quantizer positive and complementary inputs. FOINP is capacitively coupled to the output of a fiber optic receiver, while FOINN is capacitively coupled to the VCC of the fiber optic receiver. Recommended capacitor values: 10nF, 5%. FOINP voltage must be higher during the "high light" state than during the low-light state</li> <li>PECL/LVPECL Compatible Interface Mode:</li> <li>PECL/LVPECL interface positive and complementary inputs. These inputs form a differential input pair that receives 100BASE-FX, 100BASE-SX, FLNP Bursts or 10BASE-FL signal from a fiber optic PMD. The PMD outputs are AC coupled to these inputs with 10nF, 5% capacitors. The common mode voltage is set internally with ~900Ω (or so) resistors from each input pin to an on-chip voltage reference. FOINP voltage must be higher during the "high light" state than during the "low light" state</li> </ul> |

| 30      | CQOS        |     | Data quantizer offset cancellation loop capacitor. An external capacitor between this pin and VCC determines the dominant pole of the offset cancellation feedback loop. The recommended value is .1µF, 10%. It is only required in "Fiber Optic Interface" mode.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| 29      | SDFO        | I   | The two operating modes available for this pin are selected with the configuration pin PECLQU or the configuration bit PECLQU <30.7><br><b>Fiber Optic Interface Mode:</b><br>This pin is not used and should be connected to VCC.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| PIN     | PIN DESCRIPTIONS (continued) |     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |  |  |  |  |  |  |

|---------|------------------------------|-----|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|

| Pin No. | Signal Name                  | I/O | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |  |  |  |  |  |  |

|         |                              |     | <b>PECL/LVPECL Compatible Interface Mode:</b><br>This input pin is connected to the Signal Detect (SD) output of a fiber optic<br>PMD. The voltage level at this pin is compared to the voltage level at pin<br>SDTH to determine the logic value. If it is lower than the input at FOINP/<br>FOINN is rejected. If it is higher than the input at FOINP/FOINN is passed to<br>the internal circuits.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |  |  |  |  |  |  |

|         | P LINK FUNCTION              |     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |  |  |  |  |  |  |

| 40      | BCKPLINK                     | I/O | <ul> <li>INPUT MODE:</li> <li>At power up, pin 40 (BCKPLINK) is read and the BCKPDIS register &lt;28.1&gt; is set appropriately. A high (VCC) at power up causes Register 28, Bit 1 (BCKPDIS) to be set high (1) disabling the Back-up link function. BCKPDIS can subsequently be over written by the management interface at any time. Note: This pin is typically read a few microseconds after power-up, if it is tied to supplies that do not track the ML6652 power, improper results may occur. For BCKPLINK, use VCCD (pin 19) as the pull up point, do not add decoupling capacitors to Pin 40 (without thoroughly understanding your PCB layout power up dynamics the safest course is to make short connections and do not add decoupling capacitors to this pin).</li> <li>OUTPUT MODE:</li> <li>After power-up, BCKPLINK is used as an output. It is Active high to enable a secondary fiber link via a second ML6652 device (see Functional Description, Backup Link Mode in this data sheet for details).</li> <li>Use this function in forced 100Mbps mode, non loopback only</li> </ul> |  |  |  |  |  |  |

| LED STA | TUS                          |     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |  |  |  |  |  |  |

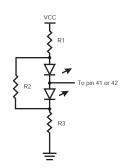

| 41      | TPINSPD                      | 0   | This output goes high to indicate that a 100Mbps signal is present at the TPINP/<br>TPINN interface, and it goes low to indicate that a 10Mbps signal is present at<br>the TPINP/TPINN interface. The signal can be idle or packets. This pin is set to<br>high impedance otherwise.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |  |  |  |  |  |  |

| 42      | FOINSPD                      | 0   | This output goes high to indicate that a 100Mbps signal is present at the FOINP/FOINN interface, and it goes low to indicate that a 10Mbps signal is present at the FOINP/FOINN interface. The signal can be idle or packets. This pin is set to high impedance otherwise.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |  |  |  |  |  |  |

| 43      | TPANDT                       | 0   | When TPINSPD is in the high impedance state, no 10 or 100Mbps signal at TPINP/TPINN, the TPANDT LED pulls low while receiving Auto-Negotiation signal at the TPINP/TPINN interface. When TPINSPD is not in the high impedance state, the TPANDT pin pulls low to indicate that a data packet is being detected at the TPINP/TPINN interface. When a data packet is indicated, the pulse width at TPANDT is stretched to a minimum of 1.3 to 2.7ms to improve visibility. In any other case this pin is in high impedance state.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |  |  |  |  |  |  |

| PIN     | PIN DESCRIPTIONS (continued) |     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |  |  |  |  |  |

|---------|------------------------------|-----|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| Pin No. | Signal Name                  | I/O | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |  |  |  |  |  |

| LED ST/ | ATUS (CONTINUEI              | D)  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |  |  |  |  |  |

|         | FOANDT                       | 0   | When FOINSPD is in the high impedance state, no 10 or 100Mbps signal at FOINP/FOINN, the FOANDT LED pulls low while receiving Auto-Negotiation signal at the FOINP/FOINN interface. When FOINSPD is not in the high impedance state, the FOANDT pin pulls low to indicate that a data packet is being detected at the FOINP/FOINN interface. When a data packet is indicated, the pulse width at FOANDT is stretched to a minimum of 1.3 to 2.7ms to improve visibility. In any other case this pin is in high impedance state. |  |  |  |  |  |

|         | EMENT INTERFAC               | E   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |  |  |  |  |  |

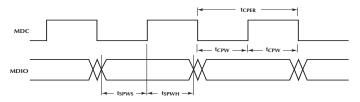

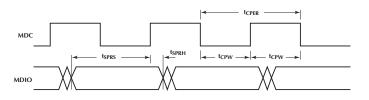

| 16      | MDIO                         |     | Management data TTL compatible input/output pin. Connect to ground if<br>unused                                                                                                                                                                                                                                                                                                                                                                                                                                                 |  |  |  |  |  |

| 17      | MDC                          |     | Management clock TTL input. The maximum frequency can be 12.5MHz instead of the 2.5MHz limit of IEEE 802.3. Connect to ground if unused                                                                                                                                                                                                                                                                                                                                                                                         |  |  |  |  |  |

|         | NCE CLOCK                    |     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |  |  |  |  |  |

| 18      | REFCLK                       |     | 25MHz Reference Clock CMOS input. This clock is used for internal digital<br>logic, and as a reference for the PLLs.                                                                                                                                                                                                                                                                                                                                                                                                            |  |  |  |  |  |

|         | AND GROUND                   |     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |  |  |  |  |  |

| 2       | GNDT                         |     | Ground for the twisted pair driver output stage.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |  |  |  |  |